MIKROKONTROLER 8051 Mikrokontroler q q q Mali raunar

- Slides: 65

MIKROKONTROLER 8051

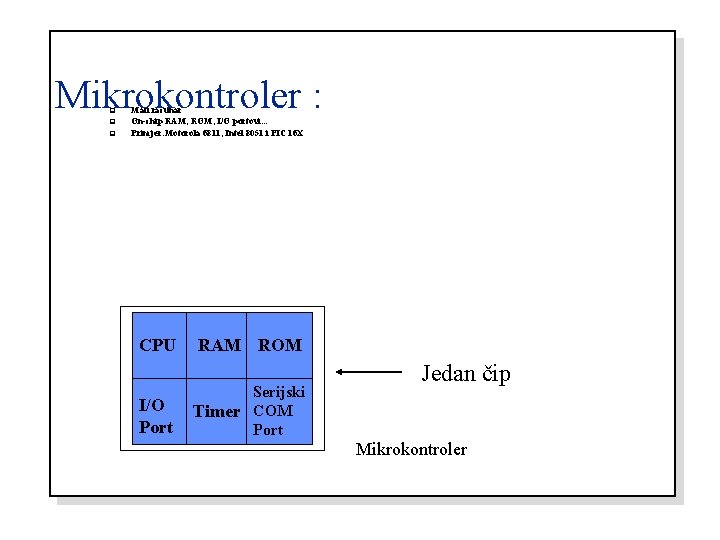

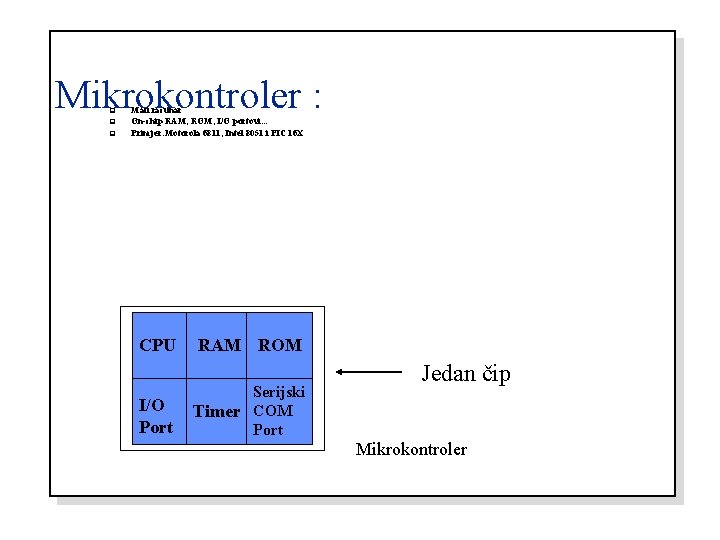

Mikrokontroler : q q q Mali računar On-chip RAM, ROM, I/O portovi. . . Primjer: Motorola 6811, Intel 8051 i PIC 16 X CPU I/O Port RAM ROM Serijski Timer COM Port Jedan čip Mikrokontroler

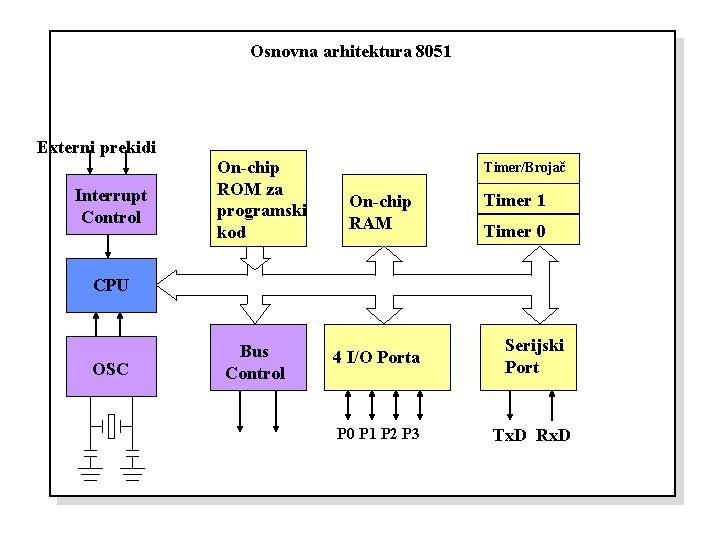

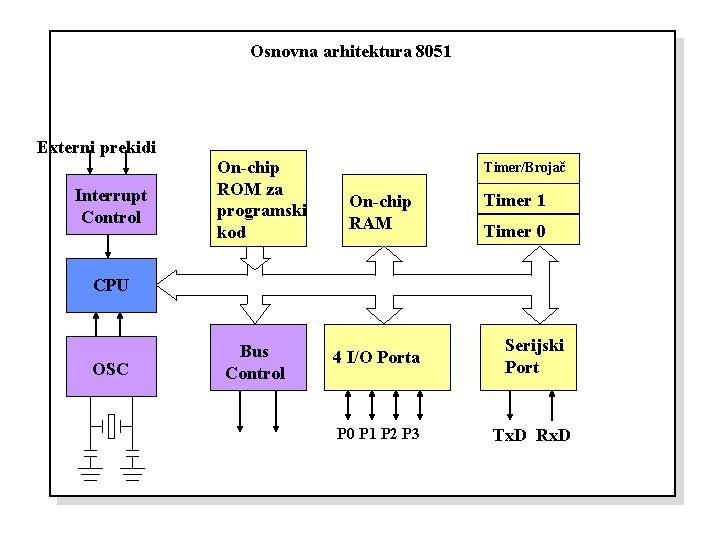

Osnovna arhitektura 8051 Externi prekidi Interrupt Control On-chip ROM za programski kod Timer/Brojač On-chip RAM Timer 1 Timer 0 CPU OSC Bus Control 4 I/O Porta Serijski Port P 0 P 1 P 2 P 3 Tx. D Rx. D

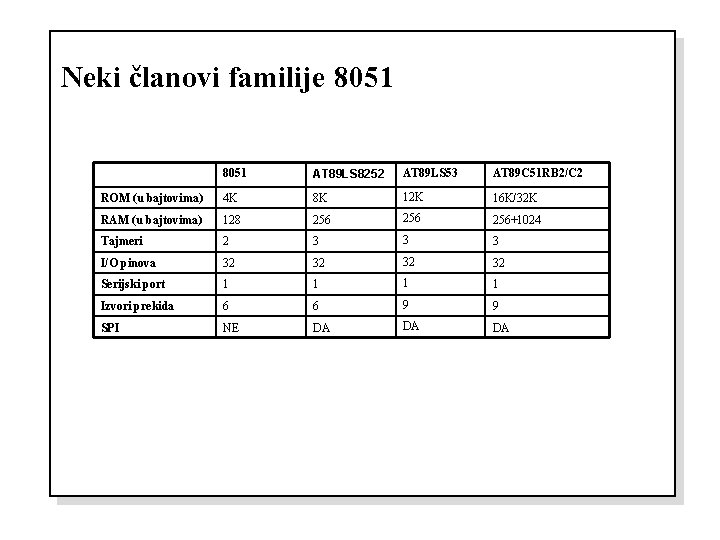

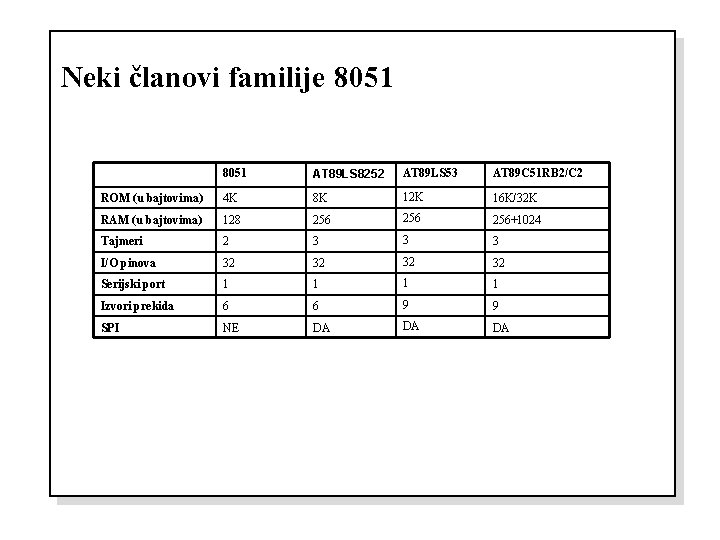

Neki članovi familije 8051 AT 89 LS 8252 AT 89 LS 53 AT 89 C 51 RB 2/C 2 ROM (u bajtovima) 4 K 8 K 12 K 16 K/32 K RAM (u bajtovima) 128 256 256+1024 Tajmeri 2 3 3 3 I/O pinova 32 32 Serijski port 1 1 Izvori prekida 6 6 9 9 SPI NE DA DA DA

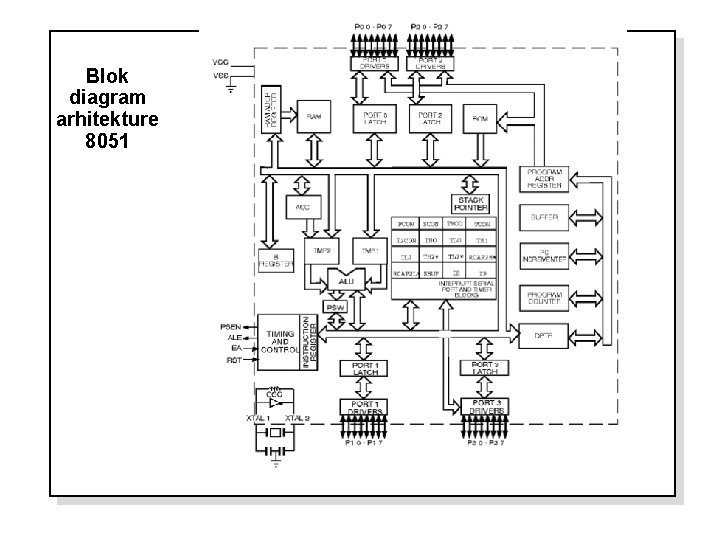

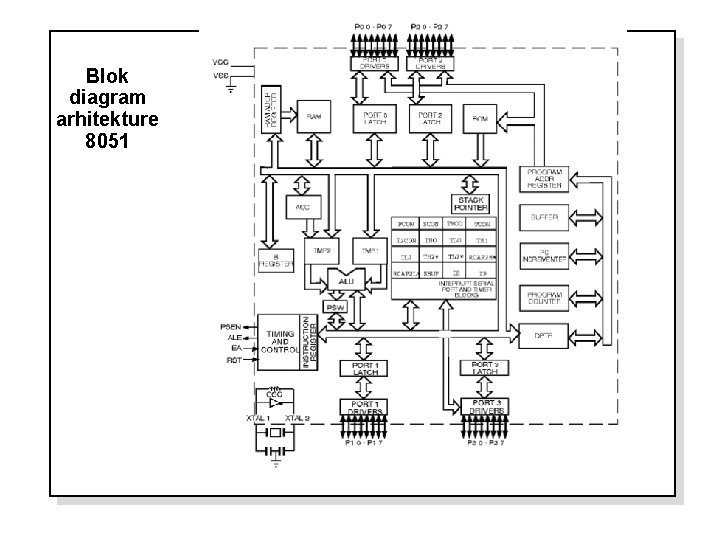

Blok diagram arhitekture 8051

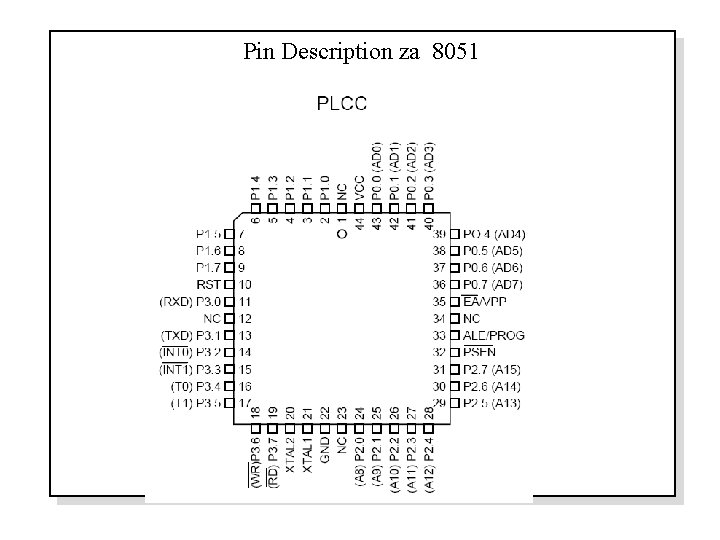

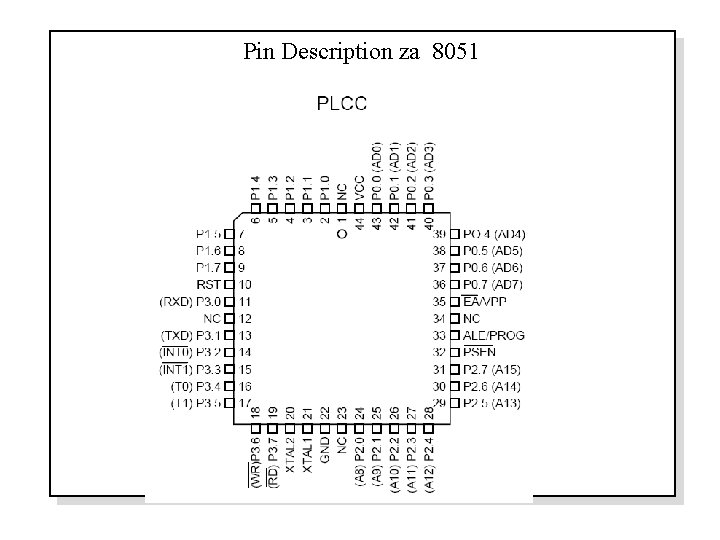

Pin Description za 8051

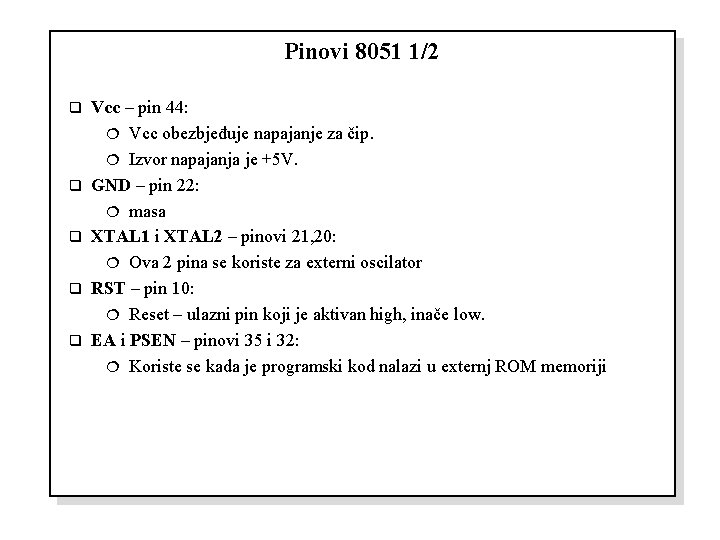

Pinovi 8051 1/2 q q q Vcc – pin 44: ¦ Vcc obezbjeđuje napajanje za čip. ¦ Izvor napajanja je +5 V. GND – pin 22: ¦ masa XTAL 1 i XTAL 2 – pinovi 21, 20: ¦ Ova 2 pina se koriste za externi oscilator RST – pin 10: ¦ Reset – ulazni pin koji je aktivan high, inače low. EA i PSEN – pinovi 35 i 32: ¦ Koriste se kada je programski kod nalazi u externj ROM memoriji

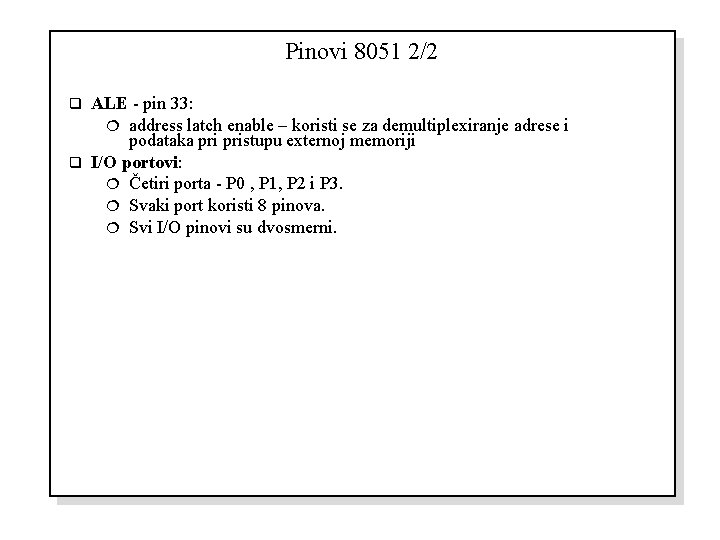

Pinovi 8051 2/2 ALE - pin 33: ¦ address latch enable – koristi se za demultiplexiranje adrese i podataka pristupu externoj memoriji q I/O portovi: ¦ Četiri porta - P 0 , P 1, P 2 i P 3. ¦ Svaki port koristi 8 pinova. ¦ Svi I/O pinovi su dvosmerni. q

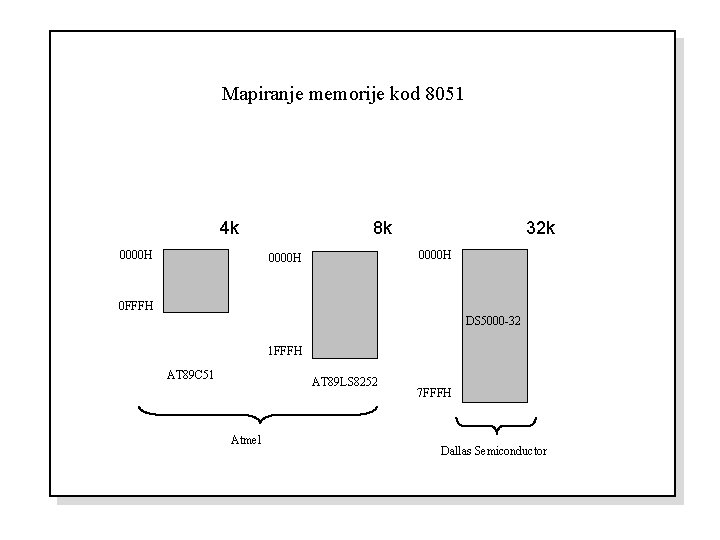

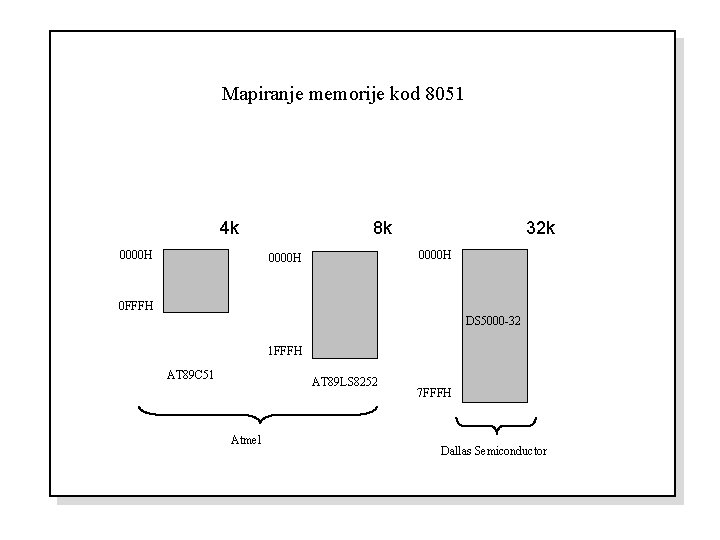

Mapiranje memorije kod 8051 4 k 0000 H 8 k 32 k 0000 H 0 FFFH DS 5000 -32 1 FFFH AT 89 C 51 AT 89 LS 8252 Atmel 7 FFFH Dallas Semiconductor

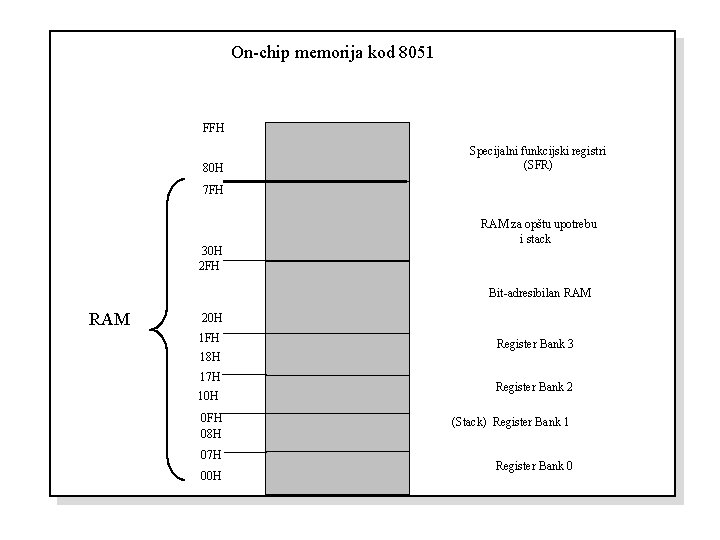

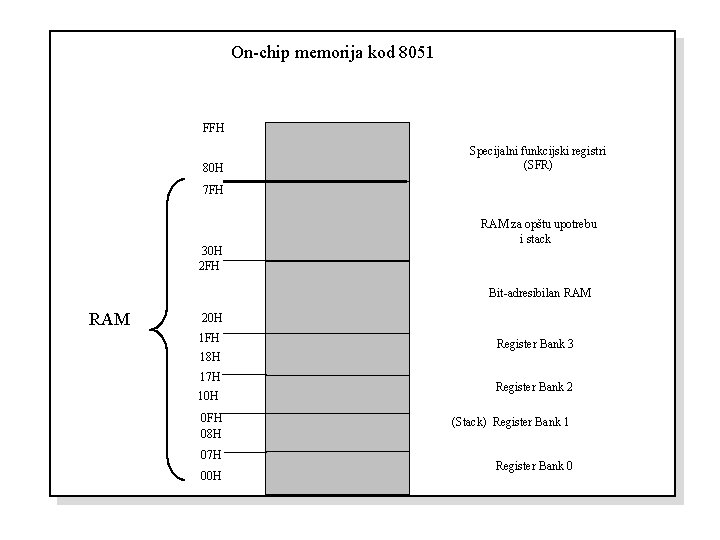

On-chip memorija kod 8051 FFH 80 H Specijalni funkcijski registri (SFR) 7 FH 30 H 2 FH RAM za opštu upotrebu i stack Bit-adresibilan RAM 20 H 1 FH 18 H 17 H 10 H 0 FH 08 H 07 H 00 H Register Bank 3 Register Bank 2 (Stack) Register Bank 1 Register Bank 0

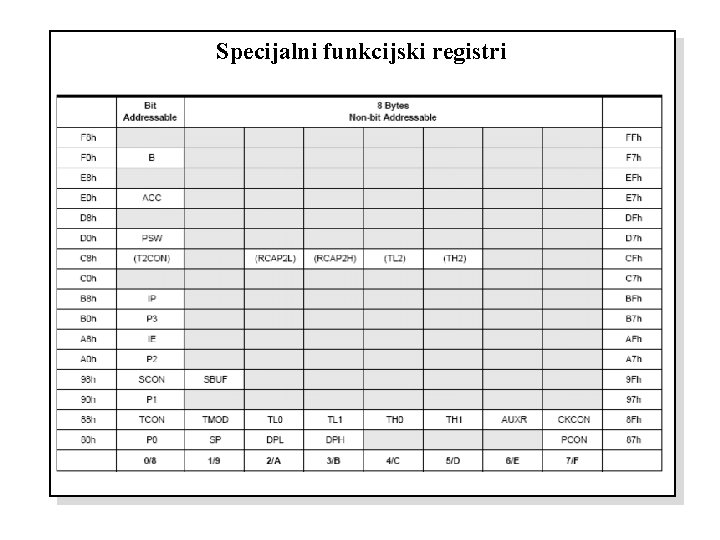

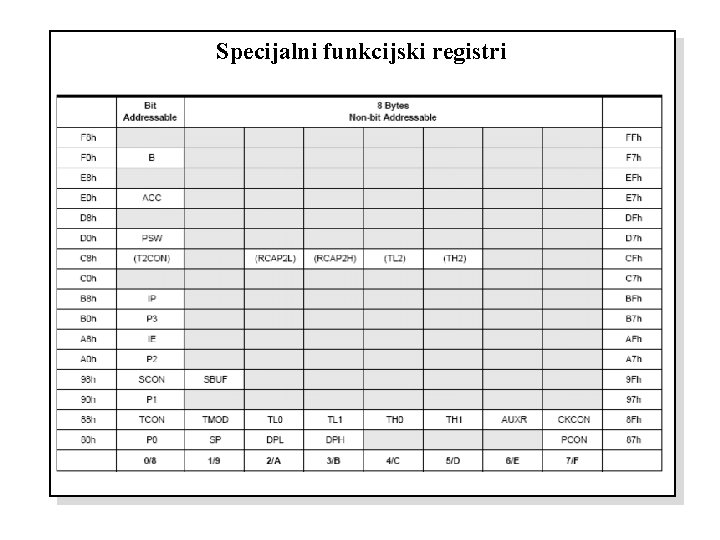

Specijalni funkcijski registri

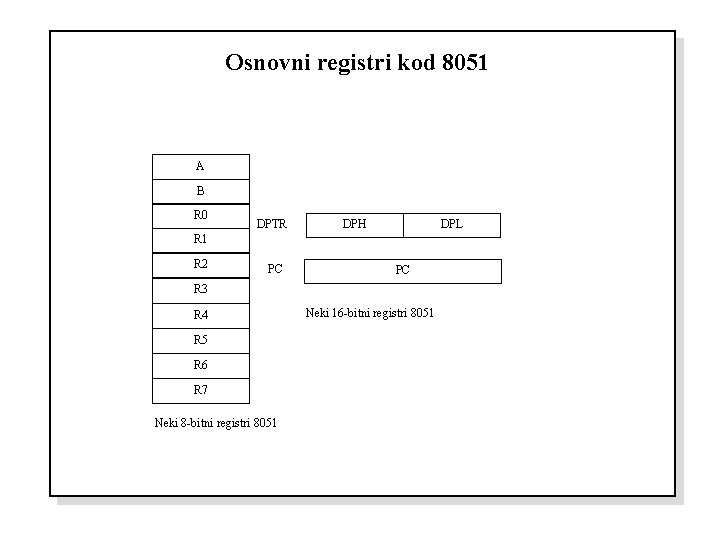

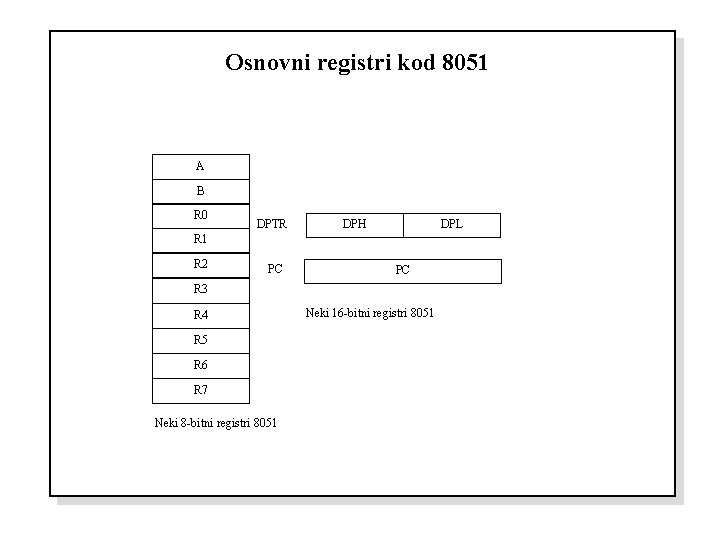

Osnovni registri kod 8051 A B R 0 DPTR DPH DPL R 1 R 2 PC PC R 3 R 4 R 5 R 6 R 7 Neki 8 -bitni registri 8051 Neki 16 -bitni registri 8051

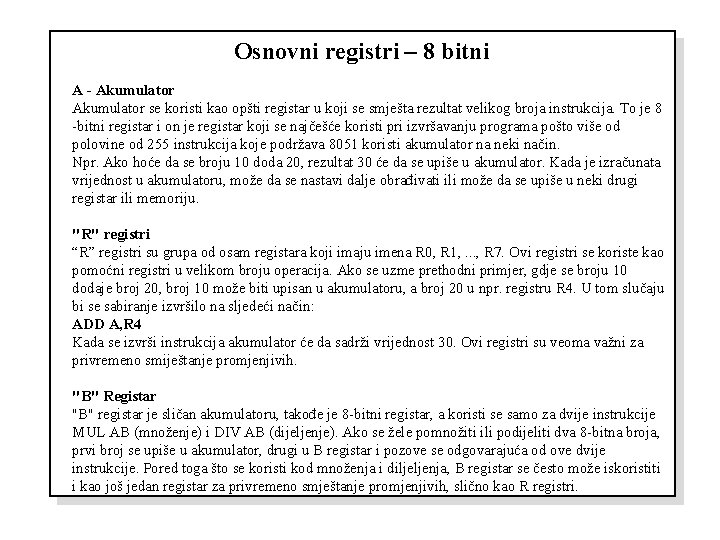

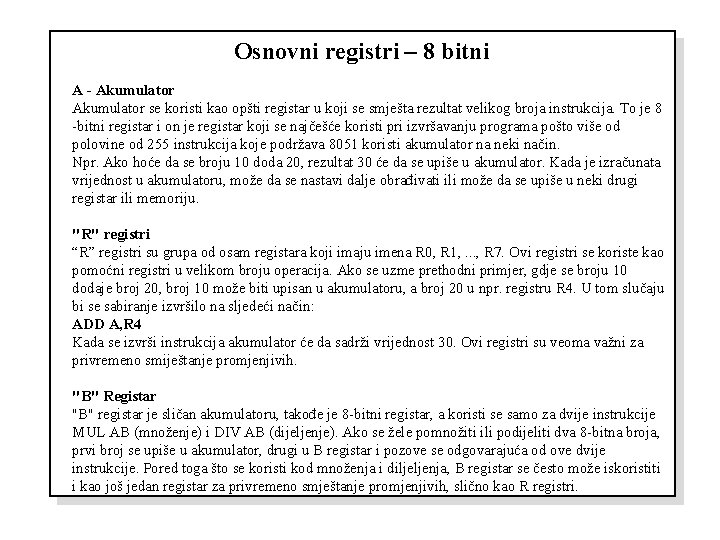

Osnovni registri – 8 bitni A - Akumulator se koristi kao opšti registar u koji se smješta rezultat velikog broja instrukcija. To je 8 -bitni registar i on je registar koji se najčešće koristi pri izvršavanju programa pošto više od polovine od 255 instrukcija koje podržava 8051 koristi akumulator na neki način. Npr. Ako hoće da se broju 10 doda 20, rezultat 30 će da se upiše u akumulator. Kada je izračunata vrijednost u akumulatoru, može da se nastavi dalje obrađivati ili može da se upiše u neki drugi registar ili memoriju. "R" registri “R” registri su grupa od osam registara koji imaju imena R 0, R 1, . . . , R 7. Ovi registri se koriste kao pomoćni registri u velikom broju operacija. Ako se uzme prethodni primjer, gdje se broju 10 dodaje broj 20, broj 10 može biti upisan u akumulatoru, a broj 20 u npr. registru R 4. U tom slučaju bi se sabiranje izvršilo na sljedeći način: ADD A, R 4 Kada se izvrši instrukcija akumulator će da sadrži vrijednost 30. Ovi registri su veoma važni za privremeno smiještanje promjenjivih. "B" Registar "B" registar je sličan akumulatoru, takođe je 8 -bitni registar, a koristi se samo za dvije instrukcije MUL AB (množenje) i DIV AB (dijeljenje). Ako se žele pomnožiti ili podijeliti dva 8 -bitna broja, prvi broj se upiše u akumulator, drugi u B registar i pozove se odgovarajuća od ove dvije instrukcije. Pored toga što se koristi kod množenja i diljeljenja, B registar se često može iskoristiti i kao još jedan registar za privremeno smještanje promjenjivih, slično kao R registri.

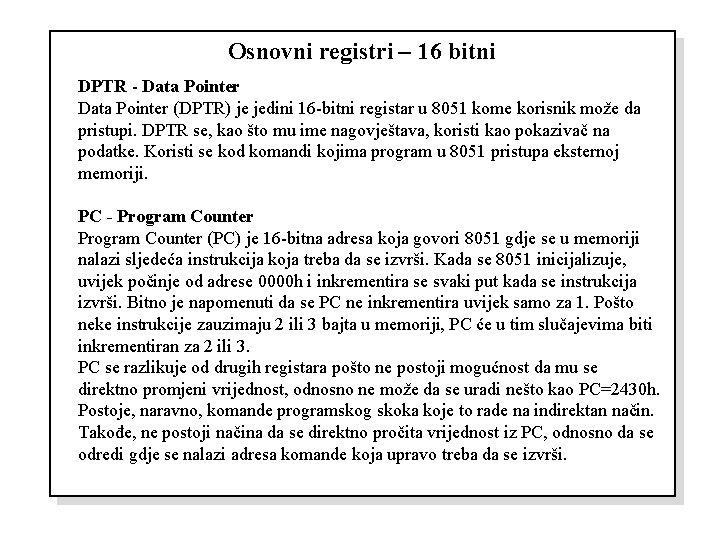

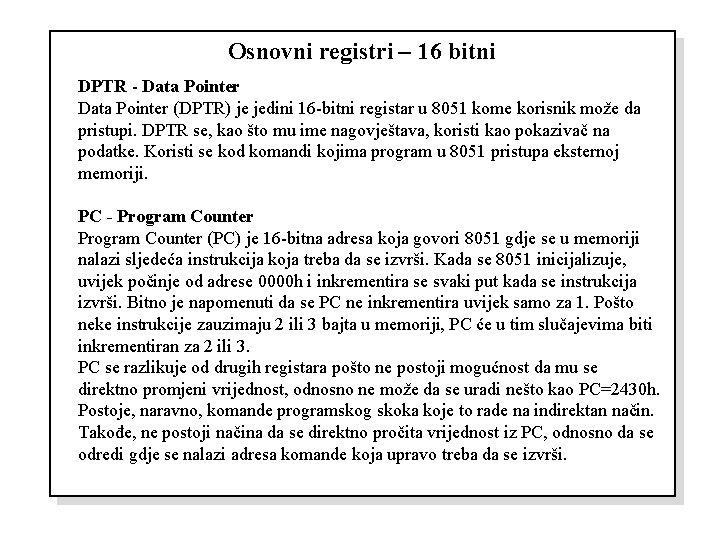

Osnovni registri – 16 bitni DPTR - Data Pointer (DPTR) je jedini 16 -bitni registar u 8051 kome korisnik može da pristupi. DPTR se, kao što mu ime nagovještava, koristi kao pokazivač na podatke. Koristi se kod komandi kojima program u 8051 pristupa eksternoj memoriji. PC - Program Counter (PC) je 16 -bitna adresa koja govori 8051 gdje se u memoriji nalazi sljedeća instrukcija koja treba da se izvrši. Kada se 8051 inicijalizuje, uvijek počinje od adrese 0000 h i inkrementira se svaki put kada se instrukcija izvrši. Bitno je napomenuti da se PC ne inkrementira uvijek samo za 1. Pošto neke instrukcije zauzimaju 2 ili 3 bajta u memoriji, PC će u tim slučajevima biti inkrementiran za 2 ili 3. PC se razlikuje od drugih registara pošto ne postoji mogućnost da mu se direktno promjeni vrijednost, odnosno ne može da se uradi nešto kao PC=2430 h. Postoje, naravno, komande programskog skoka koje to rade na indirektan način. Takođe, ne postoji načina da se direktno pročita vrijednost iz PC, odnosno da se odredi gdje se nalazi adresa komande koja upravo treba da se izvrši.

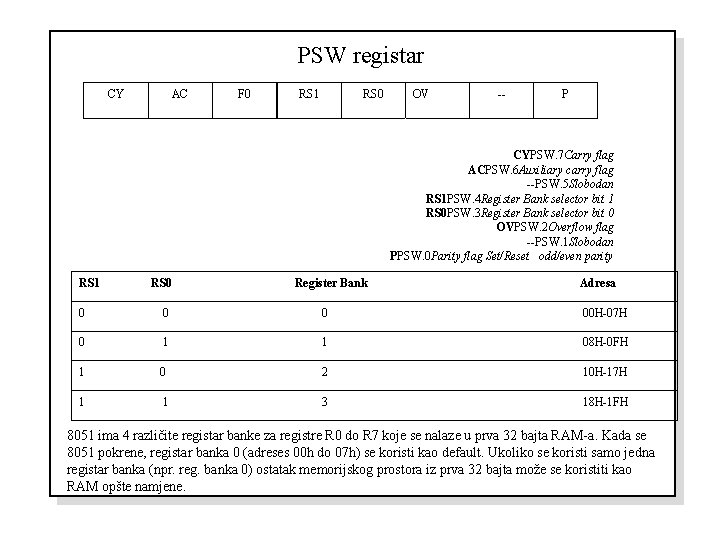

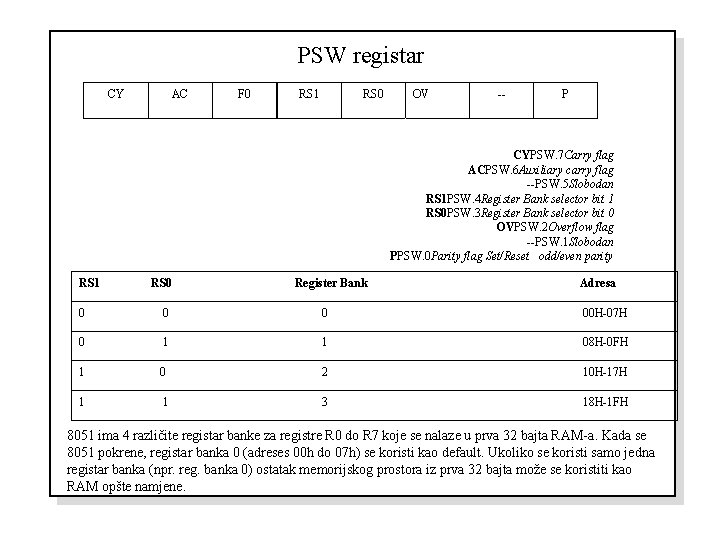

PSW registar CY AC F 0 RS 1 RS 0 OV -- P CYPSW. 7 Carry flag ACPSW. 6 Auxiliary carry flag --PSW. 5 Slobodan RS 1 PSW. 4 Register Bank selector bit 1 RS 0 PSW. 3 Register Bank selector bit 0 OVPSW. 2 Overflow flag --PSW. 1 Slobodan PPSW. 0 Parity flag Set/Reset odd/even parity RS 1 RS 0 Register Bank Adresa 0 00 H-07 H 0 1 1 08 H-0 FH 1 0 2 10 H-17 H 1 1 3 18 H-1 FH 8051 ima 4 različite registar banke za registre R 0 do R 7 koje se nalaze u prva 32 bajta RAM-a. Kada se 8051 pokrene, registar banka 0 (adreses 00 h do 07 h) se koristi kao default. Ukoliko se koristi samo jedna registar banka (npr. reg. banka 0) ostatak memorijskog prostora iz prva 32 bajta može se koristiti kao RAM opšte namjene.

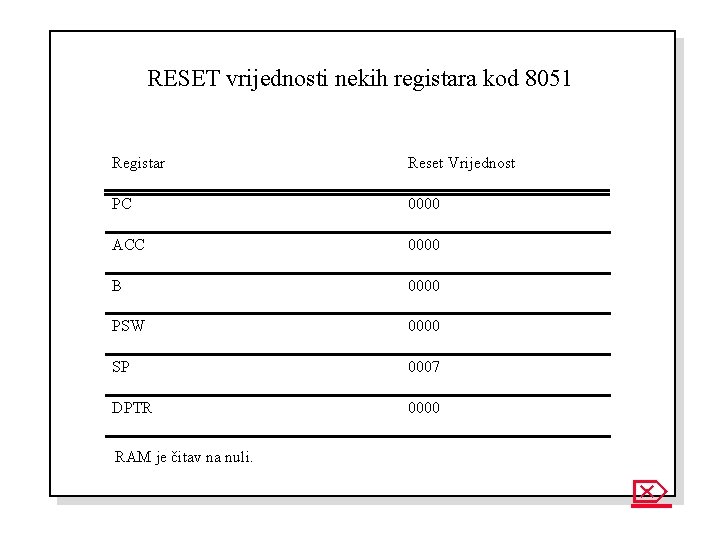

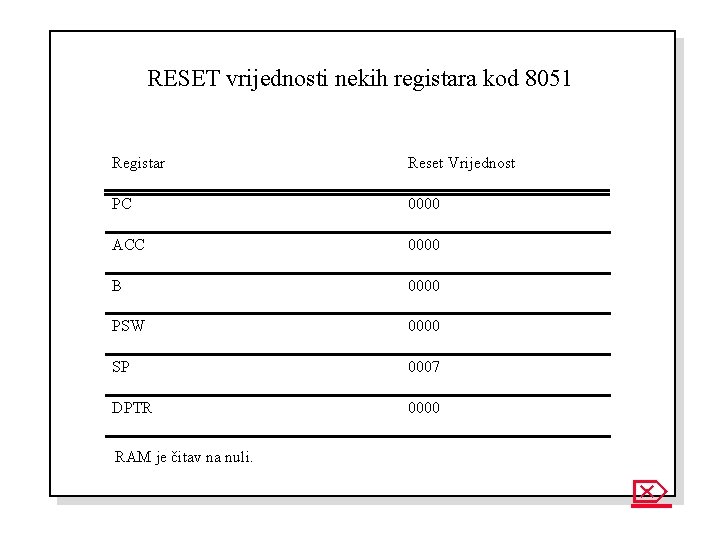

RESET vrijednosti nekih registara kod 8051 Registar Reset Vrijednost PC 0000 ACC 0000 B 0000 PSW 0000 SP 0007 DPTR 0000 RAM je čitav na nuli.

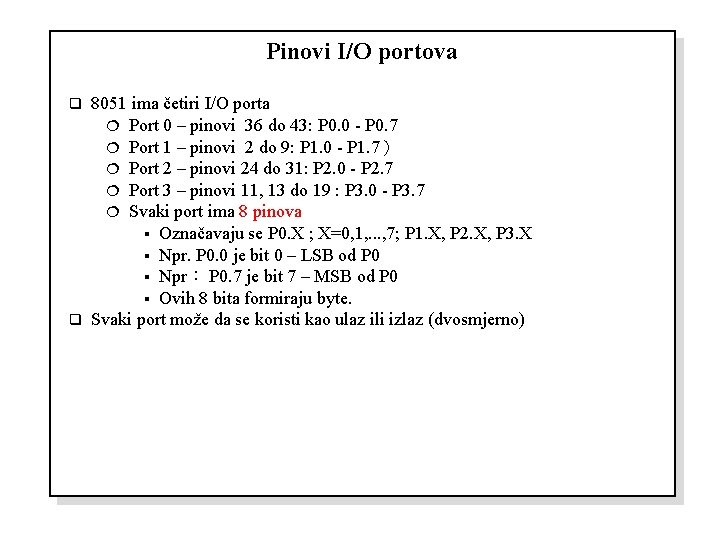

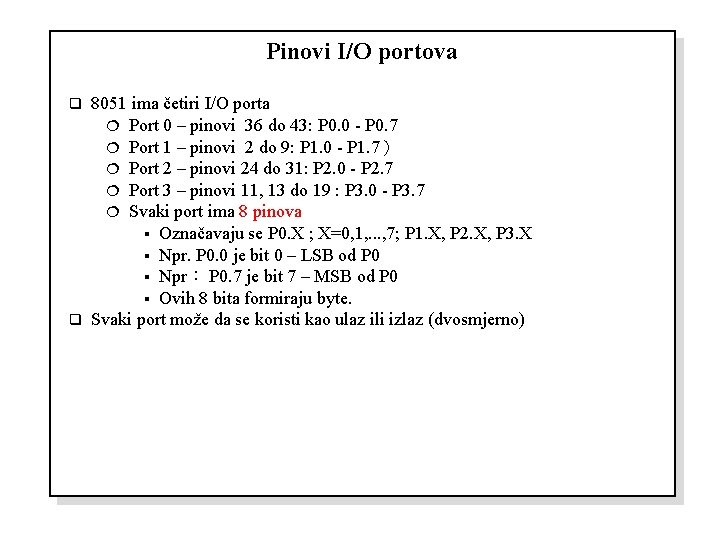

Pinovi I/O portova 8051 ima četiri I/O porta ¦ Port 0 – pinovi 36 do 43: P 0. 0 - P 0. 7 ¦ Port 1 – pinovi 2 do 9: P 1. 0 - P 1. 7) ¦ Port 2 – pinovi 24 do 31: P 2. 0 - P 2. 7 ¦ Port 3 – pinovi 11, 13 do 19 : P 3. 0 - P 3. 7 ¦ Svaki port ima 8 pinova § Označavaju se P 0. X ; X=0, 1, . . . , 7; P 1. X, P 2. X, P 3. X § Npr. P 0. 0 je bit 0 – LSB od P 0 § Npr: P 0. 7 je bit 7 – MSB od P 0 § Ovih 8 bita formiraju byte. q Svaki port može da se koristi kao ulaz ili izlaz (dvosmjerno) q

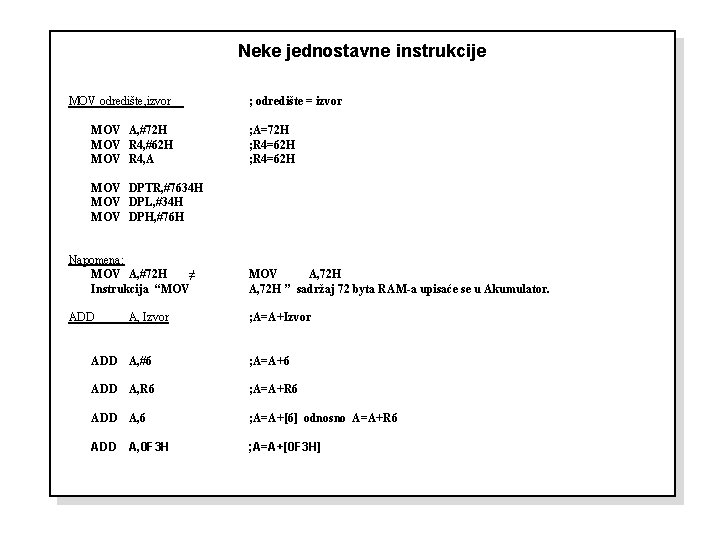

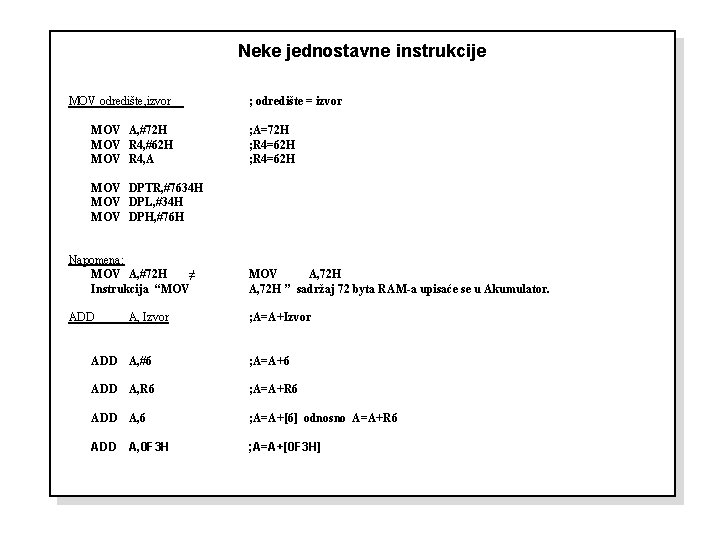

Neke jednostavne instrukcije MOV odredište, izvor MOV A, #72 H MOV R 4, #62 H MOV R 4, A ; odredište = izvor ; A=72 H ; R 4=62 H MOV DPTR, #7634 H MOV DPL, #34 H MOV DPH, #76 H Napomena: MOV A, #72 H ≠ Instrukcija “MOV A, 72 H ” sadržaj 72 byta RAM-a upisaće se u Akumulator. ADD ; A=A+Izvor A, Izvor ADD A, #6 ; A=A+6 ADD A, R 6 ; A=A+R 6 ADD A, 6 ; A=A+[6] odnosno A=A+R 6 ADD A, 0 F 3 H ; A=A+[0 F 3 H]

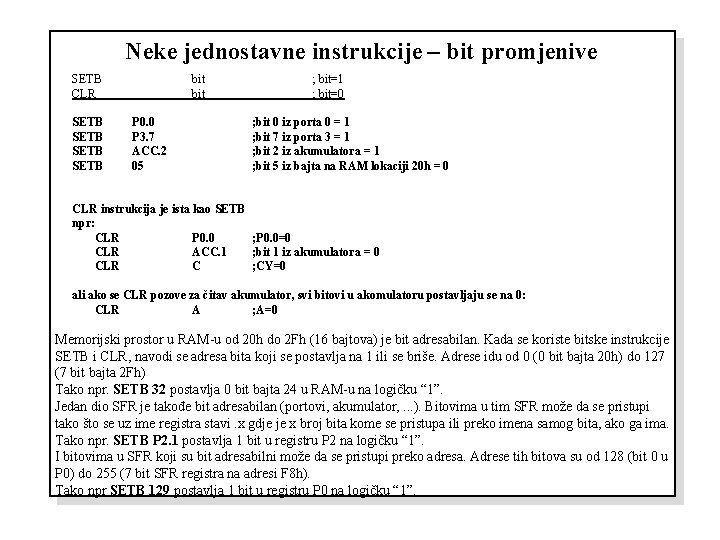

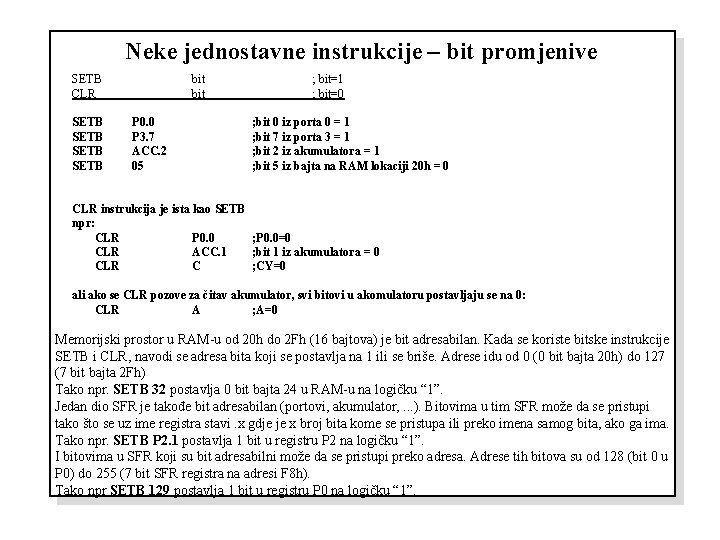

Neke jednostavne instrukcije – bit promjenive SETB CLR SETB bit P 0. 0 P 3. 7 ACC. 2 05 ; bit=1 ; bit=0 ; bit 0 iz porta 0 = 1 ; bit 7 iz porta 3 = 1 ; bit 2 iz akumulatora = 1 ; bit 5 iz bajta na RAM lokaciji 20 h = 0 CLR instrukcija je ista kao SETB npr: CLR P 0. 0 ; P 0. 0=0 CLR ACC. 1 ; bit 1 iz akumulatora = 0 CLR C ; CY=0 ali ako se CLR pozove za čitav akumulator, svi bitovi u akomulatoru postavljaju se na 0: CLR A ; A=0 Memorijski prostor u RAM-u od 20 h do 2 Fh (16 bajtova) je bit adresabilan. Kada se koriste bitske instrukcije SETB i CLR, navodi se adresa bita koji se postavlja na 1 ili se briše. Adrese idu od 0 (0 bit bajta 20 h) do 127 (7 bit bajta 2 Fh) Tako npr. SETB 32 postavlja 0 bit bajta 24 u RAM-u na logičku “ 1”. Jedan dio SFR je takođe bit adresabilan (portovi, akumulator, . . . ). Bitovima u tim SFR može da se pristupi tako što se uz ime registra stavi. x gdje je x broj bita kome se pristupa ili preko imena samog bita, ako ga ima. Tako npr. SETB P 2. 1 postavlja 1 bit u registru P 2 na logičku “ 1”. I bitovima u SFR koji su bit adresabilni može da se pristupi preko adresa. Adrese tih bitova su od 128 (bit 0 u P 0) do 255 (7 bit SFR registra na adresi F 8 h). Tako npr SETB 129 postavlja 1 bit u registru P 0 na logičku “ 1”.

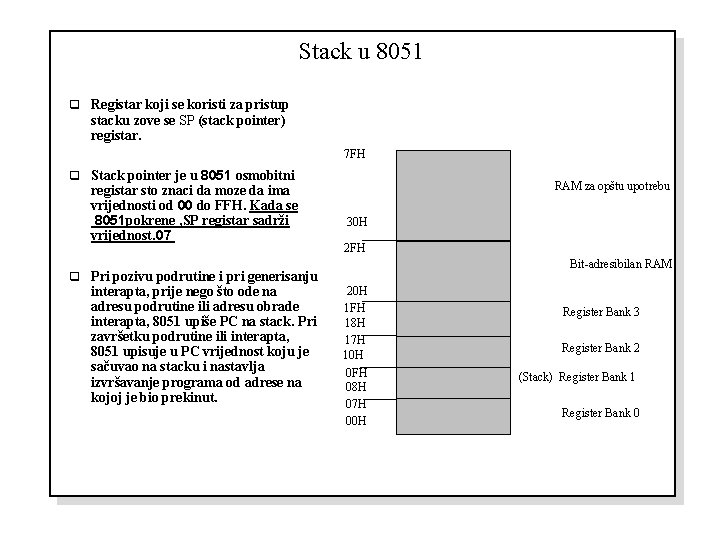

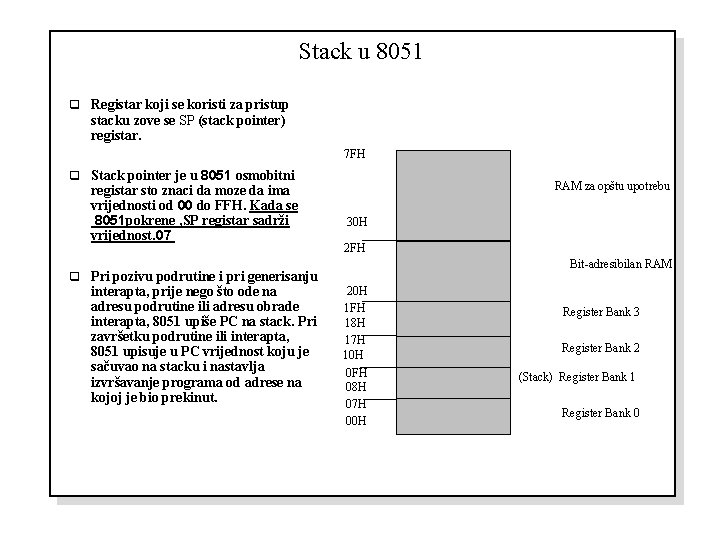

Stack u 8051 q Registar koji se koristi za pristup stacku zove se SP (stack pointer) registar. 7 FH q q Stack pointer je u 8051 osmobitni registar sto znaci da moze da ima vrijednosti od 00 do FFH. Kada se 8051 pokrene , SP registar sadrži vrijednost. 07 Pri pozivu podrutine i pri generisanju interapta, prije nego što ode na adresu podrutine ili adresu obrade interapta, 8051 upiše PC na stack. Pri završetku podrutine ili interapta, 8051 upisuje u PC vrijednost koju je sačuvao na stacku i nastavlja izvršavanje programa od adrese na kojoj je bio prekinut. RAM za opštu upotrebu 30 H 2 FH Bit-adresibilan RAM 20 H 1 FH 18 H 17 H 10 H 0 FH 08 H 07 H 00 H Register Bank 3 Register Bank 2 (Stack) Register Bank 1 Register Bank 0

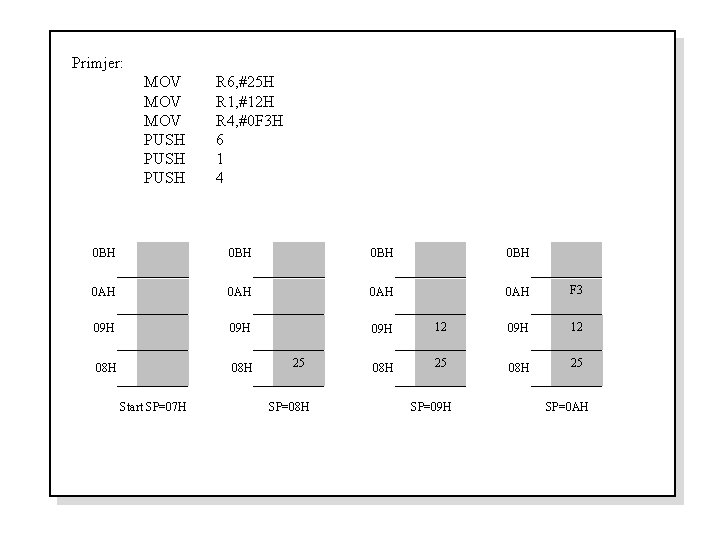

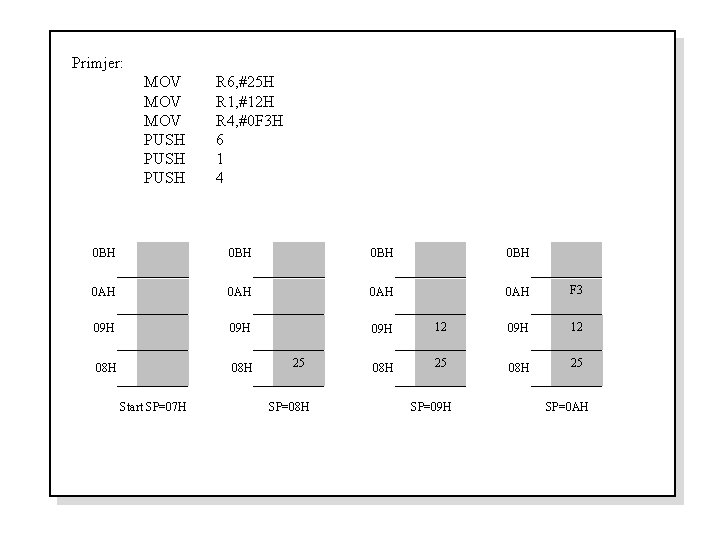

Primjer: MOV MOV PUSH R 6, #25 H R 1, #12 H R 4, #0 F 3 H 6 1 4 0 BH 0 BH 0 AH 0 AH F 3 09 H 09 H 12 08 H 08 H 25 Start SP=07 H 25 SP=08 H SP=09 H SP=0 AH

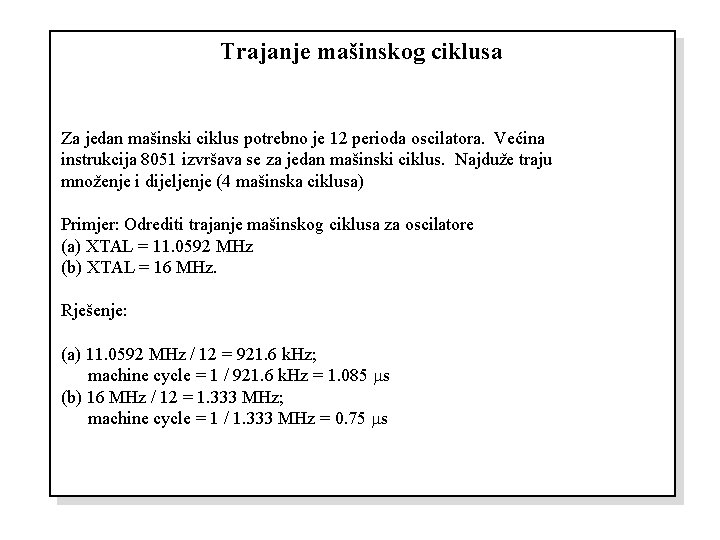

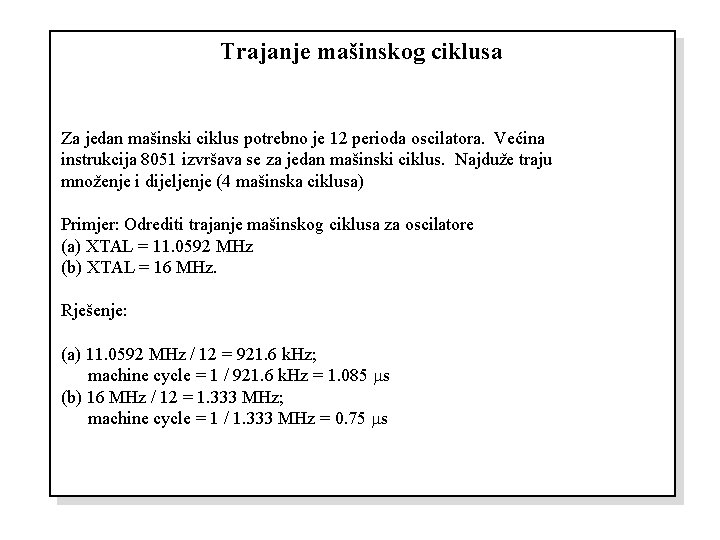

Trajanje mašinskog ciklusa Za jedan mašinski ciklus potrebno je 12 perioda oscilatora. Većina instrukcija 8051 izvršava se za jedan mašinski ciklus. Najduže traju množenje i dijeljenje (4 mašinska ciklusa) Primjer: Odrediti trajanje mašinskog ciklusa za oscilatore (a) XTAL = 11. 0592 MHz (b) XTAL = 16 MHz. Rješenje: (a) 11. 0592 MHz / 12 = 921. 6 k. Hz; machine cycle = 1 / 921. 6 k. Hz = 1. 085 s (b) 16 MHz / 12 = 1. 333 MHz; machine cycle = 1 / 1. 333 MHz = 0. 75 s

Načini adresiranja q q q Neposredno adresiranje Adresiranje preko registara Direktno adresiranje Indirektno adresiranje Adresiranje eksterne memorije Adresiranje ROM memorije

Neposredni način adresiranja Neposredno adresiranje se zove tako jer vrijednost koja se upisuje u memoriju neposredno dolazi iza izvršnog koda u memoriji. Na taj način, instrukcija sama diktira koja vrijednost će biti upisana u memoriju Na primjer, instrukcija: MOV A, #20 h Ova instrukcija koristi neposredno adresiranje jer će u akumulator biti upisana vrijednost koja neposredno dolazi iza izvršnog koda - u ovom slučaju 20 (hexadecimalno). Na taj način u programskoj memoriji je upisano 7420. Neposredno adresiranje je veoma brzo jer se vrijednost koja se upisuje nalazi u samoj instrukciji. S druge strane, pošto je vrijednost koja se upisuje fiksno upisana pri kompajliranju, nema fleksibilnosti.

Adresiranje preko registara Podacima u SFR i registrima Rn iz izabrane registar banke u RAM se može pristupiti preko imena registra Na primjer: MOV Rn, A ; n=0, . . , 7 ADD A, Rn MOV DPL, R 6 S tim da se ne može koristiti DPTR registar je on 16 -bitni Npr. MOV DPTR, A nije korektno Takođe, ne mogu se koristiti istovremeno kao izvor i odredište registri iz RAM memorije sto znači da MOV Rm, Rn nije korektno

Direktno adresiranje se zove tako jer se vrijednost koja se upisuje u memoriju dobija tako što se direktno preuzima sa neke memorijske lokacije. Na primjer: MOV A, 30 h Ova instrukcija će da pročita podatke iz interne RAM adrese 30 (heksadecimalno) i upisati ih u akumulator. Direktno adresiranje je brzo jer, iako vrijednost koja se upisuje nije uključena direktno u instrukciju, brzo joj se pristupa posto je upisana u interni RAM. Takođe, ovaj način adresiranja je fleksibilniji od neposrednog adresiranja pošto se upisuju podaci koji se nalaze na datoj adresi i koji mogu da se mijenjaju. Kada se koristi direktno adresiranje, sve instrukcije koje se pristupaju adresama između 00 h i 7 Fh odnose se na interni RAM. Sve instrukcije koje pristupaju adresama između 80 h i FFh odnose se na SFR kontrolne registre koji kontrolišu rad mikrokontrolera.

Indirektno adresiranje je veoma koristan način adresiranje koji u mnogim slučajevima pokazuje izuzetan nivo fleksibilnosti. Indirektno adresiranje se koristi na sljedeći način: MOV A, @R 0 Ova instrukcija će dovesti do toga da se u akomulator upiše vrijednost iz internog rama koja se nalazi na adresi koja je upisana u R 0. Na primjer, recima da se u R 0 nalazi vrijednost 40 h i da je na adresi 40 h u internom RAM-u upisana vrijednost 67 h. Kada se navedena instrukcija izvrši, mikrokontroler će da provjeri vrijednost koja je upisana u R 0. Pošto je u R 0 upisana vrijednost 40 h, mikrokontroler će da preuzme vrijednost sa adrese 40 h (na kojoj je upisano 67 h) i upisati je u akomulator. Na taj način kada se instrukcija izvrši, u akumulator će biti upisana vrijednost 67 h. Indirektno adresiranje se uvijek odnosi na interni RAM, nikada se ne odnosi na SFR. Ukoliko bi na osnovu prethodnog primjera željeli upisati vrijednost na port 1 kome se pristupa preko SFR registra P 1 koji se nalazi na adresi 90 izgleda kao da bi to moglo da se uradi na sljedeći način: MOV R 0, #90 h ; Upisivanje adrese porta 1 MOV @R 0, #01 h ; Upisivanje 01 na port 1 – GREŠKA!!!! Ovo nije korektno. Pošto se indirektno adresiranje uvijek odnosi na interni RAM, ove dvije instrukcije će, u slučaju da se koristi kontroler 8051, proizvesti nedefinisan rezultat pošto on ima samo 128 bajtova internog RAM-a (adrese 00 h do 7 Fh). Kontroler 8052 ima 256 bajtova internog RAM-a. Kod njega se nižim 128 bajtova, koji su isti kao kod osnovnog 8051 kontrolera, može pristupiti i direktno i indirektno. Memorijskom prostoru u internom RAM-u od 128 do 255 kod ovog kontrolera može da se pristupi samo indirektno. Na taj način, kod ovog kontrolera, kada se pristupa memorijskim lokacijama od 128 do 255 direktno, pristupa se SFR kontrolnim registrima, a kada se ovim lokacijama pristupa indirektno, pristupa se internom RAM-u.

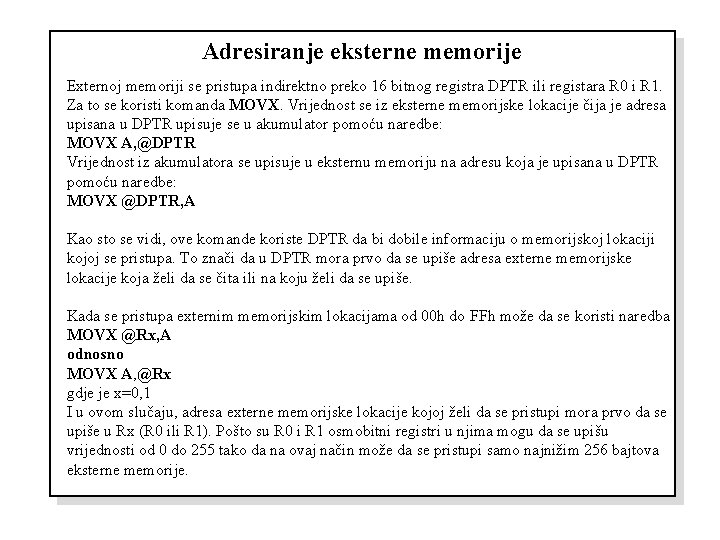

Adresiranje eksterne memorije Externoj memoriji se pristupa indirektno preko 16 bitnog registra DPTR ili registara R 0 i R 1. Za to se koristi komanda MOVX. Vrijednost se iz eksterne memorijske lokacije čija je adresa upisana u DPTR upisuje se u akumulator pomoću naredbe: MOVX A, @DPTR Vrijednost iz akumulatora se upisuje u eksternu memoriju na adresu koja je upisana u DPTR pomoću naredbe: MOVX @DPTR, A Kao sto se vidi, ove komande koriste DPTR da bi dobile informaciju o memorijskoj lokaciji kojoj se pristupa. To znači da u DPTR mora prvo da se upiše adresa externe memorijske lokacije koja želi da se čita ili na koju želi da se upiše. Kada se pristupa externim memorijskim lokacijama od 00 h do FFh može da se koristi naredba MOVX @Rx, A odnosno MOVX A, @Rx gdje je x=0, 1 I u ovom slučaju, adresa externe memorijske lokacije kojoj želi da se pristupi mora prvo da se upiše u Rx (R 0 ili R 1). Pošto su R 0 i R 1 osmobitni registri u njima mogu da se upišu vrijednosti od 0 do 255 tako da na ovaj način može da se pristupi samo najnižim 256 bajtova eksterne memorije.

Adresiranje ROM memorije Ovaj način adresiranja se koristi za pristup look-up tabelama sa podacima koje se nalaze u ROM memoriji 8051 MOVC A, @A+DPTR Preuzima se bajt koji se nalazi na ROM adresi koja se dobije kada se sabere sadržaj iz akumulatora sa sadržajem 16 bitnog registra DPTR i smješta u akumulator

Prekidi - interrupts Prekidi omogućavaju mikrokontroleru da ima "multi-tasking" funkcionalnost iako on u stvari radi jedan po jedan zadatak. Prekid se pokreće kada se dogodi određeni događaj koji je povezan sa njim. Kada se taj događaj desi, mikrokontroler privremeno prestaje sa normalnim izvršavanjem programa i izvršava poseban dio koda koji se tiče obrade tog prekida. Obrada prekida obavlja zadatke koji su potrebni da bi se obradio događaj koji je doveo do prekida i nakon toga vraća izvršavanje programa na tačku u kojoj je bio prekinut. Kod 8051 sljedeći događaji mogu da uzrokuju odgovarajući prekid: • Timer 0 Overflow. • Timer 1 Overflow. • Prijem/Slanje bajta serijskom komunikacijom. • Externi događaj 0 • Externi događaj 1 Znači, možemo da konfigurišemo 8051 tako da kada Timer 0 odbroji neko vrijeme ili kada se jedan bajt podataka primi/pošalje preko serijske komunikacije, pozove se odgovarajuća procedura za obradu prekida.

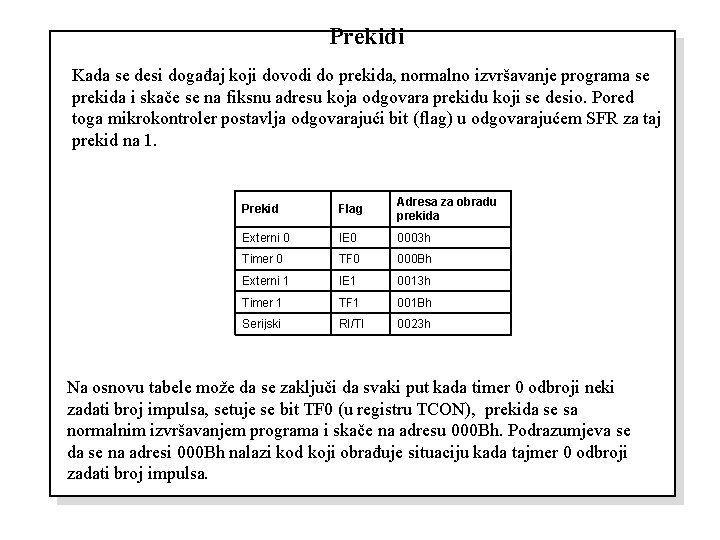

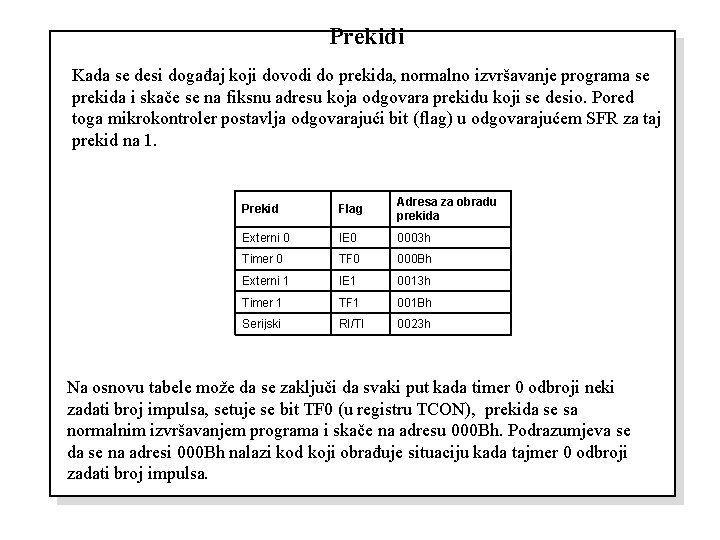

Prekidi Kada se desi događaj koji dovodi do prekida, normalno izvršavanje programa se prekida i skače se na fiksnu adresu koja odgovara prekidu koji se desio. Pored toga mikrokontroler postavlja odgovarajući bit (flag) u odgovarajućem SFR za taj prekid na 1. Prekid Flag Adresa za obradu prekida Externi 0 IE 0 0003 h Timer 0 TF 0 000 Bh Externi 1 IE 1 0013 h Timer 1 TF 1 001 Bh Serijski RI/TI 0023 h Na osnovu tabele može da se zaključi da svaki put kada timer 0 odbroji neki zadati broj impulsa, setuje se bit TF 0 (u registru TCON), prekida se sa normalnim izvršavanjem programa i skače na adresu 000 Bh. Podrazumjeva se da se na adresi 000 Bh nalazi kod koji obrađuje situaciju kada tajmer 0 odbroji zadati broj impulsa.

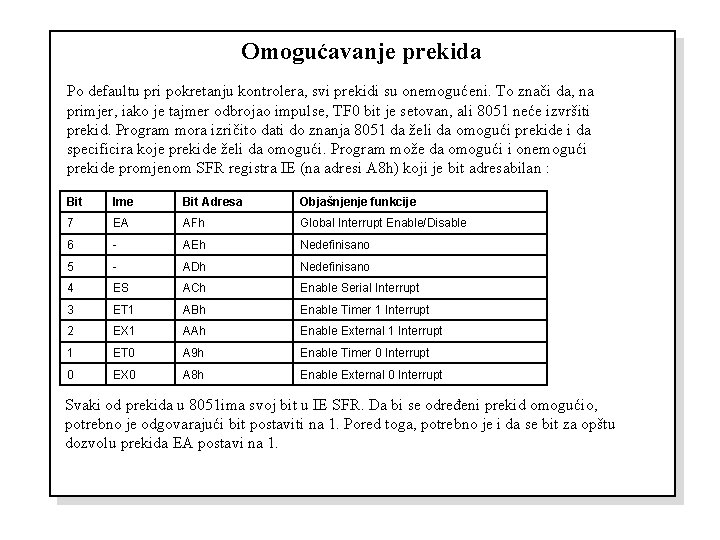

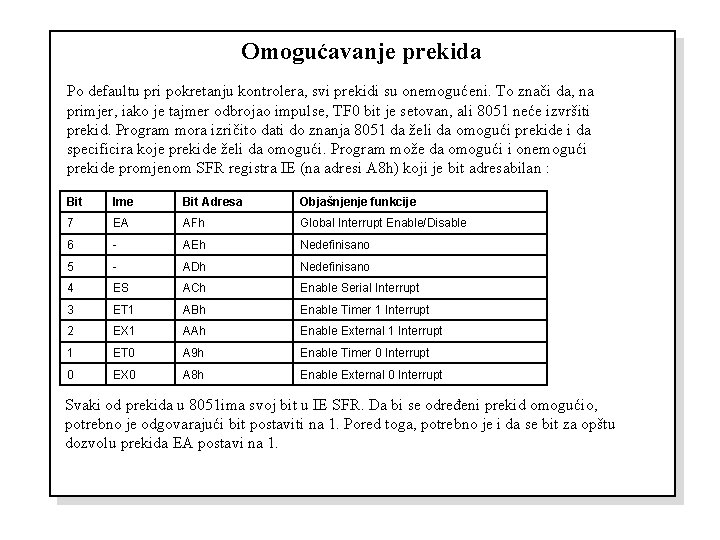

Omogućavanje prekida Po defaultu pri pokretanju kontrolera, svi prekidi su onemogućeni. To znači da, na primjer, iako je tajmer odbrojao impulse, TF 0 bit je setovan, ali 8051 neće izvršiti prekid. Program mora izričito dati do znanja 8051 da želi da omogući prekide i da specificira koje prekide želi da omogući. Program može da omogući i onemogući prekide promjenom SFR registra IE (na adresi A 8 h) koji je bit adresabilan : Bit Ime Bit Adresa Objašnjenje funkcije 7 EA AFh Global Interrupt Enable/Disable 6 - AEh Nedefinisano 5 - ADh Nedefinisano 4 ES ACh Enable Serial Interrupt 3 ET 1 ABh Enable Timer 1 Interrupt 2 EX 1 AAh Enable External 1 Interrupt 1 ET 0 A 9 h Enable Timer 0 Interrupt 0 EX 0 A 8 h Enable External 0 Interrupt Svaki od prekida u 8051 ima svoj bit u IE SFR. Da bi se određeni prekid omogućio, potrebno je odgovarajući bit postaviti na 1. Pored toga, potrebno je i da se bit za opštu dozvolu prekida EA postavi na 1.

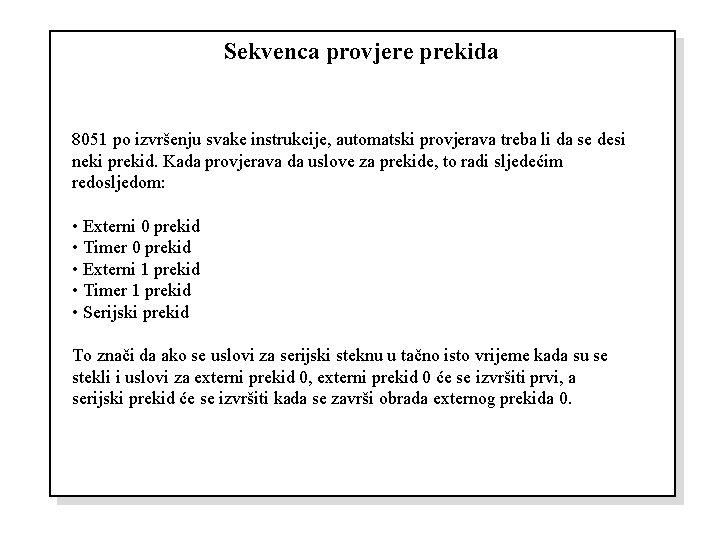

Sekvenca provjere prekida 8051 po izvršenju svake instrukcije, automatski provjerava treba li da se desi neki prekid. Kada provjerava da uslove za prekide, to radi sljedećim redosljedom: • Externi 0 prekid • Timer 0 prekid • Externi 1 prekid • Timer 1 prekid • Serijski prekid To znači da ako se uslovi za serijski steknu u tačno isto vrijeme kada su se stekli i uslovi za externi prekid 0, externi prekid 0 će se izvršiti prvi, a serijski prekid će se izvršiti kada se završi obrada externog prekida 0.

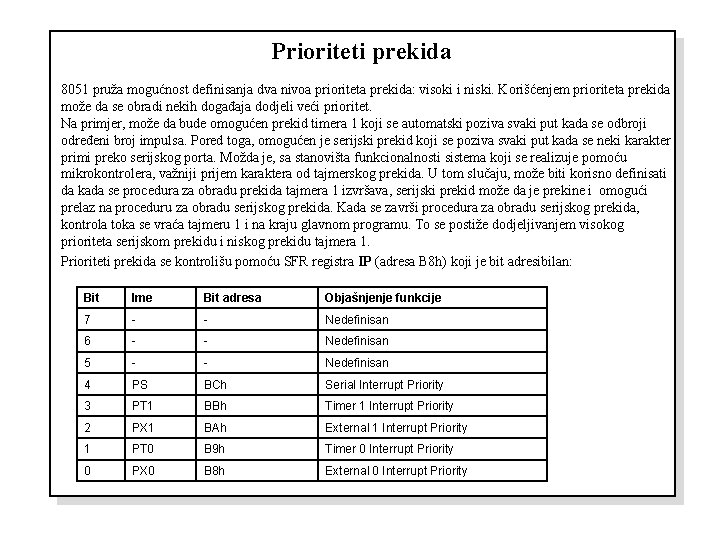

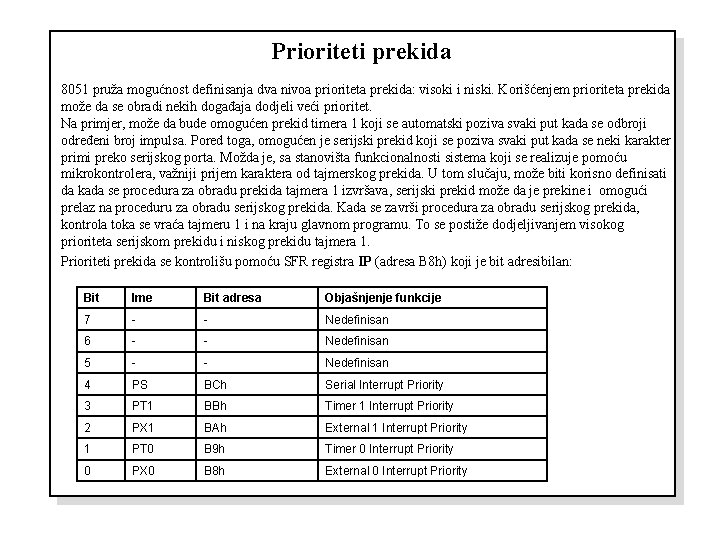

Prioriteti prekida 8051 pruža mogućnost definisanja dva nivoa prioriteta prekida: visoki i niski. Korišćenjem prioriteta prekida može da se obradi nekih događaja dodjeli veći prioritet. Na primjer, može da bude omogućen prekid timera 1 koji se automatski poziva svaki put kada se odbroji određeni broj impulsa. Pored toga, omogućen je serijski prekid koji se poziva svaki put kada se neki karakter primi preko serijskog porta. Možda je, sa stanovišta funkcionalnosti sistema koji se realizuje pomoću mikrokontrolera, važniji prijem karaktera od tajmerskog prekida. U tom slučaju, može biti korisno definisati da kada se procedura za obradu prekida tajmera 1 izvršava, serijski prekid može da je prekine i omogući prelaz na proceduru za obradu serijskog prekida. Kada se završi procedura za obradu serijskog prekida, kontrola toka se vraća tajmeru 1 i na kraju glavnom programu. To se postiže dodjeljivanjem visokog prioriteta serijskom prekidu i niskog prekidu tajmera 1. Prioriteti prekida se kontrolišu pomoću SFR registra IP (adresa B 8 h) koji je bit adresibilan: Bit Ime Bit adresa Objašnjenje funkcije 7 - - Nedefinisan 6 - - Nedefinisan 5 - - Nedefinisan 4 PS BCh Serial Interrupt Priority 3 PT 1 BBh Timer 1 Interrupt Priority 2 PX 1 BAh External 1 Interrupt Priority 1 PT 0 B 9 h Timer 0 Interrupt Priority 0 PX 0 B 8 h External 0 Interrupt Priority

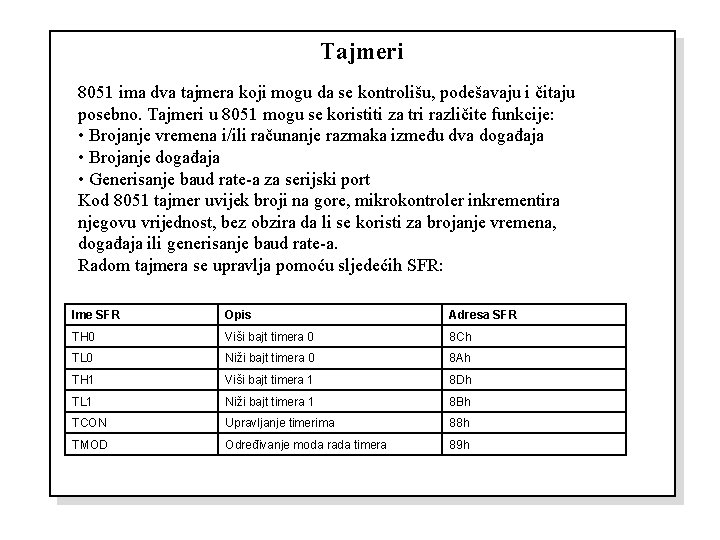

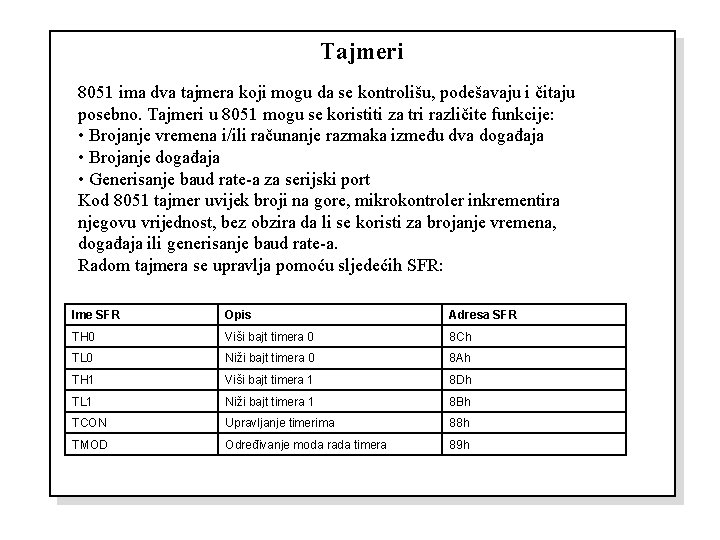

Tajmeri 8051 ima dva tajmera koji mogu da se kontrolišu, podešavaju i čitaju posebno. Tajmeri u 8051 mogu se koristiti za tri različite funkcije: • Brojanje vremena i/ili računanje razmaka između dva događaja • Brojanje događaja • Generisanje baud rate-a za serijski port Kod 8051 tajmer uvijek broji na gore, mikrokontroler inkrementira njegovu vrijednost, bez obzira da li se koristi za brojanje vremena, događaja ili generisanje baud rate-a. Radom tajmera se upravlja pomoću sljedećih SFR: Ime SFR Opis Adresa SFR TH 0 Viši bajt timera 0 8 Ch TL 0 Niži bajt timera 0 8 Ah TH 1 Viši bajt timera 1 8 Dh TL 1 Niži bajt timera 1 8 Bh TCON Upravljanje timerima 88 h TMOD Određivanje moda rada timera 89 h

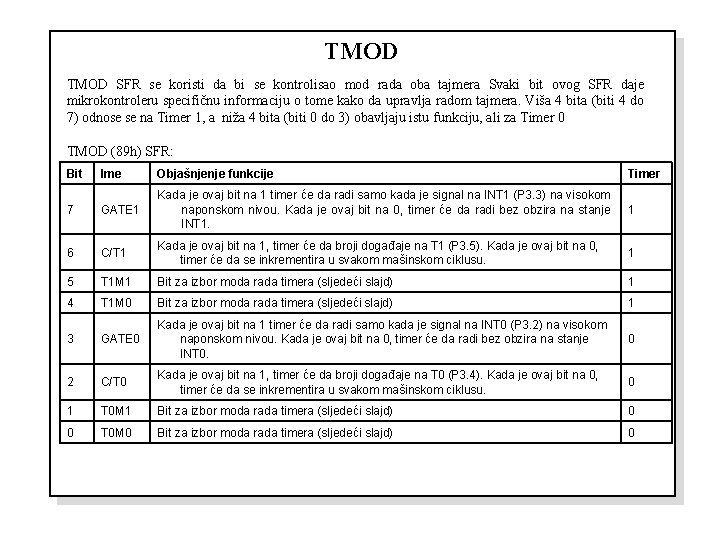

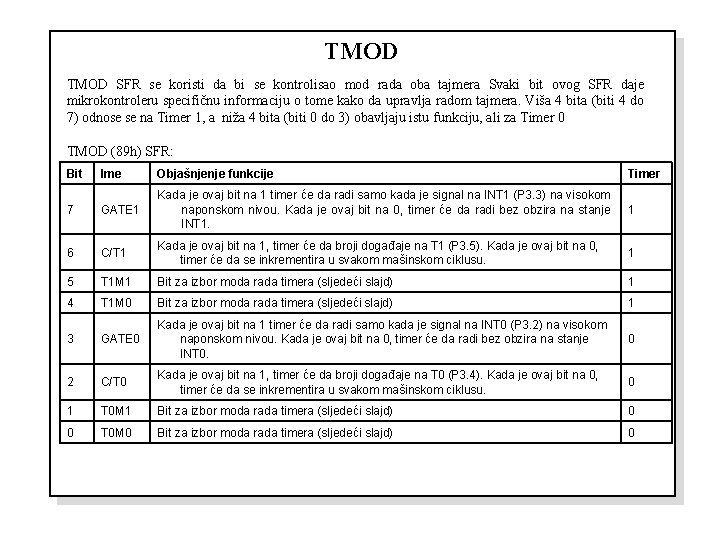

TMOD SFR se koristi da bi se kontrolisao mod rada oba tajmera Svaki bit ovog SFR daje mikrokontroleru specifičnu informaciju o tome kako da upravlja radom tajmera. Viša 4 bita (biti 4 do 7) odnose se na Timer 1, a niža 4 bita (biti 0 do 3) obavljaju istu funkciju, ali za Timer 0 TMOD (89 h) SFR: Bit Ime Objašnjenje funkcije Timer 7 GATE 1 Kada je ovaj bit na 1 timer će da radi samo kada je signal na INT 1 (P 3. 3) na visokom naponskom nivou. Kada je ovaj bit na 0, timer će da radi bez obzira na stanje INT 1. 1 6 C/T 1 Kada je ovaj bit na 1, timer će da broji događaje na T 1 (P 3. 5). Kada je ovaj bit na 0, timer će da se inkrementira u svakom mašinskom ciklusu. 1 5 T 1 M 1 Bit za izbor moda rada timera (sljedeći slajd) 1 4 T 1 M 0 Bit za izbor moda rada timera (sljedeći slajd) 1 3 GATE 0 Kada je ovaj bit na 1 timer će da radi samo kada je signal na INT 0 (P 3. 2) na visokom naponskom nivou. Kada je ovaj bit na 0, timer će da radi bez obzira na stanje INT 0. 0 2 C/T 0 Kada je ovaj bit na 1, timer će da broji događaje na T 0 (P 3. 4). Kada je ovaj bit na 0, timer će da se inkrementira u svakom mašinskom ciklusu. 0 1 T 0 M 1 Bit za izbor moda rada timera (sljedeći slajd) 0 0 T 0 M 0 Bit za izbor moda rada timera (sljedeći slajd) 0

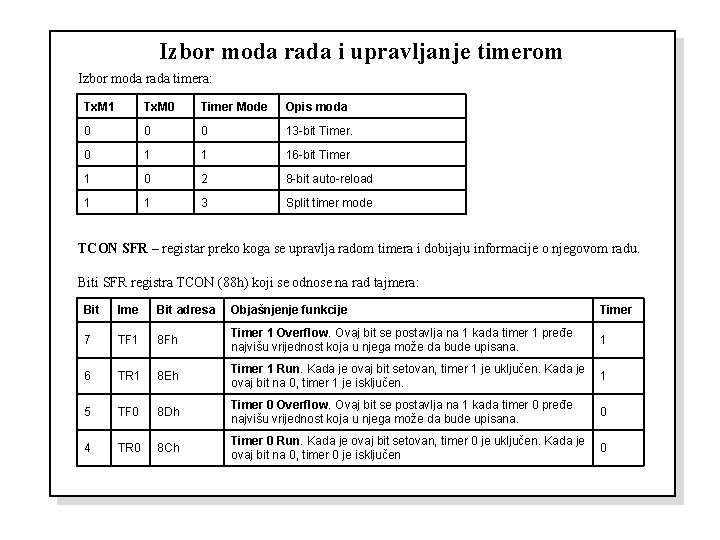

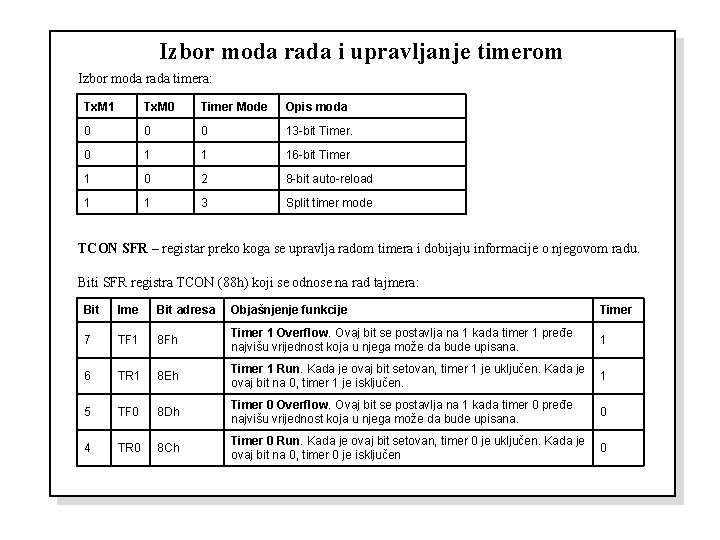

Izbor moda rada i upravljanje timerom Izbor moda rada timera: Tx. M 1 Tx. M 0 Timer Mode Opis moda 0 0 0 13 -bit Timer. 0 1 1 16 -bit Timer 1 0 2 8 -bit auto-reload 1 1 3 Split timer mode TCON SFR – registar preko koga se upravlja radom timera i dobijaju informacije o njegovom radu. Biti SFR registra TCON (88 h) koji se odnose na rad tajmera: Bit Ime Bit adresa Objašnjenje funkcije Timer 7 TF 1 8 Fh Timer 1 Overflow. Ovaj bit se postavlja na 1 kada timer 1 pređe najvišu vrijednost koja u njega može da bude upisana. 1 6 TR 1 8 Eh Timer 1 Run. Kada je ovaj bit setovan, timer 1 je uključen. Kada je ovaj bit na 0, timer 1 je isključen. 1 5 TF 0 8 Dh Timer 0 Overflow. Ovaj bit se postavlja na 1 kada timer 0 pređe najvišu vrijednost koja u njega može da bude upisana. 0 4 TR 0 8 Ch Timer 0 Run. Kada je ovaj bit setovan, timer 0 je uključen. Kada je ovaj bit na 0, timer 0 je isključen 0

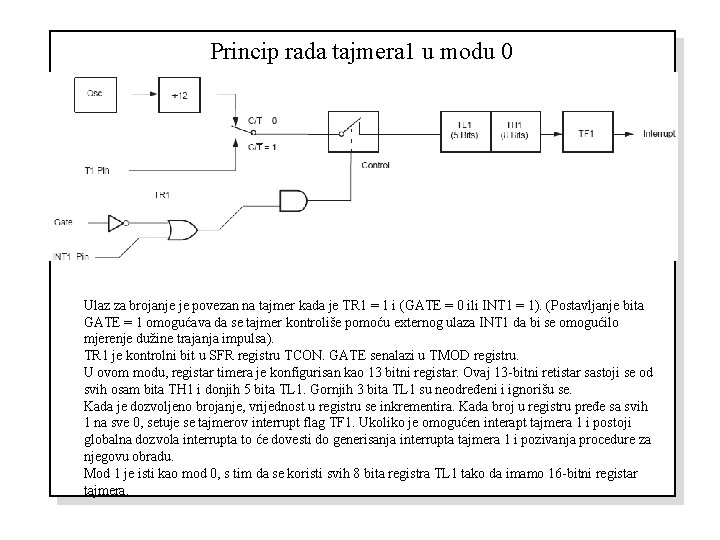

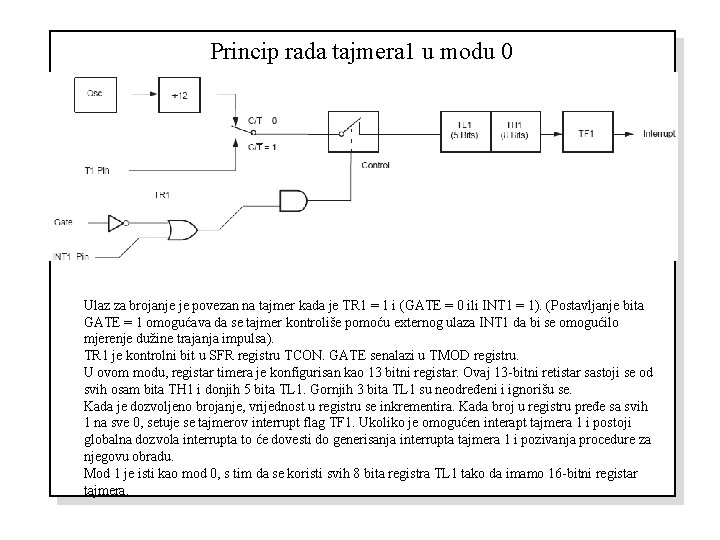

Princip rada tajmera 1 u modu 0 Ulaz za brojanje je povezan na tajmer kada je TR 1 = 1 i (GATE = 0 ili INT 1 = 1). (Postavljanje bita GATE = 1 omogućava da se tajmer kontroliše pomoću externog ulaza INT 1 da bi se omogućilo mjerenje dužine trajanja impulsa). TR 1 je kontrolni bit u SFR registru TCON. GATE senalazi u TMOD registru. U ovom modu, registar timera je konfigurisan kao 13 bitni registar. Ovaj 13 -bitni retistar sastoji se od svih osam bita TH 1 i donjih 5 bita TL 1. Gornjih 3 bita TL 1 su neodređeni i ignorišu se. Kada je dozvoljeno brojanje, vrijednost u registru se inkrementira. Kada broj u registru pređe sa svih 1 na sve 0, setuje se tajmerov interrupt flag TF 1. Ukoliko je omogućen interapt tajmera 1 i postoji globalna dozvola interrupta to će dovesti do generisanja interrupta tajmera 1 i pozivanja procedure za njegovu obradu. Mod 1 je isti kao mod 0, s tim da se koristi svih 8 bita registra TL 1 tako da imamo 16 -bitni registar tajmera.

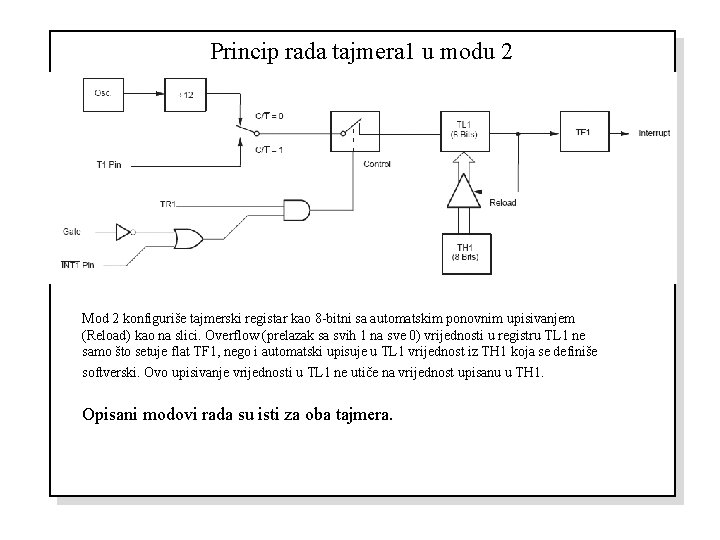

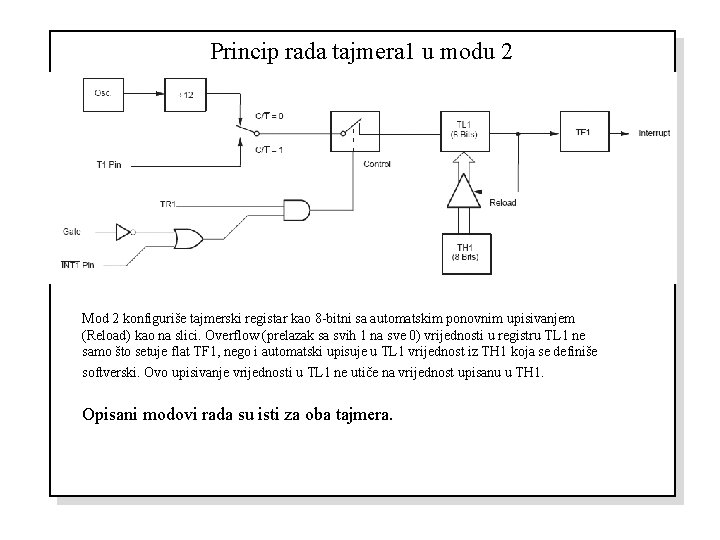

Princip rada tajmera 1 u modu 2 Mod 2 konfiguriše tajmerski registar kao 8 -bitni sa automatskim ponovnim upisivanjem (Reload) kao na slici. Overflow (prelazak sa svih 1 na sve 0) vrijednosti u registru TL 1 ne samo što setuje flat TF 1, nego i automatski upisuje u TL 1 vrijednost iz TH 1 koja se definiše softverski. Ovo upisivanje vrijednosti u TL 1 ne utiče na vrijednost upisanu u TH 1. Opisani modovi rada su isti za oba tajmera.

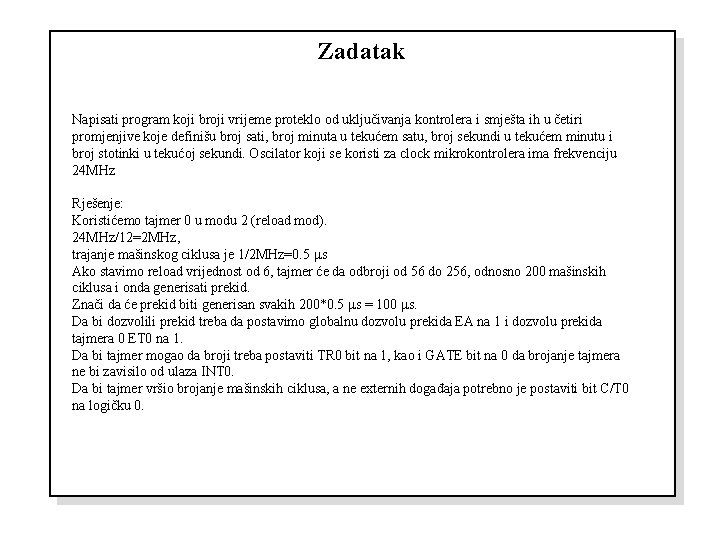

Zadatak Napisati program koji broji vrijeme proteklo od uključivanja kontrolera i smješta ih u četiri promjenjive koje definišu broj sati, broj minuta u tekućem satu, broj sekundi u tekućem minutu i broj stotinki u tekućoj sekundi. Oscilator koji se koristi za clock mikrokontrolera ima frekvenciju 24 MHz Rješenje: Koristićemo tajmer 0 u modu 2 (reload mod). 24 MHz/12=2 MHz, trajanje mašinskog ciklusa je 1/2 MHz=0. 5 s Ako stavimo reload vrijednost od 6, tajmer će da odbroji od 56 do 256, odnosno 200 mašinskih ciklusa i onda generisati prekid. Znači da će prekid biti generisan svakih 200*0. 5 s = 100 s. Da bi dozvolili prekid treba da postavimo globalnu dozvolu prekida EA na 1 i dozvolu prekida tajmera 0 ET 0 na 1. Da bi tajmer mogao da broji treba postaviti TR 0 bit na 1, kao i GATE bit na 0 da brojanje tajmera ne bi zavisilo od ulaza INT 0. Da bi tajmer vršio brojanje mašinskih ciklusa, a ne externih događaja potrebno je postaviti bit C/T 0 na logičku 0.

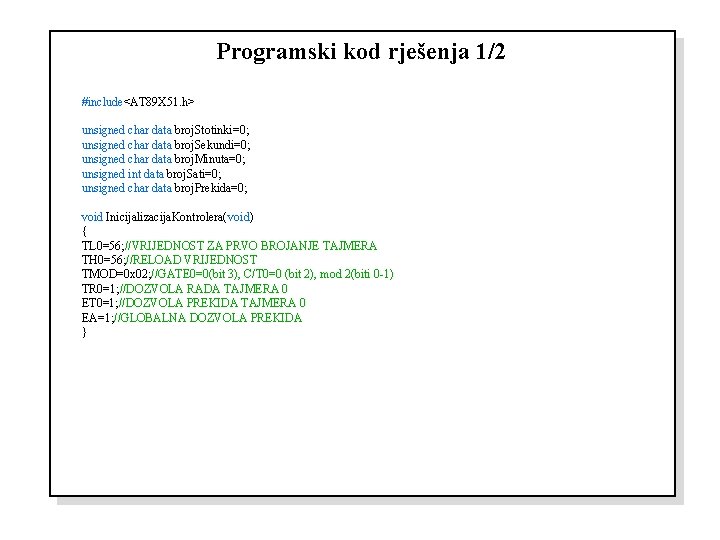

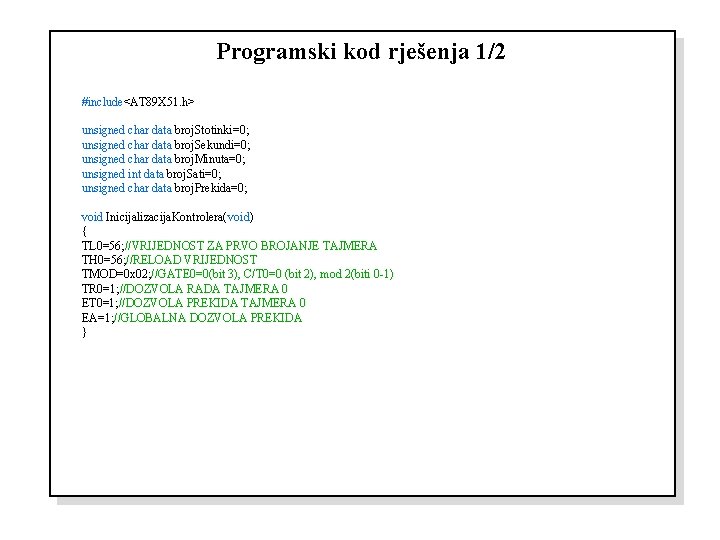

Programski kod rješenja 1/2 #include<AT 89 X 51. h> unsigned char data broj. Stotinki=0; unsigned char data broj. Sekundi=0; unsigned char data broj. Minuta=0; unsigned int data broj. Sati=0; unsigned char data broj. Prekida=0; void Inicijalizacija. Kontrolera(void) { TL 0=56; //VRIJEDNOST ZA PRVO BROJANJE TAJMERA TH 0=56; //RELOAD VRIJEDNOST TMOD=0 x 02; //GATE 0=0(bit 3), C/T 0=0 (bit 2), mod 2(biti 0 -1) TR 0=1; //DOZVOLA RADA TAJMERA 0 ET 0=1; //DOZVOLA PREKIDA TAJMERA 0 EA=1; //GLOBALNA DOZVOLA PREKIDA }

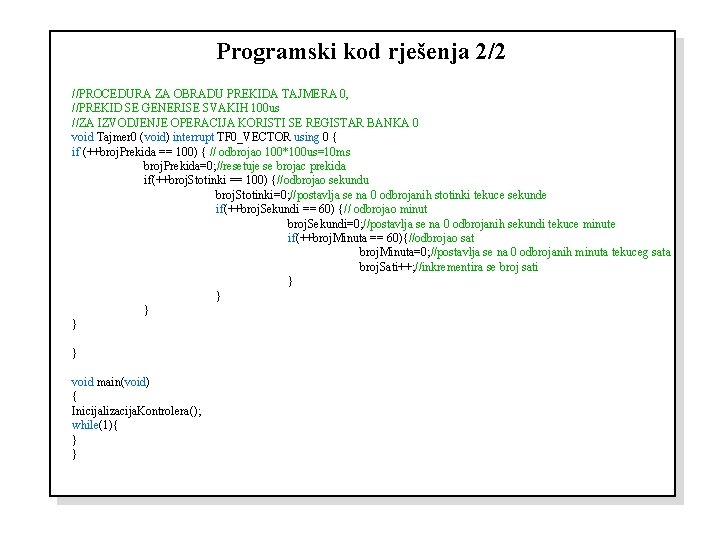

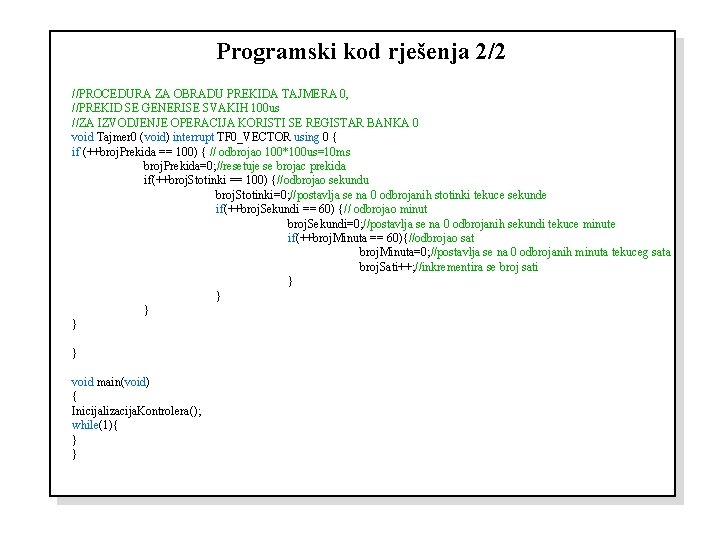

Programski kod rješenja 2/2 //PROCEDURA ZA OBRADU PREKIDA TAJMERA 0, //PREKID SE GENERISE SVAKIH 100 us //ZA IZVODJENJE OPERACIJA KORISTI SE REGISTAR BANKA 0 void Tajmer 0 (void) interrupt TF 0_VECTOR using 0 { if (++broj. Prekida == 100) { // odbrojao 100*100 us=10 ms broj. Prekida=0; //resetuje se brojac prekida if(++broj. Stotinki == 100) {//odbrojao sekundu broj. Stotinki=0; //postavlja se na 0 odbrojanih stotinki tekuce sekunde if(++broj. Sekundi == 60) {// odbrojao minut broj. Sekundi=0; //postavlja se na 0 odbrojanih sekundi tekuce minute if(++broj. Minuta == 60){//odbrojao sat broj. Minuta=0; //postavlja se na 0 odbrojanih minuta tekuceg sata broj. Sati++; //inkrementira se broj sati } } } void main(void) { Inicijalizacija. Kontrolera(); while(1){ } }

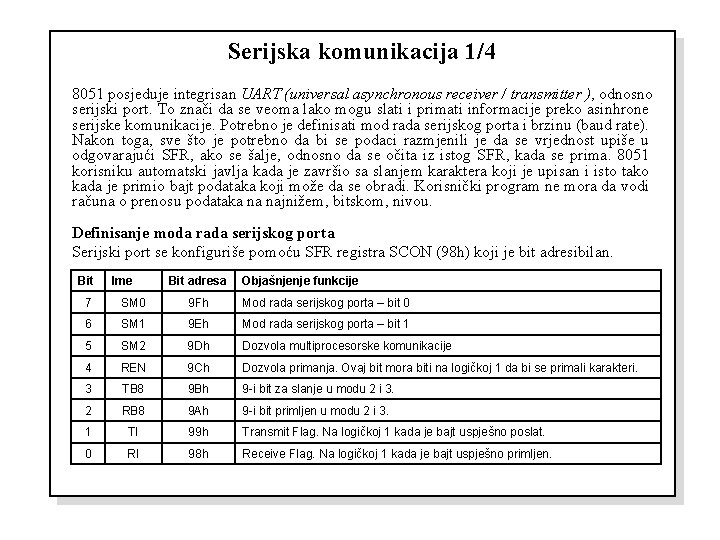

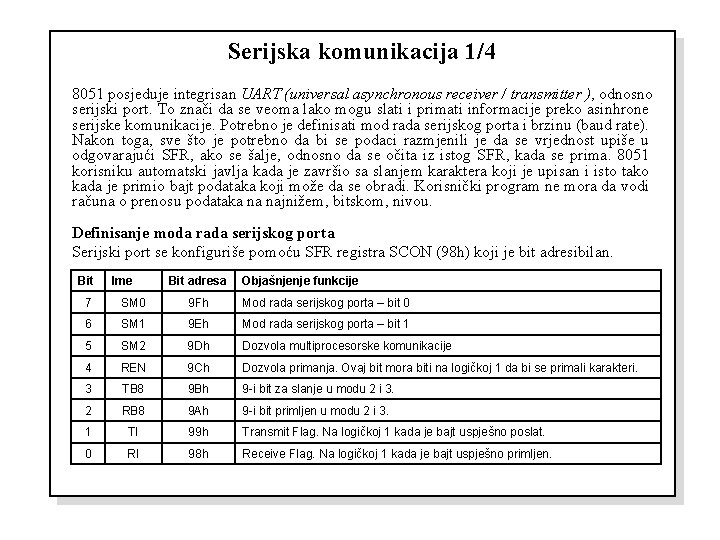

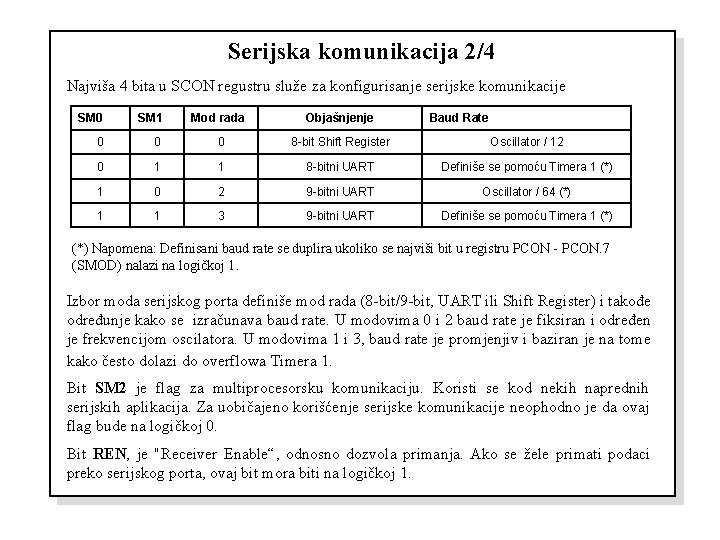

Serijska komunikacija 1/4 8051 posjeduje integrisan UART (universal asynchronous receiver / transmitter ), odnosno serijski port. To znači da se veoma lako mogu slati i primati informacije preko asinhrone serijske komunikacije. Potrebno je definisati mod rada serijskog porta i brzinu (baud rate). Nakon toga, sve što je potrebno da bi se podaci razmjenili je da se vrjednost upiše u odgovarajući SFR, ako se šalje, odnosno da se očita iz istog SFR, kada se prima. 8051 korisniku automatski javlja kada je završio sa slanjem karaktera koji je upisan i isto tako kada je primio bajt podataka koji može da se obradi. Korisnički program ne mora da vodi računa o prenosu podataka na najnižem, bitskom, nivou. Definisanje moda rada serijskog porta Serijski port se konfiguriše pomoću SFR registra SCON (98 h) koji je bit adresibilan. Bit Ime Bit adresa Objašnjenje funkcije 7 SM 0 9 Fh Mod rada serijskog porta – bit 0 6 SM 1 9 Eh Mod rada serijskog porta – bit 1 5 SM 2 9 Dh Dozvola multiprocesorske komunikacije 4 REN 9 Ch Dozvola primanja. Ovaj bit mora biti na logičkoj 1 da bi se primali karakteri. 3 TB 8 9 Bh 9 -i bit za slanje u modu 2 i 3. 2 RB 8 9 Ah 9 -i bit primljen u modu 2 i 3. 1 TI 99 h Transmit Flag. Na logičkoj 1 kada je bajt uspješno poslat. 0 RI 98 h Receive Flag. Na logičkoj 1 kada je bajt uspješno primljen.

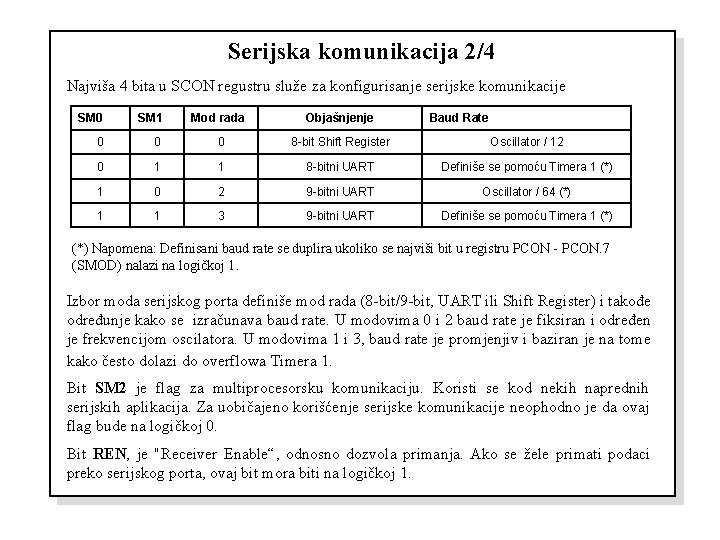

Serijska komunikacija 2/4 Najviša 4 bita u SCON regustru služe za konfigurisanje serijske komunikacije SM 0 SM 1 Mod rada Objašnjenje 0 Baud Rate 0 0 8 -bit Shift Register Oscillator / 12 0 1 1 8 -bitni UART Definiše se pomoću Timera 1 (*) 1 0 2 9 -bitni UART Oscillator / 64 (*) 1 1 3 9 -bitni UART Definiše se pomoću Timera 1 (*) Napomena: Definisani baud rate se duplira ukoliko se najviši bit u registru PCON - PCON. 7 (SMOD) nalazi na logičkoj 1. Izbor moda serijskog porta definiše mod rada (8 -bit/9 -bit, UART ili Shift Register) i takođe određunje kako se izračunava baud rate. U modovima 0 i 2 baud rate je fiksiran i određen je frekvencijom oscilatora. U modovima 1 i 3, baud rate je promjenjiv i baziran je na tome kako često dolazi do overflowa Timera 1. Bit SM 2 je flag za multiprocesorsku komunikaciju. Koristi se kod nekih naprednih serijskih aplikacija. Za uobičajeno korišćenje serijske komunikacije neophodno je da ovaj flag bude na logičkoj 0. Bit REN, je "Receiver Enable“, odnosno dozvola primanja. Ako se žele primati podaci preko serijskog porta, ovaj bit mora biti na logičkoj 1.

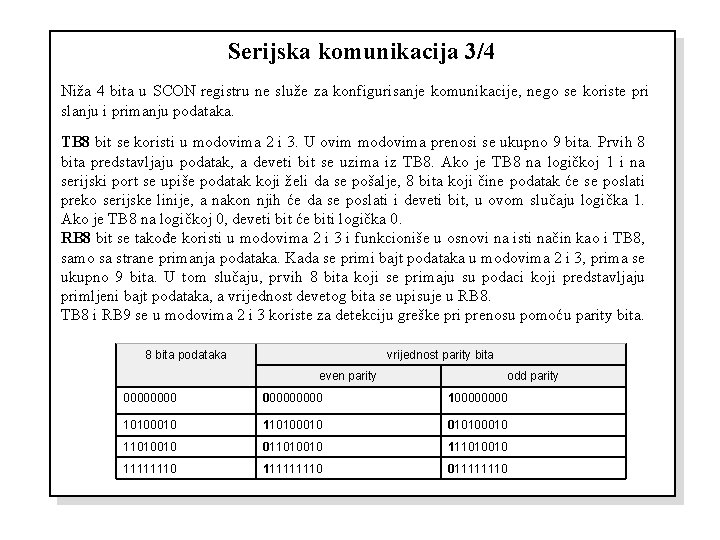

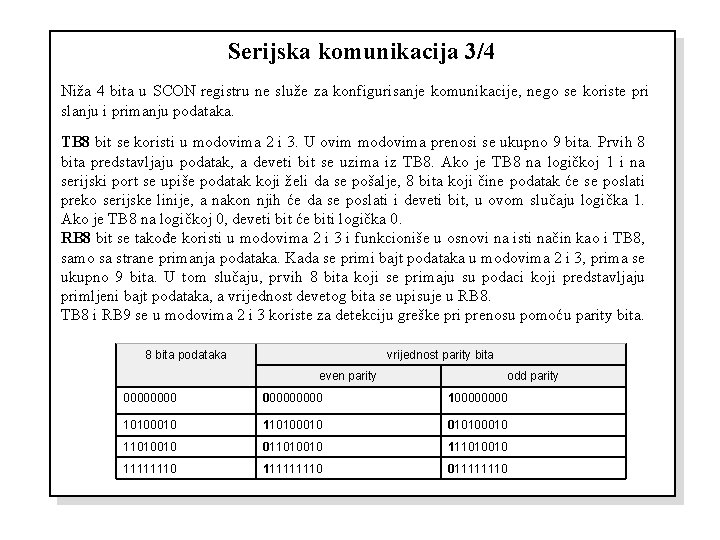

Serijska komunikacija 3/4 Niža 4 bita u SCON registru ne služe za konfigurisanje komunikacije, nego se koriste pri slanju i primanju podataka. TB 8 bit se koristi u modovima 2 i 3. U ovim modovima prenosi se ukupno 9 bita. Prvih 8 bita predstavljaju podatak, a deveti bit se uzima iz TB 8. Ako je TB 8 na logičkoj 1 i na serijski port se upiše podatak koji želi da se pošalje, 8 bita koji čine podatak će se poslati preko serijske linije, a nakon njih će da se poslati i deveti bit, u ovom slučaju logička 1. Ako je TB 8 na logičkoj 0, deveti bit će biti logička 0. RB 8 bit se takođe koristi u modovima 2 i 3 i funkcioniše u osnovi na isti način kao i TB 8, samo sa strane primanja podataka. Kada se primi bajt podataka u modovima 2 i 3, prima se ukupno 9 bita. U tom slučaju, prvih 8 bita koji se primaju su podaci koji predstavljaju primljeni bajt podataka, a vrijednost devetog bita se upisuje u RB 8. TB 8 i RB 9 se u modovima 2 i 3 koriste za detekciju greške pri prenosu pomoću parity bita. 8 bita podataka vrijednost parity bita even parity odd parity 000000000 10000 10100010 110100010 010100010 11010010 011010010 11111110 011111110

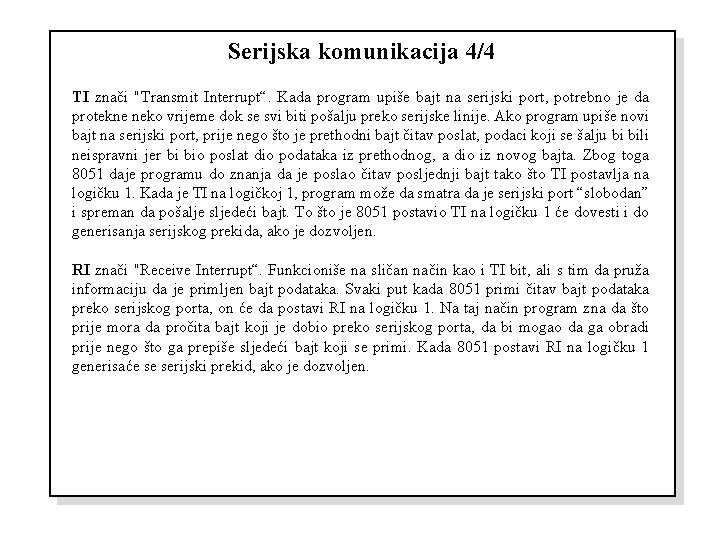

Serijska komunikacija 4/4 TI znači "Transmit Interrupt“. Kada program upiše bajt na serijski port, potrebno je da protekne neko vrijeme dok se svi biti pošalju preko serijske linije. Ako program upiše novi bajt na serijski port, prije nego što je prethodni bajt čitav poslat, podaci koji se šalju bi bili neispravni jer bi bio poslat dio podataka iz prethodnog, a dio iz novog bajta. Zbog toga 8051 daje programu do znanja da je poslao čitav posljednji bajt tako što TI postavlja na logičku 1. Kada je TI na logičkoj 1, program može da smatra da je serijski port “slobodan” i spreman da pošalje sljedeći bajt. To što je 8051 postavio TI na logičku 1 će dovesti i do generisanja serijskog prekida, ako je dozvoljen. RI znači "Receive Interrupt“. Funkcioniše na sličan način kao i TI bit, ali s tim da pruža informaciju da je primljen bajt podataka. Svaki put kada 8051 primi čitav bajt podataka preko serijskog porta, on će da postavi RI na logičku 1. Na taj način program zna da što prije mora da pročita bajt koji je dobio preko serijskog porta, da bi mogao da ga obradi prije nego što ga prepiše sljedeći bajt koji se primi. Kada 8051 postavi RI na logičku 1 generisaće se serijski prekid, ako je dozvoljen.

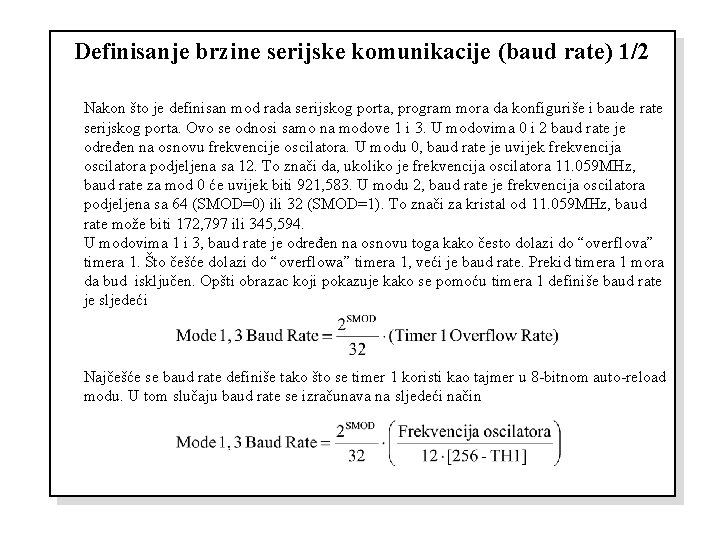

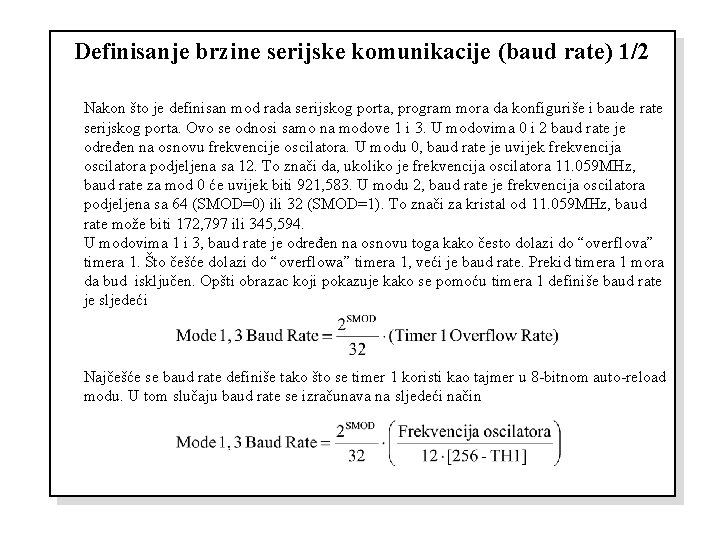

Definisanje brzine serijske komunikacije (baud rate) 1/2 Nakon što je definisan mod rada serijskog porta, program mora da konfiguriše i baude rate serijskog porta. Ovo se odnosi samo na modove 1 i 3. U modovima 0 i 2 baud rate je određen na osnovu frekvencije oscilatora. U modu 0, baud rate je uvijek frekvencija oscilatora podjeljena sa 12. To znači da, ukoliko je frekvencija oscilatora 11. 059 MHz, baud rate za mod 0 će uvijek biti 921, 583. U modu 2, baud rate je frekvencija oscilatora podjeljena sa 64 (SMOD=0) ili 32 (SMOD=1). To znači za kristal od 11. 059 MHz, baud rate može biti 172, 797 ili 345, 594. U modovima 1 i 3, baud rate je određen na osnovu toga kako često dolazi do “overflova” timera 1. Što češće dolazi do “overflowa” timera 1, veći je baud rate. Prekid timera 1 mora da bud isključen. Opšti obrazac koji pokazuje kako se pomoću timera 1 definiše baud rate je sljedeći Najčešće se baud rate definiše tako što se timer 1 koristi kao tajmer u 8 -bitnom auto-reload modu. U tom slučaju baud rate se izračunava na sljedeći način

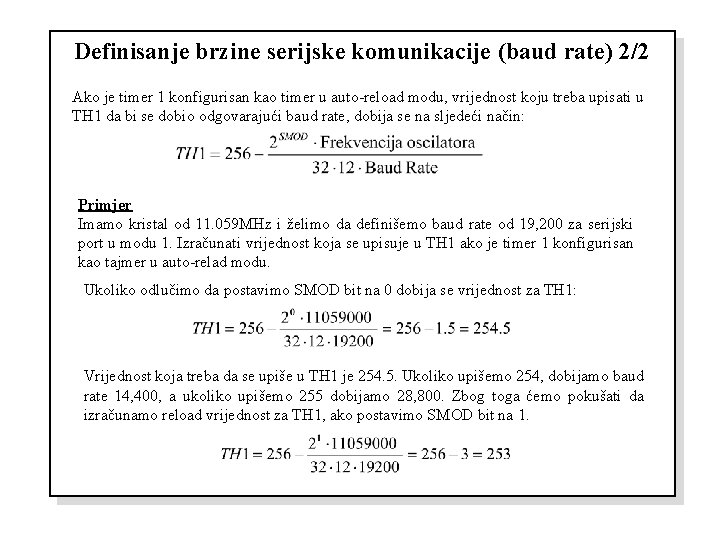

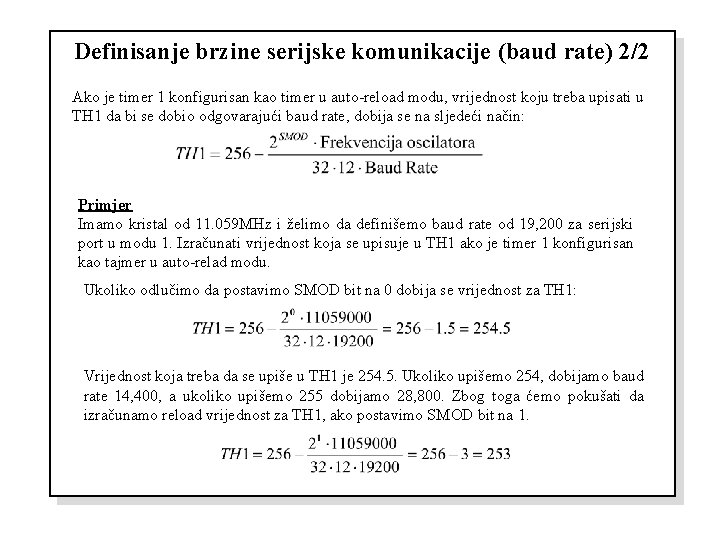

Definisanje brzine serijske komunikacije (baud rate) 2/2 Ako je timer 1 konfigurisan kao timer u auto-reload modu, vrijednost koju treba upisati u TH 1 da bi se dobio odgovarajući baud rate, dobija se na sljedeći način: Primjer Imamo kristal od 11. 059 MHz i želimo da definišemo baud rate od 19, 200 za serijski port u modu 1. Izračunati vrijednost koja se upisuje u TH 1 ako je timer 1 konfigurisan kao tajmer u auto-relad modu. Ukoliko odlučimo da postavimo SMOD bit na 0 dobija se vrijednost za TH 1: Vrijednost koja treba da se upiše u TH 1 je 254. 5. Ukoliko upišemo 254, dobijamo baud rate 14, 400, a ukoliko upišemo 255 dobijamo 28, 800. Zbog toga ćemo pokušati da izračunamo reload vrijednost za TH 1, ako postavimo SMOD bit na 1.

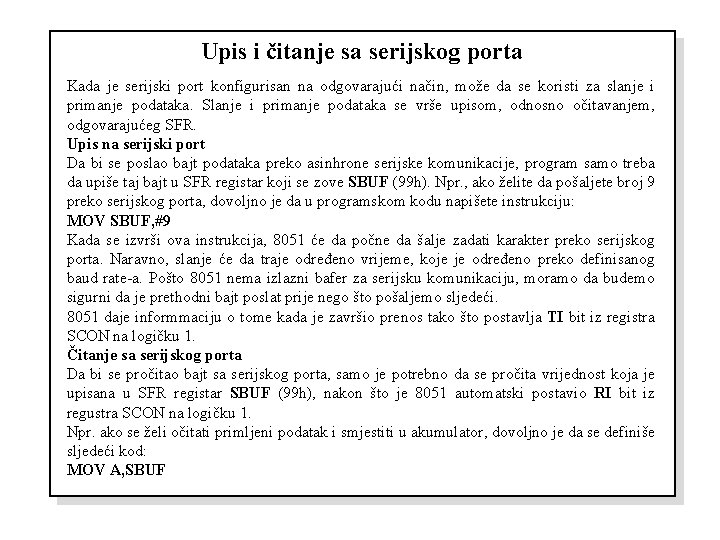

Upis i čitanje sa serijskog porta Kada je serijski port konfigurisan na odgovarajući način, može da se koristi za slanje i primanje podataka. Slanje i primanje podataka se vrše upisom, odnosno očitavanjem, odgovarajućeg SFR. Upis na serijski port Da bi se poslao bajt podataka preko asinhrone serijske komunikacije, program samo treba da upiše taj bajt u SFR registar koji se zove SBUF (99 h). Npr. , ako želite da pošaljete broj 9 preko serijskog porta, dovoljno je da u programskom kodu napišete instrukciju: MOV SBUF, #9 Kada se izvrši ova instrukcija, 8051 će da počne da šalje zadati karakter preko serijskog porta. Naravno, slanje će da traje određeno vrijeme, koje je određeno preko definisanog baud rate-a. Pošto 8051 nema izlazni bafer za serijsku komunikaciju, moramo da budemo sigurni da je prethodni bajt poslat prije nego što pošaljemo sljedeći. 8051 daje informmaciju o tome kada je završio prenos tako što postavlja TI bit iz registra SCON na logičku 1. Čitanje sa serijskog porta Da bi se pročitao bajt sa serijskog porta, samo je potrebno da se pročita vrijednost koja je upisana u SFR registar SBUF (99 h), nakon što je 8051 automatski postavio RI bit iz regustra SCON na logičku 1. Npr. ako se želi očitati primljeni podatak i smjestiti u akumulator, dovoljno je da se definiše sljedeći kod: MOV A, SBUF

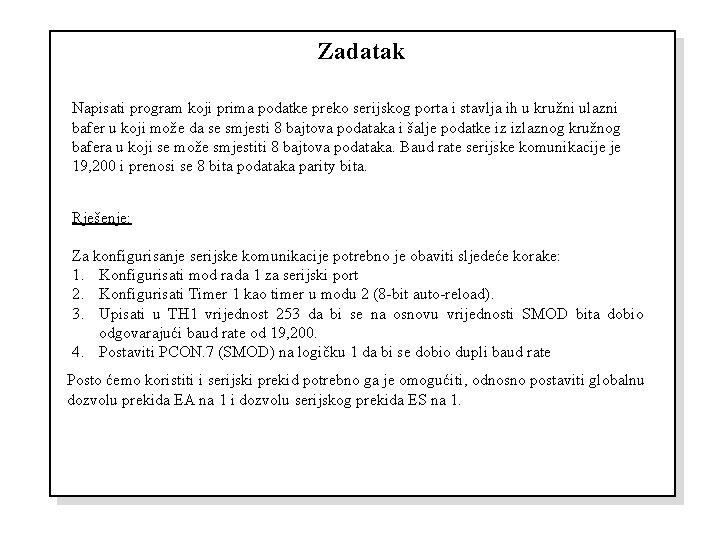

Zadatak Napisati program koji prima podatke preko serijskog porta i stavlja ih u kružni ulazni bafer u koji može da se smjesti 8 bajtova podataka i šalje podatke iz izlaznog kružnog bafera u koji se može smjestiti 8 bajtova podataka. Baud rate serijske komunikacije je 19, 200 i prenosi se 8 bita podataka parity bita. Rješenje: Za konfigurisanje serijske komunikacije potrebno je obaviti sljedeće korake: 1. Konfigurisati mod rada 1 za serijski port 2. Konfigurisati Timer 1 kao timer u modu 2 (8 -bit auto-reload). 3. Upisati u TH 1 vrijednost 253 da bi se na osnovu vrijednosti SMOD bita dobio odgovarajući baud rate od 19, 200. 4. Postaviti PCON. 7 (SMOD) na logičku 1 da bi se dobio dupli baud rate Posto ćemo koristiti i serijski prekid potrebno ga je omogućiti, odnosno postaviti globalnu dozvolu prekida EA na 1 i dozvolu serijskog prekida ES na 1.

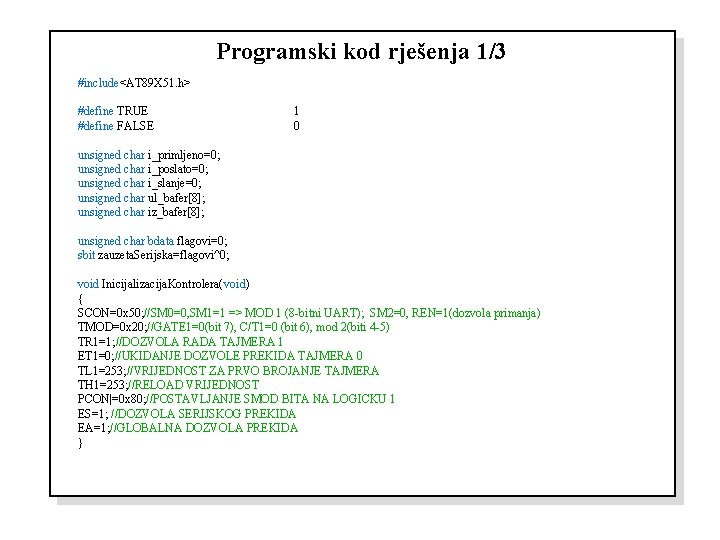

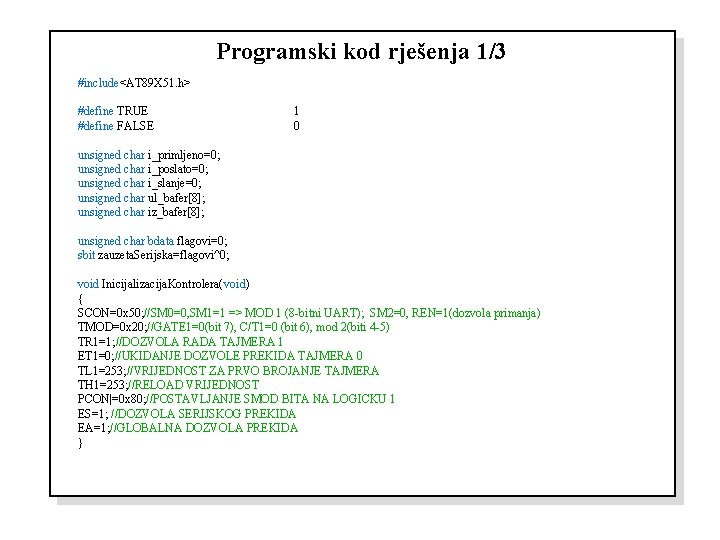

Programski kod rješenja 1/3 #include<AT 89 X 51. h> #define TRUE #define FALSE 1 0 unsigned char i_primljeno=0; unsigned char i_poslato=0; unsigned char i_slanje=0; unsigned char ul_bafer[8]; unsigned char iz_bafer[8]; unsigned char bdata flagovi=0; sbit zauzeta. Serijska=flagovi^0; void Inicijalizacija. Kontrolera(void) { SCON=0 x 50; //SM 0=0, SM 1=1 => MOD 1 (8 -bitni UART); SM 2=0, REN=1(dozvola primanja) TMOD=0 x 20; //GATE 1=0(bit 7), C/T 1=0 (bit 6), mod 2(biti 4 -5) TR 1=1; //DOZVOLA RADA TAJMERA 1 ET 1=0; //UKIDANJE DOZVOLE PREKIDA TAJMERA 0 TL 1=253; //VRIJEDNOST ZA PRVO BROJANJE TAJMERA TH 1=253; //RELOAD VRIJEDNOST PCON|=0 x 80; //POSTAVLJANJE SMOD BITA NA LOGICKU 1 ES=1; //DOZVOLA SERIJSKOG PREKIDA EA=1; //GLOBALNA DOZVOLA PREKIDA }

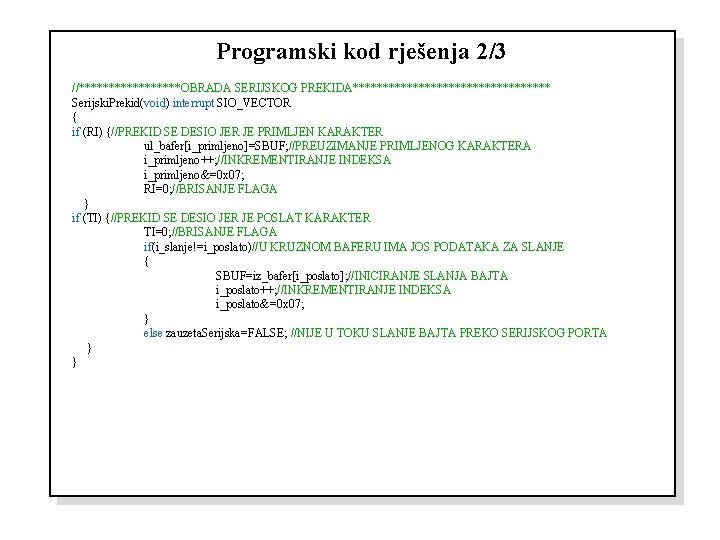

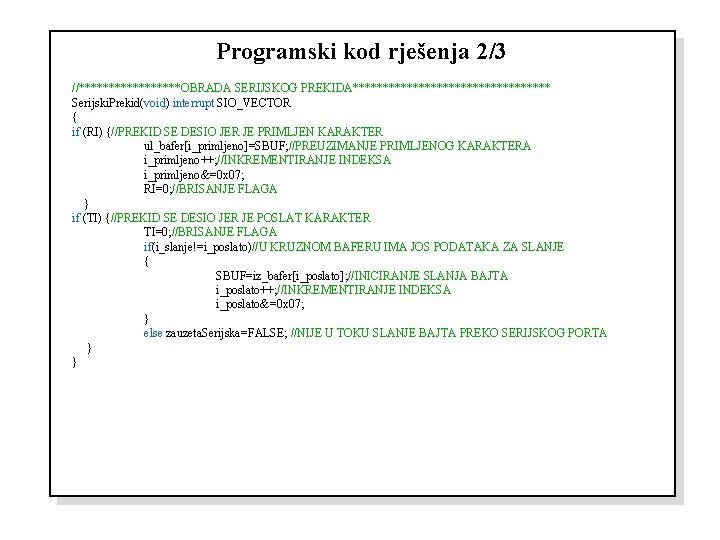

Programski kod rješenja 2/3 //*********OBRADA SERIJSKOG PREKIDA***************** Serijski. Prekid(void) interrupt SIO_VECTOR { if (RI) {//PREKID SE DESIO JER JE PRIMLJEN KARAKTER ul_bafer[i_primljeno]=SBUF; //PREUZIMANJE PRIMLJENOG KARAKTERA i_primljeno++; //INKREMENTIRANJE INDEKSA i_primljeno&=0 x 07; RI=0; //BRISANJE FLAGA } if (TI) {//PREKID SE DESIO JER JE POSLAT KARAKTER TI=0; //BRISANJE FLAGA if(i_slanje!=i_poslato)//U KRUZNOM BAFERU IMA JOS PODATAKA ZA SLANJE { SBUF=iz_bafer[i_poslato]; //INICIRANJE SLANJA BAJTA i_poslato++; //INKREMENTIRANJE INDEKSA i_poslato&=0 x 07; } else zauzeta. Serijska=FALSE; //NIJE U TOKU SLANJE BAJTA PREKO SERIJSKOG PORTA } }

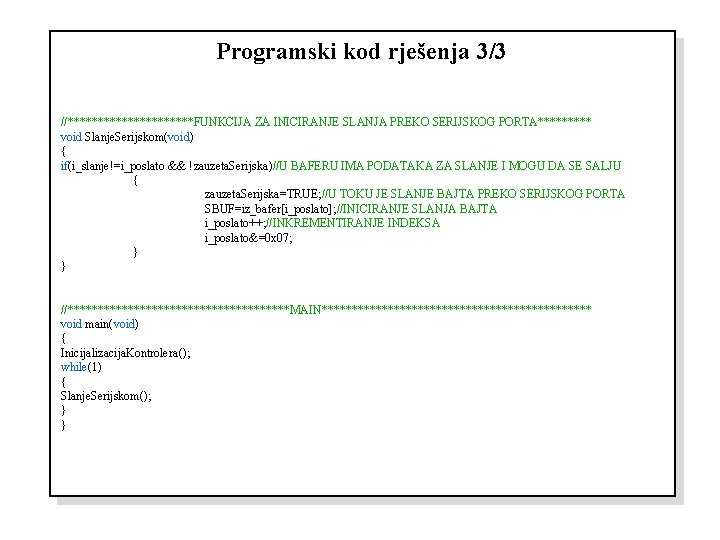

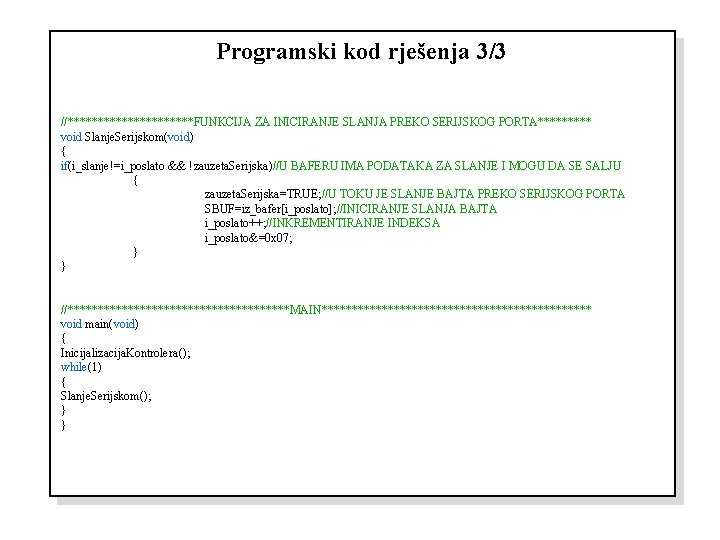

Programski kod rješenja 3/3 //***********FUNKCIJA ZA INICIRANJE SLANJA PREKO SERIJSKOG PORTA***** void Slanje. Serijskom(void) { if(i_slanje!=i_poslato && !zauzeta. Serijska)//U BAFERU IMA PODATAKA ZA SLANJE I MOGU DA SE SALJU { zauzeta. Serijska=TRUE; //U TOKU JE SLANJE BAJTA PREKO SERIJSKOG PORTA SBUF=iz_bafer[i_poslato]; //INICIRANJE SLANJA BAJTA i_poslato++; //INKREMENTIRANJE INDEKSA i_poslato&=0 x 07; } } //*******************MAIN*********************** void main(void) { Inicijalizacija. Kontrolera(); while(1) { Slanje. Serijskom(); } }

Neki dodatni resursi kod mikrokontrolera baziranih na 8051 arhitekturi SPI (Serial Peripheral Interface) – koristi se za sinhronu serijsku komunikaciju procesora sa periferijama ili za komunikaciju između dva procesora q Watchdog Timer q

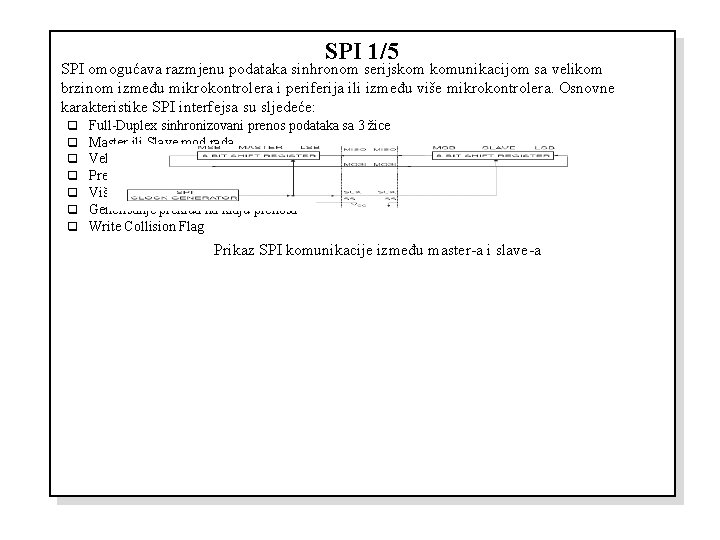

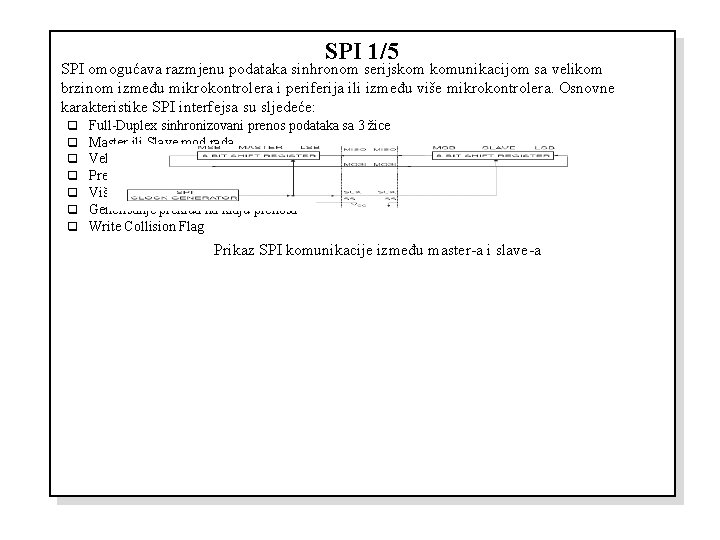

SPI 1/5 SPI omogućava razmjenu podataka sinhronom serijskom komunikacijom sa velikom brzinom između mikrokontrolera i periferija ili između više mikrokontrolera. Osnovne karakteristike SPI interfejsa su sljedeće: q q q q Full-Duplex sinhronizovani prenos podataka sa 3 žice Master ili Slave mod rada Velika brzina Prenos podataka sa prvim LSB ili prvim MSB Više programabilnih brzina prenosa Generisanje prekida na kraju prenosa Write Collision Flag Prikaz SPI komunikacije između master-a i slave-a

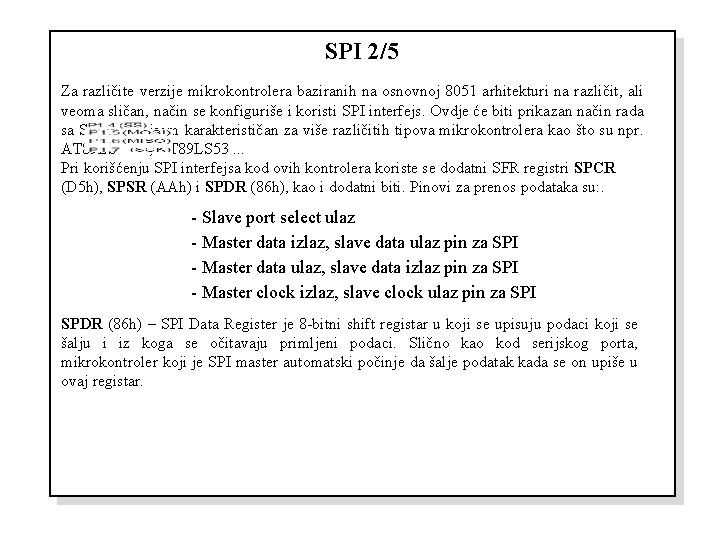

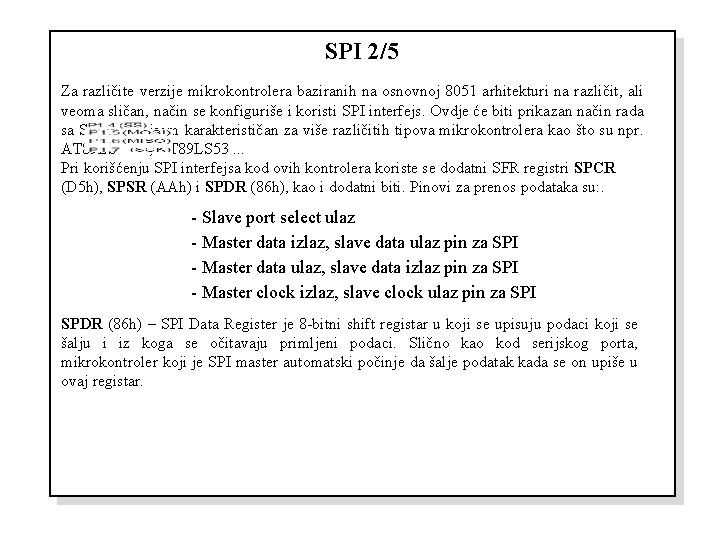

SPI 2/5 Za različite verzije mikrokontrolera baziranih na osnovnoj 8051 arhitekturi na različit, ali veoma sličan, način se konfiguriše i koristi SPI interfejs. Ovdje će biti prikazan način rada sa SPI interfejsom karakterističan za više različitih tipova mikrokontrolera kao što su npr. AT 89 LS 8252, AT 89 LS 53. . . Pri korišćenju SPI interfejsa kod ovih kontrolera koriste se dodatni SFR registri SPCR (D 5 h), SPSR (AAh) i SPDR (86 h), kao i dodatni biti. Pinovi za prenos podataka su: . - Slave port select ulaz - Master data izlaz, slave data ulaz pin za SPI - Master data ulaz, slave data izlaz pin za SPI - Master clock izlaz, slave clock ulaz pin za SPI SPDR (86 h) – SPI Data Register je 8 -bitni shift registar u koji se upisuju podaci koji se šalju i iz koga se očitavaju primljeni podaci. Slično kao kod serijskog porta, mikrokontroler koji je SPI master automatski počinje da šalje podatak kada se on upiše u ovaj registar.

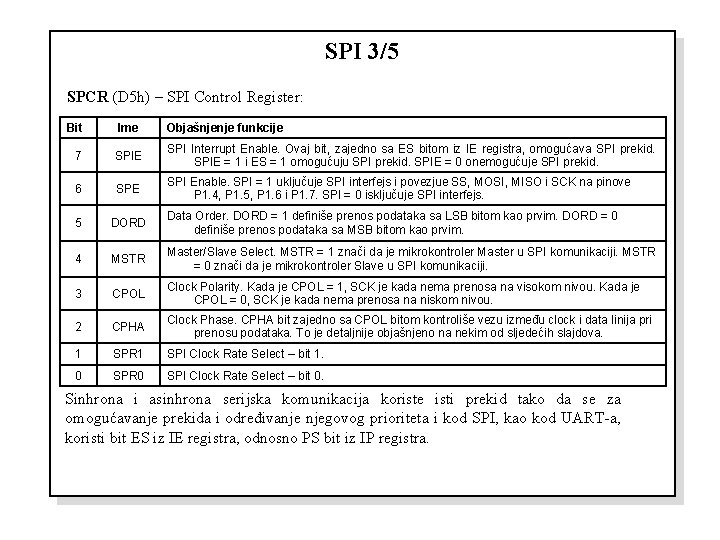

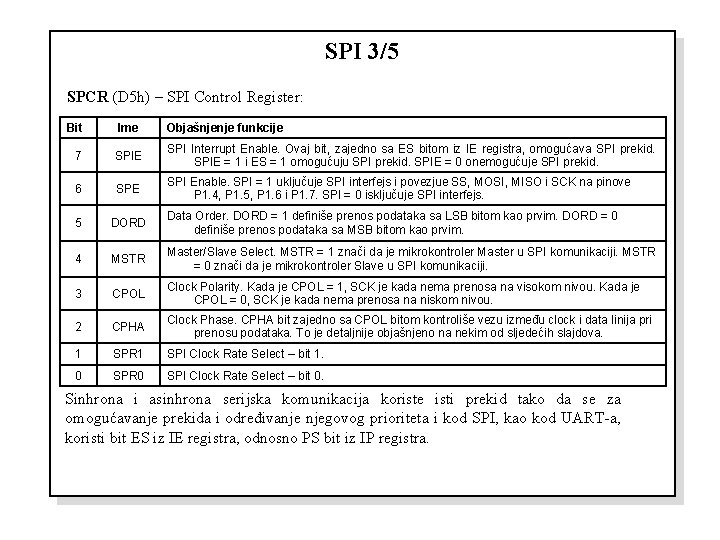

SPI 3/5 SPCR (D 5 h) – SPI Control Register: Bit Ime Objašnjenje funkcije 7 SPIE SPI Interrupt Enable. Ovaj bit, zajedno sa ES bitom iz IE registra, omogućava SPI prekid. SPIE = 1 i ES = 1 omogućuju SPI prekid. SPIE = 0 onemogućuje SPI prekid. 6 SPE SPI Enable. SPI = 1 uključuje SPI interfejs i povezjue SS, MOSI, MISO i SCK na pinove P 1. 4, P 1. 5, P 1. 6 i P 1. 7. SPI = 0 isključuje SPI interfejs. 5 DORD Data Order. DORD = 1 definiše prenos podataka sa LSB bitom kao prvim. DORD = 0 definiše prenos podataka sa MSB bitom kao prvim. 4 MSTR Master/Slave Select. MSTR = 1 znači da je mikrokontroler Master u SPI komunikaciji. MSTR = 0 znači da je mikrokontroler Slave u SPI komunikaciji. 3 CPOL Clock Polarity. Kada je CPOL = 1, SCK je kada nema prenosa na visokom nivou. Kada je CPOL = 0, SCK je kada nema prenosa na niskom nivou. 2 CPHA Clock Phase. CPHA bit zajedno sa CPOL bitom kontroliše vezu između clock i data linija pri prenosu podataka. To je detaljnije objašnjeno na nekim od sljedećih slajdova. 1 SPR 1 SPI Clock Rate Select – bit 1. 0 SPR 0 SPI Clock Rate Select – bit 0. Sinhrona i asinhrona serijska komunikacija koriste isti prekid tako da se za omogućavanje prekida i određivanje njegovog prioriteta i kod SPI, kao kod UART-a, koristi bit ES iz IE registra, odnosno PS bit iz IP registra.

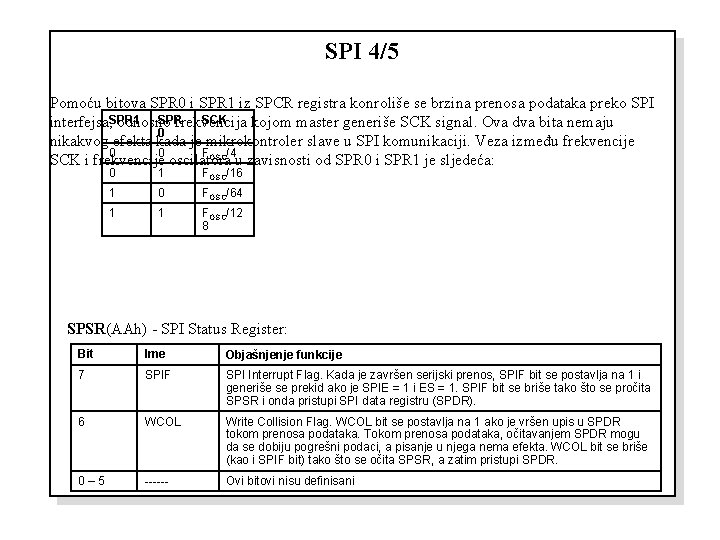

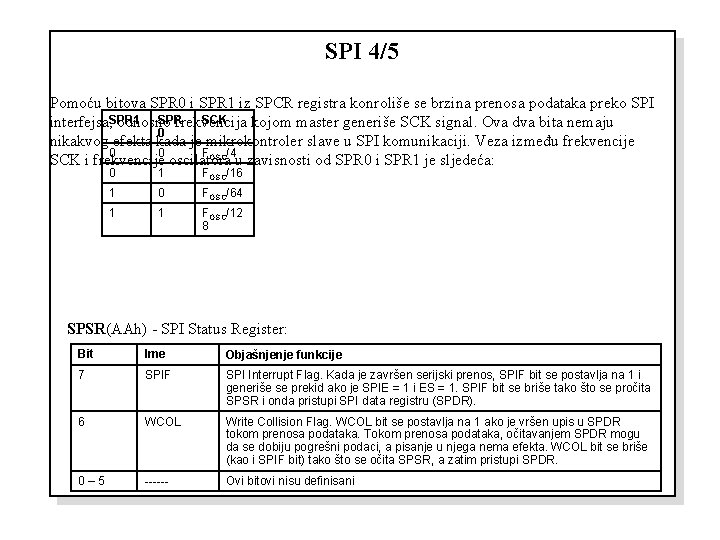

SPI 4/5 Pomoću bitova SPR 0 i SPR 1 iz SPCR registra konroliše se brzina prenosa podataka preko SPI SPR SCK interfejsa, SPR 1 odnosno frekvencija kojom master generiše SCK signal. Ova dva bita nemaju 0 nikakvog efekta kada je mikrokontroler slave u SPI komunikaciji. Veza između frekvencije 0 0 FOSC/4 SCK i frekvencije oscilatora u zavisnosti od SPR 0 i SPR 1 je sljedeća: 0 1 FOSC/16 1 0 FOSC/64 1 1 FOSC/12 8 SPSR(AAh) - SPI Status Register: Bit Ime Objašnjenje funkcije 7 SPIF SPI Interrupt Flag. Kada je završen serijski prenos, SPIF bit se postavlja na 1 i generiše se prekid ako je SPIE = 1 i ES = 1. SPIF bit se briše tako što se pročita SPSR i onda pristupi SPI data registru (SPDR). 6 WCOL Write Collision Flag. WCOL bit se postavlja na 1 ako je vršen upis u SPDR tokom prenosa podataka. Tokom prenosa podataka, očitavanjem SPDR mogu da se dobiju pogrešni podaci, a pisanje u njega nema efekta. WCOL bit se briše (kao i SPIF bit) tako što se očita SPSR, a zatim pristupi SPDR. 0– 5 ------ Ovi bitovi nisu definisani

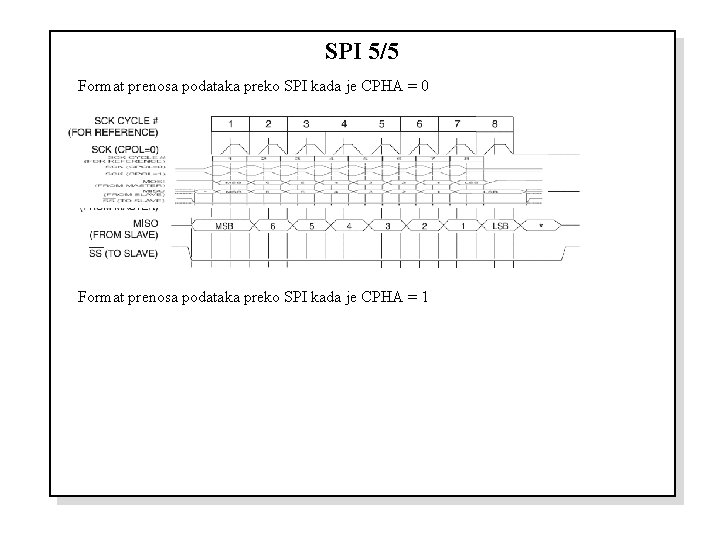

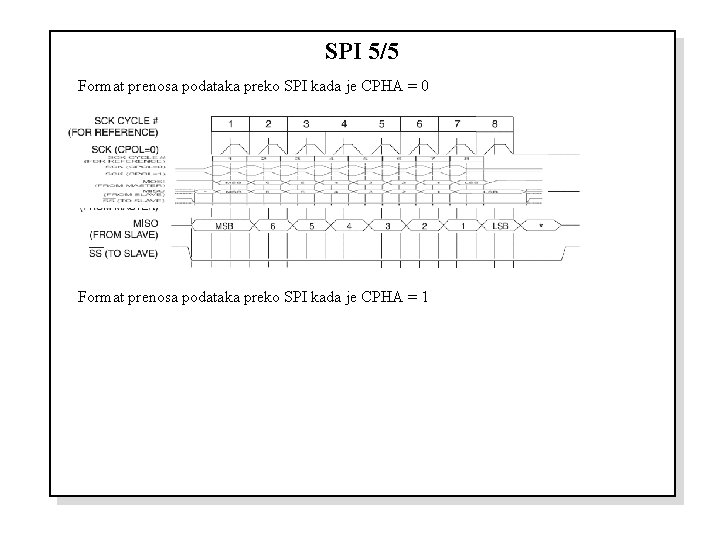

SPI 5/5 Format prenosa podataka preko SPI kada je CPHA = 0 Format prenosa podataka preko SPI kada je CPHA = 1

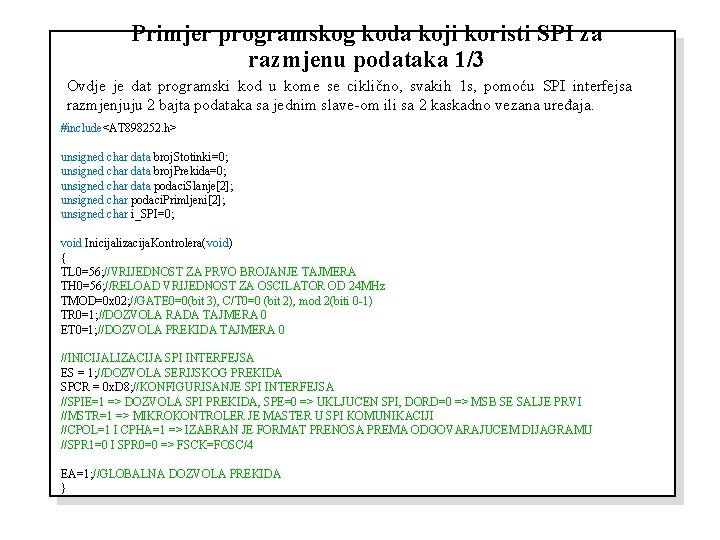

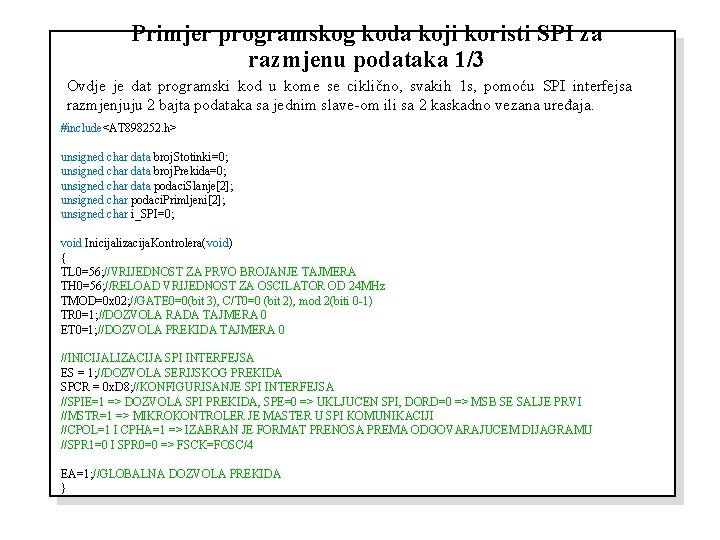

Primjer programskog koda koji koristi SPI za razmjenu podataka 1/3 Ovdje je dat programski kod u kome se ciklično, svakih 1 s, pomoću SPI interfejsa razmjenjuju 2 bajta podataka sa jednim slave-om ili sa 2 kaskadno vezana uređaja. #include<AT 898252. h> unsigned char data broj. Stotinki=0; unsigned char data broj. Prekida=0; unsigned char data podaci. Slanje[2]; unsigned char podaci. Primljeni[2]; unsigned char i_SPI=0; void Inicijalizacija. Kontrolera(void) { TL 0=56; //VRIJEDNOST ZA PRVO BROJANJE TAJMERA TH 0=56; //RELOAD VRIJEDNOST ZA OSCILATOR OD 24 MHz TMOD=0 x 02; //GATE 0=0(bit 3), C/T 0=0 (bit 2), mod 2(biti 0 -1) TR 0=1; //DOZVOLA RADA TAJMERA 0 ET 0=1; //DOZVOLA PREKIDA TAJMERA 0 //INICIJALIZACIJA SPI INTERFEJSA ES = 1; //DOZVOLA SERIJSKOG PREKIDA SPCR = 0 x. D 8; //KONFIGURISANJE SPI INTERFEJSA //SPIE=1 => DOZVOLA SPI PREKIDA, SPE=0 => UKLJUCEN SPI, DORD=0 => MSB SE SALJE PRVI //MSTR=1 => MIKROKONTROLER JE MASTER U SPI KOMUNIKACIJI //CPOL=1 I CPHA=1 => IZABRAN JE FORMAT PRENOSA PREMA ODGOVARAJUCEM DIJAGRAMU //SPR 1=0 I SPR 0=0 => FSCK=FOSC/4 EA=1; //GLOBALNA DOZVOLA PREKIDA }

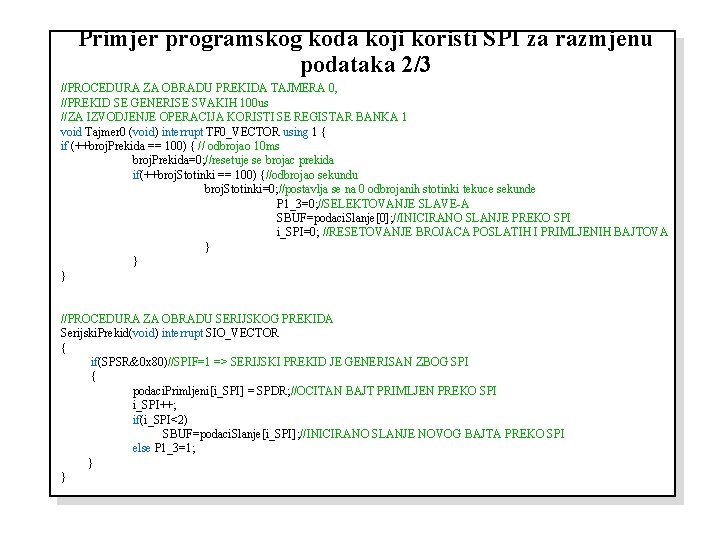

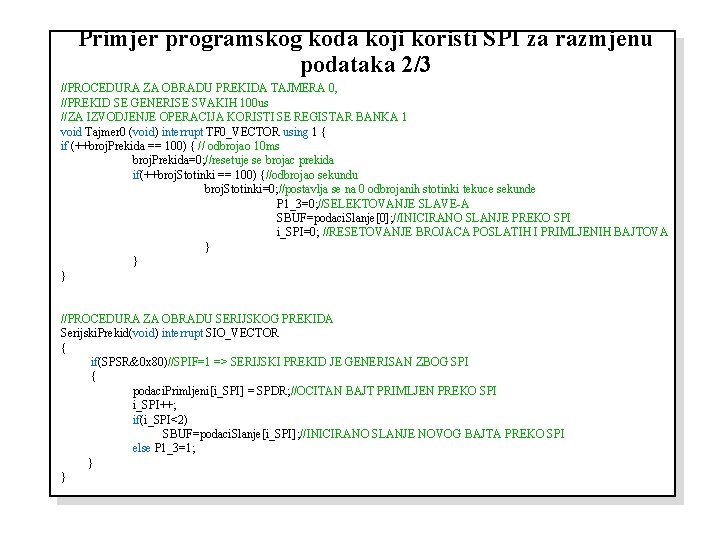

Primjer programskog koda koji koristi SPI za razmjenu podataka 2/3 //PROCEDURA ZA OBRADU PREKIDA TAJMERA 0, //PREKID SE GENERISE SVAKIH 100 us //ZA IZVODJENJE OPERACIJA KORISTI SE REGISTAR BANKA 1 void Tajmer 0 (void) interrupt TF 0_VECTOR using 1 { if (++broj. Prekida == 100) { // odbrojao 10 ms broj. Prekida=0; //resetuje se brojac prekida if(++broj. Stotinki == 100) {//odbrojao sekundu broj. Stotinki=0; //postavlja se na 0 odbrojanih stotinki tekuce sekunde P 1_3=0; //SELEKTOVANJE SLAVE-A SBUF=podaci. Slanje[0]; //INICIRANO SLANJE PREKO SPI i_SPI=0; //RESETOVANJE BROJACA POSLATIH I PRIMLJENIH BAJTOVA } } } //PROCEDURA ZA OBRADU SERIJSKOG PREKIDA Serijski. Prekid(void) interrupt SIO_VECTOR { if(SPSR&0 x 80)//SPIF=1 => SERIJSKI PREKID JE GENERISAN ZBOG SPI { podaci. Primljeni[i_SPI] = SPDR; //OCITAN BAJT PRIMLJEN PREKO SPI i_SPI++; if(i_SPI<2) SBUF=podaci. Slanje[i_SPI]; //INICIRANO SLANJE NOVOG BAJTA PREKO SPI else P 1_3=1; } }

Primjer programskog koda koji koristi SPI za razmjenu podataka 3/3 //FUNKCIJA MAIN void main (void) { Inicijalizacija. Kontrolera(); while (1){ } }

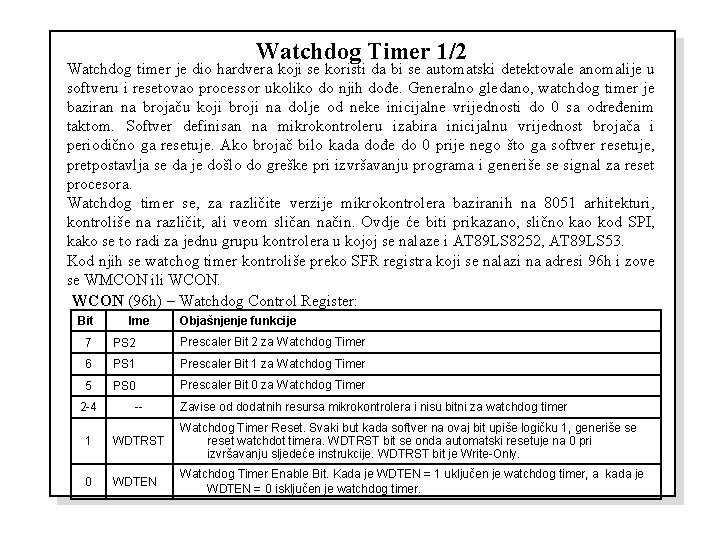

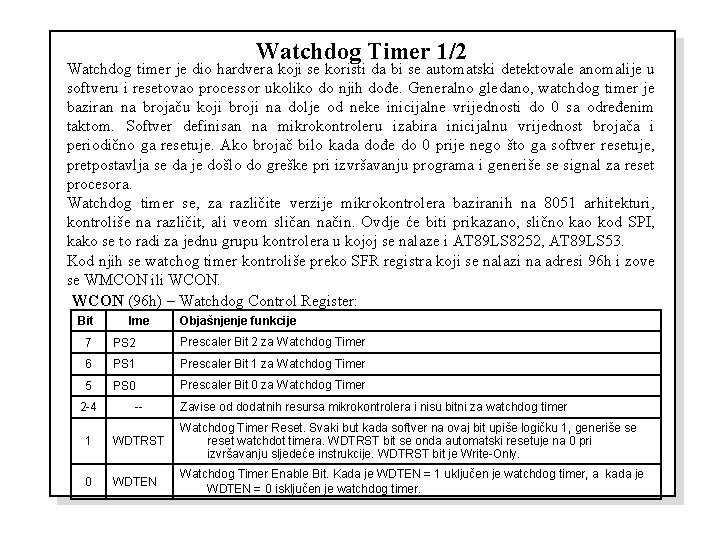

Watchdog Timer 1/2 Watchdog timer je dio hardvera koji se koristi da bi se automatski detektovale anomalije u softveru i resetovao processor ukoliko do njih dođe. Generalno gledano, watchdog timer je baziran na brojaču koji broji na dolje od neke inicijalne vrijednosti do 0 sa određenim taktom. Softver definisan na mikrokontroleru izabira inicijalnu vrijednost brojača i periodično ga resetuje. Ako brojač bilo kada dođe do 0 prije nego što ga softver resetuje, pretpostavlja se da je došlo do greške pri izvršavanju programa i generiše se signal za reset procesora. Watchdog timer se, za različite verzije mikrokontrolera baziranih na 8051 arhitekturi, kontroliše na različit, ali veom sličan način. Ovdje će biti prikazano, slično kao kod SPI, kako se to radi za jednu grupu kontrolera u kojoj se nalaze i AT 89 LS 8252, AT 89 LS 53. Kod njih se watchog timer kontroliše preko SFR registra koji se nalazi na adresi 96 h i zove se WMCON ili WCON (96 h) – Watchdog Control Register: Bit Ime Objašnjenje funkcije 7 PS 2 Prescaler Bit 2 za Watchdog Timer 6 PS 1 Prescaler Bit 1 za Watchdog Timer 5 PS 0 Prescaler Bit 0 za Watchdog Timer 2 -4 -- Zavise od dodatnih resursa mikrokontrolera i nisu bitni za watchdog timer 1 WDTRST Watchdog Timer Reset. Svaki but kada softver na ovaj bit upiše logičku 1, generiše se reset watchdot timera. WDTRST bit se onda automatski resetuje na 0 pri izvršavanju sljedeće instrukcije. WDTRST bit je Write-Only. 0 WDTEN Watchdog Timer Enable Bit. Kada je WDTEN = 1 uključen je watchdog timer, a kada je WDTEN = 0 isključen je watchdog timer.

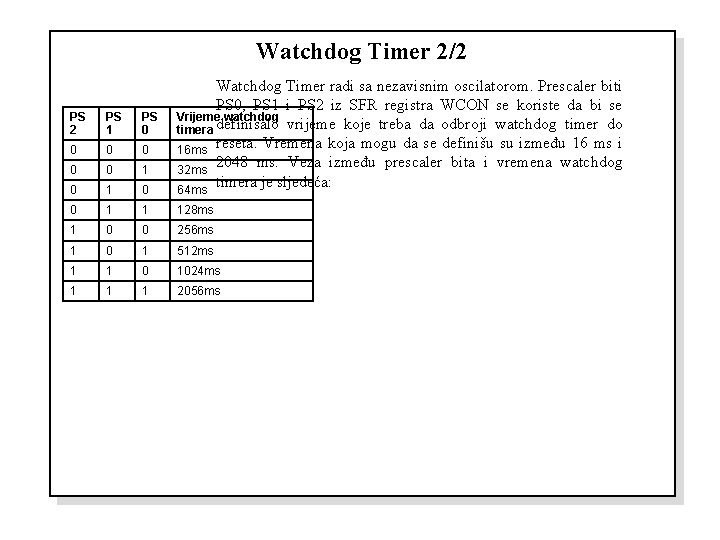

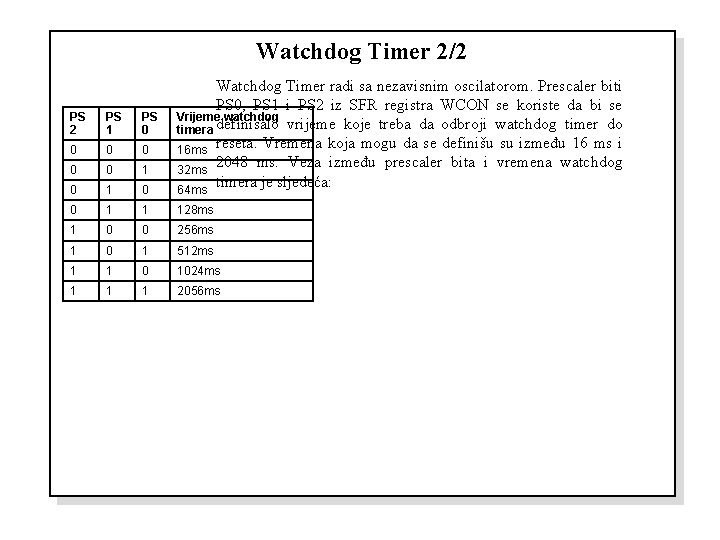

Watchdog Timer 2/2 PS 1 PS 0 0 0 1 0 Watchdog Timer radi sa nezavisnim oscilatorom. Prescaler biti PS 0, PS 1 i PS 2 iz SFR registra WCON se koriste da bi se Vrijeme watchdog timera definisalo vrijeme koje treba da odbroji watchdog timer do 16 ms reseta. Vremena koja mogu da se definišu su između 16 ms i 2048 ms. Veza između prescaler bita i vremena watchdog 32 ms timera je sljedeća: 64 ms 0 1 1 128 ms 1 0 0 256 ms 1 0 1 512 ms 1 1 0 1024 ms 1 1 1 2056 ms

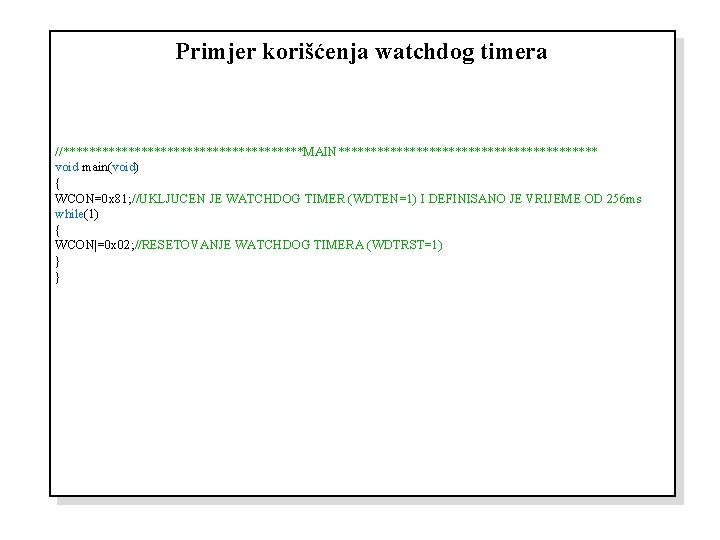

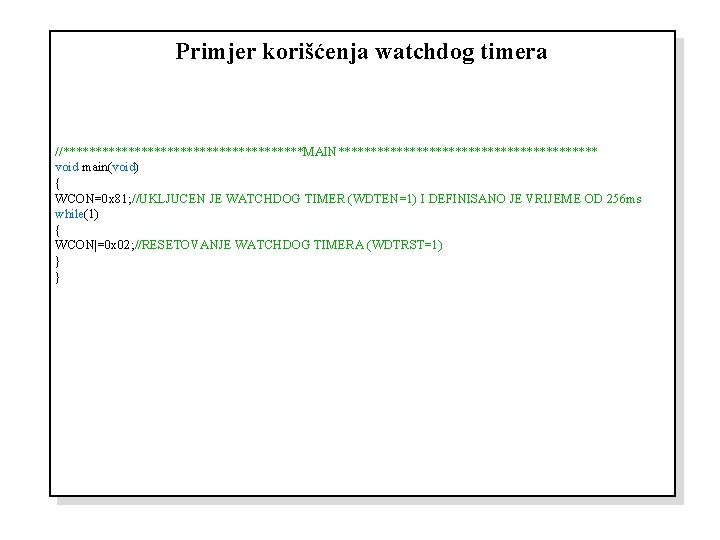

Primjer korišćenja watchdog timera //*******************MAIN******************** void main(void) { WCON=0 x 81; //UKLJUCEN JE WATCHDOG TIMER (WDTEN=1) I DEFINISANO JE VRIJEME OD 256 ms while(1) { WCON|=0 x 02; //RESETOVANJE WATCHDOG TIMERA (WDTRST=1) } }