8051 System Hanbat National University prof Song Myoung

8051 System 구조 정보통신 • 컴퓨터 공학부 송명규 Hanbat National University prof. Song Myoung Gyu 1

![8051 특징 [1] 마이크로프로세서 마이크로콘트롤러 Hanbat National University prof. Song Myoung Gyu 2 8051 특징 [1] 마이크로프로세서 마이크로콘트롤러 Hanbat National University prof. Song Myoung Gyu 2](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-2.jpg)

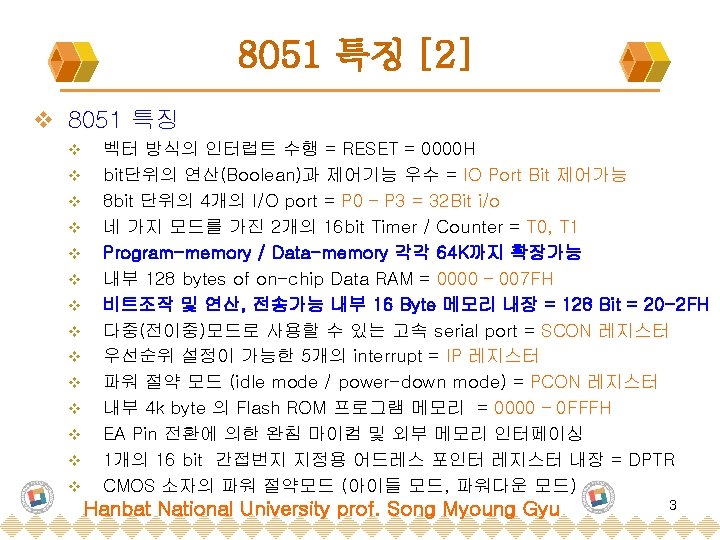

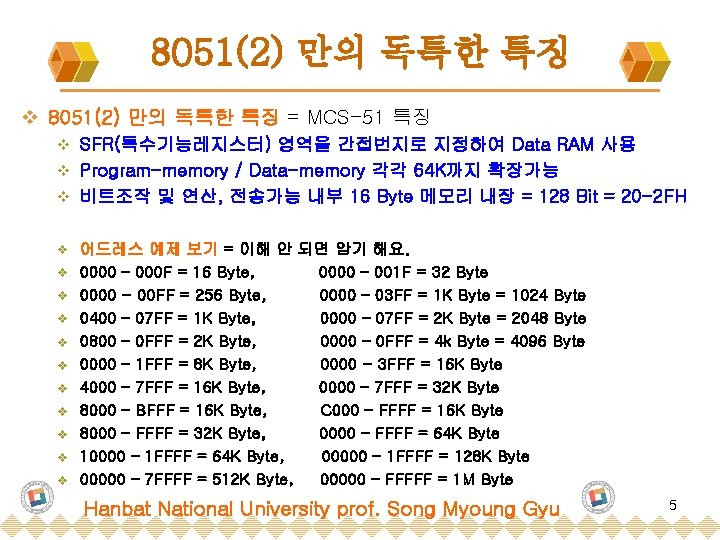

8051 특징 [1] 마이크로프로세서 마이크로콘트롤러 Hanbat National University prof. Song Myoung Gyu 2

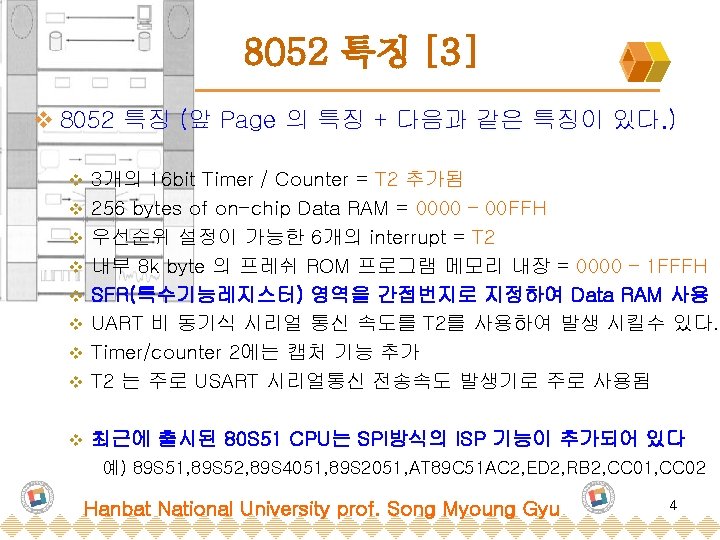

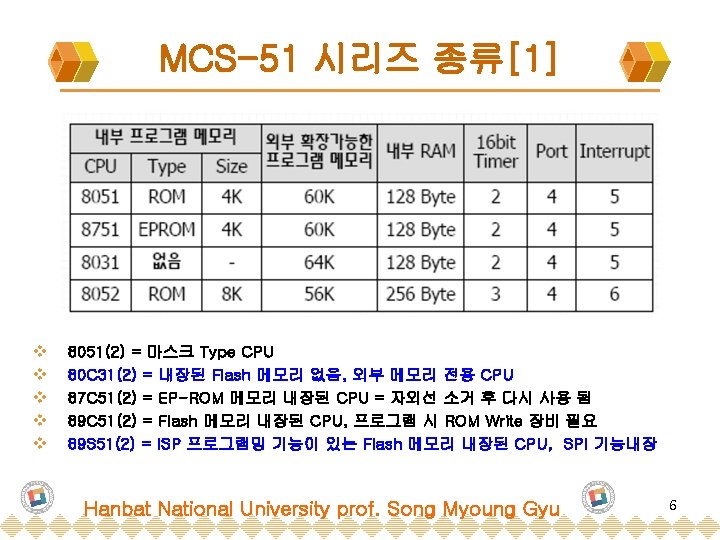

8051(2) 만의 독특한 특징 v 8051(2) 만의 독특한 특징 = MCS-51 특징 SFR(특수기능레지스터) 영역을 간접번지로 지정하여 Data RAM 사용 v Program-memory / Data-memory 각각 64 K까지 확장가능 v 비트조작 및 연산, 전송가능 내부 16 Byte 메모리 내장 = 128 Bit = 20 -2 FH v v v 어드레스 예제 보기 = 이해 안 되면 암기 해요. 0000 – 000 F = 16 Byte, 0000 – 001 F = 32 Byte 0000 - 00 FF = 256 Byte, 0000 – 03 FF = 1 K Byte = 1024 Byte 0400 – 07 FF = 1 K Byte, 0000 – 07 FF = 2 K Byte = 2048 Byte 0800 – 0 FFF = 2 K Byte, 0000 – 0 FFF = 4 k Byte = 4096 Byte 0000 – 1 FFF = 8 K Byte, 0000 - 3 FFF = 16 K Byte 4000 – 7 FFF = 16 K Byte, 0000 – 7 FFF = 32 K Byte 8000 – BFFF = 16 K Byte, C 000 – FFFF = 16 K Byte 8000 – FFFF = 32 K Byte, 0000 – FFFF = 64 K Byte 10000 – 1 FFFF = 64 K Byte, 00000 – 1 FFFF = 128 K Byte 00000 – 7 FFFF = 512 K Byte, 00000 – FFFFF = 1 M Byte Hanbat National University prof. Song Myoung Gyu 5

![MCS-51 시리즈 종류[2] Atmel 사에서 출시되는 8051 시리즈 Hanbat National University prof. Song Myoung MCS-51 시리즈 종류[2] Atmel 사에서 출시되는 8051 시리즈 Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-7.jpg)

MCS-51 시리즈 종류[2] Atmel 사에서 출시되는 8051 시리즈 Hanbat National University prof. Song Myoung Gyu 7

![MCS-51 시리즈 종류[3] Philps 사에서 출시되는 8051 시리즈 Hanbat National University prof. Song Myoung MCS-51 시리즈 종류[3] Philps 사에서 출시되는 8051 시리즈 Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-8.jpg)

MCS-51 시리즈 종류[3] Philps 사에서 출시되는 8051 시리즈 Hanbat National University prof. Song Myoung Gyu 8

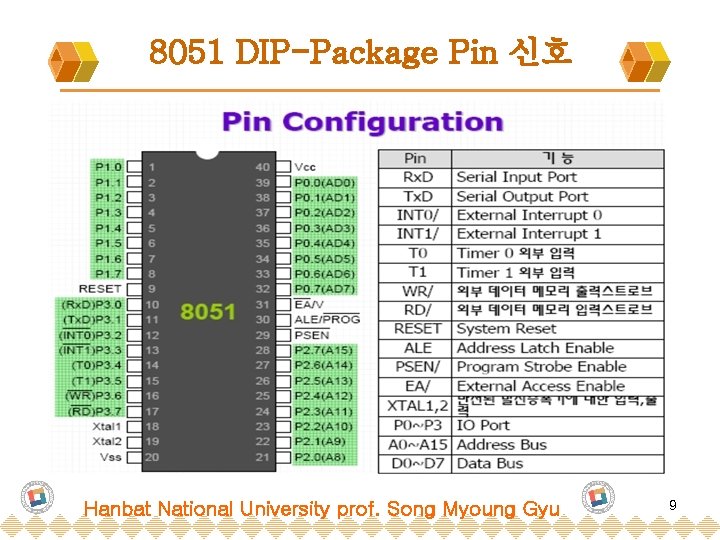

8051 DIP-Package Pin 신호 Hanbat National University prof. Song Myoung Gyu 9

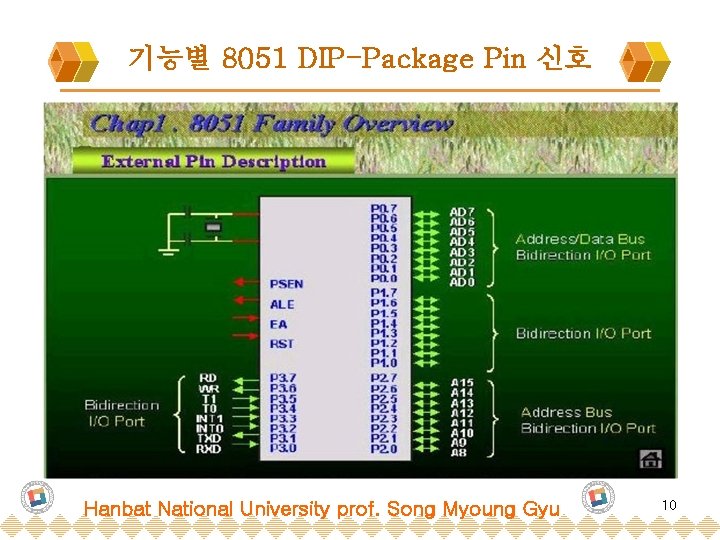

기능별 8051 DIP-Package Pin 신호 Hanbat National University prof. Song Myoung Gyu 10

![8051 외부 Pin 기능 [1] Pin 기 능 Rx. D 시리얼 입력 포트 Tx. 8051 외부 Pin 기능 [1] Pin 기 능 Rx. D 시리얼 입력 포트 Tx.](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-11.jpg)

8051 외부 Pin 기능 [1] Pin 기 능 Rx. D 시리얼 입력 포트 Tx. D 시리얼 출력 포트 INT 0 외부 인터럽트 0 INT 1 외부 인터럽트 1 T 0 타이머 0 외부 입력 T 1 타이머 1 외부 입력 WR 외부 데이터 메모리 출력 스트로브 RD 외부 데이터 메모리 입력 스트로브 RESET 시스템 리셋 ALE/PROG Address Latch Enable PSEN Program Strobe ENable EA/Vpp External Access Enable XTAL 1, 2 반전된 발진 증폭기에 대한 입력, 출력 P 0~3 입출력 포트 A 0~A 15 Address Bus D 0~D 7 Data Bus Hanbat National University prof. Song Myoung Gyu 11

![8051 외부 Pin 기능 [2] Hanbat National University prof. Song Myoung Gyu 12 8051 외부 Pin 기능 [2] Hanbat National University prof. Song Myoung Gyu 12](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-12.jpg)

8051 외부 Pin 기능 [2] Hanbat National University prof. Song Myoung Gyu 12

![8051 외부 Pin 기능 [3] Hanbat National University prof. Song Myoung Gyu 13 8051 외부 Pin 기능 [3] Hanbat National University prof. Song Myoung Gyu 13](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-13.jpg)

8051 외부 Pin 기능 [3] Hanbat National University prof. Song Myoung Gyu 13

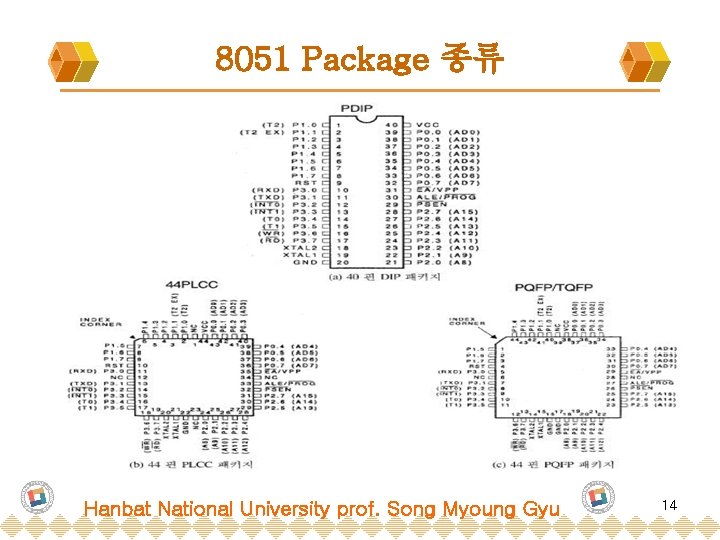

8051 Package 종류 Hanbat National University prof. Song Myoung Gyu 14

![8051 Block Diagram [1] Hanbat National University prof. Song Myoung Gyu 15 8051 Block Diagram [1] Hanbat National University prof. Song Myoung Gyu 15](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-15.jpg)

8051 Block Diagram [1] Hanbat National University prof. Song Myoung Gyu 15

![8051 Block Diagram [2] Hanbat National University prof. Song Myoung Gyu 16 8051 Block Diagram [2] Hanbat National University prof. Song Myoung Gyu 16](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-16.jpg)

8051 Block Diagram [2] Hanbat National University prof. Song Myoung Gyu 16

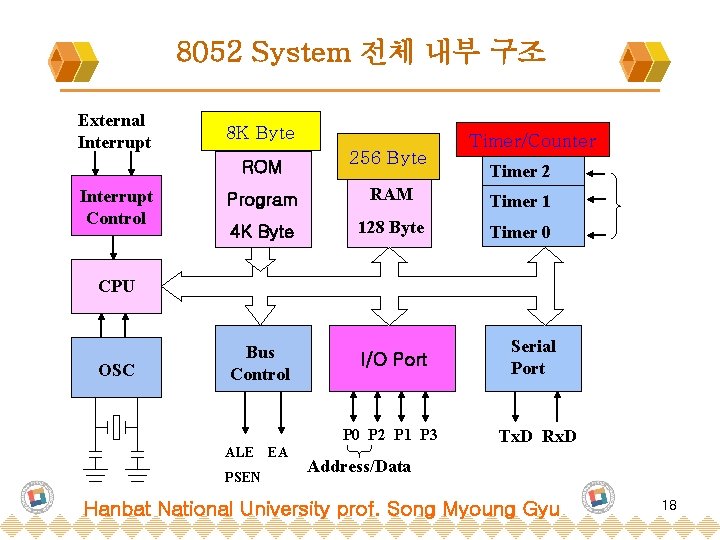

8051 System 전체 내부 구조 Hanbat National University prof. Song Myoung Gyu 17

8052 System 전체 내부 구조 External Interrupt Control 8 K Byte Timer/Counter ROM 256 Byte Program RAM Timer 1 4 K Byte 128 Byte Timer 0 Bus Control I/O Port Serial Port P 0 P 2 P 1 P 3 Tx. D Rx. D Timer 2 CPU OSC ALE EA PSEN Address/Data Hanbat National University prof. Song Myoung Gyu 18

![8051 주요 레지스터 [1] v CPU v PC (Program Counter) v v 16 bit 8051 주요 레지스터 [1] v CPU v PC (Program Counter) v v 16 bit](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-19.jpg)

8051 주요 레지스터 [1] v CPU v PC (Program Counter) v v 16 bit Register = 다음에 수행할 명령어 번지수를 가리키는 어드레스 포인터 ALU (Arithmetic Logic Unit) = 누산기 v 8 bit 논리연산 v 캐리 없는 덧셈, 캐리 있는 덧셈/뺄셈 v 8 bit / 16 bit increment, 8 bit decrement v BCD(Binary Coded Decimal) 10진 조정 v 곱셈 / 나눗셈 v AND, OR, XOR, rotate v Byte/Bit complement v Nibble 단위의 데이터 교환 v Bit 단위 (Boolean) 처리기능 v 조건 점프의 판단기능 v 연산 결과값 저장 및 연산상테 반영 = PSW 레지스터와 연결동작 Hanbat National University prof. Song Myoung Gyu 19

![8051 주요 레지스터[5] PSW (Program Status Word) Register [1] Hanbat National University prof. Song 8051 주요 레지스터[5] PSW (Program Status Word) Register [1] Hanbat National University prof. Song](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-23.jpg)

8051 주요 레지스터[5] PSW (Program Status Word) Register [1] Hanbat National University prof. Song Myoung Gyu 23

![8051 주요 레지스터[6] PSW (Program Status Word) Register [2] Hanbat National University prof. Song 8051 주요 레지스터[6] PSW (Program Status Word) Register [2] Hanbat National University prof. Song](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-24.jpg)

8051 주요 레지스터[6] PSW (Program Status Word) Register [2] Hanbat National University prof. Song Myoung Gyu 24

![8051 주요 레지스터[7] PSW (Program Status Word) Register [3] Hanbat National University prof. Song 8051 주요 레지스터[7] PSW (Program Status Word) Register [3] Hanbat National University prof. Song](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-25.jpg)

8051 주요 레지스터[7] PSW (Program Status Word) Register [3] Hanbat National University prof. Song Myoung Gyu 25

![SFR(Special Function Register) 특수기능 레지스터 [1] Hanbat National University prof. Song Myoung Gyu 26 SFR(Special Function Register) 특수기능 레지스터 [1] Hanbat National University prof. Song Myoung Gyu 26](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-26.jpg)

SFR(Special Function Register) 특수기능 레지스터 [1] Hanbat National University prof. Song Myoung Gyu 26

![SFR(Special Function Register) 특수기능 레지스터 [2] Hanbat National University prof. Song Myoung Gyu 27 SFR(Special Function Register) 특수기능 레지스터 [2] Hanbat National University prof. Song Myoung Gyu 27](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-27.jpg)

SFR(Special Function Register) 특수기능 레지스터 [2] Hanbat National University prof. Song Myoung Gyu 27

![SFR(Special Function Register) 특수기능 레지스터 [3] Hanbat National University prof. Song Myoung Gyu 28 SFR(Special Function Register) 특수기능 레지스터 [3] Hanbat National University prof. Song Myoung Gyu 28](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-28.jpg)

SFR(Special Function Register) 특수기능 레지스터 [3] Hanbat National University prof. Song Myoung Gyu 28

![SFR(Special Function Register) 특수기능 레지스터 [4] Hanbat National University prof. Song Myoung Gyu 29 SFR(Special Function Register) 특수기능 레지스터 [4] Hanbat National University prof. Song Myoung Gyu 29](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-29.jpg)

SFR(Special Function Register) 특수기능 레지스터 [4] Hanbat National University prof. Song Myoung Gyu 29

![SFR(Special Function Register) 특수기능 레지스터 [5] Hanbat National University prof. Song Myoung Gyu 30 SFR(Special Function Register) 특수기능 레지스터 [5] Hanbat National University prof. Song Myoung Gyu 30](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-30.jpg)

SFR(Special Function Register) 특수기능 레지스터 [5] Hanbat National University prof. Song Myoung Gyu 30

![SFR(Special Function Register) 특수기능 레지스터 [6] Hanbat National University prof. Song Myoung Gyu 31 SFR(Special Function Register) 특수기능 레지스터 [6] Hanbat National University prof. Song Myoung Gyu 31](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-31.jpg)

SFR(Special Function Register) 특수기능 레지스터 [6] Hanbat National University prof. Song Myoung Gyu 31

![SFR(Special Function Register) 특수기능 레지스터 [8] v 내부 RAM 0 x 80 ~ 0 SFR(Special Function Register) 특수기능 레지스터 [8] v 내부 RAM 0 x 80 ~ 0](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-33.jpg)

SFR(Special Function Register) 특수기능 레지스터 [8] v 내부 RAM 0 x 80 ~ 0 x. FF에 할당 = 직접번지 지정 방식으로만 접근 가능 v CPU 동작과 관련된 레지스터 = A, B, PSW, SP, DPTR v 포트 (Port) : P 0, P 1, P 2, P 3 v Interrupt : IP, IE v Power Control : PCON v Timer : TCON, TMOD, TL 0, TL 1, TH 0, TH 1 v Serial 통신 : SCON, SBUF v 주변 칩과 내장 주변기기 연계성 = 참고용 - UART = 8251(1 ch), 8250(2 ch) - Timer/Count = 8253(1 M), 8254(4 M) - 외부인터럽트 = 8259 - I/O Port = 8255 Hanbat National University prof. Song Myoung Gyu 33

![SFR(Special Function Register) 특수기능 레지스터 [9] Hanbat National University prof. Song Myoung Gyu 34 SFR(Special Function Register) 특수기능 레지스터 [9] Hanbat National University prof. Song Myoung Gyu 34](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-34.jpg)

SFR(Special Function Register) 특수기능 레지스터 [9] Hanbat National University prof. Song Myoung Gyu 34

![8051 Memory MAP 1. 메모리 구조 [1] v - 64 K Byte 프로그램 메모리 8051 Memory MAP 1. 메모리 구조 [1] v - 64 K Byte 프로그램 메모리](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-35.jpg)

8051 Memory MAP 1. 메모리 구조 [1] v - 64 K Byte 프로그램 메모리 (Program Memory, CODE) - 64 K Byte 외부 데이터 메모리 (External Data Memory, XDATA) - 256 Byte 내부 데이터 메모리 (Internal Data Memory, 8052, IDATA) - 128 Byte 내부 데이터 메모리 (Internal Data Memory, 8051, DATA) Hanbat National University prof. Song Myoung Gyu 35

![8051 Memory MAP 1. 메모리 구조 [2] Hanbat National University prof. Song Myoung Gyu 8051 Memory MAP 1. 메모리 구조 [2] Hanbat National University prof. Song Myoung Gyu](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-36.jpg)

8051 Memory MAP 1. 메모리 구조 [2] Hanbat National University prof. Song Myoung Gyu 36

![8051 Memory MAP 1. 메모리 구조 [3] Hanbat National University prof. Song Myoung Gyu 8051 Memory MAP 1. 메모리 구조 [3] Hanbat National University prof. Song Myoung Gyu](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-37.jpg)

8051 Memory MAP 1. 메모리 구조 [3] Hanbat National University prof. Song Myoung Gyu 37

![8051 Memory MAP 2. 프로그램 메모리 [1] FFFF EA = 1 External ROM 64 8051 Memory MAP 2. 프로그램 메모리 [1] FFFF EA = 1 External ROM 64](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-38.jpg)

8051 Memory MAP 2. 프로그램 메모리 [1] FFFF EA = 1 External ROM 64 K 4 K(8051) 0 FFF 0000 Internal ROM EA=1 60 K 1000 0 FFF EA=0 0000 60 K Byte 외부 EA = 0 64 K Byte 외부 4 K Byte 내부 Program Memory Hanbat National University prof. Song Myoung Gyu 38

![8051 Memory MAP 2. 프로그램 메모리 [2] 8051 프로그램 메모리 8052 프로그램 메모리 Hanbat 8051 Memory MAP 2. 프로그램 메모리 [2] 8051 프로그램 메모리 8052 프로그램 메모리 Hanbat](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-39.jpg)

8051 Memory MAP 2. 프로그램 메모리 [2] 8051 프로그램 메모리 8052 프로그램 메모리 Hanbat National University prof. Song Myoung Gyu 39

![8051 Memory MAP 2. 프로그램 메모리 [3] Hanbat National University prof. Song Myoung Gyu 8051 Memory MAP 2. 프로그램 메모리 [3] Hanbat National University prof. Song Myoung Gyu](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-40.jpg)

8051 Memory MAP 2. 프로그램 메모리 [3] Hanbat National University prof. Song Myoung Gyu 40

![8051 Memory MAP 2. 프로그램 메모리 [4] v v v 8051 : 내부 4 8051 Memory MAP 2. 프로그램 메모리 [4] v v v 8051 : 내부 4](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-41.jpg)

8051 Memory MAP 2. 프로그램 메모리 [4] v v v 8051 : 내부 4 K Byte 내장 = 0000 - 0 FFFH 8052 : 냬부 8 K Byte 내장 = 000 – 1 FFFH 외부에 최대 64 K Byte 까지 인터페이스 할수 있다. EA Pin(31번)에 의해 외부 및 내부 Program Memory를 선택 가능 C언어 Key 워드 = code, const = PSEN 신호 와 연계 됨 Hanbat National University prof. Song Myoung Gyu 41

![8051 Memory MAP 3. Internal Data 메모리 구조 [1] Hanbat National University prof. Song 8051 Memory MAP 3. Internal Data 메모리 구조 [1] Hanbat National University prof. Song](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-42.jpg)

8051 Memory MAP 3. Internal Data 메모리 구조 [1] Hanbat National University prof. Song Myoung Gyu 42

![8051 Memory MAP 3. Internal Data 메모리 구조 [2] Hanbat National University prof. Song 8051 Memory MAP 3. Internal Data 메모리 구조 [2] Hanbat National University prof. Song](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-43.jpg)

8051 Memory MAP 3. Internal Data 메모리 구조 [2] Hanbat National University prof. Song Myoung Gyu 43

![8051 Memory MAP 3. Internal Data 메모리 구조 [3] FF FFFF Special Function Register 8051 Memory MAP 3. Internal Data 메모리 구조 [3] FF FFFF Special Function Register](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-44.jpg)

8051 Memory MAP 3. Internal Data 메모리 구조 [3] FF FFFF Special Function Register 80 7 F 30 2 F 20 1 F 18 17 10 0 F 08 07 00 (SFR) User Data Memory area Bit unit Processing area Bank 3 (R 0~R 7) Bank 2 (R 0~R 7) Bank 1 (R 0~R 7) Bank 0 (R 0~R 7) External RAM 64 K 0000 Data Memory Hanbat National University prof. Song Myoung Gyu 44

![8051 Memory MAP 3. Internal Data 메모리 구조 [4] Hanbat National University prof. Song 8051 Memory MAP 3. Internal Data 메모리 구조 [4] Hanbat National University prof. Song](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-45.jpg)

8051 Memory MAP 3. Internal Data 메모리 구조 [4] Hanbat National University prof. Song Myoung Gyu 45

![8051 Memory MAP 3. Internal Data 메모리 구조 [5] v Internal Memory v v 8051 Memory MAP 3. Internal Data 메모리 구조 [5] v Internal Memory v v](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-46.jpg)

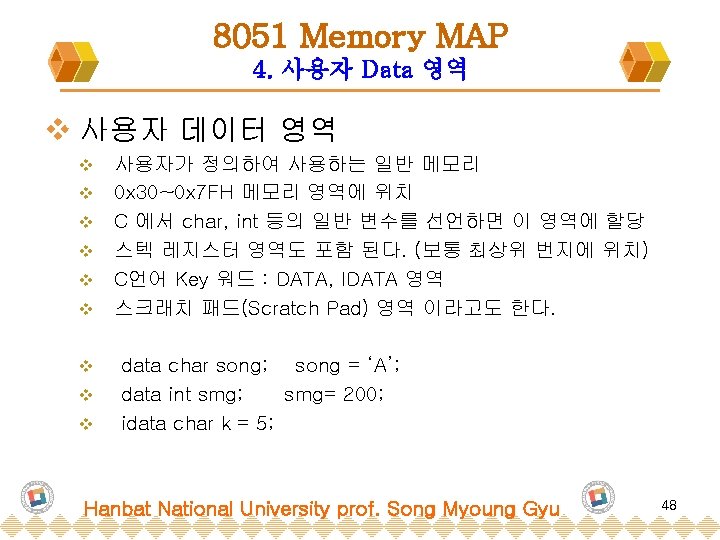

8051 Memory MAP 3. Internal Data 메모리 구조 [5] v Internal Memory v v v 내부 Data 메모리는 일반 Data RAM 영역, SFR 영역으로 구분 하위 128 Byte(00 -7 Fh) = 직접(data) 및 간접(idata) 번지로 호출 상위 128 Byte(80 -FFh) = 8052에만 있음, 직접(data)번지 = SFR 영역 간접(idata)번지 = 유저 RAM영역 8051 = 하위 128 Byte만 있음 8052 = 하위 128 Byte + 상위 128 Byte 가 있음 Data 저장 및 Stack 영역으로 사용 Stack = Stack point (SP) 는리셋되면 07 h = 뱅크 1영역에 위치 30 – 7 Fh는 사용자 RAM영역 = 직, 간접번지 지정가능, 사용자 Stack 위치 Common Variable Area (User Data Area = 30 – 7 Fh) Special Function Register (SFR = 80 - FFh) Bit unit processing variable area = 20 – 2 Fh C언어 Key 워드 = DATA(직접 00 -7 Fh), IDATA(간접 80 -FFh, 0852) Hanbat National University prof. Song Myoung Gyu 46

![8051 Memory MAP 3. Internal Data 메모리 구조 [6] 8051 데이타 메모리 8052 데이타 8051 Memory MAP 3. Internal Data 메모리 구조 [6] 8051 데이타 메모리 8052 데이타](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-47.jpg)

8051 Memory MAP 3. Internal Data 메모리 구조 [6] 8051 데이타 메모리 8052 데이타 메모리 Hanbat National University prof. Song Myoung Gyu 47

![8051 Memory MAP 5. Bit Addressable 영역 [1] Hanbat National University prof. Song Myoung 8051 Memory MAP 5. Bit Addressable 영역 [1] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-49.jpg)

8051 Memory MAP 5. Bit Addressable 영역 [1] Hanbat National University prof. Song Myoung Gyu 49

![8051 Memory MAP 5. Bit Addressable 영역 [2] Hanbat National University prof. Song Myoung 8051 Memory MAP 5. Bit Addressable 영역 [2] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-50.jpg)

8051 Memory MAP 5. Bit Addressable 영역 [2] Hanbat National University prof. Song Myoung Gyu 50

![8051 Memory MAP 5. Bit Addressable 영역 [3] v v 내부 RAM 0 x 8051 Memory MAP 5. Bit Addressable 영역 [3] v v 내부 RAM 0 x](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-51.jpg)

8051 Memory MAP 5. Bit Addressable 영역 [3] v v 내부 RAM 0 x 20~0 x 2 F 16바이트 각 비트 별로 변수 선언 가능 16 x 8=128개의 비트 변수 선언 가능 비트 번호 0 x 00~0 x 7 F로 선언 v C에서 선언과 사용 - bit keyst; - 0과 1의 boolean 상태 bit save, cy; save = (P 1^4) ^ (P 1^5); - 포트 1의 4와 5핀의 상태를 XOR 한다 cy = (P 1^4 & P 1^5) | (save & P 1^6); bit key_flag = 0; key_flag = (~(key_flag); BDATA char key_buf; key_buf = 0 x 77; bit key_chk_flag = key_buf^0; key_chk_flag = 1; if(key_촤_flag){ } v v v v Hanbat National University prof. Song Myoung Gyu 51

![8051 Memory MAP 6. Register Banks [1] Hanbat National University prof. Song Myoung Gyu 8051 Memory MAP 6. Register Banks [1] Hanbat National University prof. Song Myoung Gyu](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-52.jpg)

8051 Memory MAP 6. Register Banks [1] Hanbat National University prof. Song Myoung Gyu 52

![8051 Memory MAP 6. Register Banks [2] v PWS의 RS 1: RS 0에 의해 8051 Memory MAP 6. Register Banks [2] v PWS의 RS 1: RS 0에 의해](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-53.jpg)

8051 Memory MAP 6. Register Banks [2] v PWS의 RS 1: RS 0에 의해 뱅크가 할당되면 레지스터 R 0~R 7은 해당 뱅크로 주소 값이 설정 된다 RS[1: 0]=10 RS[1: 0]=01 RS[1: 0]=00 RS[1: 0]=11 R 7 07 R 7 0 F R 7 17 R 7 1 F R 6 06 R 6 0 E R 6 16 R 6 1 E R 5 05 R 5 0 D R 5 15 R 5 1 D R 4 04 R 4 0 C R 4 14 R 4 1 C R 3 03 R 3 0 B R 3 13 R 3 1 B R 2 02 R 2 0 A R 2 12 R 2 1 A R 1 01 R 1 09 R 1 11 R 1 19 R 0 00 R 0 08 R 0 10 R 0 18 bank 0 bank 1 bank 2 bank 3 R 0 : 00 R 0 : 08 R 0 : 10 R 0 : 18 Hanbat National University prof. Song Myoung Gyu 53

![8051 Memory MAP 6. Register Banks [3] Hanbat National University prof. Song Myoung Gyu 8051 Memory MAP 6. Register Banks [3] Hanbat National University prof. Song Myoung Gyu](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-54.jpg)

8051 Memory MAP 6. Register Banks [3] Hanbat National University prof. Song Myoung Gyu 54

![8051 Memory MAP 6. Register Banks [4] bank 0 bank 1 bank 2 bank 8051 Memory MAP 6. Register Banks [4] bank 0 bank 1 bank 2 bank](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-55.jpg)

8051 Memory MAP 6. Register Banks [4] bank 0 bank 1 bank 2 bank 3 . . . R 2 03 02 R 2 4 D 0 A R 2 B 5 12 R 2 B 5 1 A R 1 D 3 01 R 1 C 3 09 R 1 A 5 11 R 1 44 19 R 0 34 00 R 0 13 08 R 0 22 10 R 0 30 18 PSW RS[1: 0]=00 RS[1: 0]=01 RS[1: 0]=10 RS[1: 0]=11 R 0 34 13 22 30 Before A 11 22 33 44 After 34 13 22 30 A Hanbat National University prof. Song Myoung Gyu 55

![8051 Memory MAP 6. Register Banks [6] Hanbat National University prof. Song Myoung Gyu 8051 Memory MAP 6. Register Banks [6] Hanbat National University prof. Song Myoung Gyu](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-57.jpg)

8051 Memory MAP 6. Register Banks [6] Hanbat National University prof. Song Myoung Gyu 57

![8051 Memory MAP 6. Register Banks [7] v CPU Common Register = 00 – 8051 Memory MAP 6. Register Banks [7] v CPU Common Register = 00 –](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-58.jpg)

8051 Memory MAP 6. Register Banks [7] v CPU Common Register = 00 – 1 FH v R 0~R 7 Common register 4 bank v v v v 8개의 일반 데이터 저장용 레지스터 4개의 뱅크로 구성 기억장치에 주소지정으로 접근이 가능 CPU의 임시 기억장치의 역할 수행 순수 DATA만 저장 가능 A Register와 직접 자료교환 가능 뱅크 설정은 PSW의 RS 1: RS 0 bit를 설정하면, 이 R 0~R 7은 해당 메모리에 할당 된다. MOV PSW, #18 H, PSW = 0 x 18; // 뱅크 3 선택 SETB RS 1 CLR RS 0 // 뱅크 2 선택 sfr PSW = 0 xd 0; sbit RS 1 = PSW^4; sbit RS 0 = PSW^3; RS 1 = 1; RS 0 = 0; //뱅크 2 선택 v Hanbat National University prof. Song Myoung Gyu 58

![8051 Memory MAP 7. Extern Memory Interface [1] Hanbat National University prof. Song Myoung 8051 Memory MAP 7. Extern Memory Interface [1] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-59.jpg)

8051 Memory MAP 7. Extern Memory Interface [1] Hanbat National University prof. Song Myoung Gyu 59

![8051 Memory MAP 7. Extern Memory Interface [2] Hanbat National University prof. Song Myoung 8051 Memory MAP 7. Extern Memory Interface [2] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-60.jpg)

8051 Memory MAP 7. Extern Memory Interface [2] Hanbat National University prof. Song Myoung Gyu 60

![8051 Memory MAP 8. Extern Program Memory [1] Hanbat National University prof. Song Myoung 8051 Memory MAP 8. Extern Program Memory [1] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-61.jpg)

8051 Memory MAP 8. Extern Program Memory [1] Hanbat National University prof. Song Myoung Gyu 61

![8051 Memory MAP 8. Extern Program Memory [2] v v 8051은 내부 4 K 8051 Memory MAP 8. Extern Program Memory [2] v v 8051은 내부 4 K](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-62.jpg)

8051 Memory MAP 8. Extern Program Memory [2] v v 8051은 내부 4 K 바이트 ROM 0 x 0000~0 x 0 FFF 8051은 내부 8 K 바이트 ROM 0 x 0000 -0 x 1 FFF 외부 프로그램 메모리 가능 (64 K 바이트) 내부 ROM과 외부 ROM이 있을 경우 내부의 4 K 바이트 ROM을 선택 가능 FFFF EA=1 외부 ROM 64 K 외부 ROM 60 K 4 K(8051) 내부 ROM 사용 외부 ROM 4 K사용 않함 1000 0 FFF 0000 프로그램 메모리 FFFF EA=0 4 K(8051) 0 FFF 내부 ROM 사용 않함 1000 0 FFF 0000 프로그램 메모리 Hanbat National University prof. Song Myoung Gyu 62

![8051 Memory MAP 8. Extern Program Memory [3] 프로그램 메모리 타이밍 챠트 Hanbat National 8051 Memory MAP 8. Extern Program Memory [3] 프로그램 메모리 타이밍 챠트 Hanbat National](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-63.jpg)

8051 Memory MAP 8. Extern Program Memory [3] 프로그램 메모리 타이밍 챠트 Hanbat National University prof. Song Myoung Gyu 63

![8051 Memory MAP 8. Extern Program Memory [4] 명령어 읽기 타이밍 챠트 Hanbat National 8051 Memory MAP 8. Extern Program Memory [4] 명령어 읽기 타이밍 챠트 Hanbat National](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-64.jpg)

8051 Memory MAP 8. Extern Program Memory [4] 명령어 읽기 타이밍 챠트 Hanbat National University prof. Song Myoung Gyu 64

![8051 Memory MAP 8. Extern Program Memory [5] 외부 프로그램 메모리 확장 (외부 ROM) 8051 Memory MAP 8. Extern Program Memory [5] 외부 프로그램 메모리 확장 (외부 ROM)](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-65.jpg)

8051 Memory MAP 8. Extern Program Memory [5] 외부 프로그램 메모리 확장 (외부 ROM) v v 64 K 바이트 까지 확장 가능한 프로그램 메모리 내부 4 K 바이트는 EA 핀으로 제어 v EA=0 : 전 영역을 외부 ROM으로 0 x 0000~0 x. FFFF v EA=1 : 8051 = 내부ROM(0 x 0000~0 x 0 FFF)+외부ROM(0 x 1000 -0 x. FFFF 8052 = 내부ROM(0 x 0000~0 x 1 FFF)+외부ROM(0 x 2000 -0 x. FFFF) 외부 ROM 리드시 PSEN 신호 출력 C언어 Key 워드 : CODE, CONST asm : MOV A, #90 h MOV DPTR, #3000 h MOVC A, @A+DPTR Hanbat National University prof. Song Myoung Gyu 65

![8051 Memory MAP 9. Extern Data Memory [1] Hanbat National University prof. Song Myoung 8051 Memory MAP 9. Extern Data Memory [1] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-66.jpg)

8051 Memory MAP 9. Extern Data Memory [1] Hanbat National University prof. Song Myoung Gyu 66

![8051 Memory MAP 9. Extern Data Memory [2] Hanbat National University prof. Song Myoung 8051 Memory MAP 9. Extern Data Memory [2] Hanbat National University prof. Song Myoung](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-67.jpg)

8051 Memory MAP 9. Extern Data Memory [2] Hanbat National University prof. Song Myoung Gyu 67

![8051 Memory MAP 9. Extern Data Memory [3] 외부 데이터 메모리 쓰기 타이밍 챠트 8051 Memory MAP 9. Extern Data Memory [3] 외부 데이터 메모리 쓰기 타이밍 챠트](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-68.jpg)

8051 Memory MAP 9. Extern Data Memory [3] 외부 데이터 메모리 쓰기 타이밍 챠트 Hanbat National University prof. Song Myoung Gyu 68

![8051 Memory MAP 9. Extern Data Memory [4] 외부 데이터 메모리 읽기 타이밍 챠트 8051 Memory MAP 9. Extern Data Memory [4] 외부 데이터 메모리 읽기 타이밍 챠트](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-69.jpg)

8051 Memory MAP 9. Extern Data Memory [4] 외부 데이터 메모리 읽기 타이밍 챠트 Hanbat National University prof. Song Myoung Gyu 69

![8051 Memory MAP 9. Extern Data Memory [5] v외부 v v v 데이터 메모리 8051 Memory MAP 9. Extern Data Memory [5] v외부 v v v 데이터 메모리](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-70.jpg)

8051 Memory MAP 9. Extern Data Memory [5] v외부 v v v 데이터 메모리 (외부 RAM) 내부 데이터 메모리와 별도로 64 K 바이트 까지 확장 가능 별도의 명령에 의해 외부 Data Access C언어 Key 워드 : XDATA(0000 -ffff), PDATA(0000 -00 ff) v. MOVX A, @DPTR v. MOVX @DPTR, A v. RD, WR 신호 출력 #define SELECT (*(unsigned char*)(0 x 1 fc 48)) SELECT = 0 x 9 e; #define ADDR (*(unsigned char xdata *)(0 x 12000)) ADDR = 0 x 31; C = *((char xdata *) 0 x 17000); Hanbat National University prof. Song Myoung Gyu 70

![8051 메모리 인터페이스 샘플 회로도 [1] Hanbat National University prof. Song Myoung Gyu 71 8051 메모리 인터페이스 샘플 회로도 [1] Hanbat National University prof. Song Myoung Gyu 71](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-71.jpg)

8051 메모리 인터페이스 샘플 회로도 [1] Hanbat National University prof. Song Myoung Gyu 71

![8051 메모리 인터페이스 샘플 회로도 [2] fc 0 1 48 Hanbat National University prof. 8051 메모리 인터페이스 샘플 회로도 [2] fc 0 1 48 Hanbat National University prof.](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-72.jpg)

8051 메모리 인터페이스 샘플 회로도 [2] fc 0 1 48 Hanbat National University prof. Song Myoung Gyu 72

![8051 메모리 인터페이스 샘플 회로도 [3] Hanbat National University prof. Song Myoung Gyu 73 8051 메모리 인터페이스 샘플 회로도 [3] Hanbat National University prof. Song Myoung Gyu 73](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-73.jpg)

8051 메모리 인터페이스 샘플 회로도 [3] Hanbat National University prof. Song Myoung Gyu 73

![8051 메모리 인터페이스 샘플 회로도 [4] Hanbat National University prof. Song Myoung Gyu 74 8051 메모리 인터페이스 샘플 회로도 [4] Hanbat National University prof. Song Myoung Gyu 74](http://slidetodoc.com/presentation_image_h/849269015809e2fafe491e07ce73baaf/image-74.jpg)

8051 메모리 인터페이스 샘플 회로도 [4] Hanbat National University prof. Song Myoung Gyu 74

- Slides: 74