8051 l l 8051 CPU 8051 dolicomnaver com

![뱅크의 개념 PSW MOV A, R 0 RS[1: 0]=10 RS[1: 0]=01 RS[1: 0]=00 RS[1: 뱅크의 개념 PSW MOV A, R 0 RS[1: 0]=10 RS[1: 0]=01 RS[1: 0]=00 RS[1:](https://slidetodoc.com/presentation_image_h2/74b7649fc3bdb9dedaf84b45028cf776/image-22.jpg)

- Slides: 83

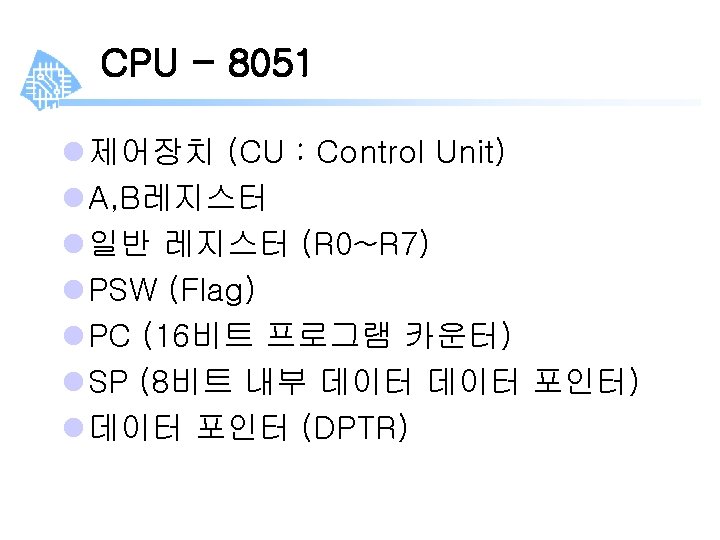

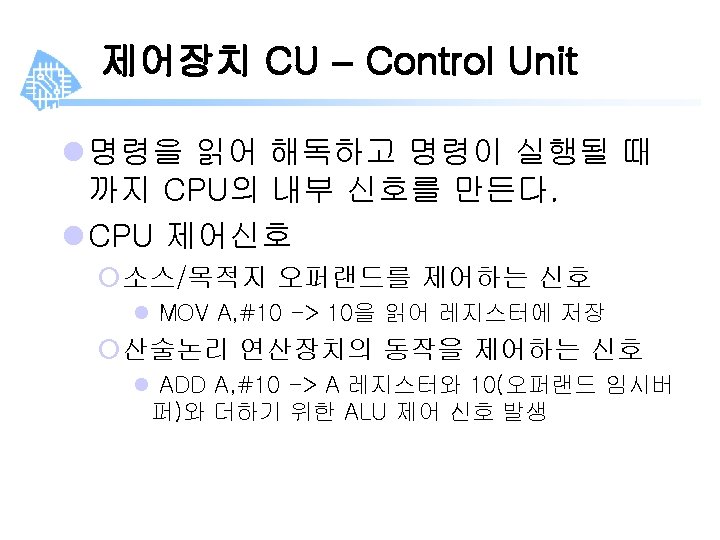

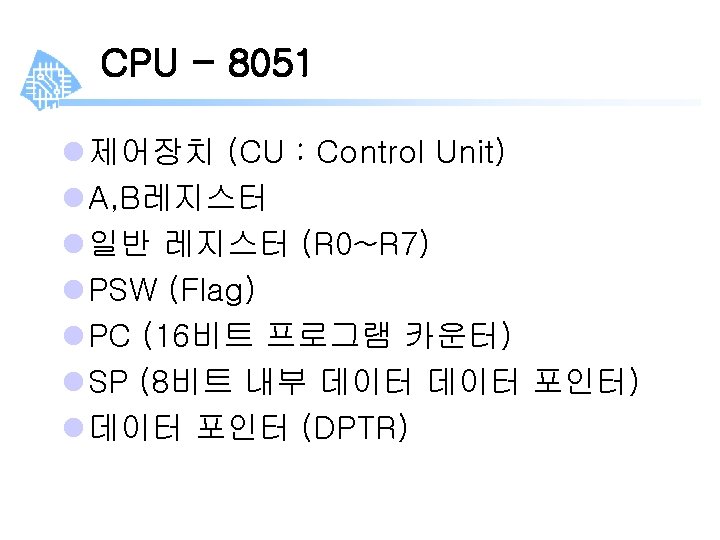

8051의 이해 l l 8051의 칩 구성 및 CPU 이해 메모리 구조 8051의 신호 포트 구성 dolicom@naver. com http: //blog. naver. com/dolicom

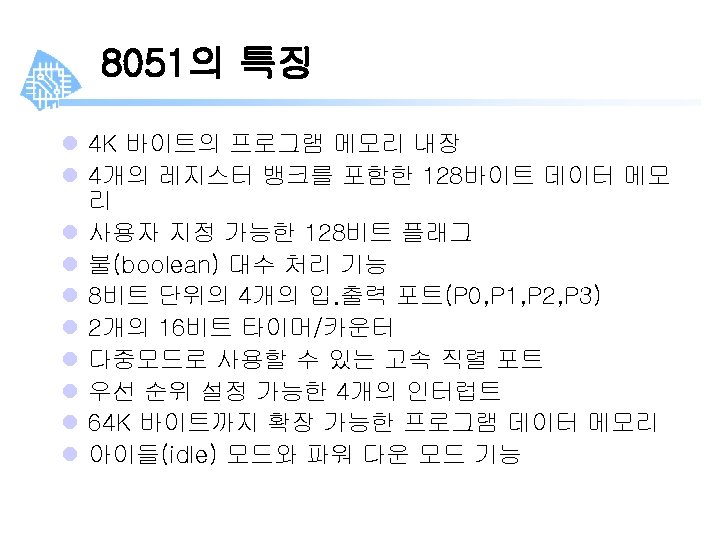

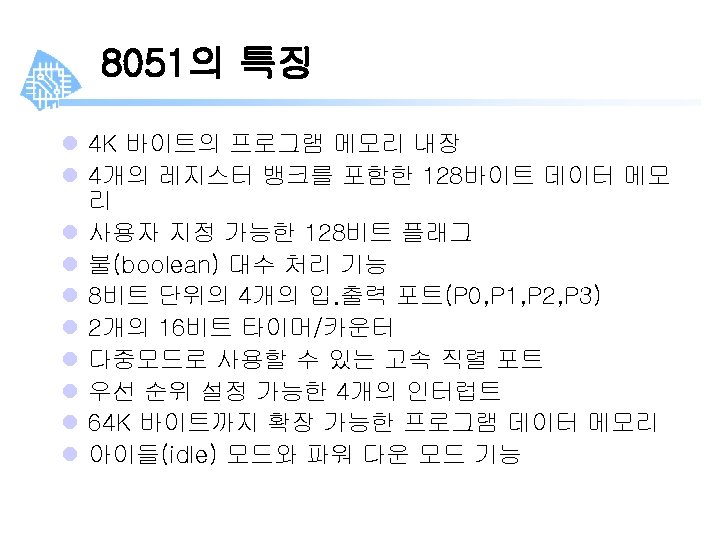

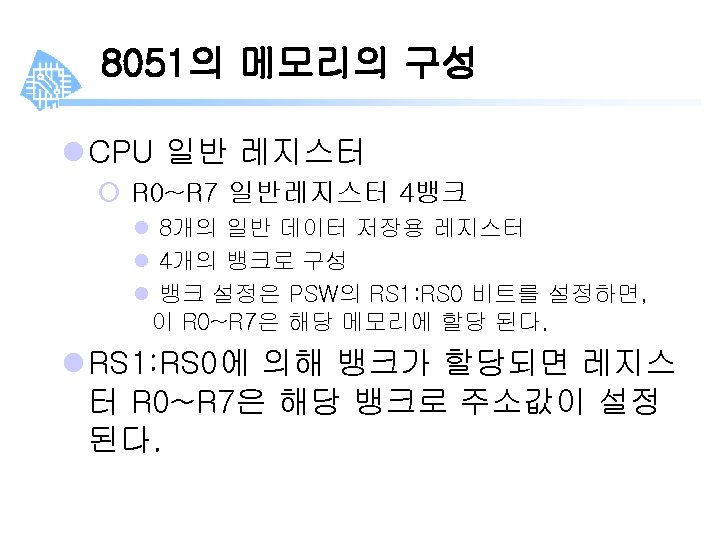

8051 패밀리 기능 ROM (program) RAM (데이터) Timer I/O 핀 Serial 포트 인터럽트 소스 8051 4 K 128 2 32 1 6 8052 8 K 256 3 32 1 8 8031 0 K 128 2 32 1 6

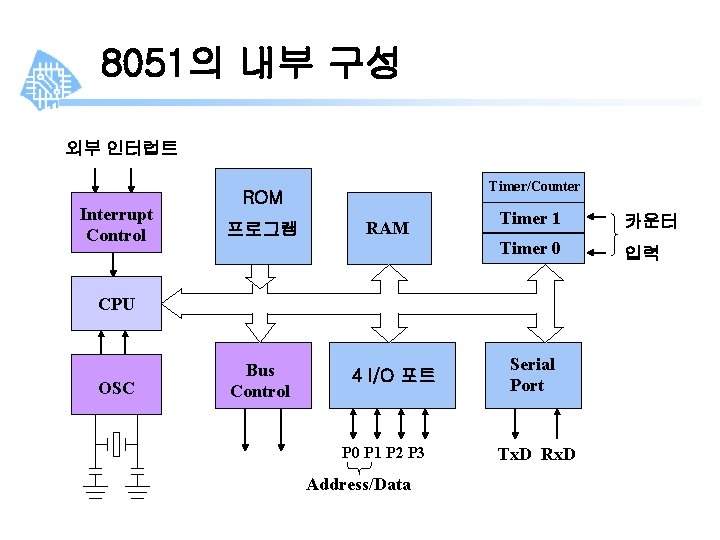

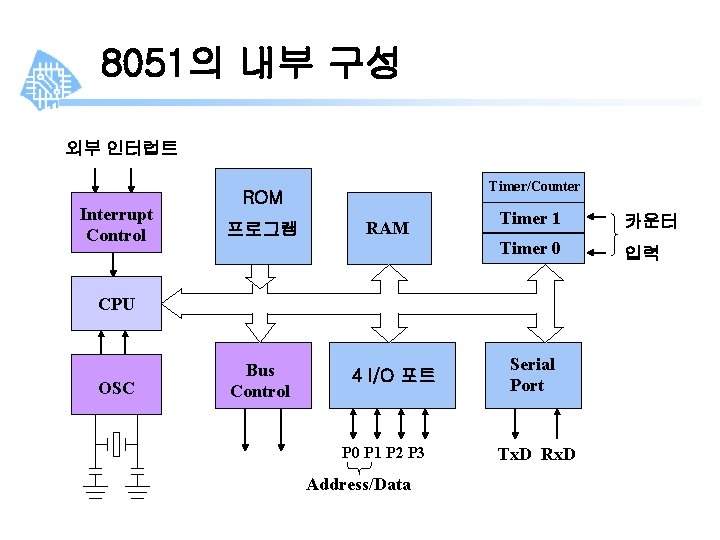

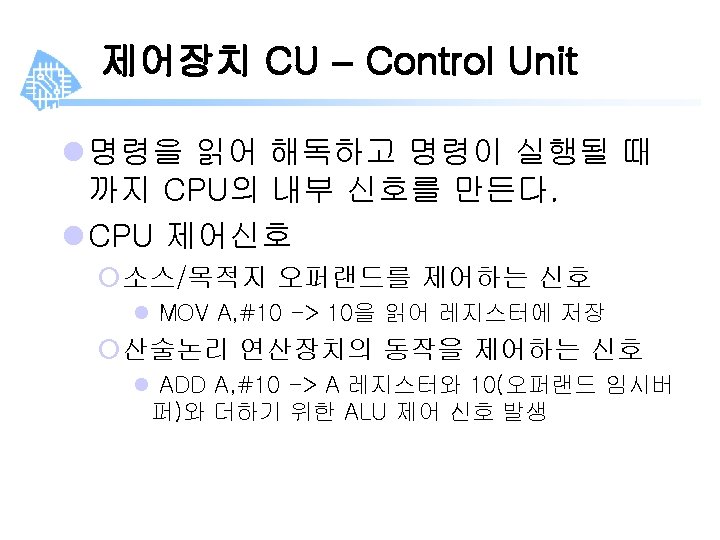

8051의 내부 구성 외부 인터럽트 Interrupt Control Timer/Counter ROM 프로그램 RAM Timer 1 카운터 Timer 0 입력 CPU OSC Bus Control 4 I/O 포트 P 0 P 1 P 2 P 3 Address/Data Serial Port Tx. D Rx. D

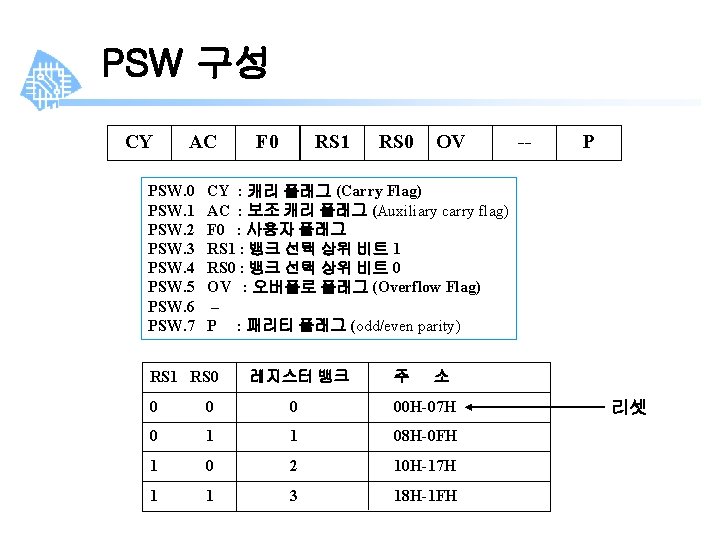

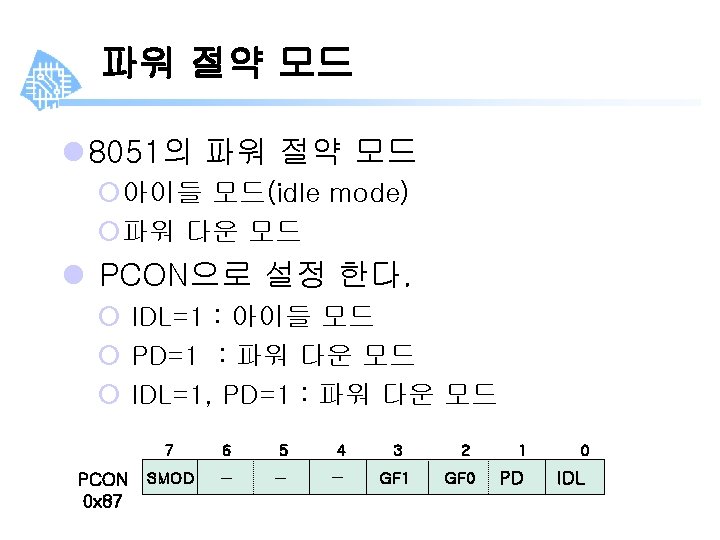

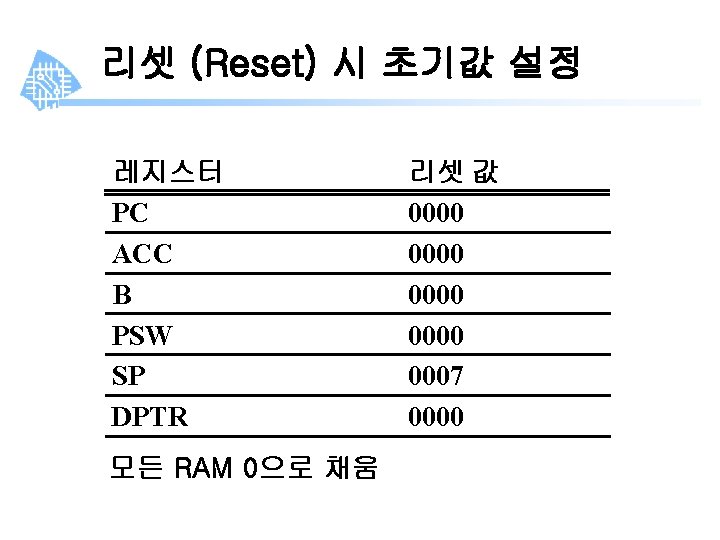

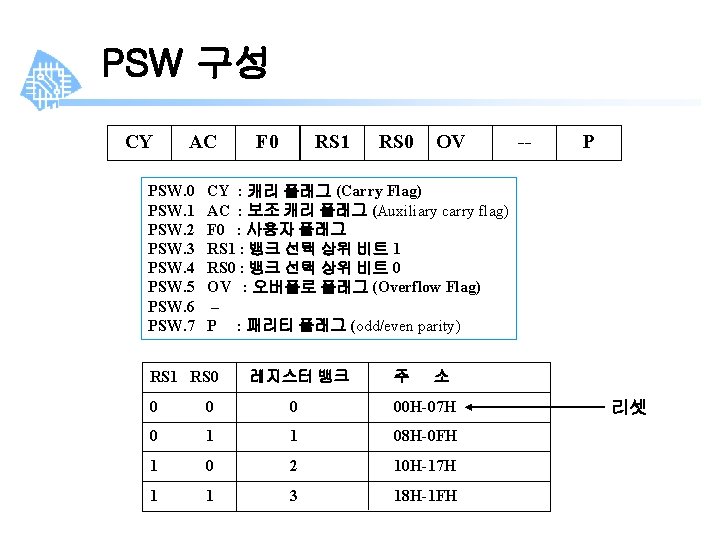

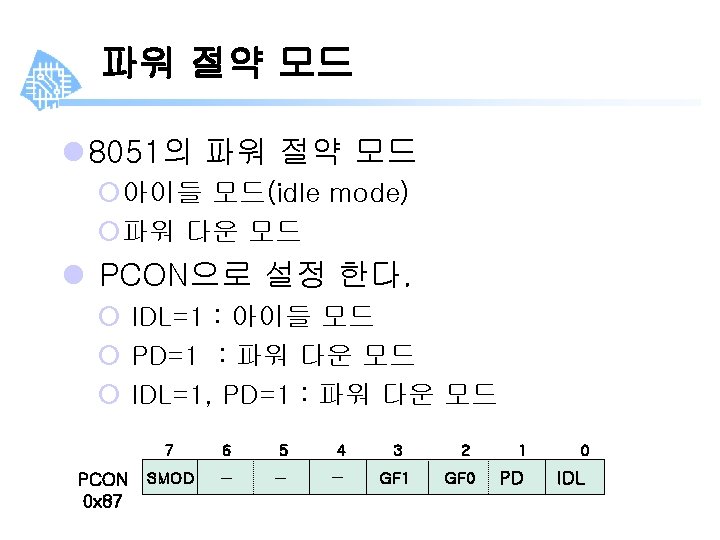

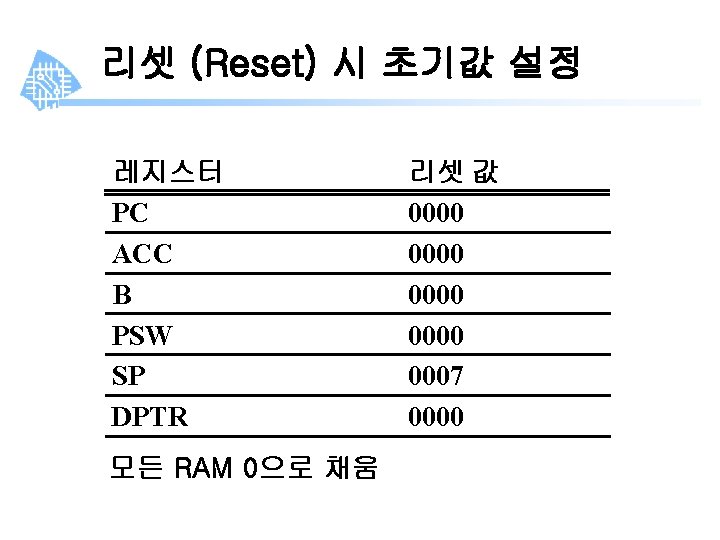

PSW 구성 CY AC PSW. 0 PSW. 1 PSW. 2 PSW. 3 PSW. 4 PSW. 5 PSW. 6 PSW. 7 F 0 RS 1 RS 0 OV -- P CY : 캐리 플래그 (Carry Flag) AC : 보조 캐리 플래그 (Auxiliary carry flag) F 0 : 사용자 플래그 RS 1 : 뱅크 선택 상위 비트 1 RS 0 : 뱅크 선택 상위 비트 0 OV : 오버플로 플래그 (Overflow Flag) – P : 패리티 플래그 (odd/even parity) RS 1 RS 0 레지스터 뱅크 주 소 0 00 H-07 H 0 1 1 08 H-0 FH 1 0 2 10 H-17 H 1 1 3 18 H-1 FH 리셋

![뱅크의 개념 PSW MOV A R 0 RS1 010 RS1 001 RS1 000 RS1 뱅크의 개념 PSW MOV A, R 0 RS[1: 0]=10 RS[1: 0]=01 RS[1: 0]=00 RS[1:](https://slidetodoc.com/presentation_image_h2/74b7649fc3bdb9dedaf84b45028cf776/image-22.jpg)

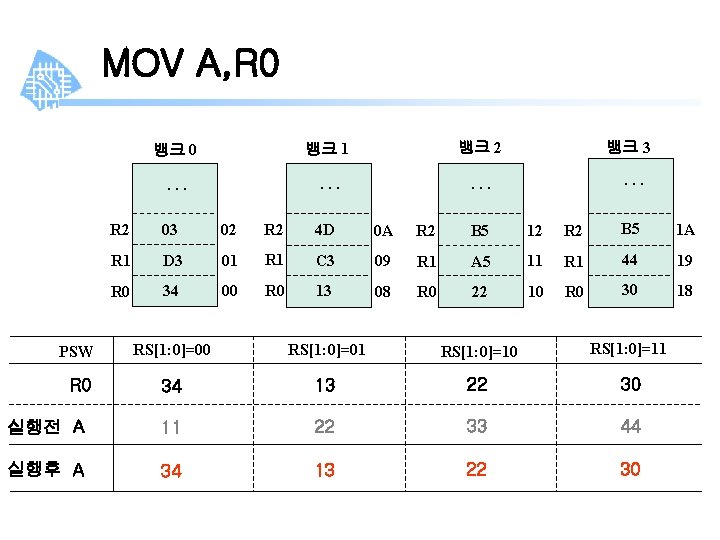

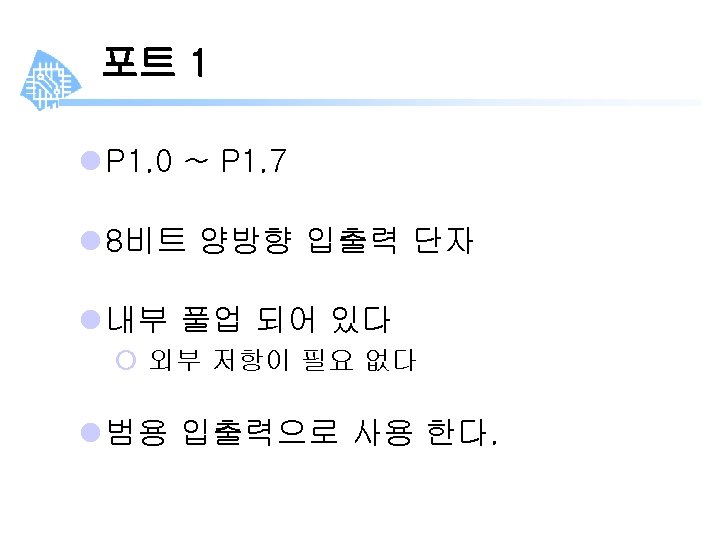

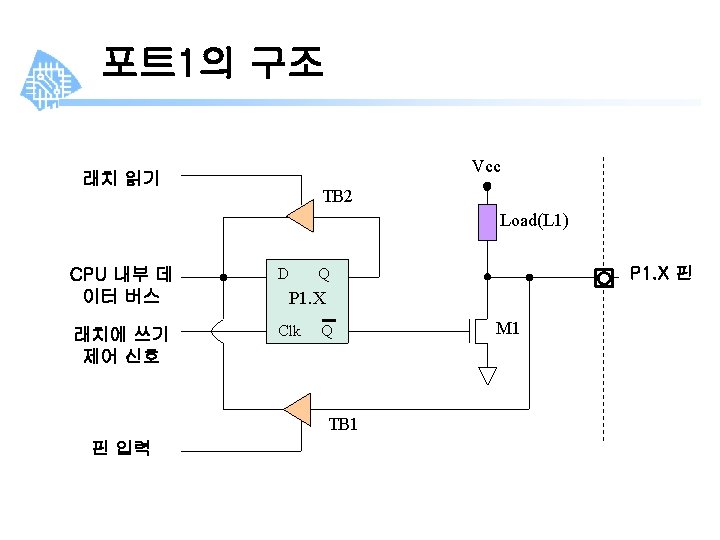

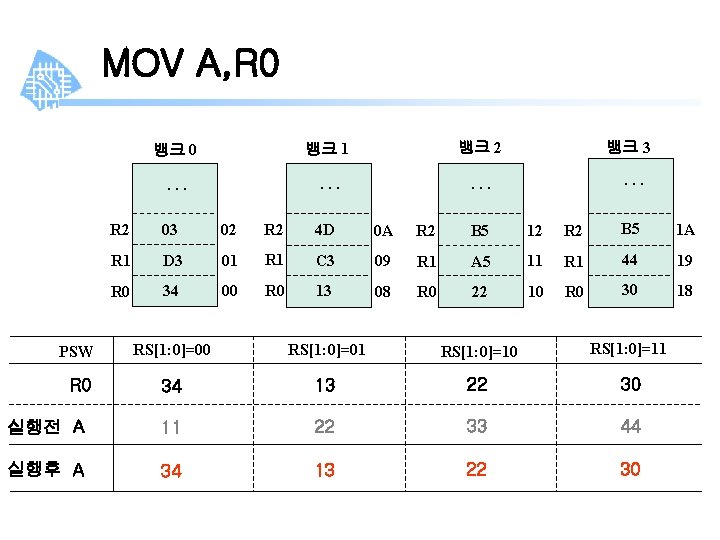

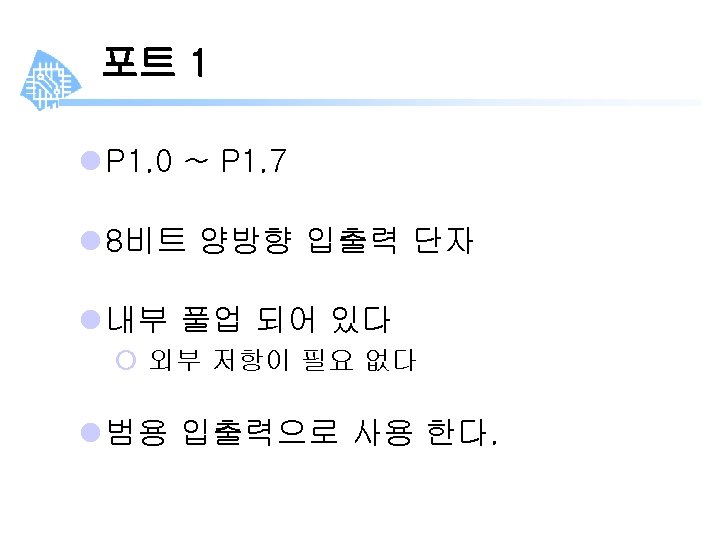

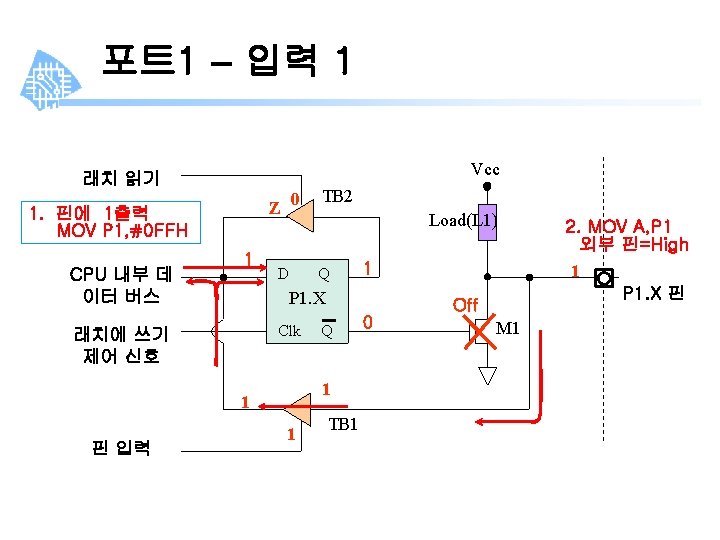

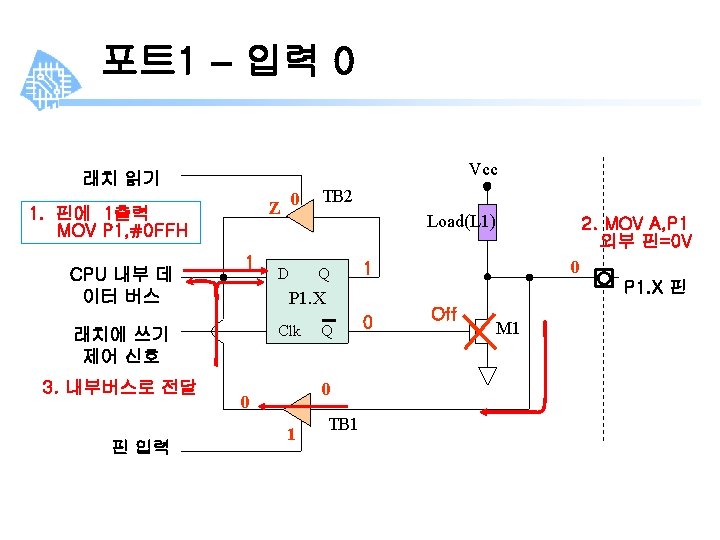

뱅크의 개념 PSW MOV A, R 0 RS[1: 0]=10 RS[1: 0]=01 RS[1: 0]=00 RS[1: 0]=11 R 7 07 R 7 0 F R 7 17 R 7 1 F R 6 06 R 6 0 E R 6 16 R 6 1 E R 5 05 R 5 0 D R 5 15 R 5 1 D R 4 04 R 4 0 C R 4 14 R 4 1 C R 3 03 R 3 0 B R 3 13 R 3 1 B R 2 02 R 2 0 A R 2 12 R 2 1 A R 1 01 R 1 09 R 1 11 R 1 19 R 0 00 R 0 08 R 0 10 R 0 18 뱅크 0 뱅크 1 뱅크 2 뱅크 3 R 0 : 00 R 0 : 08 R 0 : 10 R 0 : 18

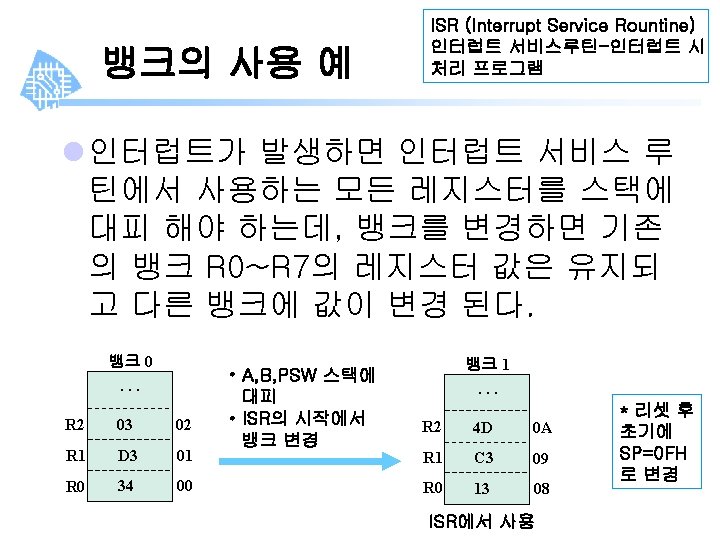

MOV A, R 0 뱅크 1 뱅크 2 . . 뱅크 3. . . R 2 03 02 R 2 4 D 0 A R 2 B 5 12 R 2 B 5 1 A R 1 D 3 01 R 1 C 3 09 R 1 A 5 11 R 1 44 19 R 0 34 00 R 0 13 08 R 0 22 10 R 0 30 18 PSW RS[1: 0]=00 RS[1: 0]=01 RS[1: 0]=10 RS[1: 0]=11 R 0 34 13 22 30 실행전 A 11 22 33 44 실행후 A 34 13 22 30

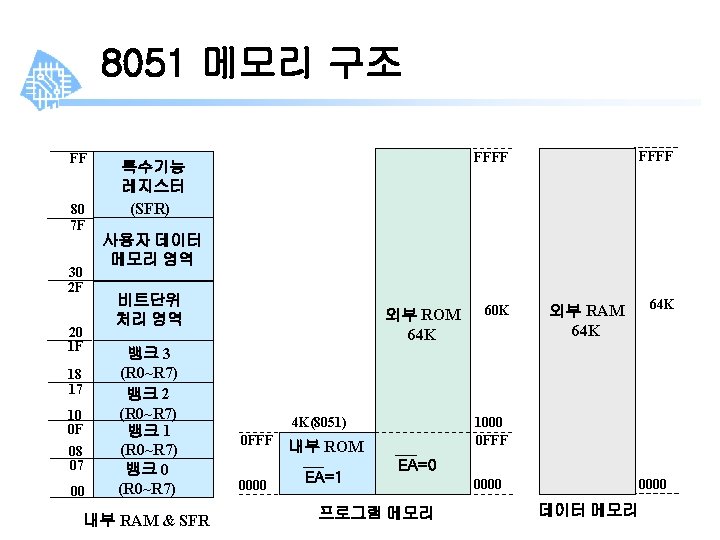

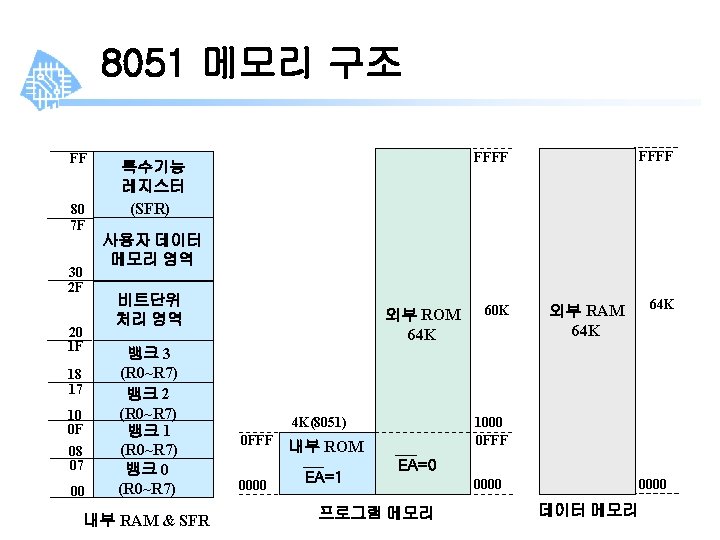

SFR – 특수 기능 레지스터 l 내부 RAM 0 x 80 ~ 0 x. FF에 할당 l CPU 동작과 관련된 레지스터 ¡ A, B, PSW, SP, DPTR l 포트 (Port) : P 0, P 1, P 2, P 3 l Interrupt : IP, IE l Power Control : PCON l Timer : TCON, TMOD, TL 0, TL 1, TH 0, TH 1 l Serial 통신 : SCON, SBUF

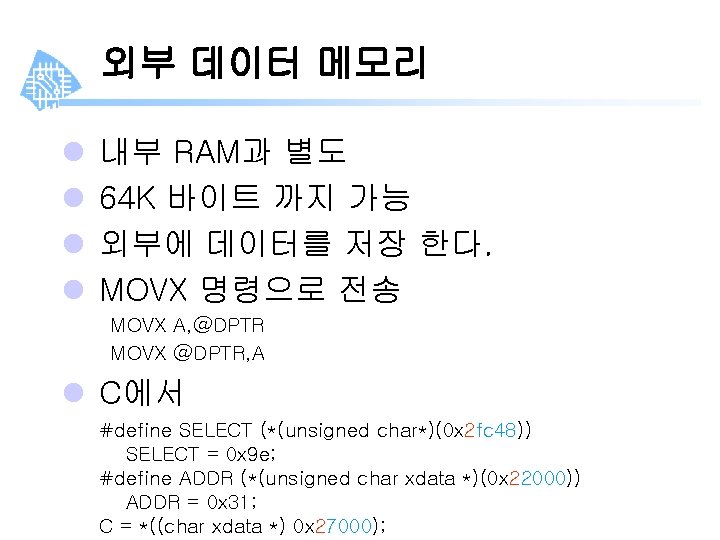

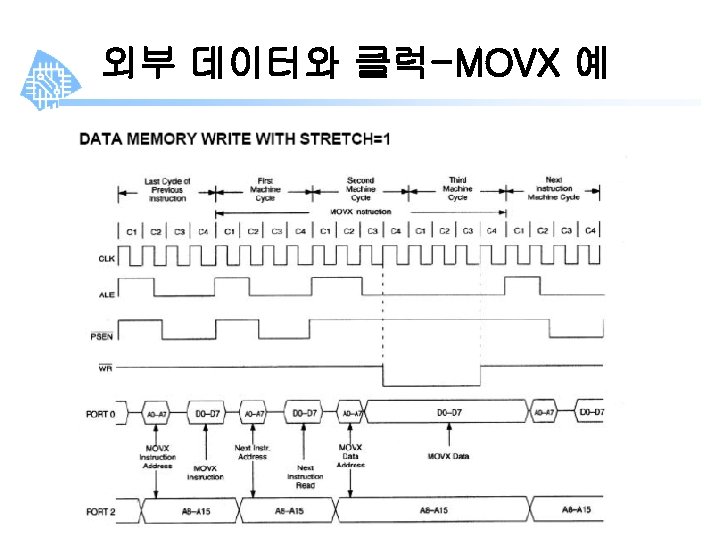

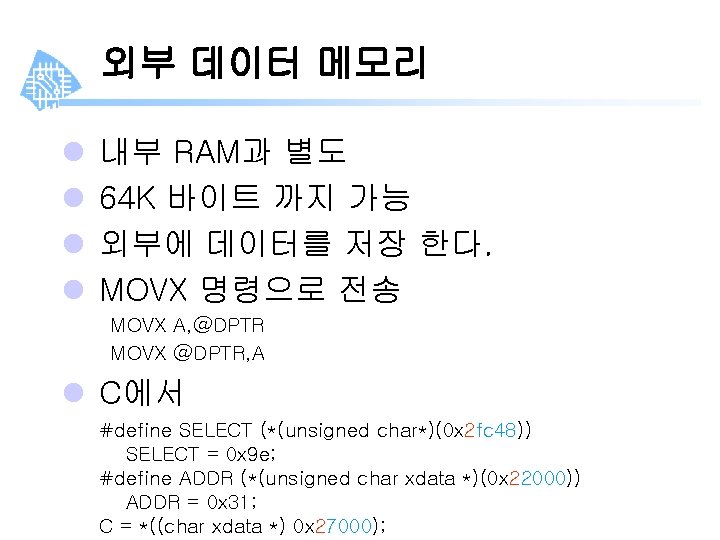

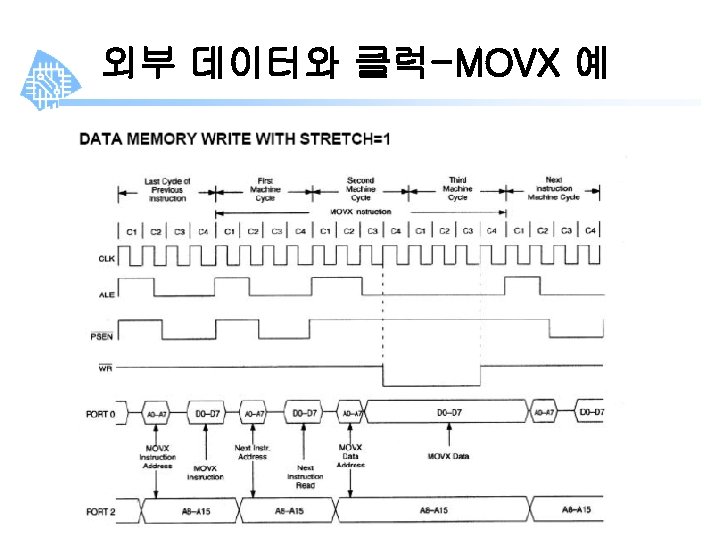

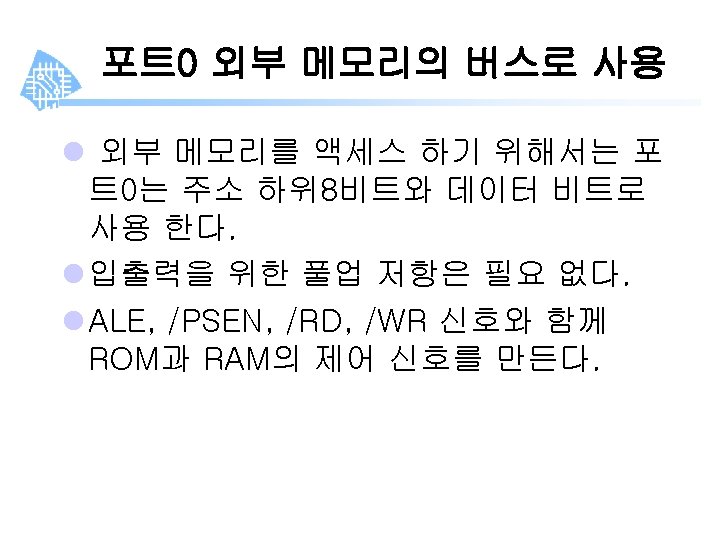

외부 데이터 메모리 l l 내부 RAM과 별도 64 K 바이트 까지 가능 외부에 데이터를 저장 한다. MOVX 명령으로 전송 MOVX A, @DPTR MOVX @DPTR, A l C에서 #define SELECT (*(unsigned char*)(0 x 2 fc 48)) SELECT = 0 x 9 e; #define ADDR (*(unsigned char xdata *)(0 x 22000)) ADDR = 0 x 31; C = *((char xdata *) 0 x 27000);

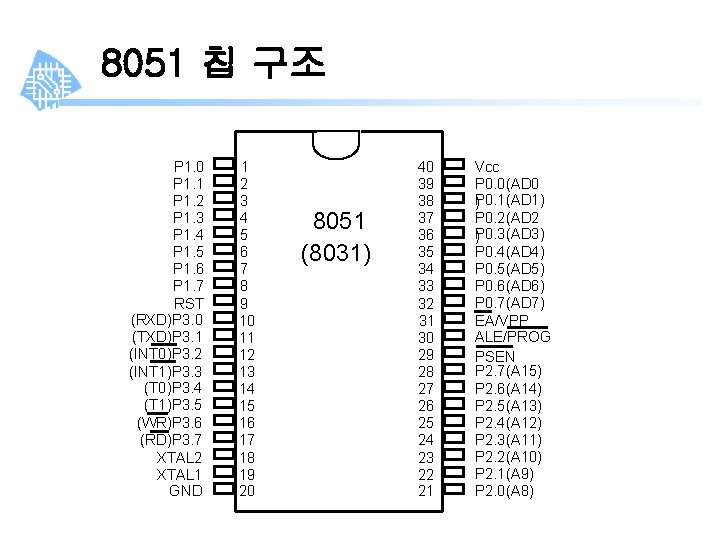

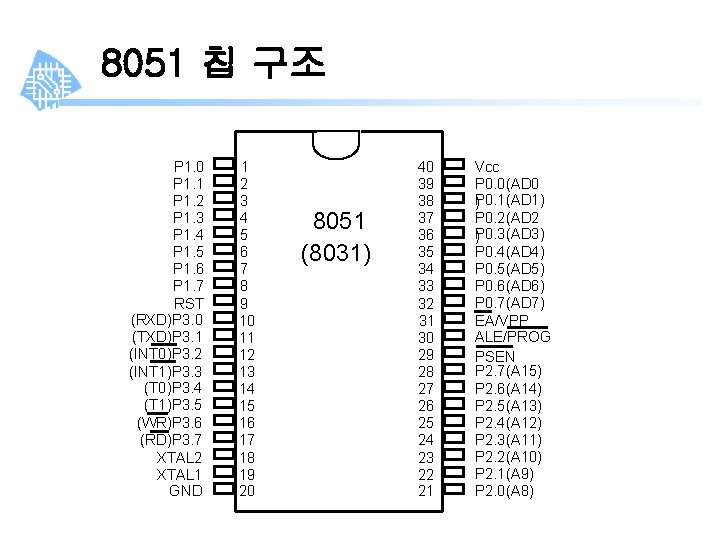

8051 칩 구조 P 1. 0 P 1. 1 P 1. 2 P 1. 3 P 1. 4 P 1. 5 P 1. 6 P 1. 7 RST (RXD)P 3. 0 (TXD)P 3. 1 (INT 0)P 3. 2 (INT 1)P 3. 3 (T 0)P 3. 4 (T 1)P 3. 5 (WR)P 3. 6 (RD)P 3. 7 XTAL 2 XTAL 1 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 8051 (8031) 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 Vcc P 0. 0(AD 0 P ) 0. 1(AD 1) P 0. 2(AD 2 P ) 0. 3(AD 3) P 0. 4(AD 4) P 0. 5(AD 5) P 0. 6(AD 6) P 0. 7(AD 7) EA/VPP ALE/PROG PSEN P 2. 7(A 15) P 2. 6(A 14) P 2. 5(A 13) P 2. 4(A 12) P 2. 3(A 11) P 2. 2(A 10) P 2. 1(A 9) P 2. 0(A 8)

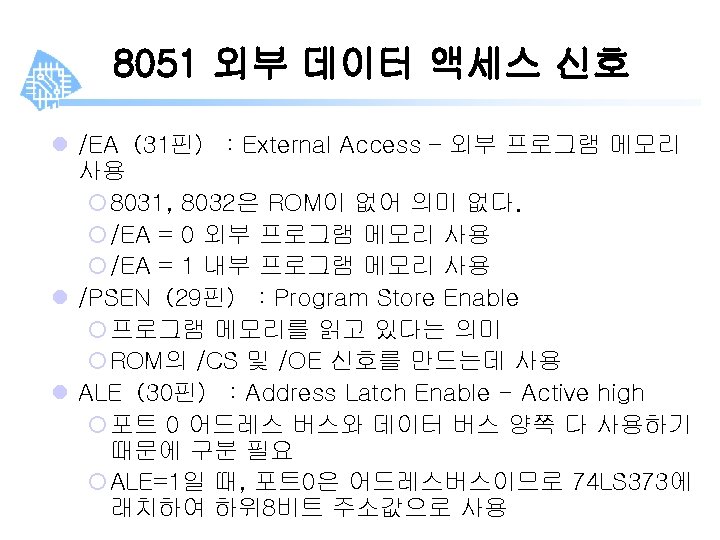

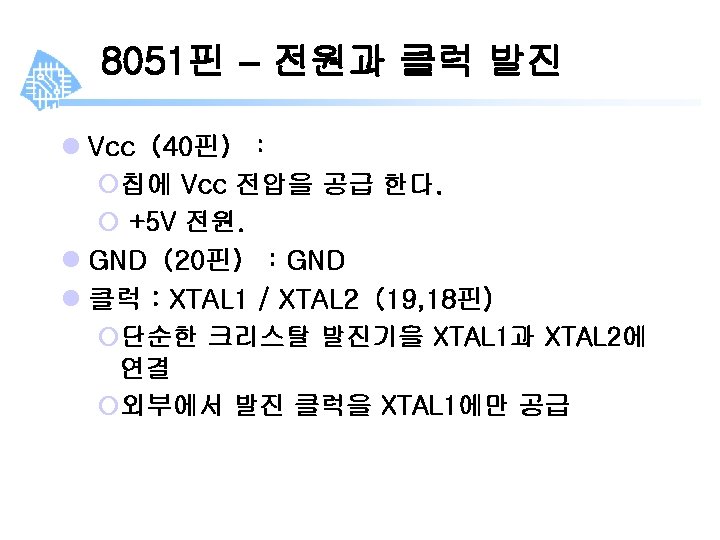

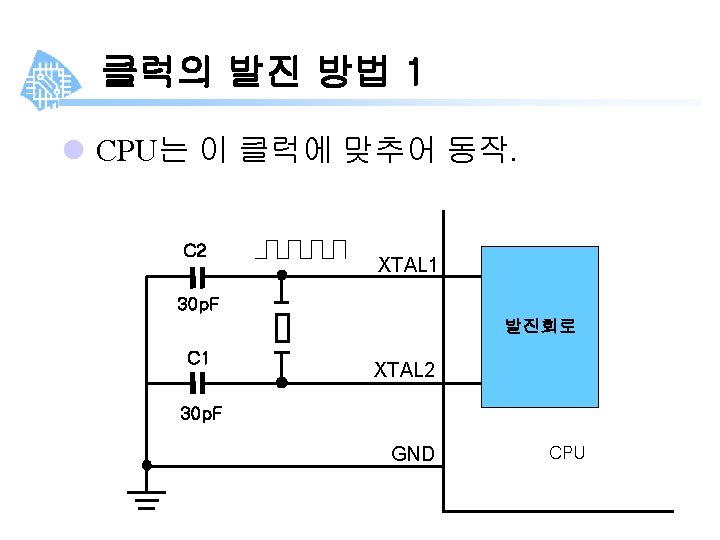

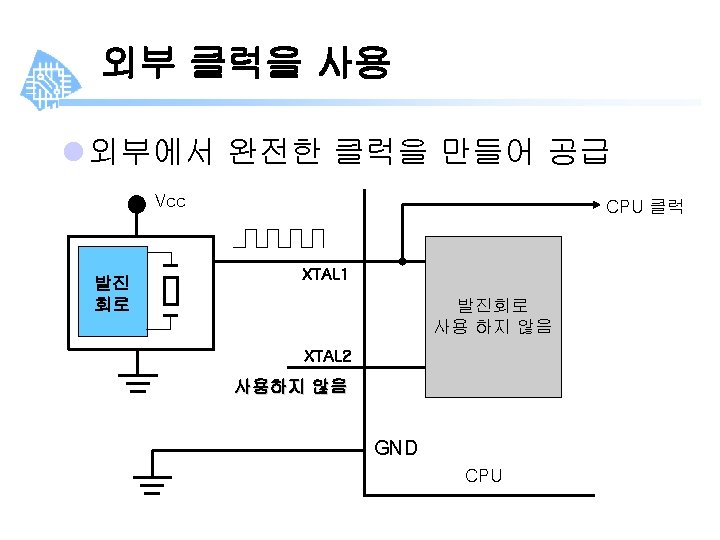

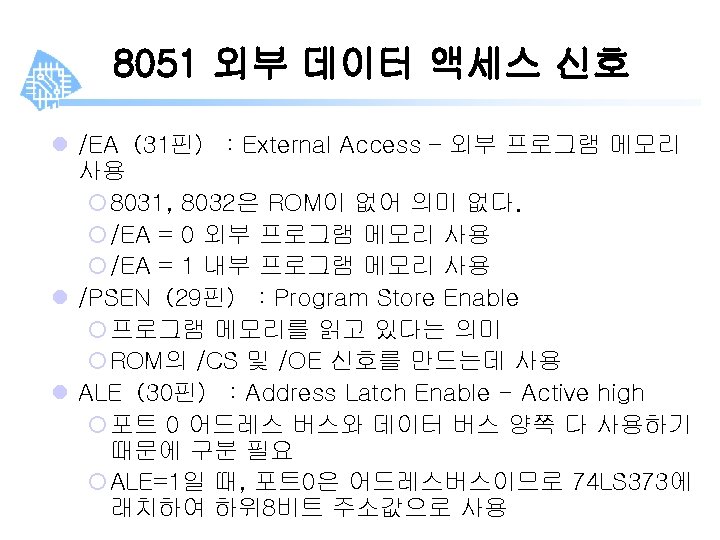

8051의 핀 기능 l 포트의 구조 및 기능 l RESET 리셋 l ALE (Address Latch Enable) l PSEN l EA l XTAL 1, XTAL 2 l 전원 : VCC(+5 V), VSS(GND)

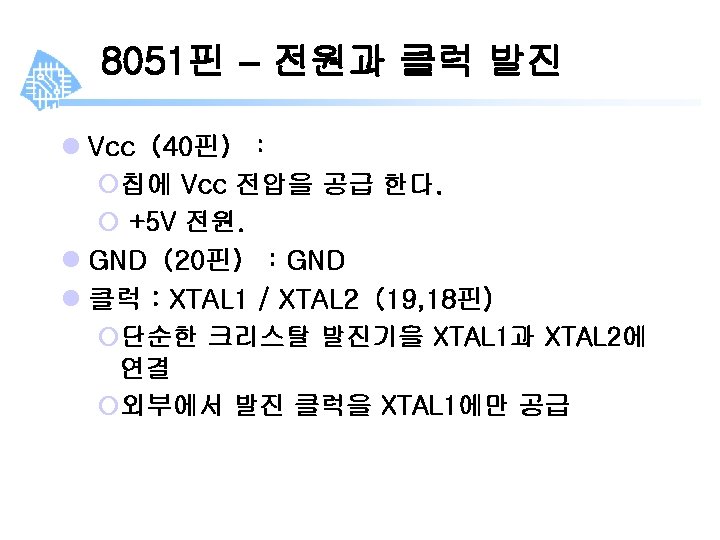

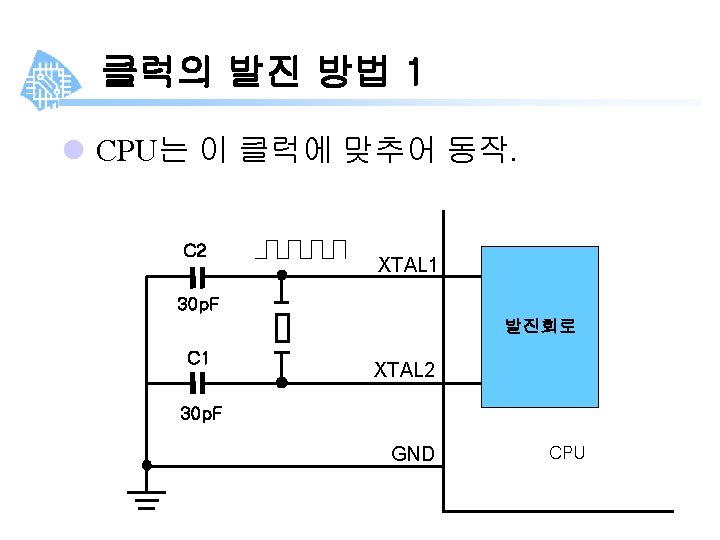

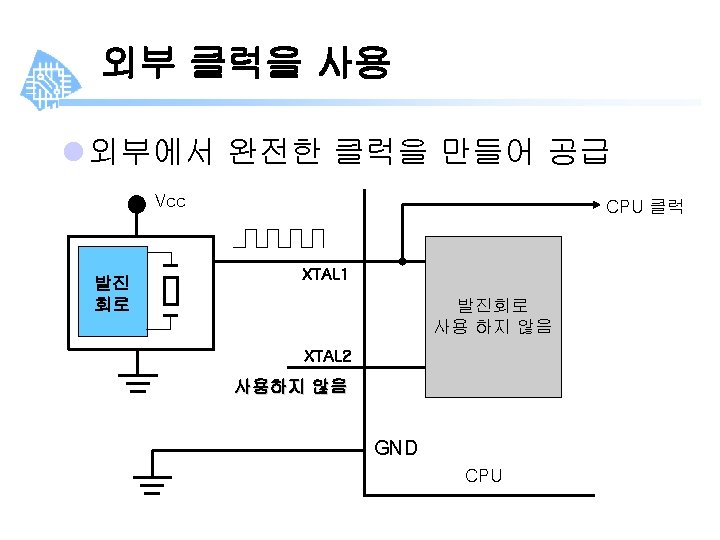

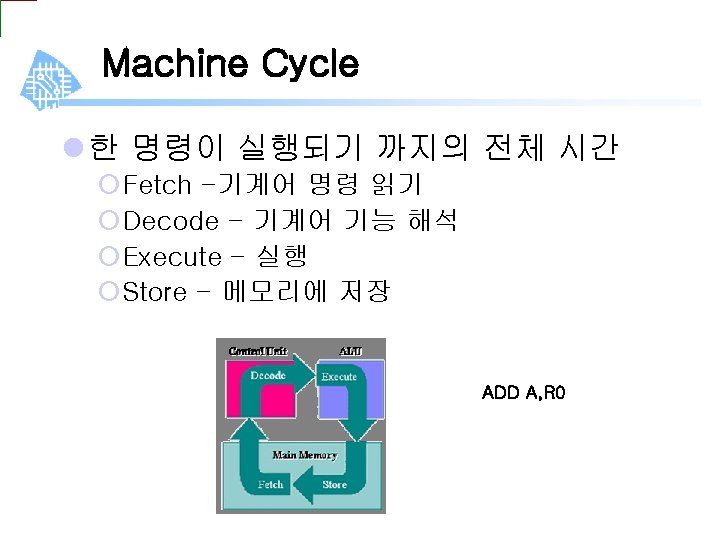

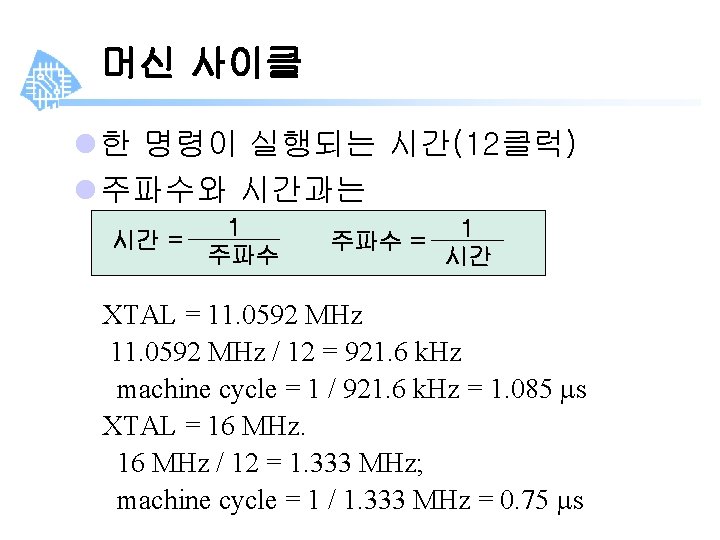

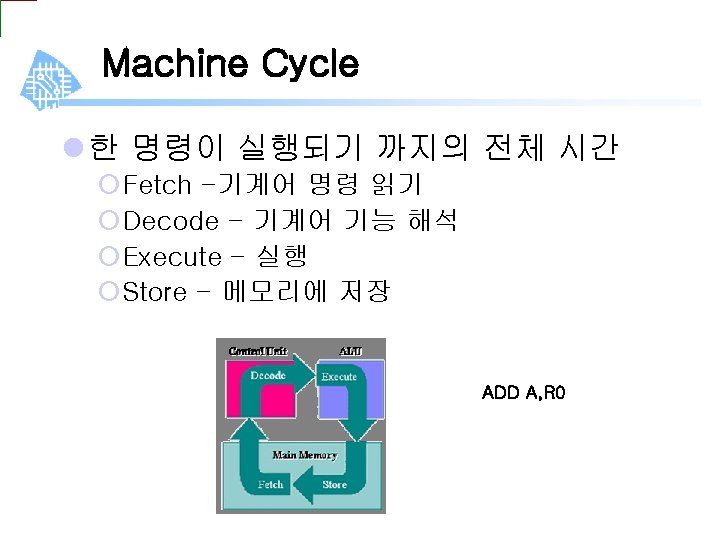

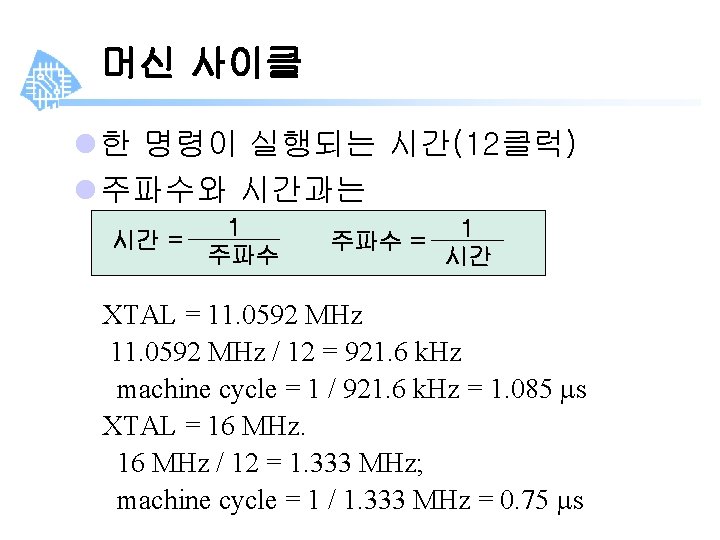

머신 사이클 l 한 명령이 실행되는 시간(12클럭) l 주파수와 시간과는 시간 = 1 주파수 = 1 시간 XTAL = 11. 0592 MHz / 12 = 921. 6 k. Hz machine cycle = 1 / 921. 6 k. Hz = 1. 085 s XTAL = 16 MHz / 12 = 1. 333 MHz; machine cycle = 1 / 1. 333 MHz = 0. 75 s

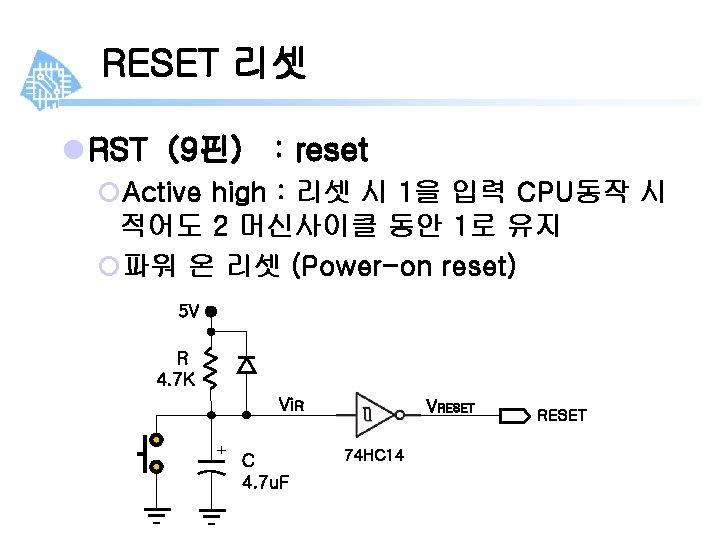

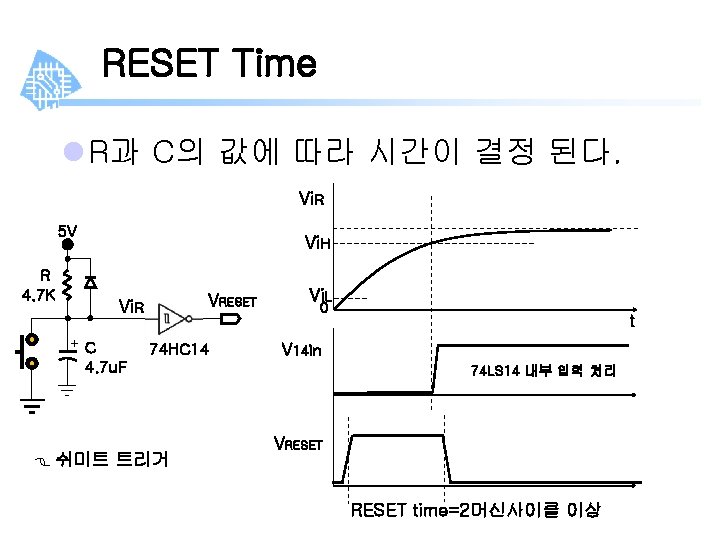

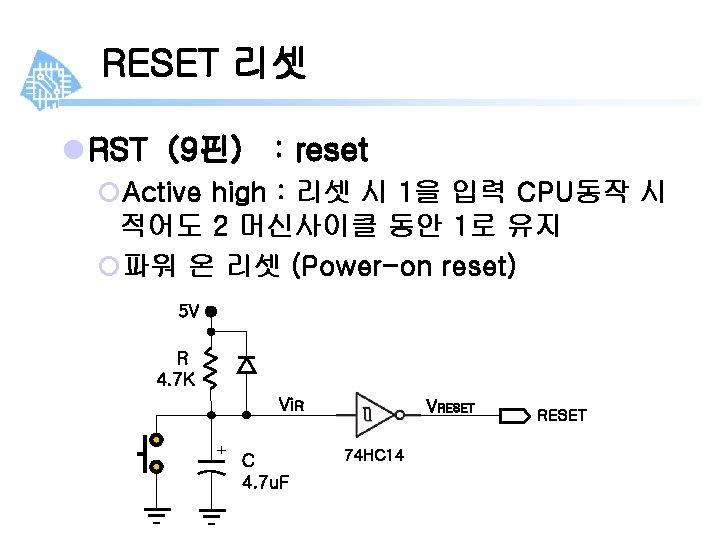

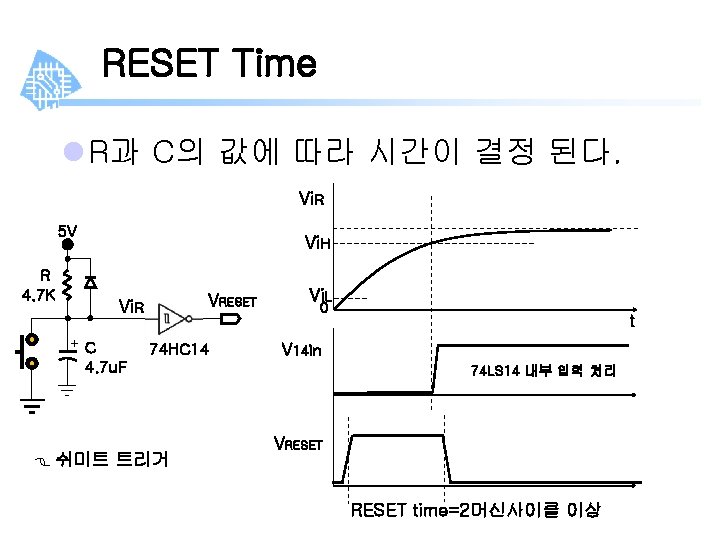

RESET 리셋 l RST(9핀):reset ¡Active high : 리셋 시 1을 입력 CPU동작 시 적어도 2 머신사이클 동안 1로 유지 ¡파워 온 리셋 (Power-on reset) 5 V R 4. 7 K Vi. R C 4. 7 u. F VRESET 74 HC 14 RESET

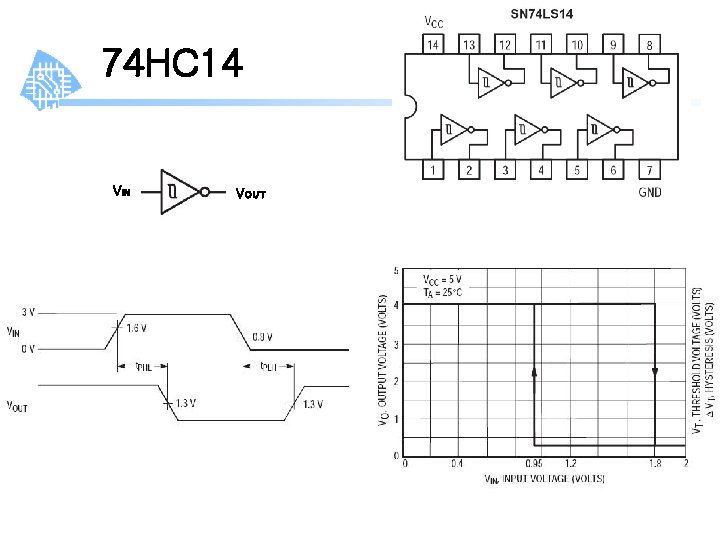

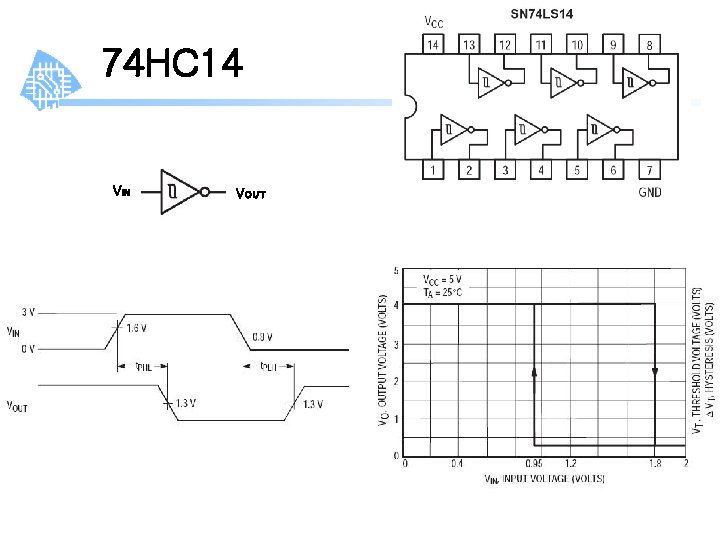

74 HC 14 VIN VOUT

RESET Time l R과 C의 값에 따라 시간이 결정 된다. Vi. R 5 V R 4. 7 K Vi. H VRESET Vi. R C 4. 7 u. F 74 HC 14 쉬미트 트리거 Vi. L 0 t V 14 in 74 LS 14 내부 입력 처리 VRESET time=2머신사이클 이상

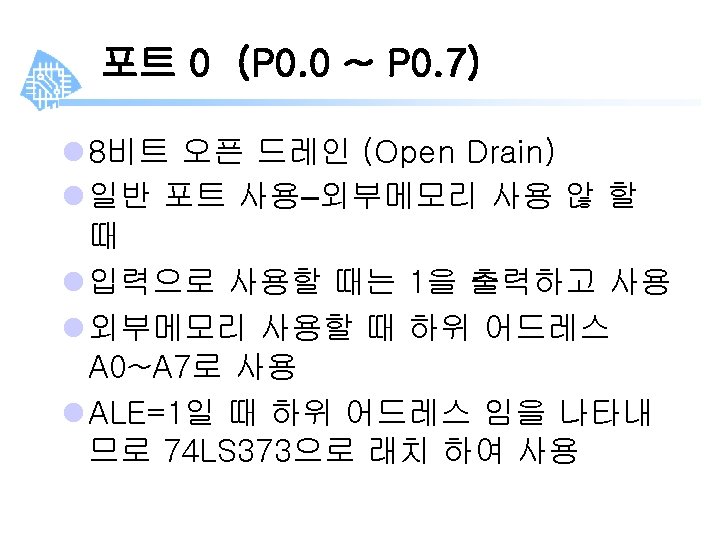

8051의 이해 8051 포트 P 0~P 3

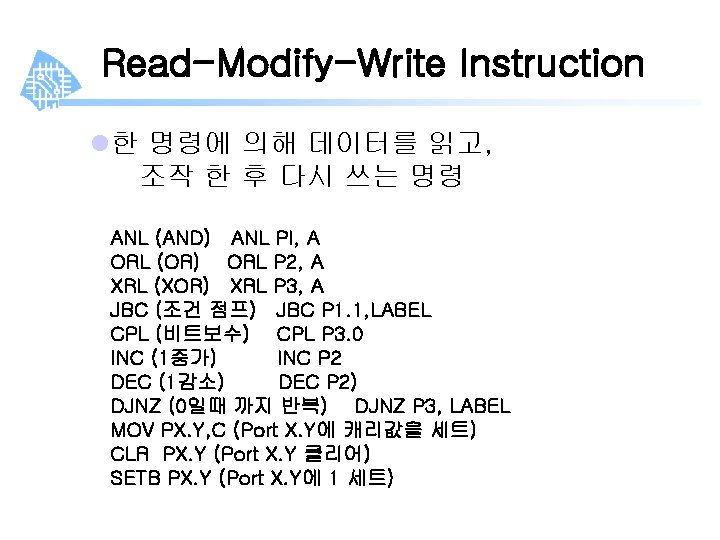

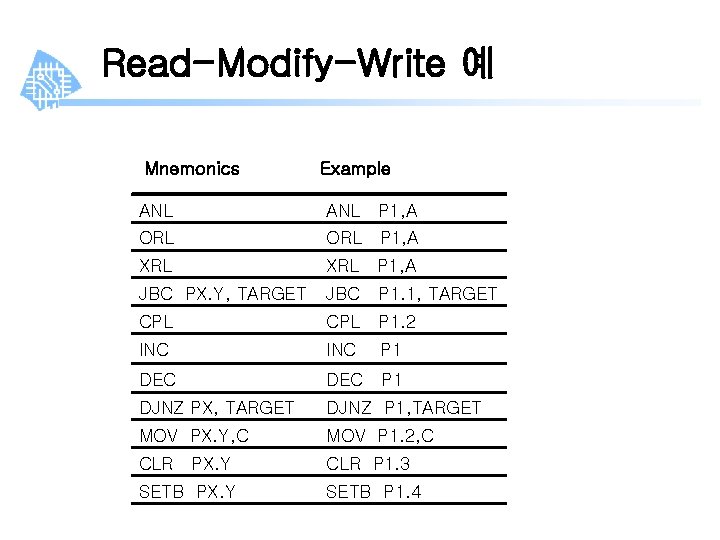

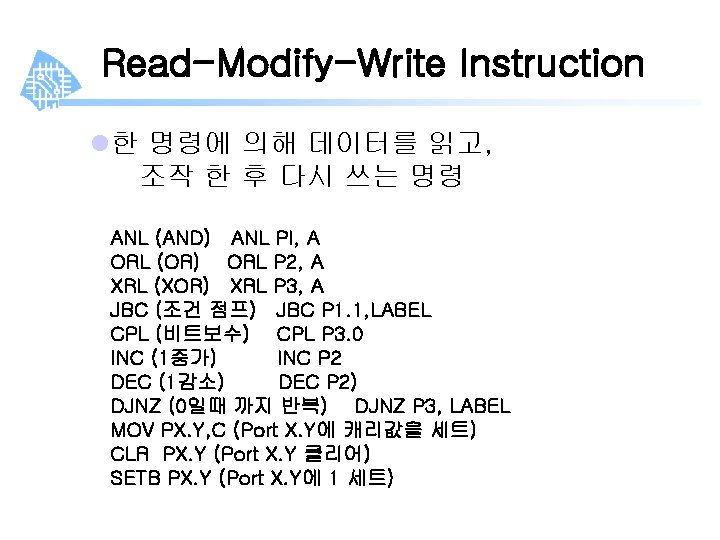

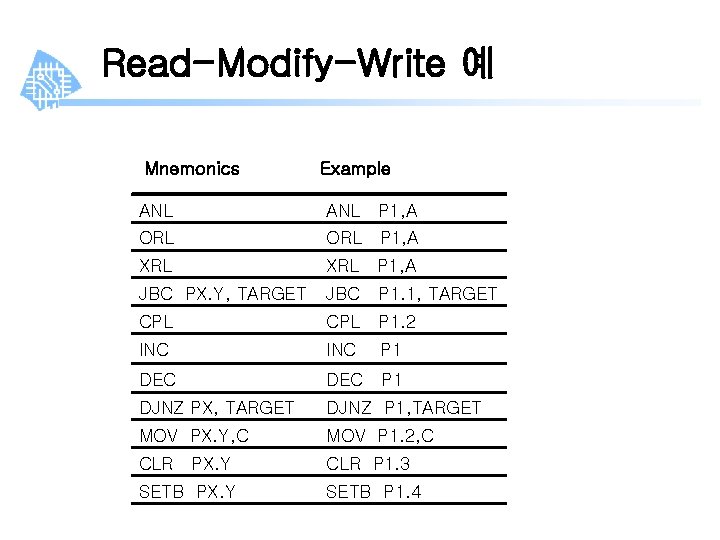

Read-Modify-Write Instruction l한 명령에 의해 데이터를 읽고, 조작 한 후 다시 쓰는 명령 ANL (AND) ANL PI, A ORL (OR) ORL P 2, A XRL (XOR) XRL P 3, A JBC (조건 점프) JBC P 1. 1, LABEL CPL (비트보수) CPL P 3. 0 INC (1증가) INC P 2 DEC (1감소) DEC P 2) DJNZ (0일때 까지 반복) DJNZ P 3, LABEL MOV PX. Y, C (Port X. Y에 캐리값을 세트) CLR PX. Y (Port X. Y 클리어) SETB PX. Y (Port X. Y에 1 세트)

Read-Modify-Write 예 Mnemonics Example ANL P 1, A ORL P 1, A XRL P 1, A JBC PX. Y, TARGET JBC P 1. 1, TARGET CPL P 1. 2 INC DEC P 1 DJNZ PX, TARGET DJNZ P 1, TARGET MOV PX. Y, C MOV P 1. 2, C CLR PX. Y CLR P 1. 3 SETB PX. Y SETB P 1. 4 P 1

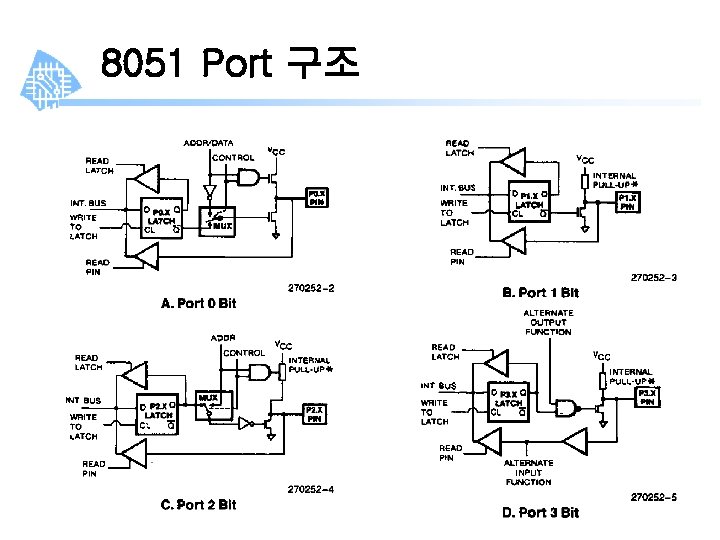

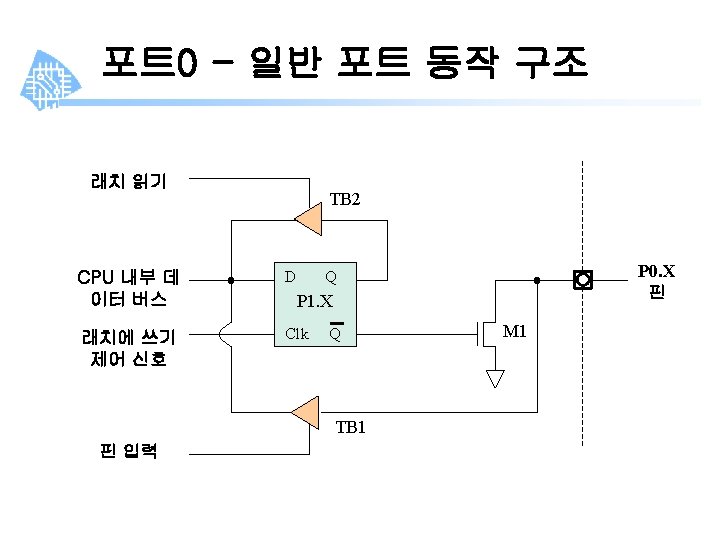

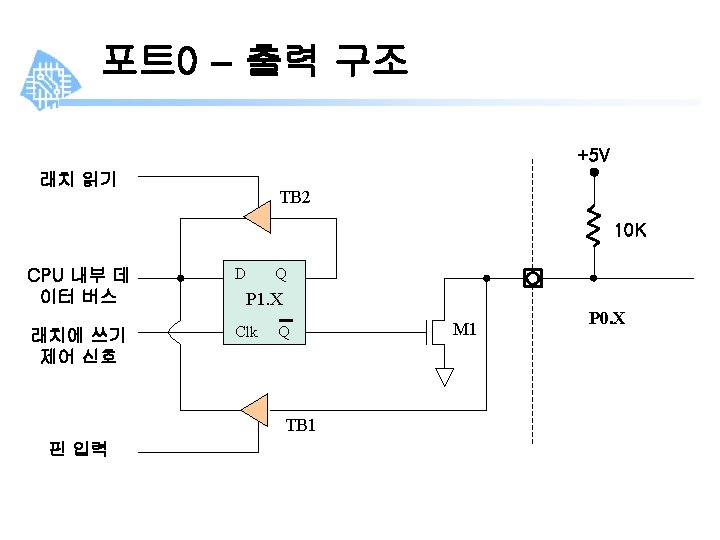

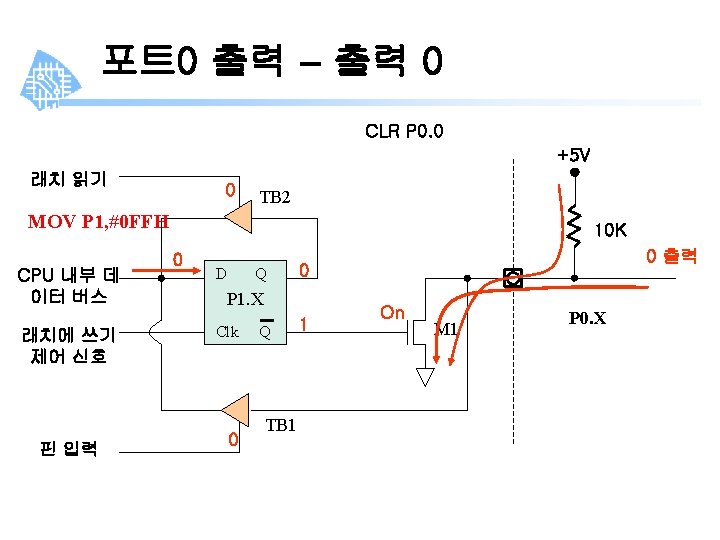

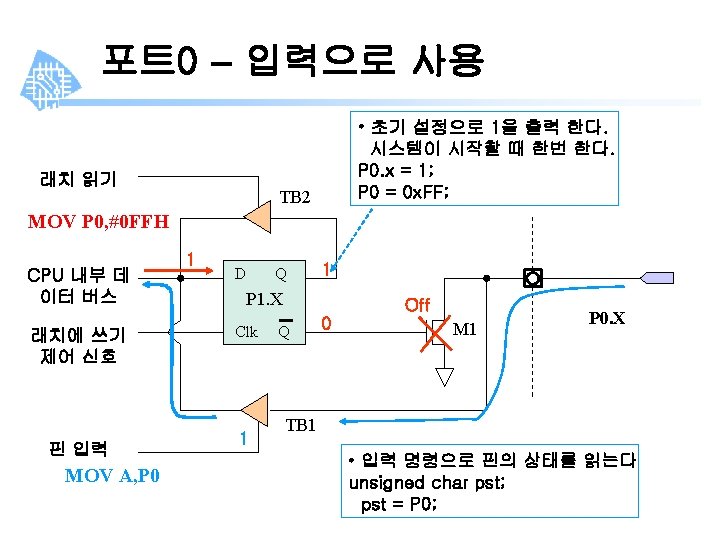

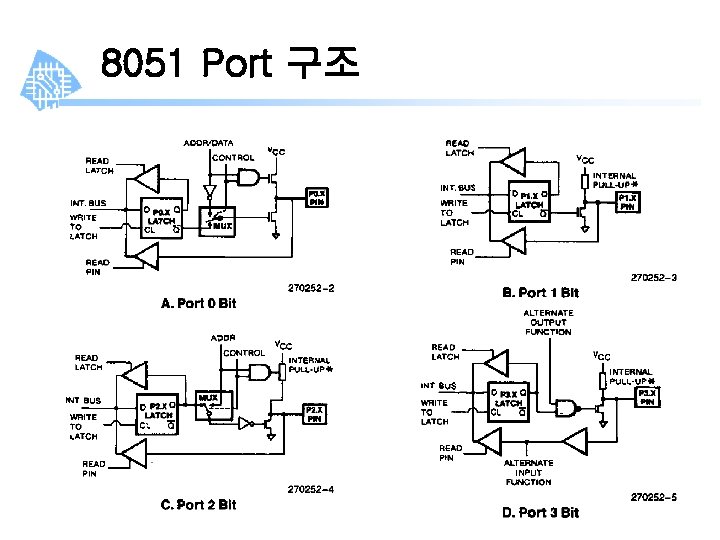

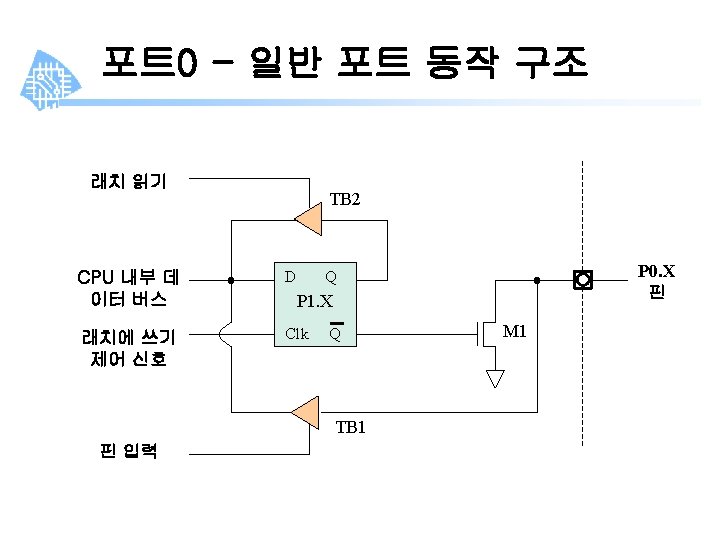

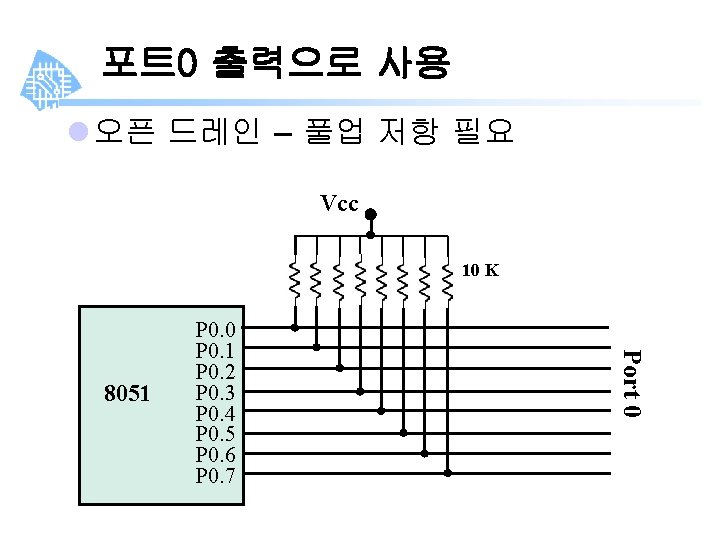

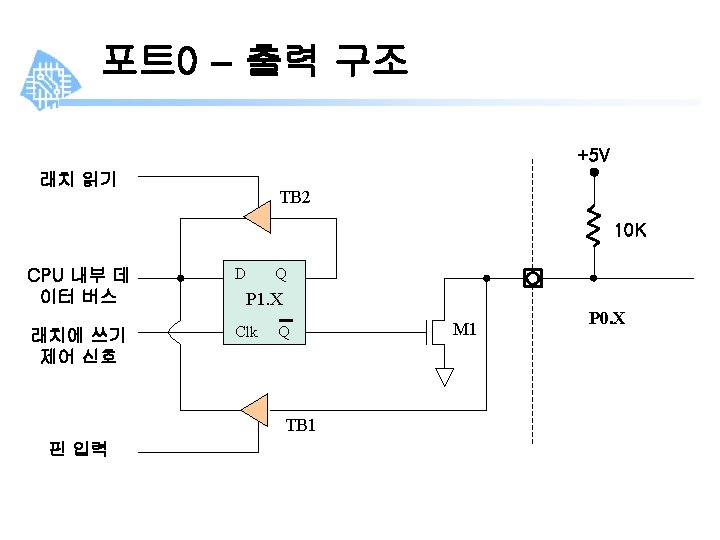

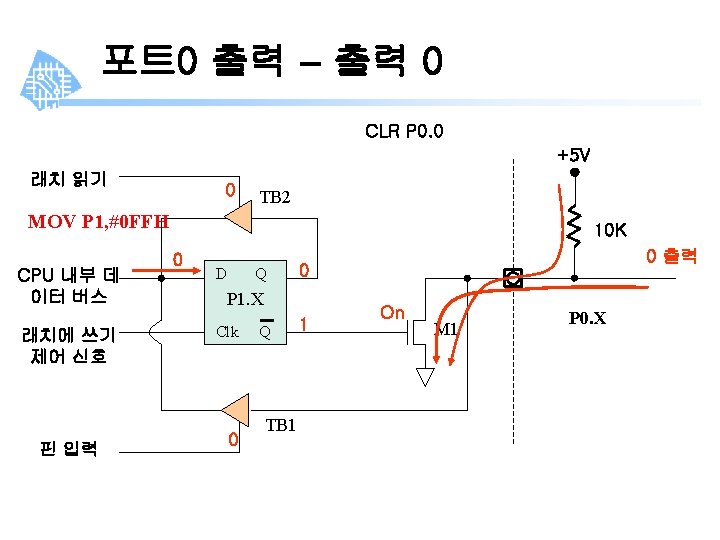

8051 Port 구조

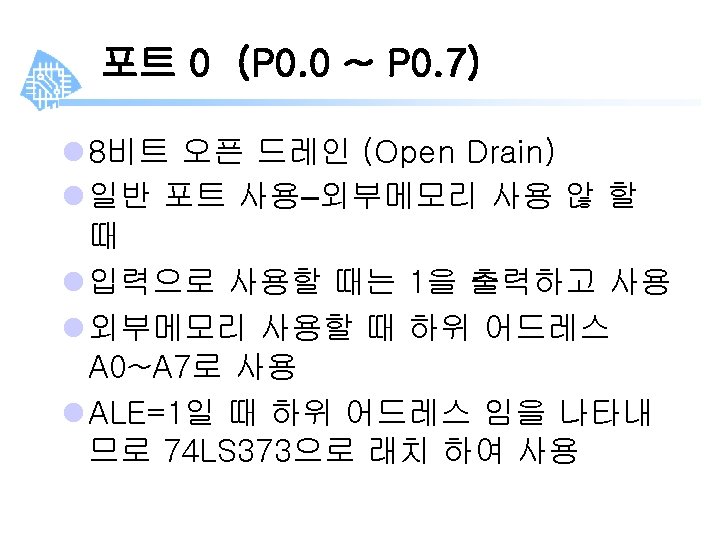

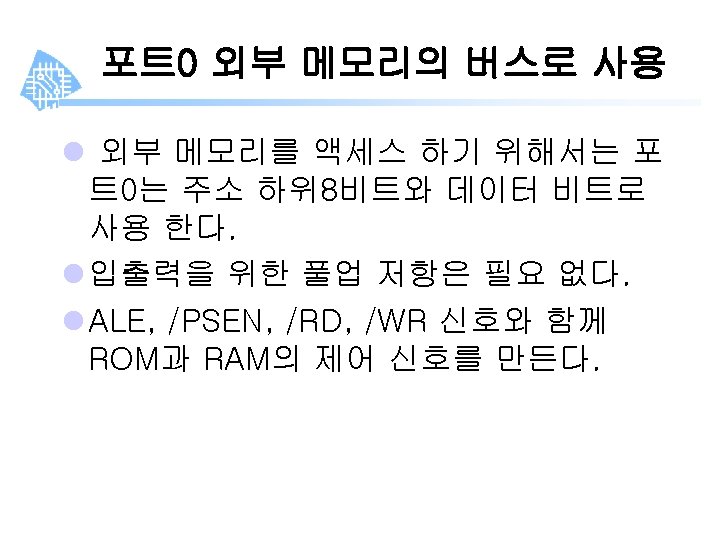

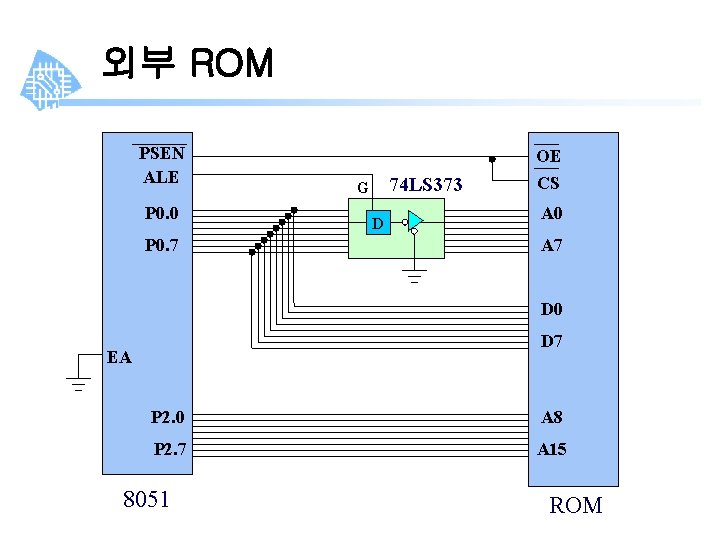

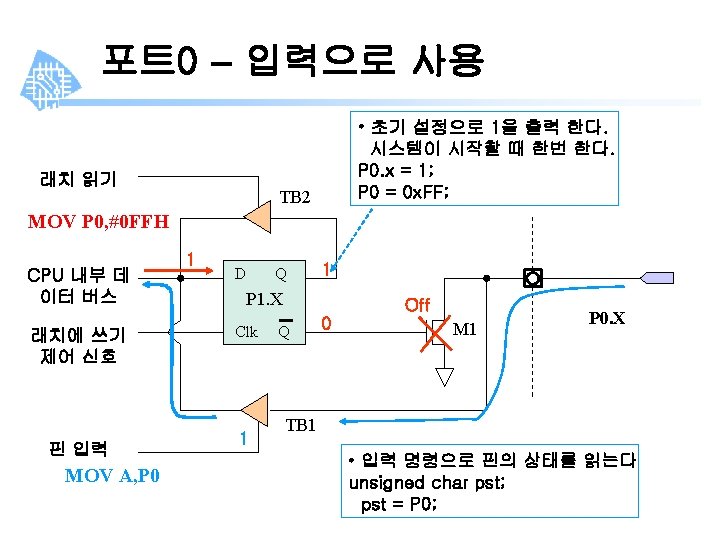

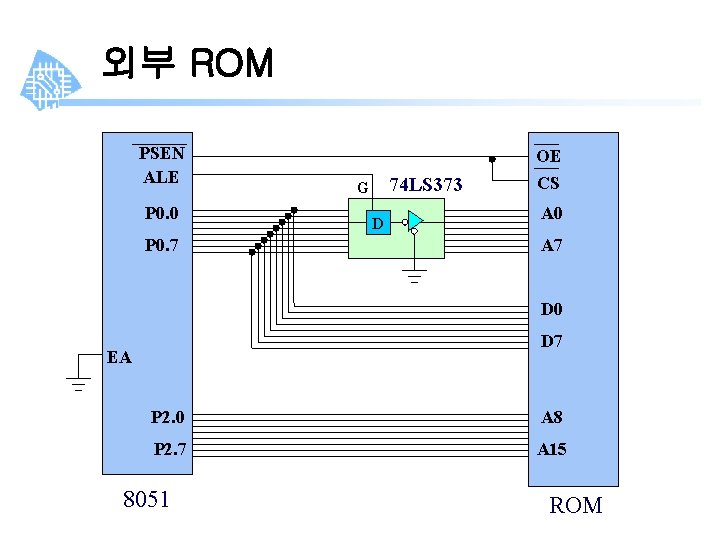

외부 ROM PSEN ALE P 0. 0 P 0. 7 74 LS 373 G D OE CS A 0 A 7 D 0 D 7 EA P 2. 0 A 8 P 2. 7 A 15 8051 ROM

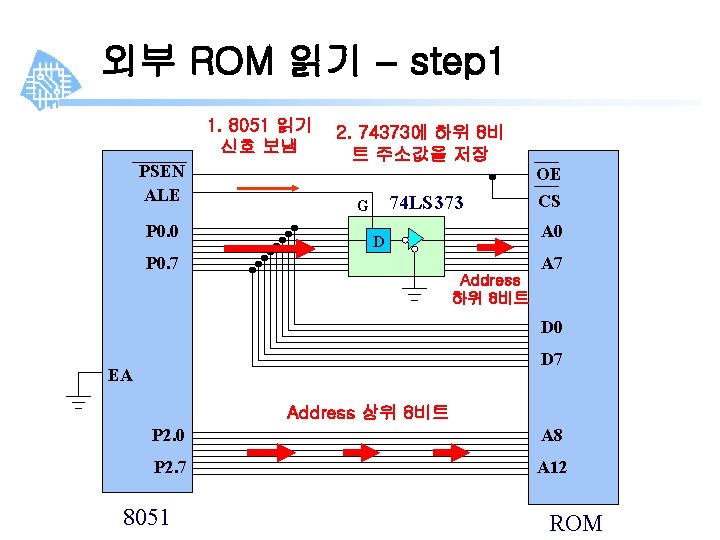

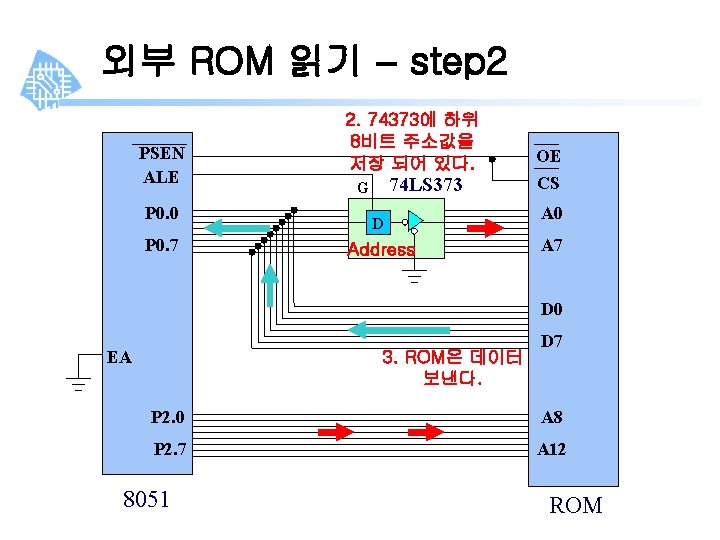

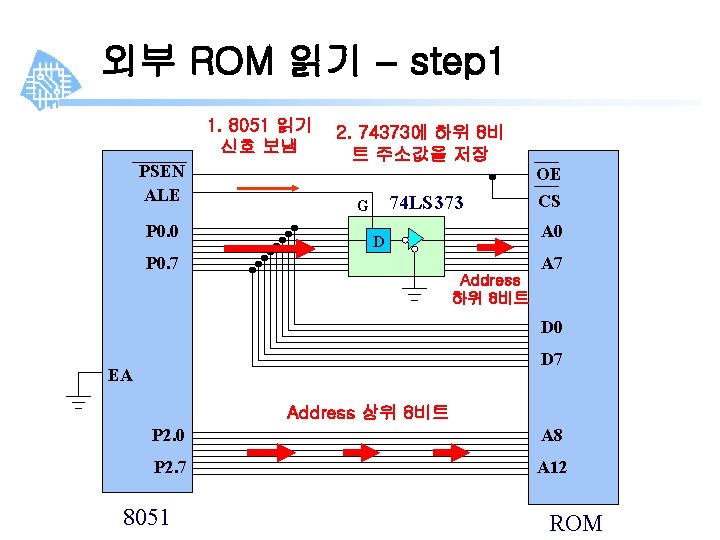

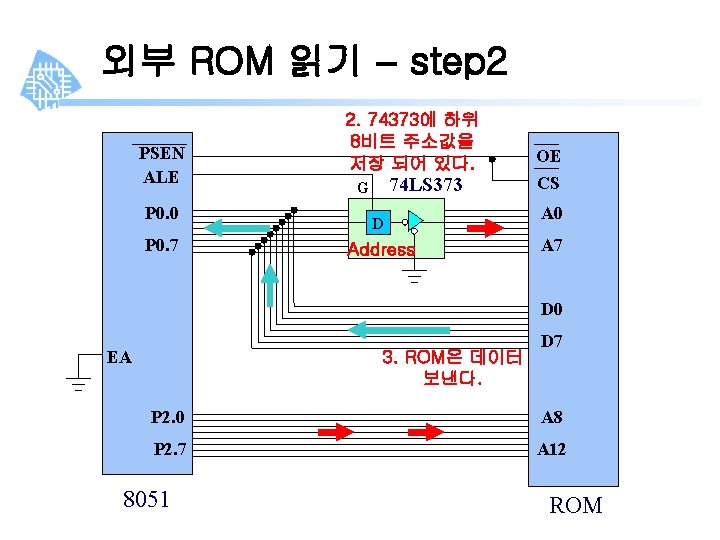

외부 ROM 읽기 – step 1 1. 8051 읽기 신호 보냄 PSEN ALE P 0. 0 2. 74373에 하위 8비 트 주소값을 저장 74 LS 373 G A 0 D P 0. 7 OE CS Address 하위 8비트 A 7 D 0 D 7 EA Address 상위 8비트 P 2. 0 A 8 P 2. 7 A 12 8051 ROM

외부 ROM 읽기 – step 2 PSEN ALE P 0. 0 P 0. 7 2. 74373에 하위 8비트 주소값을 저장 되어 있다. 74 LS 373 G D Address OE CS A 0 A 7 D 0 EA 3. ROM은 데이터 보낸다. D 7 P 2. 0 A 8 P 2. 7 A 12 8051 ROM

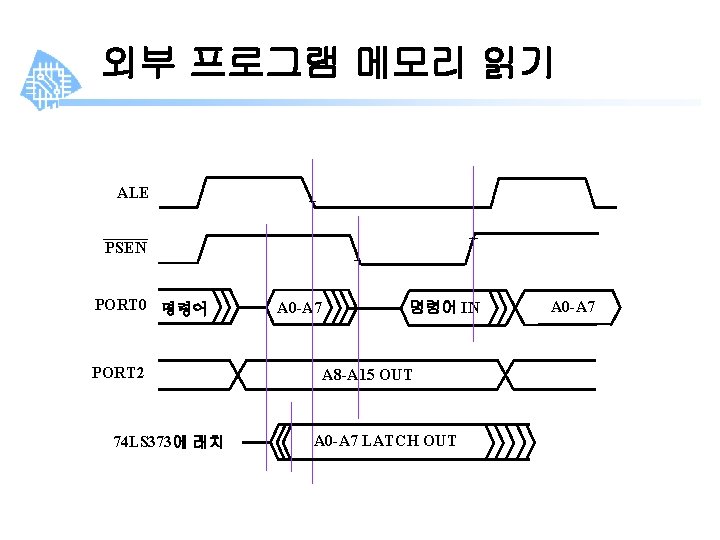

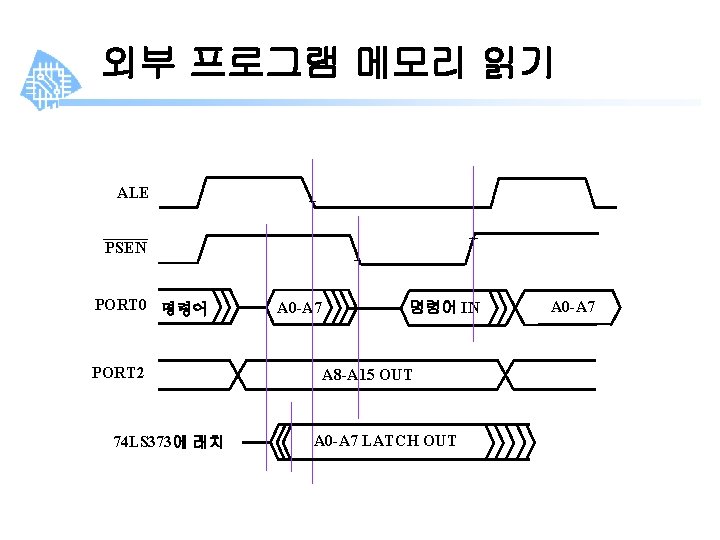

외부 프로그램 메모리 읽기 ALE PSEN PORT 0 명령어 PORT 2 74 LS 373에 래치 A 0 -A 7 명령어 IN A 8 -A 15 OUT A 0 -A 7 LATCH OUT A 0 -A 7

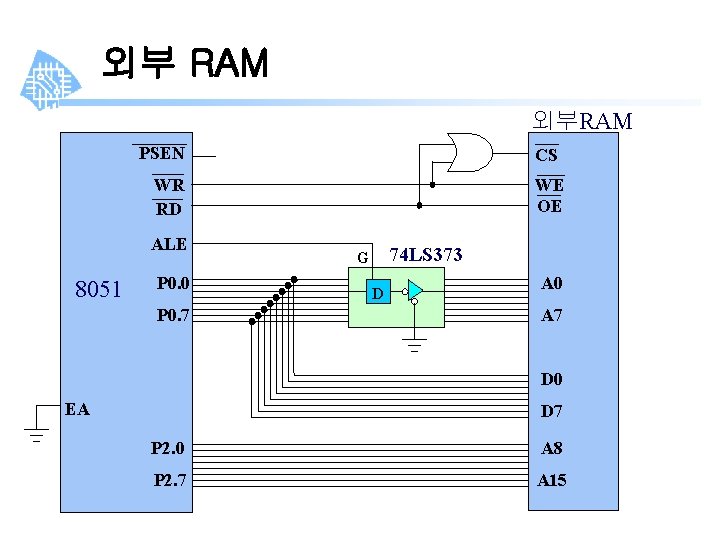

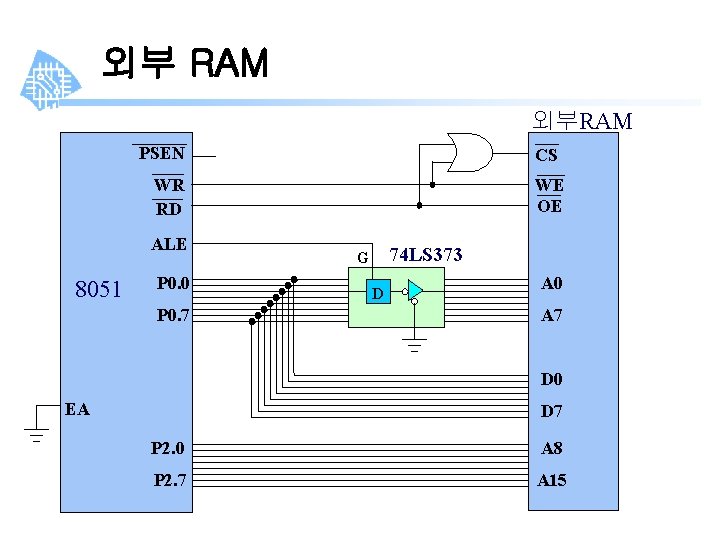

외부 RAM 외부RAM PSEN CS WR RD ALE 8051 P 0. 0 P 0. 7 WE OE 74 LS 373 G D A 0 A 7 D 0 EA D 7 P 2. 0 A 8 P 2. 7 A 15

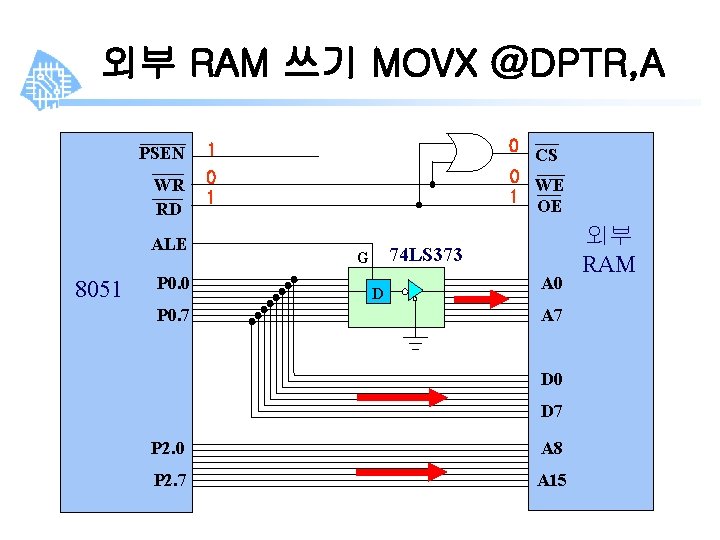

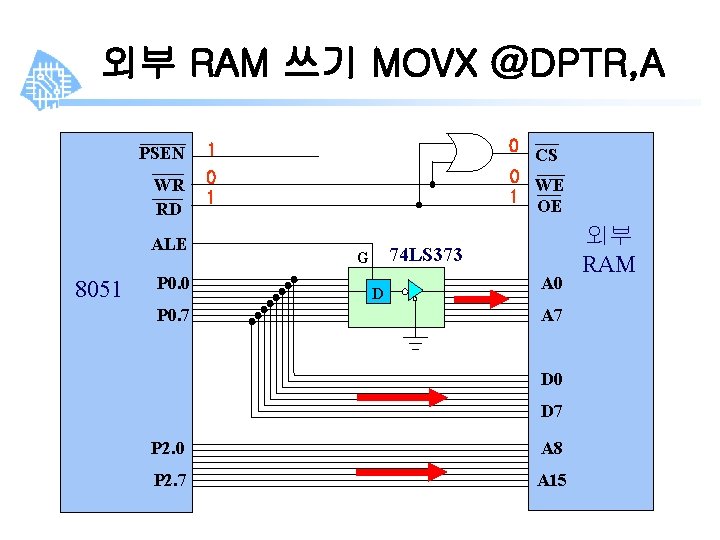

외부 RAM 쓰기 MOVX @DPTR, A PSEN 1 0 WR RD 0 1 0 WE 1 OE ALE 8051 P 0. 0 P 0. 7 CS 74 LS 373 G D A 0 A 7 D 0 D 7 P 2. 0 A 8 P 2. 7 A 15 외부 RAM

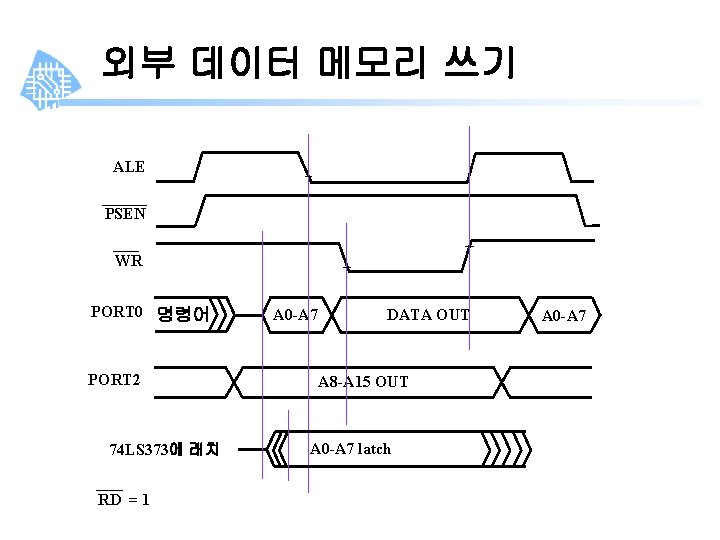

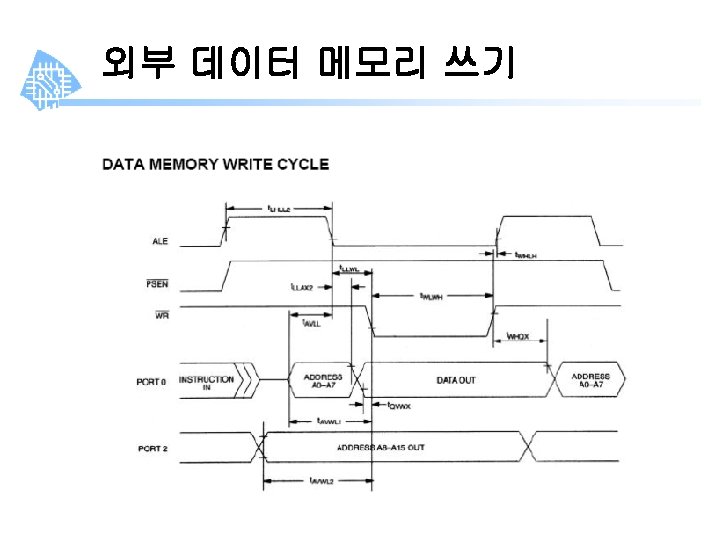

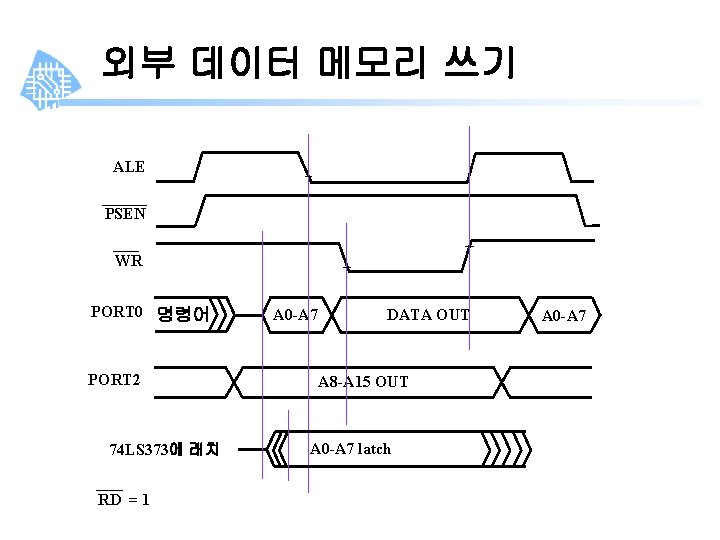

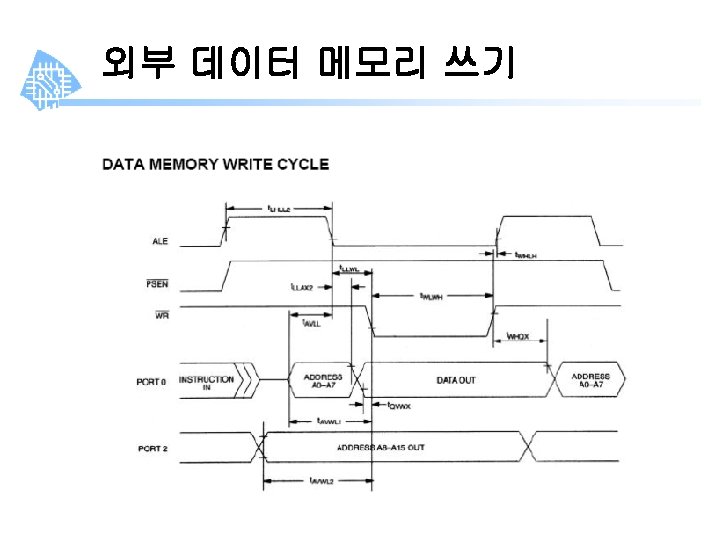

외부 데이터 메모리 쓰기 ALE PSEN WR PORT 0 명령어 PORT 2 74 LS 373에 래치 RD = 1 A 0 -A 7 DATA OUT A 8 -A 15 OUT A 0 -A 7 latch A 0 -A 7

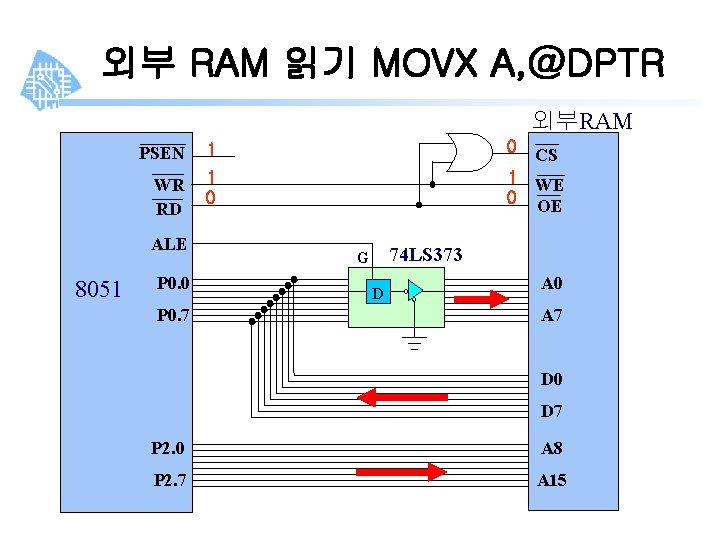

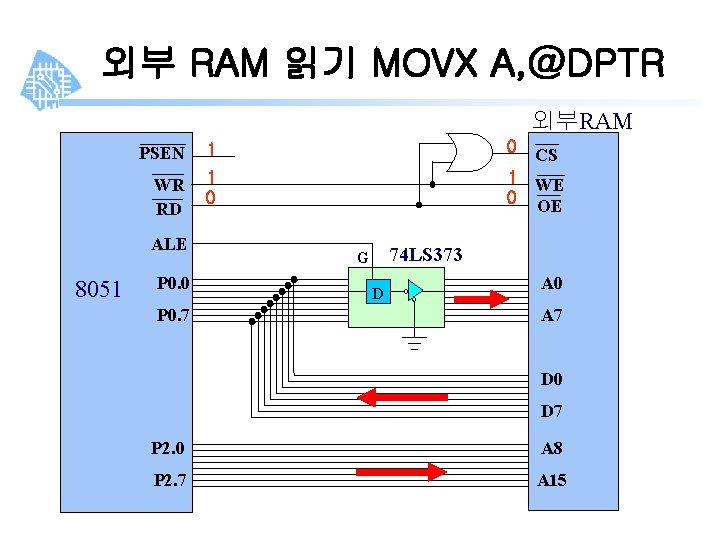

외부 RAM 읽기 MOVX A, @DPTR 외부RAM PSEN 1 0 WR RD 1 0 1 WE 0 OE ALE 8051 P 0. 0 P 0. 7 CS 74 LS 373 G D A 0 A 7 D 0 D 7 P 2. 0 A 8 P 2. 7 A 15

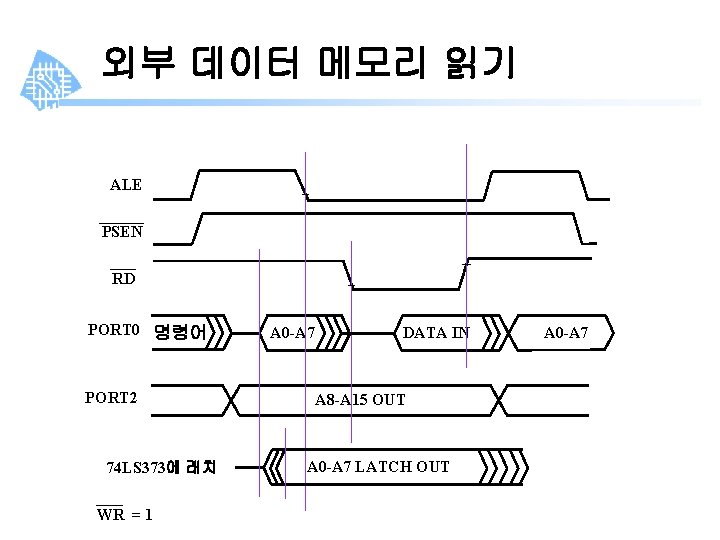

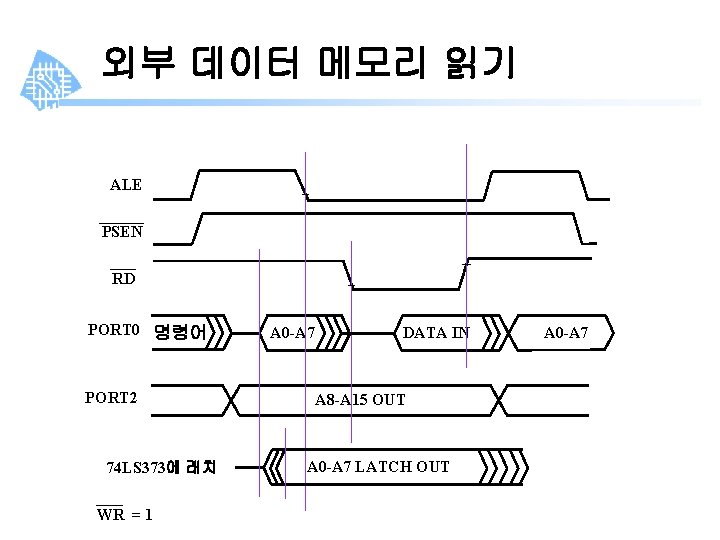

외부 데이터 메모리 읽기 ALE PSEN RD PORT 0 명령어 PORT 2 74 LS 373에 래치 WR = 1 A 0 -A 7 DATA IN A 8 -A 15 OUT A 0 -A 7 LATCH OUT A 0 -A 7

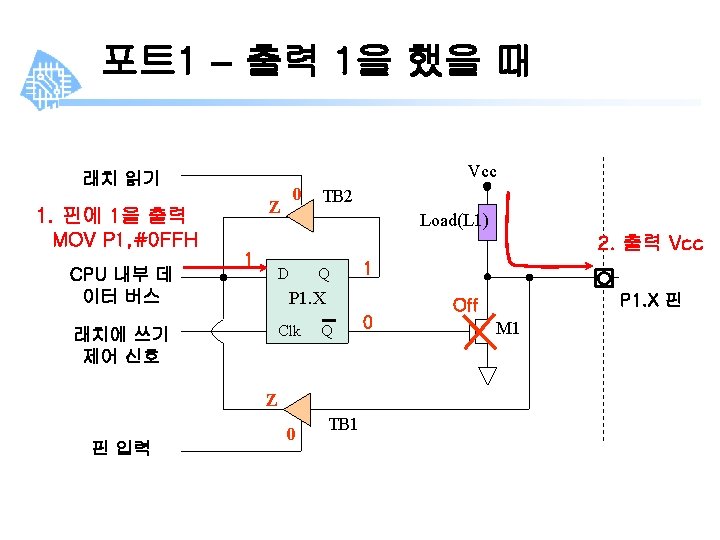

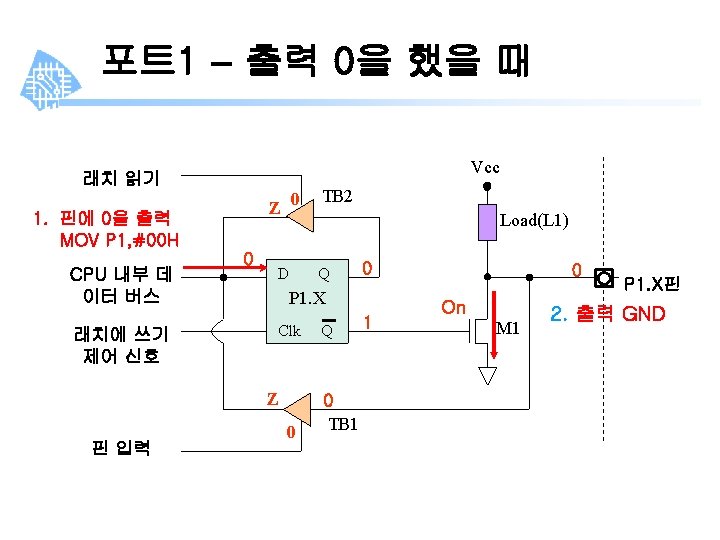

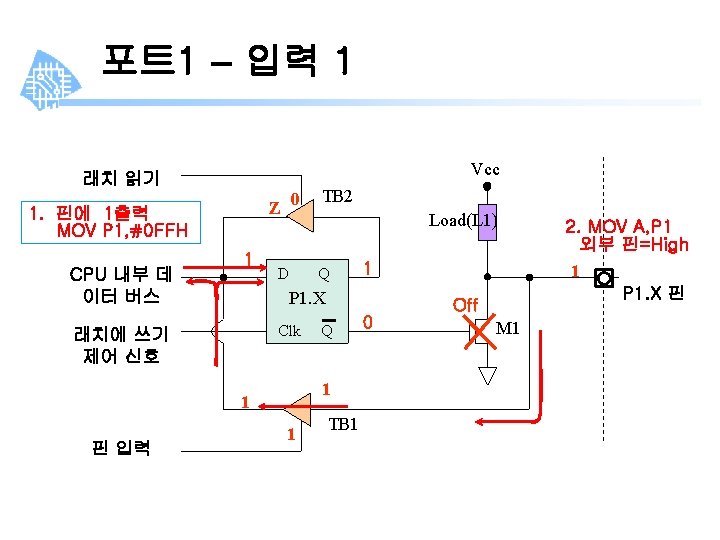

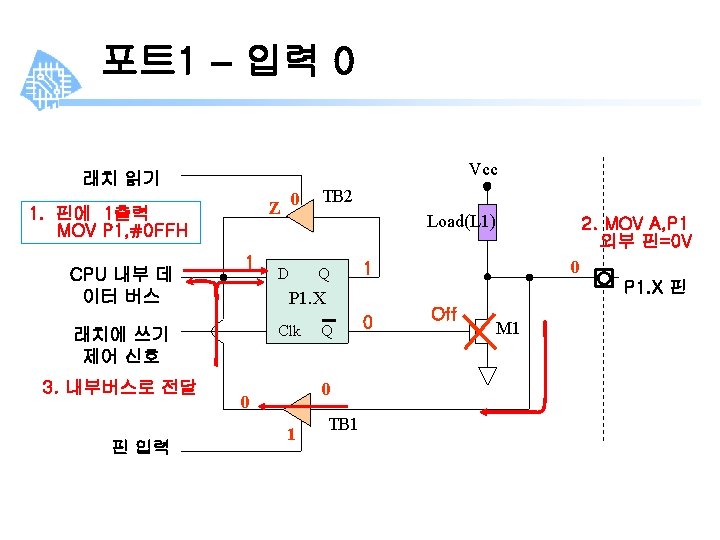

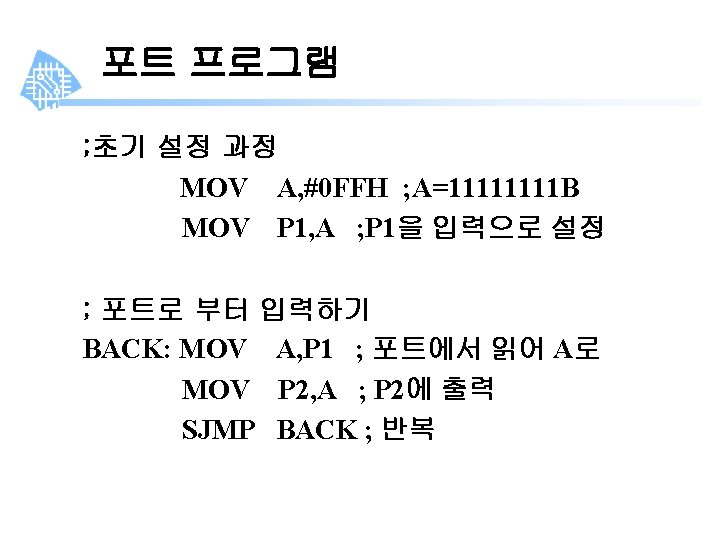

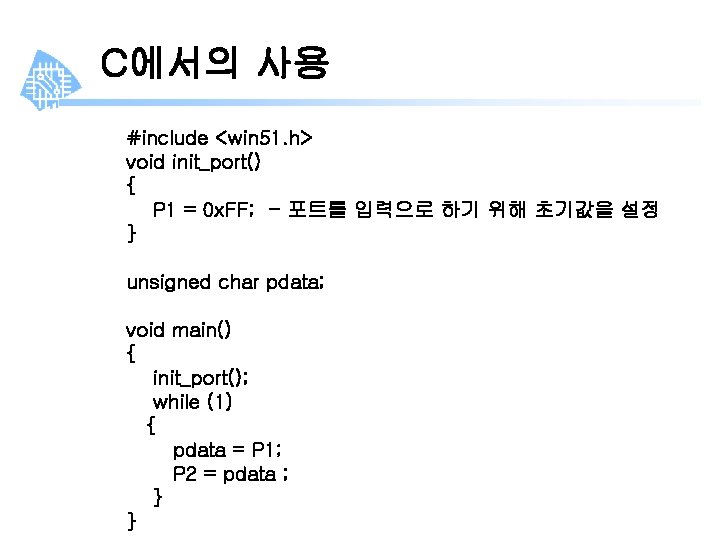

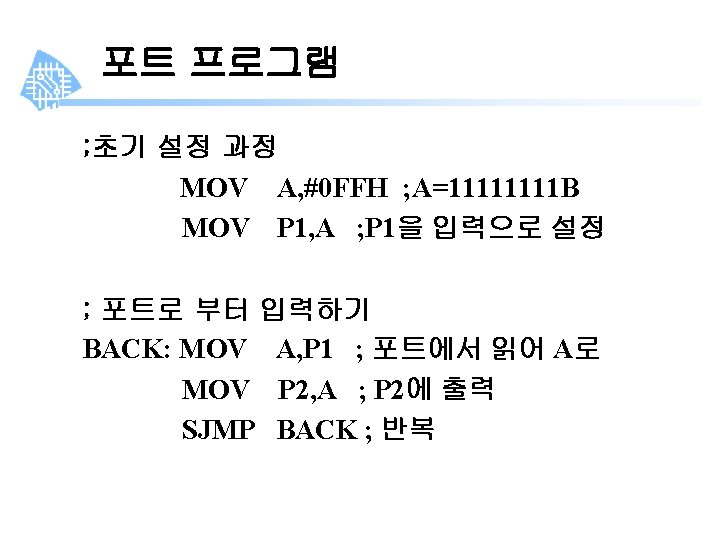

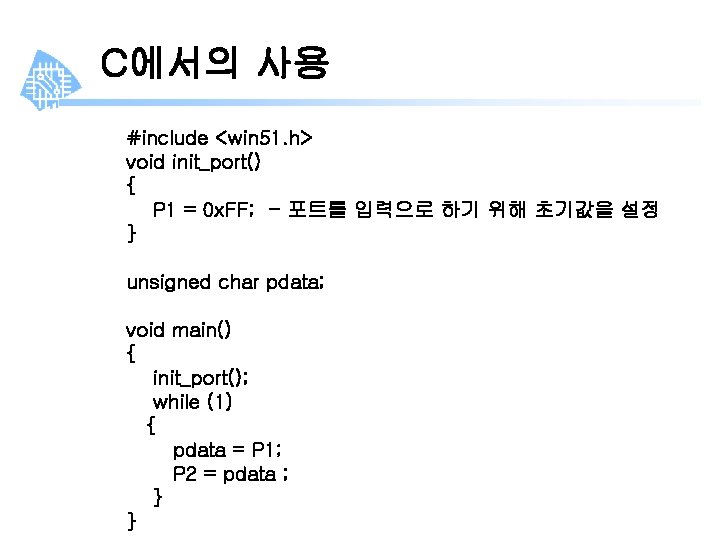

C에서의 사용 #include <win 51. h> void init_port() { P 1 = 0 x. FF; - 포트를 입력으로 하기 위해 초기값을 설정 } unsigned char pdata; void main() { init_port(); while (1) { pdata = P 1; P 2 = pdata ; } }

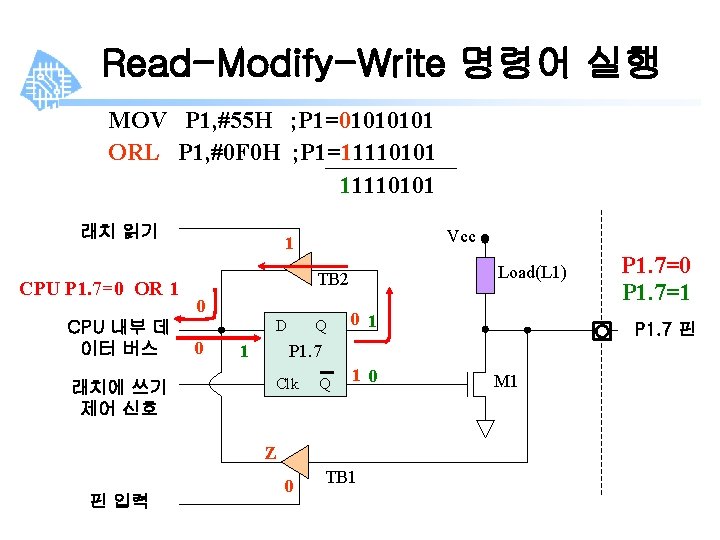

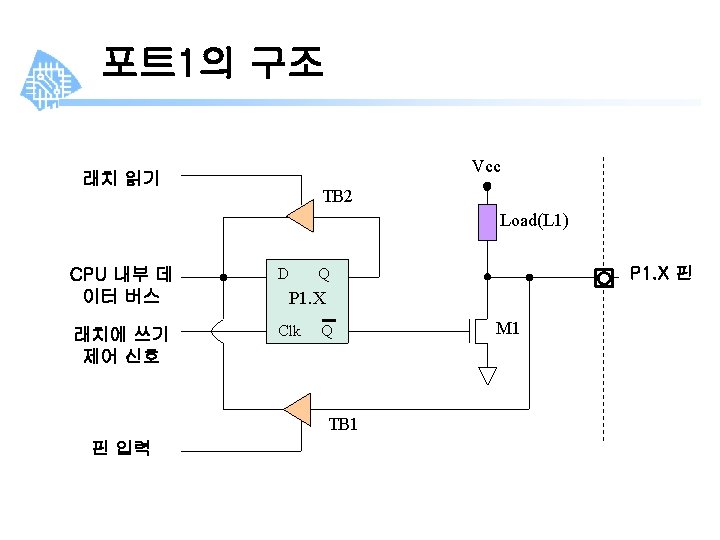

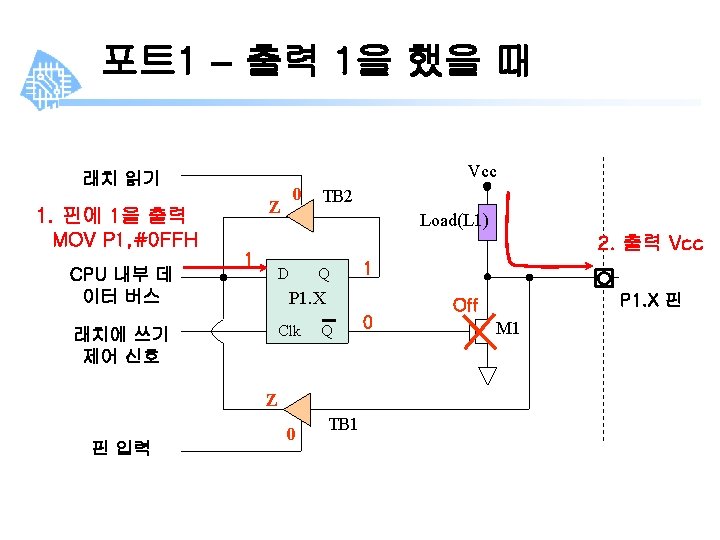

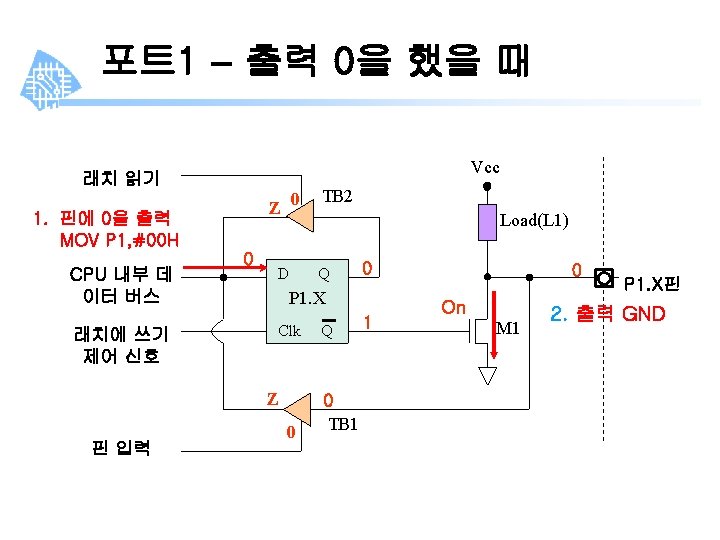

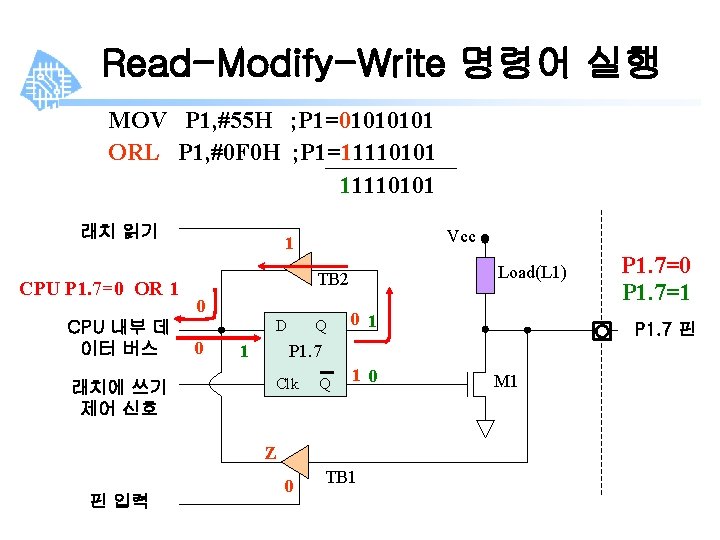

Read-Modify-Write 명령어 실행 MOV P 1, #55 H ; P 1=0101 ORL P 1, #0 F 0 H ; P 1=11110101 래치 읽기 CPU P 1. 7=0 OR 1 CPU 내부 데 이터 버스 래치에 쓰기 제어 신호 Vcc 1 Load(L 1) TB 2 0 D 0 Q 0 1 Clk Q 1 0 Z 핀 입력 P 1. 7 핀 P 1. 7 1 0 TB 1 P 1. 7=0 P 1. 7=1 M 1

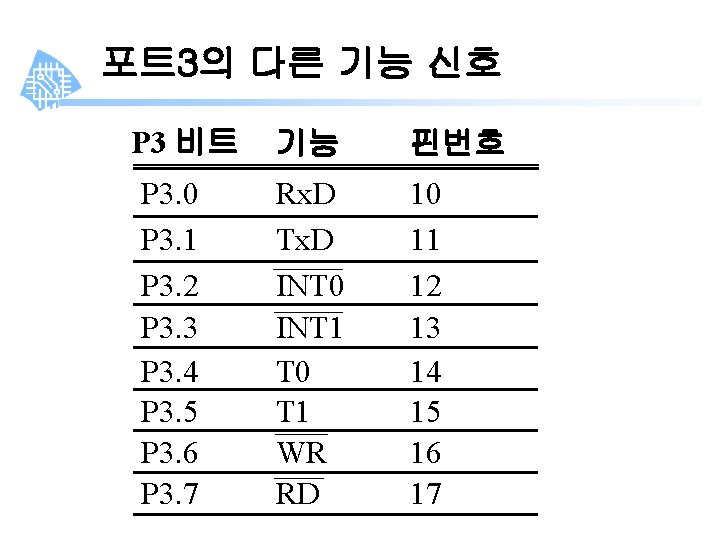

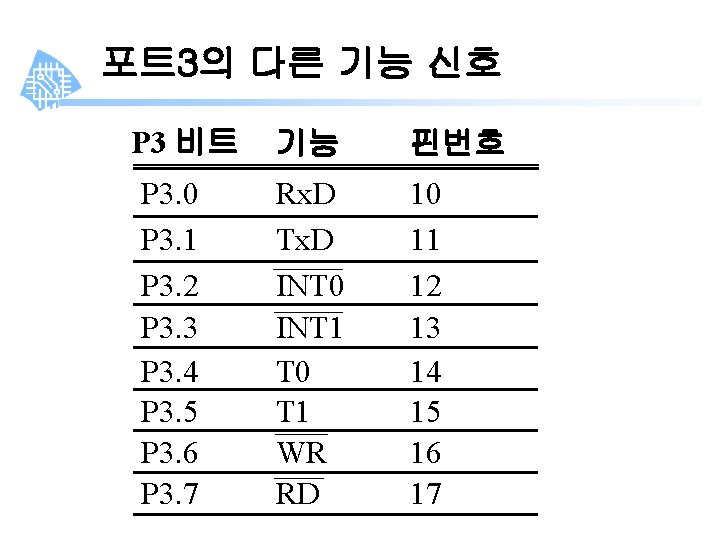

포트 3의 다른 기능 신호 P 3 비트 P 3. 0 P 3. 1 P 3. 2 P 3. 3 P 3. 4 P 3. 5 P 3. 6 P 3. 7 기능 핀번호 Rx. D Tx. D INT 0 INT 1 T 0 T 1 WR RD 10 11 12 13 14 15 16 17