l l dolicomnaver com http blog naver comdolicom

디지털 회로 l 디지털 논리의 표현 l 디지털 회로 구현 dolicom@naver. com http: //blog. naver. com/dolicom

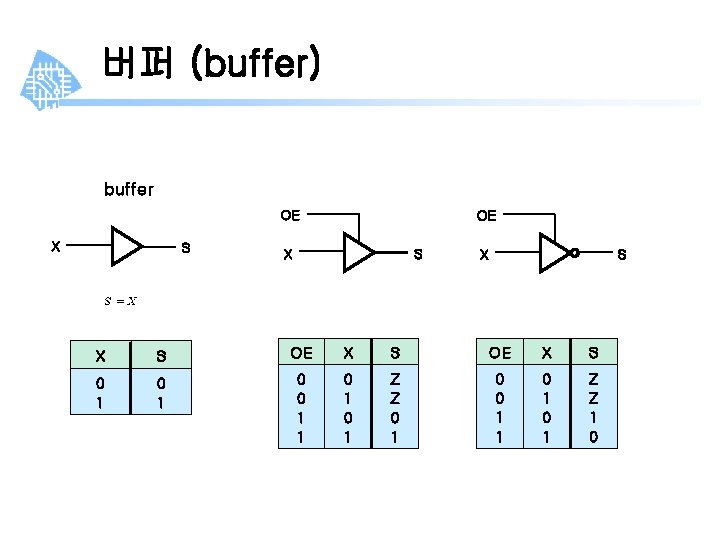

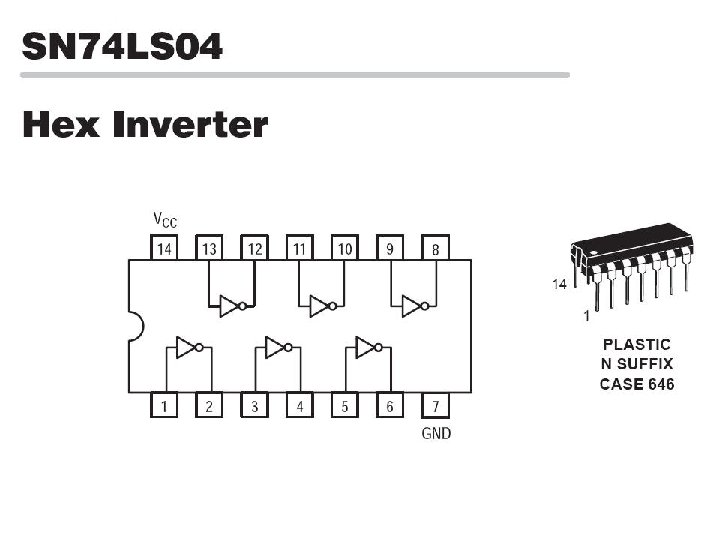

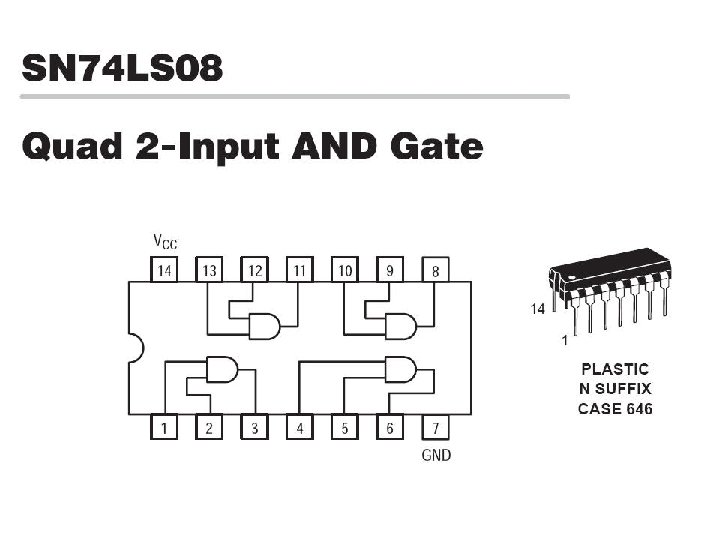

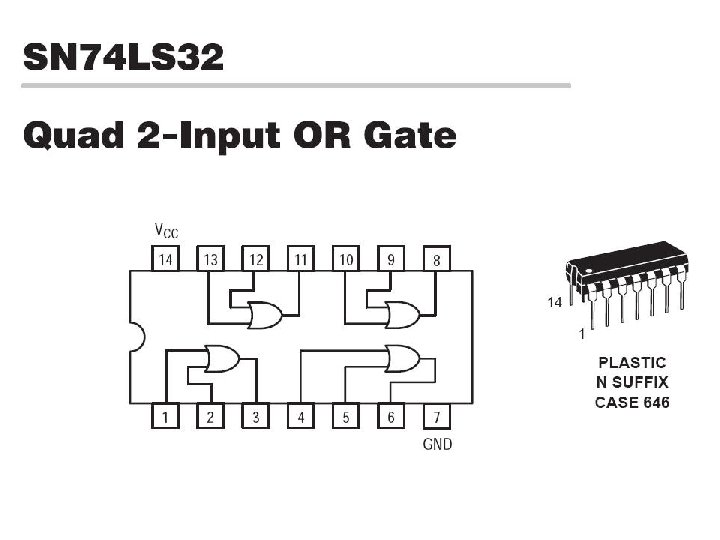

버퍼 (buffer) buffer OE X S OE S X X S OE X S 0 1 0 0 1 1 0 1 Z Z 1 0

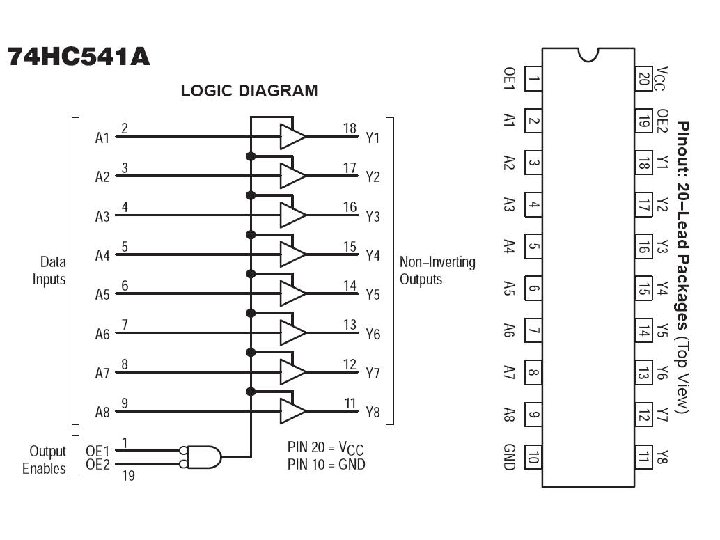

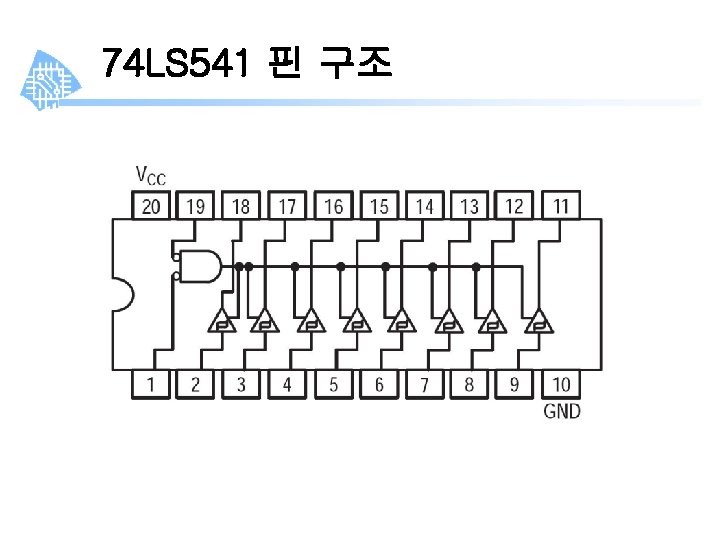

74 LS 541 핀 구조

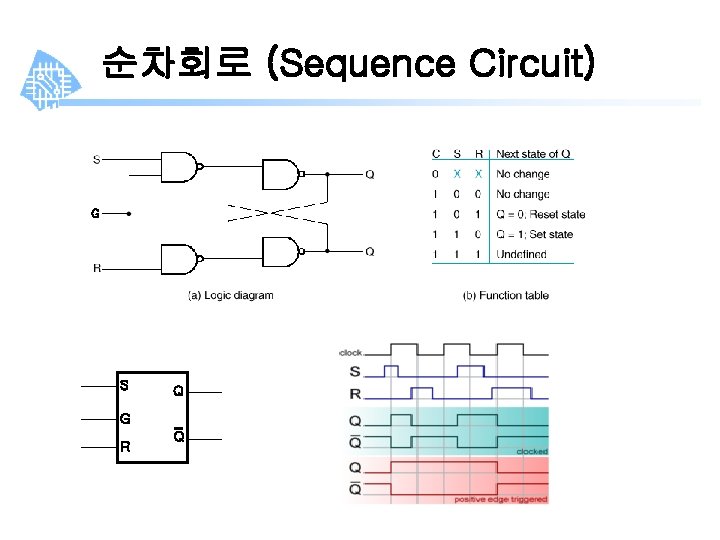

순차회로 (Sequence Circuit) G S Q G R Q

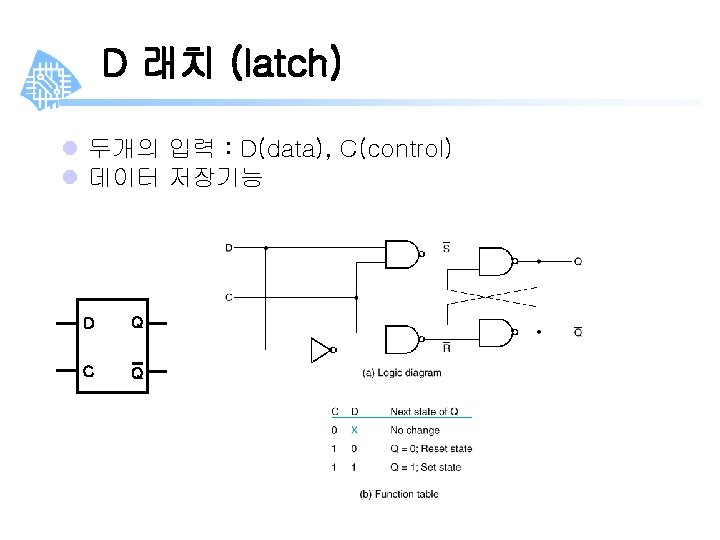

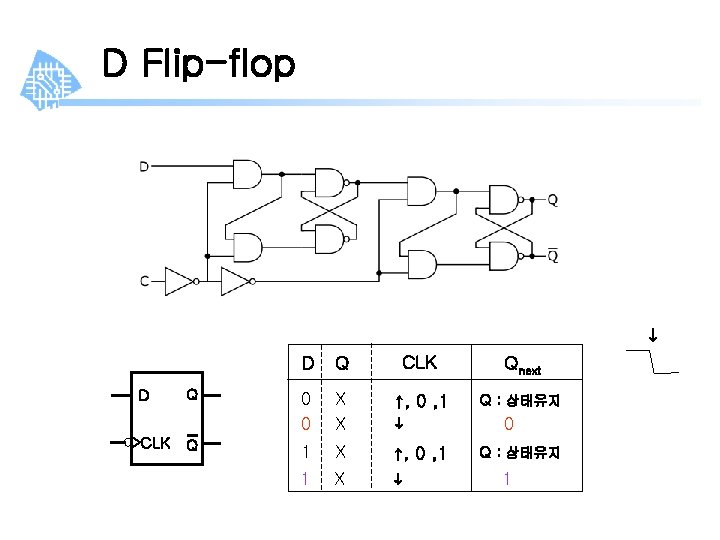

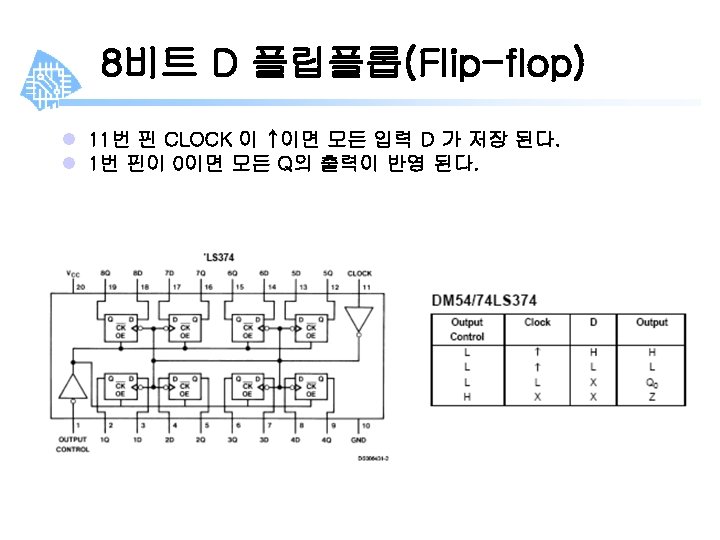

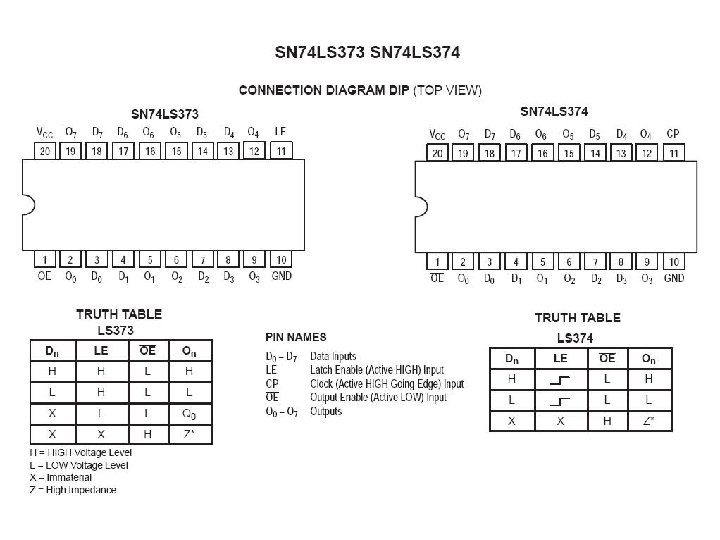

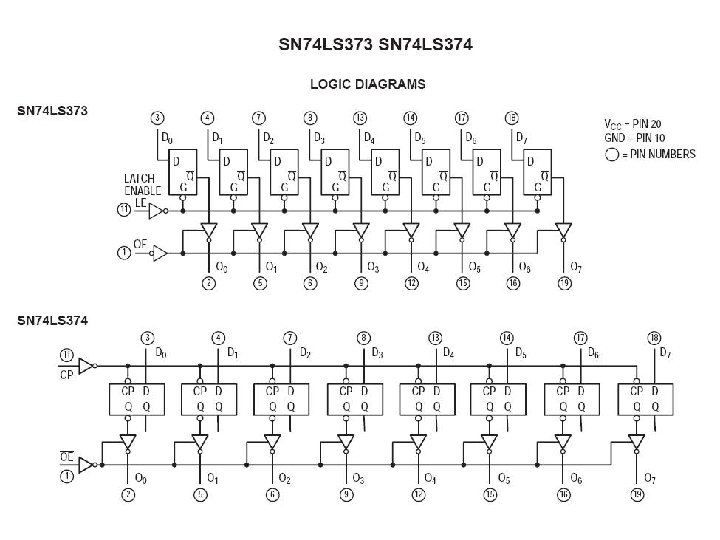

D Flip-flop D Q >CLK Q CLK D Q 0 0 X X ↑, 1 1 X X ↑, 0 , 1 Q : 상태유지 0 Qnext 0 , 1 Q : 상태유지 1

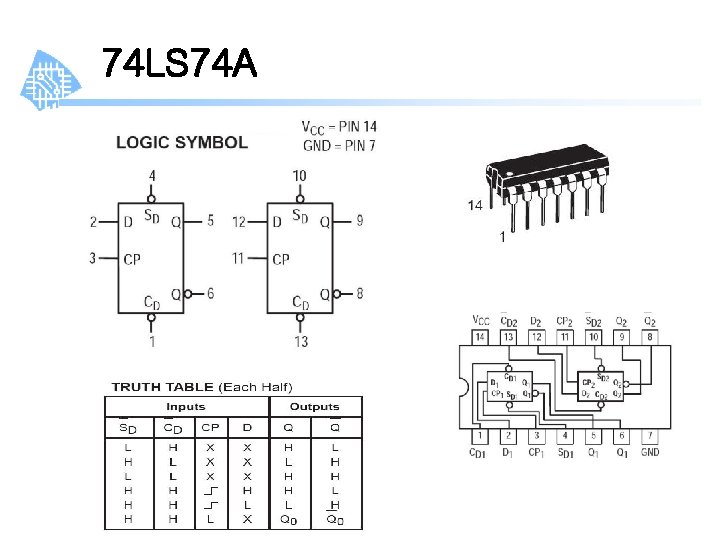

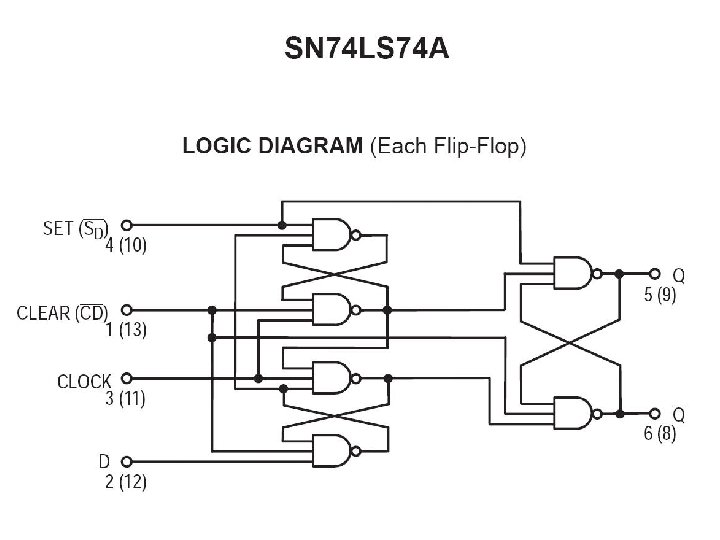

74 LS 74 A

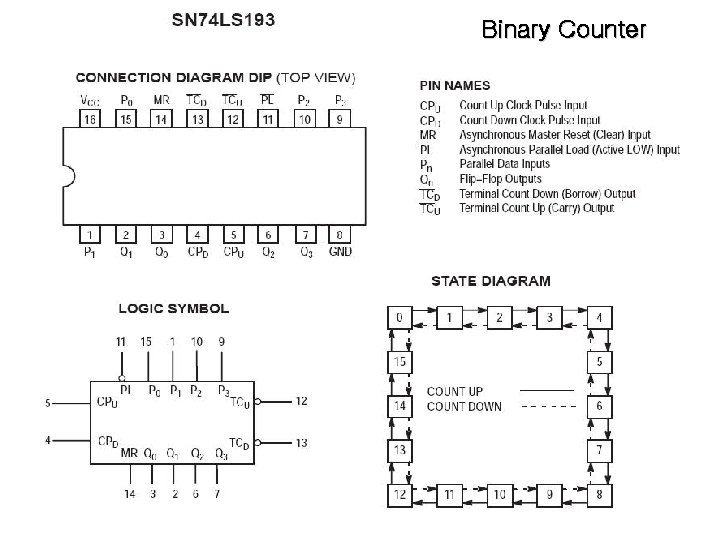

Binary Counter

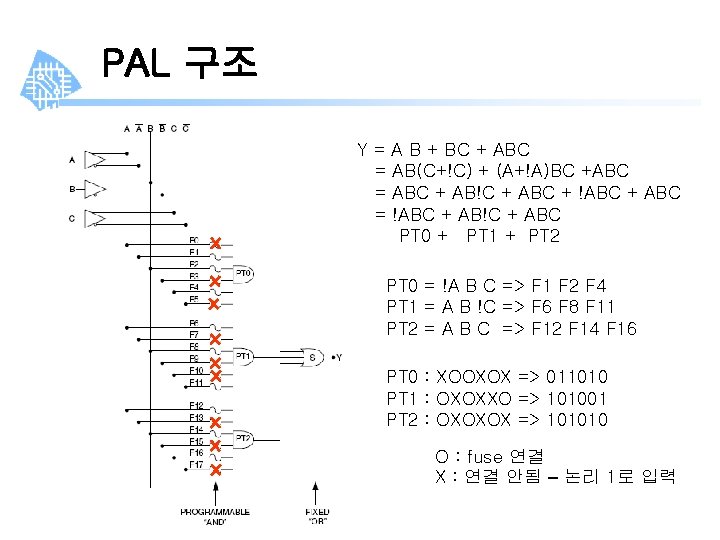

PAL 구조 Y = A B + BC + ABC = AB(C+!C) + (A+!A)BC +ABC = ABC + AB!C + ABC + !ABC + ABC = !ABC + AB!C + ABC PT 0 + PT 1 + PT 2 PT 0 = !A B C => F 1 F 2 F 4 PT 1 = A B !C => F 6 F 8 F 11 PT 2 = A B C => F 12 F 14 F 16 PT 0 : XOOXOX => 011010 PT 1 : OXOXXO => 101001 PT 2 : OXOXOX => 101010 O : fuse 연결 X : 연결 안됨 – 논리 1로 입력

PLD 2 l SPLD (Simple Programmable Logic) ¡PAL과 유사한 구조. 게이트 수는 약 200개 정도. l CPLD (Complex Programmable Logic Device) ¡특별한 논리함수를 구현을 위한 Embedded Array Block을 가지고 있다. l FPGA (Field Programmable Gate Array) ¡PLD의 블록간의 연결에 Array구조와 Row구조 사용 ¡게이트의 용량이 많다.

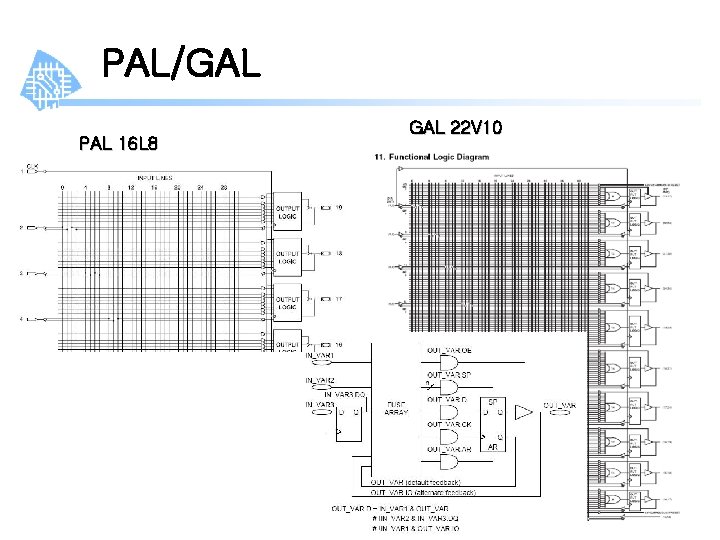

PAL/GAL PAL 16 L 8 GAL 22 V 10

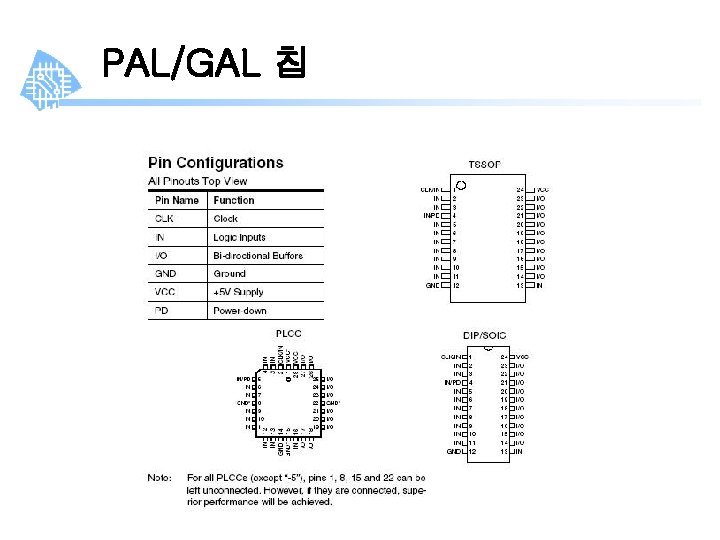

PAL/GAL 칩

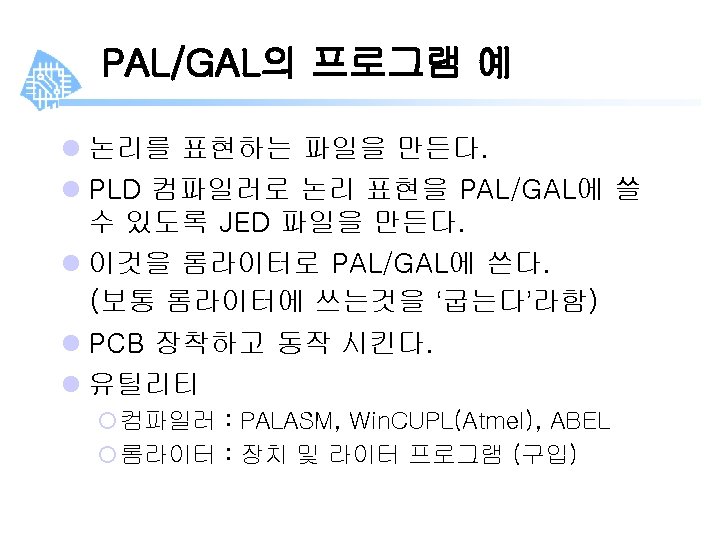

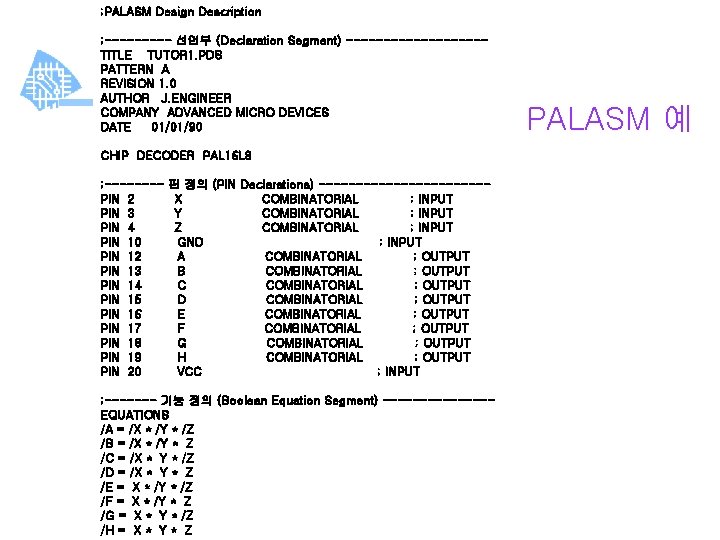

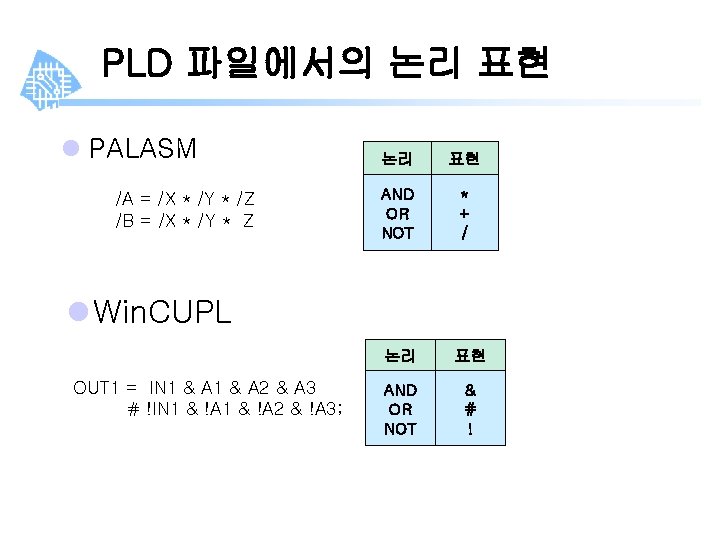

; PALASM Design Description ; ----- 선언부 (Declaration Segment) ---------TITLE TUTOR 1. PDS PATTERN A REVISION 1. 0 AUTHOR J. ENGINEER COMPANY ADVANCED MICRO DEVICES DATE 01/01/90 PAL/GAL 프로그램 예 CHIP DECODER PAL 16 L 8 ; -------PIN 2 PIN 3 PIN 4 PIN 10 PIN 12 PIN 13 PIN 14 PIN 15 PIN 16 PIN 17 PIN 18 PIN 19 PIN 20 핀 정의 (PIN Declarations) -----------X COMBINATORIAL ; INPUT Y COMBINATORIAL ; INPUT Z COMBINATORIAL ; INPUT GND ; INPUT A COMBINATORIAL ; OUTPUT B COMBINATORIAL ; OUTPUT C COMBINATORIAL ; OUTPUT D COMBINATORIAL ; OUTPUT E COMBINATORIAL ; OUTPUT F COMBINATORIAL ; OUTPUT G COMBINATORIAL ; OUTPUT H COMBINATORIAL ; OUTPUT VCC ; INPUT ; ------- 기능 정의 (Boolean Equation Segment) -------EQUATIONS /A = /X * /Y * /Z /B = /X * /Y * Z /C = /X * Y * /Z /D = /X * Y * Z /E = X * /Y * /Z /F = X * /Y * Z /G = X * Y * /Z /H = X * Y * Z PALASM 예

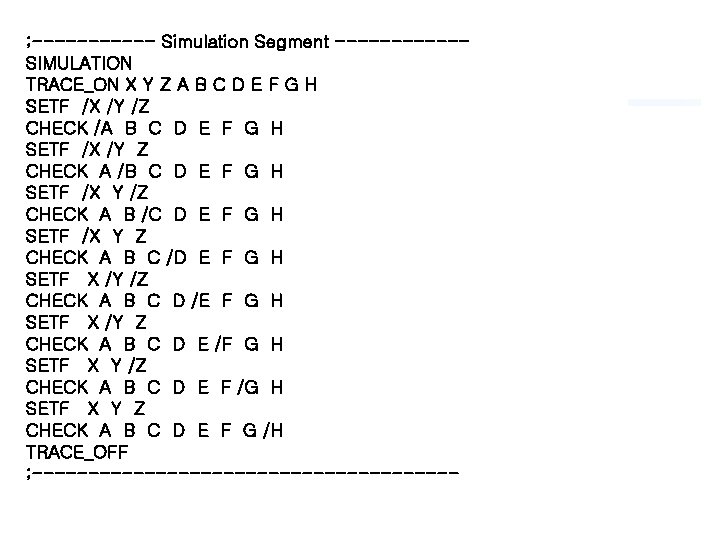

; ------ Simulation Segment ------SIMULATION TRACE_ON X Y Z A B C D E F G H SETF /X /Y /Z CHECK /A B C D E F G H SETF /X /Y Z CHECK A /B C D E F G H SETF /X Y /Z CHECK A B /C D E F G H SETF /X Y Z CHECK A B C /D E F G H SETF X /Y /Z CHECK A B C D /E F G H SETF X /Y Z CHECK A B C D E /F G H SETF X Y /Z CHECK A B C D E F /G H SETF X Y Z CHECK A B C D E F G /H TRACE_OFF ; ------------------- PAL/GAL 예

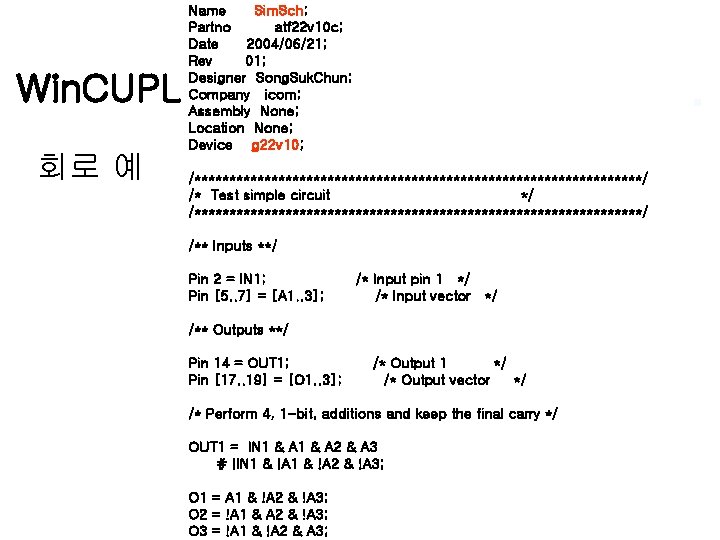

Win. CUPL 회로 예 Name Sim. Sch; Partno atf 22 v 10 c; Date 2004/06/21; Rev 01; Designer Song. Suk. Chun; Company icom; Assembly None; Location None; Device g 22 v 10; /********************************/ /* Test simple circuit */ /********************************/ /** Inputs **/ Pin 2 = IN 1; Pin [5. . 7] = [A 1. . 3]; /* Input pin 1 */ /* Input vector */ /** Outputs **/ Pin 14 = OUT 1; Pin [17. . 19] = [O 1. . 3]; /* Output 1 */ /* Output vector */ /* Perform 4, 1 -bit, additions and keep the final carry */ OUT 1 = IN 1 & A 2 & A 3 # !IN 1 & !A 2 & !A 3; O 1 = A 1 & !A 2 & !A 3; O 2 = !A 1 & A 2 & !A 3; O 3 = !A 1 & !A 2 & A 3;

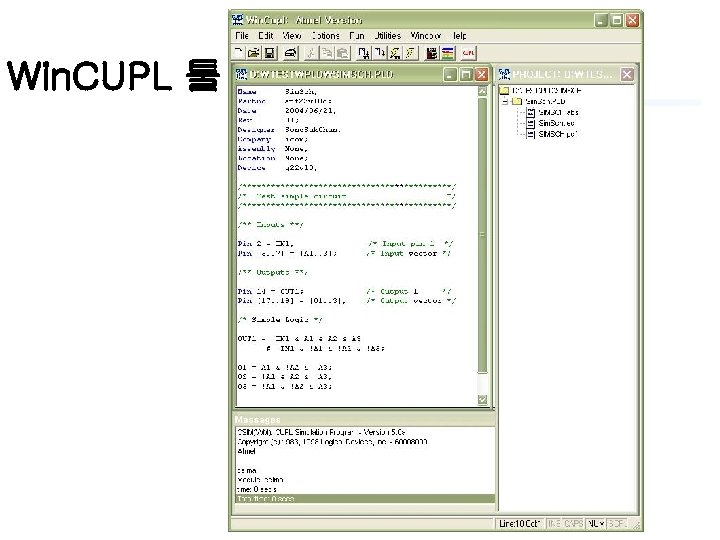

Win. CUPL 툴

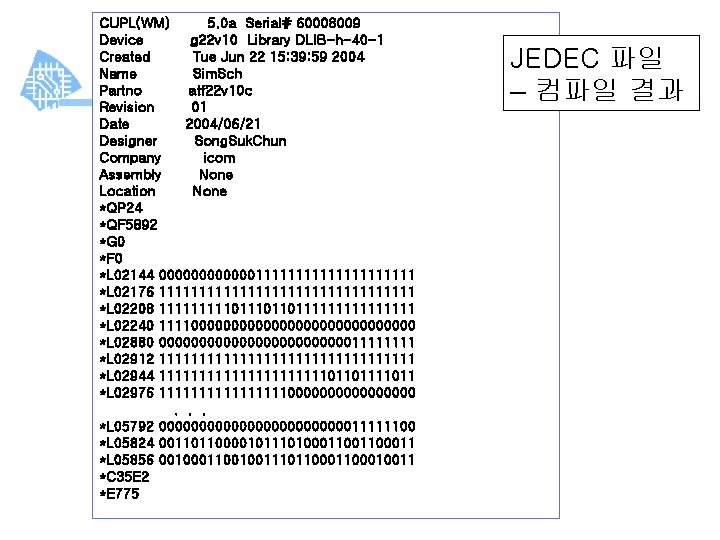

CUPL(WM) 5. 0 a Serial# 60008009 Device g 22 v 10 Library DLIB-h-40 -1 Created Tue Jun 22 15: 39: 59 2004 Name Sim. Sch Partno atf 22 v 10 c Revision 01 Date 2004/06/21 Designer Song. Suk. Chun Company icom Assembly None Location None *QP 24 *QF 5892 *G 0 *F 0 *L 02144 0000001111111111 *L 02176 1111111111111111 *L 02208 11111011011111111 *L 02240 111100000000000000 *L 02880 0000000000001111 *L 02912 1111111111111111 *L 02944 11111111111011011 *L 02976 1111111100000000. . . *L 05792 00000000000011111100 *L 05824 0011011000010111010001100011 *L 05856 001000110010011101100010011 *C 35 E 2 *E 775 JED 파일 JEDEC 파일 – 컴파일 결과

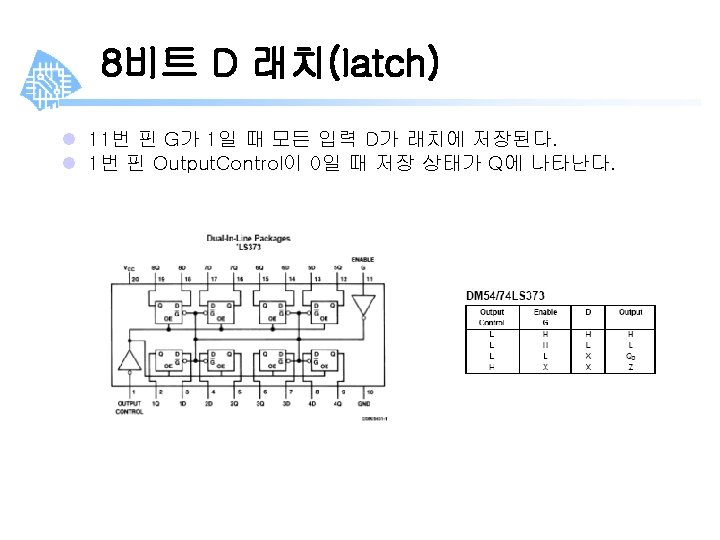

- Slides: 52