Power Efficient Tensilica Processor IP to Address New

- Slides: 23

Power Efficient Tensilica® Processor IP to Address New Trends in Consumer and Automotive Products Jeffrey Xu Sr. Business Development Manager Cadence Design Systems D&R IP-SOC Days Shanghai September 12 th, 2019

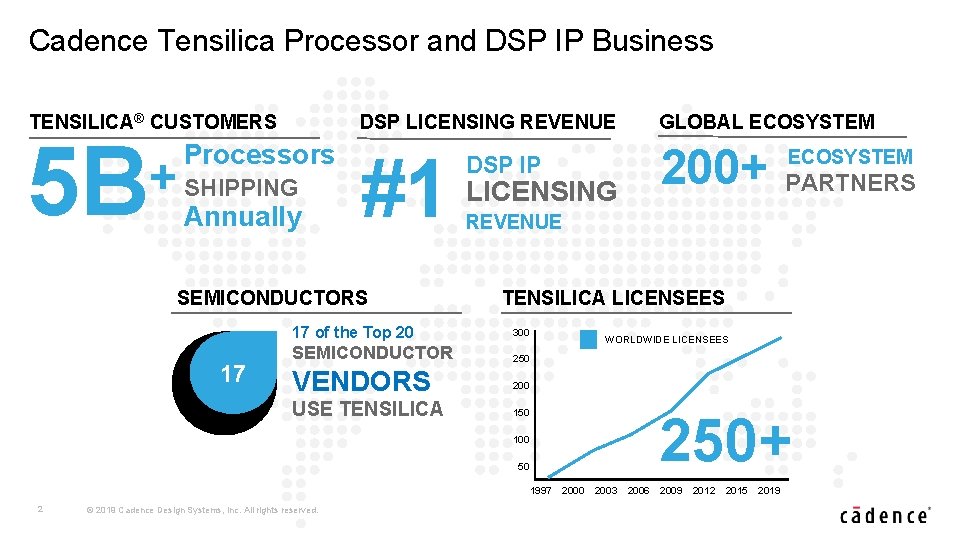

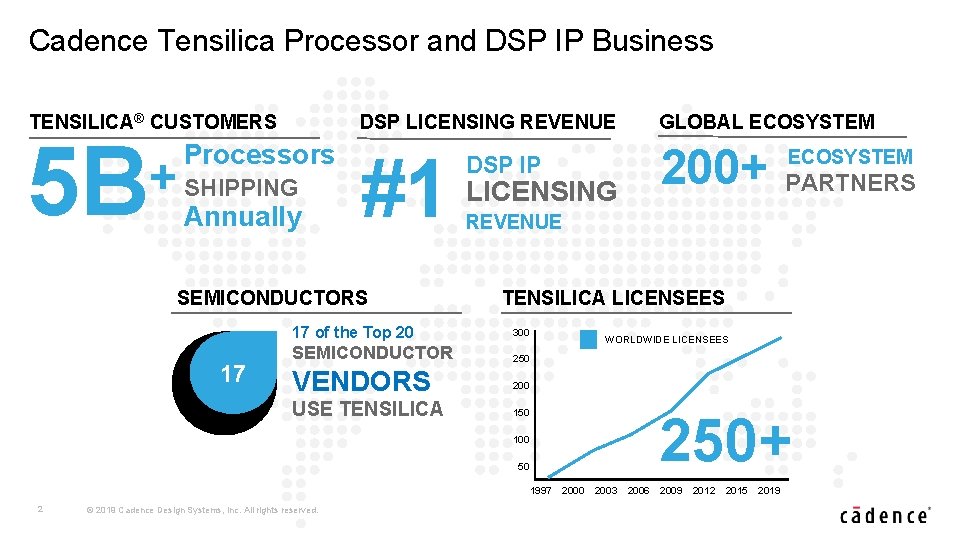

Cadence Tensilica Processor and DSP IP Business TENSILICA® CUSTOMERS 5 B Processors + SHIPPING Annually DSP LICENSING REVENUE GLOBAL ECOSYSTEM #1 200+ SEMICONDUCTORS 17 DSP IP LICENSING TENSILICA LICENSEES 17 of the Top 20 300 SEMICONDUCTOR 250 VENDORS 200 USE TENSILICA 150 WORLDWIDE LICENSEES 250+ 50 1997 © 2019 Cadence Design Systems, Inc. All rights reserved. PARTNERS REVENUE 100 2 ECOSYSTEM 2000 2003 2006 2009 2012 2015 2019

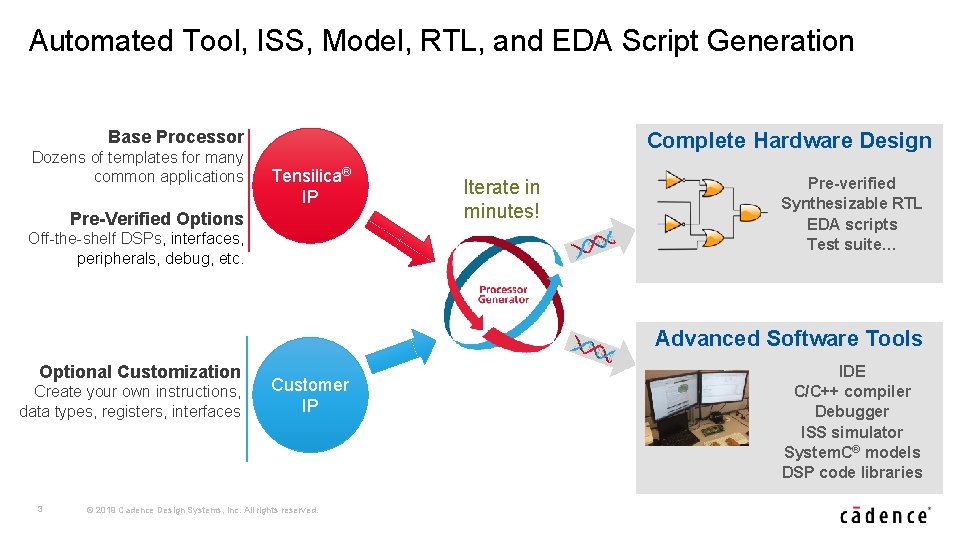

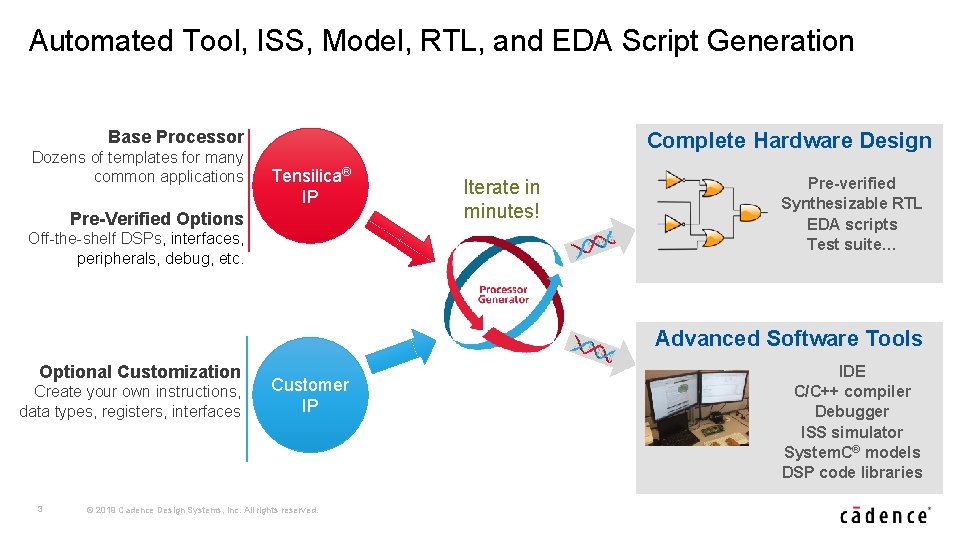

Automated Tool, ISS, Model, RTL, and EDA Script Generation Base Processor Dozens of templates for many common applications Complete Hardware Design Tensilica® IP Pre-Verified Options Off-the-shelf DSPs, interfaces, peripherals, debug, etc. Iterate in minutes! Pre-verified Synthesizable RTL EDA scripts Test suite… Advanced Software Tools Optional Customization Create your own instructions, data types, registers, interfaces 3 Customer IP © 2019 Cadence Design Systems, Inc. All rights reserved. IDE C/C++ compiler Debugger ISS simulator System. C® models DSP code libraries

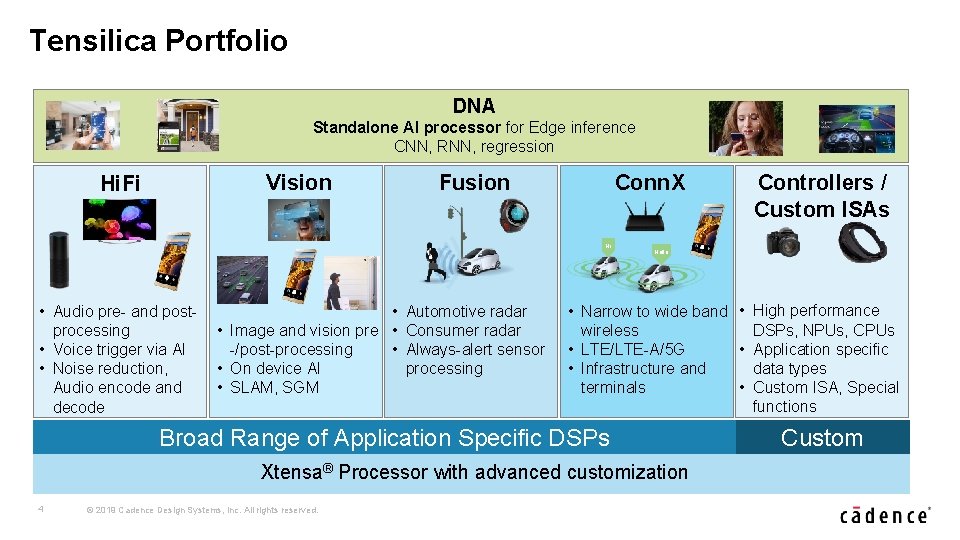

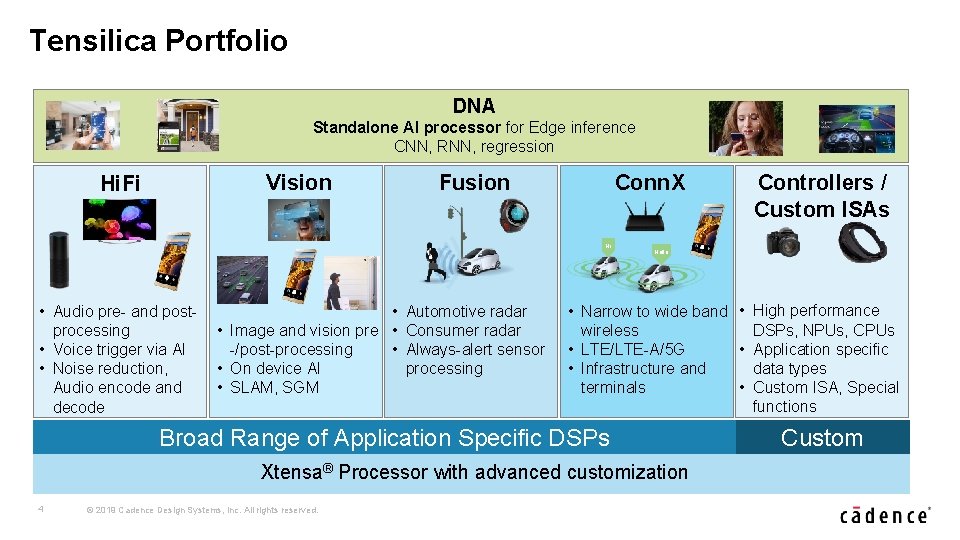

Tensilica Portfolio DNA Standalone AI processor for Edge inference CNN, RNN, regression Vision Hi. Fi Fusion Conn. X Hi • Audio pre- and postprocessing • Voice trigger via AI • Noise reduction, Audio encode and decode • Automotive radar • Image and vision pre • Consumer radar • Always-alert sensor -/post-processing • On device AI • SLAM, SGM Hello • Narrow to wide band • High performance DSPs, NPUs, CPUs wireless • Application specific • LTE/LTE-A/5 G data types • Infrastructure and • Custom ISA, Special terminals functions Broad Range of Application Specific DSPs Xtensa® Processor with advanced customization 4 © 2019 Cadence Design Systems, Inc. All rights reserved. Controllers / Custom ISAs Custom

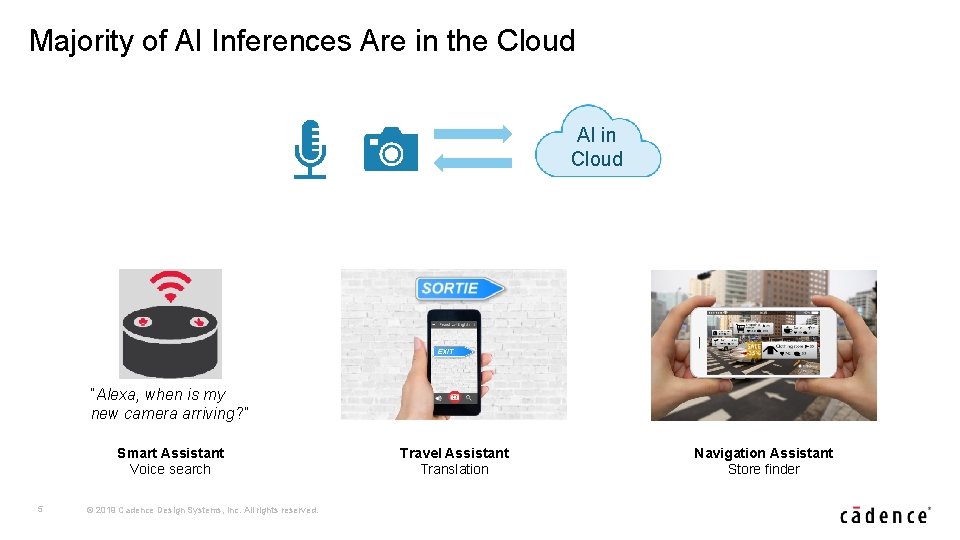

Majority of AI Inferences Are in the Cloud AI in Cloud “Alexa, when is my new camera arriving? ” Smart Assistant Voice search 5 © 2019 Cadence Design Systems, Inc. All rights reserved. Travel Assistant Translation Navigation Assistant Store finder

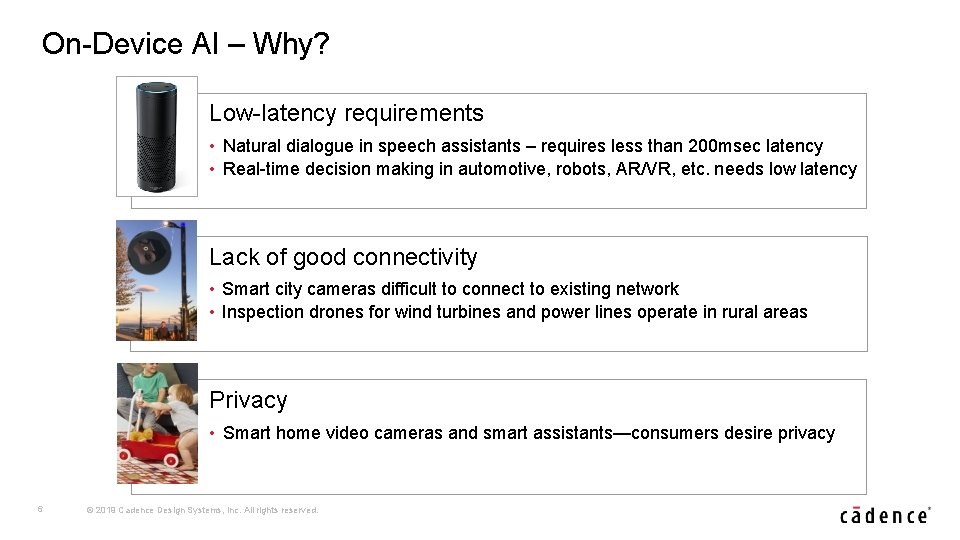

On-Device AI – Why? Low-latency requirements • Natural dialogue in speech assistants – requires less than 200 msec latency • Real-time decision making in automotive, robots, AR/VR, etc. needs low latency Lack of good connectivity • Smart city cameras difficult to connect to existing network • Inspection drones for wind turbines and power lines operate in rural areas Privacy • Smart home video cameras and smart assistants—consumers desire privacy 6 © 2019 Cadence Design Systems, Inc. All rights reserved.

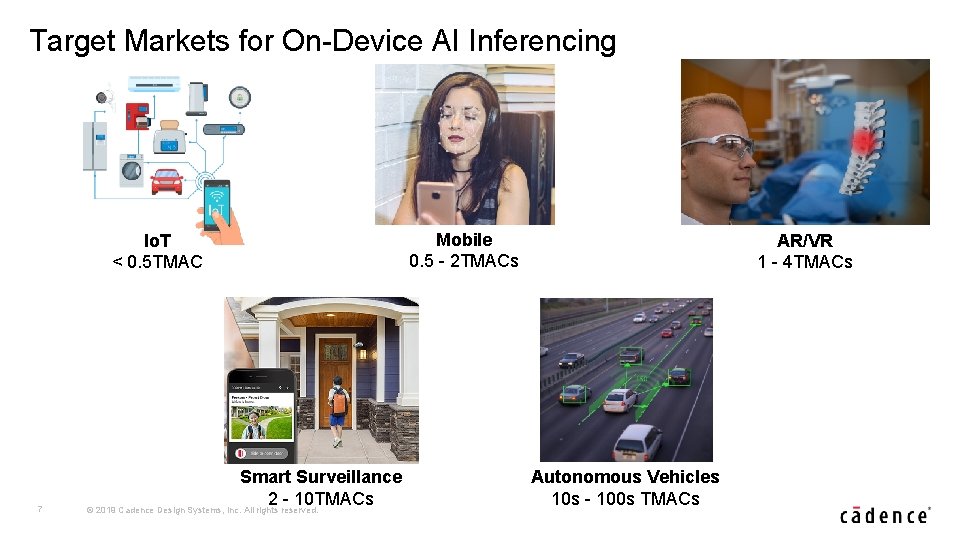

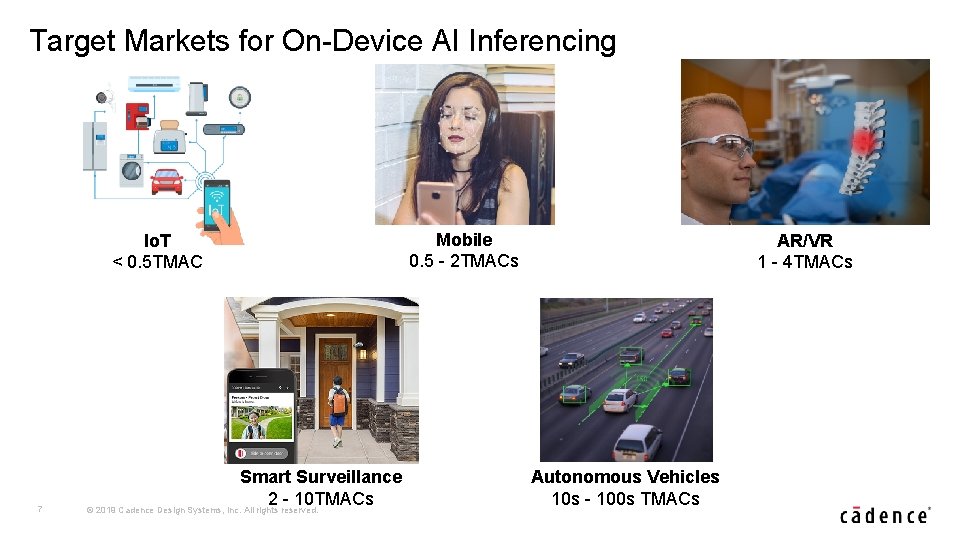

Target Markets for On-Device AI Inferencing Io. T < 0. 5 TMAC 7 Smart Surveillance 2 - 10 TMACs © 2019 Cadence Design Systems, Inc. All rights reserved. Mobile 0. 5 - 2 TMACs AR/VR 1 - 4 TMACs Autonomous Vehicles 10 s - 100 s TMACs

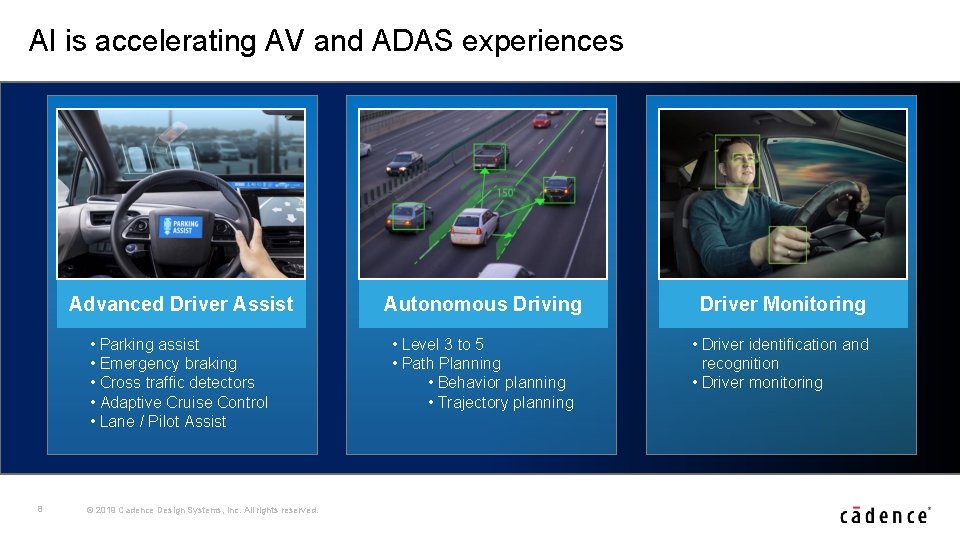

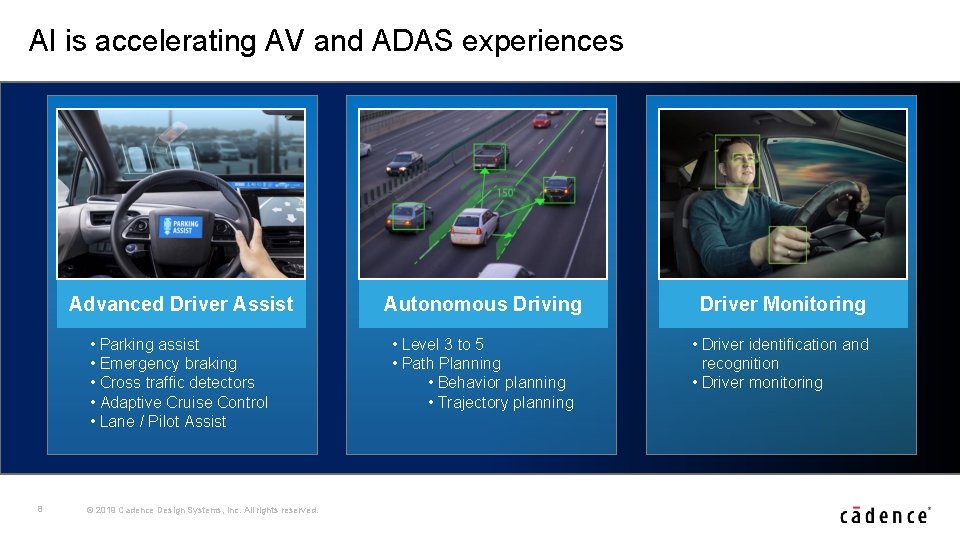

AI is accelerating AV and ADAS experiences 8 Advanced Driver Assist Autonomous Driving Driver Monitoring • Parking assist • Emergency braking • Cross traffic detectors • Adaptive Cruise Control • Lane / Pilot Assist • Level 3 to 5 • Path Planning • Behavior planning • Trajectory planning • Driver identification and recognition • Driver monitoring © 2019 Cadence Design Systems, Inc. All rights reserved.

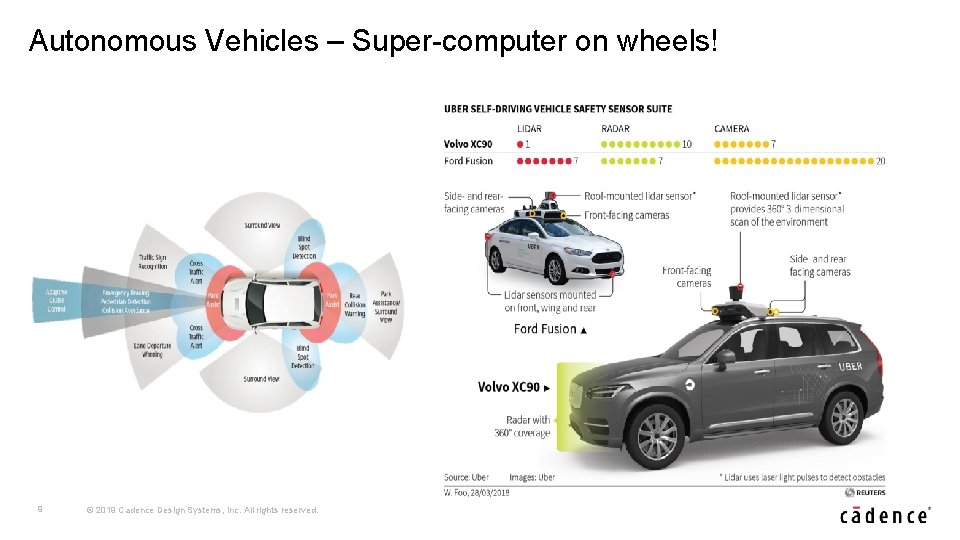

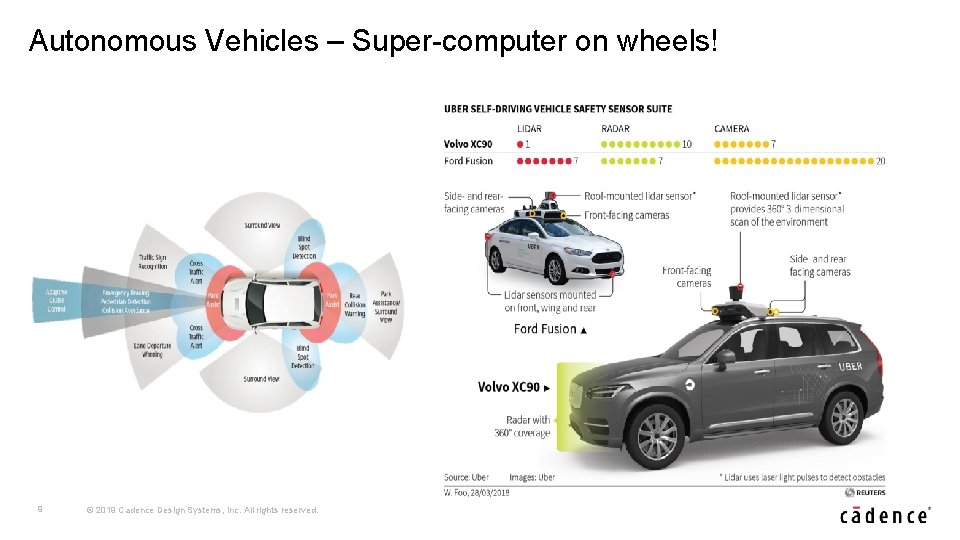

Autonomous Vehicles – Super-computer on wheels! 9 © 2019 Cadence Design Systems, Inc. All rights reserved.

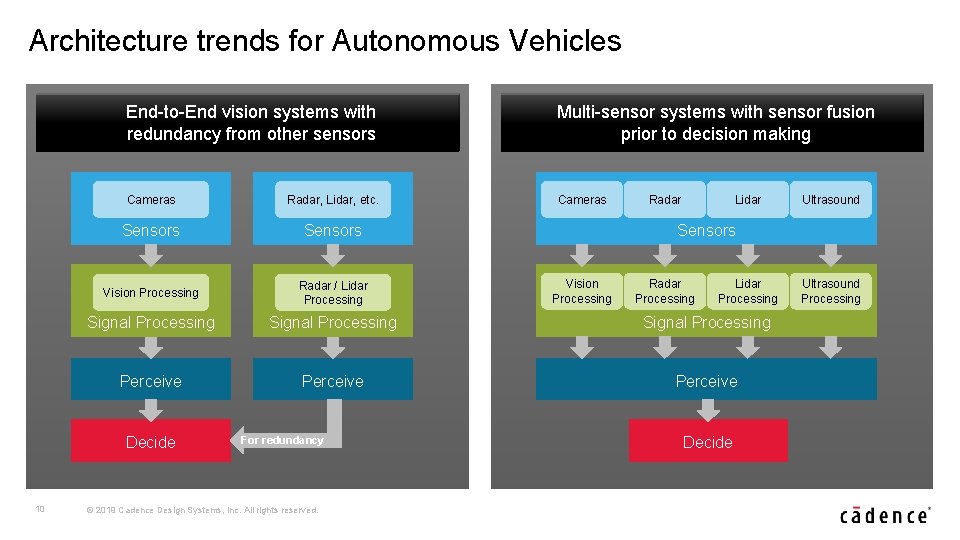

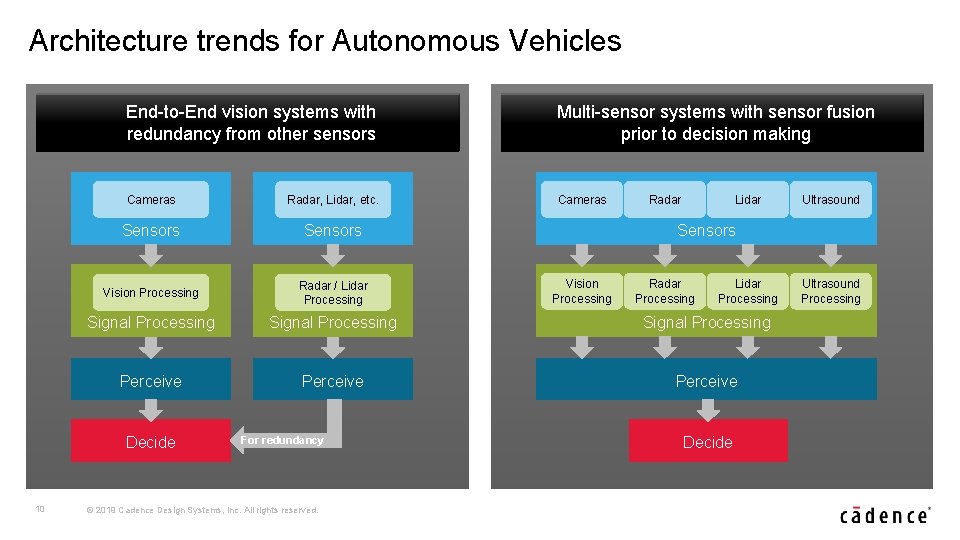

Architecture trends for Autonomous Vehicles End-to-End vision systems with redundancy from other sensors Multi-sensor systems with sensor fusion prior to decision making Cameras Radar, Lidar, etc. Cameras Sensors Vision Processing Radar / Lidar Processing Signal Processing Perceive Decide 10 For redundancy © 2019 Cadence Design Systems, Inc. All rights reserved. Radar Lidar Ultrasound Sensors Vision Processing Radar Processing Lidar Processing Decide Ultrasound Processing

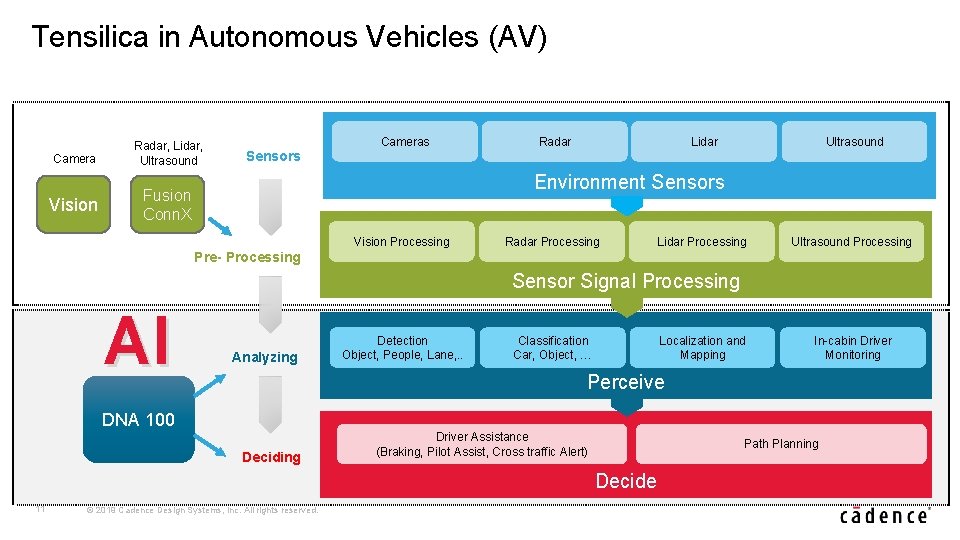

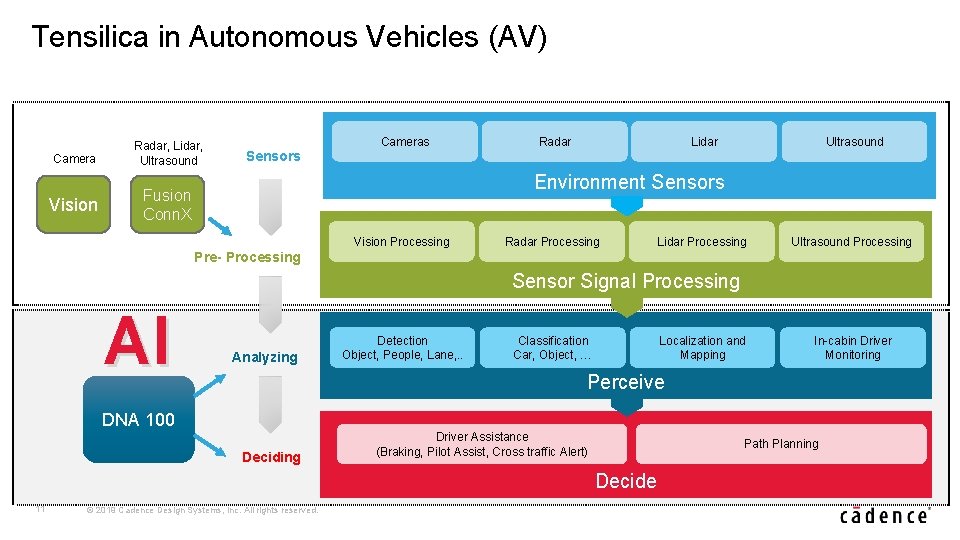

Tensilica in Autonomous Vehicles (AV) Camera Radar, Lidar, Ultrasound Vision Fusion Conn. X Cameras Radar Lidar Ultrasound Sensors Environment Sensors Vision Processing Radar Processing Lidar Processing Ultrasound Processing Pre- Processing Sensor Signal Processing AI Analyzing Detection Object, People, Lane, . . Classification Car, Object, … Localization and Mapping In-cabin Driver Monitoring Perceive DNA 100 Deciding Driver Assistance (Braking, Pilot Assist, Cross traffic Alert) Path Planning Decide 11 © 2019 Cadence Design Systems, Inc. All rights reserved.

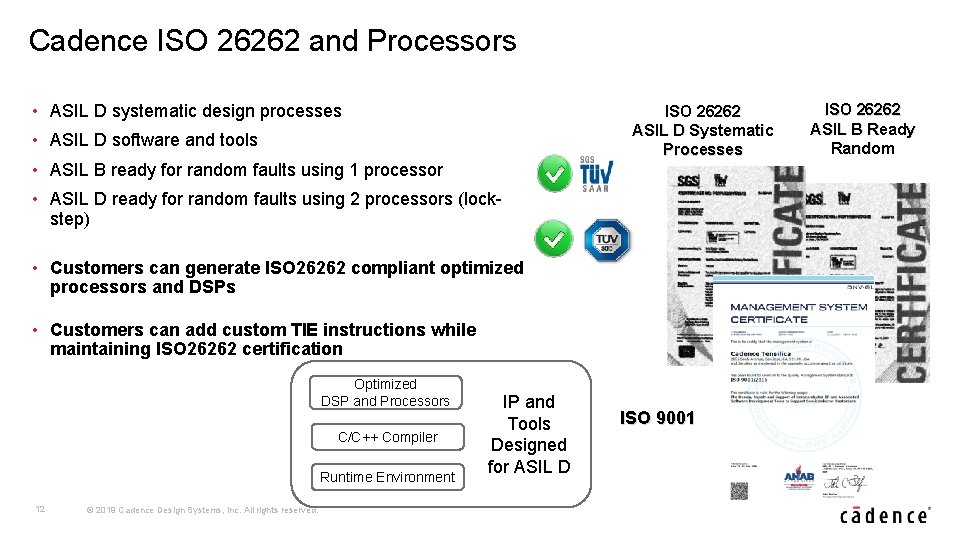

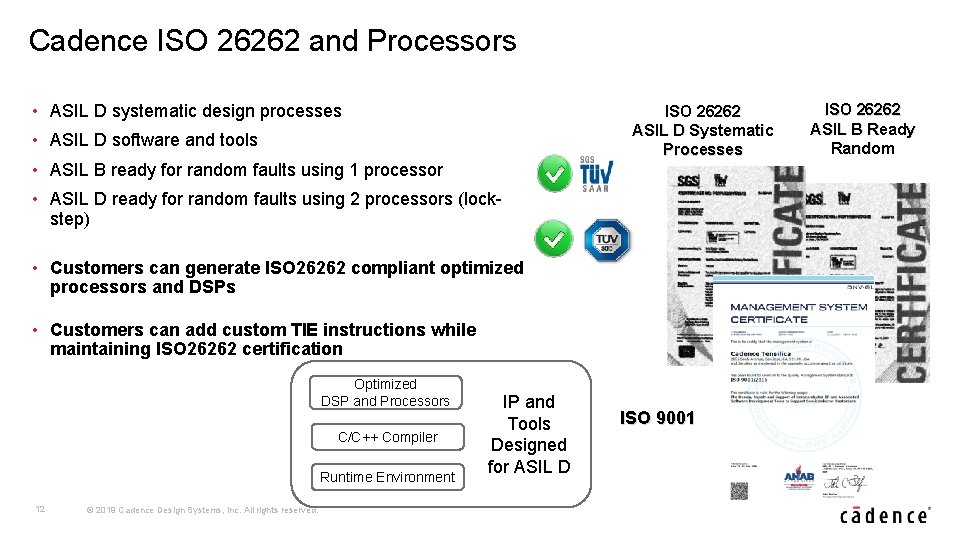

Cadence ISO 26262 and Processors • ASIL D systematic design processes ISO 26262 ASIL D Systematic Processes • ASIL D software and tools • ASIL B ready for random faults using 1 processor • ASIL D ready for random faults using 2 processors (lockstep) • Customers can generate ISO 26262 compliant optimized processors and DSPs • Customers can add custom TIE instructions while maintaining ISO 26262 certification Optimized DSP and Processors C/C++ Compiler Runtime Environment 12 © 2019 Cadence Design Systems, Inc. All rights reserved. IP and Tools Designed for ASIL D ISO 9001 ISO 26262 ASIL B Ready Random

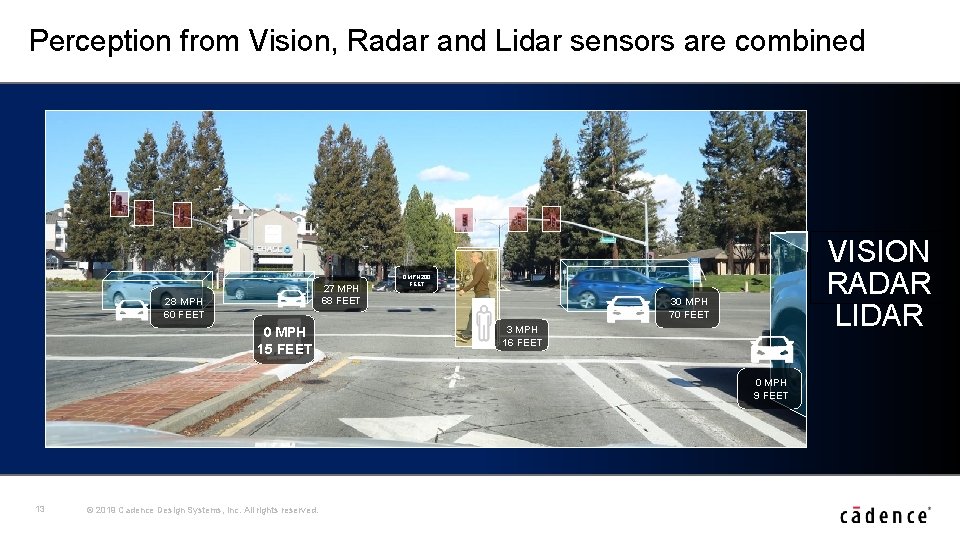

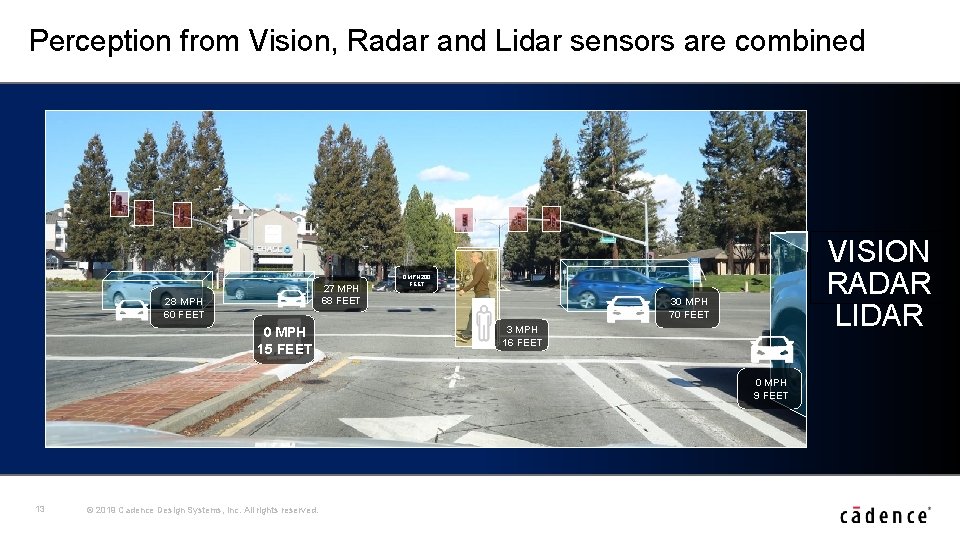

Perception from Vision, Radar and Lidar sensors are combined 27 MPH 68 FEET 28 MPH 60 FEET 0 MPH 15 FEET VISION RADAR LIDAR 0 MPH 200 FEET 30 MPH 70 FEET 3 MPH 16 FEET 0 MPH 9 FEET 13 © 2019 Cadence Design Systems, Inc. All rights reserved.

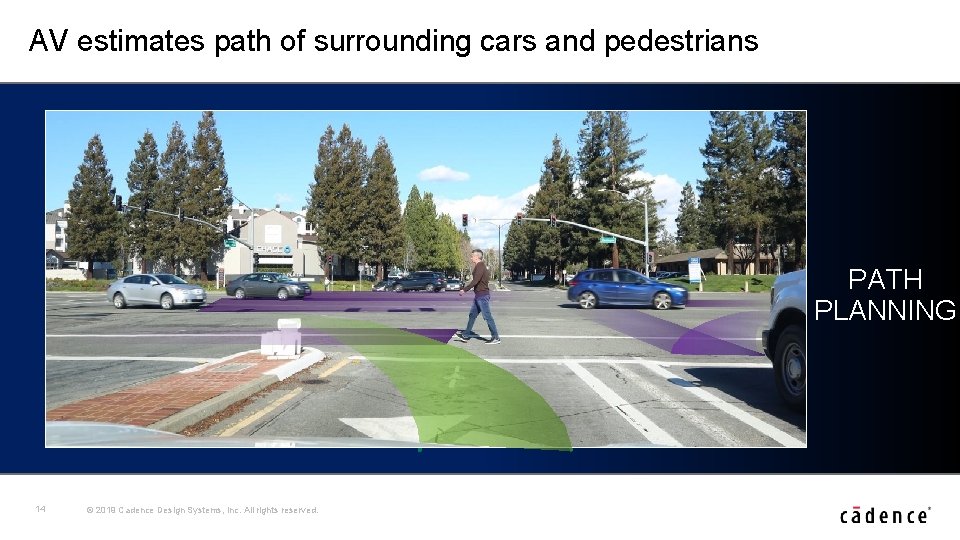

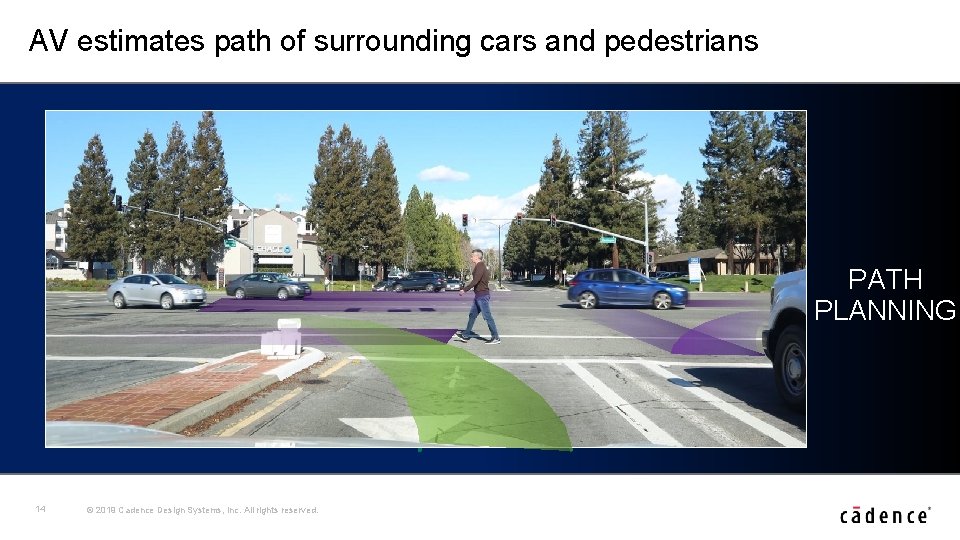

AV estimates path of surrounding cars and pedestrians PATH PLANNING 14 © 2019 Cadence Design Systems, Inc. All rights reserved.

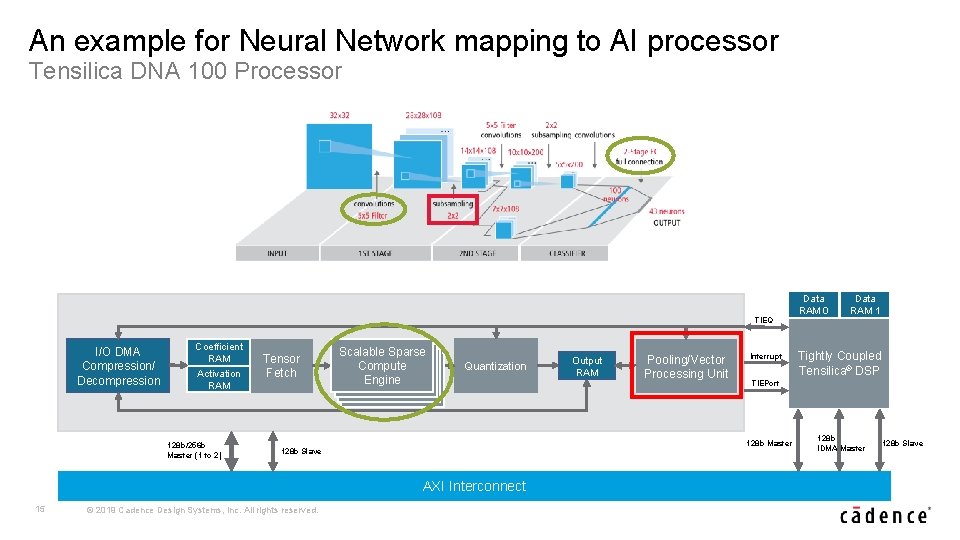

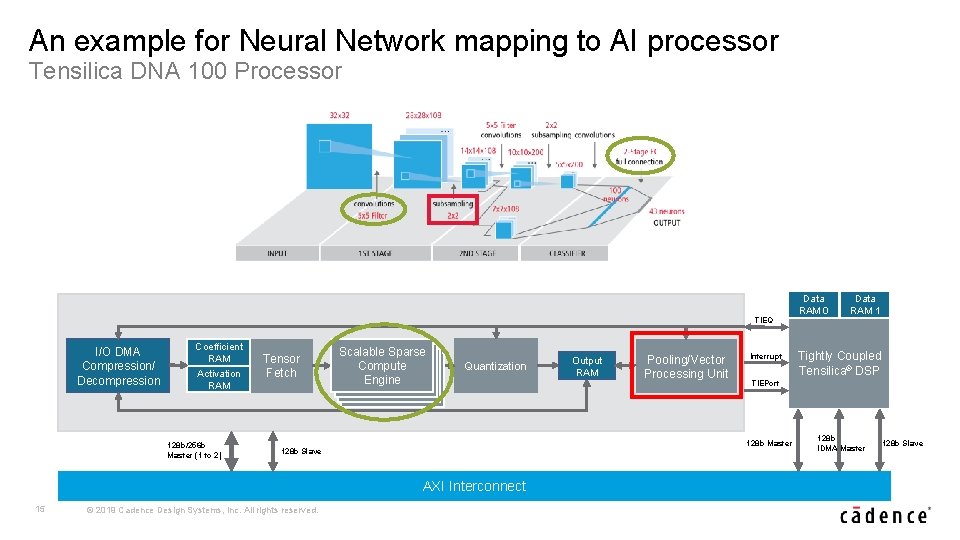

An example for Neural Network mapping to AI processor Tensilica DNA 100 Processor TIEQ I/O DMA Compression/ Decompression Coefficient RAM Activation RAM 128 b/256 b Master (1 to 2) Tensor Fetch Scalable Sparse Compute Engine Quantization © 2019 Cadence Design Systems, Inc. All rights reserved. Pooling/Vector Processing Unit Interrupt Data RAM 1 Tightly Coupled Tensilica® DSP TIEPort 128 b Master 128 b Slave AXI Interconnect 15 Output RAM Data RAM 0 128 b IDMA Master 128 b Slave

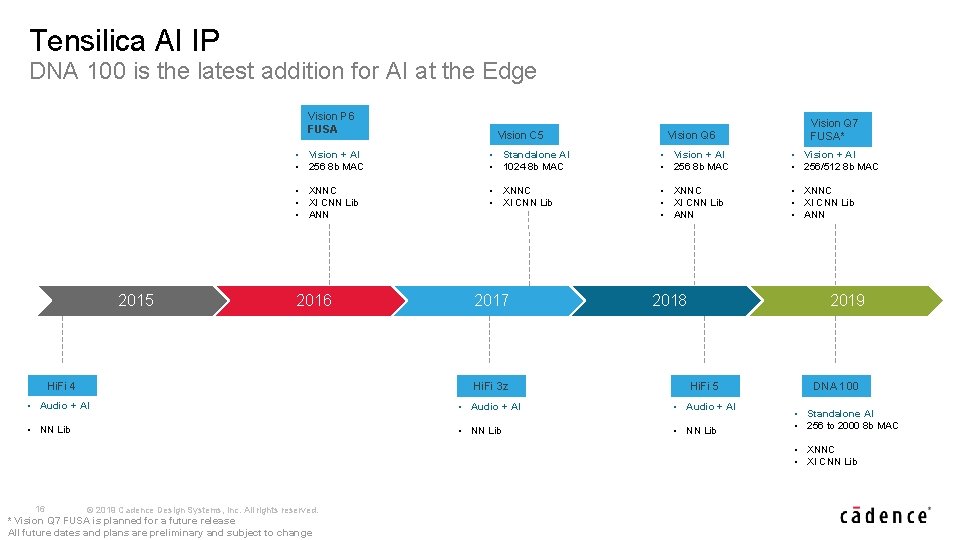

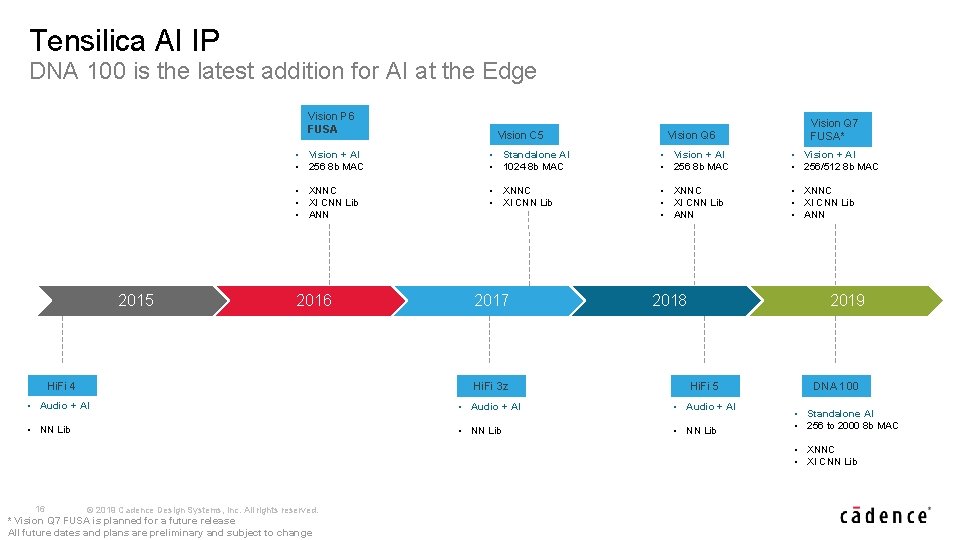

Tensilica AI IP DNA 100 is the latest addition for AI at the Edge Vision P 6 FUSA 2015 Vision C 5 Vision Q 6 Vision Q 7 FUSA* • Vision + AI • 256 8 b MAC • Standalone AI • 1024 8 b MAC • Vision + AI • 256/512 8 b MAC • XNNC • XI CNN Lib • ANN 2016 Hi. Fi 4 2017 2018 2019 Hi. Fi 3 z Hi. Fi 5 • Audio + AI • NN Lib DNA 100 • Standalone AI • 256 to 2000 8 b MAC • XNNC • XI CNN Lib 16 © 2019 Cadence Design Systems, Inc. All rights reserved. * Vision Q 7 FUSA is planned for a future release All future dates and plans are preliminary and subject to change

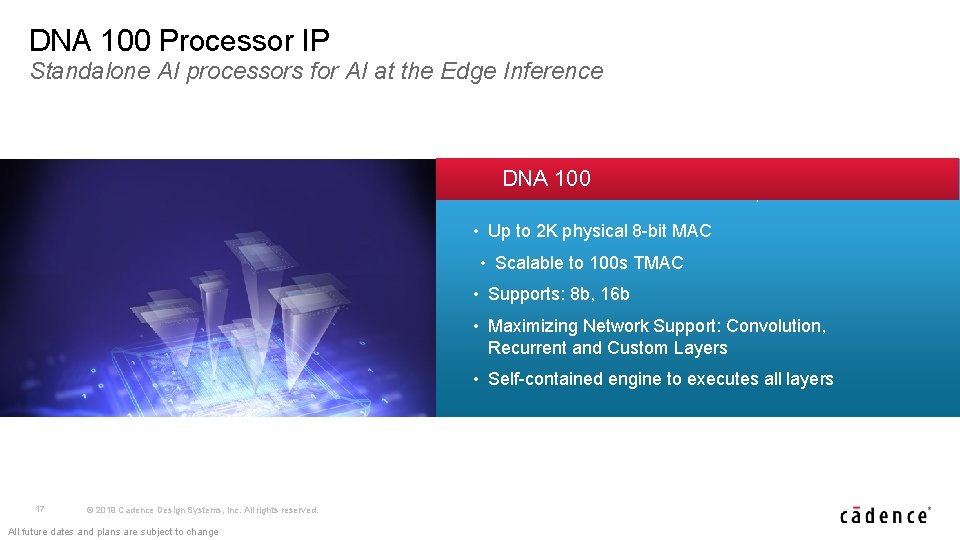

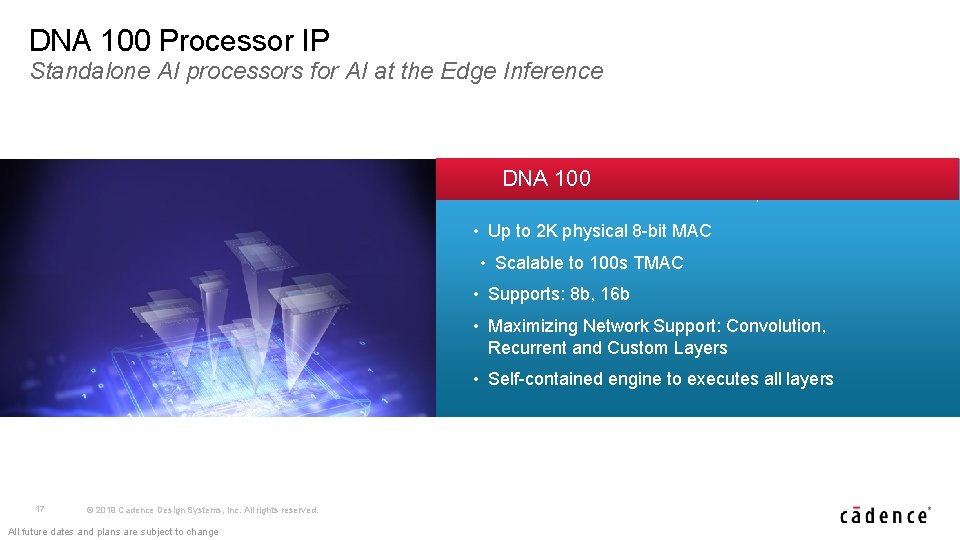

DNA 100 Processor IP Standalone AI processors for AI at the Edge Inference DNA 100 • Up to 2 K physical 8 -bit MAC • Scalable to 100 s TMAC • Supports: 8 b, 16 b • Maximizing Network Support: Convolution, Recurrent and Custom Layers • Self-contained engine to executes all layers 17 © 2019 Cadence Design Systems, Inc. All rights reserved. All future dates and plans are subject to change

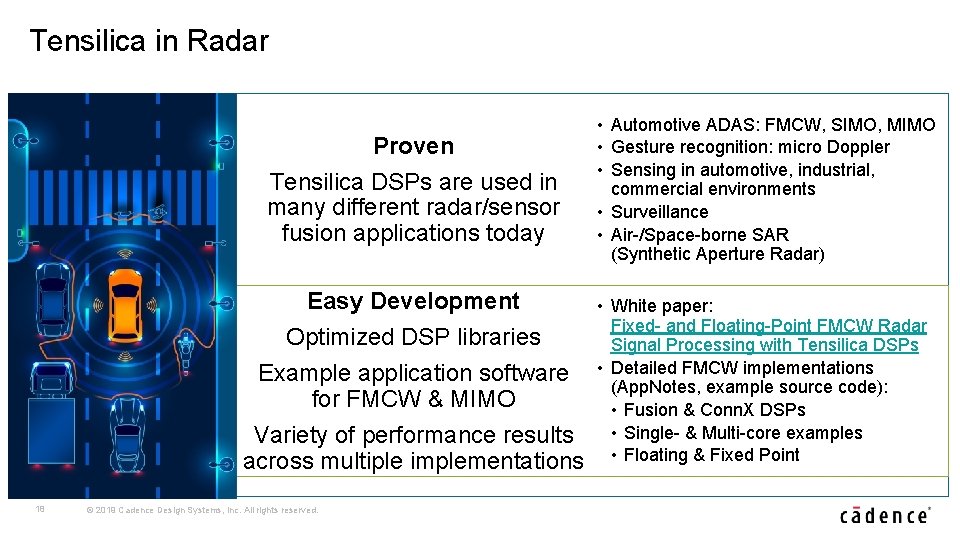

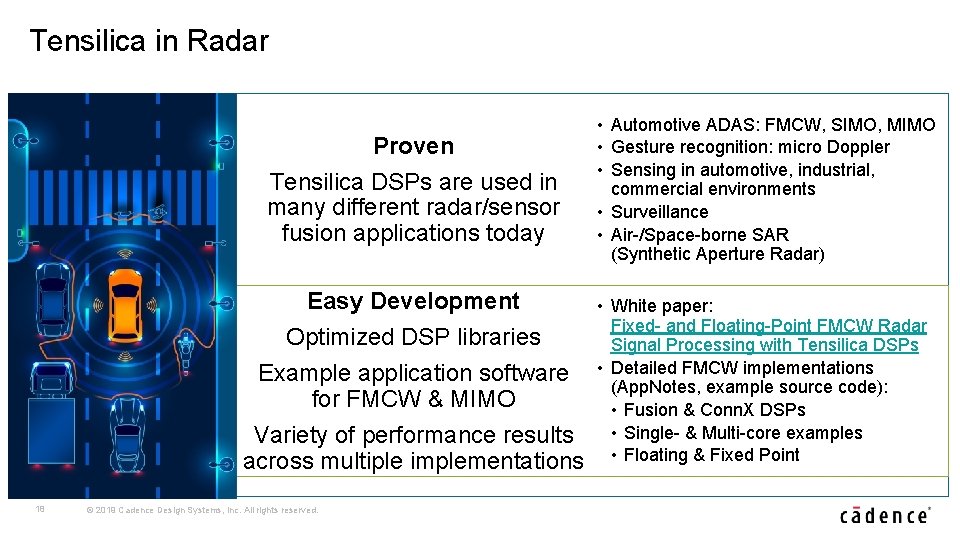

Tensilica in Radar Proven Tensilica DSPs are used in many different radar/sensor fusion applications today Easy Development Optimized DSP libraries Example application software for FMCW & MIMO Variety of performance results across multiple implementations 18 © 2019 Cadence Design Systems, Inc. All rights reserved. • Automotive ADAS: FMCW, SIMO, MIMO • Gesture recognition: micro Doppler • Sensing in automotive, industrial, commercial environments • Surveillance • Air-/Space-borne SAR (Synthetic Aperture Radar) • White paper: Fixed- and Floating-Point FMCW Radar Signal Processing with Tensilica DSPs • Detailed FMCW implementations (App. Notes, example source code): • Fusion & Conn. X DSPs • Single- & Multi-core examples • Floating & Fixed Point

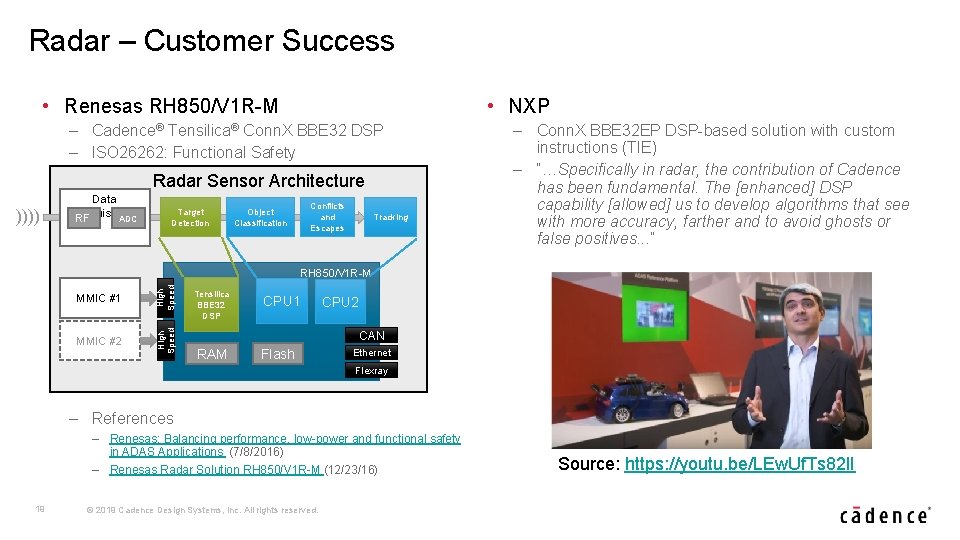

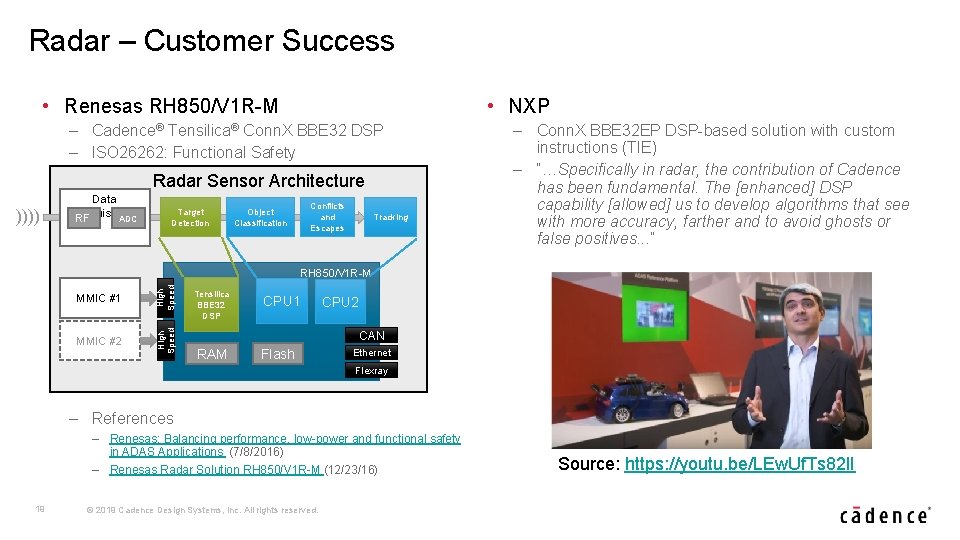

Radar – Customer Success • Renesas RH 850/V 1 R-M • NXP – Cadence® Tensilica® Conn. X BBE 32 DSP – ISO 26262: Functional Safety Radar Sensor Architecture )))) Data Acquisition ADC RF Target Detection Object Classification Conflicts and Escapes Tracking – Conn. X BBE 32 EP DSP-based solution with custom instructions (TIE) – “…Specifically in radar, the contribution of Cadence has been fundamental. The [enhanced] DSP capability [allowed] us to develop algorithms that see with more accuracy, farther and to avoid ghosts or false positives. . . ” MMIC #1 High Speed MMIC #2 High Speed RH 850/V 1 R-M Tensilica BBE 32 DSP CPU 1 CPU 2 CAN RAM Flash Ethernet Flexray – References – Renesas: Balancing performance, low-power and functional safety in ADAS Applications (7/8/2016) – Renesas Radar Solution RH 850/V 1 R-M (12/23/16) 19 © 2019 Cadence Design Systems, Inc. All rights reserved. Source: https: //youtu. be/LEw. Uf. Ts 82 l. I

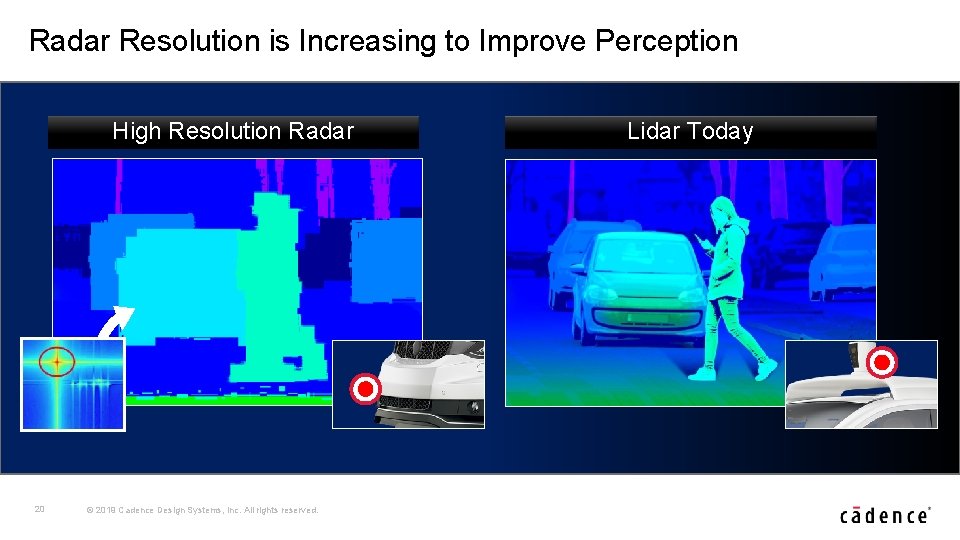

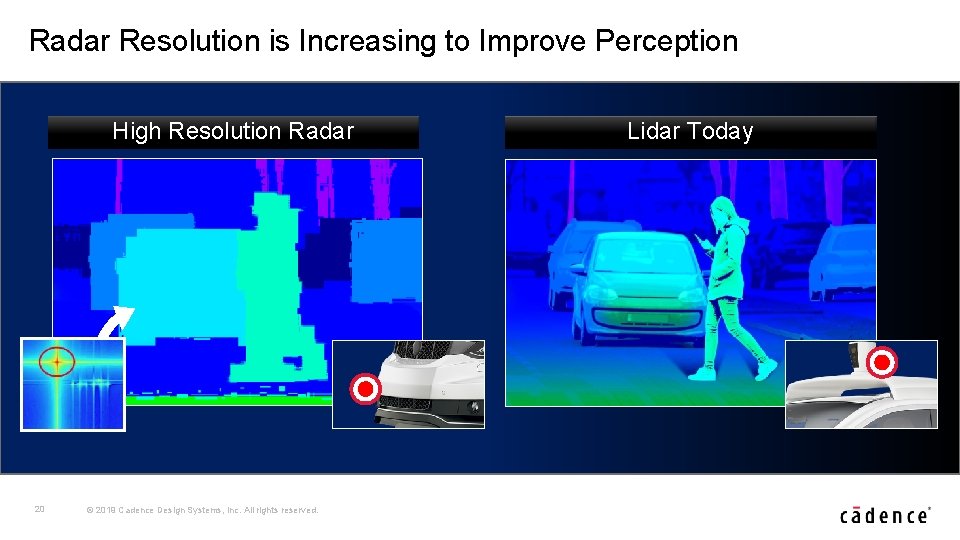

Radar Resolution is Increasing to Improve Perception High Resolution Radar 20 © 2019 Cadence Design Systems, Inc. All rights reserved. Lidar Today

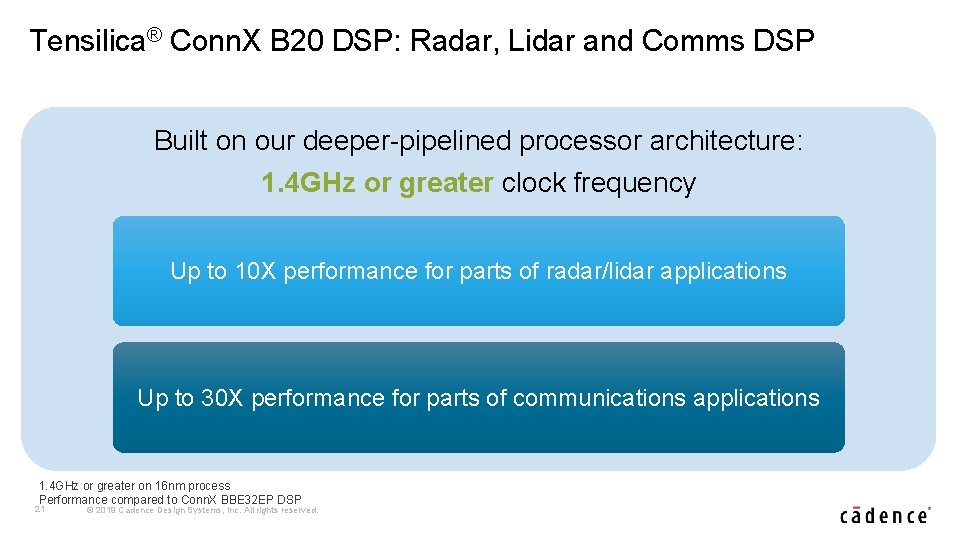

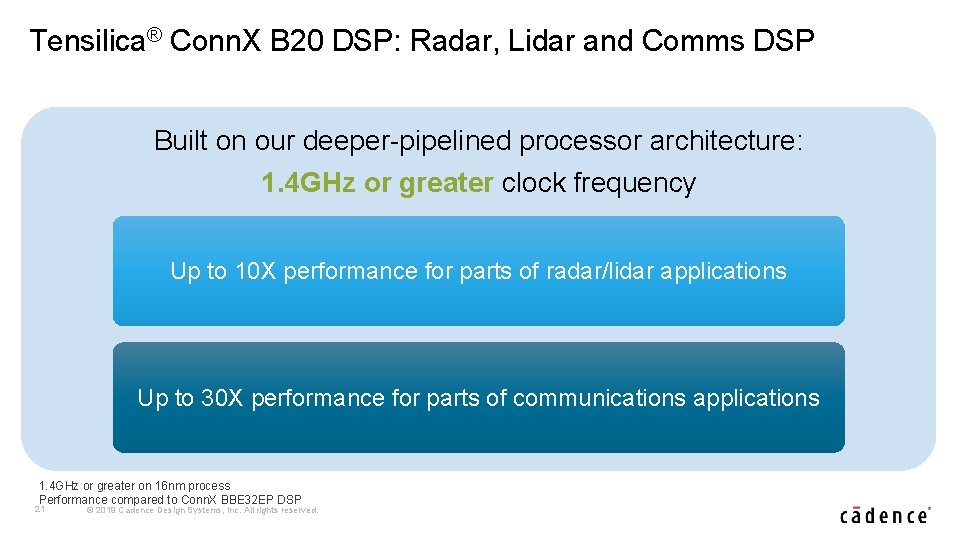

Tensilica® Conn. X B 20 DSP: Radar, Lidar and Comms DSP Built on our deeper-pipelined processor architecture: 1. 4 GHz or greater clock frequency Up to 10 X performance for parts of radar/lidar applications Up to 30 X performance for parts of communications applications 1. 4 GHz or greater on 16 nm process Performance compared to Conn. X BBE 32 EP DSP 21 © 2019 Cadence Design Systems, Inc. All rights reserved.

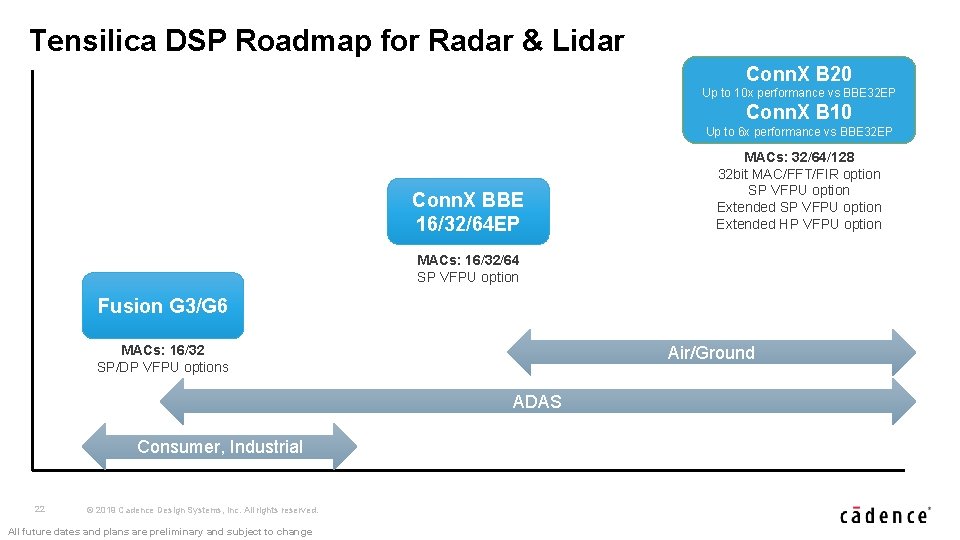

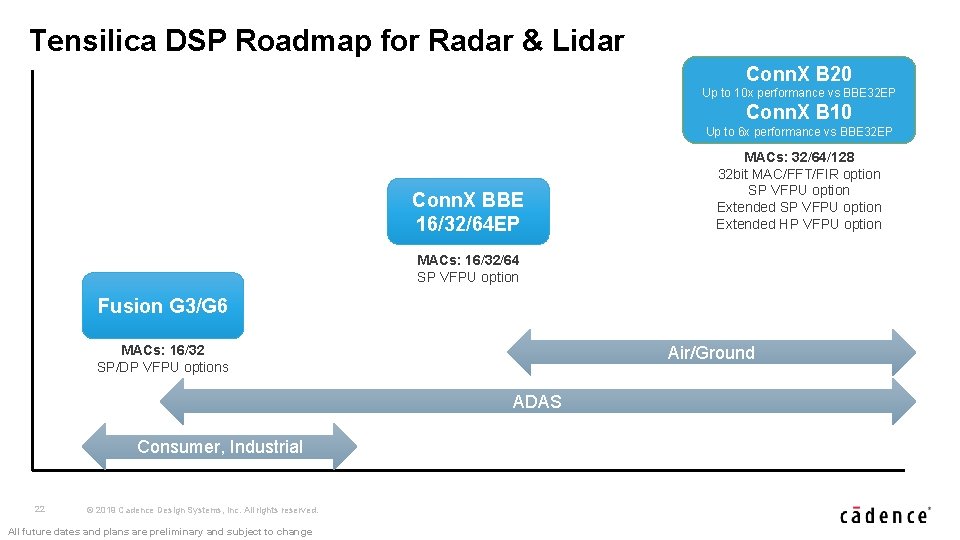

Tensilica DSP Roadmap for Radar & Lidar Conn. X B 20 Up to 10 x performance vs BBE 32 EP Conn. X B 10 Up to 6 x performance vs BBE 32 EP Conn. X BBE 16/32/64 EP MACs: 32/64/128 32 bit MAC/FFT/FIR option SP VFPU option Extended HP VFPU option MACs: 16/32/64 SP VFPU option Fusion G 3/G 6 MACs: 16/32 SP/DP VFPU options Air/Ground ADAS Consumer, Industrial 22 © 2019 Cadence Design Systems, Inc. All rights reserved. All future dates and plans are preliminary and subject to change

© 2019 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www. cadence. com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.