EntradaSada Princpios do hardware de ES Princpios do

- Slides: 60

Entrada/Saída • Princípios do hardware de E/S • Princípios do software de E/S • Camadas do software de E/S • Relógios • Gerenciamento de energia Pearson Education Sistemas Operacionais Modernos – 2ª Edição 1

Princípios do Hardware de E/S • Diversidade de dispositivos • Tipos básicos de dispositivos • Arquitetura de E/S – Introdução aos barramentos – Controladores de dispositivos • Comunicação SO (CPU) – Controlador • Controle de interrupção Pearson Education Sistemas Operacionais Modernos – 2ª Edição 2

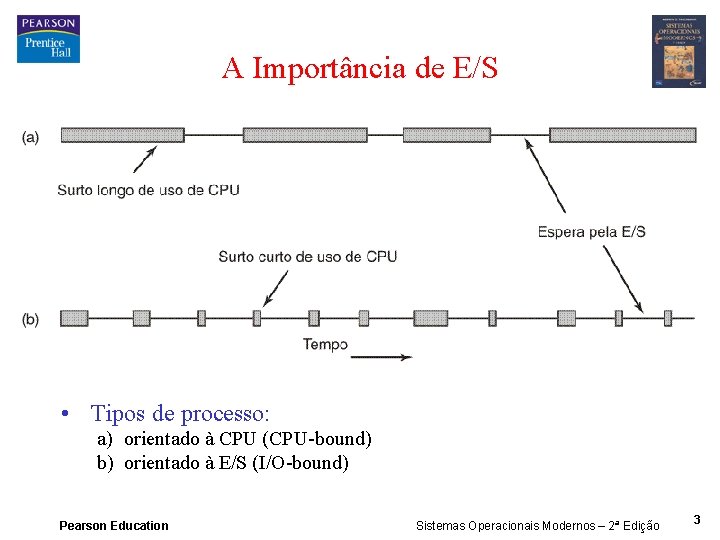

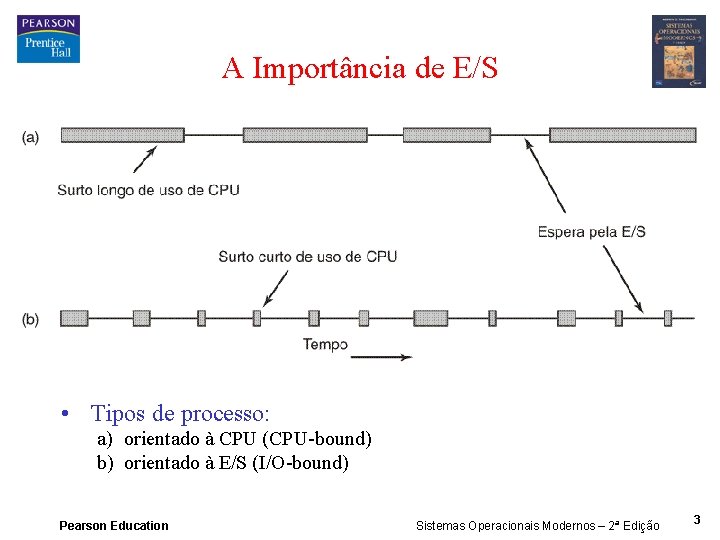

A Importância de E/S • Tipos de processo: a) orientado à CPU (CPU-bound) b) orientado à E/S (I/O-bound) Pearson Education Sistemas Operacionais Modernos – 2ª Edição 3

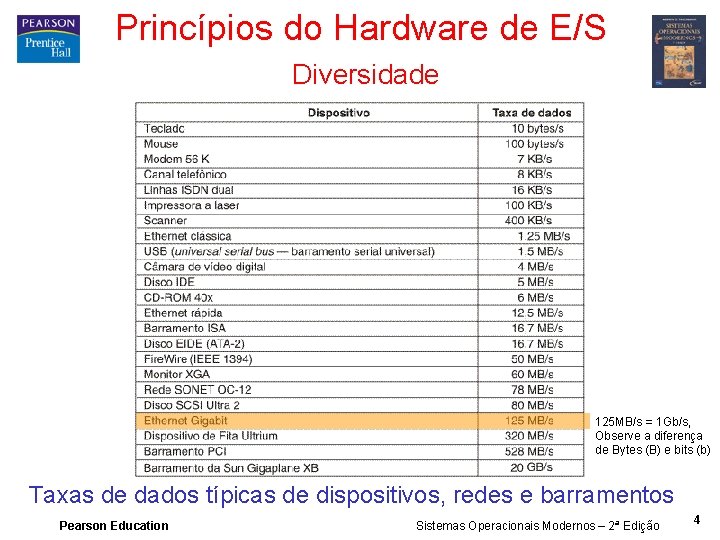

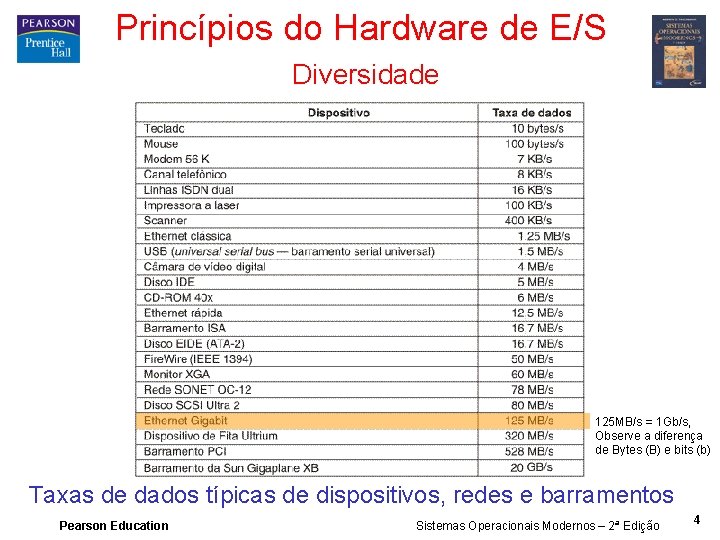

Princípios do Hardware de E/S Diversidade 125 MB/s = 1 Gb/s, Observe a diferença de Bytes (B) e bits (b) Taxas de dados típicas de dispositivos, redes e barramentos Pearson Education Sistemas Operacionais Modernos – 2ª Edição 4

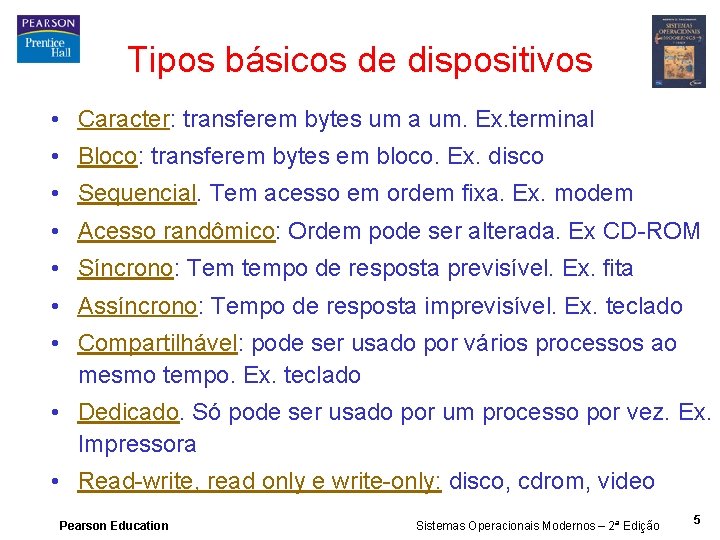

Tipos básicos de dispositivos • Caracter: transferem bytes um a um. Ex. terminal • Bloco: transferem bytes em bloco. Ex. disco • Sequencial. Tem acesso em ordem fixa. Ex. modem • Acesso randômico: Ordem pode ser alterada. Ex CD-ROM • Síncrono: Tem tempo de resposta previsível. Ex. fita • Assíncrono: Tempo de resposta imprevisível. Ex. teclado • Compartilhável: pode ser usado por vários processos ao mesmo tempo. Ex. teclado • Dedicado. Só pode ser usado por um processo por vez. Ex. Impressora • Read-write, read only e write-only: disco, cdrom, video Pearson Education Sistemas Operacionais Modernos – 2ª Edição 5

Princípios do Hardware de E/S ü Diversidade de dispositivos ü Tipos básicos de dispositivos • Arquitetura de E/S – Introdução aos barramentos – Controladores de dispositivos • Comunicação SO (CPU) – Controlador • Controle de interrupção Pearson Education Sistemas Operacionais Modernos – 2ª Edição 6

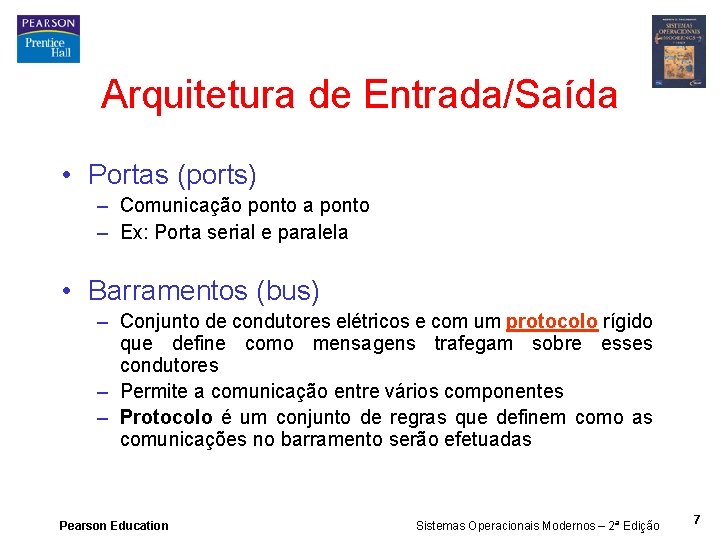

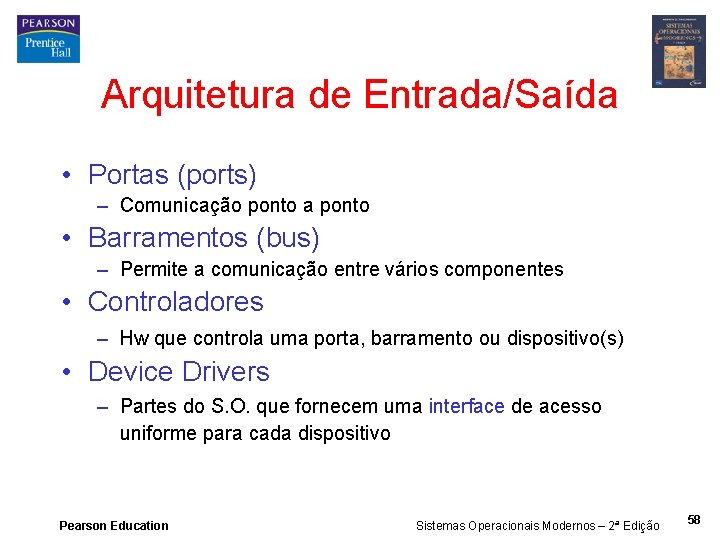

Arquitetura de Entrada/Saída • Portas (ports) – Comunicação ponto a ponto – Ex: Porta serial e paralela • Barramentos (bus) – Conjunto de condutores elétricos e com um protocolo rígido que define como mensagens trafegam sobre esses condutores – Permite a comunicação entre vários componentes – Protocolo é um conjunto de regras que definem como as comunicações no barramento serão efetuadas Pearson Education Sistemas Operacionais Modernos – 2ª Edição 7

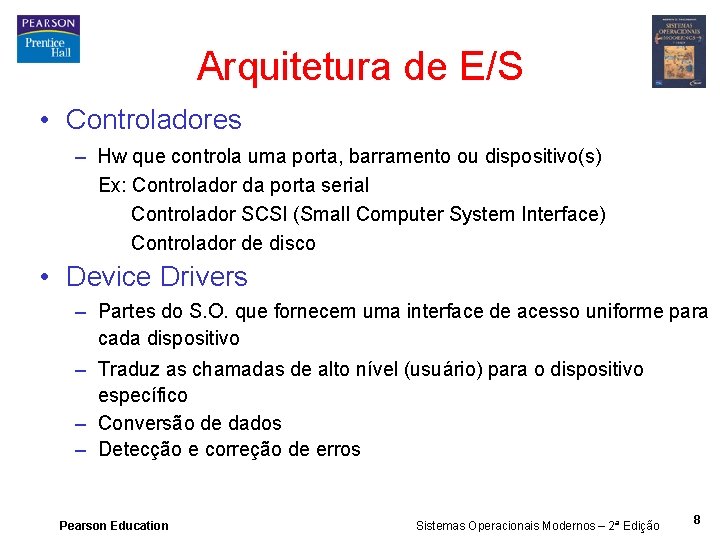

Arquitetura de E/S • Controladores – Hw que controla uma porta, barramento ou dispositivo(s) Ex: Controlador da porta serial Controlador SCSI (Small Computer System Interface) Controlador de disco • Device Drivers – Partes do S. O. que fornecem uma interface de acesso uniforme para cada dispositivo – Traduz as chamadas de alto nível (usuário) para o dispositivo específico – Conversão de dados – Detecção e correção de erros Pearson Education Sistemas Operacionais Modernos – 2ª Edição 8

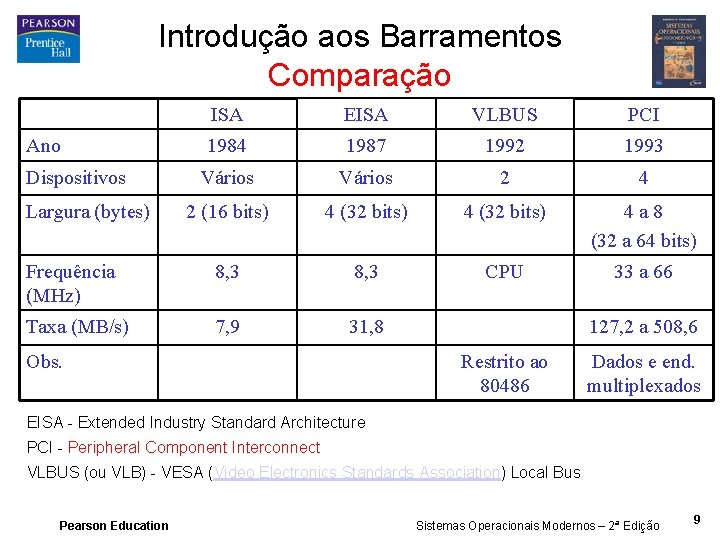

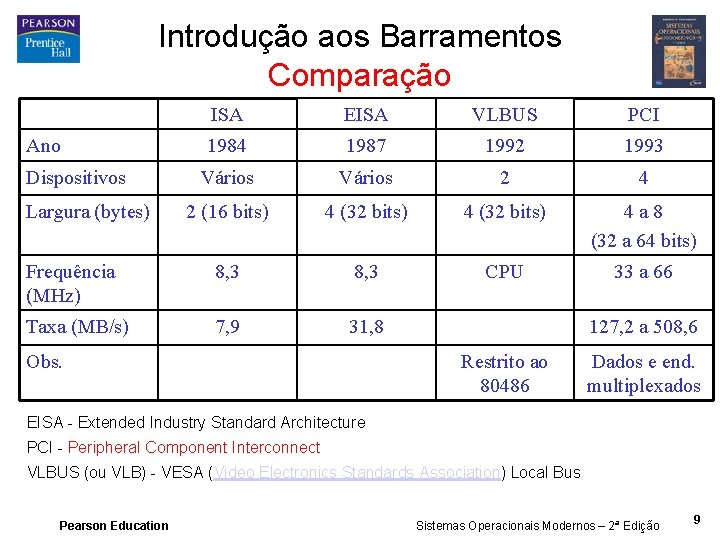

Introdução aos Barramentos Comparação ISA EISA VLBUS PCI 1984 1987 1992 1993 Vários 2 4 2 (16 bits) 4 (32 bits) 4 a 8 (32 a 64 bits) Frequência (MHz) 8, 3 CPU 33 a 66 Taxa (MB/s) 7, 9 31, 8 Ano Dispositivos Largura (bytes) Obs. 127, 2 a 508, 6 Restrito ao 80486 Dados e end. multiplexados EISA - Extended Industry Standard Architecture PCI - Peripheral Component Interconnect VLBUS (ou VLB) - VESA (Video Electronics Standards Association) Local Bus Pearson Education Sistemas Operacionais Modernos – 2ª Edição 9

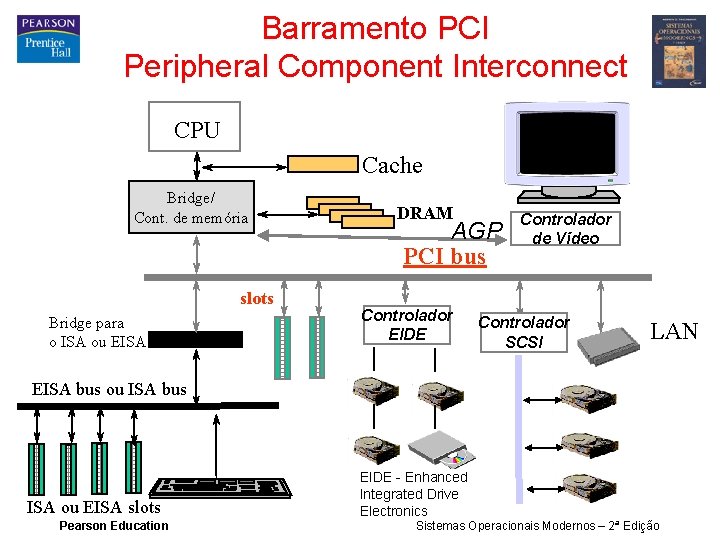

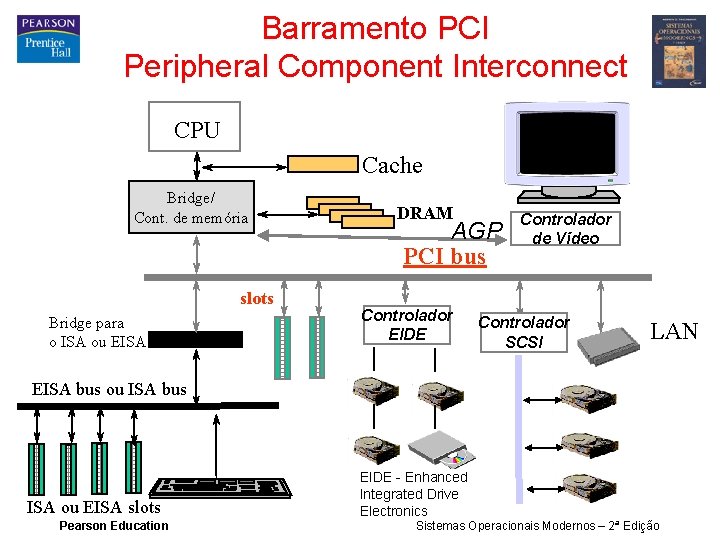

Barramento PCI Peripheral Component Interconnect CPU Cache Bridge/ Cont. de memória slots Bridge para o ISA ou EISA DRAM AGP PCI bus Controlador EIDE Controlador de Vídeo Controlador SCSI LAN EISA bus ou ISA bus ISA ou EISA slots Pearson Education EIDE - Enhanced Integrated Drive Electronics Sistemas Operacionais Modernos – 2ª Edição

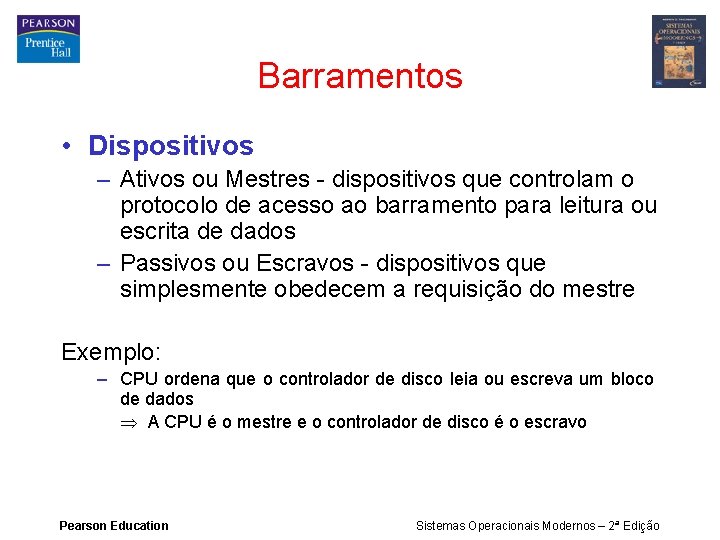

Barramentos • Dispositivos – Ativos ou Mestres - dispositivos que controlam o protocolo de acesso ao barramento para leitura ou escrita de dados – Passivos ou Escravos - dispositivos que simplesmente obedecem a requisição do mestre Exemplo: – CPU ordena que o controlador de disco leia ou escreva um bloco de dados A CPU é o mestre e o controlador de disco é o escravo Pearson Education Sistemas Operacionais Modernos – 2ª Edição

Princípios do Hardware de E/S ü Diversidade de dispositivos ü Tipos básicos de dispositivos • Arquitetura de E/S üIntrodução aos barramentos – Controladores de dispositivos • Comunicação SO (CPU) – Controlador • Controle de interrupção Pearson Education Sistemas Operacionais Modernos – 2ª Edição 12

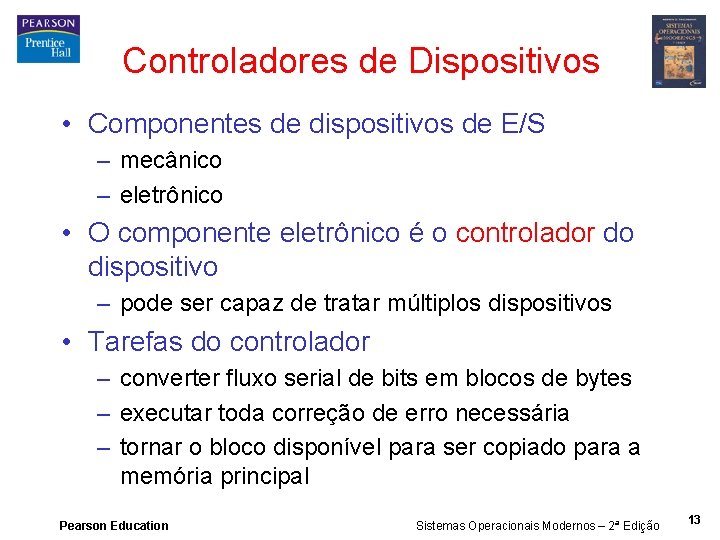

Controladores de Dispositivos • Componentes de dispositivos de E/S – mecânico – eletrônico • O componente eletrônico é o controlador do dispositivo – pode ser capaz de tratar múltiplos dispositivos • Tarefas do controlador – converter fluxo serial de bits em blocos de bytes – executar toda correção de erro necessária – tornar o bloco disponível para ser copiado para a memória principal Pearson Education Sistemas Operacionais Modernos – 2ª Edição 13

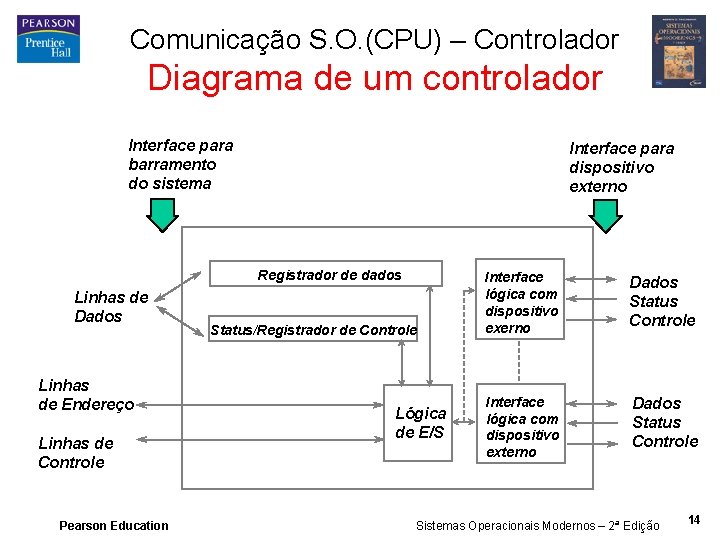

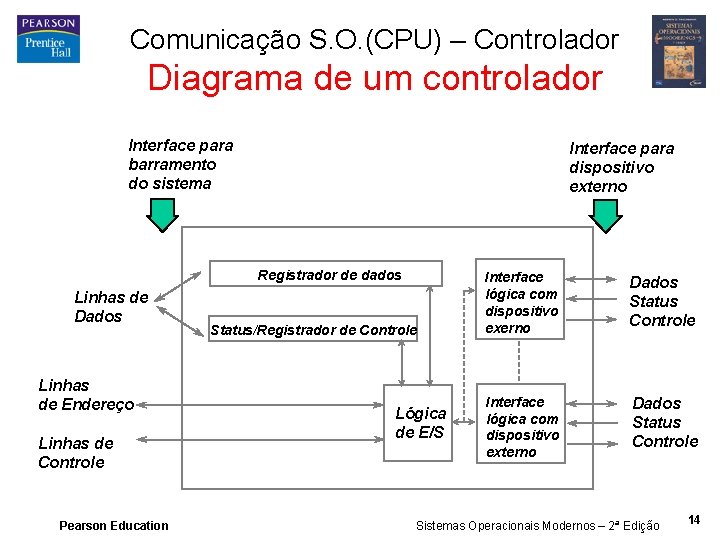

Comunicação S. O. (CPU) – Controlador Diagrama de um controlador Interface para barramento do sistema Interface para dispositivo externo Registrador de dados Linhas de Dados Linhas de Endereço Linhas de Controle Pearson Education Status/Registrador de Controle Lógica de E/S Interface lógica com dispositivo exerno Dados Status Controle Interface lógica com dispositivo externo Dados Status Controle Sistemas Operacionais Modernos – 2ª Edição 14

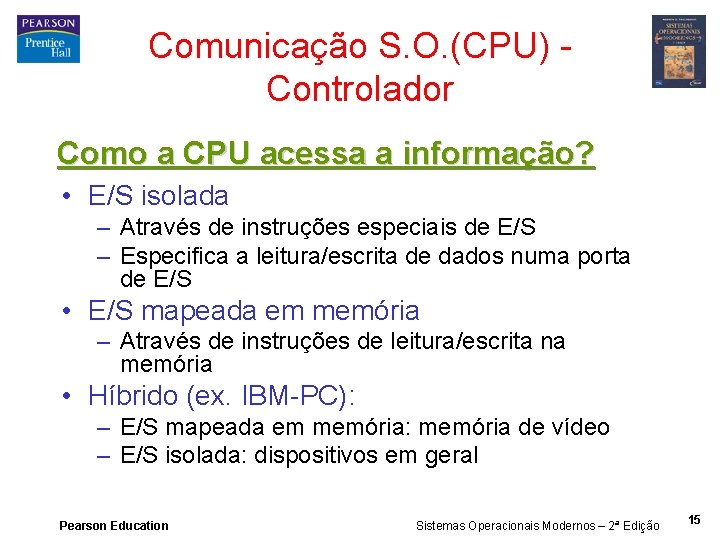

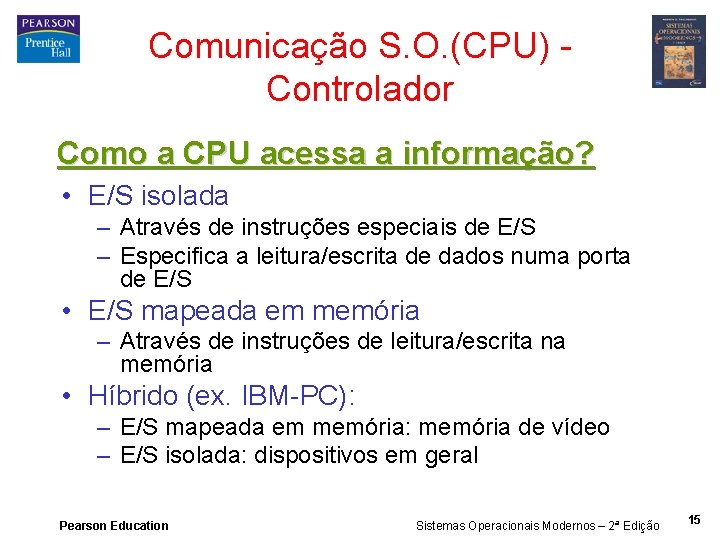

Comunicação S. O. (CPU) Controlador Como a CPU acessa a informação? • E/S isolada – Através de instruções especiais de E/S – Especifica a leitura/escrita de dados numa porta de E/S • E/S mapeada em memória – Através de instruções de leitura/escrita na memória • Híbrido (ex. IBM-PC): – E/S mapeada em memória: memória de vídeo – E/S isolada: dispositivos em geral Pearson Education Sistemas Operacionais Modernos – 2ª Edição 15

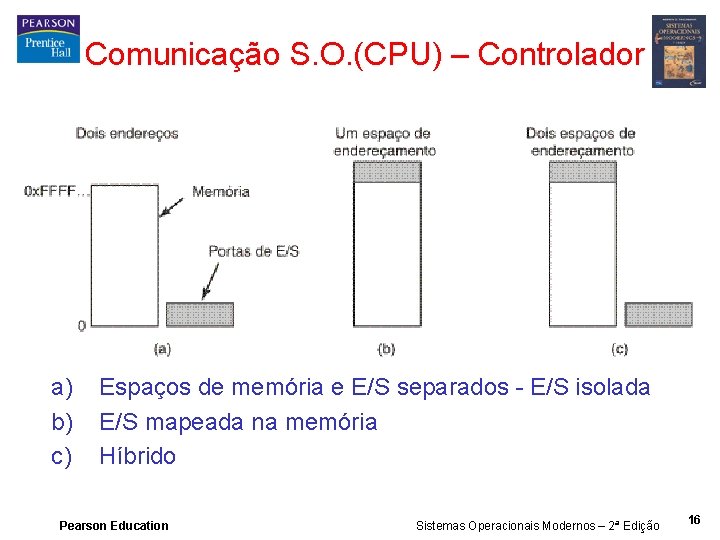

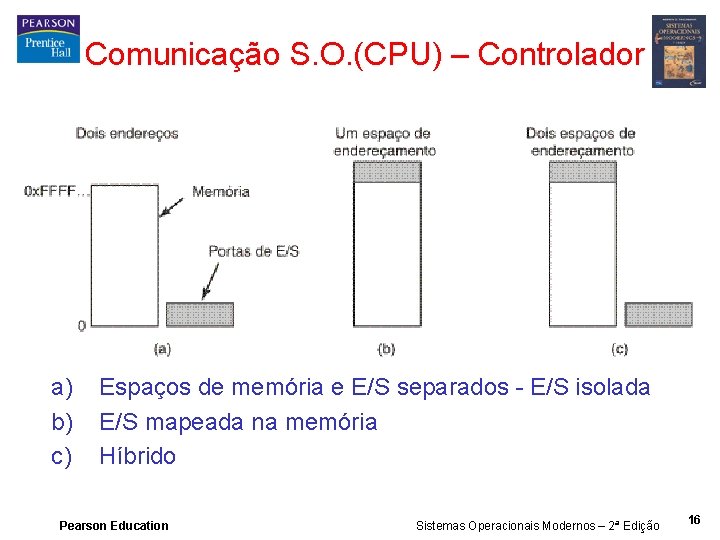

Comunicação S. O. (CPU) – Controlador a) b) c) Espaços de memória e E/S separados - E/S isolada E/S mapeada na memória Híbrido Pearson Education Sistemas Operacionais Modernos – 2ª Edição 16

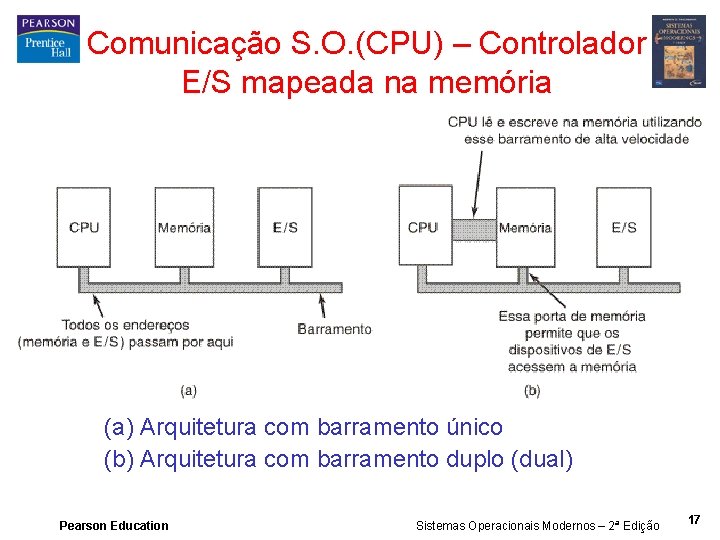

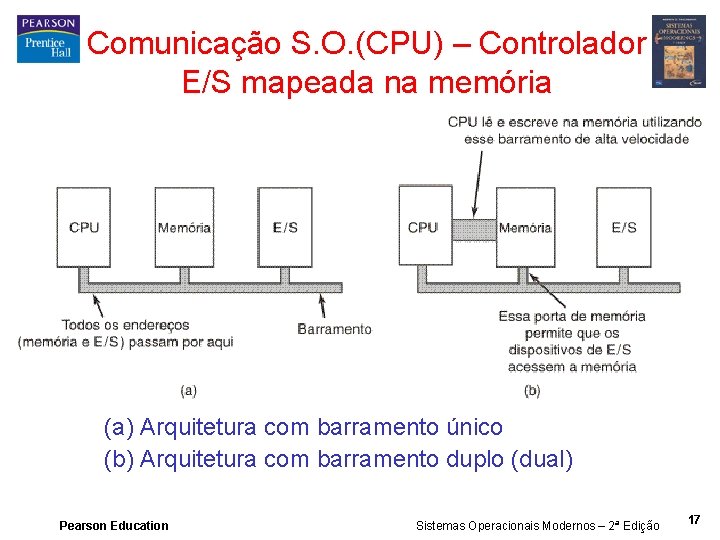

Comunicação S. O. (CPU) – Controlador E/S mapeada na memória (a) Arquitetura com barramento único (b) Arquitetura com barramento duplo (dual) Pearson Education Sistemas Operacionais Modernos – 2ª Edição 17

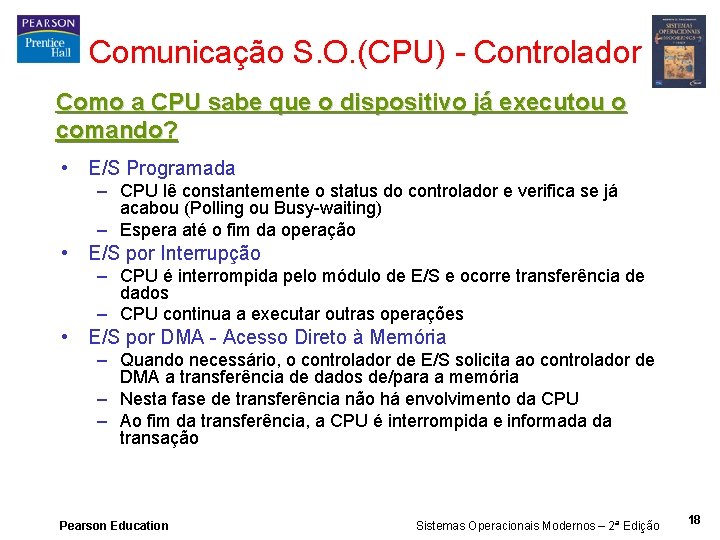

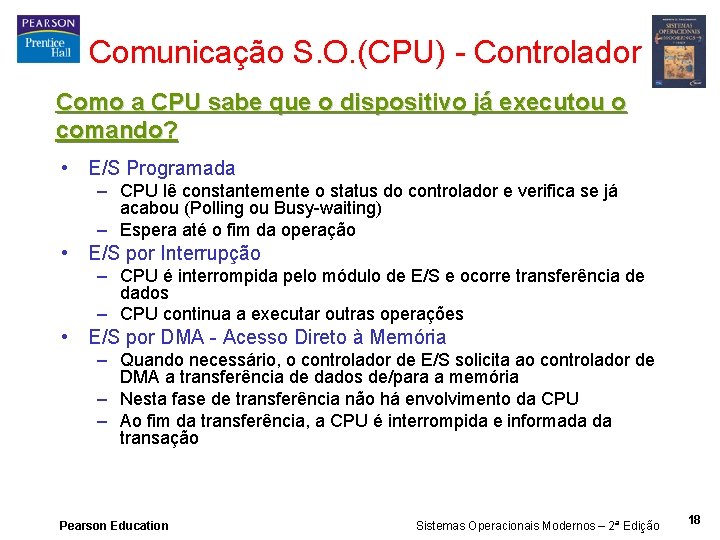

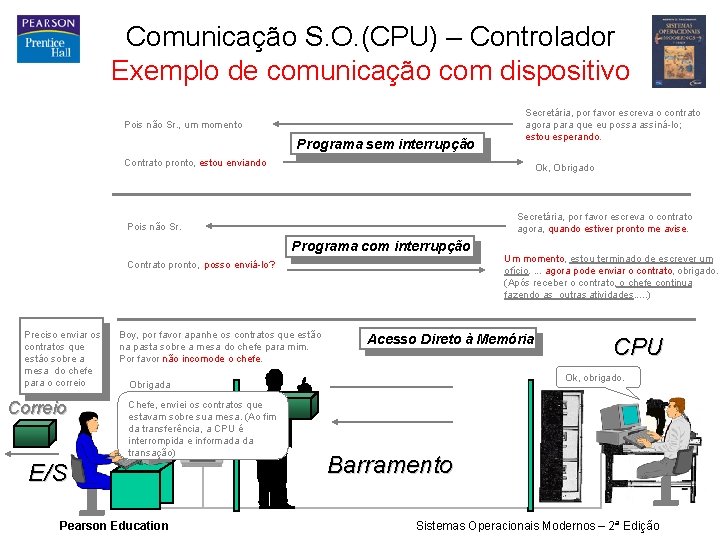

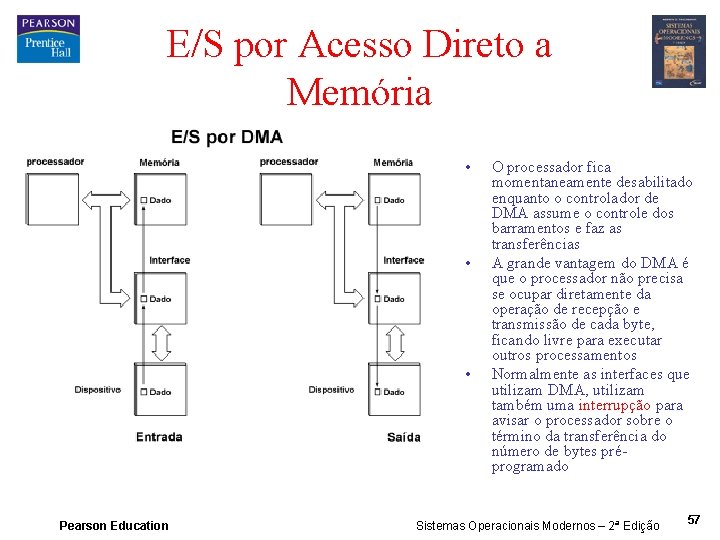

Comunicação S. O. (CPU) - Controlador Como a CPU sabe que o dispositivo já executou o comando? • E/S Programada – CPU lê constantemente o status do controlador e verifica se já acabou (Polling ou Busy-waiting) – Espera até o fim da operação • E/S por Interrupção – CPU é interrompida pelo módulo de E/S e ocorre transferência de dados – CPU continua a executar outras operações • E/S por DMA - Acesso Direto à Memória – Quando necessário, o controlador de E/S solicita ao controlador de DMA a transferência de dados de/para a memória – Nesta fase de transferência não há envolvimento da CPU – Ao fim da transferência, a CPU é interrompida e informada da transação Pearson Education Sistemas Operacionais Modernos – 2ª Edição 18

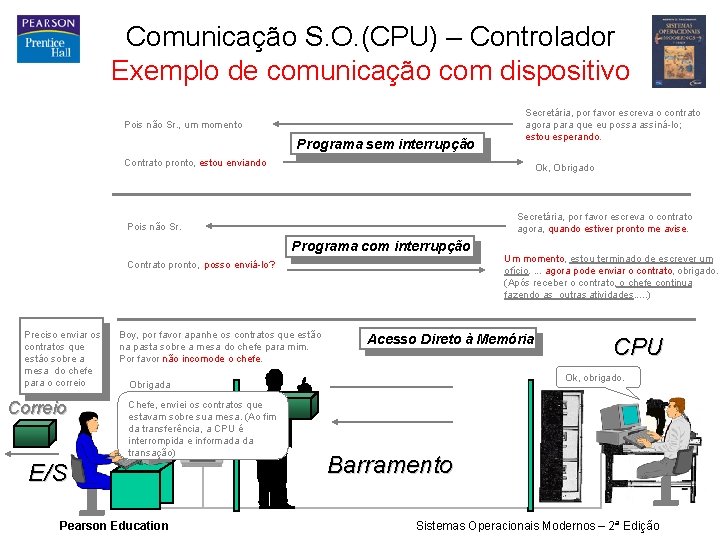

Comunicação S. O. (CPU) – Controlador Exemplo de comunicação com dispositivo Pois não Sr. , um momento Programa sem interrupção Secretária, por favor escreva o contrato agora para que eu possa assiná-lo; estou esperando. Contrato pronto, estou enviando Ok, Obrigado Secretária, por favor escreva o contrato agora, quando estiver pronto me avise. Pois não Sr. Programa com interrupção Contrato pronto, posso enviá-lo? Preciso enviar os contratos que estáo sobre a mesa do chefe para o correio Correio Boy, por favor apanhe os contratos que estão na pasta sobre a mesa do chefe para mim. Por favor não incomode o chefe. Acesso Direto à Memória E/S Pearson Education CPU Ok, obrigado. Obrigada Chefe, enviei os contratos que estavam sobre sua mesa. (Ao fim da transferência, a CPU é interrompida e informada da transação) Um momento, estou terminado de escrever um ofício. . agora pode enviar o contrato, obrigado. (Após receber o contrato, o chefe continua fazendo as outras atividades. . . ) Barramento Sistemas Operacionais Modernos – 2ª Edição

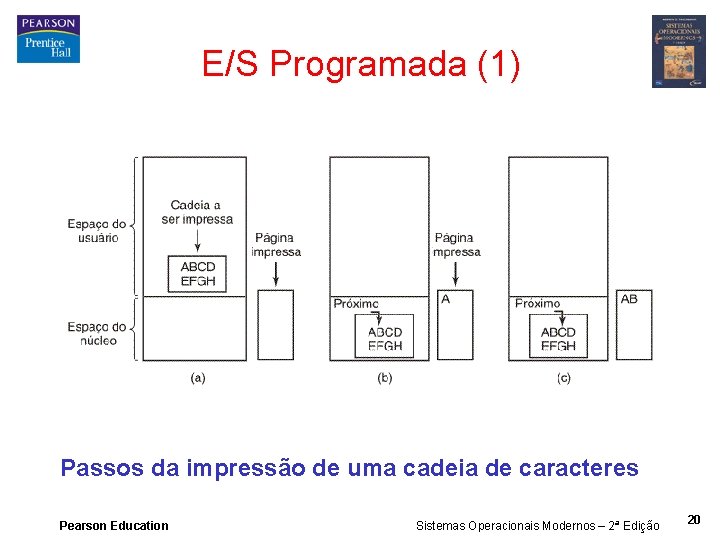

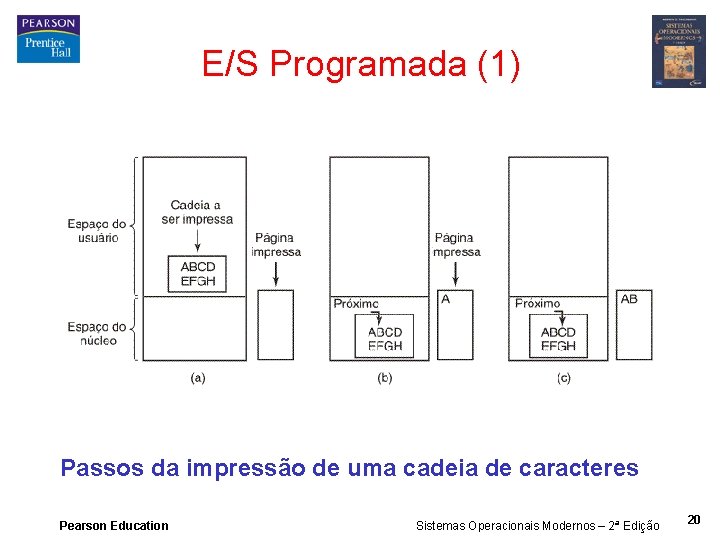

E/S Programada (1) Passos da impressão de uma cadeia de caracteres Pearson Education Sistemas Operacionais Modernos – 2ª Edição 20

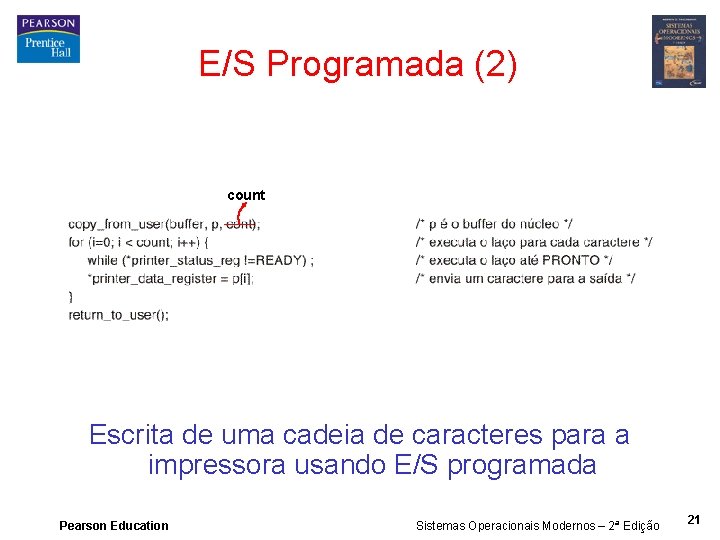

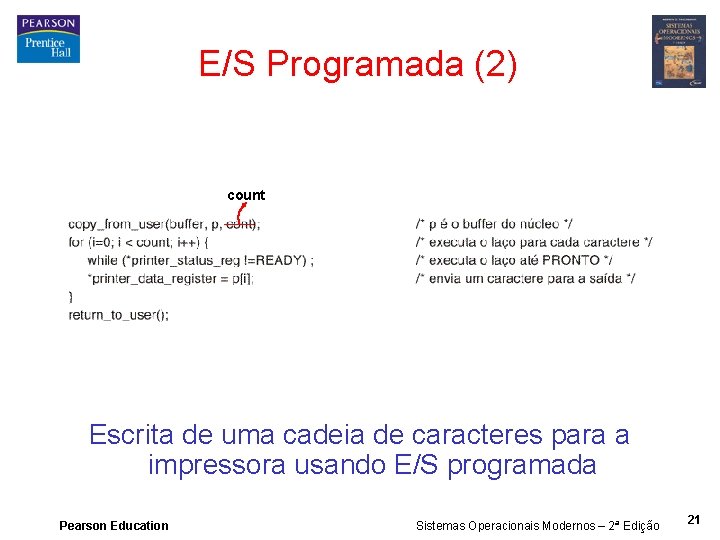

E/S Programada (2) count Escrita de uma cadeia de caracteres para a impressora usando E/S programada Pearson Education Sistemas Operacionais Modernos – 2ª Edição 21

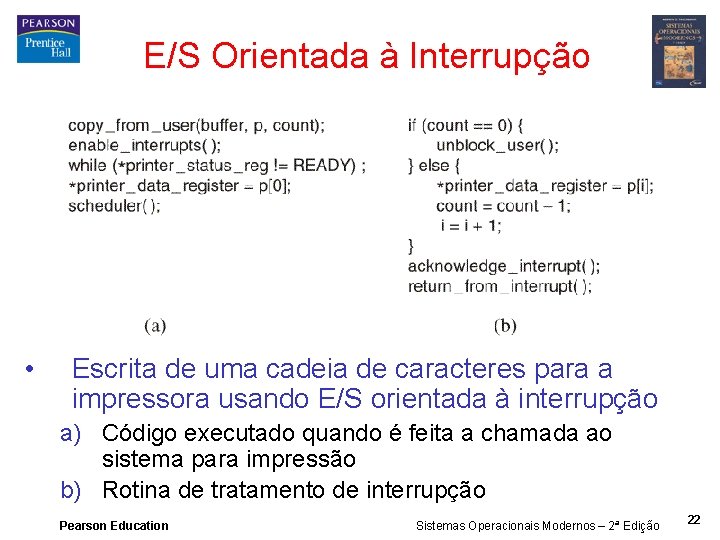

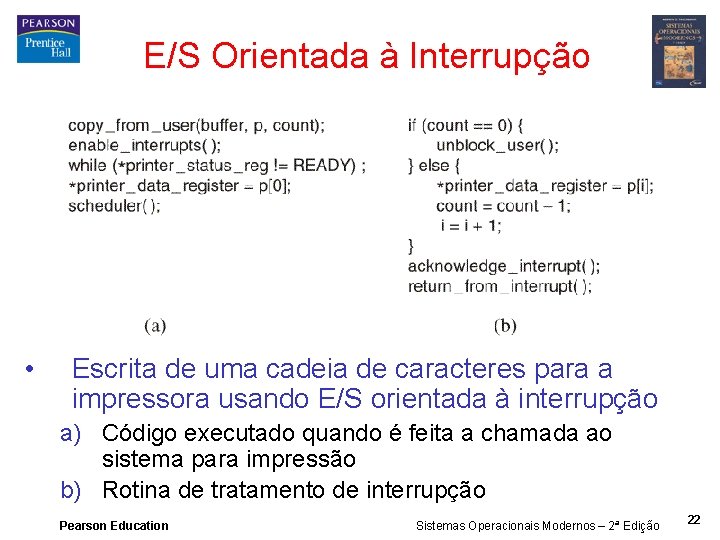

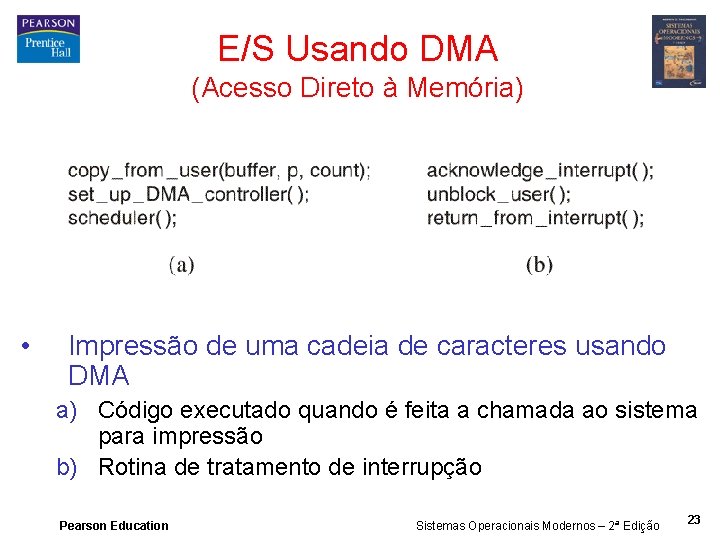

E/S Orientada à Interrupção • Escrita de uma cadeia de caracteres para a impressora usando E/S orientada à interrupção a) Código executado quando é feita a chamada ao sistema para impressão b) Rotina de tratamento de interrupção Pearson Education Sistemas Operacionais Modernos – 2ª Edição 22

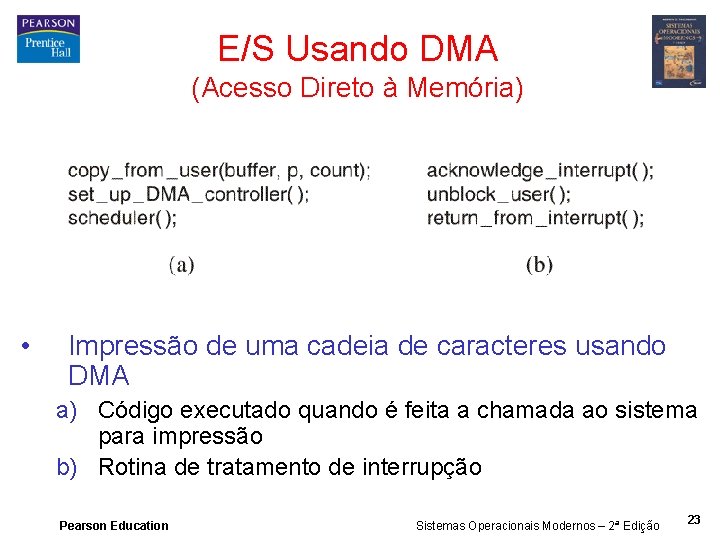

E/S Usando DMA (Acesso Direto à Memória) • Impressão de uma cadeia de caracteres usando DMA a) Código executado quando é feita a chamada ao sistema para impressão b) Rotina de tratamento de interrupção Pearson Education Sistemas Operacionais Modernos – 2ª Edição 23

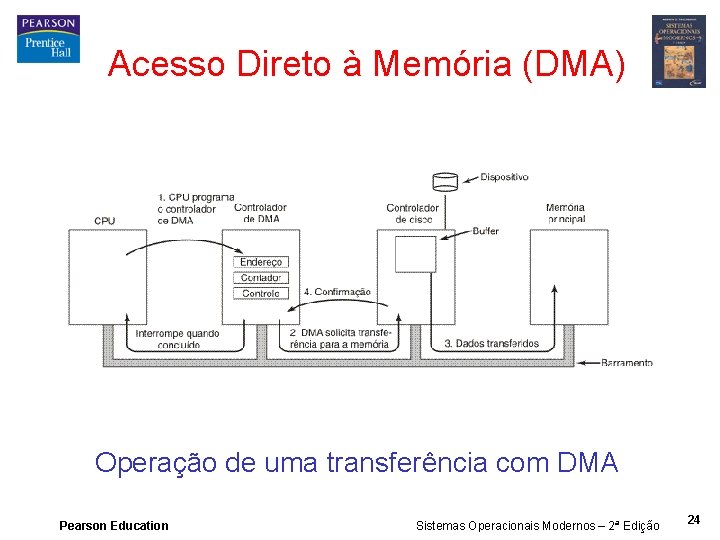

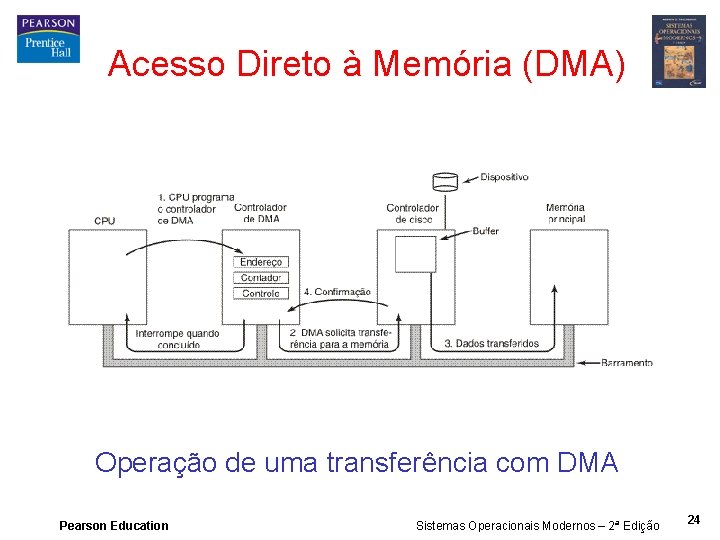

Acesso Direto à Memória (DMA) Operação de uma transferência com DMA Pearson Education Sistemas Operacionais Modernos – 2ª Edição 24

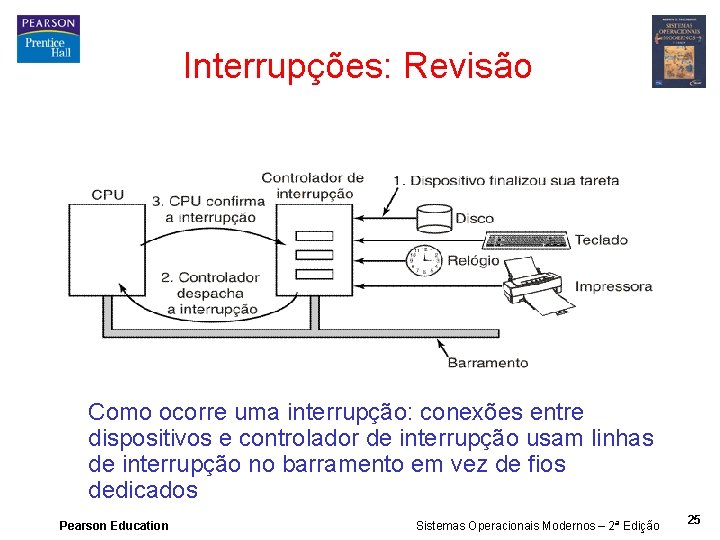

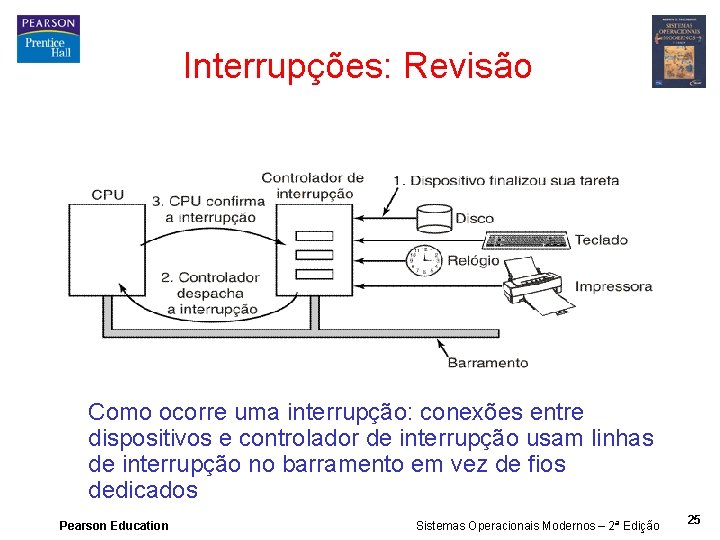

Interrupções: Revisão Como ocorre uma interrupção: conexões entre dispositivos e controlador de interrupção usam linhas de interrupção no barramento em vez de fios dedicados Pearson Education Sistemas Operacionais Modernos – 2ª Edição 25

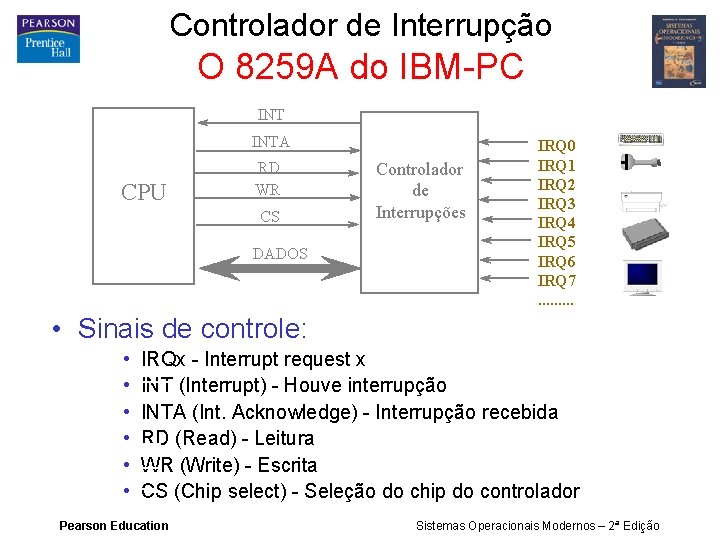

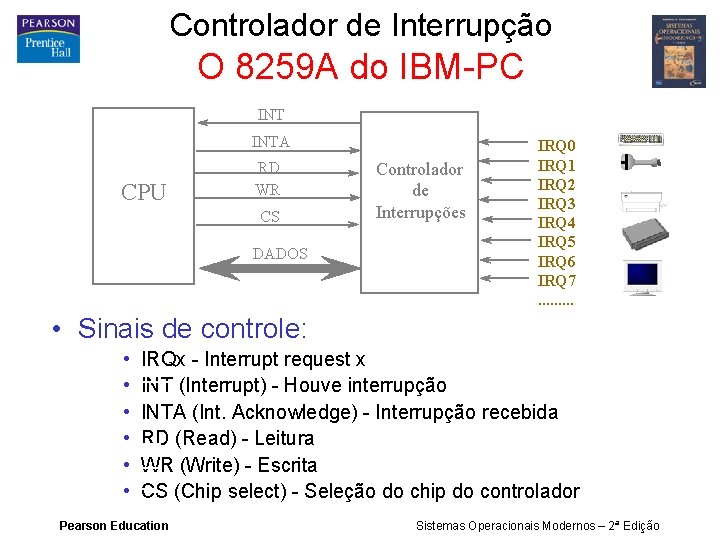

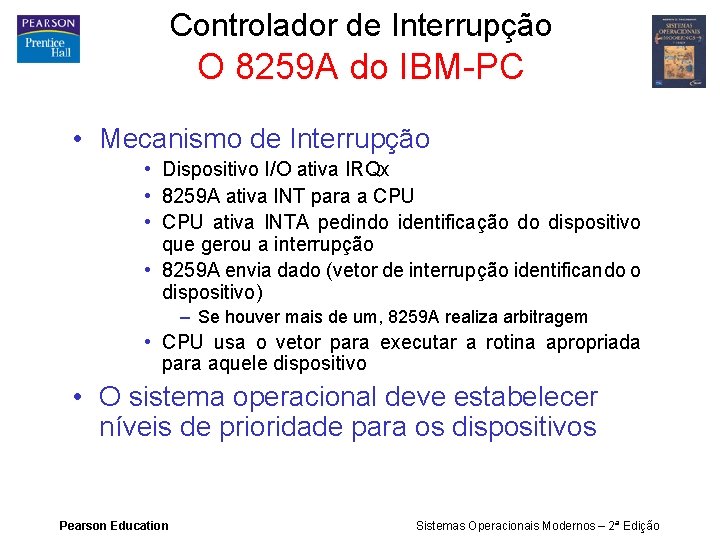

Controlador de Interrupção O 8259 A do IBM-PC INTA CPU RD WR CS DADOS Controlador de Interrupções IRQ 0 IRQ 1 IRQ 2 IRQ 3 IRQ 4 IRQ 5 IRQ 6 IRQ 7. . • Sinais de controle: • • • IRQx - Interrupt request x INT (Interrupt) - Houve interrupção INTA (Int. Acknowledge) - Interrupção recebida RD (Read) - Leitura WR (Write) - Escrita CS (Chip select) - Seleção do chip do controlador Pearson Education Sistemas Operacionais Modernos – 2ª Edição

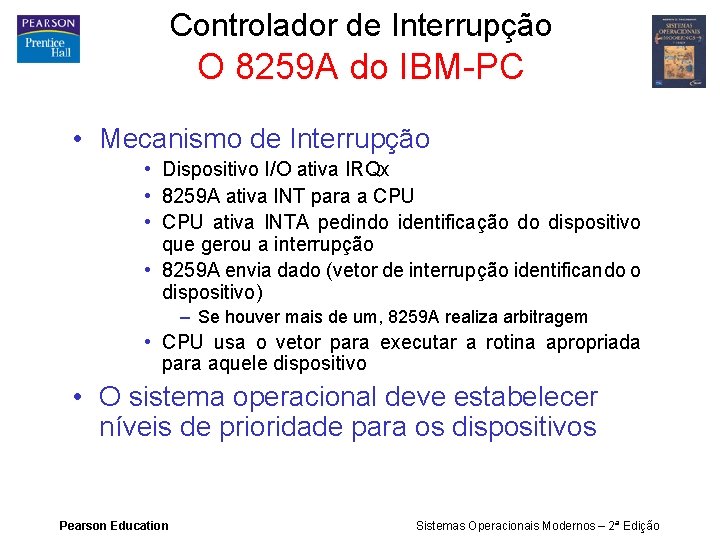

Controlador de Interrupção O 8259 A do IBM-PC • Mecanismo de Interrupção • Dispositivo I/O ativa IRQx • 8259 A ativa INT para a CPU • CPU ativa INTA pedindo identificação do dispositivo que gerou a interrupção • 8259 A envia dado (vetor de interrupção identificando o dispositivo) – Se houver mais de um, 8259 A realiza arbitragem • CPU usa o vetor para executar a rotina apropriada para aquele dispositivo • O sistema operacional deve estabelecer níveis de prioridade para os dispositivos Pearson Education Sistemas Operacionais Modernos – 2ª Edição

Para Enfatizar: A Importância da Interrupção O Elo Hardware-Software Pearson Education Sistemas Operacionais Modernos – 2ª Edição 28

Motivação • Para controlar entrada e saída de dados, não é interessante que a CPU tenha que ficar continuamente monitorando o status de dispositivos como discos ou teclados • O mecanismo de interrupções permite que o hardware "chame a atenção" da CPU quando há algo a ser feito Pearson Education Sistemas Operacionais Modernos – 2ª Edição 29

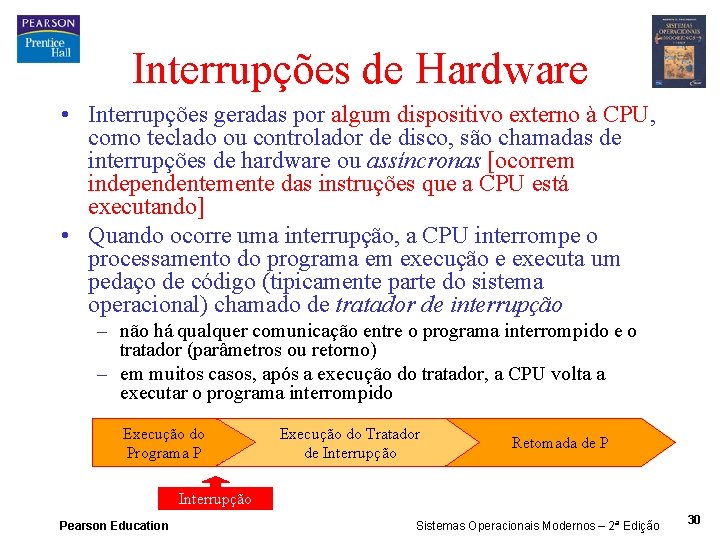

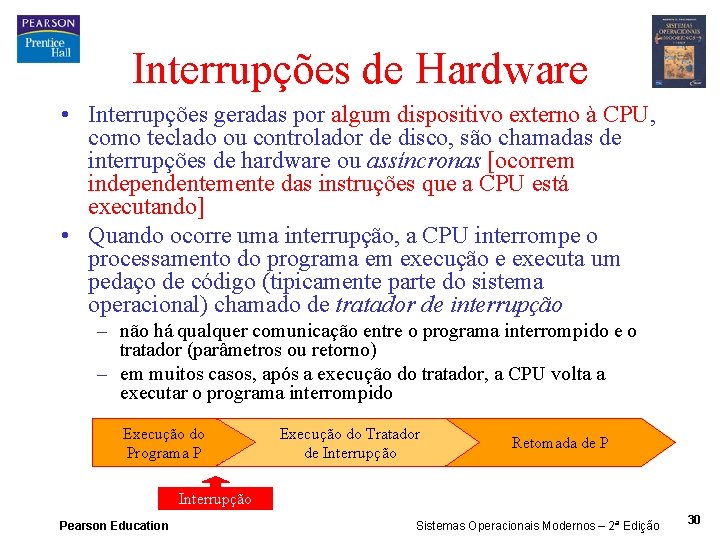

Interrupções de Hardware • Interrupções geradas por algum dispositivo externo à CPU, como teclado ou controlador de disco, são chamadas de interrupções de hardware ou assíncronas [ocorrem independentemente das instruções que a CPU está executando] • Quando ocorre uma interrupção, a CPU interrompe o processamento do programa em execução e executa um pedaço de código (tipicamente parte do sistema operacional) chamado de tratador de interrupção – não há qualquer comunicação entre o programa interrompido e o tratador (parâmetros ou retorno) – em muitos casos, após a execução do tratador, a CPU volta a executar o programa interrompido Execução do Programa P Execução do Tratador de Interrupção Retomada de P Interrupção Pearson Education Sistemas Operacionais Modernos – 2ª Edição 30

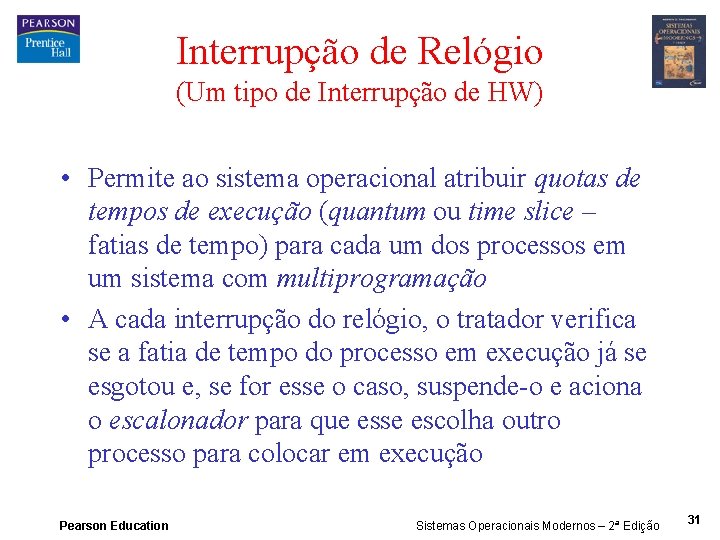

Interrupção de Relógio (Um tipo de Interrupção de HW) • Permite ao sistema operacional atribuir quotas de tempos de execução (quantum ou time slice – fatias de tempo) para cada um dos processos em um sistema com multiprogramação • A cada interrupção do relógio, o tratador verifica se a fatia de tempo do processo em execução já se esgotou e, se for esse o caso, suspende-o e aciona o escalonador para que esse escolha outro processo para colocar em execução Pearson Education Sistemas Operacionais Modernos – 2ª Edição 31

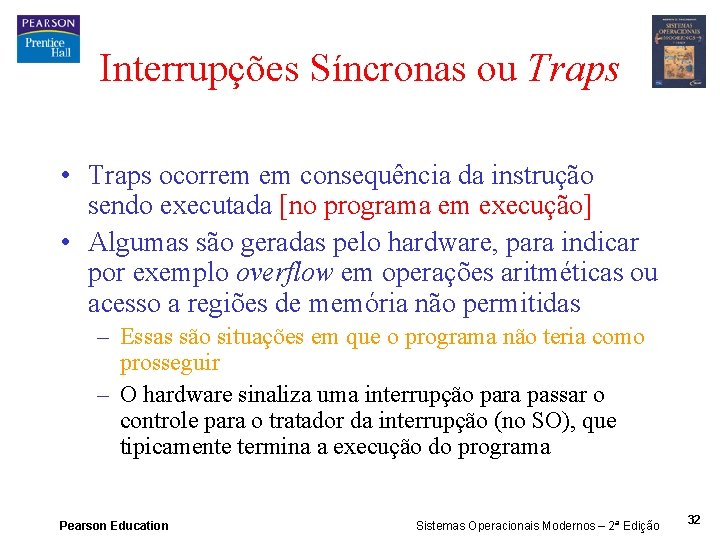

Interrupções Síncronas ou Traps • Traps ocorrem em consequência da instrução sendo executada [no programa em execução] • Algumas são geradas pelo hardware, para indicar por exemplo overflow em operações aritméticas ou acesso a regiões de memória não permitidas – Essas são situações em que o programa não teria como prosseguir – O hardware sinaliza uma interrupção para passar o controle para o tratador da interrupção (no SO), que tipicamente termina a execução do programa Pearson Education Sistemas Operacionais Modernos – 2ª Edição 32

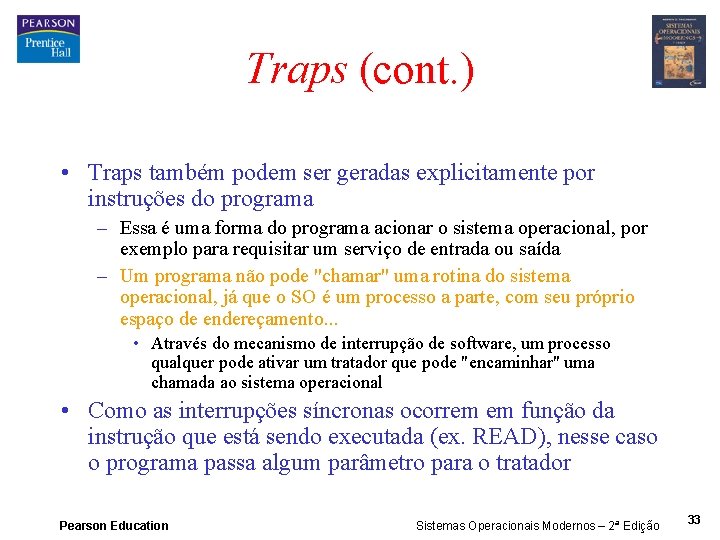

Traps (cont. ) • Traps também podem ser geradas explicitamente por instruções do programa – Essa é uma forma do programa acionar o sistema operacional, por exemplo para requisitar um serviço de entrada ou saída – Um programa não pode "chamar" uma rotina do sistema operacional, já que o SO é um processo a parte, com seu próprio espaço de endereçamento. . . • Através do mecanismo de interrupção de software, um processo qualquer pode ativar um tratador que pode "encaminhar" uma chamada ao sistema operacional • Como as interrupções síncronas ocorrem em função da instrução que está sendo executada (ex. READ), nesse caso o programa passa algum parâmetro para o tratador Pearson Education Sistemas Operacionais Modernos – 2ª Edição 33

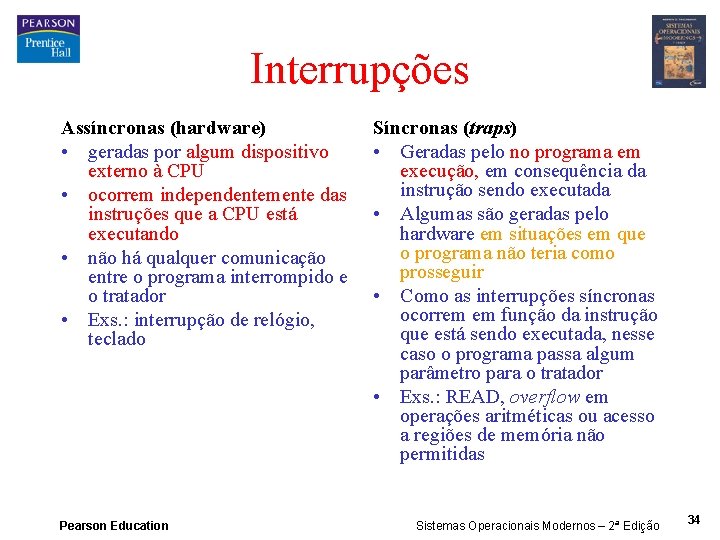

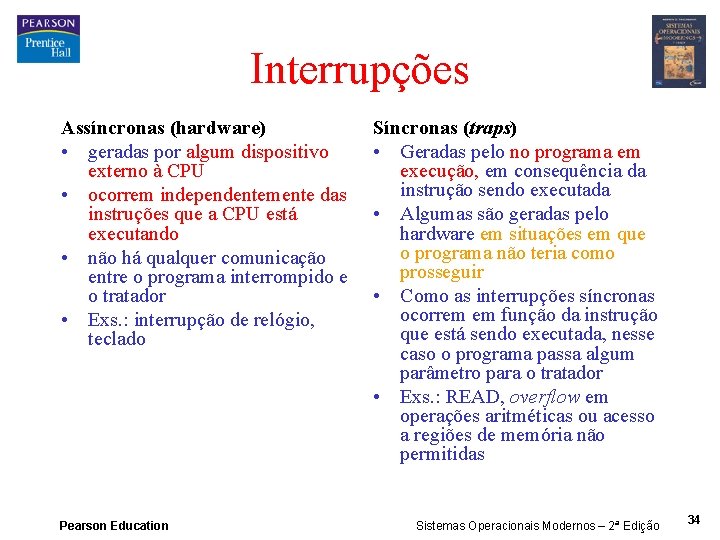

Interrupções Assíncronas (hardware) • geradas por algum dispositivo externo à CPU • ocorrem independentemente das instruções que a CPU está executando • não há qualquer comunicação entre o programa interrompido e o tratador • Exs. : interrupção de relógio, teclado Pearson Education Síncronas (traps) • Geradas pelo no programa em execução, em consequência da instrução sendo executada • Algumas são geradas pelo hardware em situações em que o programa não teria como prosseguir • Como as interrupções síncronas ocorrem em função da instrução que está sendo executada, nesse caso o programa passa algum parâmetro para o tratador • Exs. : READ, overflow em operações aritméticas ou acesso a regiões de memória não permitidas Sistemas Operacionais Modernos – 2ª Edição 34

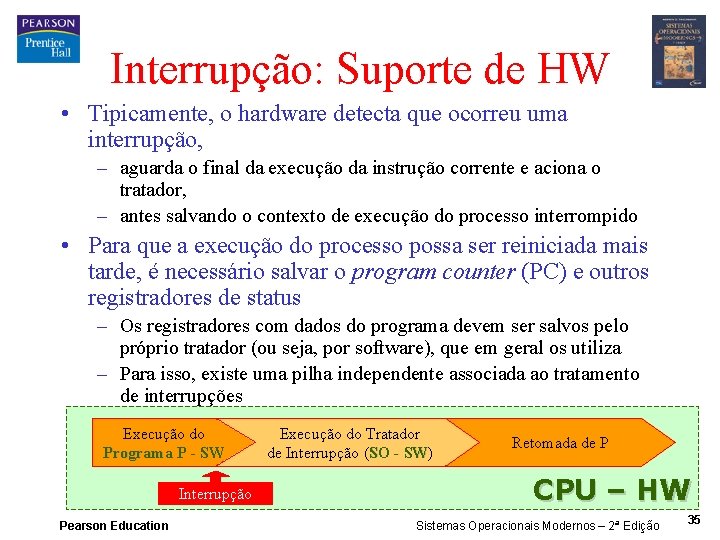

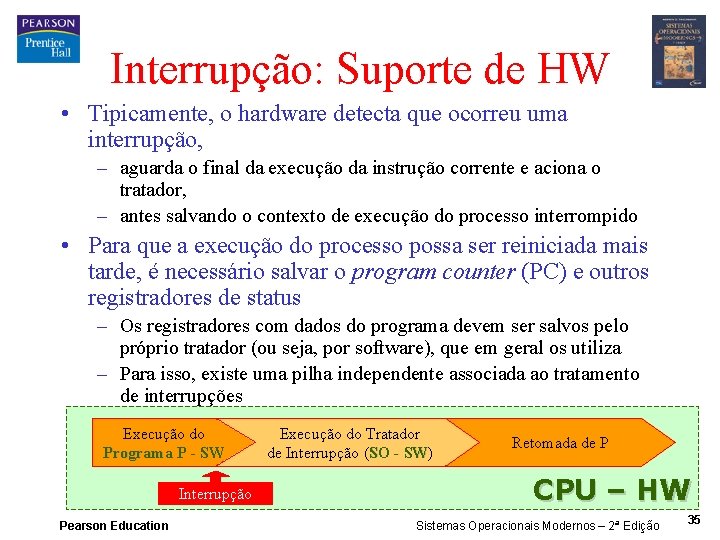

Interrupção: Suporte de HW • Tipicamente, o hardware detecta que ocorreu uma interrupção, – aguarda o final da execução da instrução corrente e aciona o tratador, – antes salvando o contexto de execução do processo interrompido • Para que a execução do processo possa ser reiniciada mais tarde, é necessário salvar o program counter (PC) e outros registradores de status – Os registradores com dados do programa devem ser salvos pelo próprio tratador (ou seja, por software), que em geral os utiliza – Para isso, existe uma pilha independente associada ao tratamento de interrupções Execução do Programa P - SW Interrupção Pearson Education Execução do Tratador de Interrupção (SO - SW) SW Retomada de P CPU – HW Sistemas Operacionais Modernos – 2ª Edição 35

Entrada/Saída üPrincípios do hardware de E/S • Princípios do software de E/S • Camadas do software de E/S • Gerenciamento de energia Pearson Education Sistemas Operacionais Modernos – 2ª Edição 36

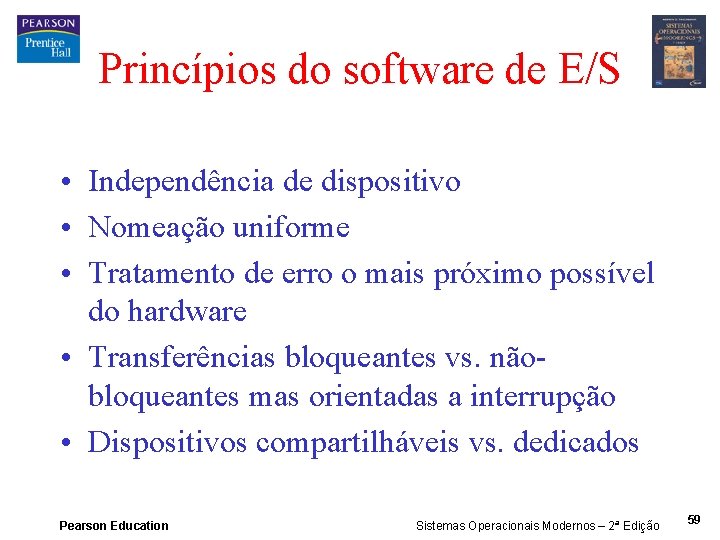

Princípios do Software de E/S Objetivos do Software de E/S (1) • Independência de dispositivo – Programas podem acessar qualquer dispositivo de E/S sem especificar previamente qual (disquete, disco rígido ou CD-ROM) • Nomeação uniforme – Nome de um arquivo ou dispositivo pode ser uma cadeia de caracteres ou um número inteiro que é independente do dispositivo • Tratamento de erro – Trata o mais próximo possível do hardware Pearson Education Sistemas Operacionais Modernos – 2ª Edição 37

Objetivos do Software de E/S (2) • Transferências Síncronas vs. Assíncronas – transferências bloqueantes vs. orientadas a interrupção – utilização de buffer para armazenamento temporário – dados provenientes de um dispositivo muitas vezes não podem ser armazenados diretamente em seu destino final – buffer, “broker”, … • Dispositivos Compartilháveis vs. Dedicados – discos são compartilháveis – unidades de fita não são Pearson Education Sistemas Operacionais Modernos – 2ª Edição 38

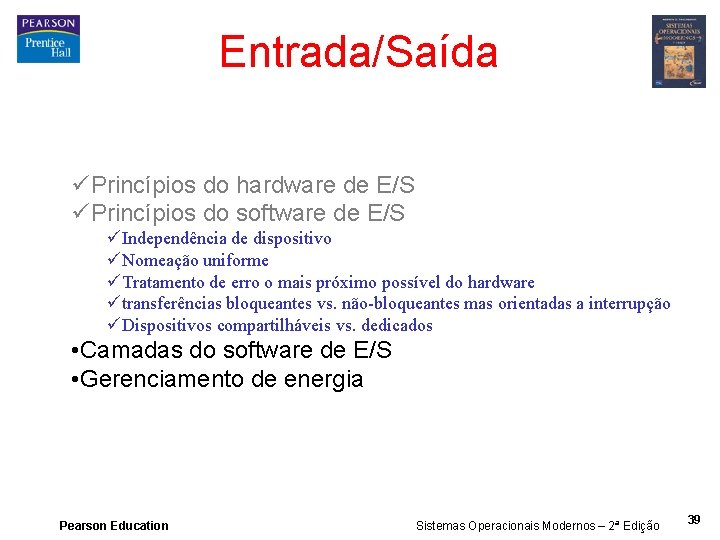

Entrada/Saída üPrincípios do hardware de E/S üPrincípios do software de E/S üIndependência de dispositivo üNomeação uniforme üTratamento de erro o mais próximo possível do hardware ütransferências bloqueantes vs. não-bloqueantes mas orientadas a interrupção üDispositivos compartilháveis vs. dedicados • Camadas do software de E/S • Gerenciamento de energia Pearson Education Sistemas Operacionais Modernos – 2ª Edição 39

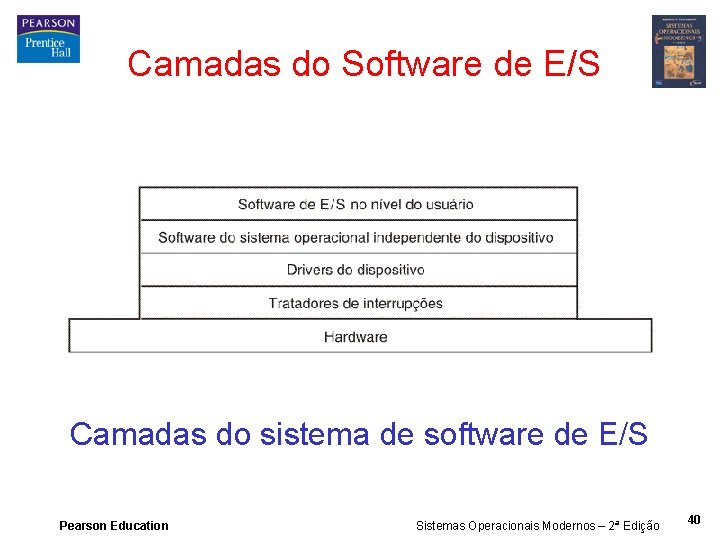

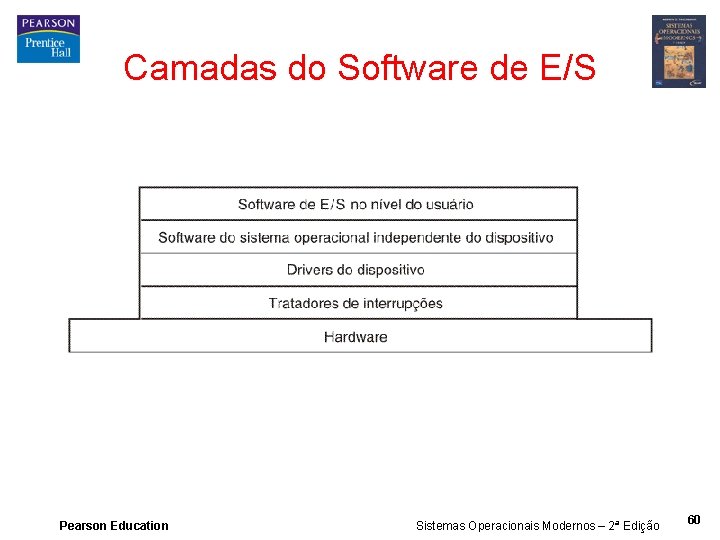

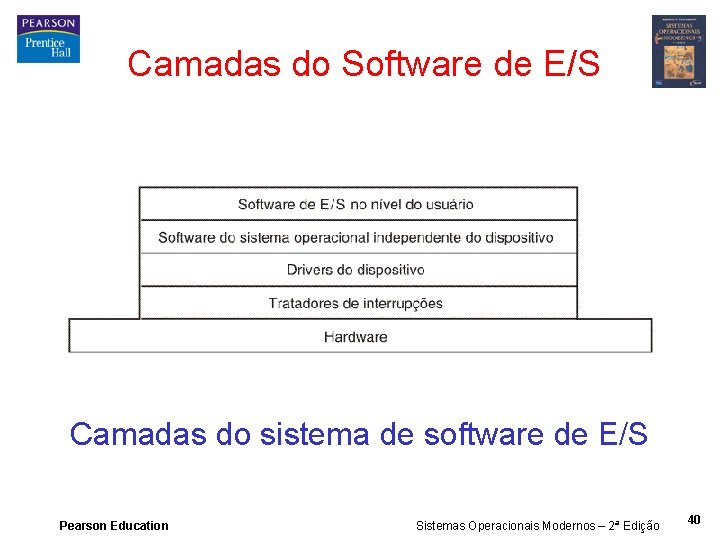

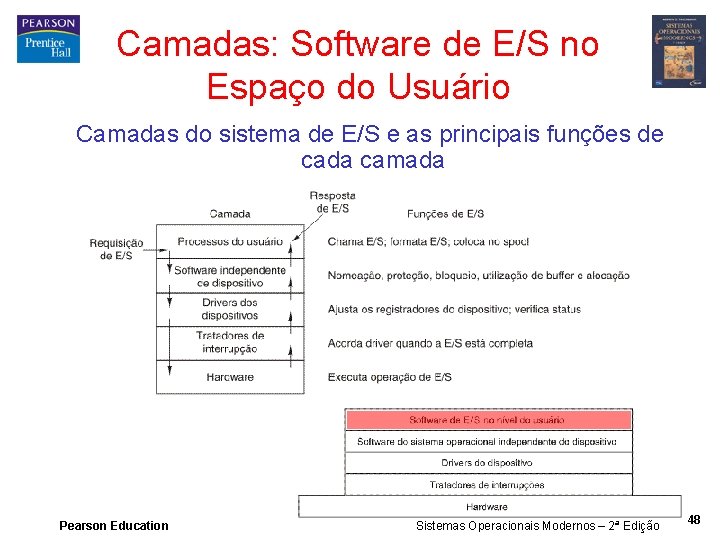

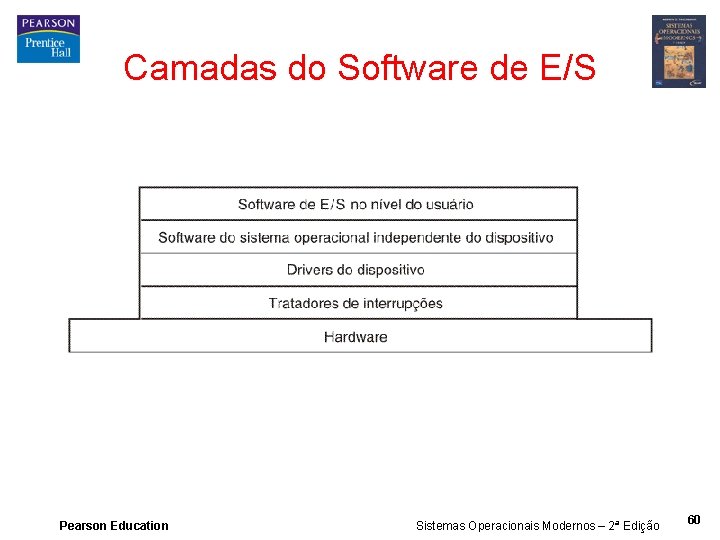

Camadas do Software de E/S Camadas do sistema de software de E/S Pearson Education Sistemas Operacionais Modernos – 2ª Edição 40

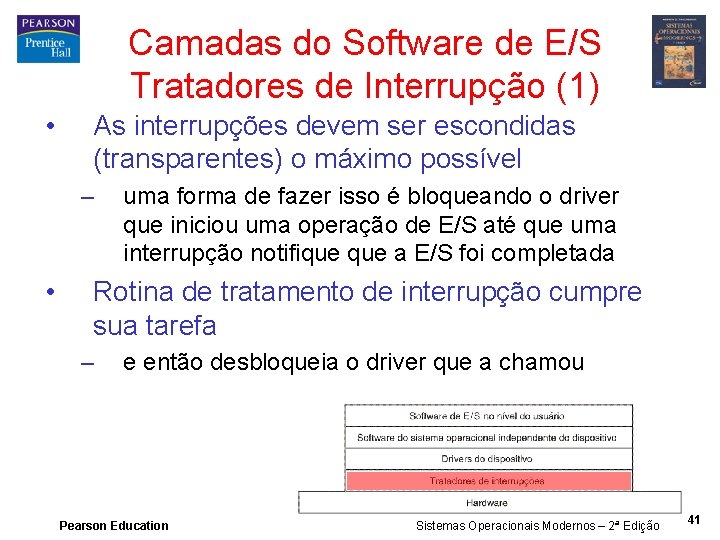

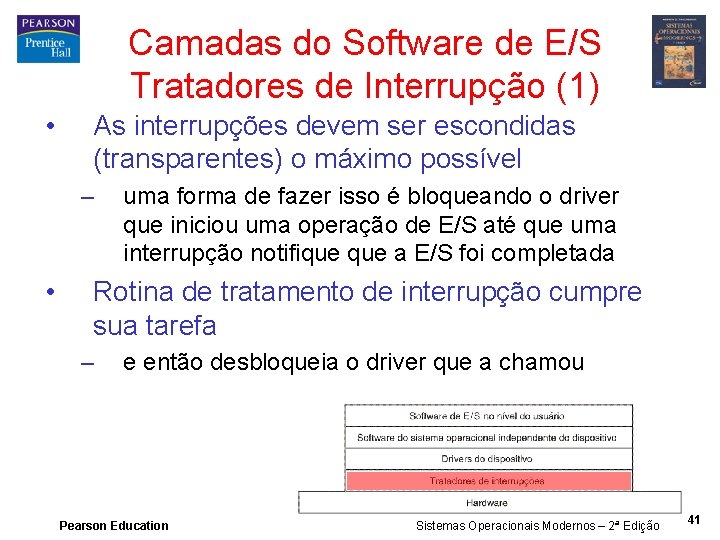

Camadas do Software de E/S Tratadores de Interrupção (1) • As interrupções devem ser escondidas (transparentes) o máximo possível – • uma forma de fazer isso é bloqueando o driver que iniciou uma operação de E/S até que uma interrupção notifique a E/S foi completada Rotina de tratamento de interrupção cumpre sua tarefa – e então desbloqueia o driver que a chamou Pearson Education Sistemas Operacionais Modernos – 2ª Edição 41

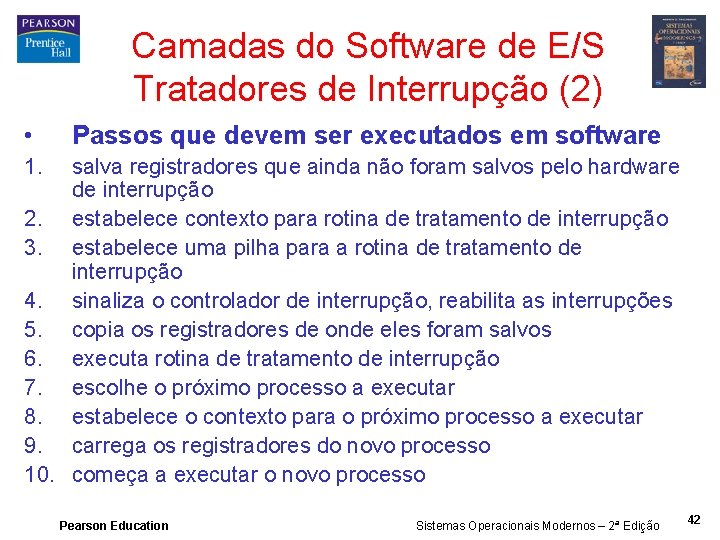

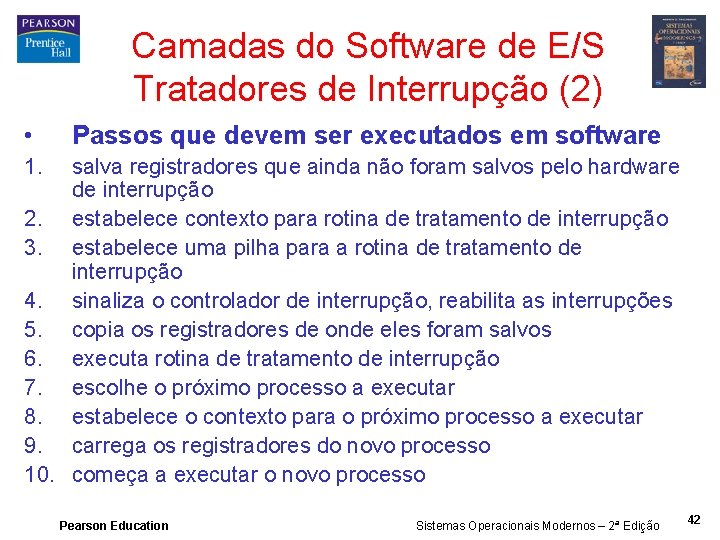

Camadas do Software de E/S Tratadores de Interrupção (2) • Passos que devem ser executados em software 1. salva registradores que ainda não foram salvos pelo hardware de interrupção 2. estabelece contexto para rotina de tratamento de interrupção 3. estabelece uma pilha para a rotina de tratamento de interrupção 4. sinaliza o controlador de interrupção, reabilita as interrupções 5. copia os registradores de onde eles foram salvos 6. executa rotina de tratamento de interrupção 7. escolhe o próximo processo a executar 8. estabelece o contexto para o próximo processo a executar 9. carrega os registradores do novo processo 10. começa a executar o novo processo Pearson Education Sistemas Operacionais Modernos – 2ª Edição 42

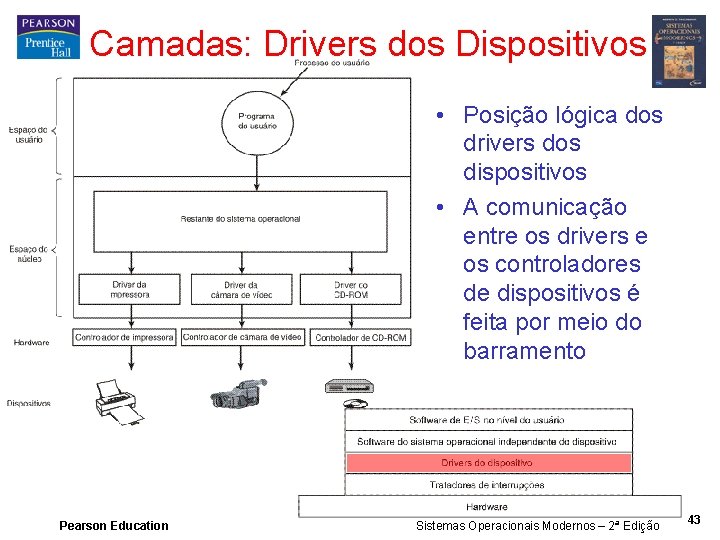

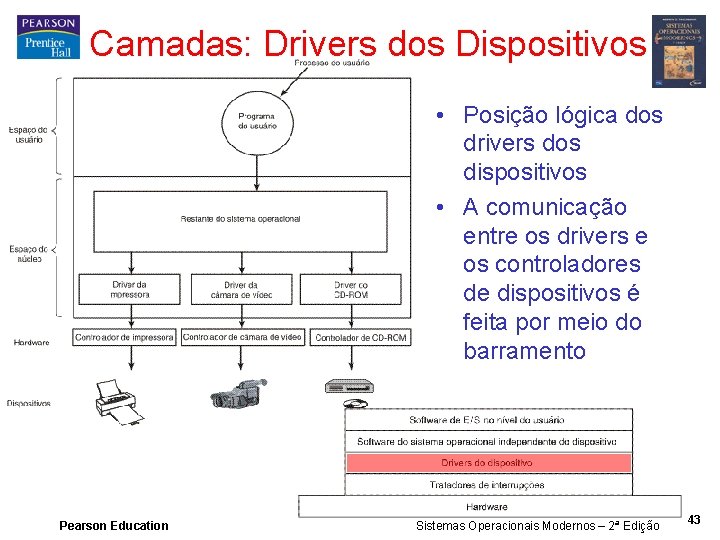

Camadas: Drivers dos Dispositivos • Posição lógica dos drivers dos dispositivos • A comunicação entre os drivers e os controladores de dispositivos é feita por meio do barramento Pearson Education Sistemas Operacionais Modernos – 2ª Edição 43

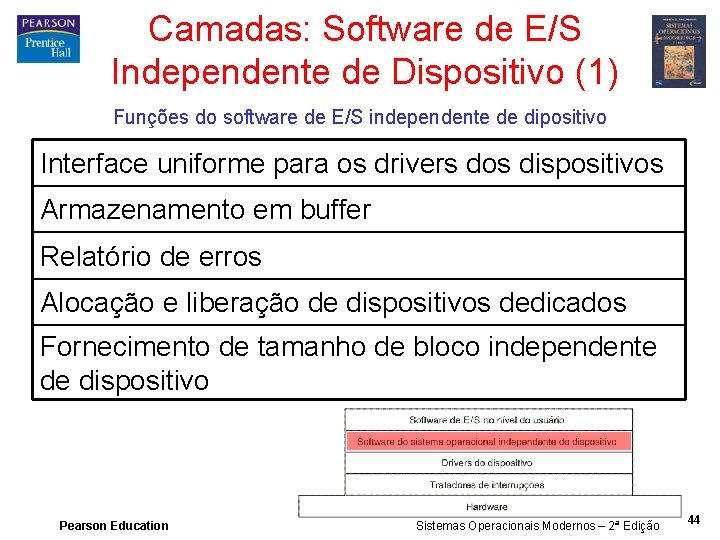

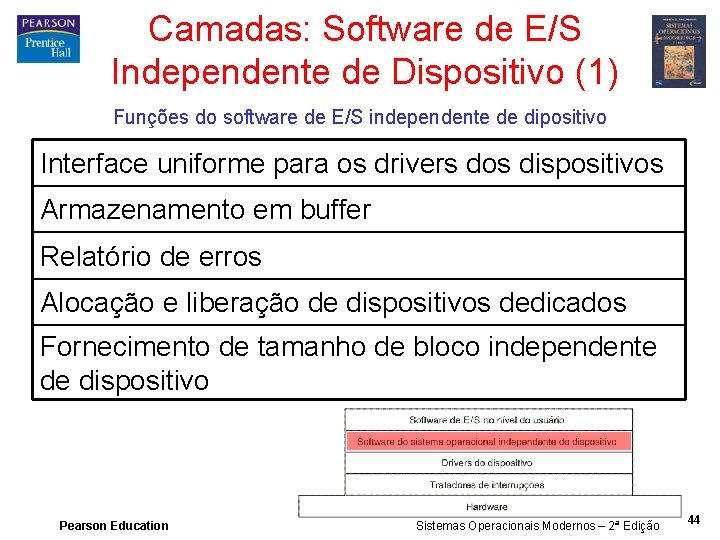

Camadas: Software de E/S Independente de Dispositivo (1) Funções do software de E/S independente de dipositivo Interface uniforme para os drivers dos dispositivos Armazenamento em buffer Relatório de erros Alocação e liberação de dispositivos dedicados Fornecimento de tamanho de bloco independente de dispositivo Pearson Education Sistemas Operacionais Modernos – 2ª Edição 44

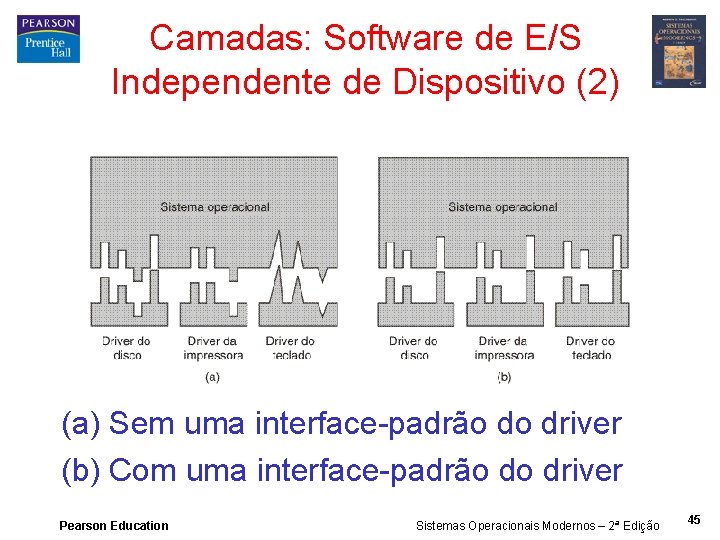

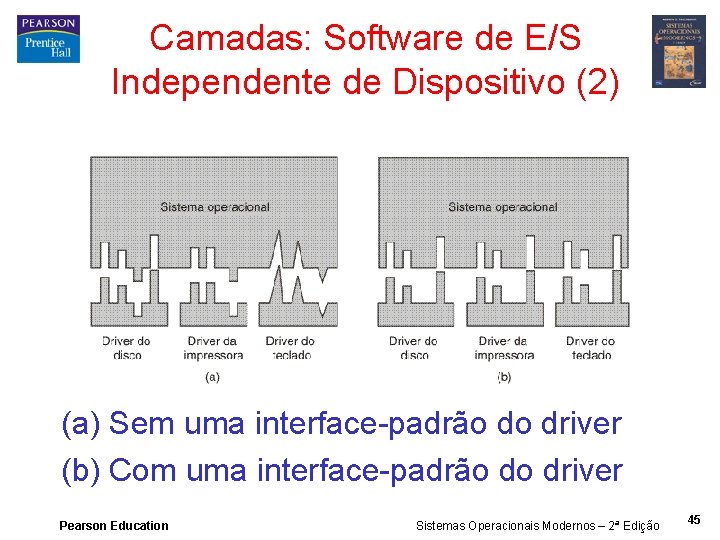

Camadas: Software de E/S Independente de Dispositivo (2) (a) Sem uma interface-padrão do driver (b) Com uma interface-padrão do driver Pearson Education Sistemas Operacionais Modernos – 2ª Edição 45

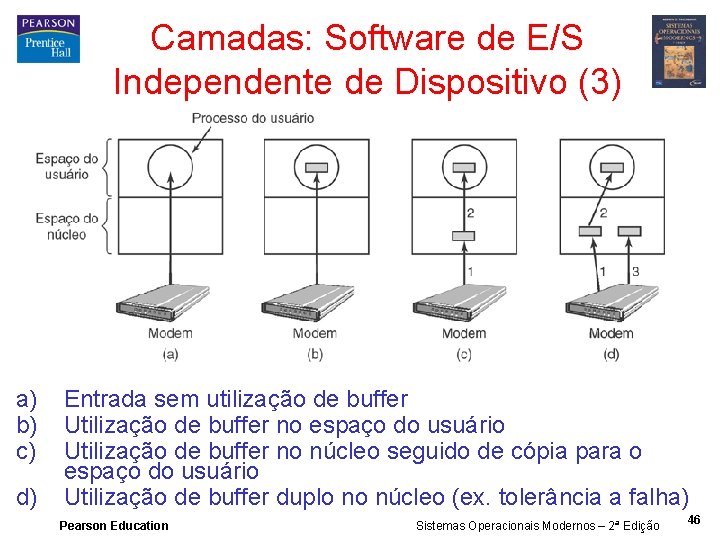

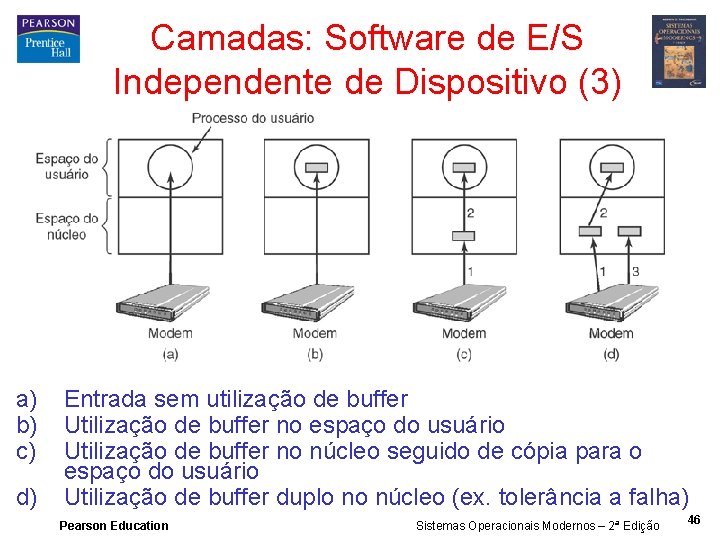

Camadas: Software de E/S Independente de Dispositivo (3) a) b) c) d) Entrada sem utilização de buffer Utilização de buffer no espaço do usuário Utilização de buffer no núcleo seguido de cópia para o espaço do usuário Utilização de buffer duplo no núcleo (ex. tolerância a falha) Pearson Education Sistemas Operacionais Modernos – 2ª Edição 46

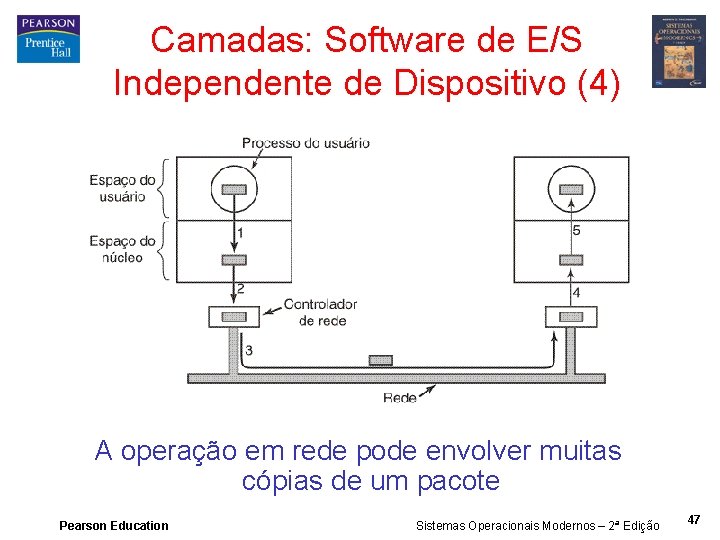

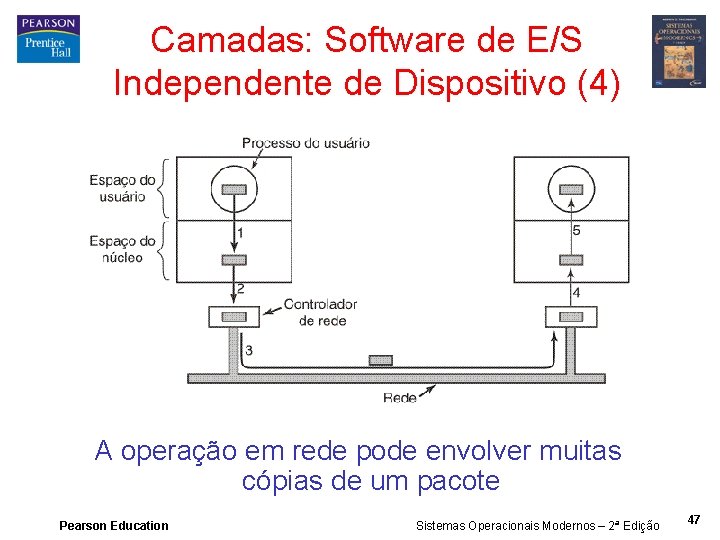

Camadas: Software de E/S Independente de Dispositivo (4) A operação em rede pode envolver muitas cópias de um pacote Pearson Education Sistemas Operacionais Modernos – 2ª Edição 47

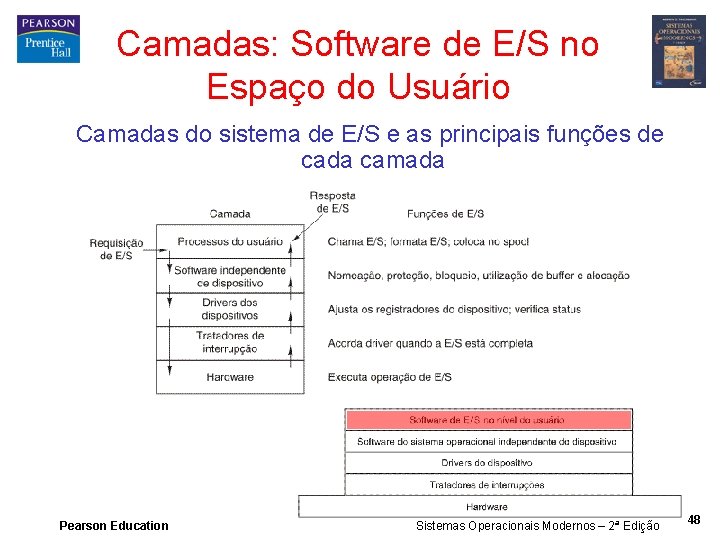

Camadas: Software de E/S no Espaço do Usuário Camadas do sistema de E/S e as principais funções de cada camada Pearson Education Sistemas Operacionais Modernos – 2ª Edição 48

Entrada/Saída üPrincípios do hardware de E/S üPrincípios do software de E/S üCamadas do software de E/S • Gerenciamento de energia Pearson Education Sistemas Operacionais Modernos – 2ª Edição 49

Gerenciamento de Energia (1) Tecnologia mais avançada Aumento do desempenho Consumo de energia de várias partes de um laptop Pearson Education Sistemas Operacionais Modernos – 2ª Edição 50

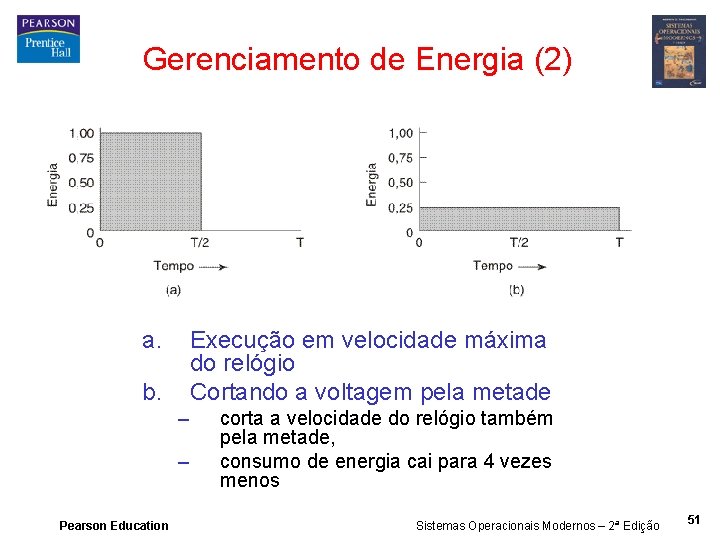

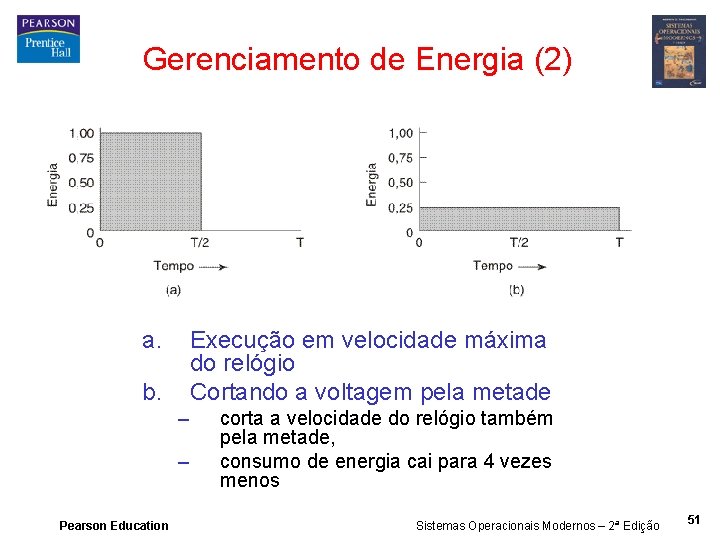

Gerenciamento de Energia (2) a. Execução em velocidade máxima do relógio Cortando a voltagem pela metade b. – – Pearson Education corta a velocidade do relógio também pela metade, consumo de energia cai para 4 vezes menos Sistemas Operacionais Modernos – 2ª Edição 51

Gerenciamento de Energia (3): Impactos na Entrada/Saída • Dizer aos programas para usar menos energia – pode significar experiências mais pobres para o usuário • Exemplos – muda de saída colorida para preto e branco – reconhecimento de fala com vocabulário reduzido – menos resolução ou detalhe em uma imagem Pearson Education Sistemas Operacionais Modernos – 2ª Edição 52

Entrada/Saída • Princípios do hardware de E/S • Princípios do software de E/S • Camadas do software de E/S • Gerenciamento de energia Pearson Education Sistemas Operacionais Modernos – 2ª Edição 53

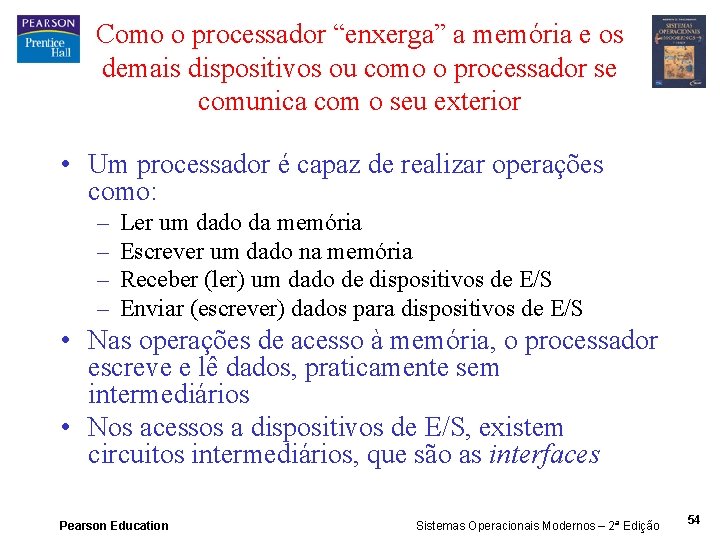

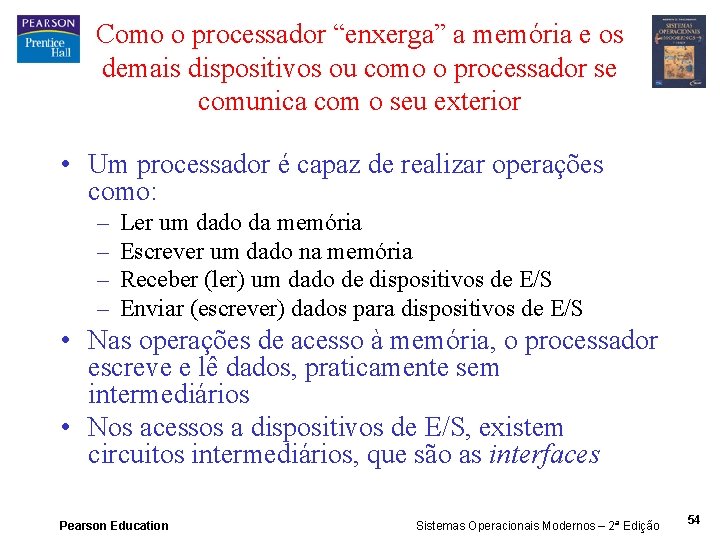

Como o processador “enxerga” a memória e os demais dispositivos ou como o processador se comunica com o seu exterior • Um processador é capaz de realizar operações como: – – Ler um dado da memória Escrever um dado na memória Receber (ler) um dado de dispositivos de E/S Enviar (escrever) dados para dispositivos de E/S • Nas operações de acesso à memória, o processador escreve e lê dados, praticamente sem intermediários • Nos acessos a dispositivos de E/S, existem circuitos intermediários, que são as interfaces Pearson Education Sistemas Operacionais Modernos – 2ª Edição 54

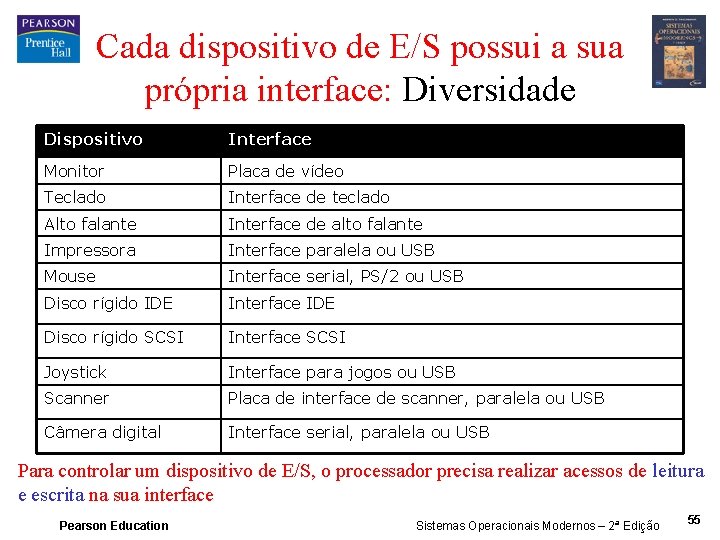

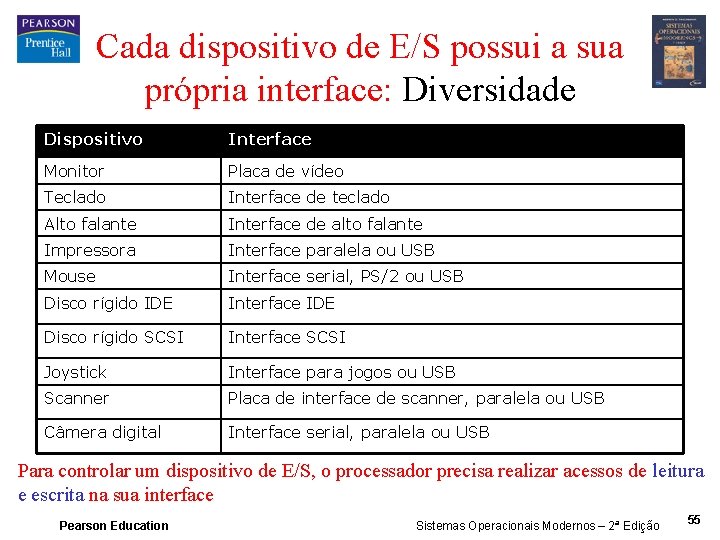

Cada dispositivo de E/S possui a sua própria interface: Diversidade Dispositivo Interface Monitor Placa de vídeo Teclado Interface de teclado Alto falante Interface de alto falante Impressora Interface paralela ou USB Mouse Interface serial, PS/2 ou USB Disco rígido IDE Interface IDE Disco rígido SCSI Interface SCSI Joystick Interface para jogos ou USB Scanner Placa de interface de scanner, paralela ou USB Câmera digital Interface serial, paralela ou USB Para controlar um dispositivo de E/S, o processador precisa realizar acessos de leitura e escrita na sua interface Pearson Education Sistemas Operacionais Modernos – 2ª Edição 55

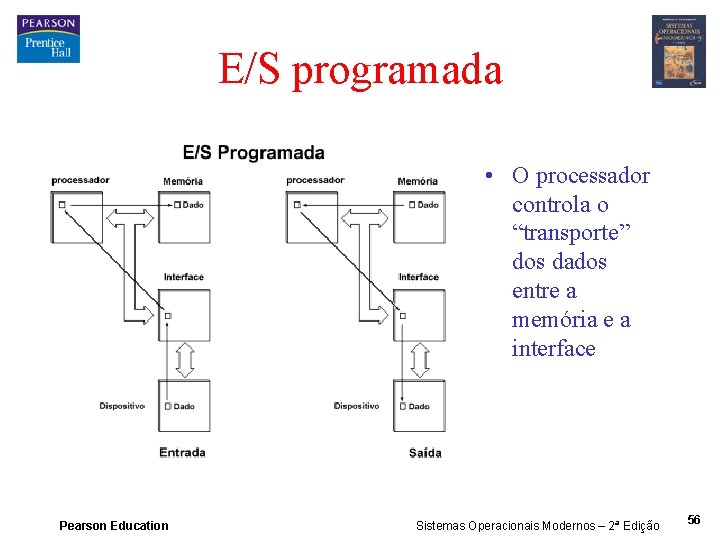

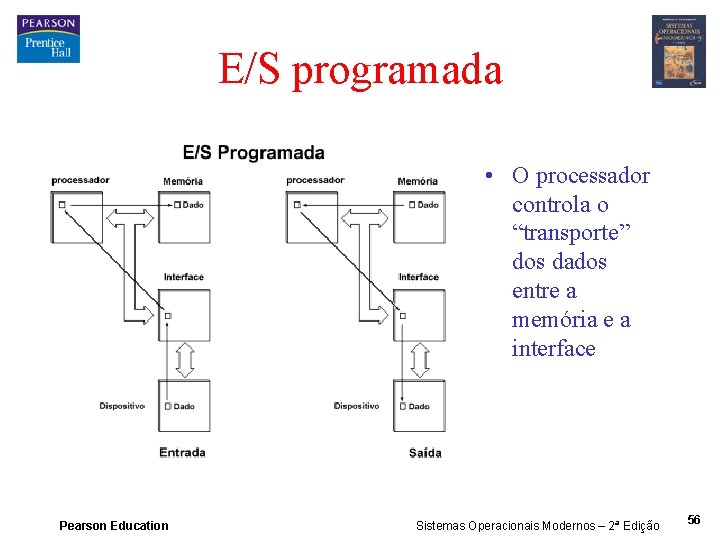

E/S programada • O processador controla o “transporte” dos dados entre a memória e a interface Pearson Education Sistemas Operacionais Modernos – 2ª Edição 56

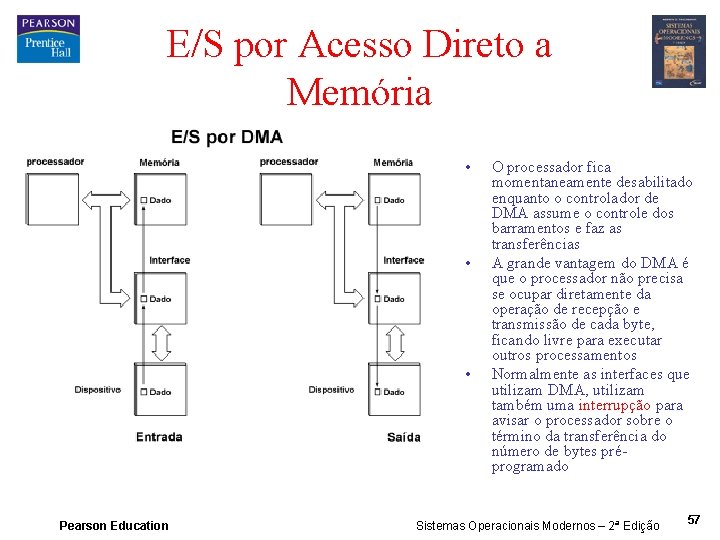

E/S por Acesso Direto a Memória • • • Pearson Education O processador fica momentaneamente desabilitado enquanto o controlador de DMA assume o controle dos barramentos e faz as transferências A grande vantagem do DMA é que o processador não precisa se ocupar diretamente da operação de recepção e transmissão de cada byte, ficando livre para executar outros processamentos Normalmente as interfaces que utilizam DMA, utilizam também uma interrupção para avisar o processador sobre o término da transferência do número de bytes préprogramado Sistemas Operacionais Modernos – 2ª Edição 57

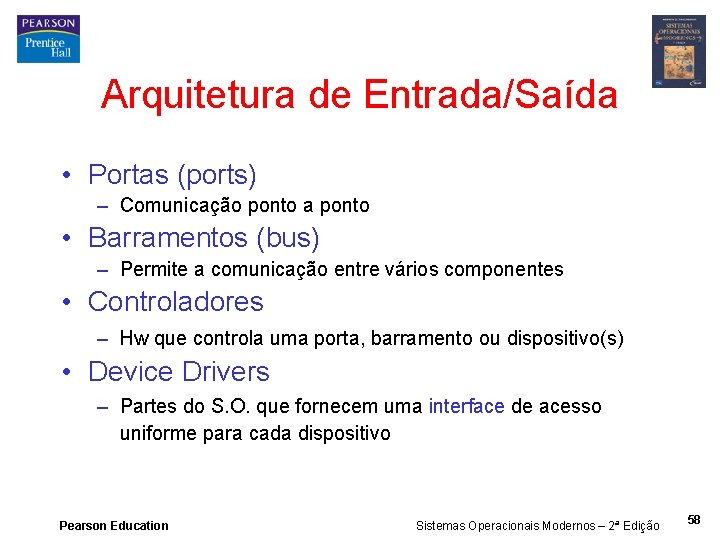

Arquitetura de Entrada/Saída • Portas (ports) – Comunicação ponto a ponto • Barramentos (bus) – Permite a comunicação entre vários componentes • Controladores – Hw que controla uma porta, barramento ou dispositivo(s) • Device Drivers – Partes do S. O. que fornecem uma interface de acesso uniforme para cada dispositivo Pearson Education Sistemas Operacionais Modernos – 2ª Edição 58

Princípios do software de E/S • Independência de dispositivo • Nomeação uniforme • Tratamento de erro o mais próximo possível do hardware • Transferências bloqueantes vs. nãobloqueantes mas orientadas a interrupção • Dispositivos compartilháveis vs. dedicados Pearson Education Sistemas Operacionais Modernos – 2ª Edição 59

Camadas do Software de E/S Pearson Education Sistemas Operacionais Modernos – 2ª Edição 60