1 Logic Circuits Combinational Logics 2 Combinational Circuits

1

ﻣﺪﺍﺭ ﻣﻨﻄﻘی Logic Circuits Combinational Logics 2

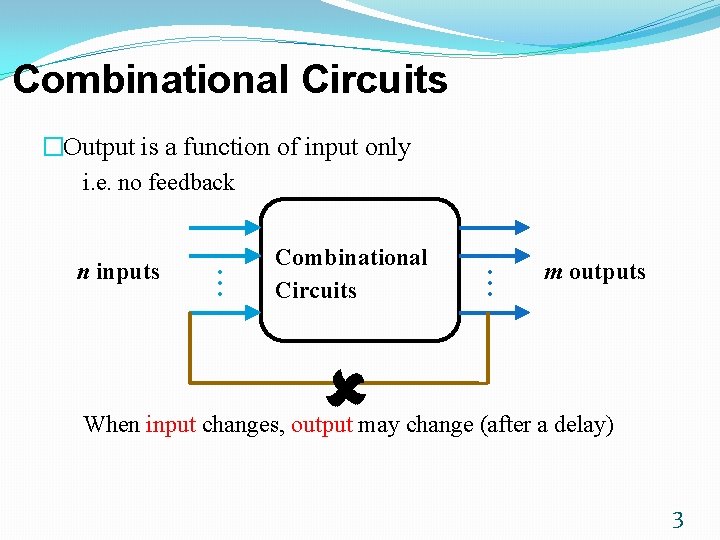

Combinational Circuits �Output is a function of input only i. e. no feedback n inputs • • • Combinational Circuits • • • m outputs When input changes, output may change (after a delay) 3

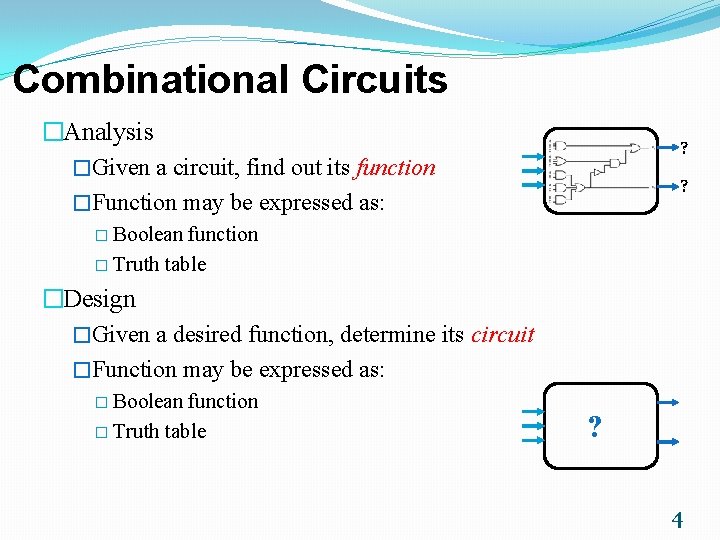

Combinational Circuits �Analysis �Given a circuit, find out its function �Function may be expressed as: ? ? � Boolean function � Truth table �Design �Given a desired function, determine its circuit �Function may be expressed as: � Boolean function � Truth table ? 4

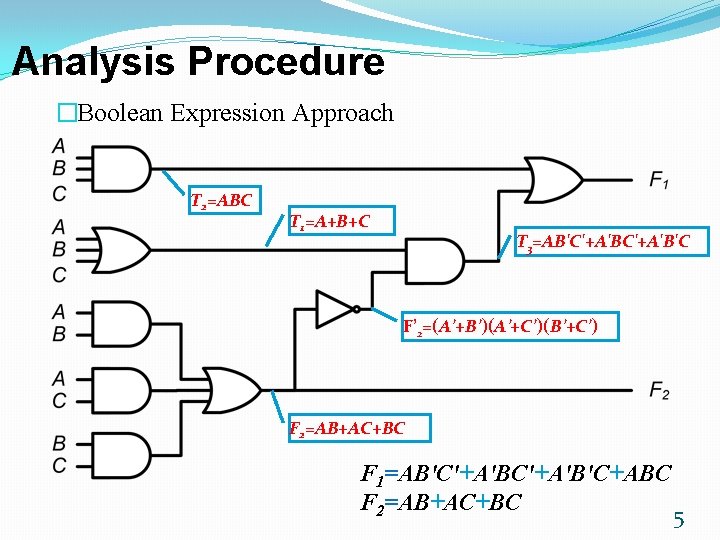

Analysis Procedure �Boolean Expression Approach T 2=ABC T 1=A+B+C T 3=AB'C'+A'B'C F’ 2=(A’+B’)(A’+C’)(B’+C’) F 2=AB+AC+BC F 1=AB'C'+A'B'C+ABC F 2=AB+AC+BC 5

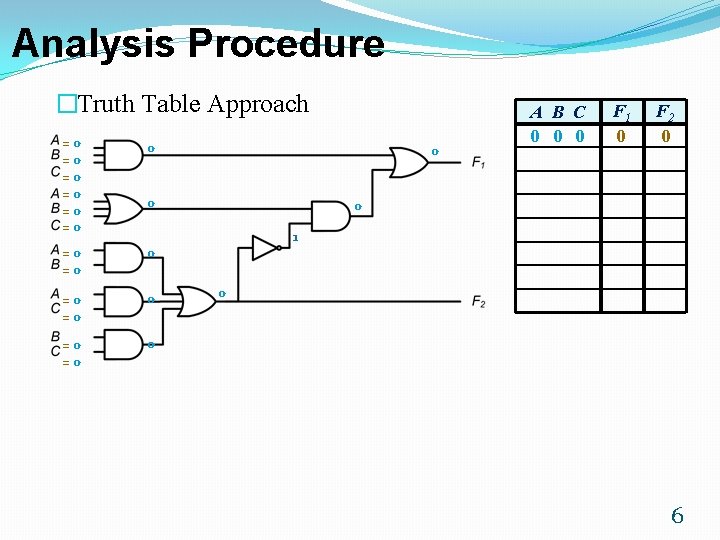

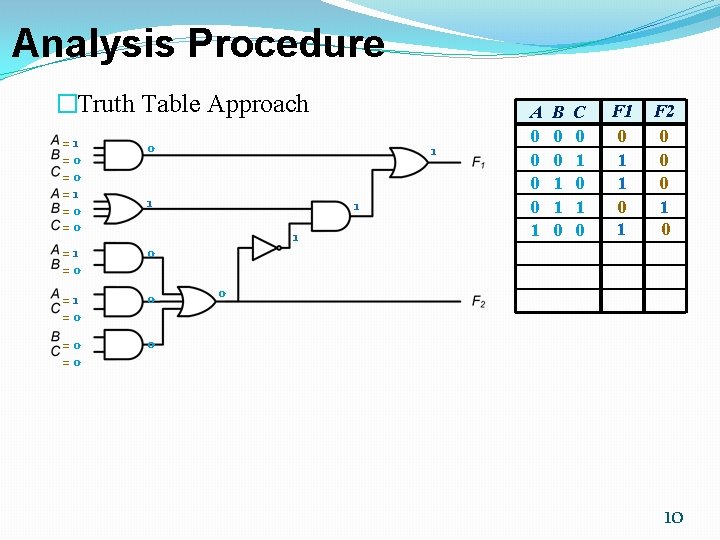

Analysis Procedure �Truth Table Approach =0 =0 =0 0 =0 =0 0 A B C 0 0 0 F 1 0 F 2 0 0 1 0 6

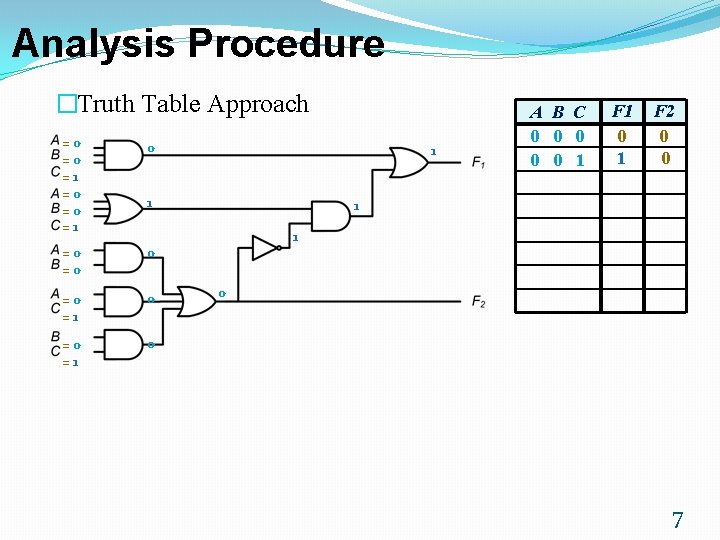

Analysis Procedure �Truth Table Approach =0 =0 =1 0 =0 =1 0 1 1 A B C 0 0 0 1 F 1 0 1 F 2 0 0 1 1 0 7

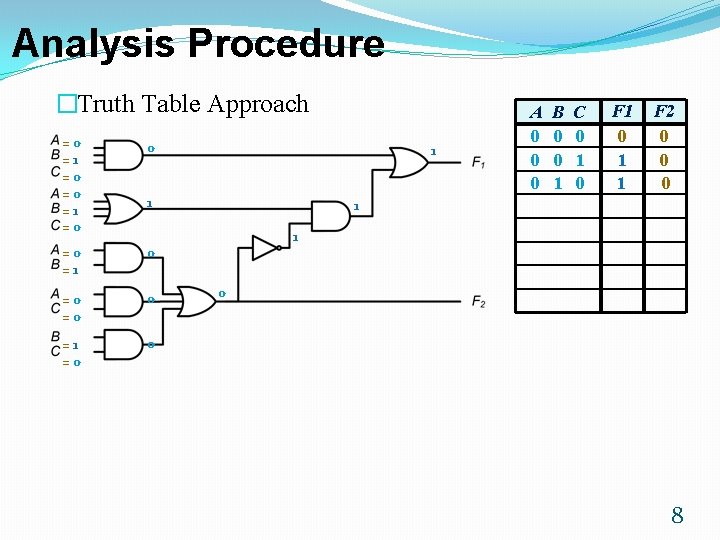

Analysis Procedure �Truth Table Approach =0 =1 =0 0 =0 =1 0 =0 =0 0 =1 =0 0 1 1 A 0 0 0 B 0 0 1 C 0 1 0 F 1 0 1 1 F 2 0 0 0 1 1 0 8

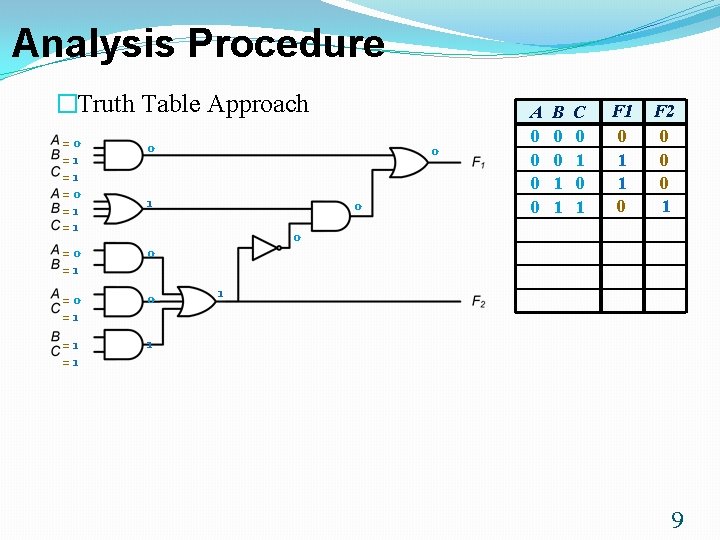

Analysis Procedure �Truth Table Approach =0 =1 =1 0 =0 =1 =1 1 0 A 0 0 B 0 0 1 1 C 0 1 F 1 0 1 1 0 F 2 0 0 0 1 9

Analysis Procedure �Truth Table Approach =1 =0 =0 0 =1 =0 0 =0 =0 0 1 1 A 0 0 1 B 0 0 1 1 0 C 0 1 0 F 1 0 1 F 2 0 0 0 10

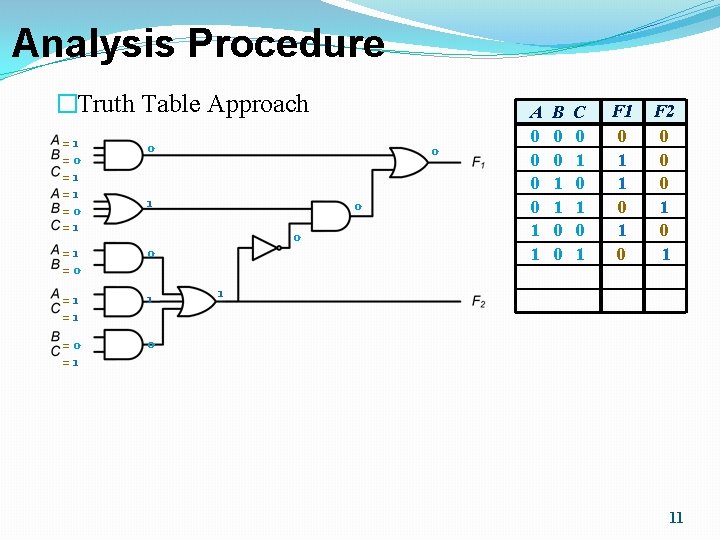

Analysis Procedure �Truth Table Approach =1 =0 =1 =0 0 =1 =1 1 =0 =1 0 0 A 0 0 1 1 B 0 0 1 1 0 0 C 0 1 0 1 F 1 0 1 0 F 2 0 0 0 1 1 11

Analysis Procedure �Truth Table Approach =1 =1 =0 0 =1 =0 0 0 1 A 0 0 1 1 1 B 0 0 1 1 0 0 1 C 0 1 0 1 0 F 1 0 1 0 0 F 2 0 0 0 1 1 12

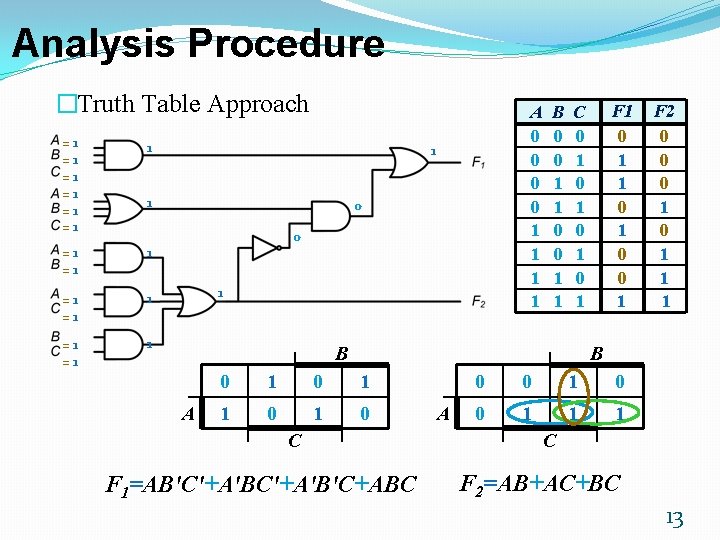

Analysis Procedure �Truth Table Approach =1 =1 =1 1 =1 =1 1 A 0 0 1 1 1 0 0 1 B 0 0 1 1 B A F 1 0 1 0 0 1 C 0 1 0 1 F 2 0 0 0 1 1 1 B 0 1 1 0 C F 1=AB'C'+A'B'C+ABC A 0 0 1 1 1 C F 2=AB+AC+BC 13

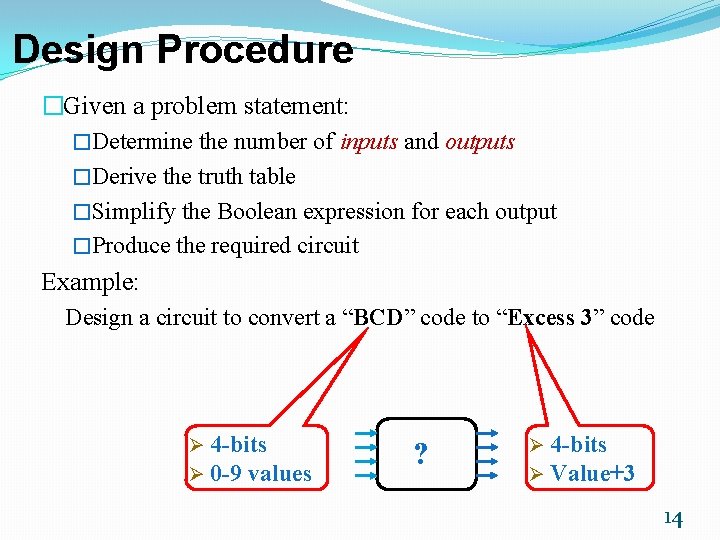

Design Procedure �Given a problem statement: �Determine the number of inputs and outputs �Derive the truth table �Simplify the Boolean expression for each output �Produce the required circuit Example: Design a circuit to convert a “BCD” code to “Excess 3” code Ø 4 -bits Ø 0 -9 values ? Ø 4 -bits Ø Value+3 14

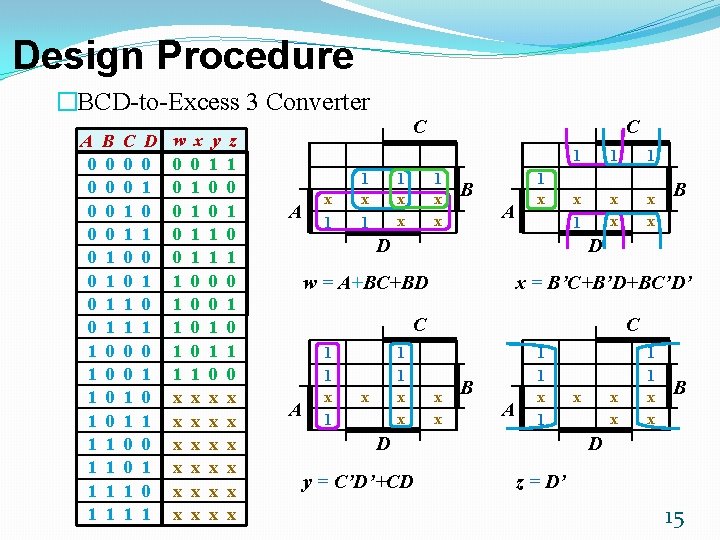

Design Procedure �BCD-to-Excess 3 Converter A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 w 0 0 0 1 1 1 x x x x 0 1 1 0 0 1 x x x y 1 0 0 1 1 0 x x x z 1 0 1 0 1 0 x x x A x 1 C 1 x 1 1 x x C 1 x x B A 1 x 1 1 1 x x x x D D w = A+BC+BD x = B’C+B’D+BC’D’ C A 1 1 x 1 1 1 x x x B C x x B A 1 1 x 1 D y = C’D’+CD x x x 1 1 x x B D z = D’ 15

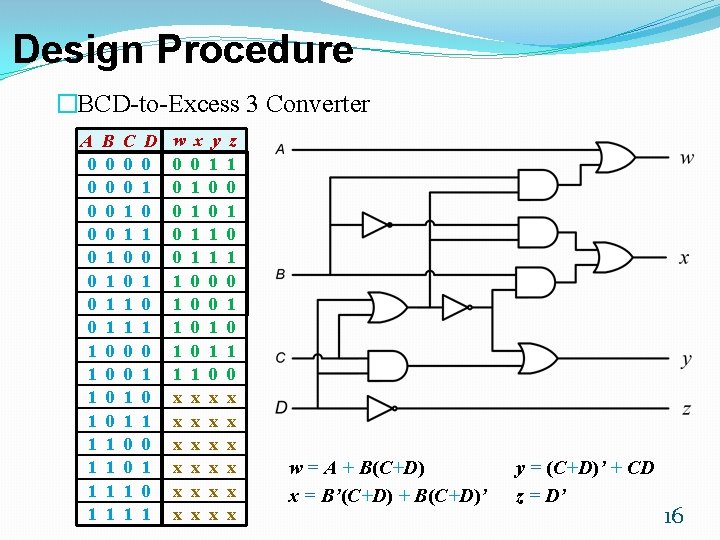

Design Procedure �BCD-to-Excess 3 Converter A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 w 0 0 0 1 1 1 x x x x 0 1 1 0 0 1 x x x y 1 0 0 1 1 0 x x x z 1 0 1 0 1 0 x x x w = A + B(C+D) x = B’(C+D) + B(C+D)’ y = (C+D)’ + CD z = D’ 16

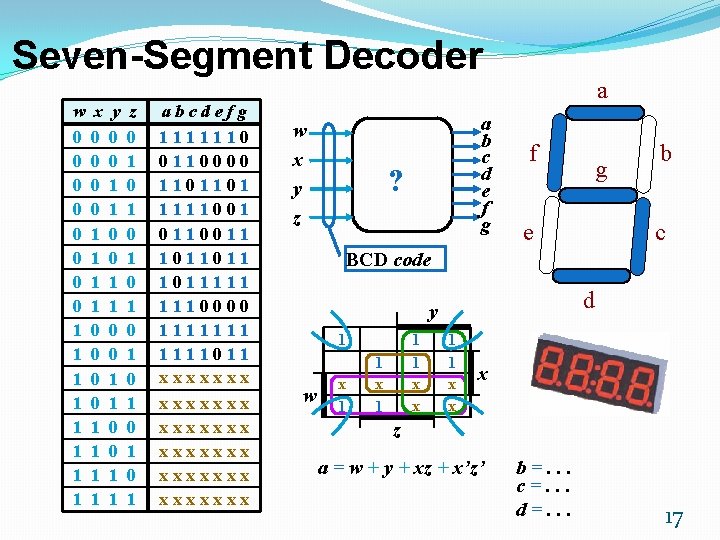

Seven-Segment Decoder w 0 0 0 0 1 1 1 1 x 0 0 0 0 1 1 1 1 y 0 0 1 1 z 0 1 0 1 abcdefg 1111110 0110000 1101101 1111001 0110011 1011111 1110000 1111111011 xxxxxxx xxxxxxx w x y z a b c d e f g ? a f g e b c BCD code d y 1 w x 1 1 1 x x x z a = w + y + xz + x’z’ b=. . . c=. . . d=. . . 17

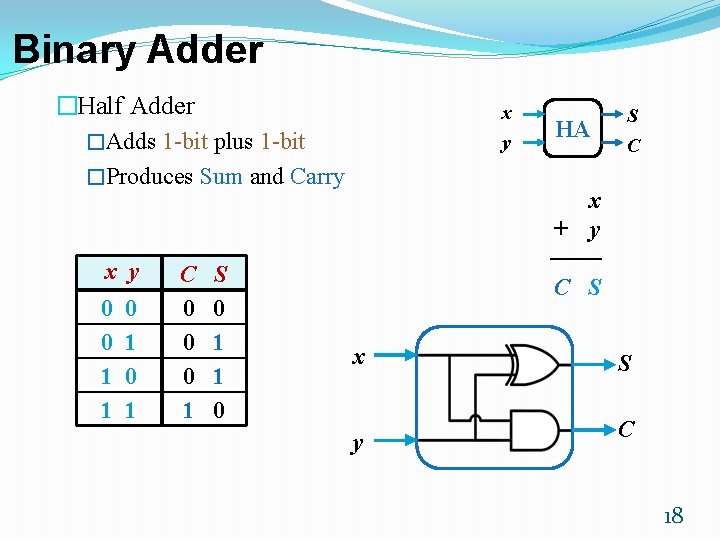

Binary Adder �Half Adder �Adds 1 -bit plus 1 -bit �Produces Sum and Carry x y 0 0 1 1 0 1 C 0 0 0 1 S 0 1 1 0 x y HA S C x + y ─── C S x y S C 18

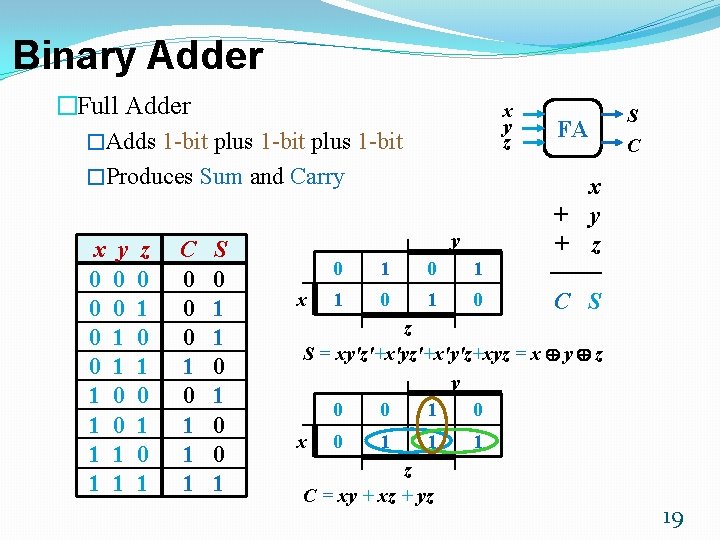

Binary Adder �Full Adder �Adds 1 -bit plus 1 -bit �Produces Sum and Carry x y 0 0 0 1 0 1 1 1 1 z 0 1 0 1 C 0 0 0 1 1 1 S 0 1 1 0 0 1 x y z y x 0 1 1 0 FA S C x + y + z ─── C S z S = xy'z'+x'y'z+xyz = x y z y 0 0 1 0 x 0 1 1 z C = xy + xz + yz 1 19

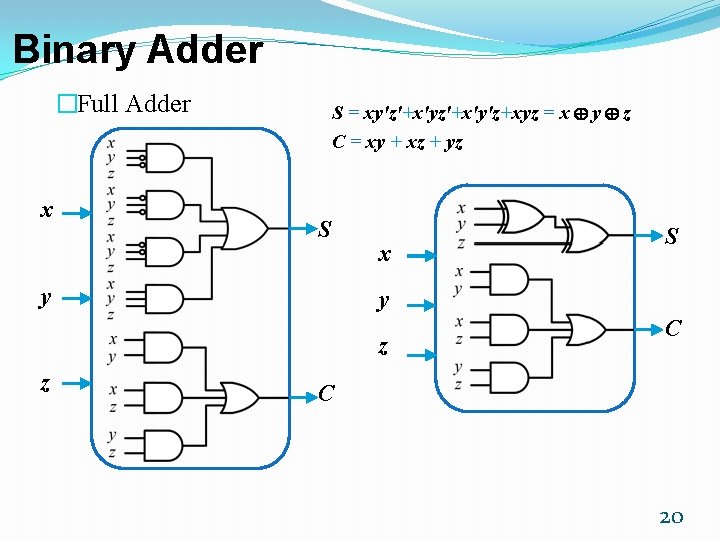

Binary Adder �Full Adder x S = xy'z'+x'y'z+xyz = x y z C = xy + xz + yz S y x y z z S C C 20

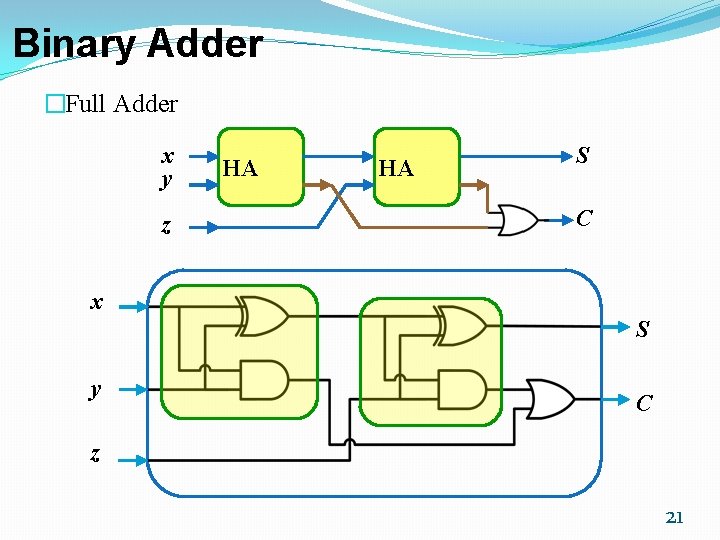

Binary Adder �Full Adder x y z HA HA S C x S y C z 21

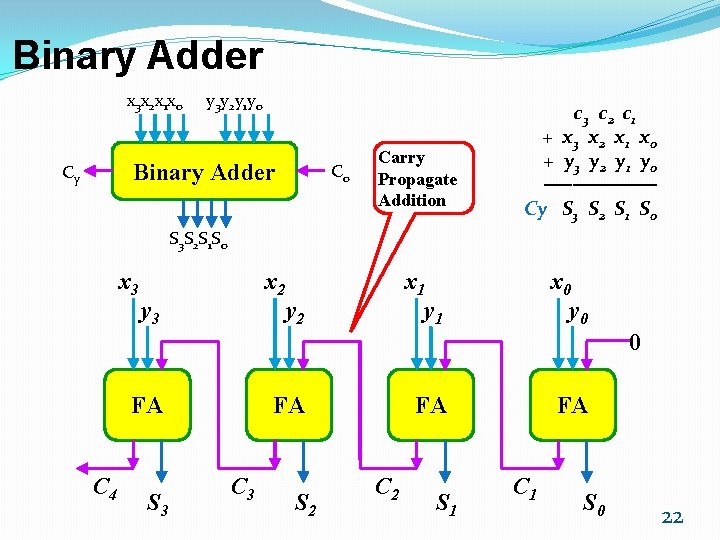

Binary Adder x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 Binary Adder Cy C 0 Carry Propagate Addition c 3 c 2 c 1. + x 3 x 2 x 1 x 0 + y 3 y 2 y 1 y 0 ──── Cy S 3 S 2 S 1 S 0 S 3 S 2 S 1 S 0 x 3 x 2 y 3 x 1 y 2 x 0 y 0 0 FA C 4 S 3 FA C 3 S 2 FA C 2 S 1 FA C 1 S 0 22

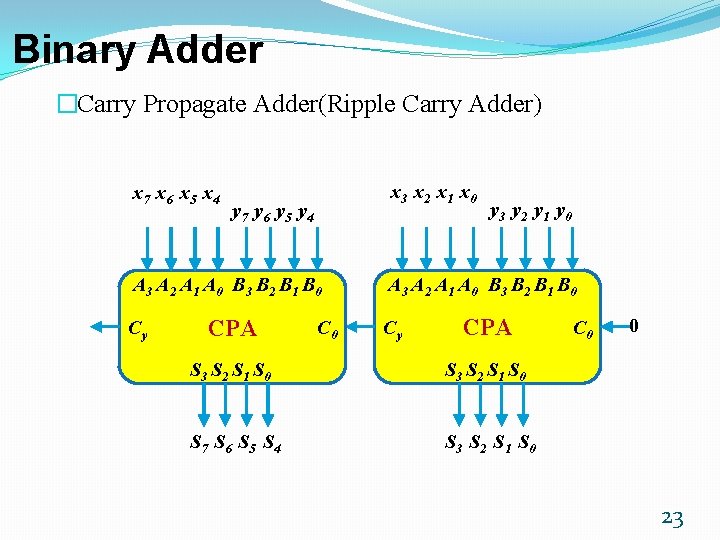

Binary Adder �Carry Propagate Adder(Ripple Carry Adder) x 7 x 6 x 5 x 4 x 3 x 2 x 1 x 0 y 7 y 6 y 5 y 4 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Cy CPA C 0 y 3 y 2 y 1 y 0 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Cy CPA S 3 S 2 S 1 S 0 S 7 S 6 S 5 S 4 S 3 S 2 S 1 S 0 C 0 0 23

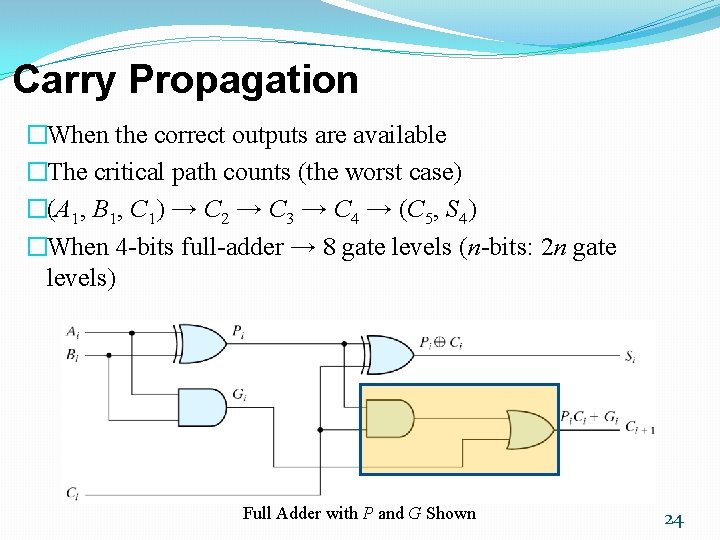

Carry Propagation �When the correct outputs are available �The critical path counts (the worst case) �(A 1, B 1, C 1) → C 2 → C 3 → C 4 → (C 5, S 4) �When 4 -bits full-adder → 8 gate levels (n-bits: 2 n gate levels) Full Adder with P and G Shown 24

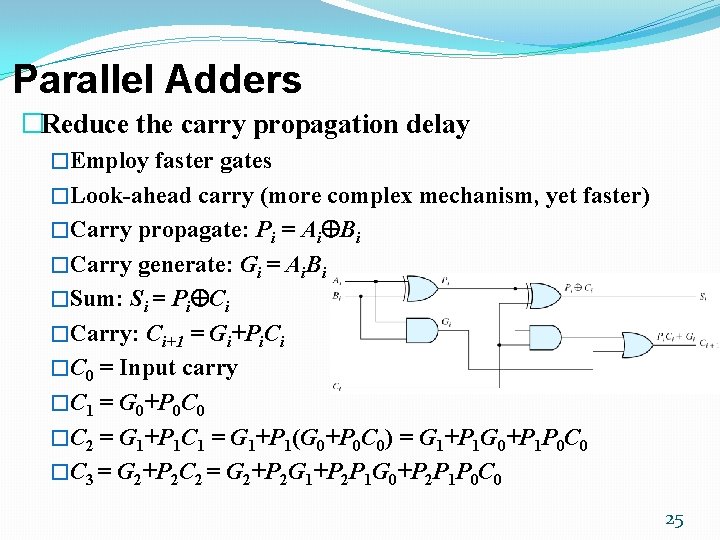

Parallel Adders �Reduce the carry propagation delay �Employ faster gates �Look-ahead carry (more complex mechanism, yet faster) �Carry propagate: Pi = Ai Bi �Carry generate: Gi = Ai. Bi �Sum: Si = Pi Ci �Carry: Ci+1 = Gi+Pi. Ci �C 0 = Input carry �C 1 = G 0+P 0 C 0 �C 2 = G 1+P 1 C 1 = G 1+P 1(G 0+P 0 C 0) = G 1+P 1 G 0+P 1 P 0 C 0 �C 3 = G 2+P 2 C 2 = G 2+P 2 G 1+P 2 P 1 G 0+P 2 P 1 P 0 C 0 25

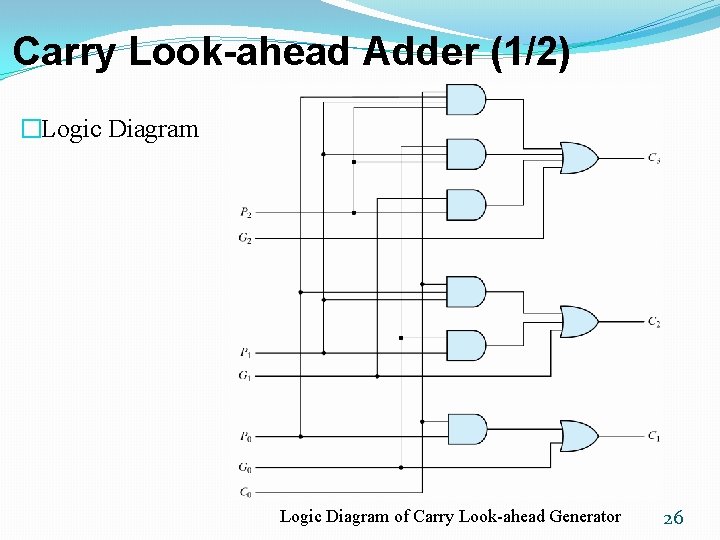

Carry Look-ahead Adder (1/2) �Logic Diagram of Carry Look-ahead Generator 26

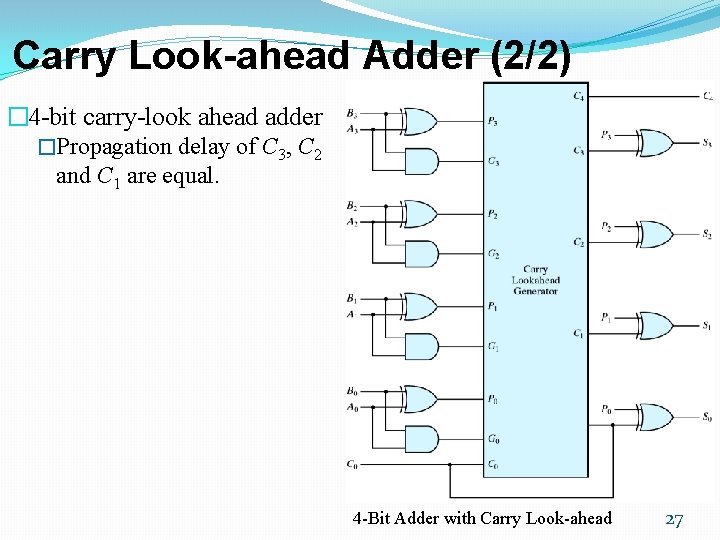

Carry Look-ahead Adder (2/2) � 4 -bit carry-look ahead adder �Propagation delay of C 3, C 2 and C 1 are equal. 4 -Bit Adder with Carry Look-ahead 27

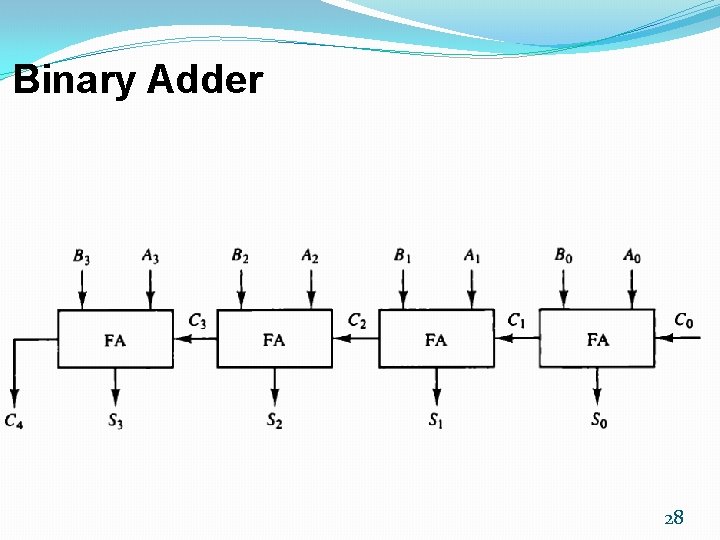

Binary Adder 28

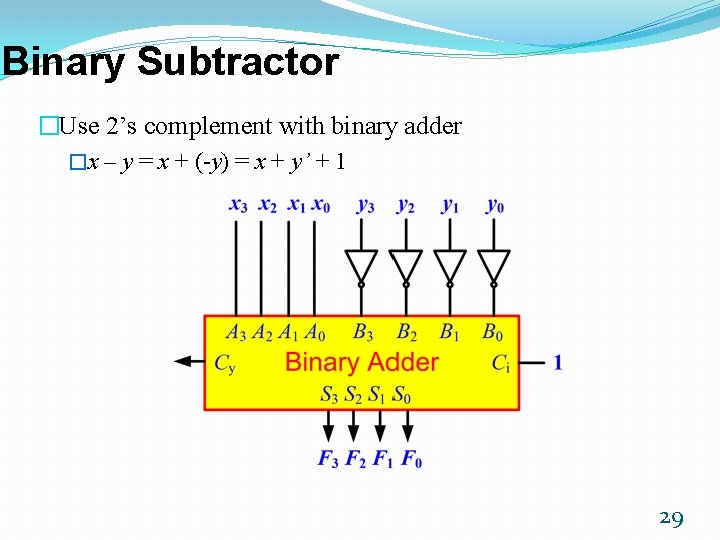

Binary Subtractor �Use 2’s complement with binary adder �x – y = x + (-y) = x + y’ + 1 29

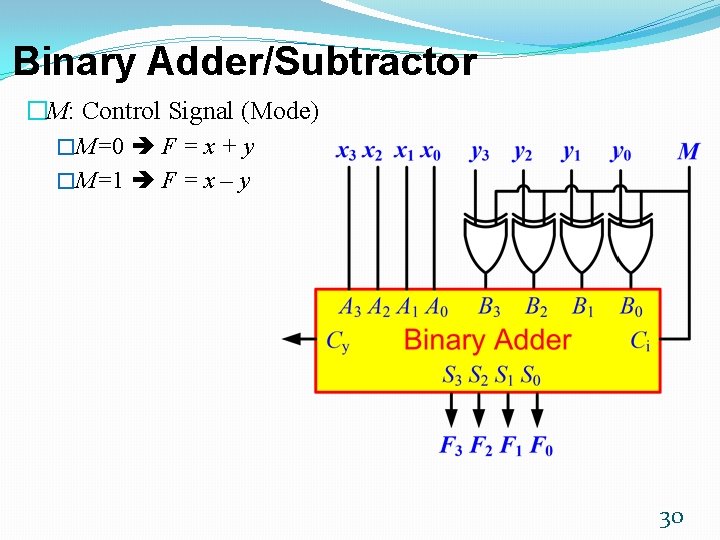

Binary Adder/Subtractor �M: Control Signal (Mode) �M=0 F = x + y �M=1 F = x – y 30

Overflow �Unsigned numbers �Addition Carry means the result is n+1 �Subtraction Carry = not(Borrow) = 1 Result is correct and positive � C = 0 Result is negative! (Take 2’s complement and place minus sign in front of it) �C �Signed numbers �Carry has no useful meaning �We should check overflow and sign bit 31

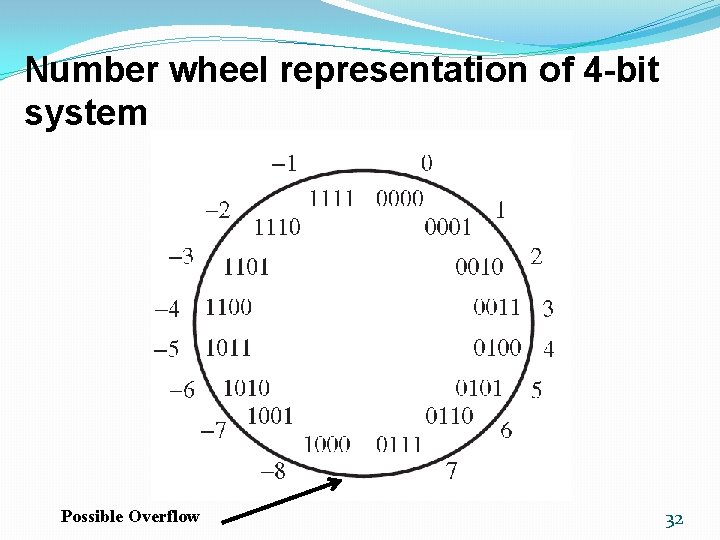

Number wheel representation of 4 -bit system Possible Overflow 32

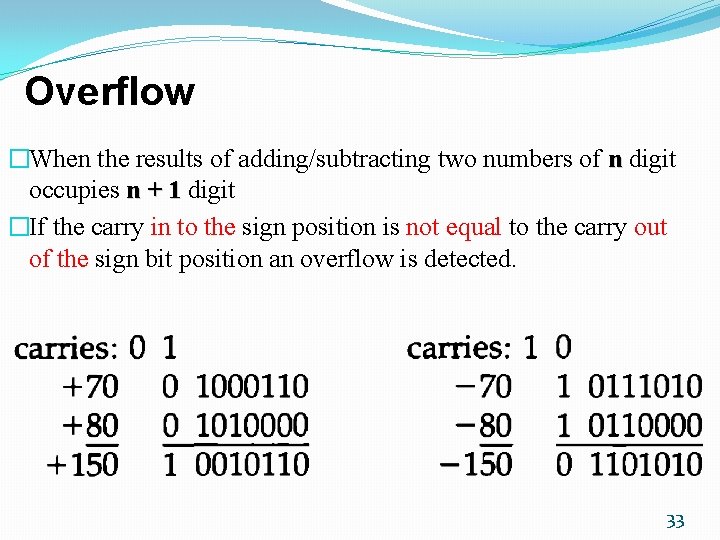

Overflow �When the results of adding/subtracting two numbers of n digit occupies n + 1 digit �If the carry in to the sign position is not equal to the carry out of the sign bit position an overflow is detected. 33

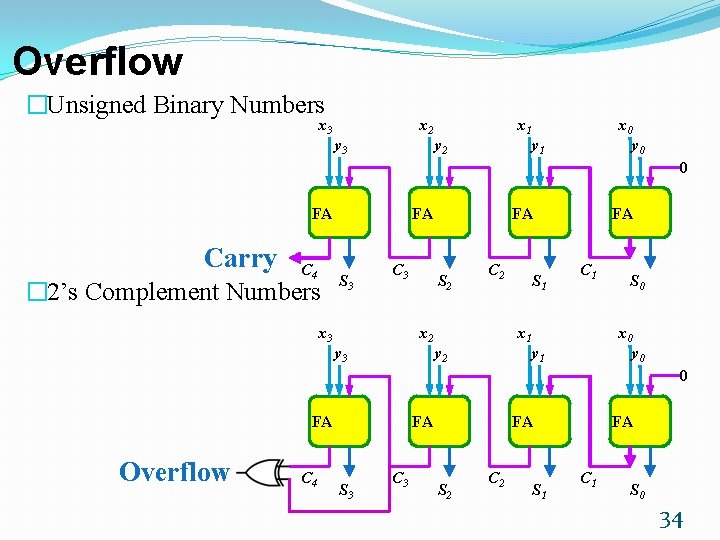

Overflow �Unsigned Binary Numbers x 3 x 2 y 3 x 1 y 2 x 0 y 1 0 FA Carry C 4 � 2’s Complement Numbers x 3 FA S 3 C 3 S 2 x 2 y 3 FA C 2 S 1 x 1 y 2 FA C 1 S 0 x 0 y 1 0 FA Overflow C 4 FA S 3 C 3 FA S 2 C 2 S 1 FA C 1 S 0 34

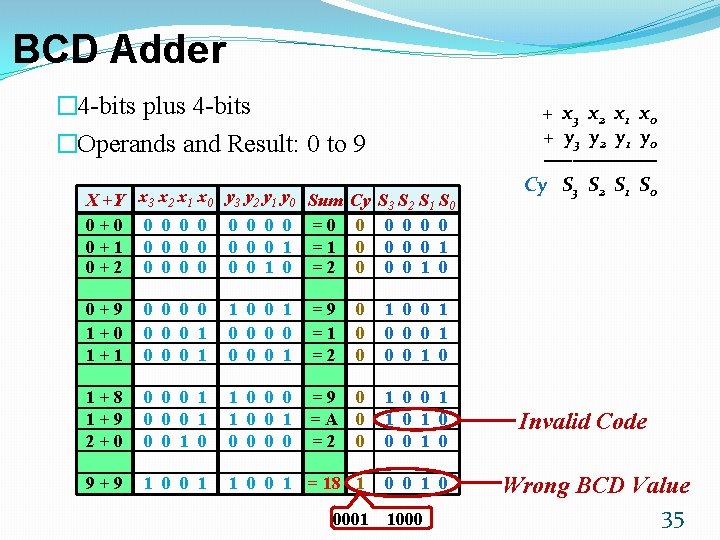

BCD Adder � 4 -bits plus 4 -bits �Operands and Result: 0 to 9 X +Y x 3 x 2 x 1 x 0 0+0 0 0 0+1 0 0 0+2 0 0 y 3 y 2 y 1 y 0 Sum 0 0 =0 0 1 =1 0 0 1 0 =2 0+9 1+0 1+1 0 0 0 0 1 1 0 0 0 0 0 1 =9 =1 =2 1+8 1+9 2+0 0 1 0 0 1 0 0 0 0 9+9 1 0 0 1 Cy 0 0 0 S 3 S 2 S 1 S 0 0 0 0 1 0 0 1 0 =9 0 =A 0 =2 0 1 0 0 1 1 0 0 0 1 = 18 1 0 0001 1000 + x 3 x 2 x 1 x 0 + y 3 y 2 y 1 y 0 ──── Cy S 3 S 2 S 1 S 0 Invalid Code Wrong BCD Value 35

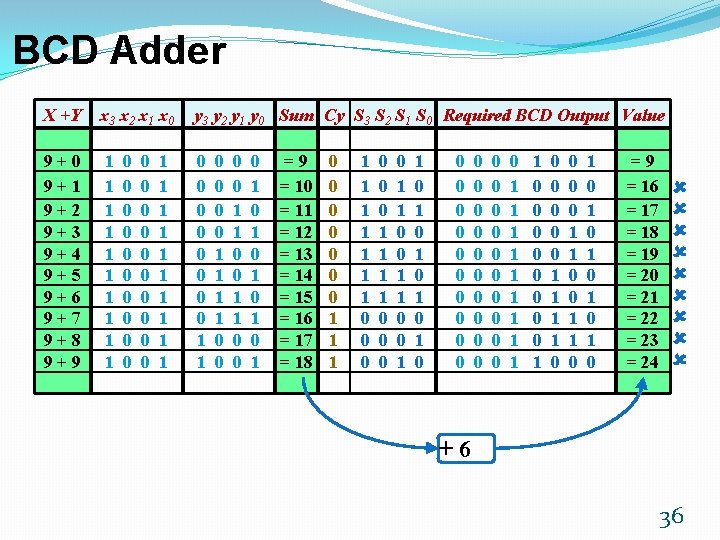

BCD Adder X +Y x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 Sum Cy S 3 S 2 S 1 S 0 Required BCD Output Value 9+0 9+1 9+2 9+3 9+4 9+5 9+6 9+7 9+8 9+9 1 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 0 0 1 1 0 0 0 1 0 1 0 1 =9 = 10 = 11 = 12 = 13 = 14 = 15 = 16 = 17 = 18 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 =9 = 16 = 17 = 18 = 19 = 20 = 21 = 22 = 23 = 24 +6 36

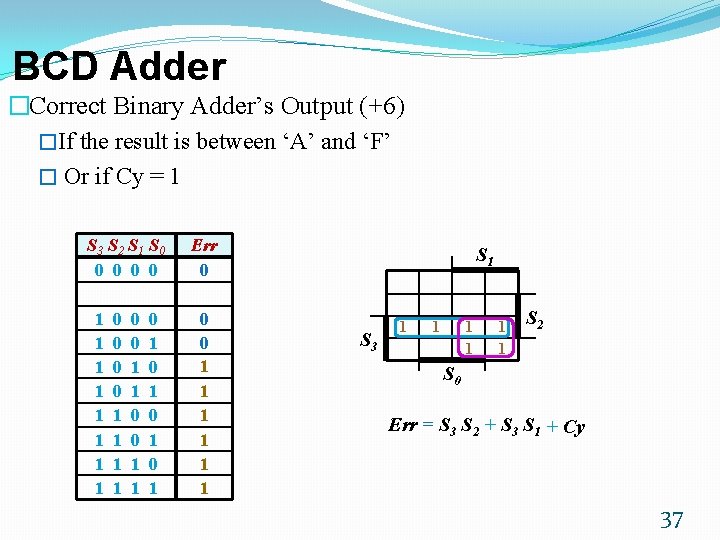

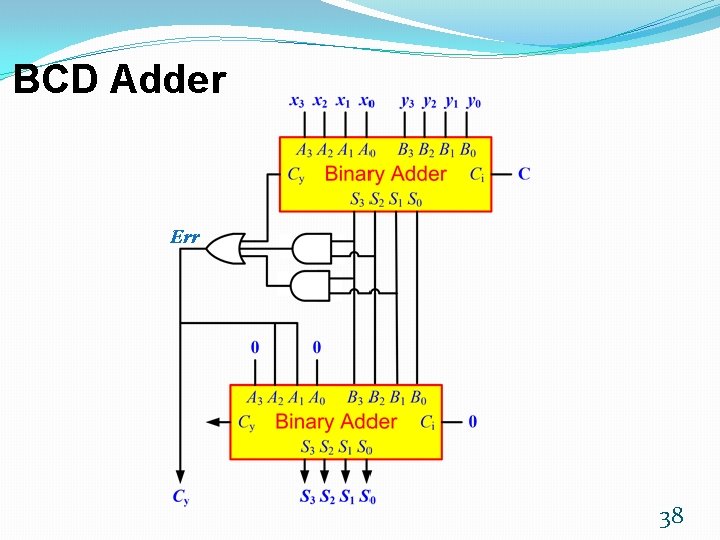

BCD Adder �Correct Binary Adder’s Output (+6) �If the result is between ‘A’ and ‘F’ � Or if Cy = 1 S 3 S 2 S 1 S 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 Err 0 0 0 1 1 1 S 1 S 3 1 1 1 S 2 S 0 Err = S 3 S 2 + S 3 S 1 + Cy 37

BCD Adder Err 38

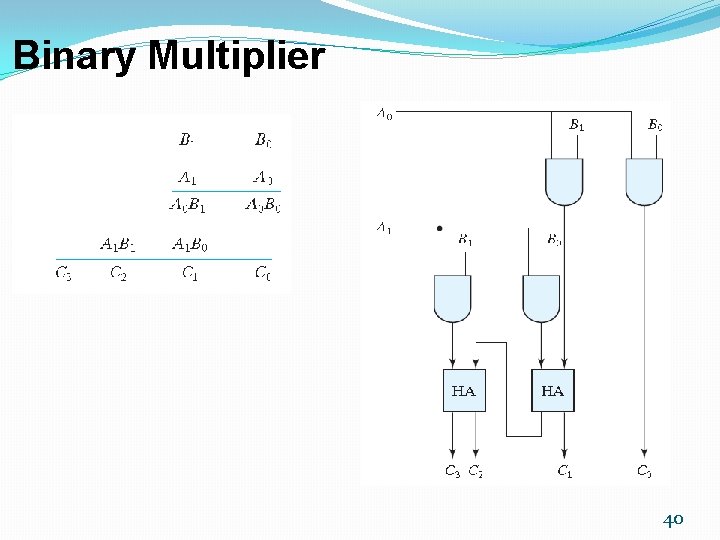

Binary Multiplier �The multiplicand is multiplied by each bit of the multiplier, starting from the least significant bit. �Each such multiplication forms a partial product. �Successive partial products are shifted one position to the left. �The final product is obtained from the sum of the partial products. Multiplicand Multiplier 39

Binary Multiplier 40

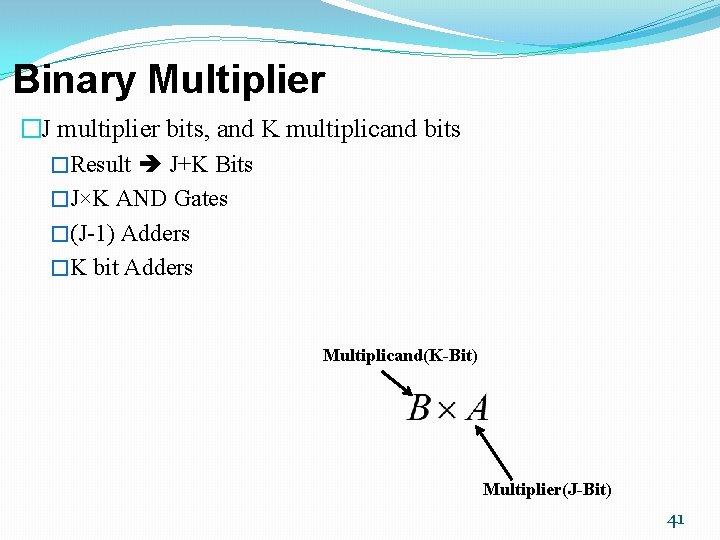

Binary Multiplier �J multiplier bits, and K multiplicand bits �Result J+K Bits �J×K AND Gates �(J-1) Adders �K bit Adders Multiplicand(K-Bit) Multiplier(J-Bit) 41

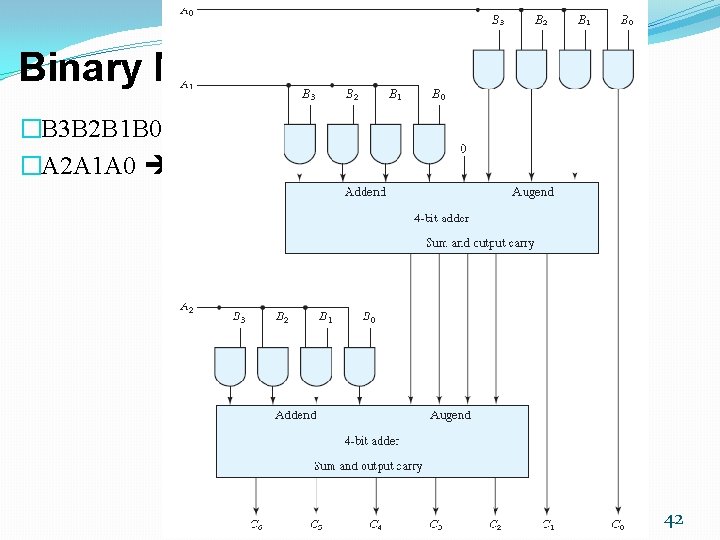

Binary Multiplier �B 3 B 2 B 1 B 0 K = 4 �A 2 A 1 A 0 J = 3 42

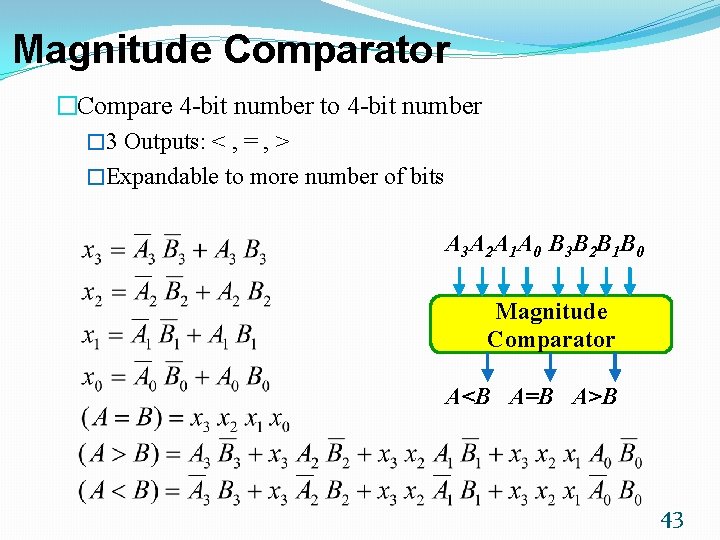

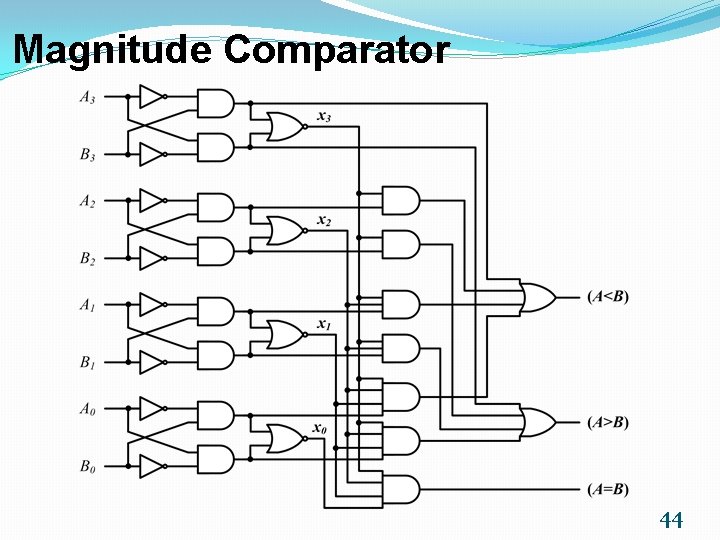

Magnitude Comparator �Compare 4 -bit number to 4 -bit number � 3 Outputs: < , = , > �Expandable to more number of bits A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Magnitude Comparator A<B A=B A>B 43

Magnitude Comparator 44

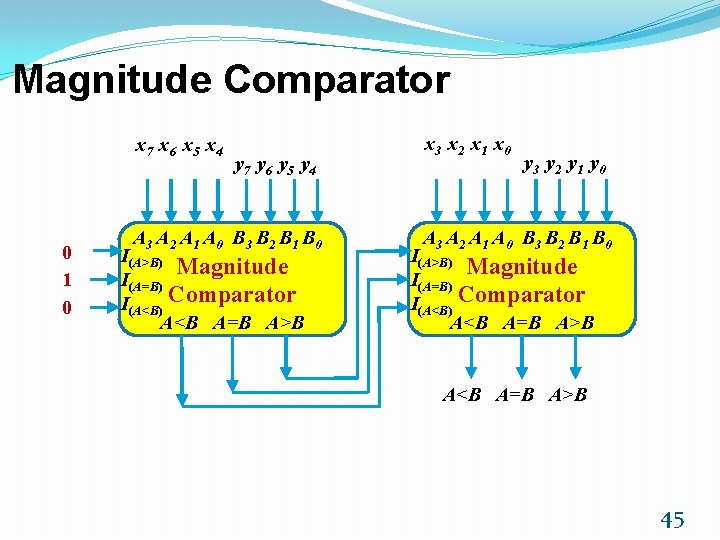

Magnitude Comparator x 7 x 6 x 5 x 4 0 1 0 y 7 y 6 y 5 y 4 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 I(A>B) Magnitude I(A=B) I(A<B) Comparator A<B A=B A>B x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 I(A>B) Magnitude I(A=B) I(A<B) Comparator A<B A=B A>B 45

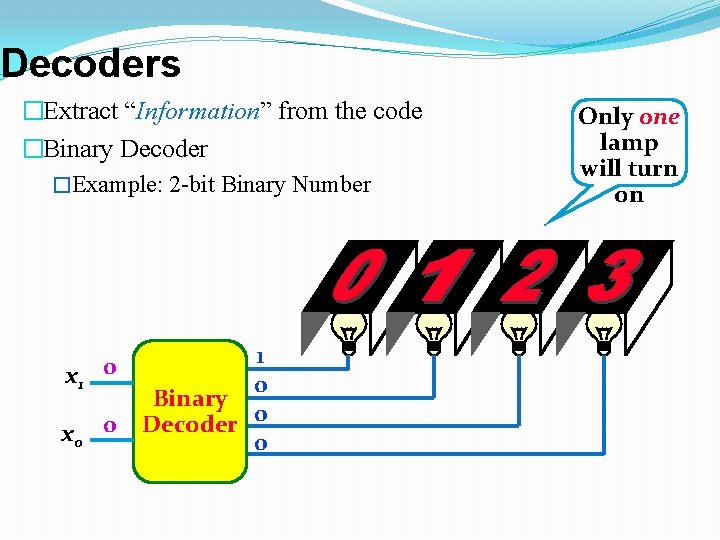

Decoders �Extract “Information” from the code �Binary Decoder �Example: 2 -bit Binary Number x 1 0 x 0 0 1 0 Binary Decoder 0 0 Only one lamp will turn on

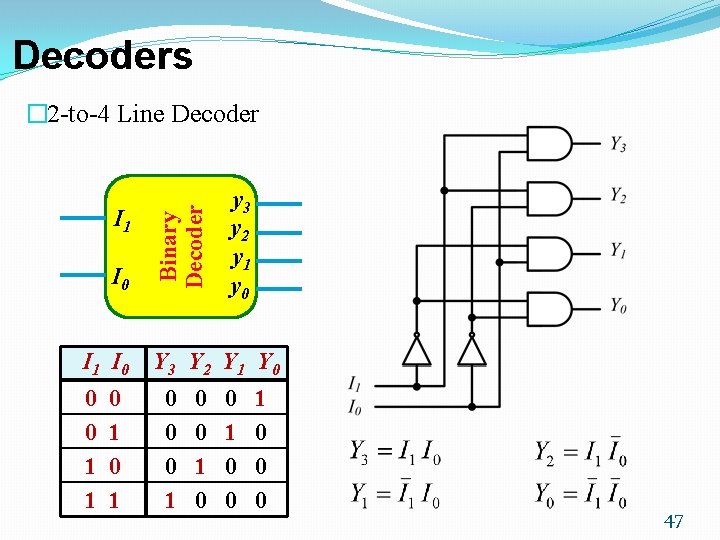

Decoders I 1 I 0 0 0 1 1 0 1 Binary Decoder � 2 -to-4 Line Decoder y 3 y 2 y 1 y 0 Y 3 Y 2 Y 1 Y 0 0 1 0 0 0 47

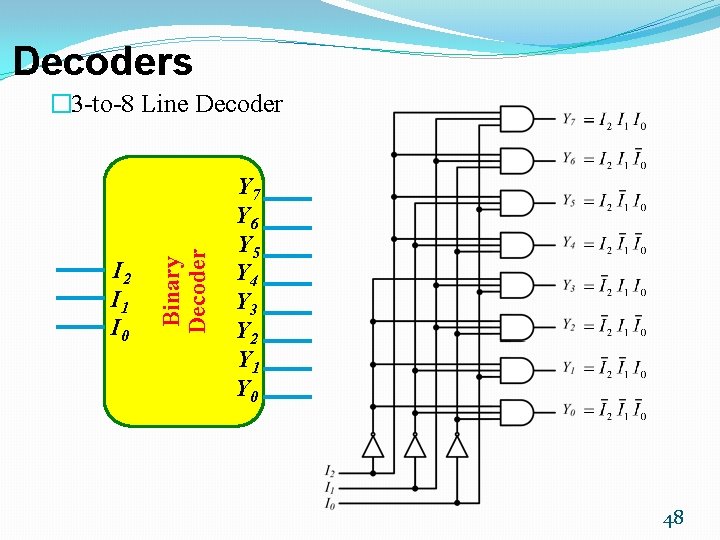

Decoders I 2 I 1 I 0 Binary Decoder � 3 -to-8 Line Decoder Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 48

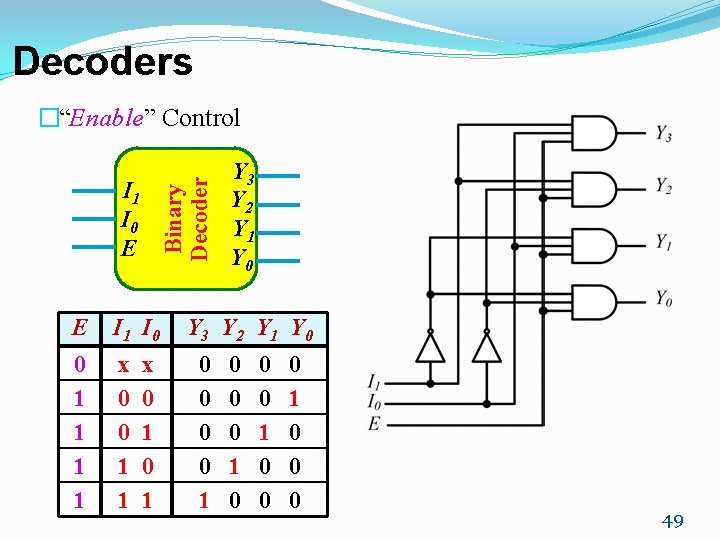

Decoders Binary Decoder �“Enable” Control I 1 I 0 E E I 1 I 0 0 1 1 x 0 1 Y 3 Y 2 Y 1 Y 0 0 0 1 0 0 0 49

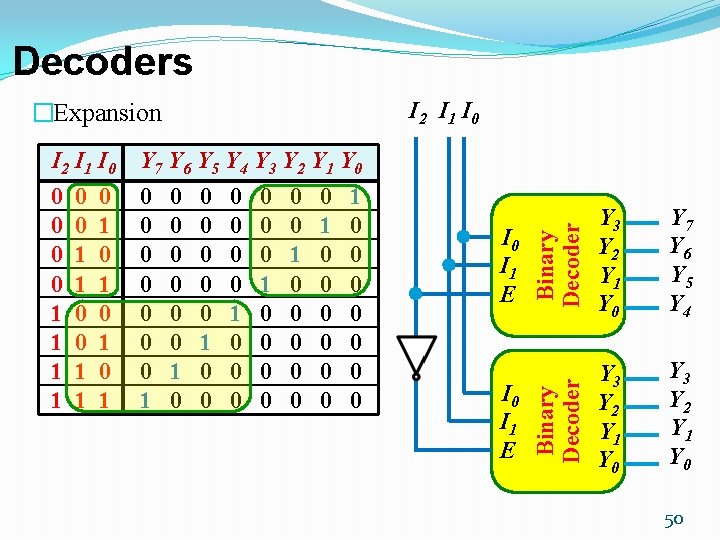

Decoders I 2 I 1 I 0 �Expansion 0 0 1 1 0 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 I 1 E I 0 I 1 E Binary Decoder 0 0 1 1 Y 3 Y 2 Y 1 Y 0 Y 7 Y 6 Y 5 Y 4 Binary Decoder I 2 I 1 I 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 50

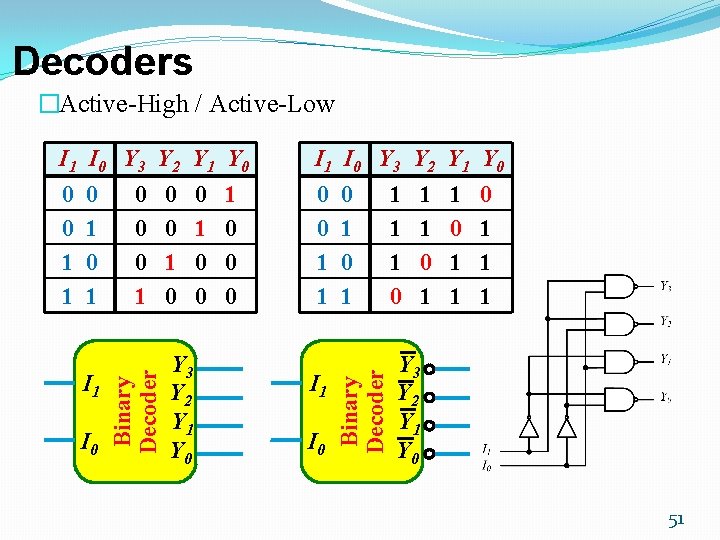

Decoders �Active-High / Active-Low I 1 I 0 Y 3 Y 2 Y 1 Y 0 0 0 1 1 I 1 I 0 0 1 Binary Decoder 0 1 0 Y 3 Y 2 Y 1 Y 0 0 1 0 0 0 I 1 I 0 0 1 1 1 1 0 Binary Decoder I 1 I 0 Y 3 Y 2 Y 1 Y 0 1 1 0 1 1 1 51

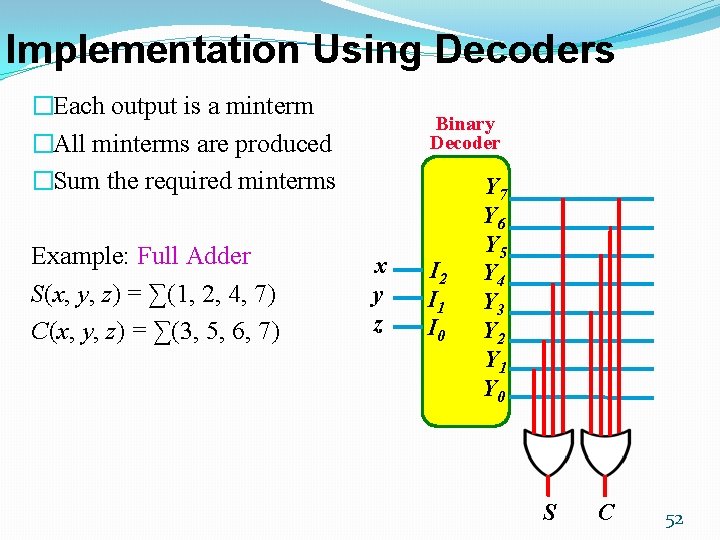

Implementation Using Decoders �Each output is a minterm �All minterms are produced �Sum the required minterms Example: Full Adder S(x, y, z) = ∑(1, 2, 4, 7) C(x, y, z) = ∑(3, 5, 6, 7) Binary Decoder x y z I 2 I 1 I 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 S C 52

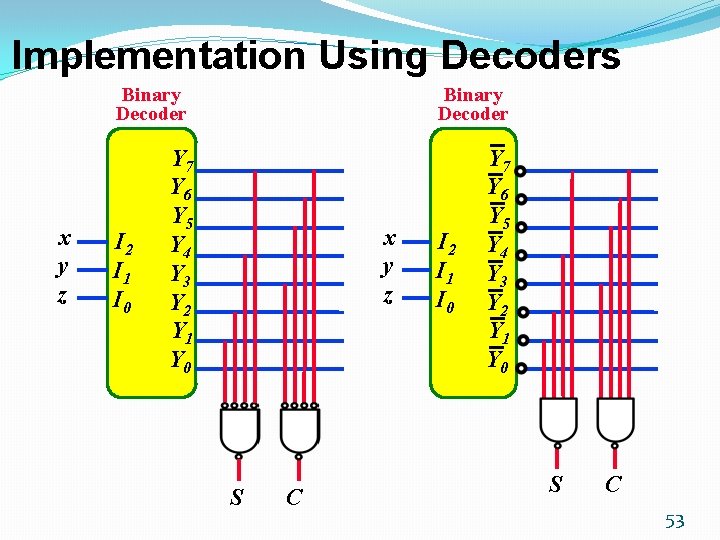

Implementation Using Decoders Binary Decoder x y z I 2 I 1 I 0 Binary Decoder Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 x y z S C I 2 I 1 I 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 S C 53

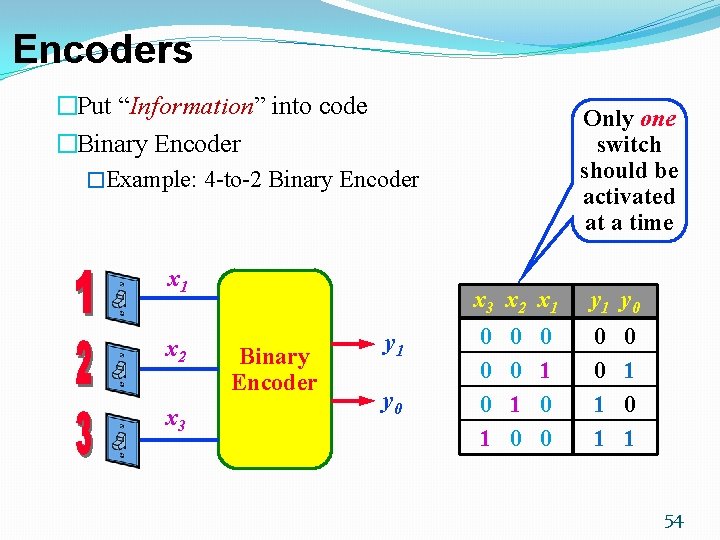

Encoders �Put “Information” into code �Binary Encoder �Example: 4 -to-2 Binary Encoder x 1 x 2 x 3 Binary Encoder y 1 y 0 Only one switch should be activated at a time x 3 x 2 x 1 y 0 0 1 0 0 1 0 1 54

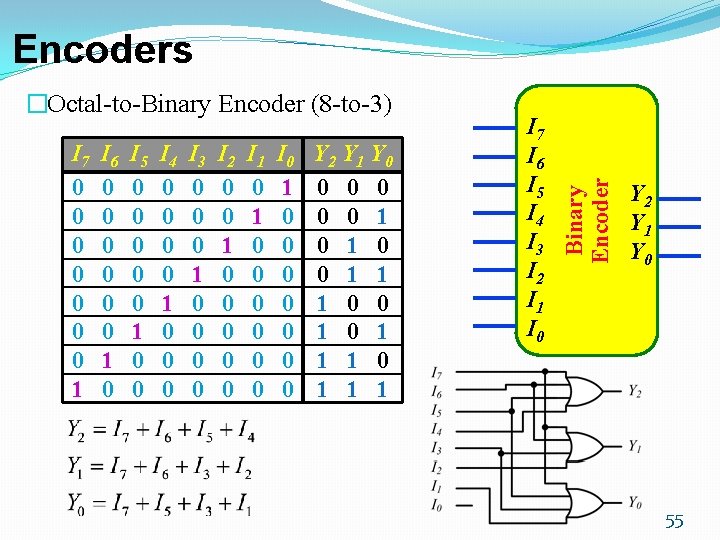

�Octal-to-Binary Encoder (8 -to-3) I 7 0 0 0 0 1 I 6 0 0 0 1 0 I 5 0 0 0 1 0 0 I 4 0 0 1 0 0 0 I 3 0 0 0 1 0 0 I 2 0 0 1 0 0 0 I 1 0 0 0 0 I 0 1 0 0 0 0 Y 2 Y 1 Y 0 0 0 1 1 1 0 0 1 1 1 I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 Binary Encoders Y 2 Y 1 Y 0 55

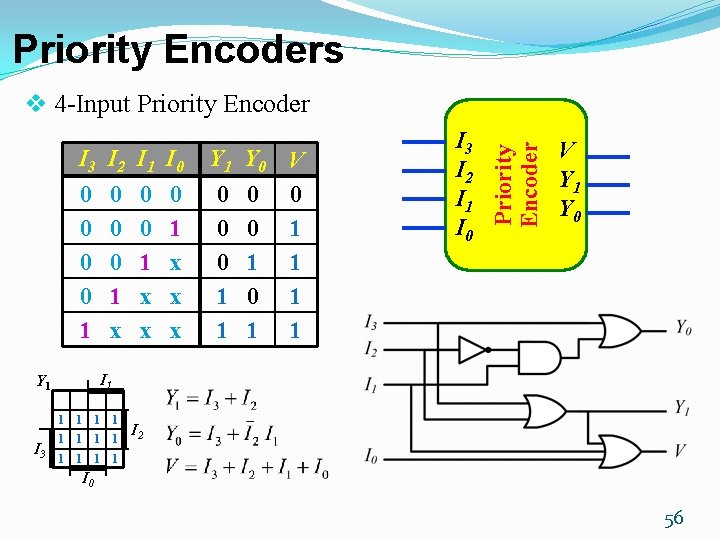

Priority Encoders I 3 I 2 I 1 I 0 0 0 1 x x x V Y 1 Y 0 I 1 Y 1 1 1 I 3 0 0 1 x x Y 1 Y 0 V 0 0 0 1 1 1 0 1 1 I 3 I 2 I 1 I 0 Priority Encoder v 4 -Input Priority Encoder 1 1 I 2 1 1 I 0 56

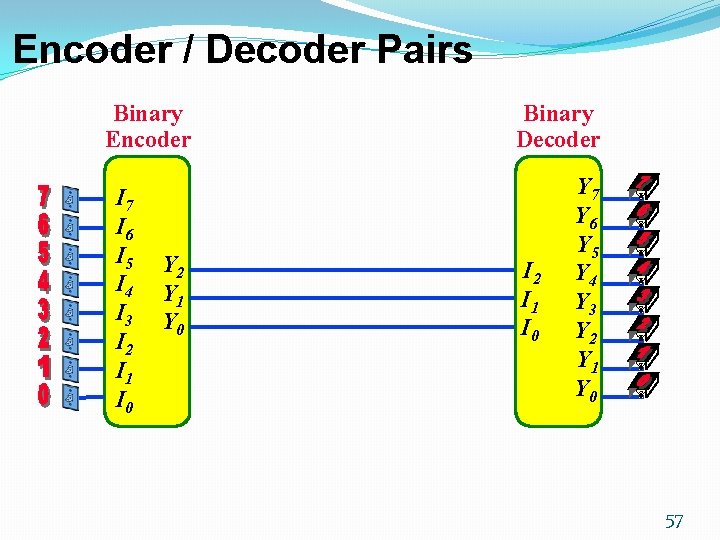

Encoder / Decoder Pairs Binary Encoder I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 Y 2 Y 1 Y 0 Binary Decoder I 2 I 1 I 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 57

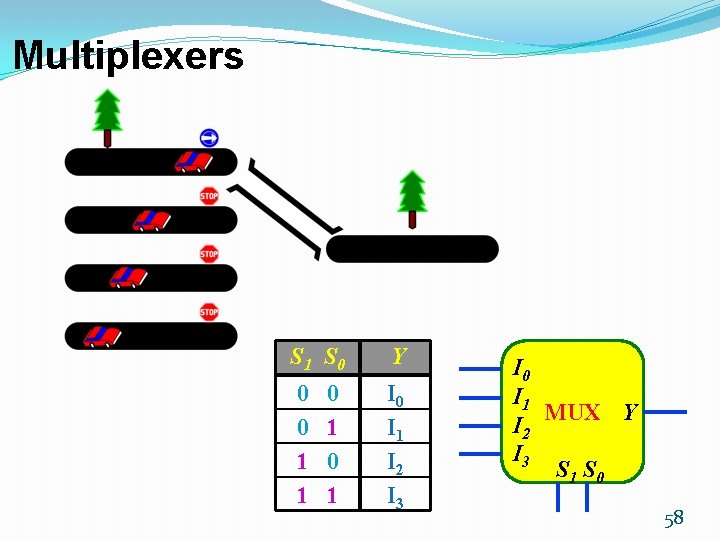

Multiplexers S 1 S 0 Y 0 0 1 1 I 0 I 1 I 2 I 3 0 1 I 0 I 1 MUX Y I 2 I 3 S 1 S 0 58

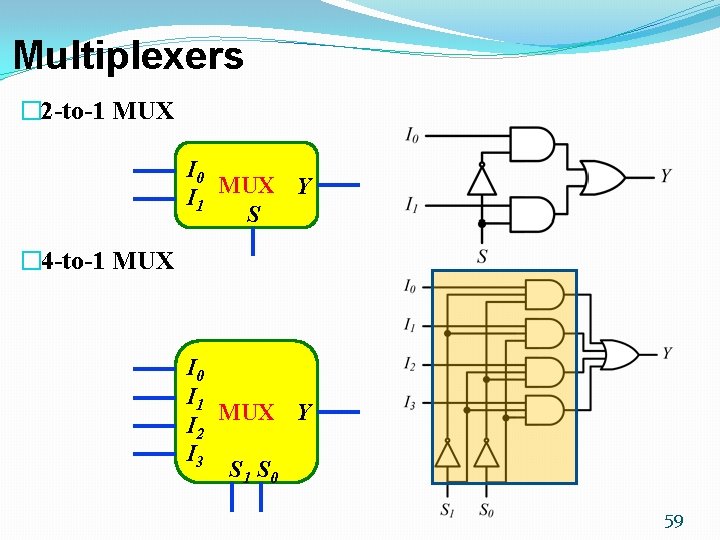

Multiplexers � 2 -to-1 MUX I 0 MUX Y I 1 S � 4 -to-1 MUX I 0 I 1 MUX Y I 2 I 3 S 1 S 0 59

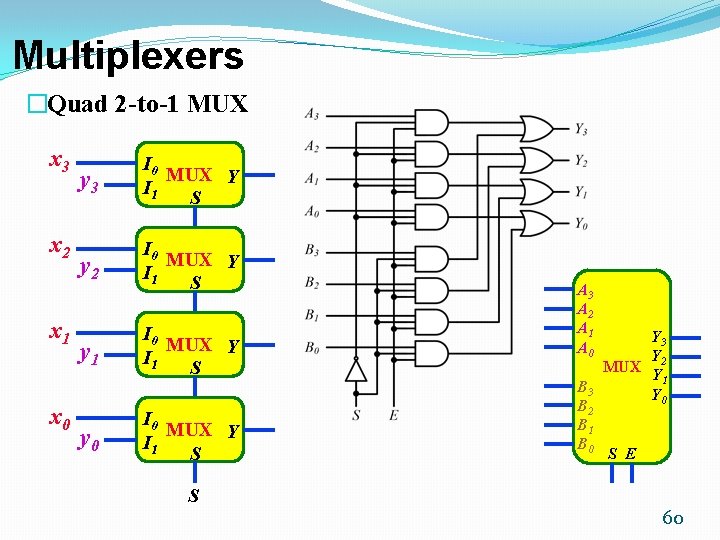

Multiplexers �Quad 2 -to-1 MUX x 3 x 2 x 1 x 0 y 3 I 0 MUX Y I 1 S y 2 I 0 MUX Y I 1 S y 1 I 0 MUX Y I 1 S y 0 I 0 MUX Y I 1 S S A 3 A 2 A 1 A 0 Y 3 Y MUX 2 Y 1 B 3 Y 0 B 2 B 1 B 0 S E 60

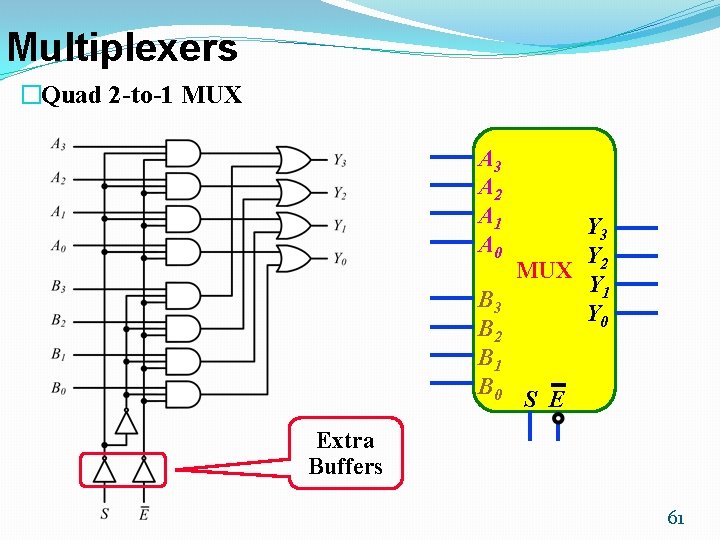

Multiplexers �Quad 2 -to-1 MUX A 3 A 2 A 1 A 0 Y 3 Y 2 MUX Y 1 B 3 Y 0 B 2 B 1 B 0 S E Extra Buffers 61

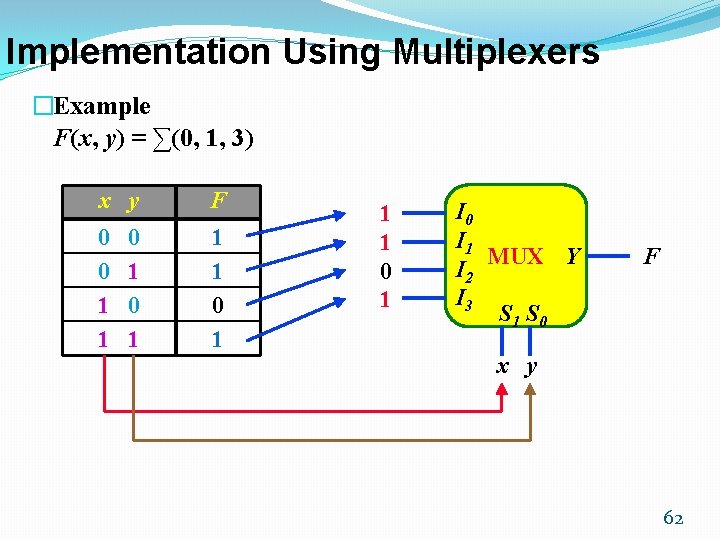

Implementation Using Multiplexers �Example F(x, y) = ∑(0, 1, 3) x y F 0 0 1 1 0 1 0 1 1 1 0 1 I 0 I 1 MUX Y I 2 I 3 S 1 S 0 F x y 62

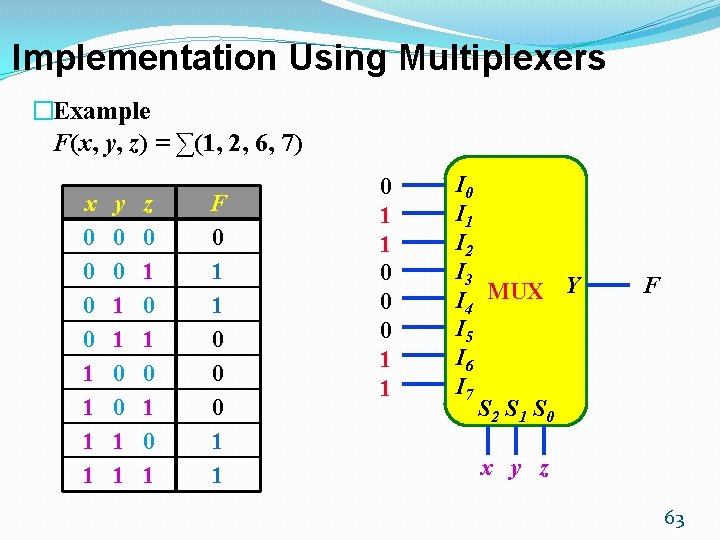

Implementation Using Multiplexers �Example F(x, y, z) = ∑(1, 2, 6, 7) x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 F 0 1 1 0 0 0 1 1 I 0 I 1 I 2 I 3 Y I 4 MUX I 5 I 6 I 7 S 2 S 1 S 0 F x y z 63

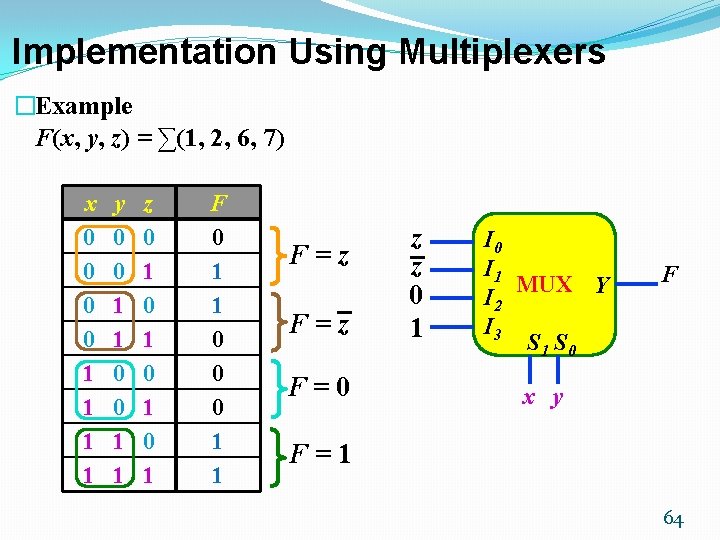

Implementation Using Multiplexers �Example F(x, y, z) = ∑(1, 2, 6, 7) x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 F 0 1 1 0 0 0 1 1 F=z F=0 z z 0 1 I 0 I 1 MUX Y I 2 I 3 S 1 S 0 F x y F=1 64

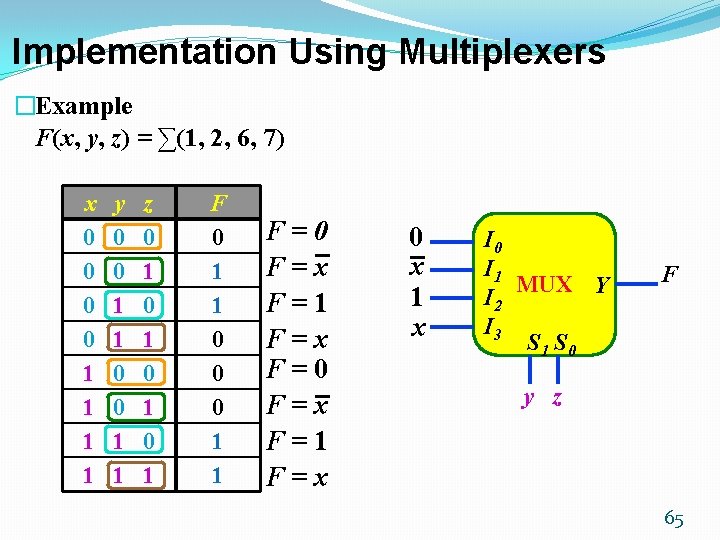

Implementation Using Multiplexers �Example F(x, y, z) = ∑(1, 2, 6, 7) x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 F 0 1 1 0 0 0 1 1 F=0 F=x F=1 F=x 0 x 1 x I 0 I 1 MUX Y I 2 I 3 S 1 S 0 F y z 65

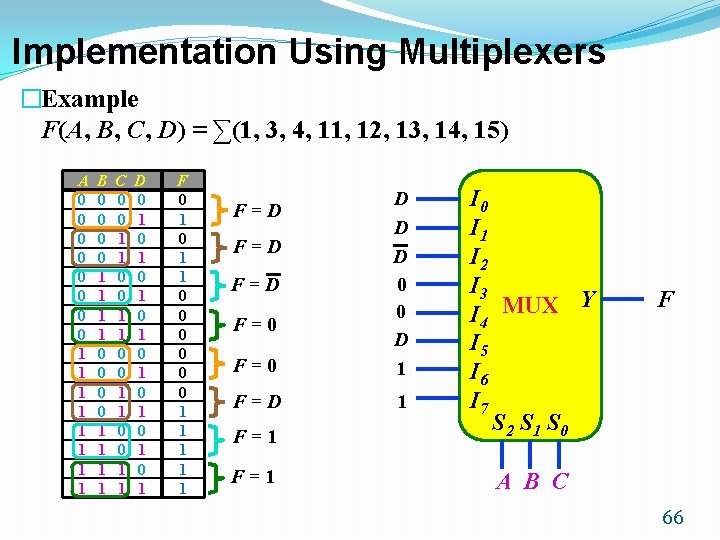

Implementation Using Multiplexers �Example F(A, B, C, D) = ∑(1, 3, 4, 11, 12, 13, 14, 15) A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 F 0 1 1 0 0 0 1 1 1 F=1 I 0 I 1 I 2 I 3 Y MUX I 4 I 5 I 6 I 7 S 2 S 1 S 0 F=1 A B C F=0 D D D 0 0 D 1 F=D F=D F=0 F 66

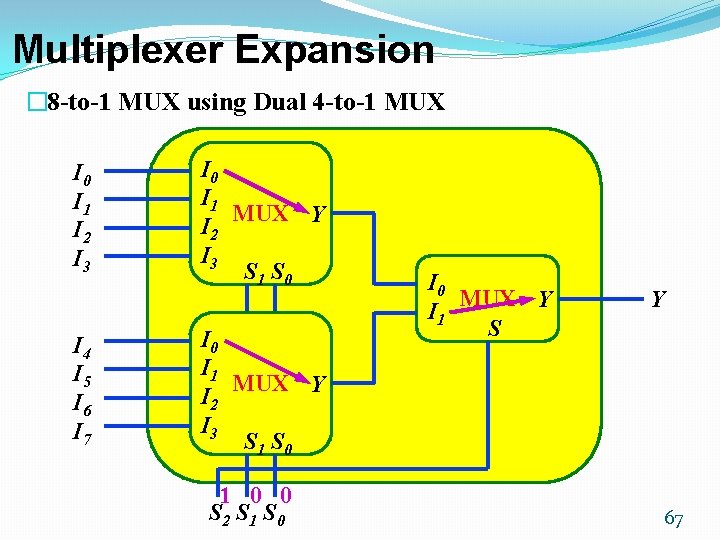

Multiplexer Expansion � 8 -to-1 MUX using Dual 4 -to-1 MUX I 0 I 1 I 2 I 3 I 4 I 5 I 6 I 7 I 0 I 1 MUX Y I 2 I 3 S 1 S 0 1 0 0 S 2 S 1 S 0 I 0 MUX Y I 1 S Y 67

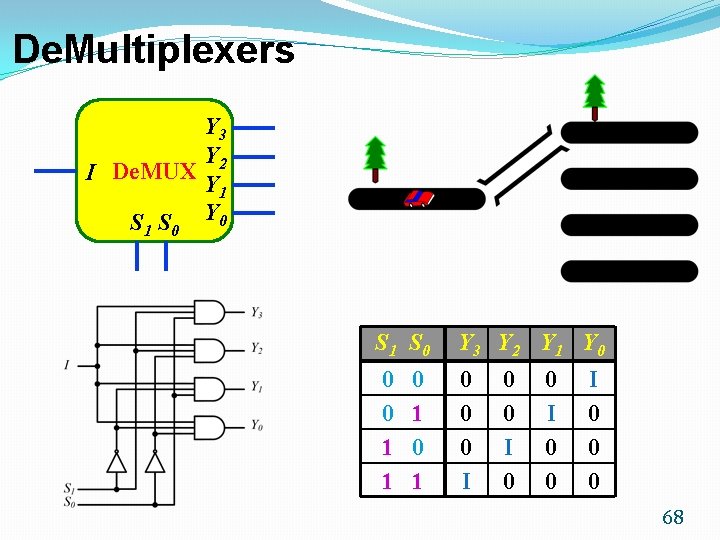

De. Multiplexers Y 3 Y 2 I De. MUX Y 1 S S Y 0 1 0 S 1 S 0 Y 3 Y 2 Y 1 Y 0 0 0 1 1 0 0 0 I 0 1 0 0 I 0 0 0 68

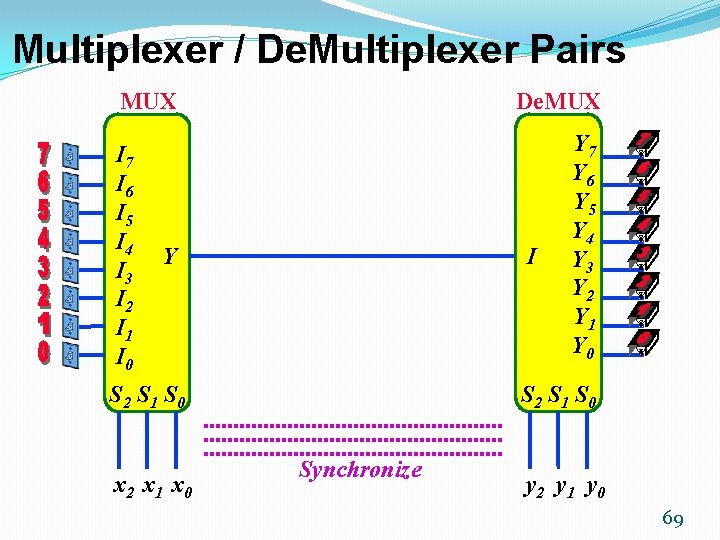

Multiplexer / De. Multiplexer Pairs MUX I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 De. MUX Y I S 2 S 1 S 0 x 2 x 1 x 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 S 2 S 1 S 0 Synchronize y 2 y 1 y 0 69

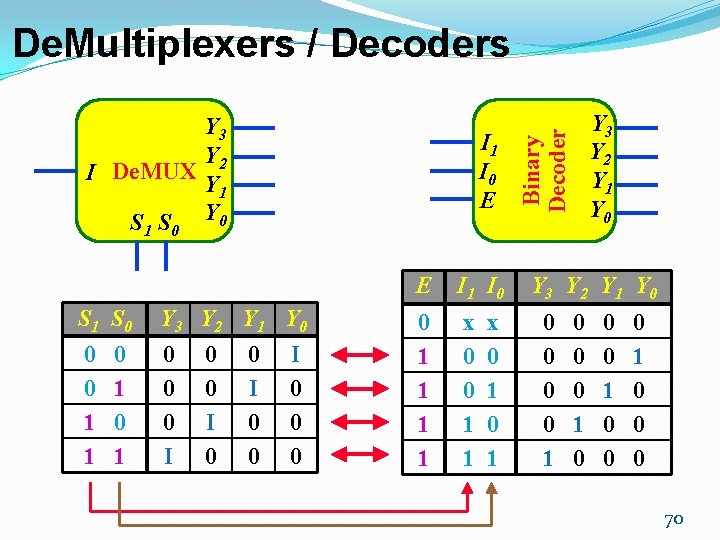

De. Multiplexers / Decoders 1 I 0 E 0 S 1 S 0 Y 3 Y 2 Y 1 Y 0 0 0 1 1 0 0 0 I 0 1 Y 3 Y 2 Y 1 Y 0 Binary Decoder Y 3 Y 2 I De. MUX Y 1 S S Y 0 0 0 I 0 0 0 E I 1 I 0 0 1 1 x 0 1 Y 3 Y 2 Y 1 Y 0 0 0 1 0 0 0 70

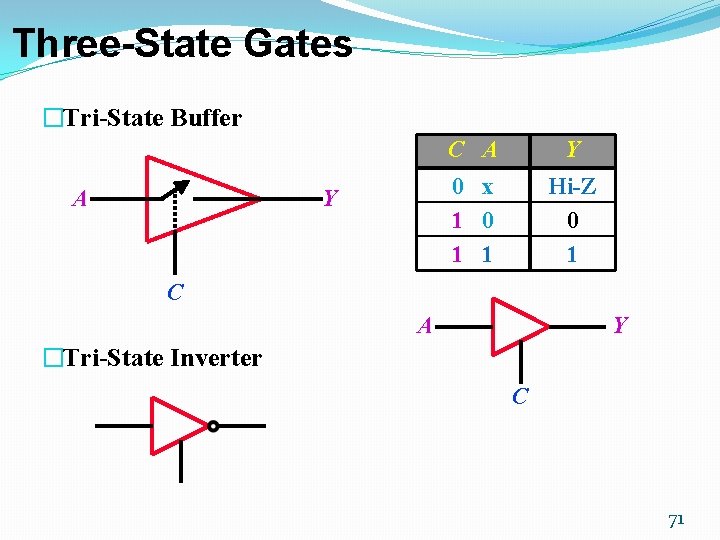

Three-State Gates �Tri-State Buffer A Y C A Y 0 x 1 0 1 1 Hi-Z 0 1 C A Y �Tri-State Inverter C 71

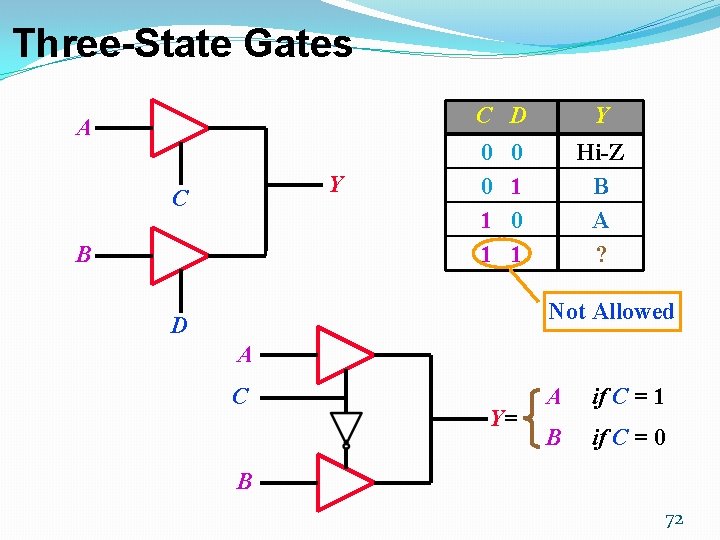

Three-State Gates C D A Y C B 0 0 1 1 Y 0 1 Hi-Z B A ? Not Allowed D A C Y= A if C = 1 B if C = 0 B 72

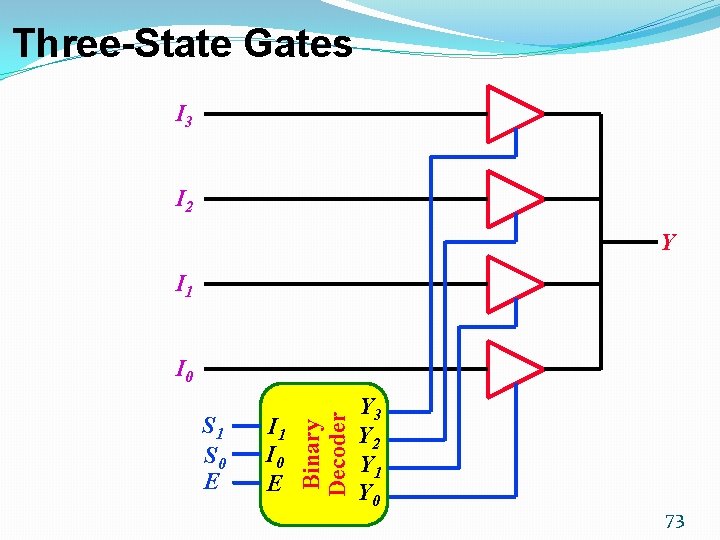

Three-State Gates I 3 I 2 Y I 1 S 0 E I 1 I 0 E Binary Decoder I 0 Y 3 Y 2 Y 1 Y 0 73

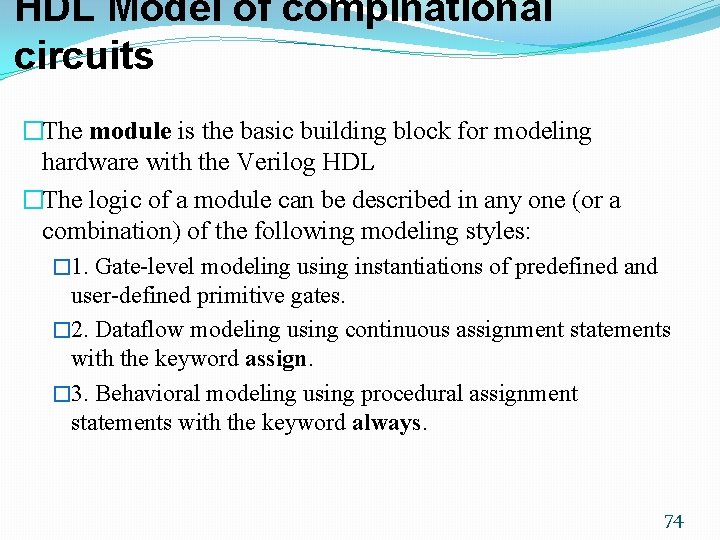

HDL Model of compinational circuits �The module is the basic building block for modeling hardware with the Verilog HDL �The logic of a module can be described in any one (or a combination) of the following modeling styles: � 1. Gate-level modeling using instantiations of predefined and user-defined primitive gates. � 2. Dataflow modeling using continuous assignment statements with the keyword assign. � 3. Behavioral modeling using procedural assignment statements with the keyword always. 74

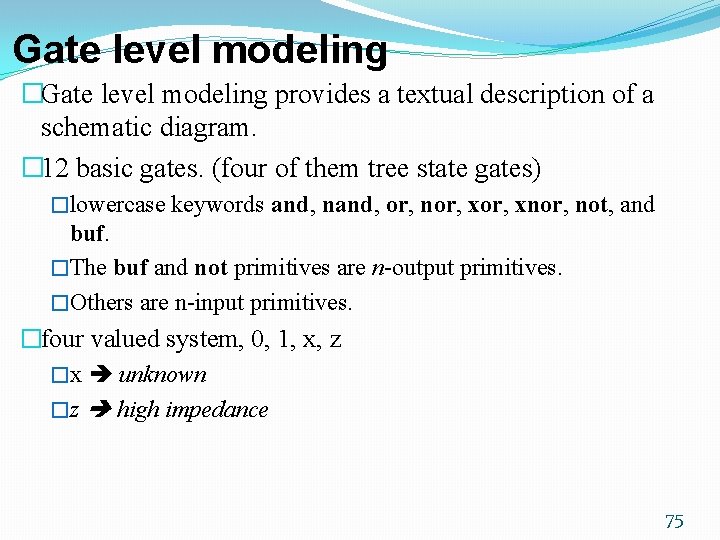

Gate level modeling �Gate level modeling provides a textual description of a schematic diagram. � 12 basic gates. (four of them tree state gates) �lowercase keywords and, nand, or, nor, xnor, not, and buf. �The buf and not primitives are n-output primitives. �Others are n-input primitives. �four valued system, 0, 1, x, z �x unknown �z high impedance 75

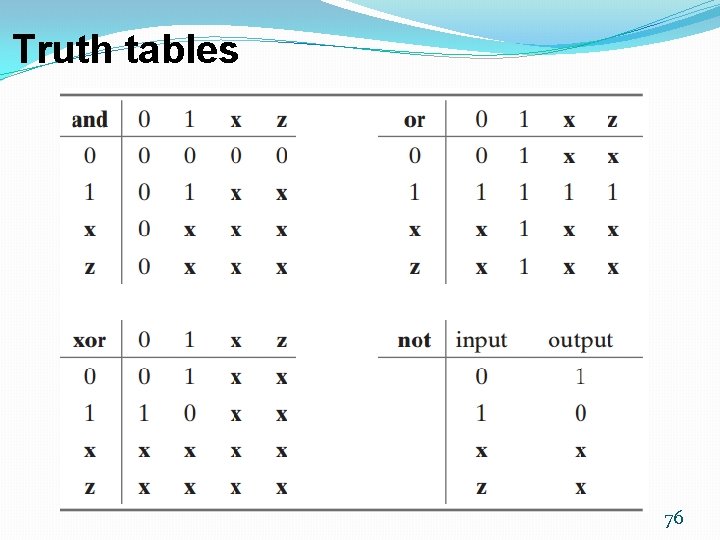

Truth tables 76

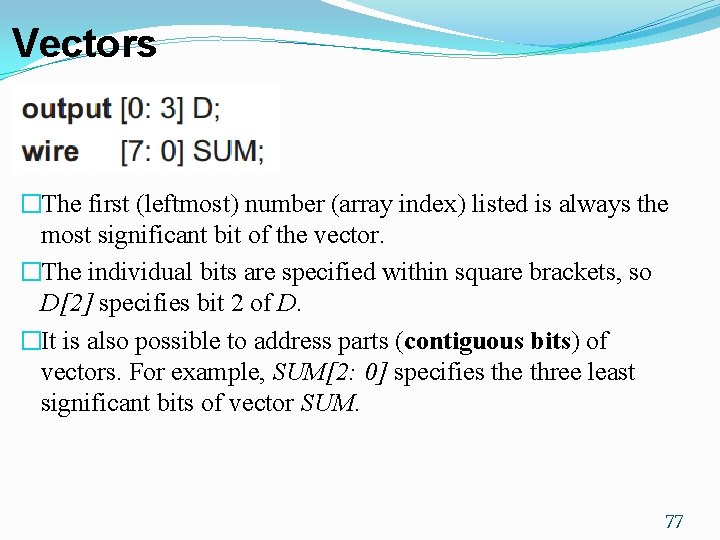

Vectors �The first (leftmost) number (array index) listed is always the most significant bit of the vector. �The individual bits are specified within square brackets, so D[2] specifies bit 2 of D. �It is also possible to address parts (contiguous bits) of vectors. For example, SUM[2: 0] specifies the three least significant bits of vector SUM. 77

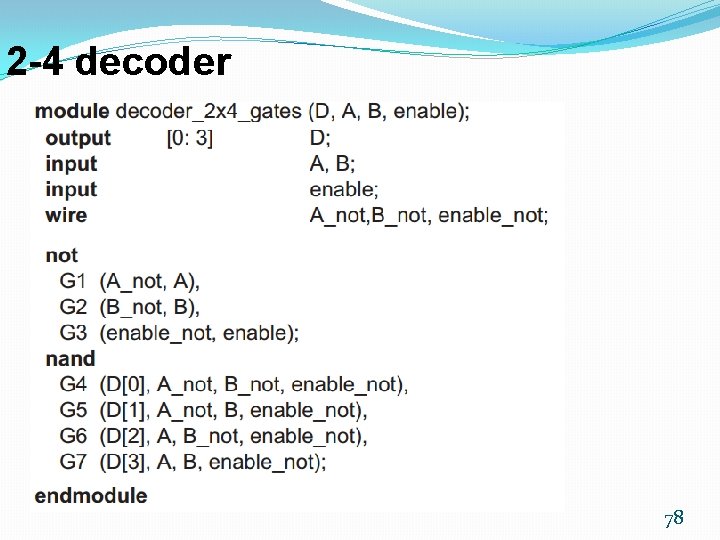

2 -4 decoder 78

Design methodology �Two or more modules can be combined to build a hierarchical description of a design. �There are two basic types of design methodologies: top down and bottom up. �In a top-down design, the top-level block is defined and then the sub-blocks necessary to build the top-level block are identified. �In a bottom-up design, the building blocks are first identified and then combined to build the top-level block. 79

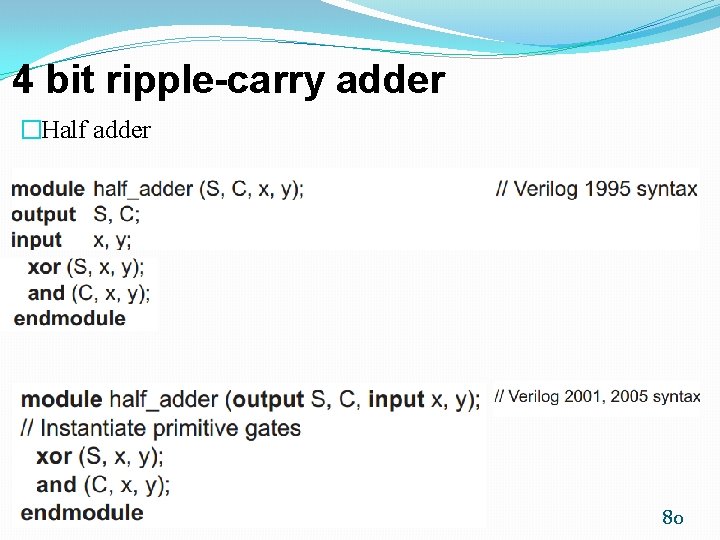

4 bit ripple-carry adder �Half adder 80

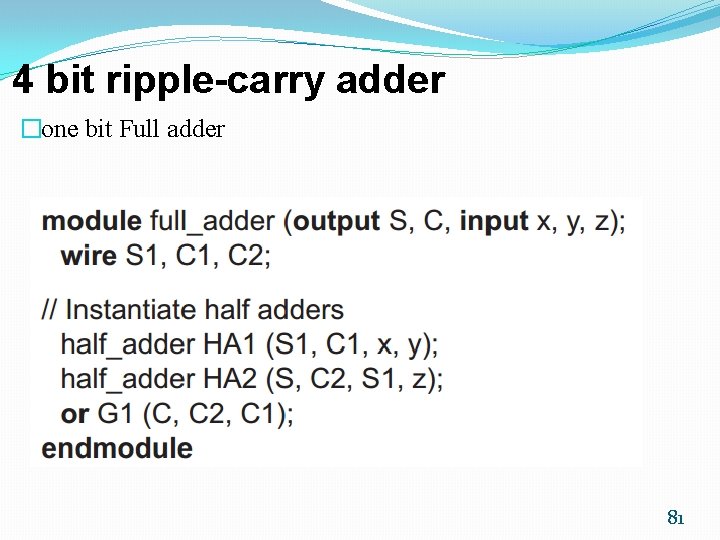

4 bit ripple-carry adder �one bit Full adder 81

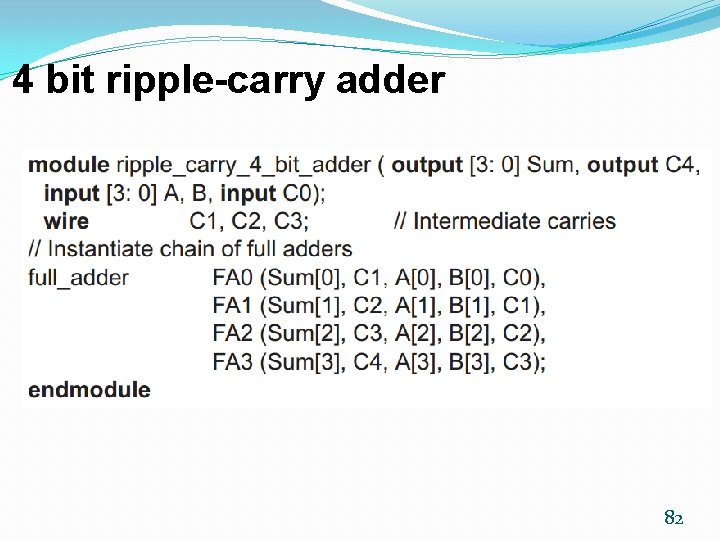

4 bit ripple-carry adder 82

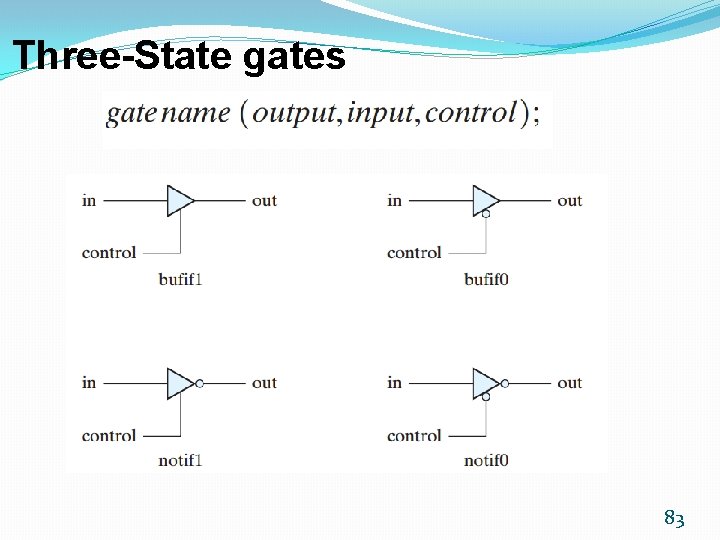

Three-State gates 83

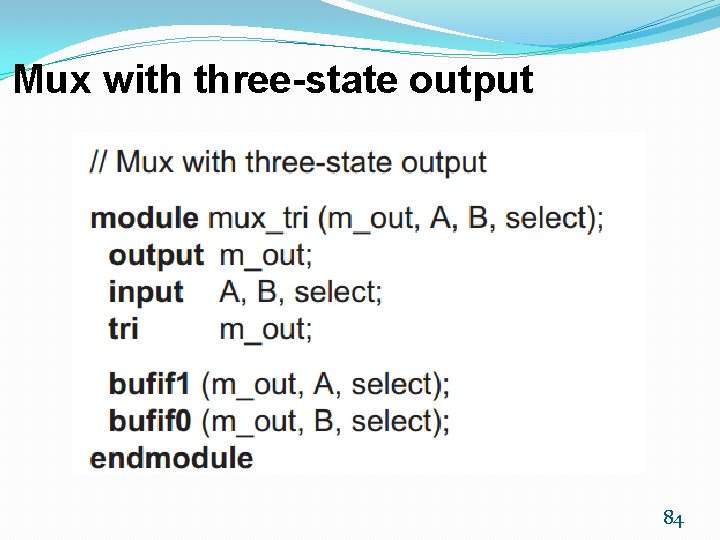

Mux with three-state output 84

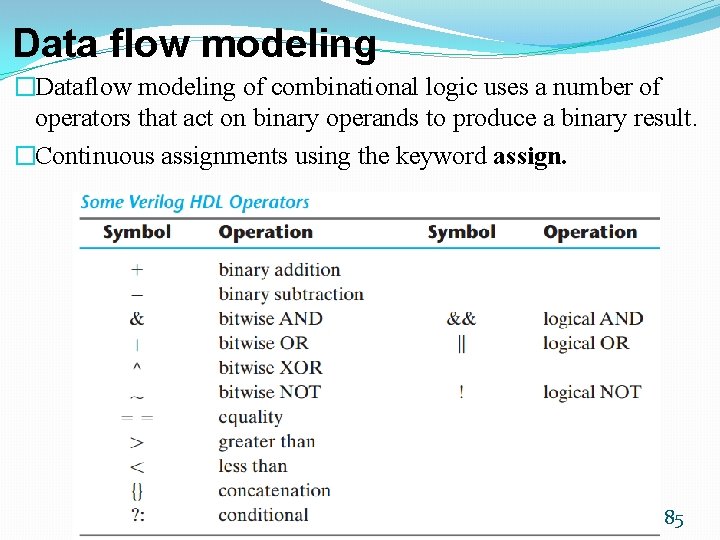

Data flow modeling �Dataflow modeling of combinational logic uses a number of operators that act on binary operands to produce a binary result. �Continuous assignments using the keyword assign. 85

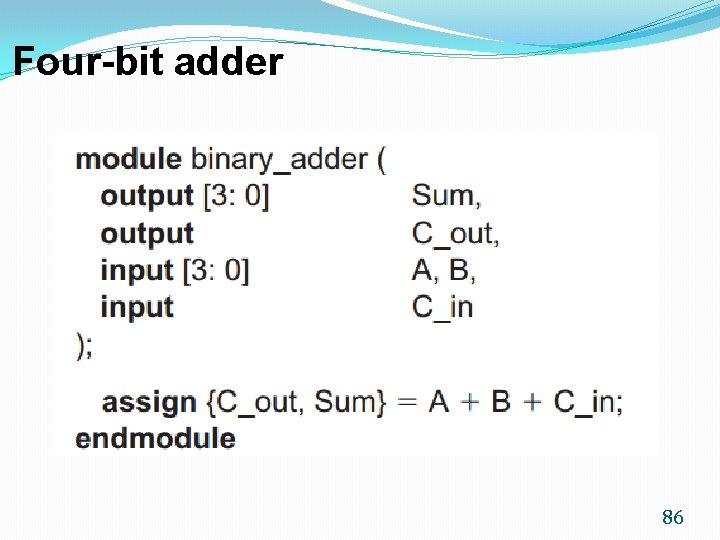

Four-bit adder 86

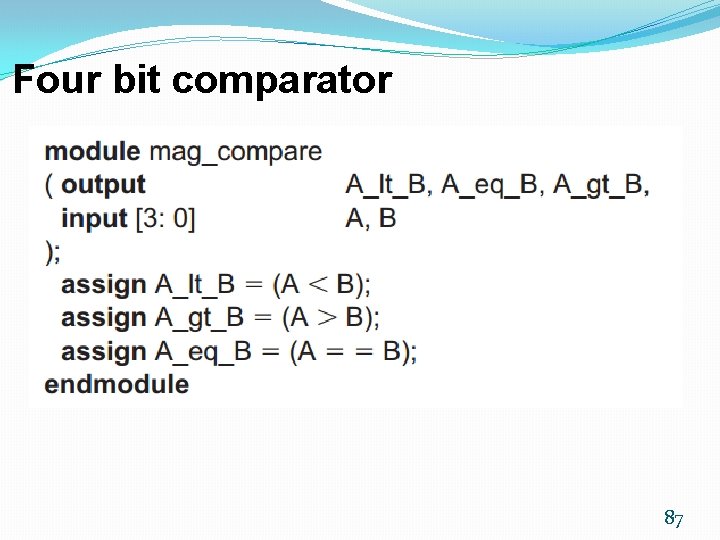

Four bit comparator 87

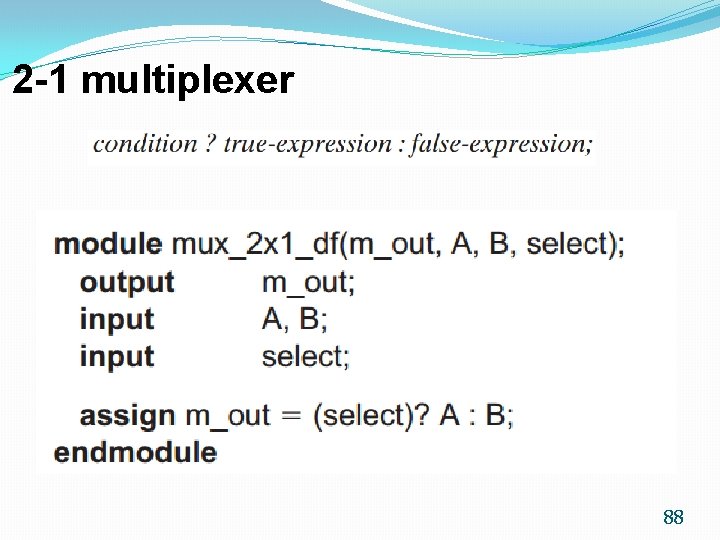

2 -1 multiplexer 88

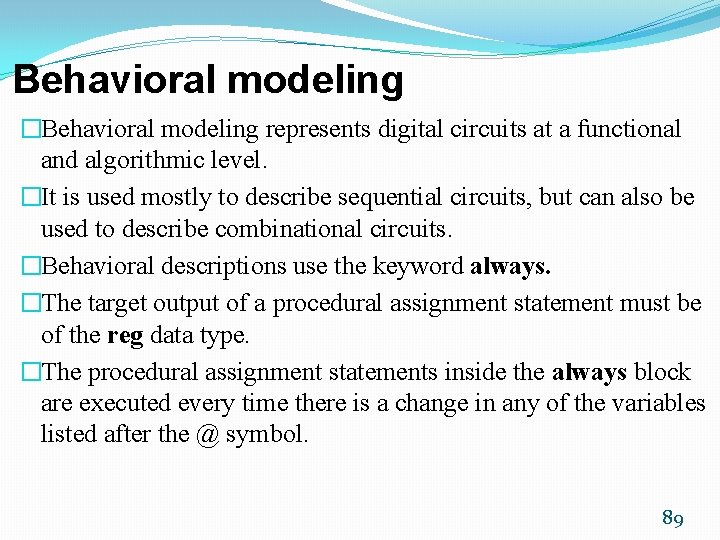

Behavioral modeling �Behavioral modeling represents digital circuits at a functional and algorithmic level. �It is used mostly to describe sequential circuits, but can also be used to describe combinational circuits. �Behavioral descriptions use the keyword always. �The target output of a procedural assignment statement must be of the reg data type. �The procedural assignment statements inside the always block are executed every time there is a change in any of the variables listed after the @ symbol. 89

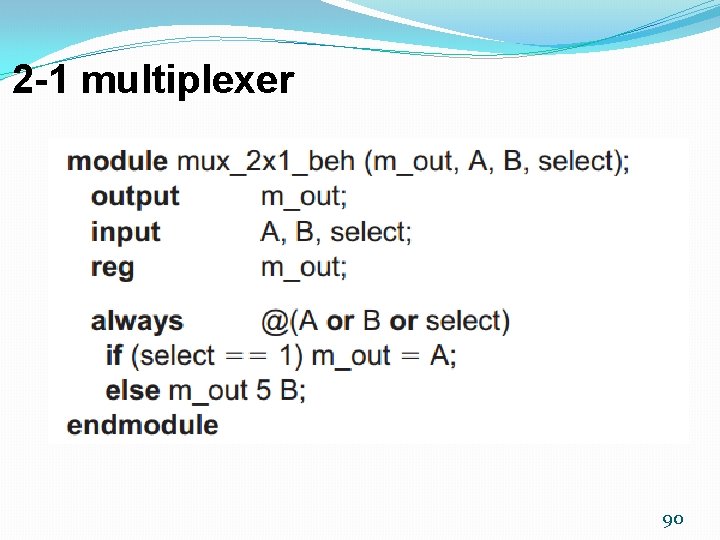

2 -1 multiplexer 90

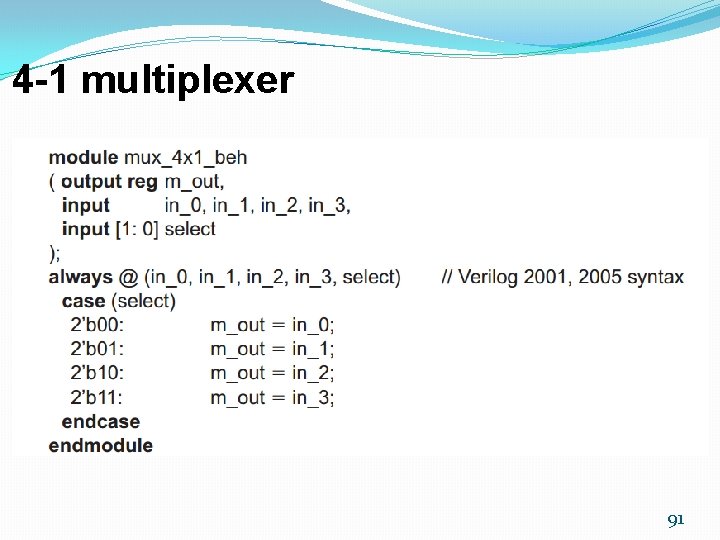

4 -1 multiplexer 91

![Number representation �[size]’[base][value] �b, B Binary, h, H Hex, d, D Decimal, o, O Number representation �[size]’[base][value] �b, B Binary, h, H Hex, d, D Decimal, o, O](http://slidetodoc.com/presentation_image_h2/86e35b268bb8aea790f49aeca1dd12ca/image-92.jpg)

Number representation �[size]’[base][value] �b, B Binary, h, H Hex, d, D Decimal, o, O Octal �Default base is 10 �The underscore (_) may be inserted in a number to improve readability of the code. � 16’b 0101_1110_0101_0011 � 16’h 5_E_5_3 92

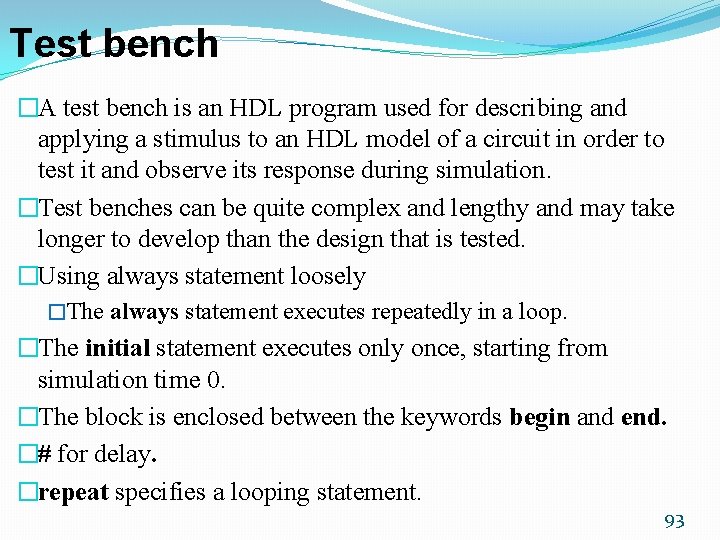

Test bench �A test bench is an HDL program used for describing and applying a stimulus to an HDL model of a circuit in order to test it and observe its response during simulation. �Test benches can be quite complex and lengthy and may take longer to develop than the design that is tested. �Using always statement loosely �The always statement executes repeatedly in a loop. �The initial statement executes only once, starting from simulation time 0. �The block is enclosed between the keywords begin and end. �# for delay. �repeat specifies a looping statement. 93

Test bench 94

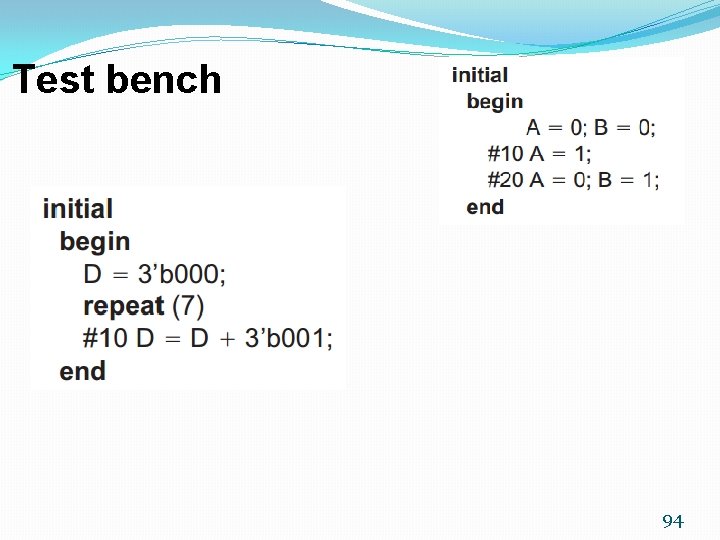

Test bench 95

Test bench �A test module is written like any other module, but it typically has no inputs or outputs. �The signals that are applied as inputs to the design module for simulation are declared in the stimulus module as local reg data type. �The outputs of the design module that are displayed for testing are declared in the stimulus module as local wire data type. �The module under test is then instantiated, using the local identifiers in its port list. 96

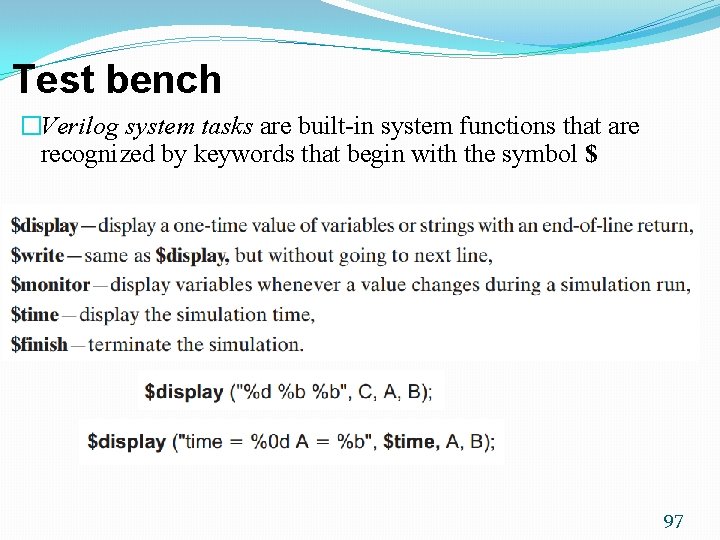

Test bench �Verilog system tasks are built-in system functions that are recognized by keywords that begin with the symbol $ 97

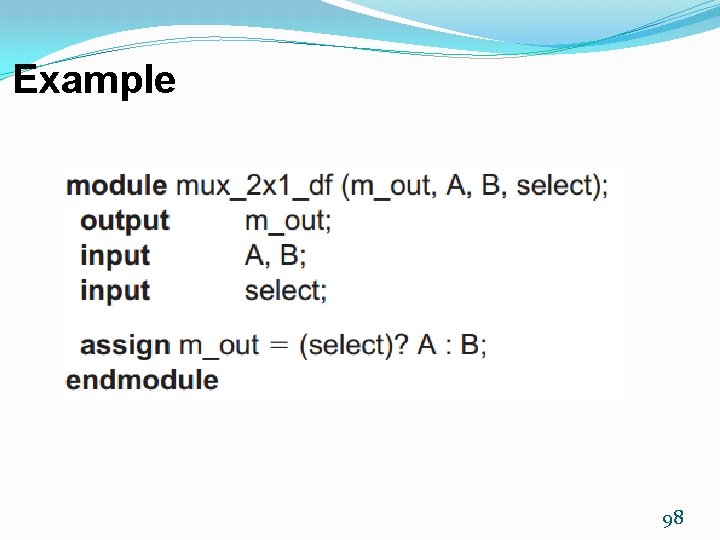

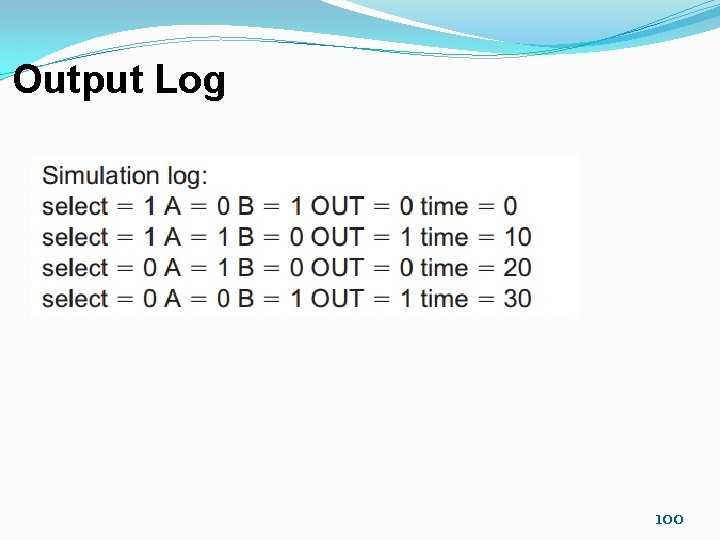

Example 98

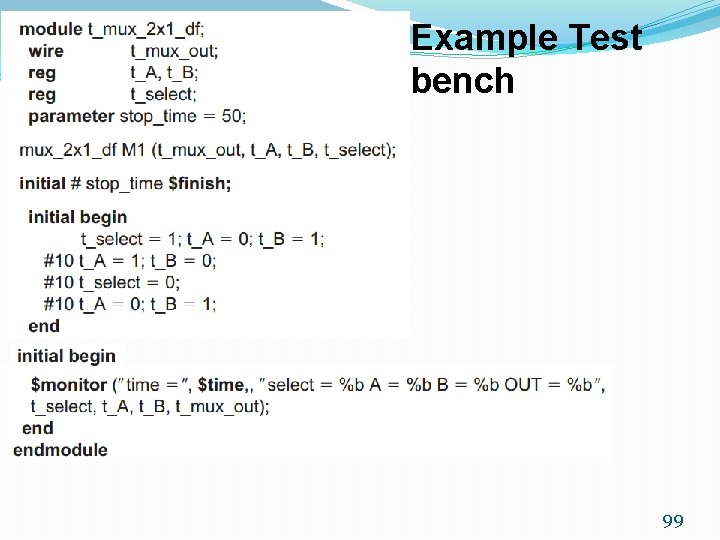

Example Test bench 99

Output Log 100

Home works � 4. 5, 4. 6, 4. 15, 4. 17, 4. 23, 4. 25, 4. 27, 4. 28, 4. 32, 4. 33, 4. 36, 4. 37, 4. 40, 4. 41, 4. 43, 4. 45 101

- Slides: 101