Lecture 13 Topics Latches Flip Flops Algorithmic State

- Slides: 72

Lecture 13 • Topics – Latches – Flip Flops – Algorithmic State Machines 1

Latches

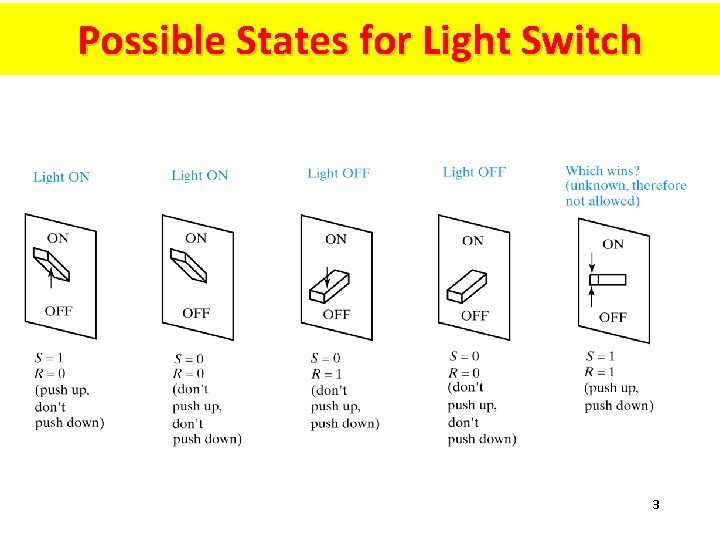

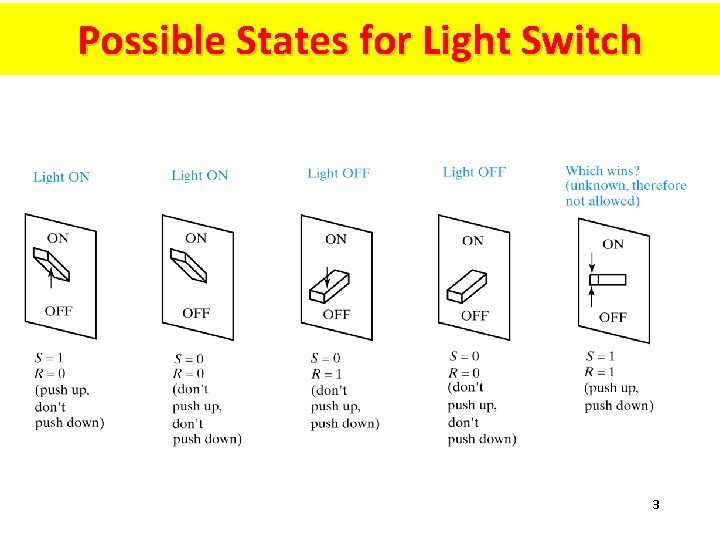

Possible States for Light Switch 3

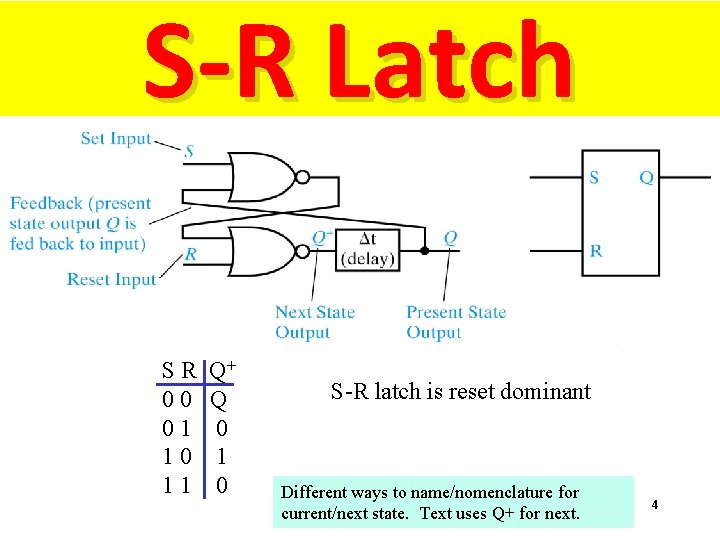

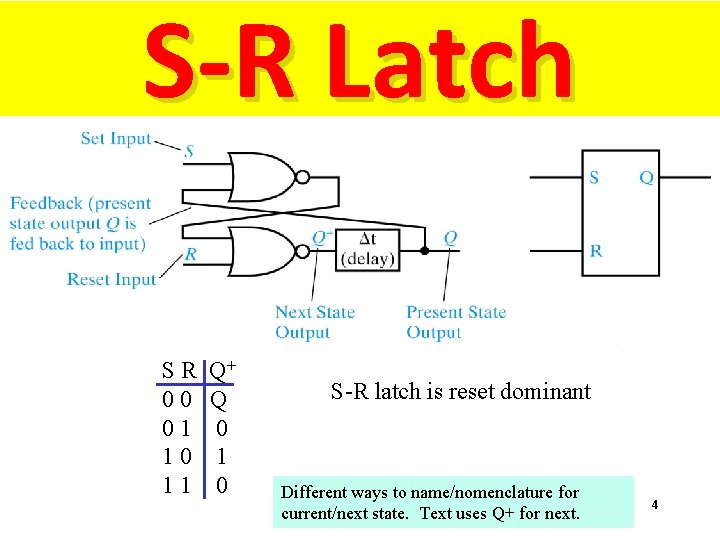

S-R Latch SR 00 01 10 11 Q+ Q 0 1 0 S-R latch is reset dominant Different ways to name/nomenclature for current/next state. Text uses Q+ for next. 4

Alternative Nomenclature for latches Present State Output Symbol Q Q Qt Qn Q 0 Y y Next State Output Symbol Q Q(t+1) Q(n+1) Q Y+ Y 5

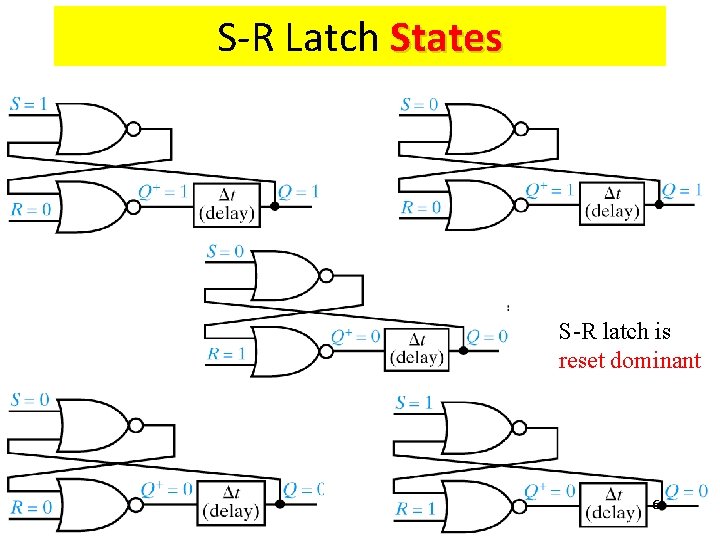

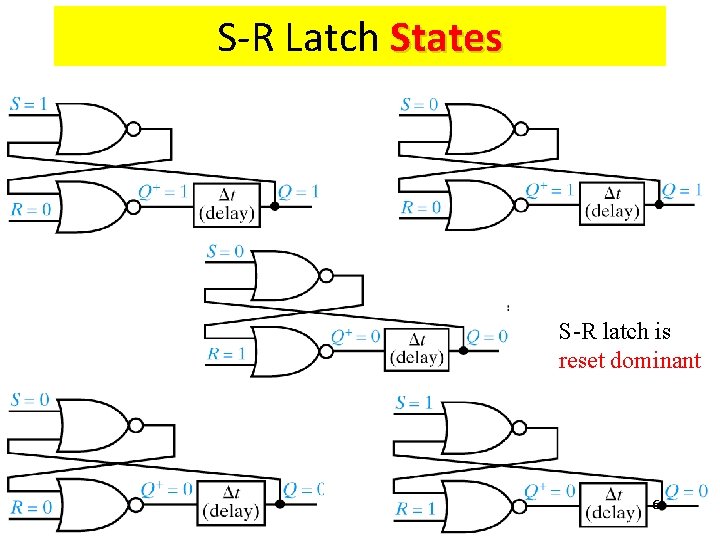

S-R Latch States S-R latch is reset dominant 6

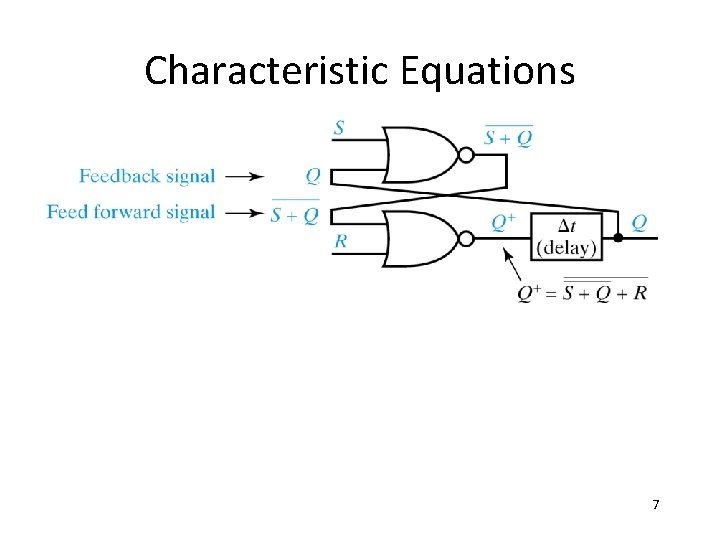

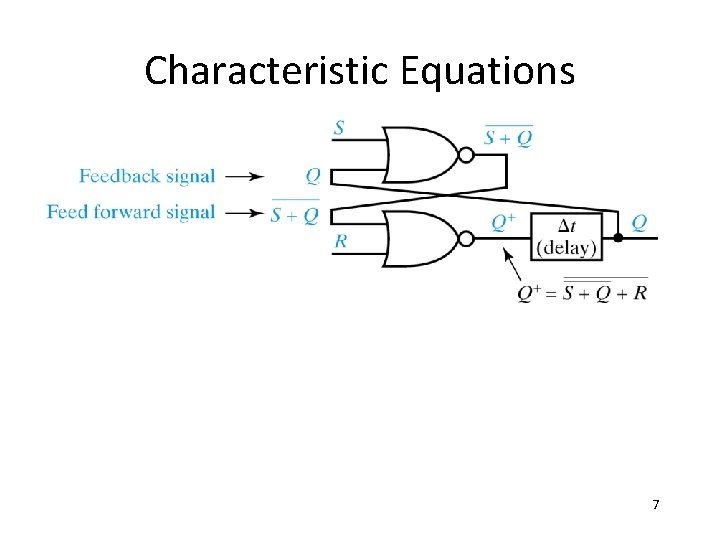

Characteristic Equations 7

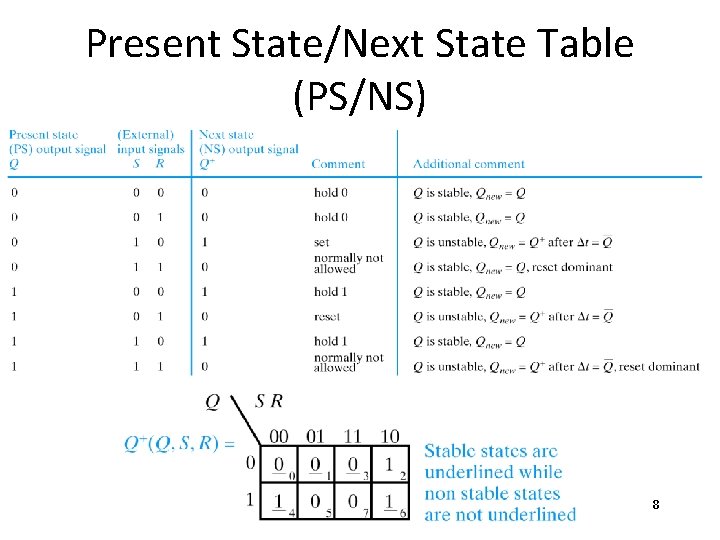

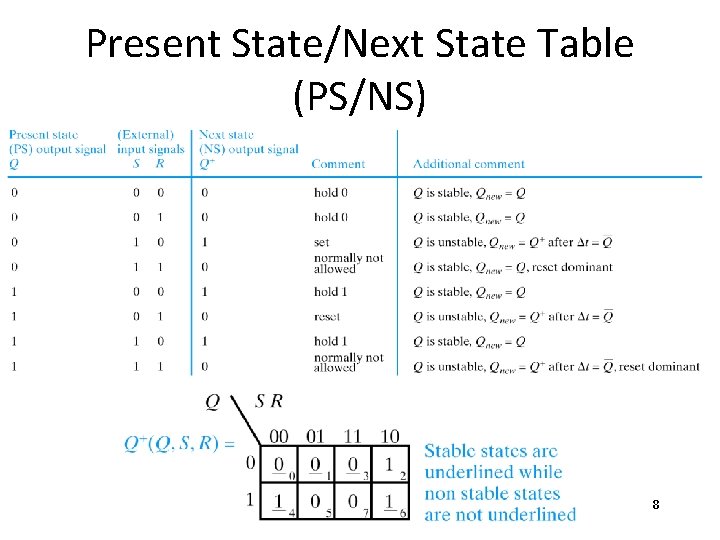

Present State/Next State Table (PS/NS) 8

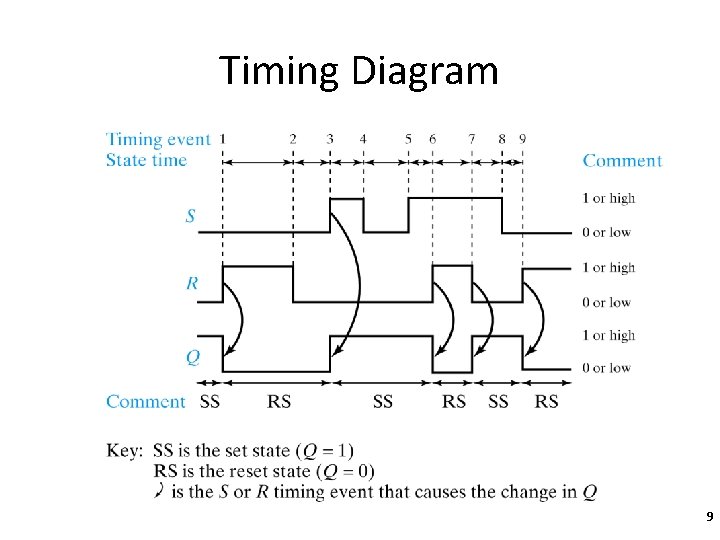

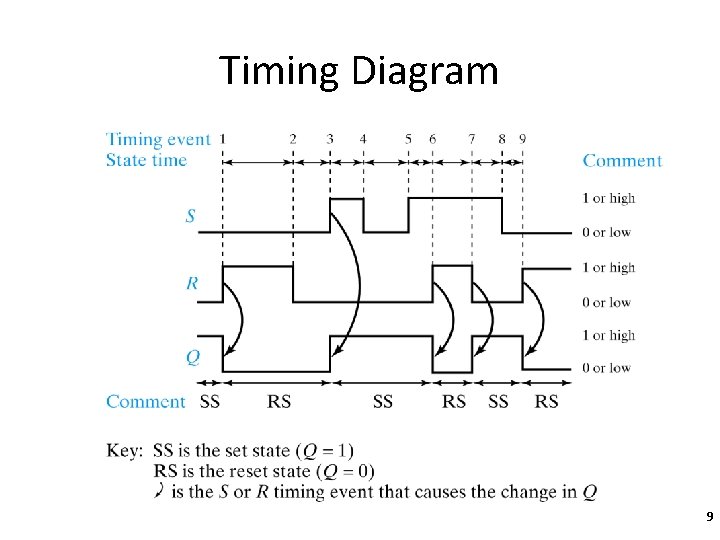

Timing Diagram 9

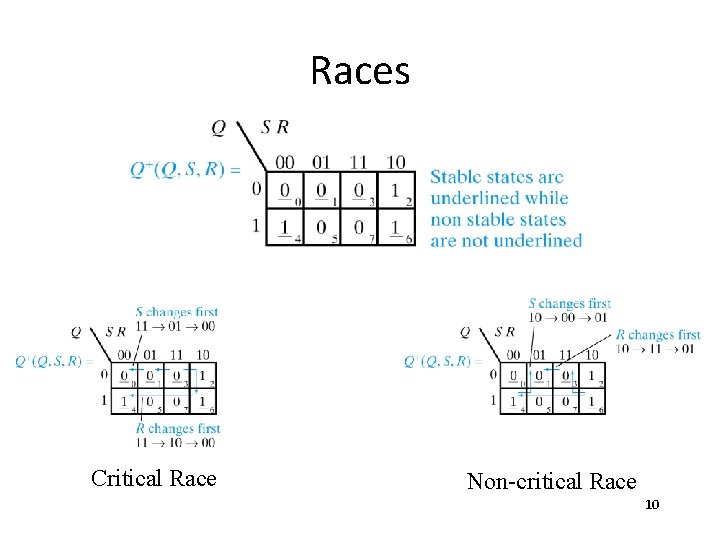

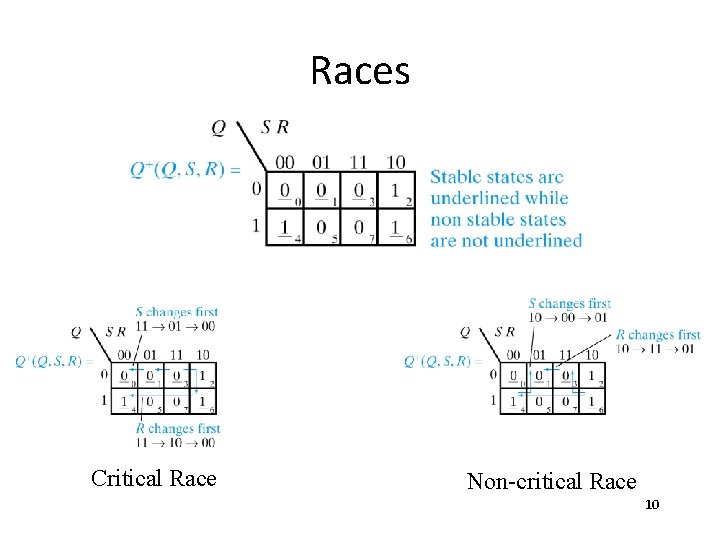

Races Critical Race Non-critical Race 10

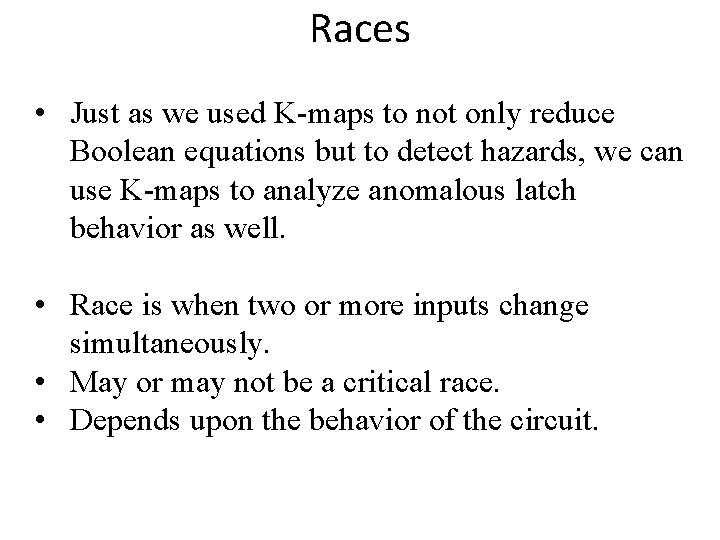

Races • Just as we used K-maps to not only reduce Boolean equations but to detect hazards, we can use K-maps to analyze anomalous latch behavior as well. • Race is when two or more inputs change simultaneously. • May or may not be a critical race. • Depends upon the behavior of the circuit.

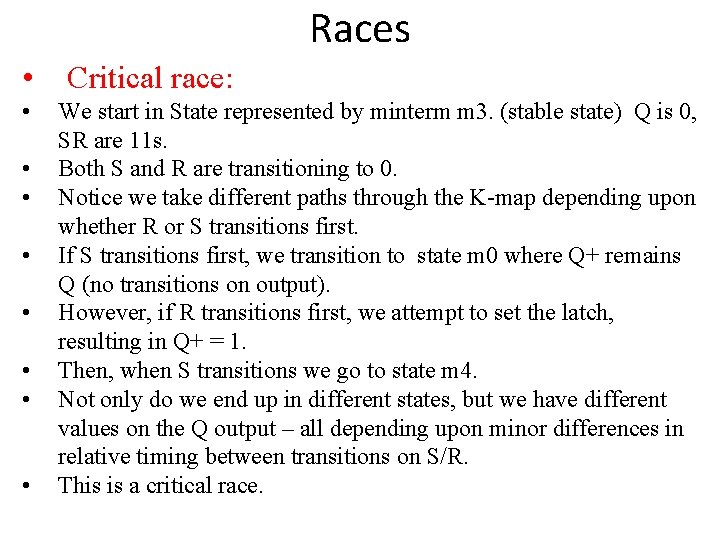

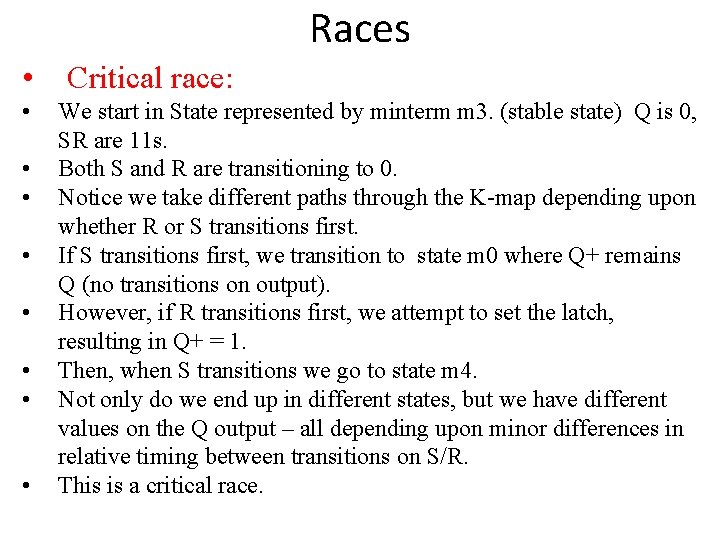

Races • • • Critical race: We start in State represented by minterm m 3. (stable state) Q is 0, SR are 11 s. Both S and R are transitioning to 0. Notice we take different paths through the K-map depending upon whether R or S transitions first. If S transitions first, we transition to state m 0 where Q+ remains Q (no transitions on output). However, if R transitions first, we attempt to set the latch, resulting in Q+ = 1. Then, when S transitions we go to state m 4. Not only do we end up in different states, but we have different values on the Q output – all depending upon minor differences in relative timing between transitions on S/R. This is a critical race.

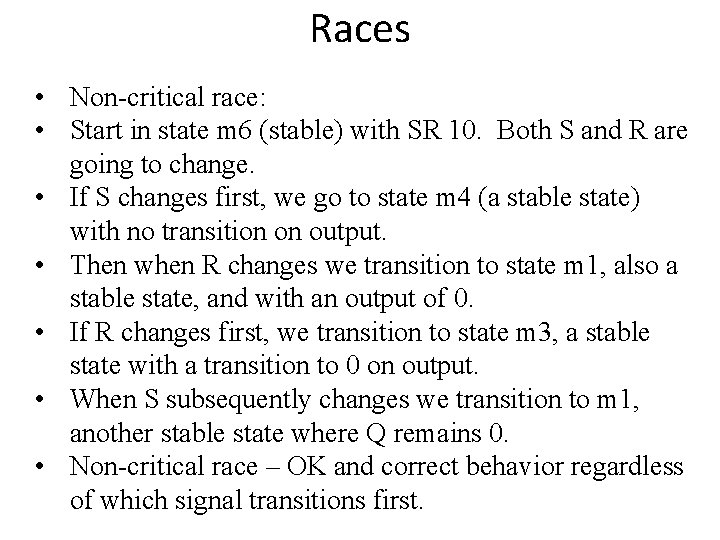

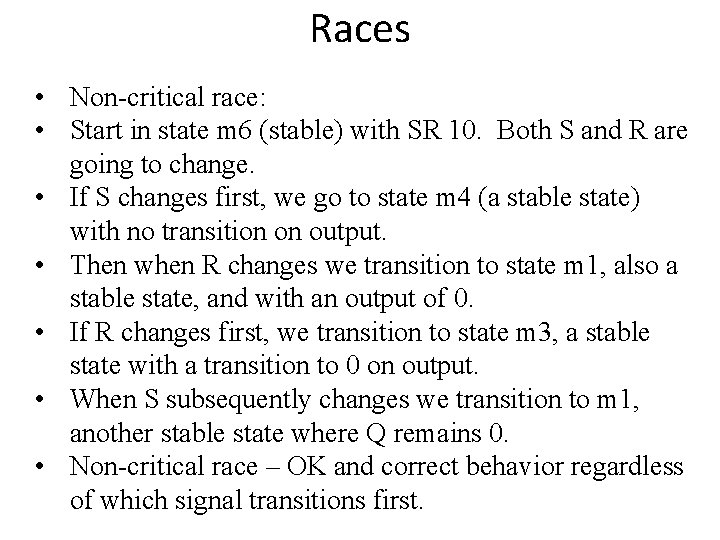

Races • Non-critical race: • Start in state m 6 (stable) with SR 10. Both S and R are going to change. • If S changes first, we go to state m 4 (a stable state) with no transition on output. • Then when R changes we transition to state m 1, also a stable state, and with an output of 0. • If R changes first, we transition to state m 3, a stable state with a transition to 0 on output. • When S subsequently changes we transition to m 1, another stable state where Q remains 0. • Non-critical race – OK and correct behavior regardless of which signal transitions first.

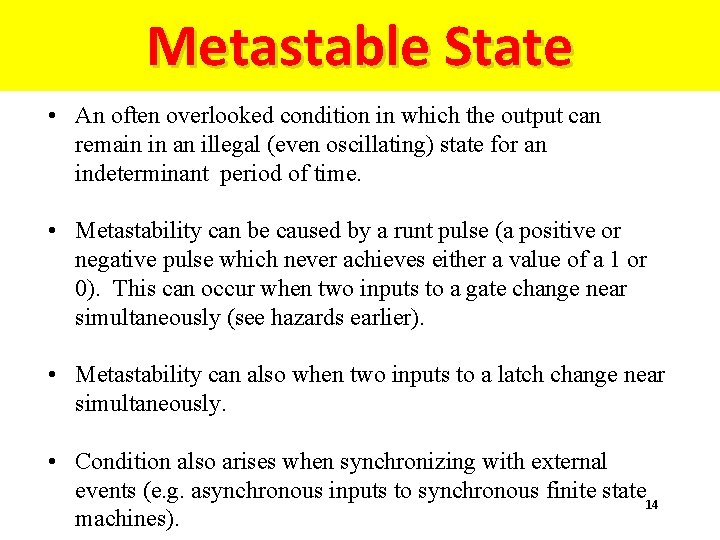

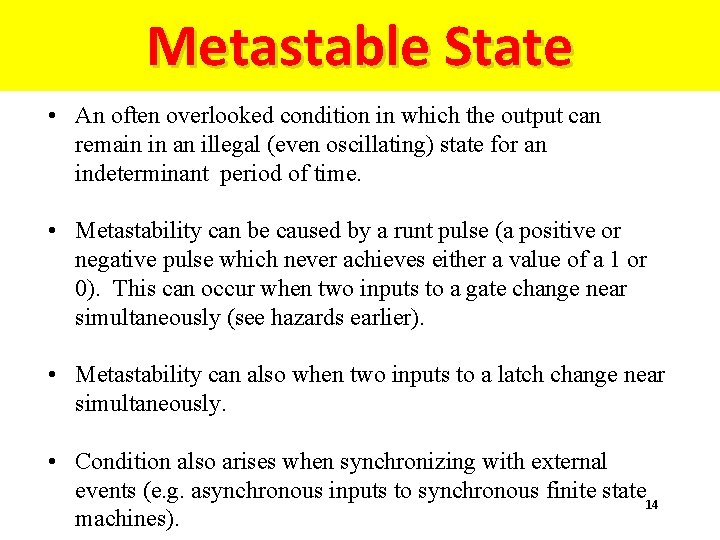

Metastable State • An often overlooked condition in which the output can remain in an illegal (even oscillating) state for an indeterminant period of time. • Metastability can be caused by a runt pulse (a positive or negative pulse which never achieves either a value of a 1 or 0). This can occur when two inputs to a gate change near simultaneously (see hazards earlier). • Metastability can also when two inputs to a latch change near simultaneously. • Condition also arises when synchronizing with external events (e. g. asynchronous inputs to synchronous finite state 14 machines).

State Machines

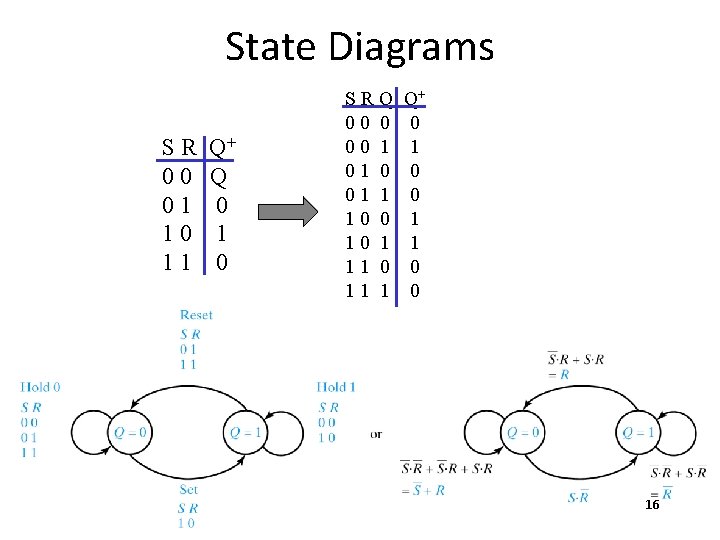

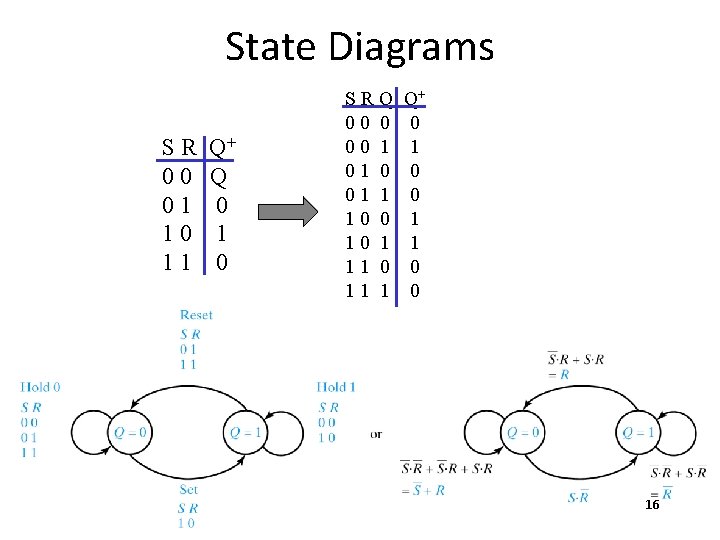

State Diagrams SR 00 01 10 11 Q+ Q 0 1 0 SRQ 00 0 00 1 01 0 01 1 10 0 10 1 11 0 11 1 Q+ 0 1 0 0 16

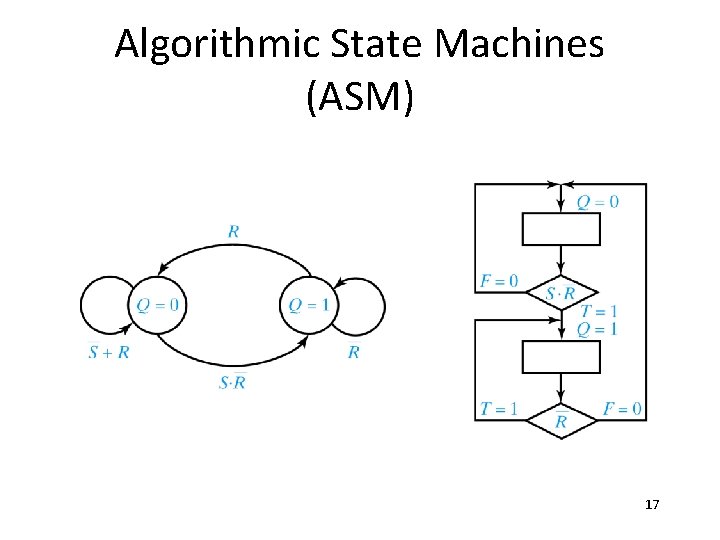

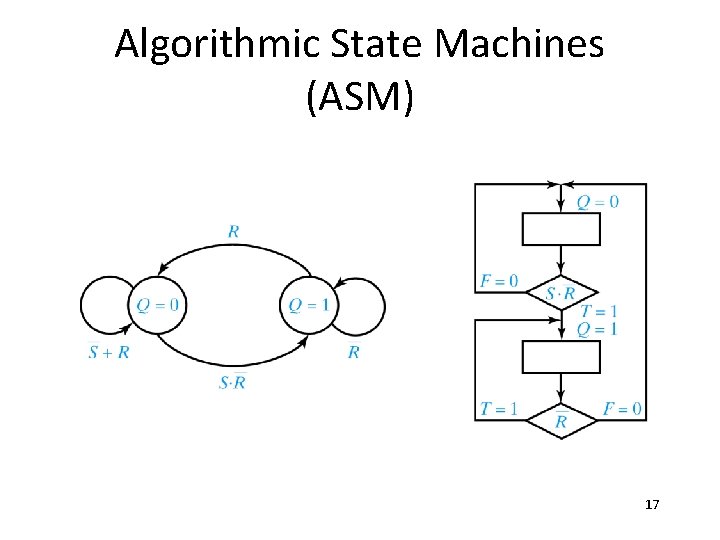

Algorithmic State Machines (ASM) 17

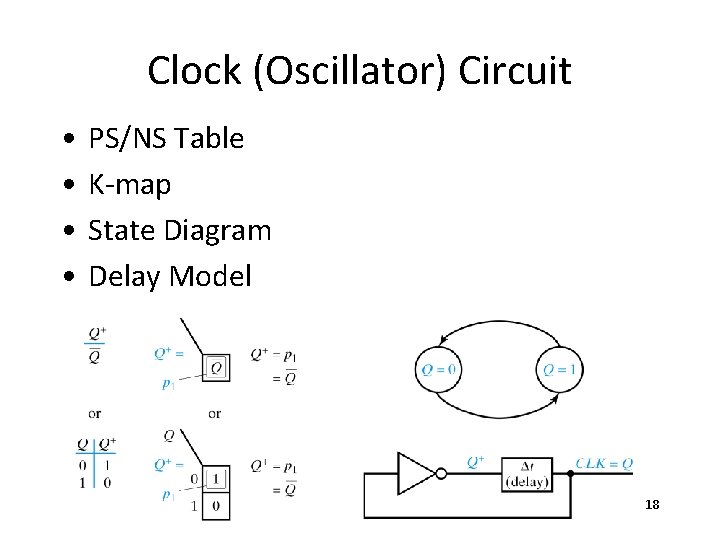

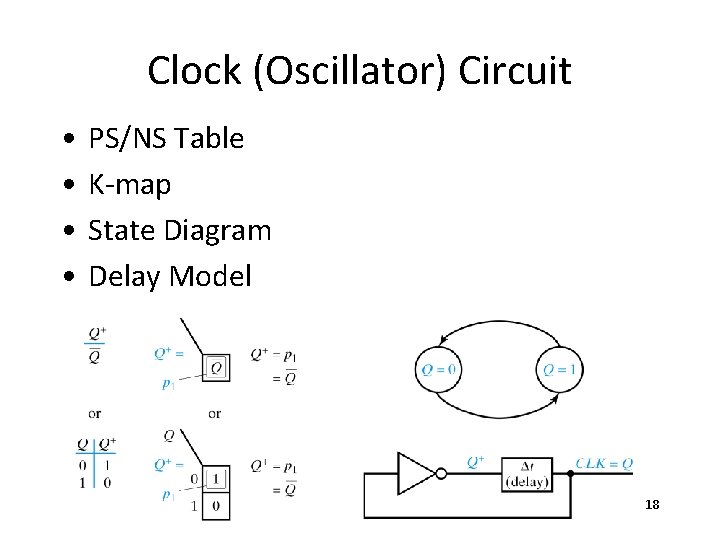

Clock (Oscillator) Circuit • • PS/NS Table K-map State Diagram Delay Model 18

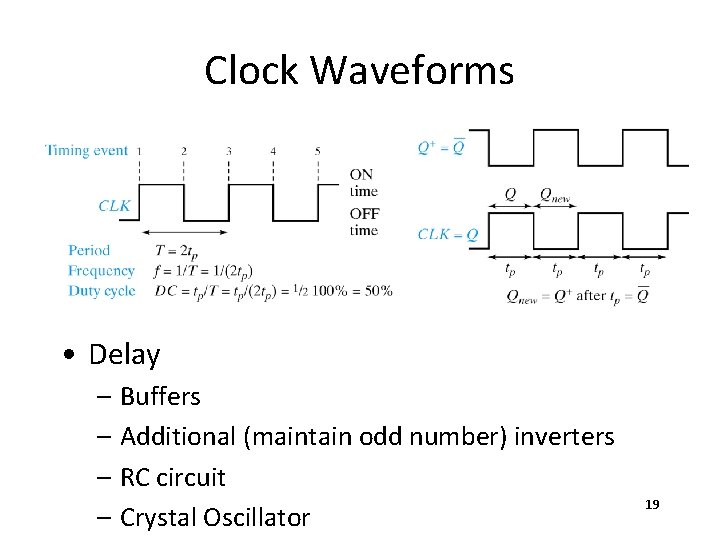

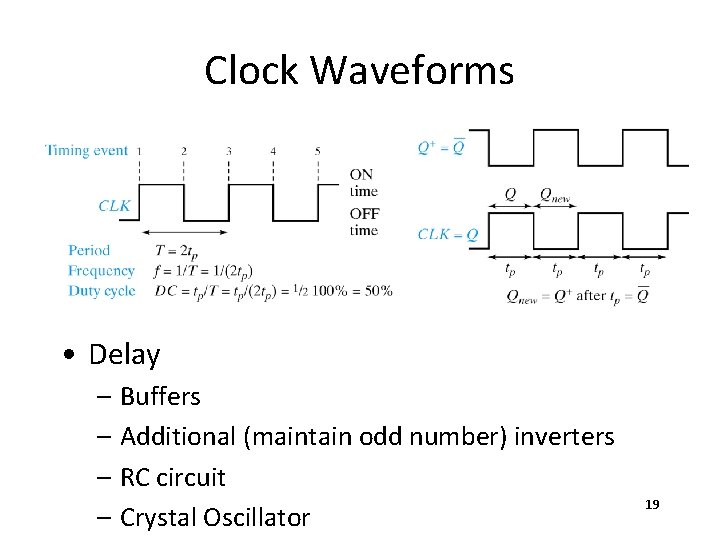

Clock Waveforms • Delay – Buffers – Additional (maintain odd number) inverters – RC circuit – Crystal Oscillator 19

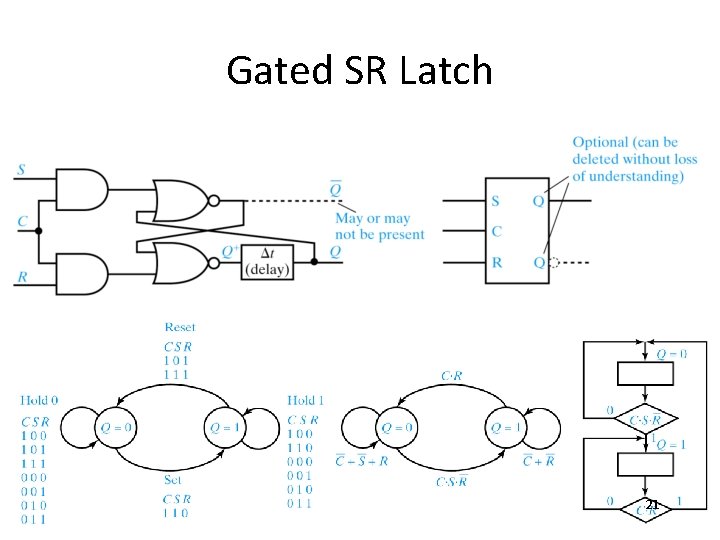

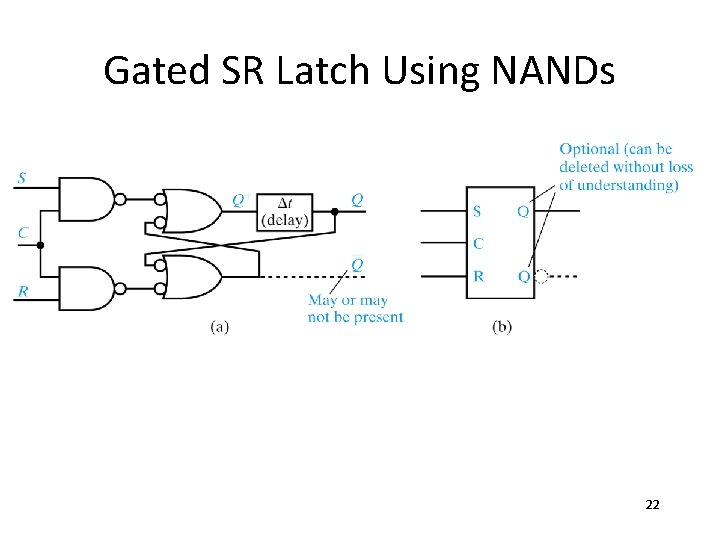

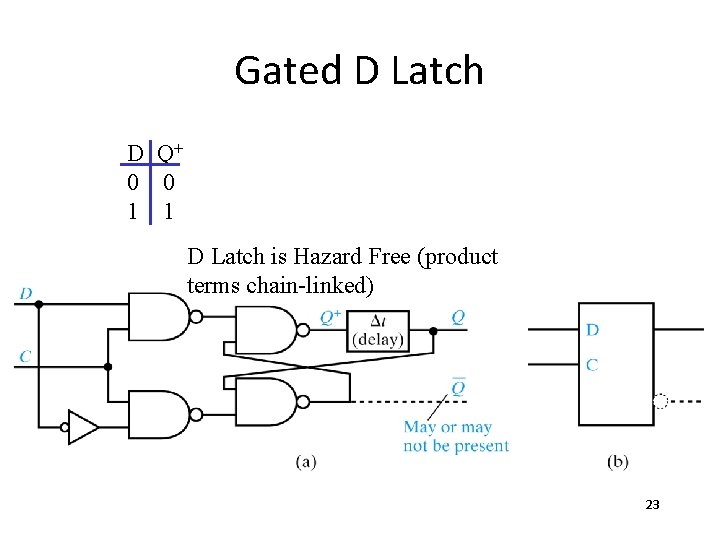

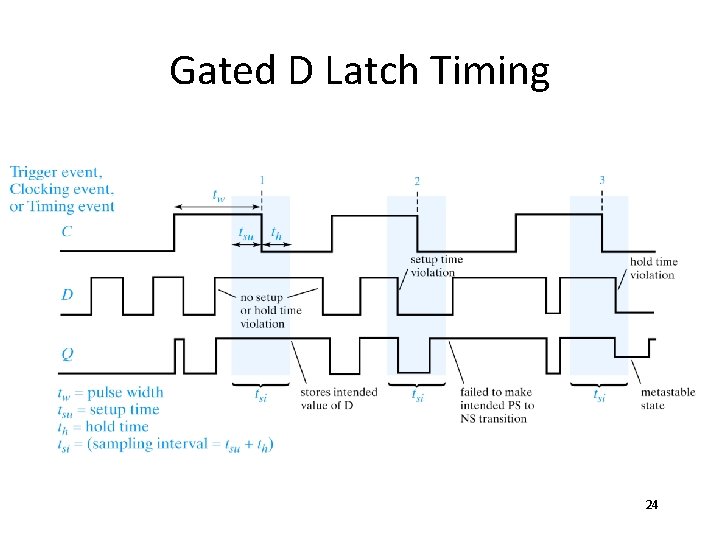

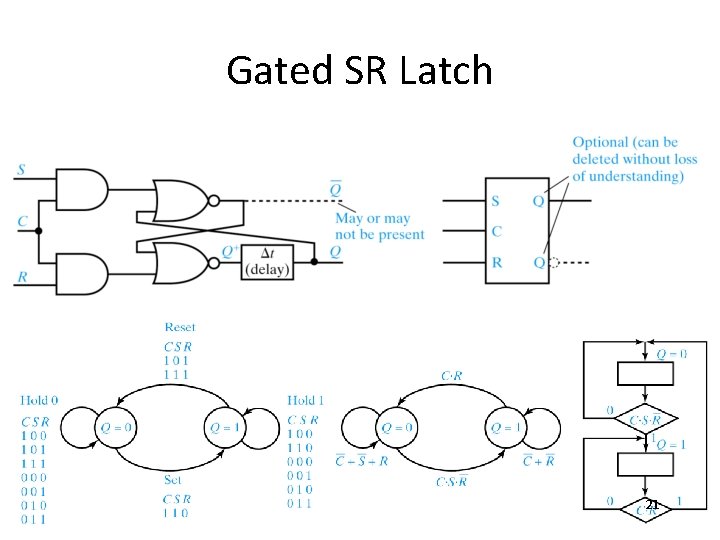

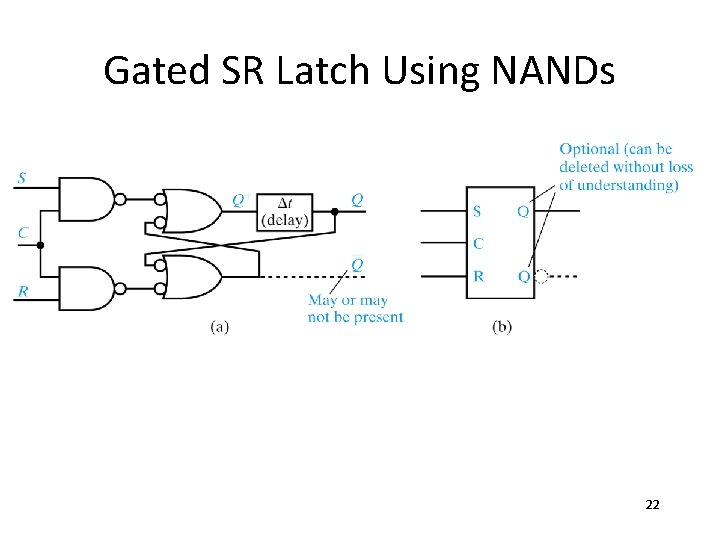

Gated Sequential Circuits • Addition of control input – Gated Latch (Level Activated) – Edge-Triggered Flip Flop – Pulse Triggered Flip Flop 20

Gated SR Latch 21

Gated SR Latch Using NANDs 22

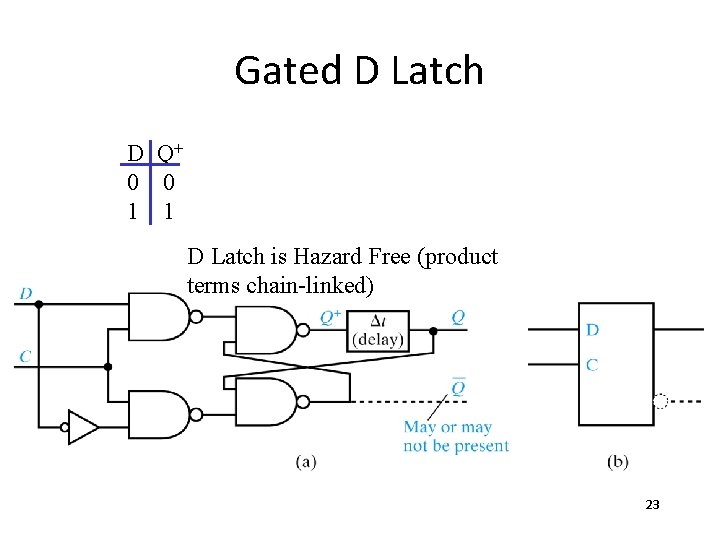

Gated D Latch D Q+ 0 0 1 1 D Latch is Hazard Free (product terms chain-linked) 23

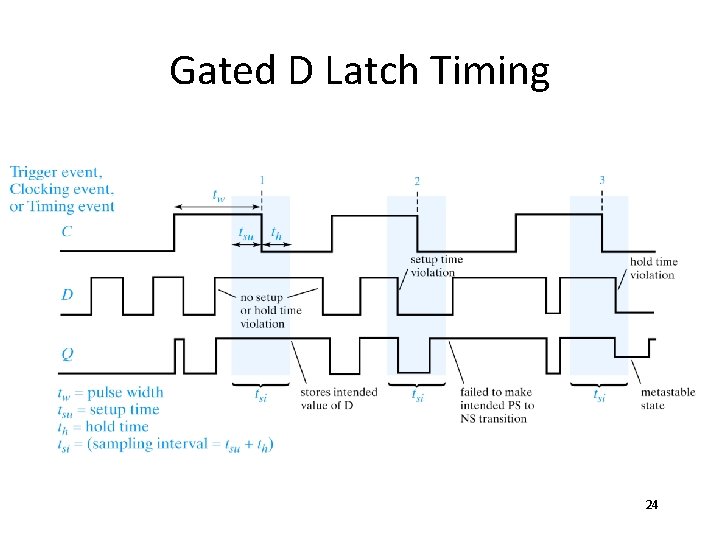

Gated D Latch Timing 24

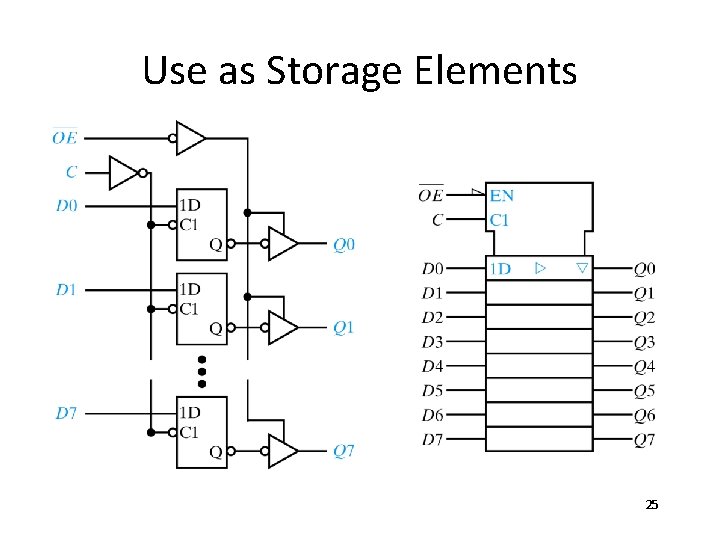

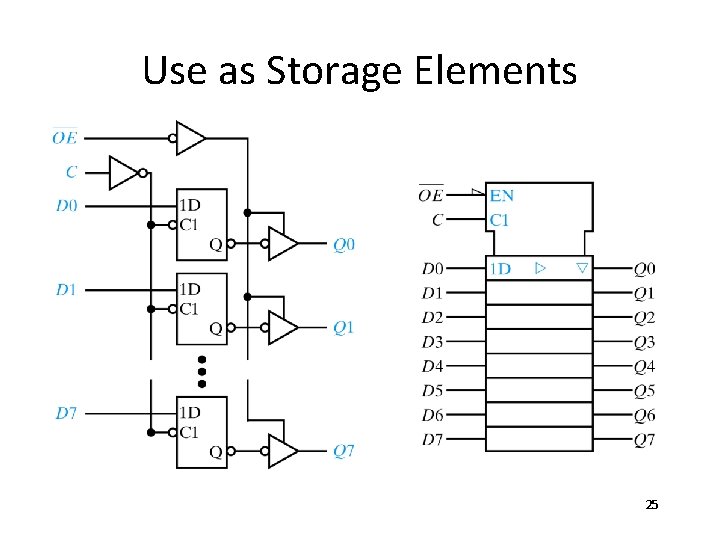

Use as Storage Elements 25

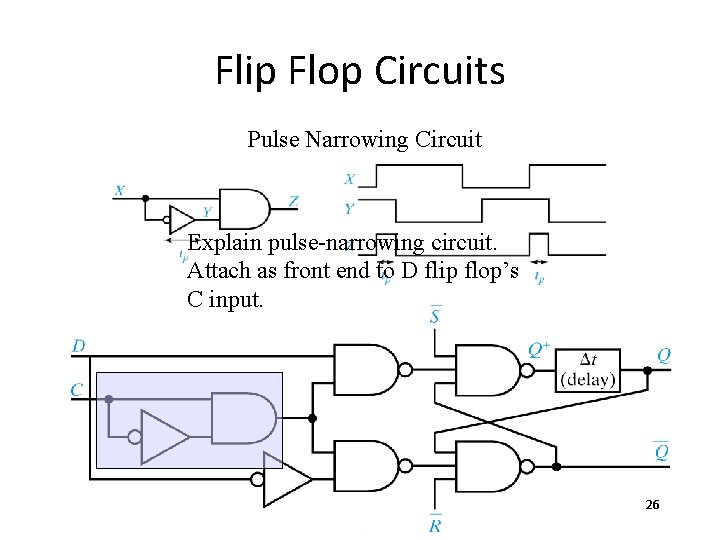

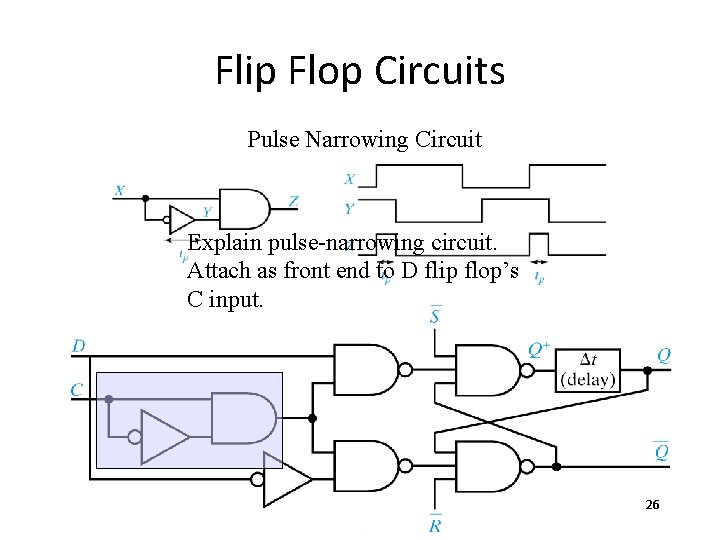

Flip Flop Circuits Pulse Narrowing Circuit Explain pulse-narrowing circuit. Attach as front end to D flip flop’s C input. 26

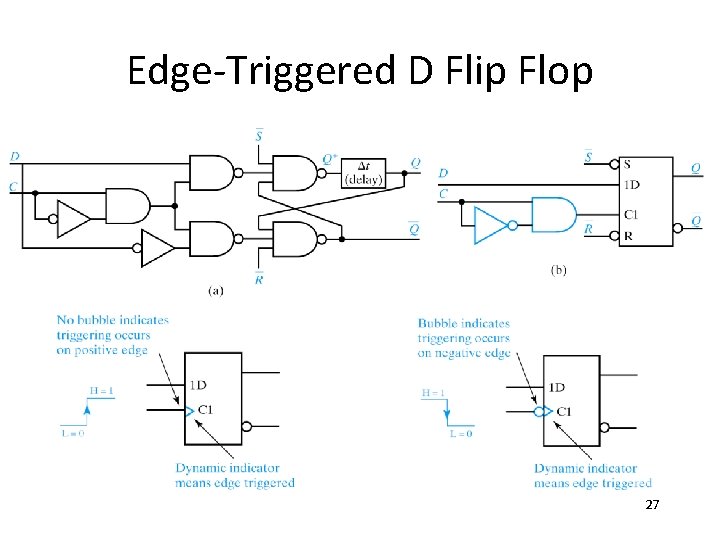

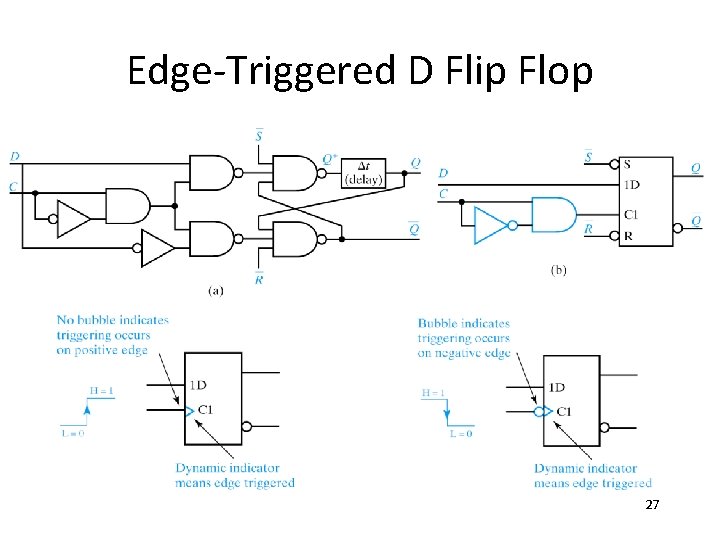

Edge-Triggered D Flip Flop 27

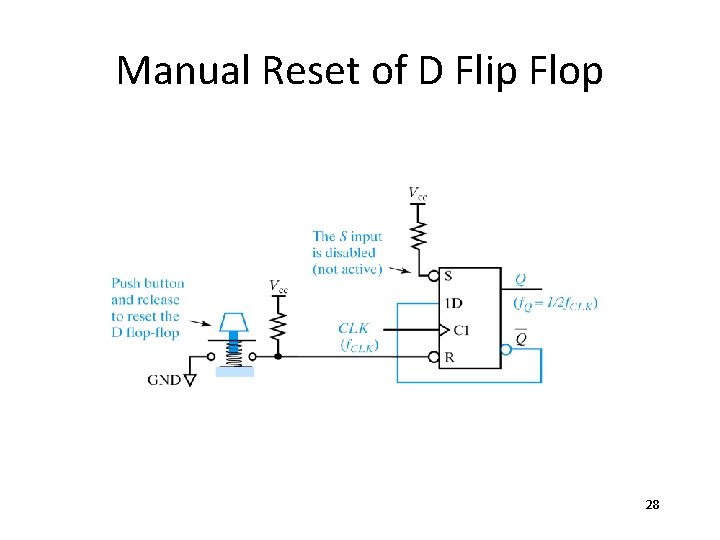

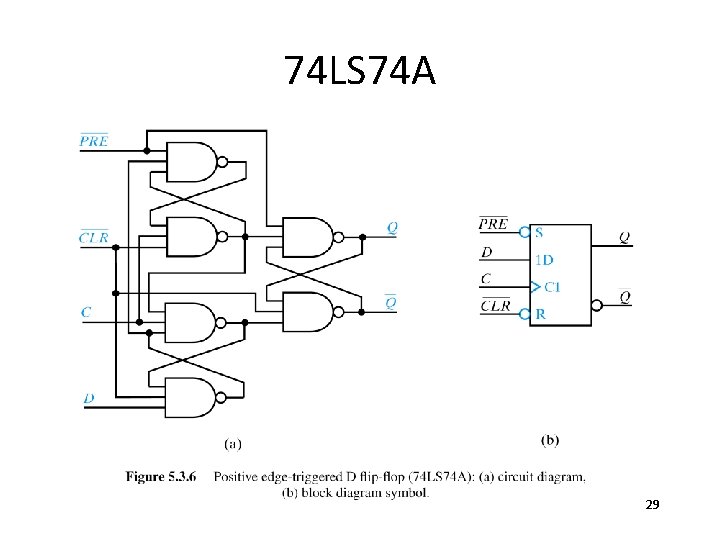

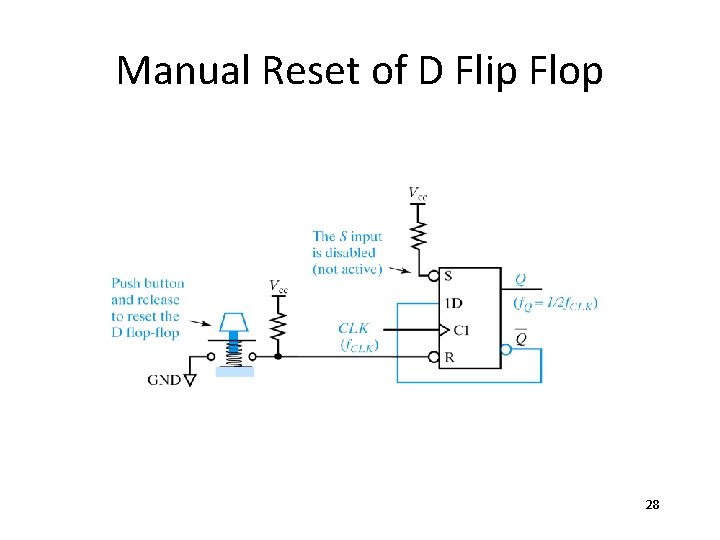

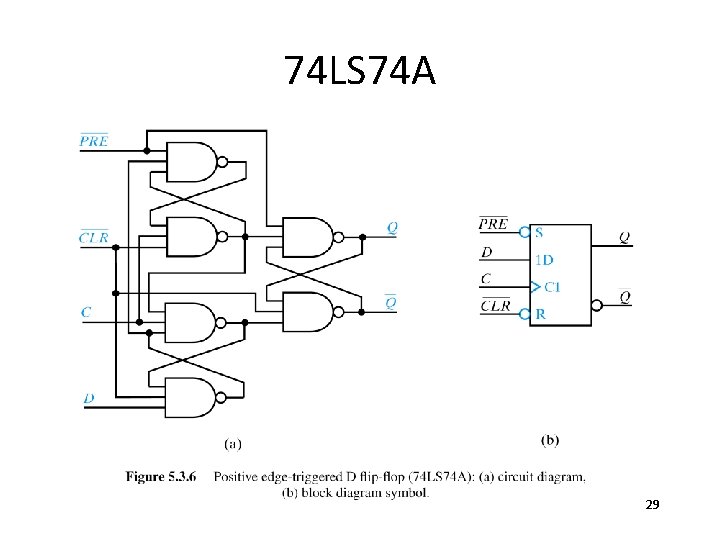

Manual Reset of D Flip Flop 28

74 LS 74 A 29

JK Flip Flops JK 00 01 10 11 Q+ Q 0 1 Q Comment No change Reset Set Toggle 30

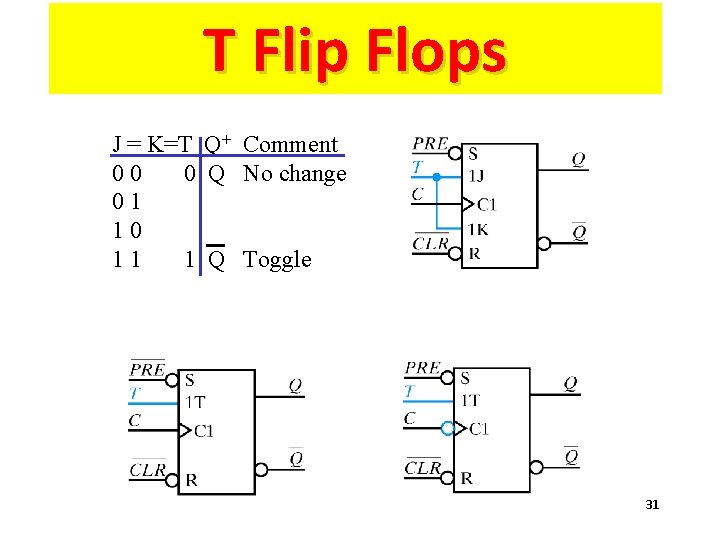

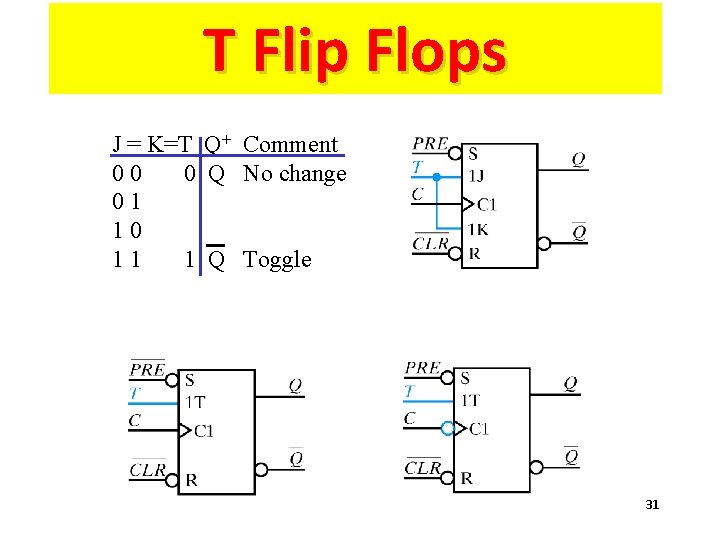

T Flip Flops J = K=T Q+ Comment 00 0 Q No change 01 10 11 1 Q Toggle 31

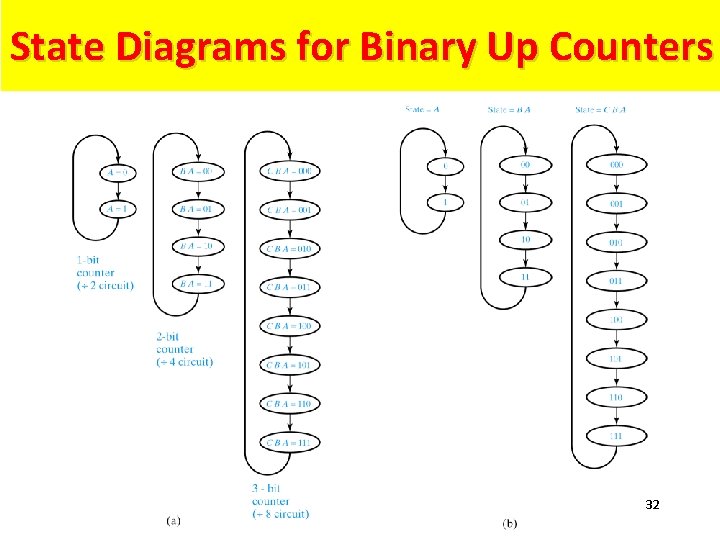

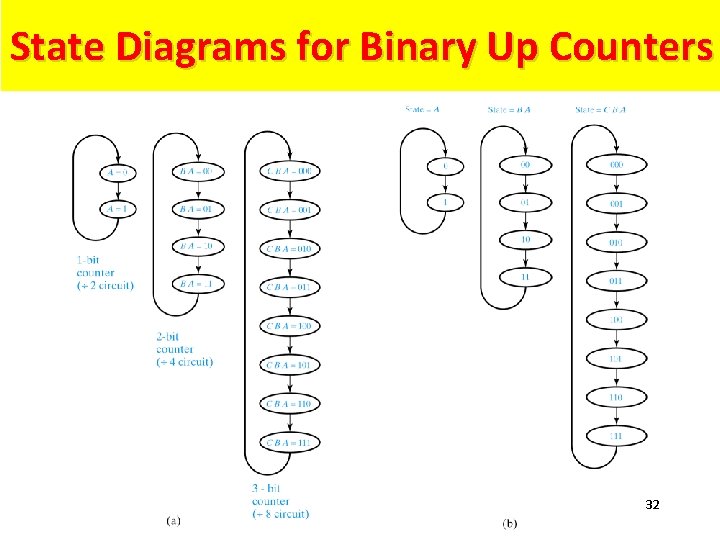

State Diagrams for Binary Up Counters 32

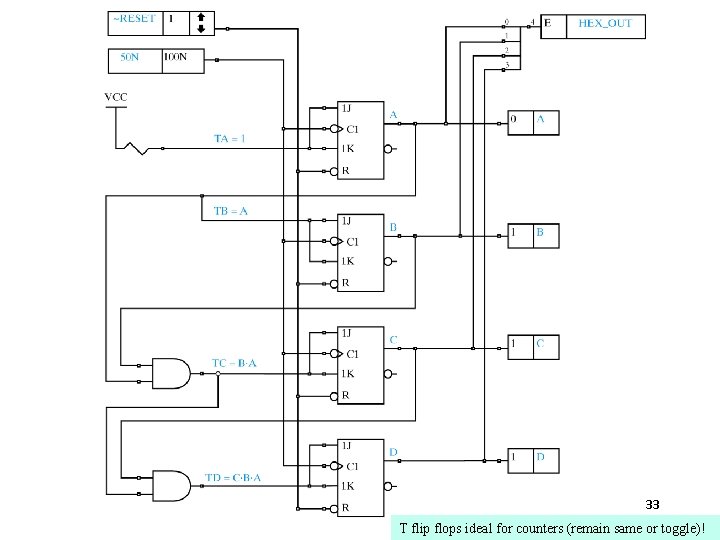

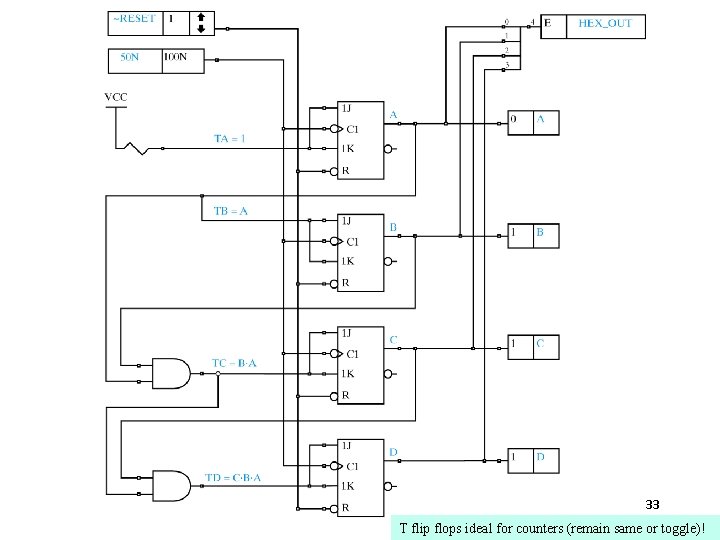

4 -Bit Binary Up Counter 33 T flip flops ideal for counters (remain same or toggle)!

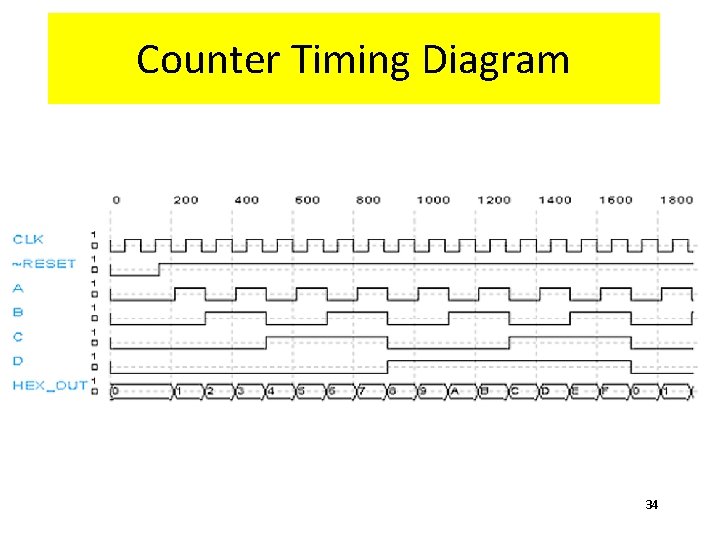

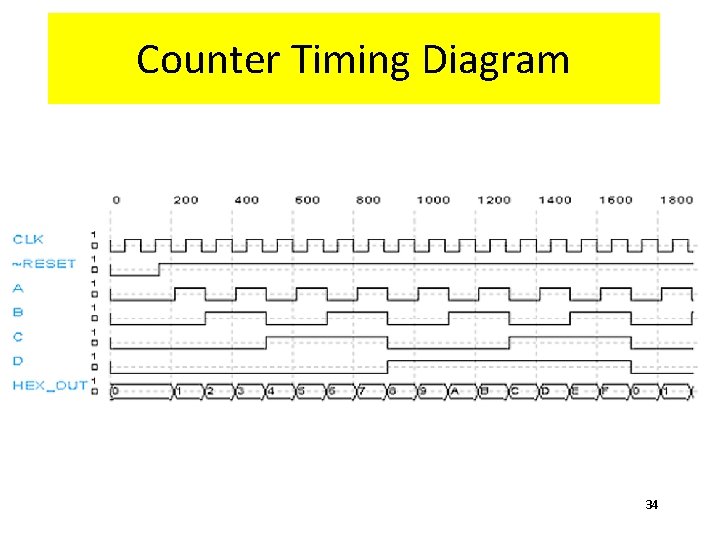

Counter Timing Diagram 34

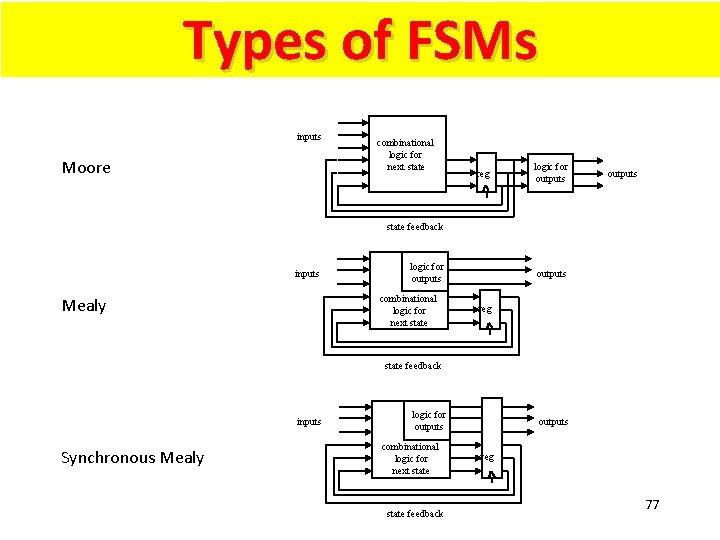

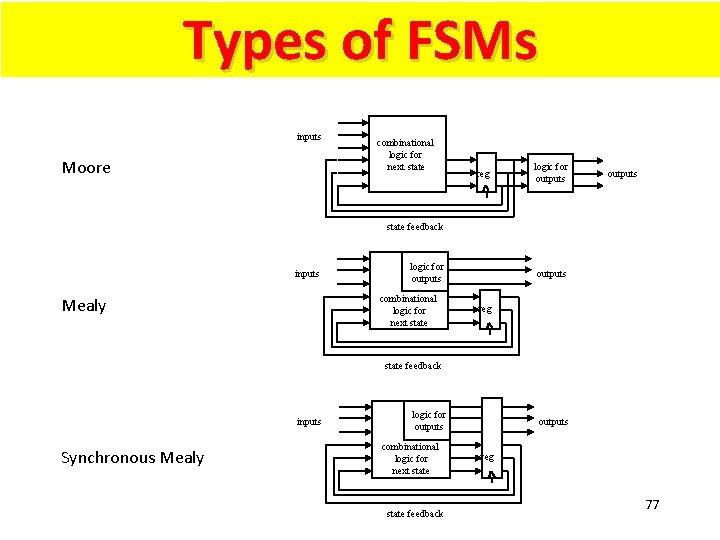

State Machines • State Transition Diagrams • Next State Tables • Mealy and Moore Machines – Mealy: Output logic uses current state and inputs – Moore: Output logic uses only current state • One Hot vs. Encoded State Machines 35

Example T-bird taillights

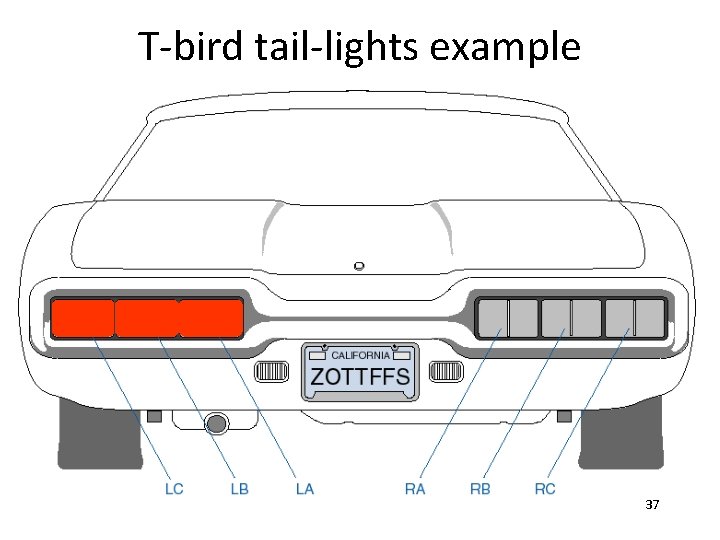

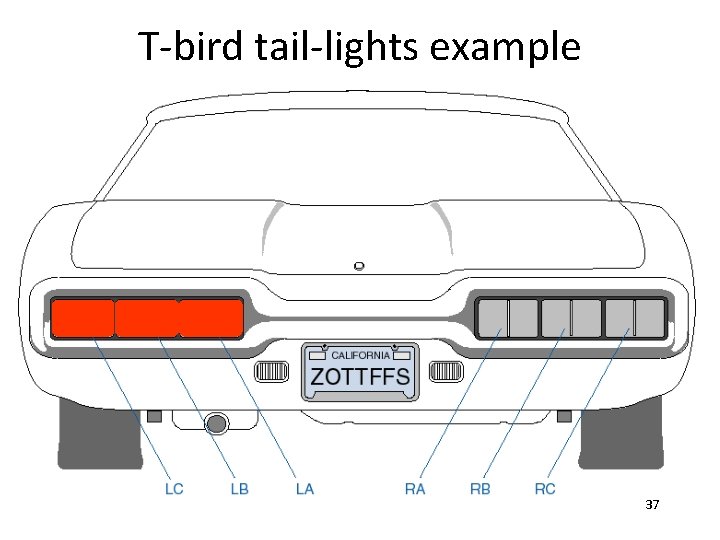

T-bird tail-lights example 37

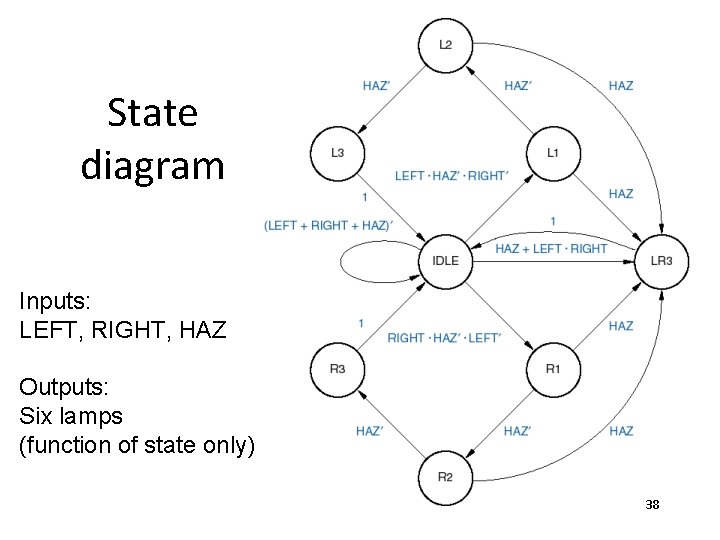

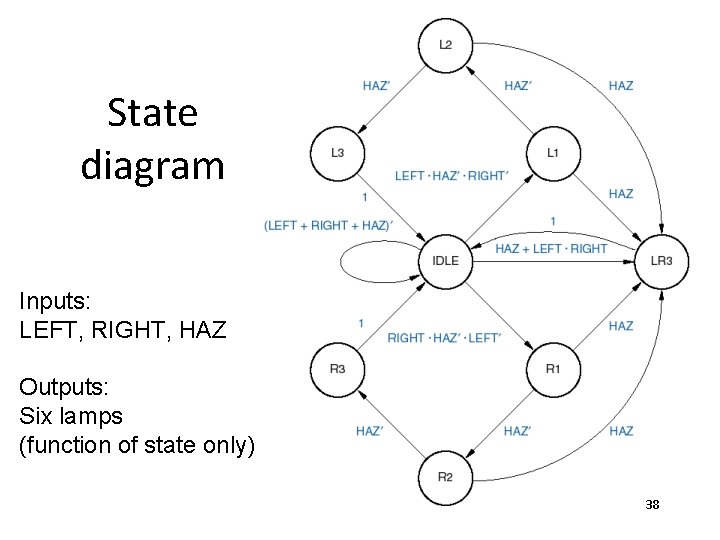

State diagram Inputs: LEFT, RIGHT, HAZ Outputs: Six lamps (function of state only) 38

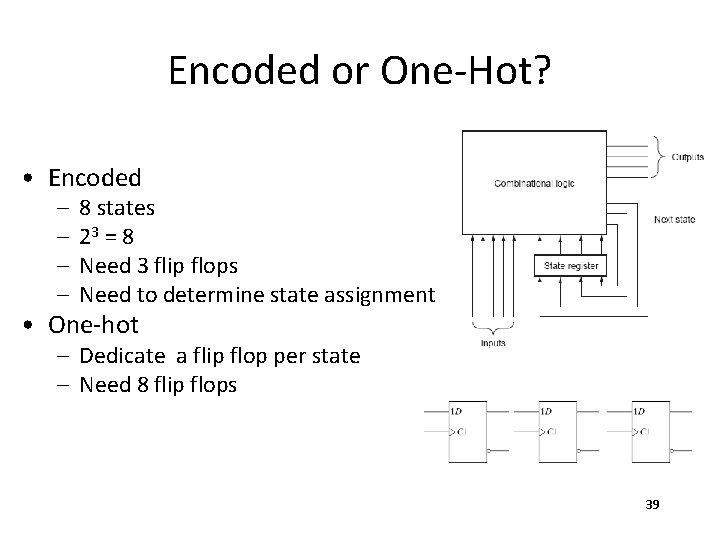

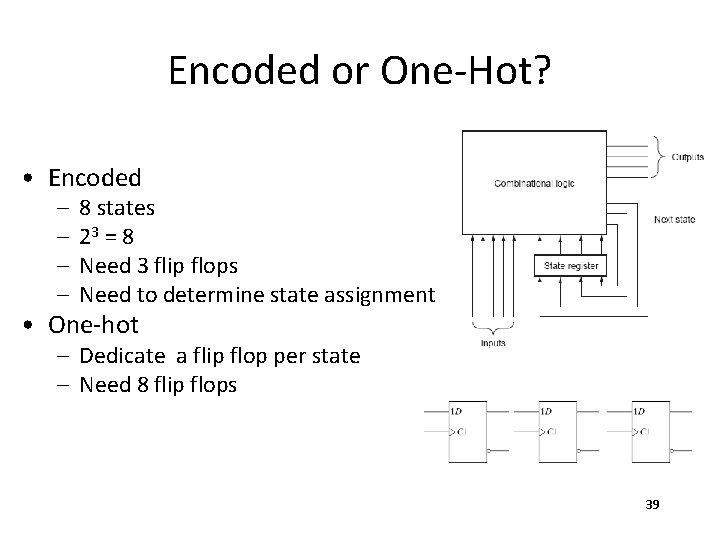

Encoded or One-Hot? • Encoded – – 8 states 23 = 8 Need 3 flip flops Need to determine state assignment • One-hot – Dedicate a flip flop per state – Need 8 flip flops 39

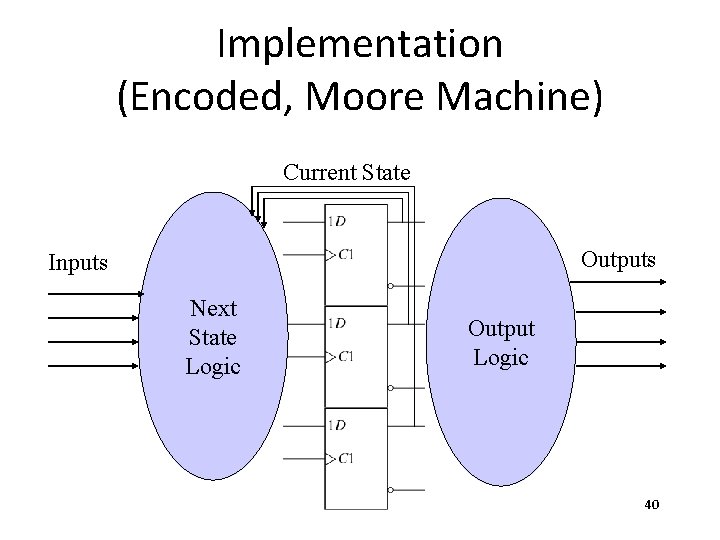

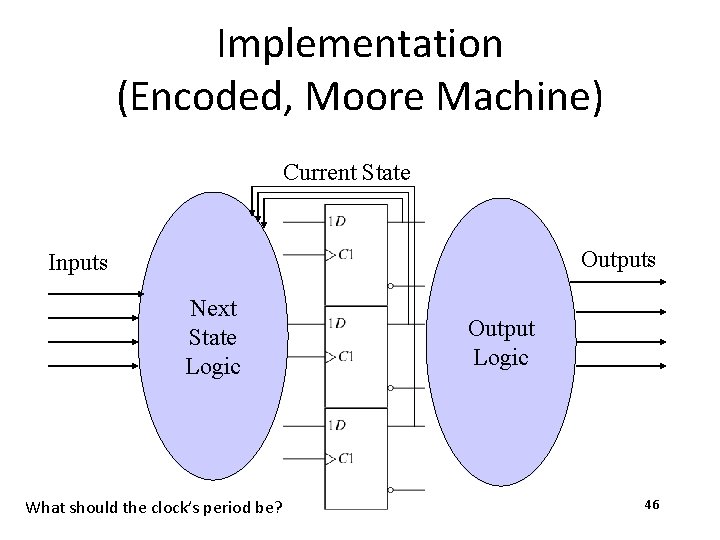

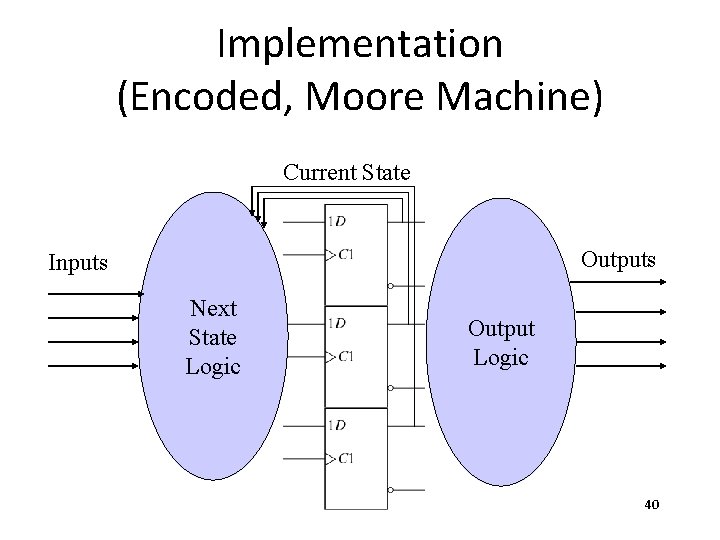

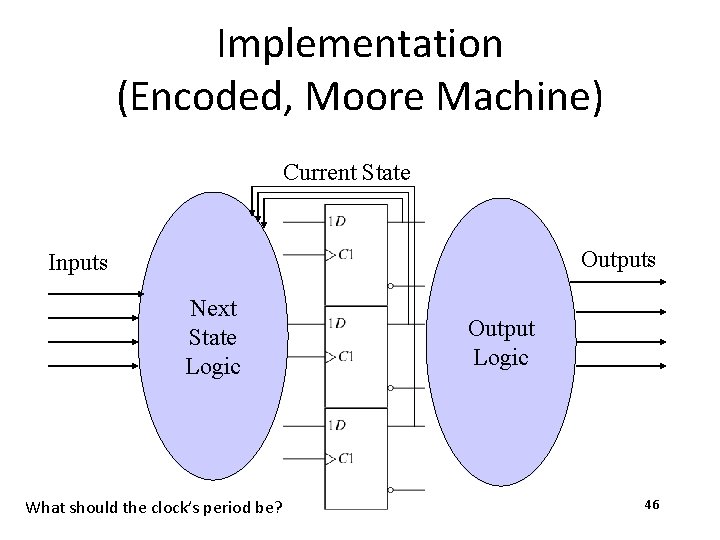

Implementation (Encoded, Moore Machine) Current State Outputs Inputs Next State Logic Output Logic 40

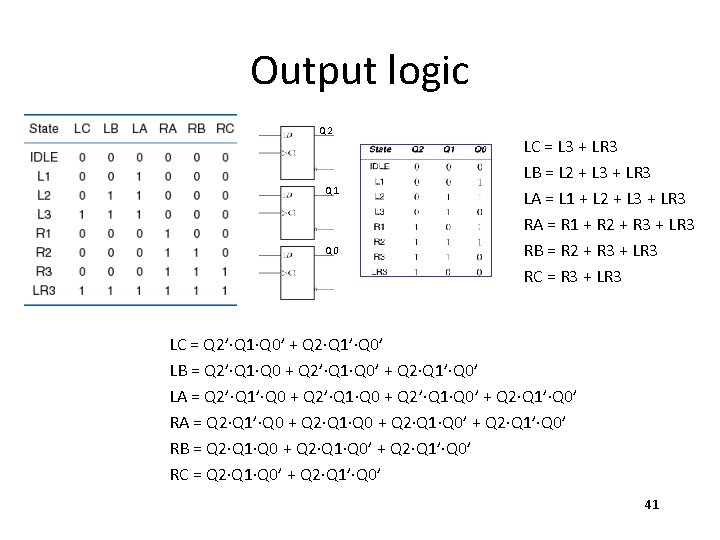

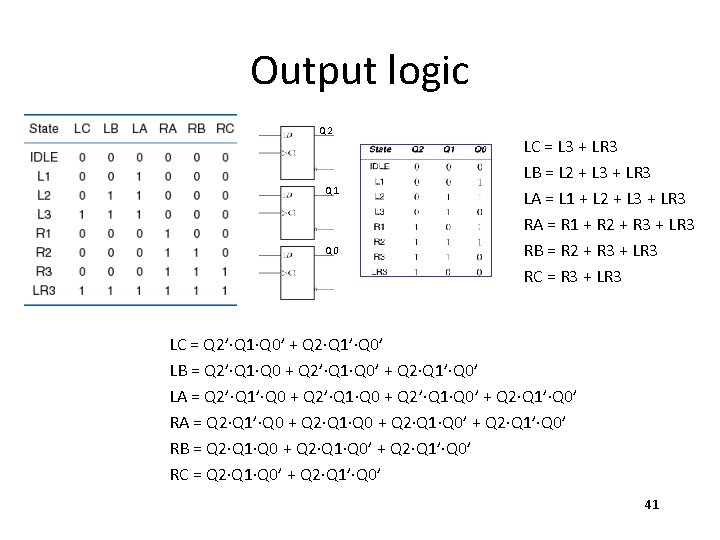

Output logic Q 2 Q 1 Q 0 LC = L 3 + LR 3 LB = L 2 + L 3 + LR 3 LA = L 1 + L 2 + L 3 + LR 3 RA = R 1 + R 2 + R 3 + LR 3 RB = R 2 + R 3 + LR 3 RC = R 3 + LR 3 LC = Q 2’×Q 1×Q 0’ + Q 2×Q 1’×Q 0’ LB = Q 2’×Q 1×Q 0 + Q 2’×Q 1×Q 0’ + Q 2×Q 1’×Q 0’ LA = Q 2’×Q 1’×Q 0 + Q 2’×Q 1×Q 0’ + Q 2×Q 1’×Q 0’ RA = Q 2×Q 1’×Q 0 + Q 2×Q 1×Q 0’ + Q 2×Q 1’×Q 0’ RB = Q 2×Q 1×Q 0 + Q 2×Q 1×Q 0’ + Q 2×Q 1’×Q 0’ RC = Q 2×Q 1×Q 0’ + Q 2×Q 1’×Q 0’ 41

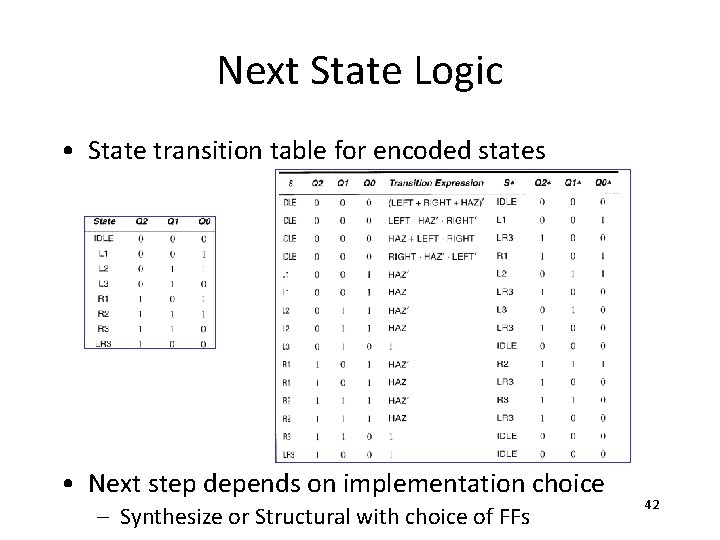

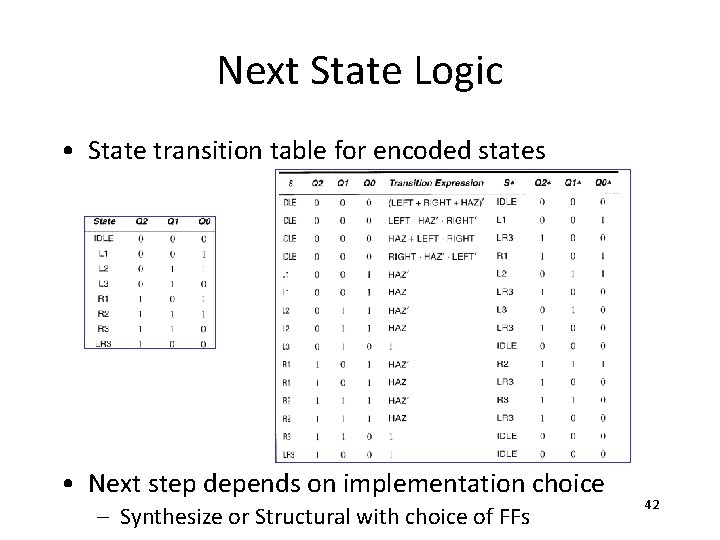

Next State Logic • State transition table for encoded states • Next step depends on implementation choice – Synthesize or Structural with choice of FFs 42

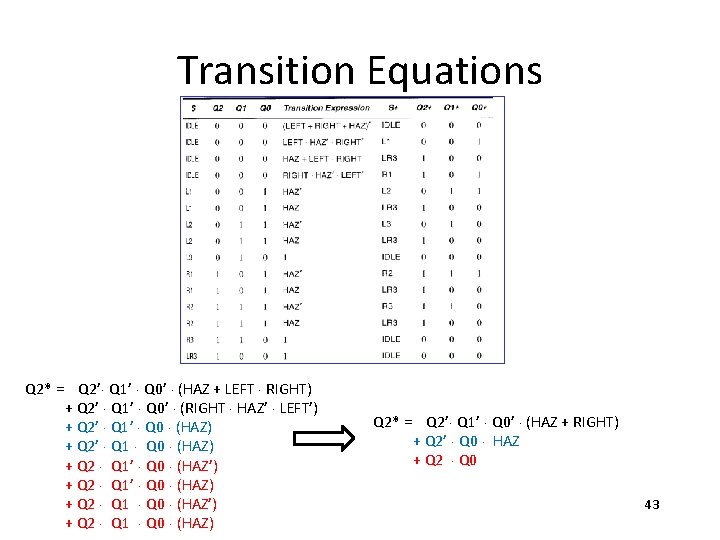

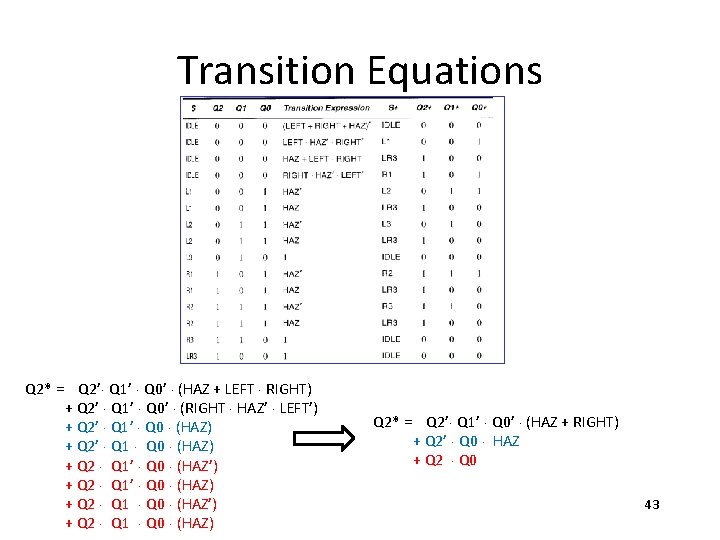

Transition Equations Q 2* = Q 2’× Q 1’ × Q 0’ × (HAZ + LEFT × RIGHT) + Q 2’ × Q 1’ × Q 0’ × (RIGHT × HAZ’ × LEFT’) + Q 2’ × Q 1’ × Q 0 × (HAZ) + Q 2’ × Q 1 × Q 0 × (HAZ) + Q 2 × Q 1’ × Q 0 × (HAZ’) + Q 2 × Q 1’ × Q 0 × (HAZ) + Q 2 × Q 1 × Q 0 × (HAZ’) + Q 2 × Q 1 × Q 0 × (HAZ) Q 2* = Q 2’× Q 1’ × Q 0’ × (HAZ + RIGHT) + Q 2’ × Q 0 × HAZ + Q 2 × Q 0 43

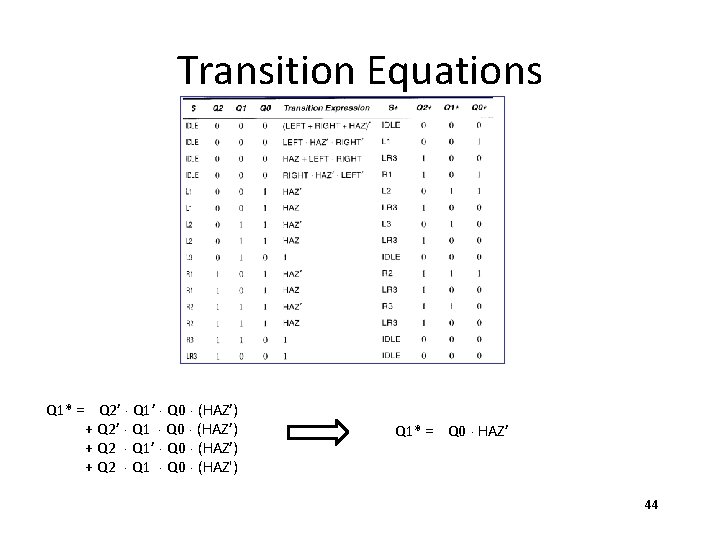

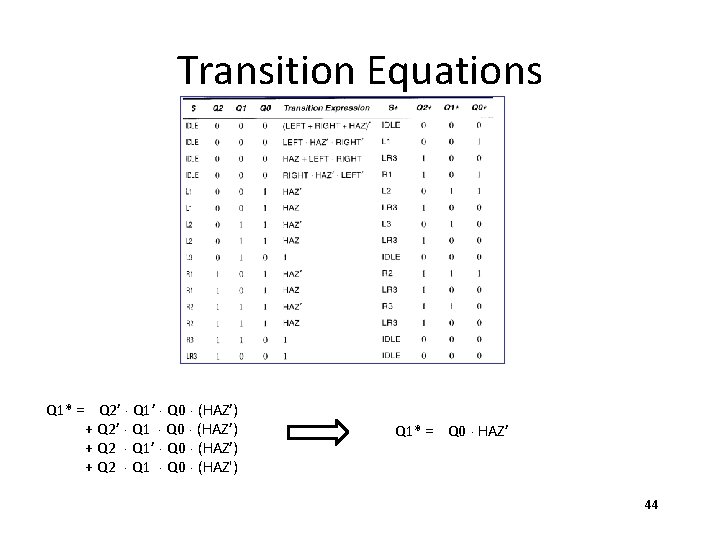

Transition Equations Q 1* = Q 2’ × Q 1’ × Q 0 × (HAZ’) + Q 2’ × Q 1 × Q 0 × (HAZ’) + Q 2 × Q 1’ × Q 0 × (HAZ’) + Q 2 × Q 1 × Q 0 × (HAZ') Q 1* = Q 0 × HAZ’ 44

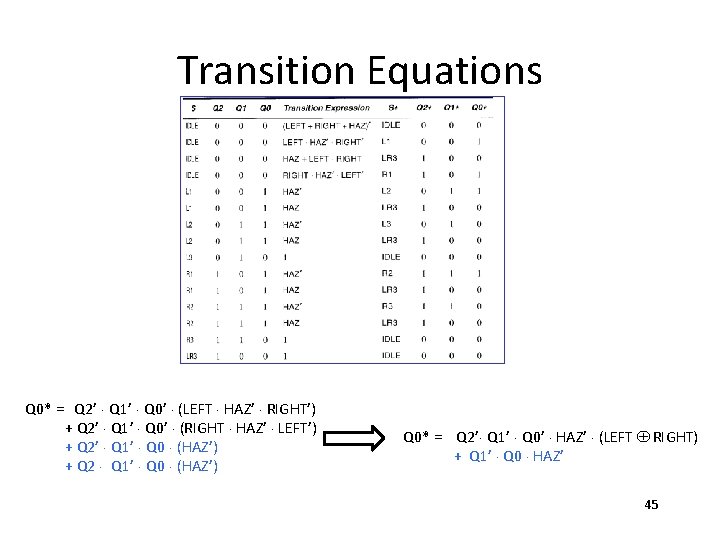

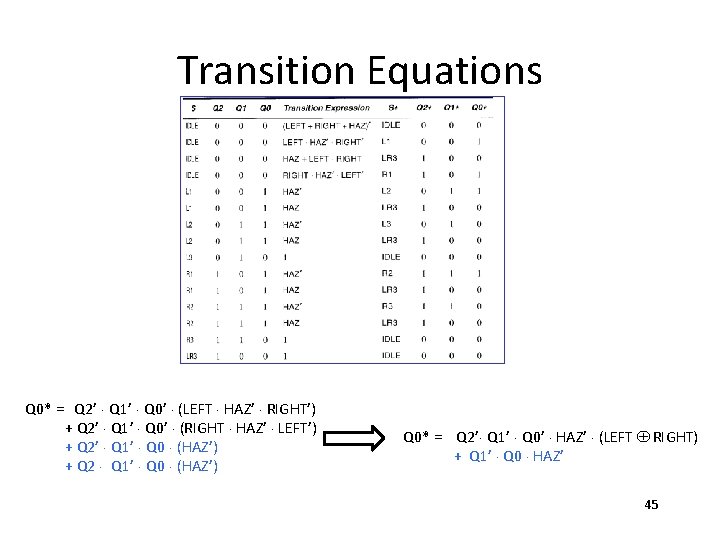

Transition Equations Q 0* = Q 2’ × Q 1’ × Q 0’ × (LEFT × HAZ’ × RIGHT’) + Q 2’ × Q 1’ × Q 0’ × (RIGHT × HAZ’ × LEFT’) + Q 2’ × Q 1’ × Q 0 × (HAZ’) + Q 2 × Q 1’ × Q 0 × (HAZ’) Q 0* = Q 2’× Q 1’ × Q 0’ × HAZ’ × (LEFT Å RIGHT) + Q 1’ × Q 0 × HAZ’ 45

Implementation (Encoded, Moore Machine) Current State Outputs Inputs Next State Logic What should the clock’s period be? Output Logic 46

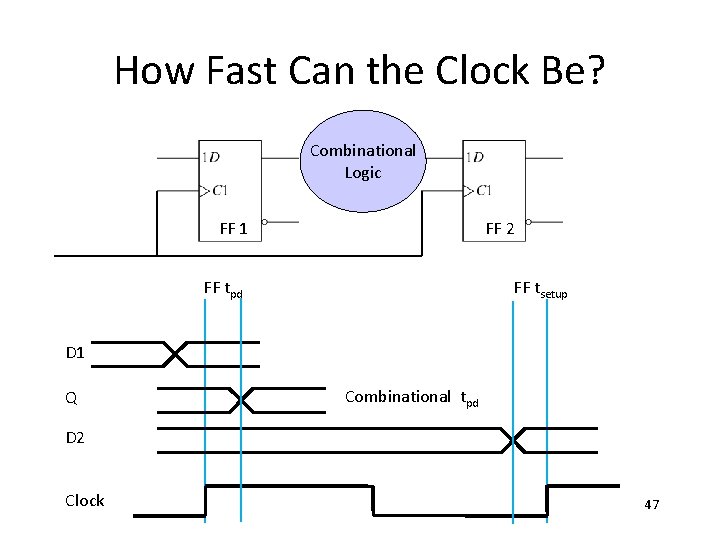

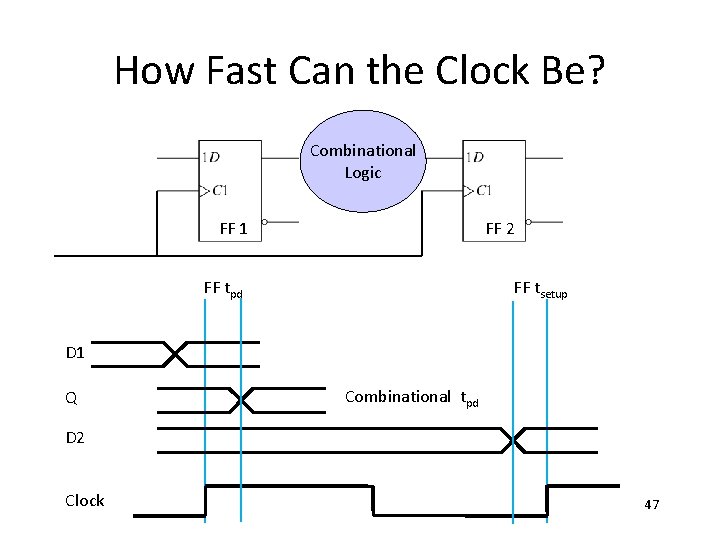

How Fast Can the Clock Be? Combinational Logic FF 1 FF 2 FF tsetup FF tpd D 1 Q Combinational tpd D 2 Clock 47

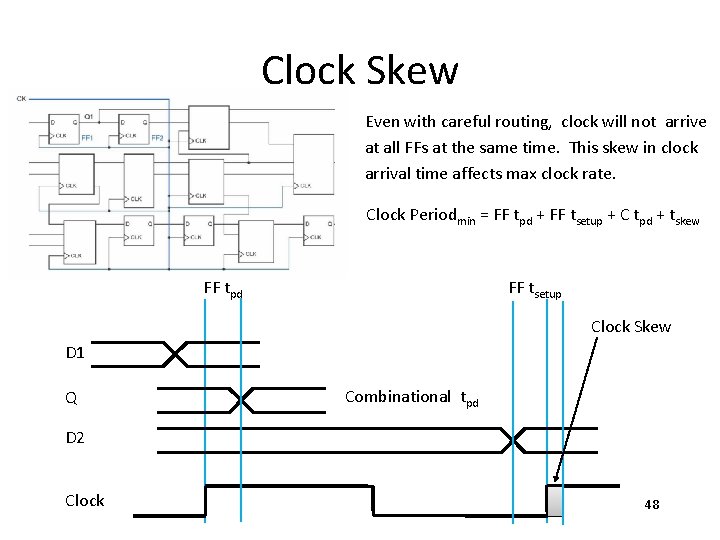

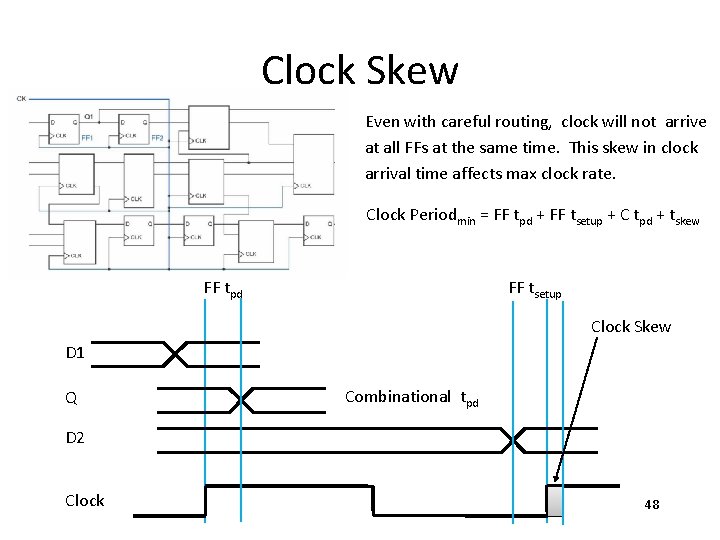

Clock Skew Even with careful routing, clock will not arrive at all FFs at the same time. This skew in clock arrival time affects max clock rate. Clock Periodmin = FF tpd + FF tsetup + C tpd + tskew FF tsetup FF tpd Clock Skew D 1 Q Combinational tpd D 2 Clock 48

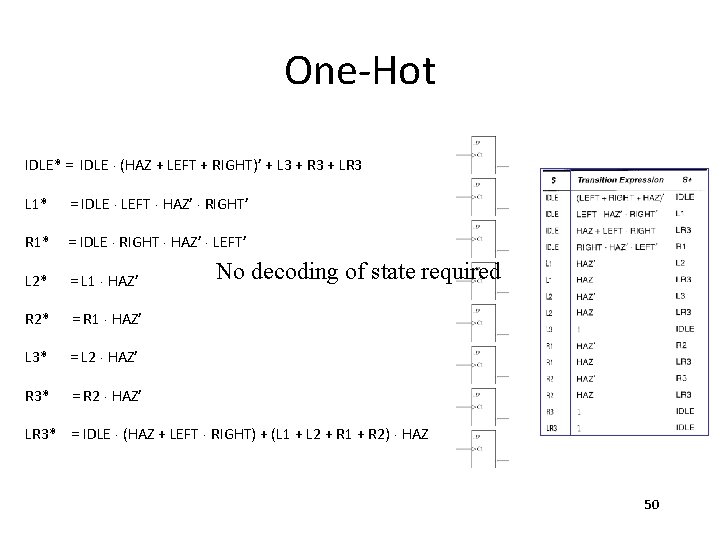

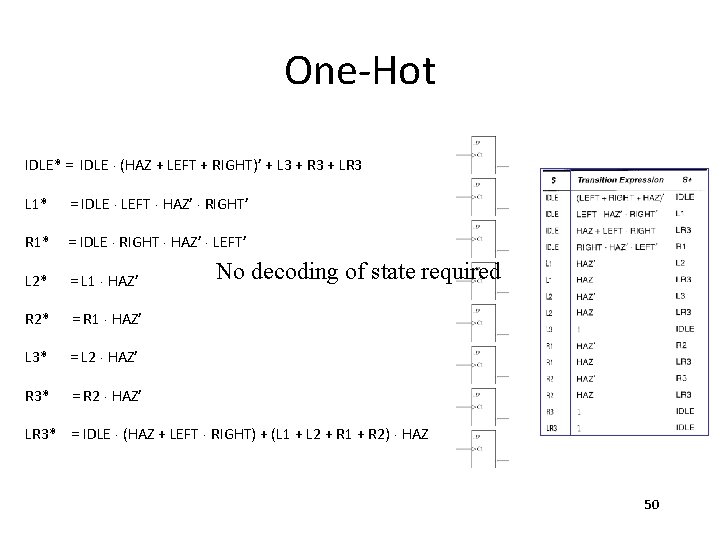

One-Hot IDLE* = IDLE × (HAZ + LEFT + RIGHT)’ + L 3 + R 3 + LR 3 L 1* = IDLE × LEFT × HAZ’ × RIGHT’ R 1* = IDLE × RIGHT × HAZ’ × LEFT’ L 2* = L 1 × HAZ’ R 2* = R 1 × HAZ’ L 3* = L 2 × HAZ’ R 3* = R 2 × HAZ’ No decoding of state required LR 3* = IDLE × (HAZ + LEFT × RIGHT) + (L 1 + L 2 + R 1 + R 2) × HAZ 50

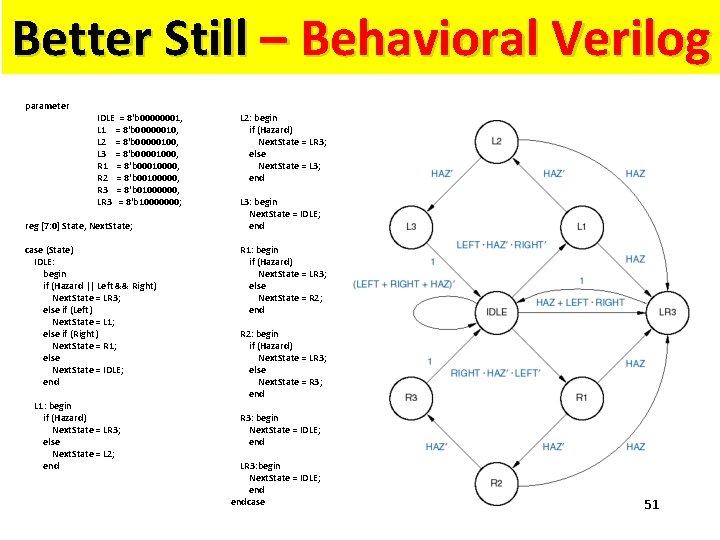

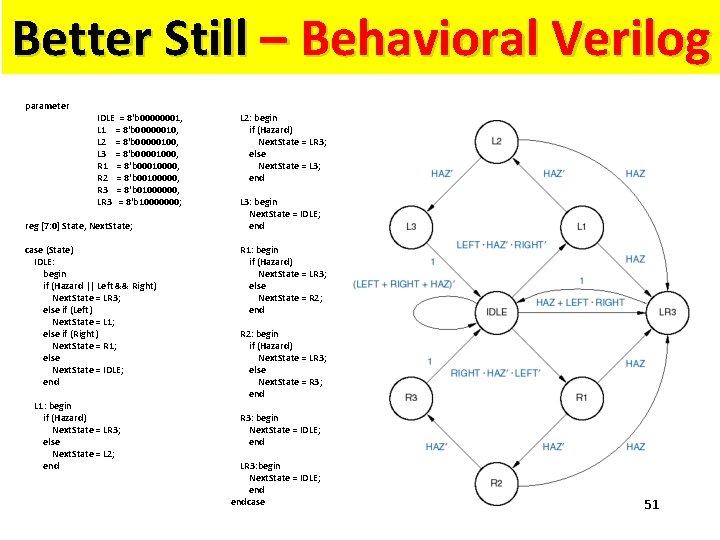

Better Still – Behavioral Verilog parameter IDLE = 8'b 00000001, L 1 = 8'b 00000010, L 2 = 8'b 00000100, L 3 = 8'b 00001000, R 1 = 8'b 00010000, R 2 = 8'b 00100000, R 3 = 8'b 01000000, LR 3 = 8'b 10000000; reg [7: 0] State, Next. State; case (State) IDLE: begin if (Hazard || Left && Right) Next. State = LR 3; else if (Left) Next. State = L 1; else if (Right) Next. State = R 1; else Next. State = IDLE; end L 1: begin if (Hazard) Next. State = LR 3; else Next. State = L 2; end L 2: begin if (Hazard) Next. State = LR 3; else Next. State = L 3; end L 3: begin Next. State = IDLE; end R 1: begin if (Hazard) Next. State = LR 3; else Next. State = R 2; end R 2: begin if (Hazard) Next. State = LR 3; else Next. State = R 3; end R 3: begin Next. State = IDLE; end LR 3: begin Next. State = IDLE; endcase 51

Example: Traffic Light Controller

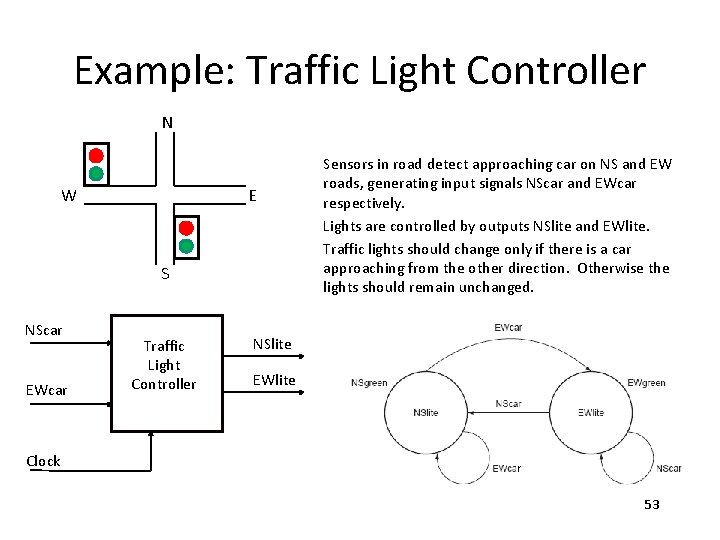

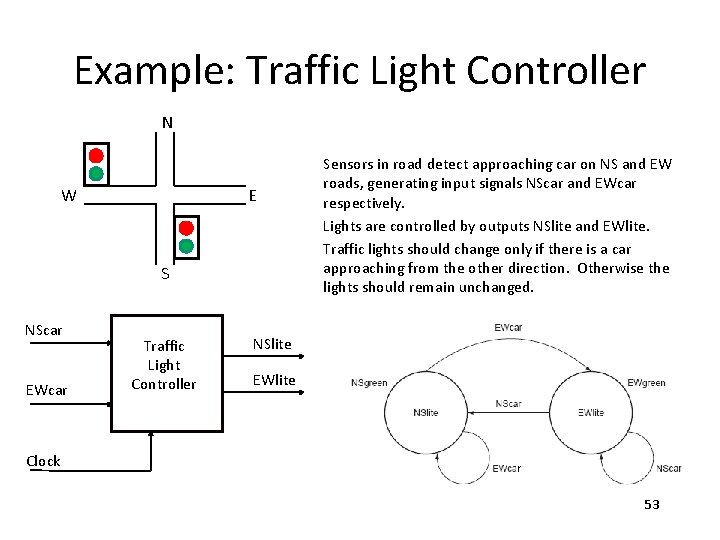

Example: Traffic Light Controller N W E S NScar EWcar Clock Traffic Light Controller Sensors in road detect approaching car on NS and EW roads, generating input signals NScar and EWcar respectively. Lights are controlled by outputs NSlite and EWlite. Traffic lights should change only if there is a car approaching from the other direction. Otherwise the lights should remain unchanged. NSlite EWlite r 53

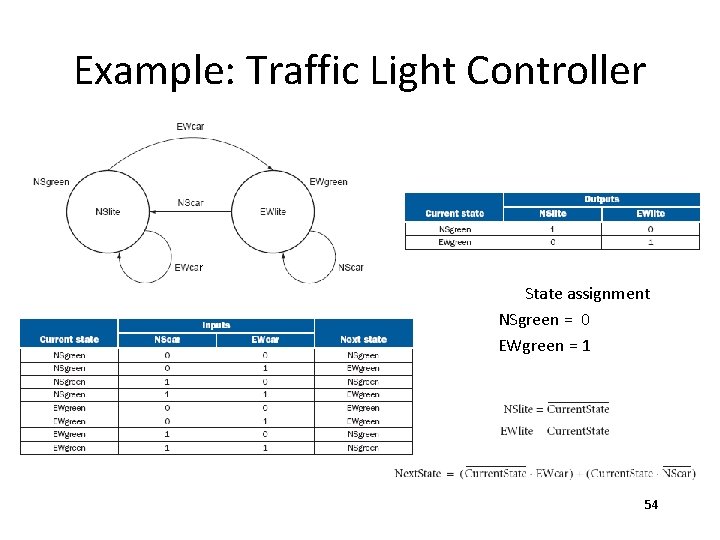

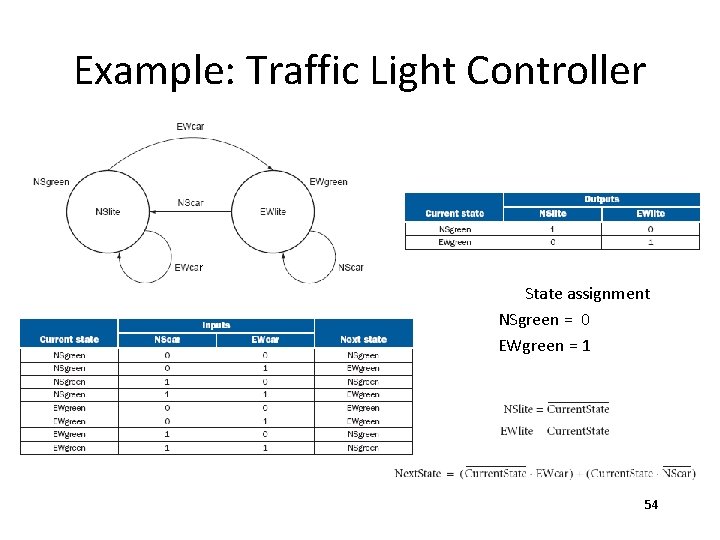

Example: Traffic Light Controller r State assignment NSgreen = 0 EWgreen = 1 54

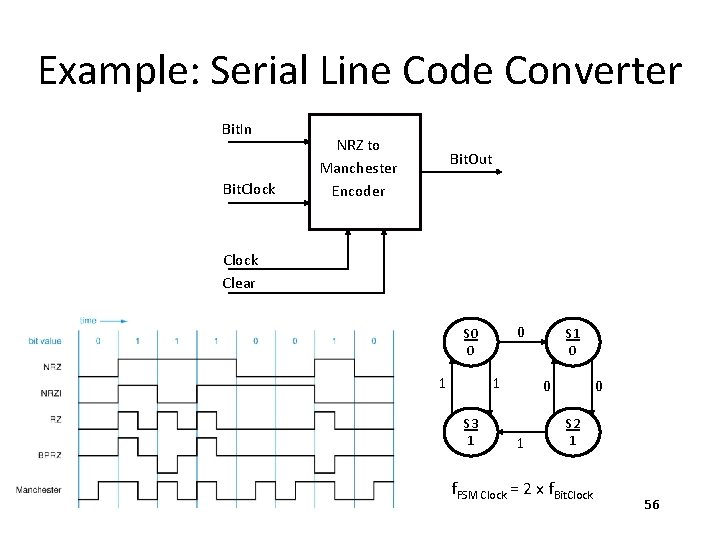

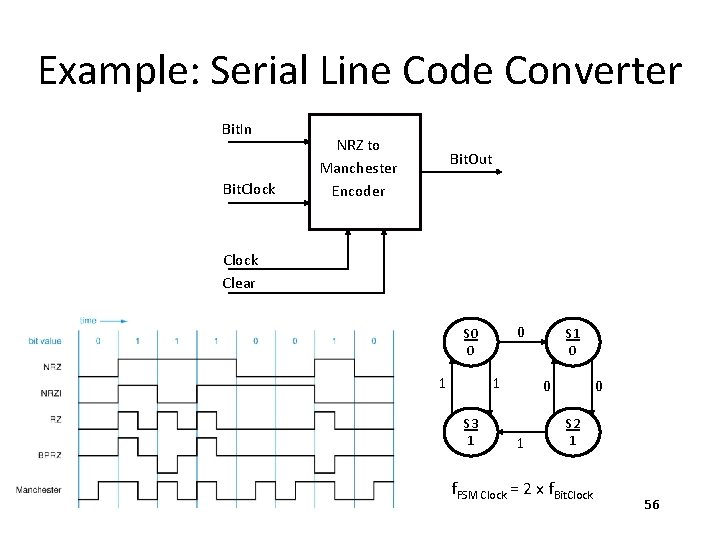

Example: Serial Line Code Converter

Example: Serial Line Code Converter Bit. In Bit. Clock NRZ to Manchester Encoder Bit. Out Clock Clear 0 S 0 0 1 1 S 3 1 S 1 0 0 1 0 S 2 1 f. FSM Clock = 2 x f. Bit. Clock 56

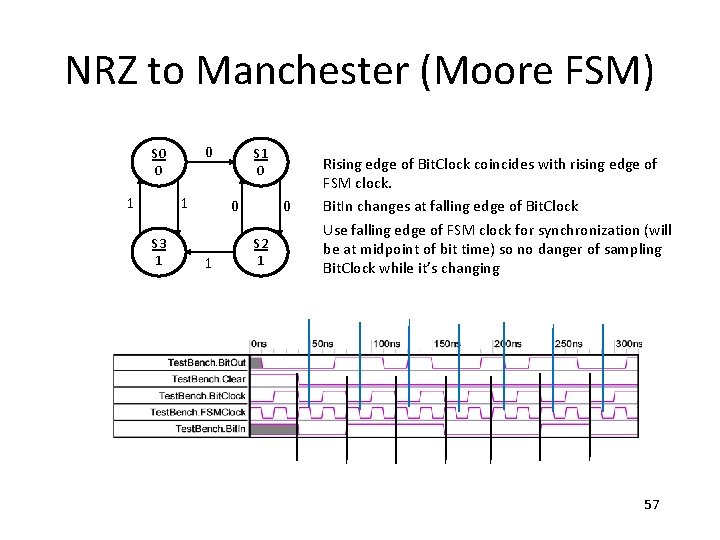

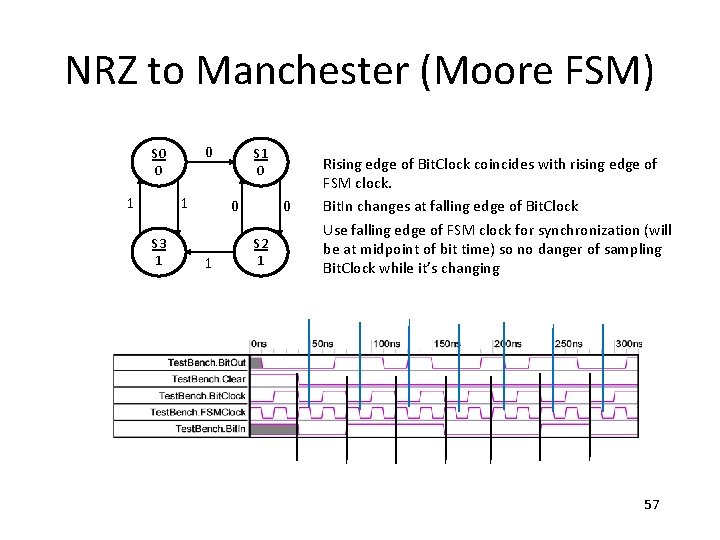

NRZ to Manchester (Moore FSM) 0 S 0 0 1 1 S 3 1 S 1 0 0 1 0 S 2 1 Rising edge of Bit. Clock coincides with rising edge of FSM clock. Bit. In changes at falling edge of Bit. Clock Use falling edge of FSM clock for synchronization (will be at midpoint of bit time) so no danger of sampling Bit. Clock while it’s changing 57

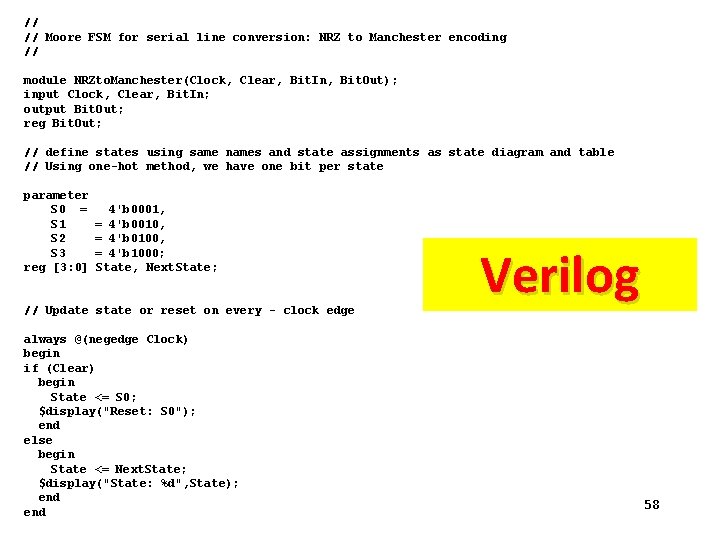

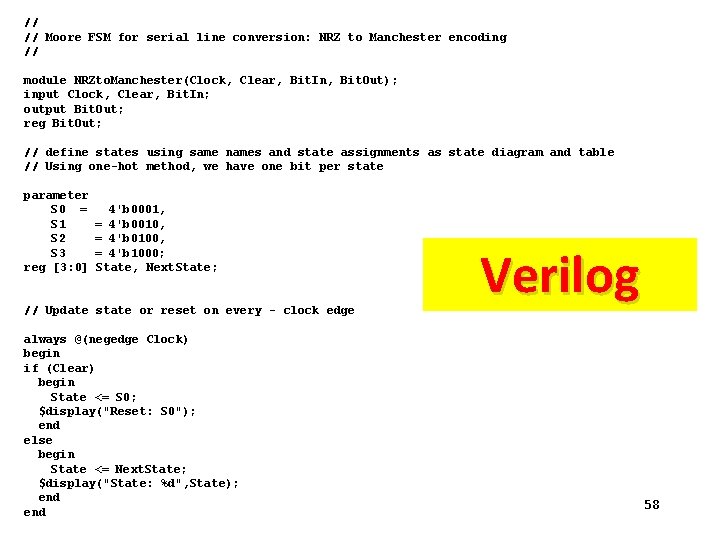

// // Moore FSM for serial line conversion: NRZ to Manchester encoding // module NRZto. Manchester(Clock, Clear, Bit. In, Bit. Out); input Clock, Clear, Bit. In; output Bit. Out; reg Bit. Out; // define states using same names and state assignments as state diagram and table // Using one-hot method, we have one bit per state parameter S 0 = S 1 S 2 S 3 reg [3: 0] 4'b 0001, = 4'b 0010, = 4'b 0100, = 4'b 1000; State, Next. State; // Update state or reset on every - clock edge always @(negedge Clock) begin if (Clear) begin State <= S 0; $display("Reset: S 0"); end else begin State <= Next. State; $display("State: %d", State); end Verilog 58

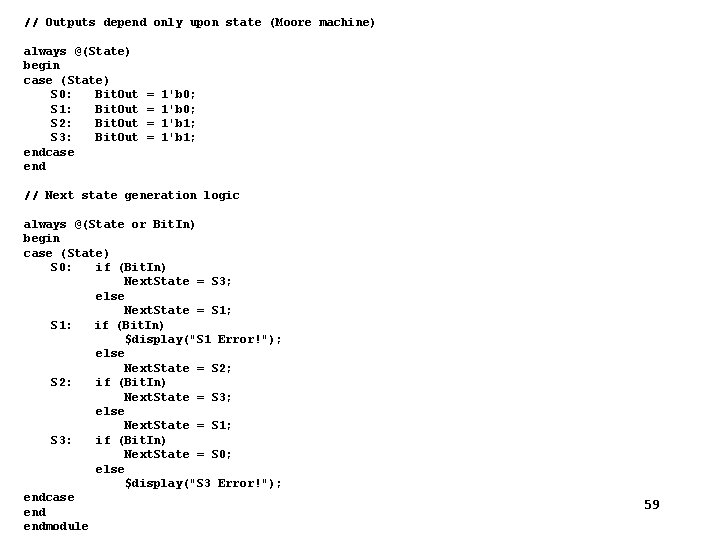

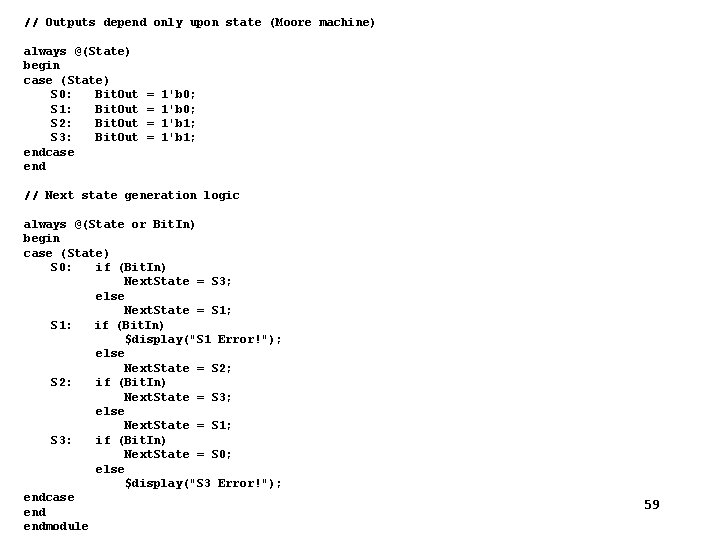

// Outputs depend only upon state (Moore machine) always @(State) begin case (State) S 0: Bit. Out S 1: Bit. Out S 2: Bit. Out S 3: Bit. Out endcase end = = 1'b 0; 1'b 1; // Next state generation logic always @(State or Bit. In) begin case (State) S 0: if (Bit. In) Next. State = S 3; else Next. State = S 1; S 1: if (Bit. In) $display("S 1 Error!"); else Next. State = S 2; S 2: if (Bit. In) Next. State = S 3; else Next. State = S 1; S 3: if (Bit. In) Next. State = S 0; else $display("S 3 Error!"); endcase endmodule 59

60

Example: Airplane Gear

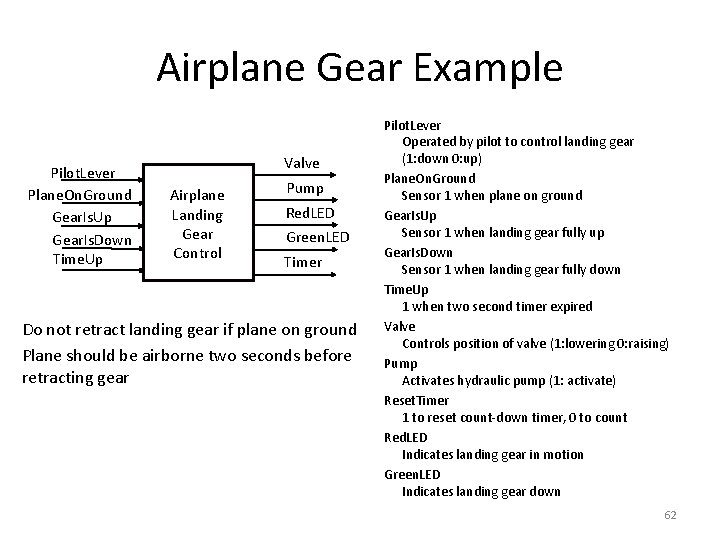

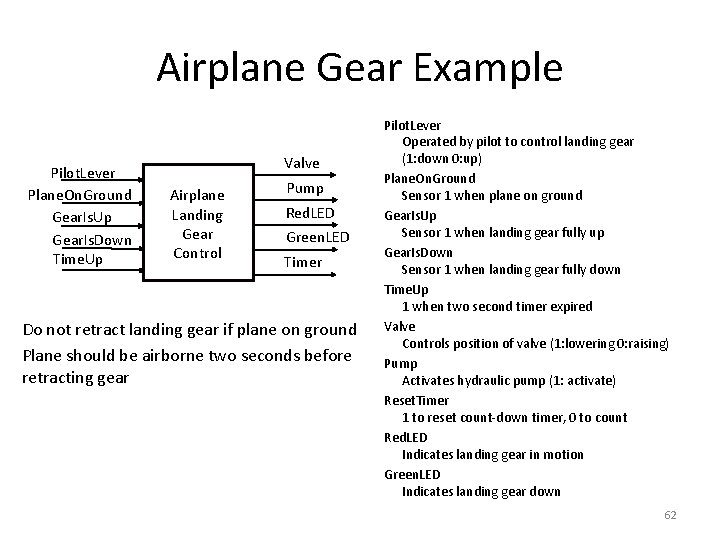

Airplane Gear Example Pilot. Lever Plane. On. Ground Gear. Is. Up Gear. Is. Down Time. Up Valve Airplane Landing Gear Control Pump Red. LED Green. LED Timer Do not retract landing gear if plane on ground Plane should be airborne two seconds before retracting gear Pilot. Lever Operated by pilot to control landing gear (1: down 0: up) Plane. On. Ground Sensor 1 when plane on ground Gear. Is. Up Sensor 1 when landing gear fully up Gear. Is. Down Sensor 1 when landing gear fully down Time. Up 1 when two second timer expired Valve Controls position of valve (1: lowering 0: raising) Pump Activates hydraulic pump (1: activate) Reset. Timer 1 to reset count-down timer, 0 to count Red. LED Indicates landing gear in motion Green. LED Indicates landing gear down 62

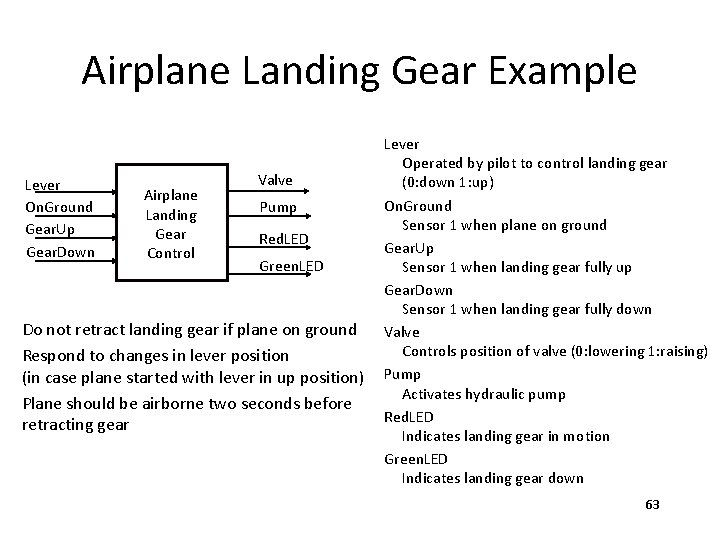

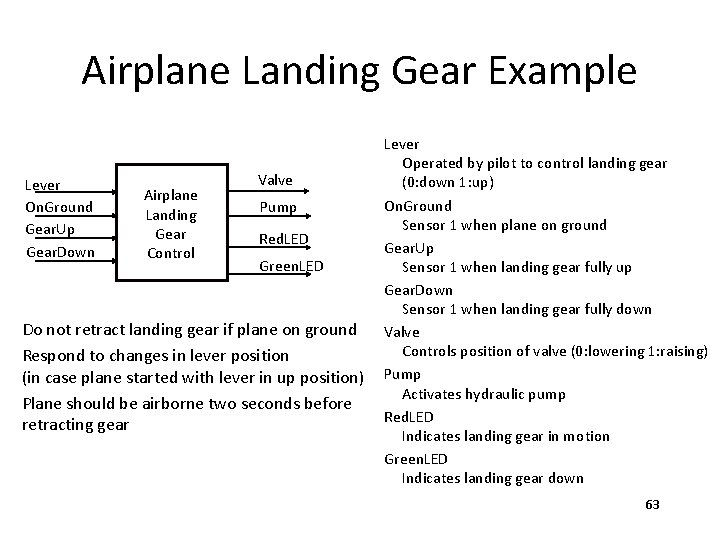

Airplane Landing Gear Example Lever On. Ground Gear. Up Gear. Down Airplane Landing Gear Control Valve Pump Red. LED Green. LED Do not retract landing gear if plane on ground Respond to changes in lever position (in case plane started with lever in up position) Plane should be airborne two seconds before retracting gear Lever Operated by pilot to control landing gear (0: down 1: up) On. Ground Sensor 1 when plane on ground Gear. Up Sensor 1 when landing gear fully up Gear. Down Sensor 1 when landing gear fully down Valve Controls position of valve (0: lowering 1: raising) Pump Activates hydraulic pump Red. LED Indicates landing gear in motion Green. LED Indicates landing gear down 63

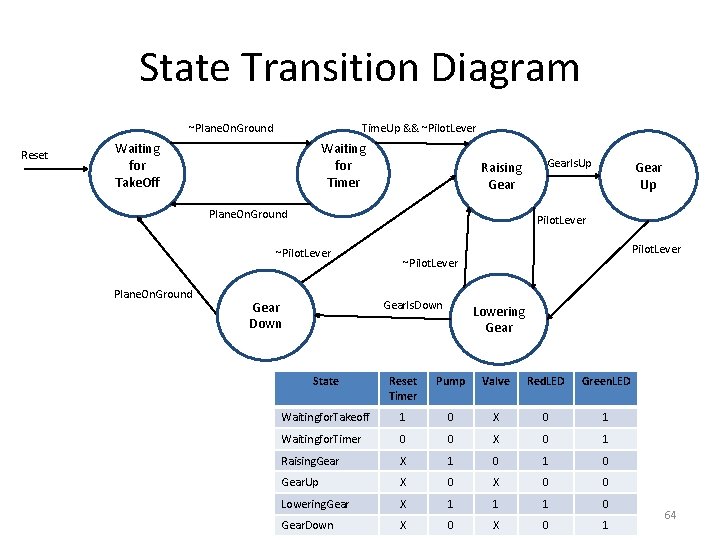

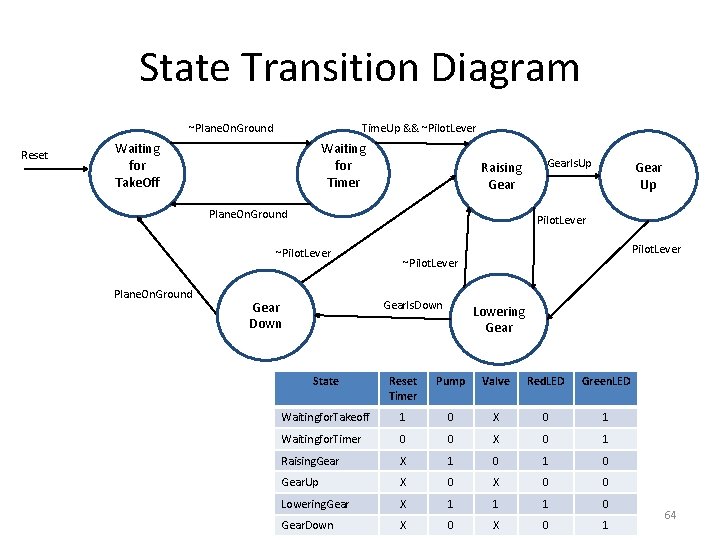

State Transition Diagram Time. Up && ~Pilot. Lever ~Plane. On. Ground Reset Waiting for Take. Off Waiting for Timer Raising Gear Plane. On. Ground Gear Up Pilot. Lever ~Pilot. Lever Plane. On. Ground Gear. Is. Up Pilot. Lever ~Pilot. Lever Gear. Is. Down Gear Down Lowering Gear State Reset Timer Pump Valve Red. LED Green. LED Waitingfor. Takeoff 1 0 X 0 1 Waitingfor. Timer 0 0 X 0 1 Raising. Gear X 1 0 Gear. Up X 0 0 Lowering. Gear X 1 1 1 0 Gear. Down X 0 1 64

Example Vending Machine • Taken from Katz & Borriello, “Contemporary Logic Design” 65

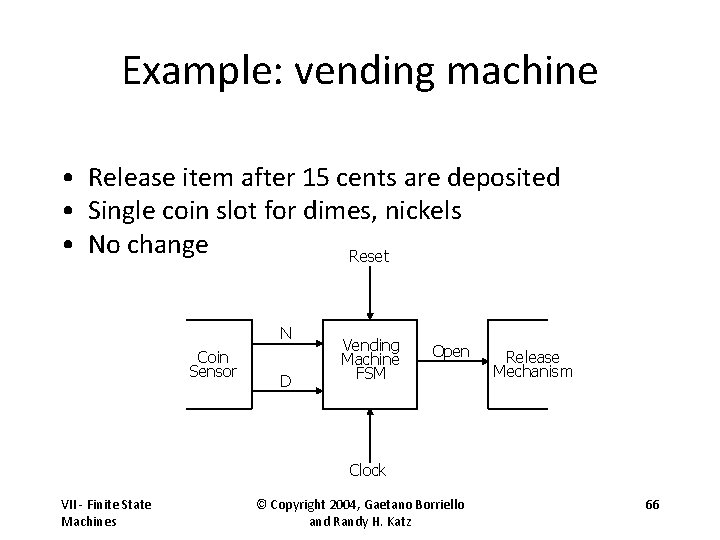

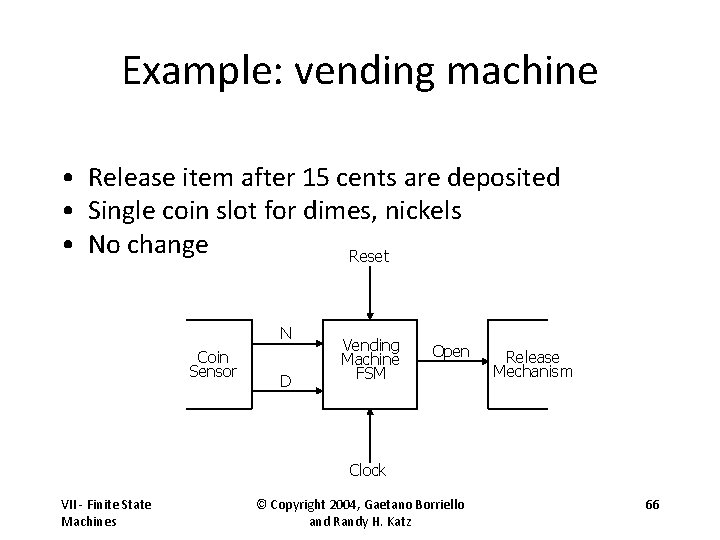

Example: vending machine • Release item after 15 cents are deposited • Single coin slot for dimes, nickels • No change Reset N Coin Sensor D Vending Machine FSM Open Release Mechanism Clock VII - Finite State Machines © Copyright 2004, Gaetano Borriello and Randy H. Katz 66

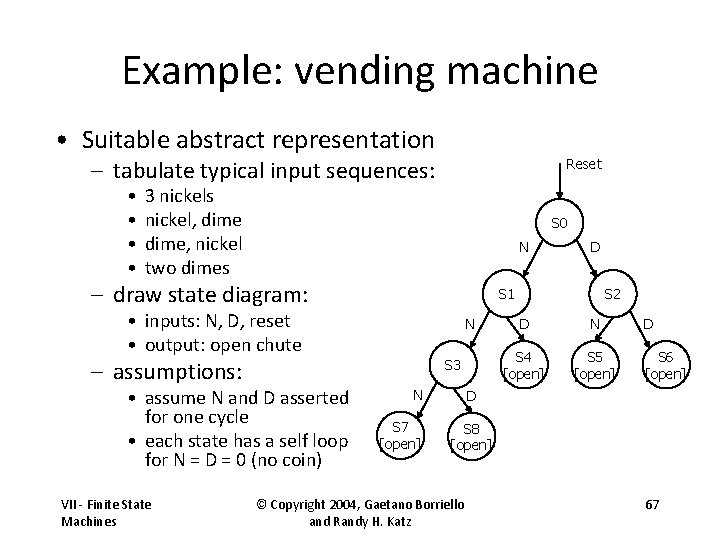

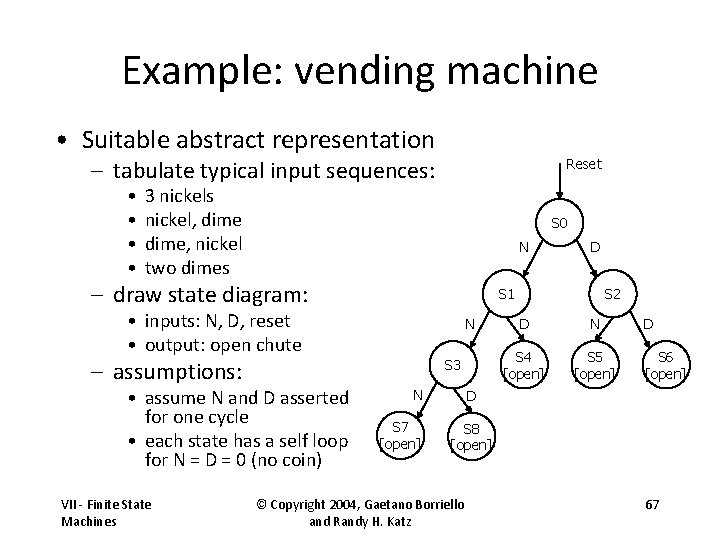

Example: vending machine • Suitable abstract representation – tabulate typical input sequences: • • Reset 3 nickels nickel, dime, nickel two dimes S 0 N – draw state diagram: S 1 • inputs: N, D, reset • output: open chute – assumptions: • assume N and D asserted for one cycle • each state has a self loop for N = D = 0 (no coin) VII - Finite State Machines D N S 3 N S 7 [open] S 2 D N S 4 [open] S 5 [open] D S 6 [open] D S 8 [open] © Copyright 2004, Gaetano Borriello and Randy H. Katz 67

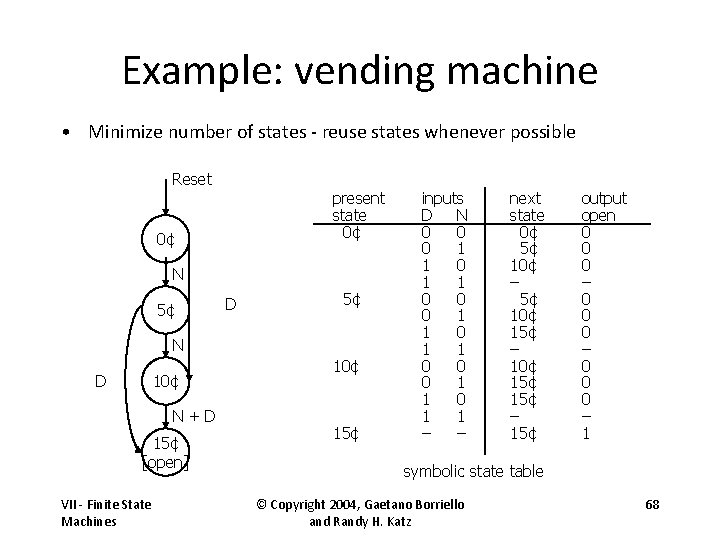

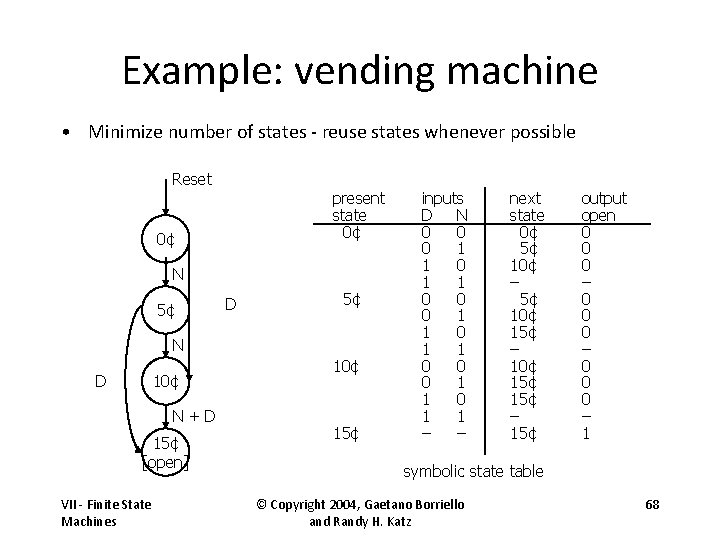

Example: vending machine • Minimize number of states - reuse states whenever possible Reset present state 0¢ 0¢ N 5¢ D 5¢ N D 10¢ N+D 15¢ [open] VII - Finite State Machines 10¢ 15¢ inputs D N 0 0 0 1 1 0 0 0 1 1 – – next state 0¢ 5¢ 10¢ – 5¢ 10¢ 15¢ – 15¢ output open 0 0 0 – 1 symbolic state table © Copyright 2004, Gaetano Borriello and Randy H. Katz 68

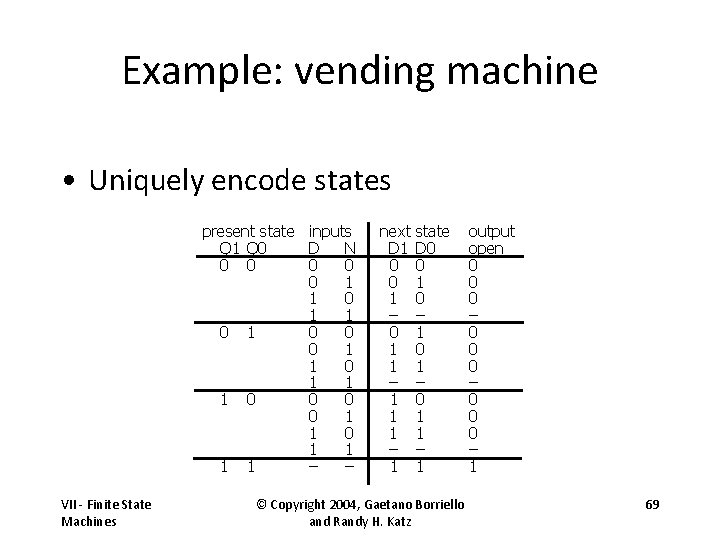

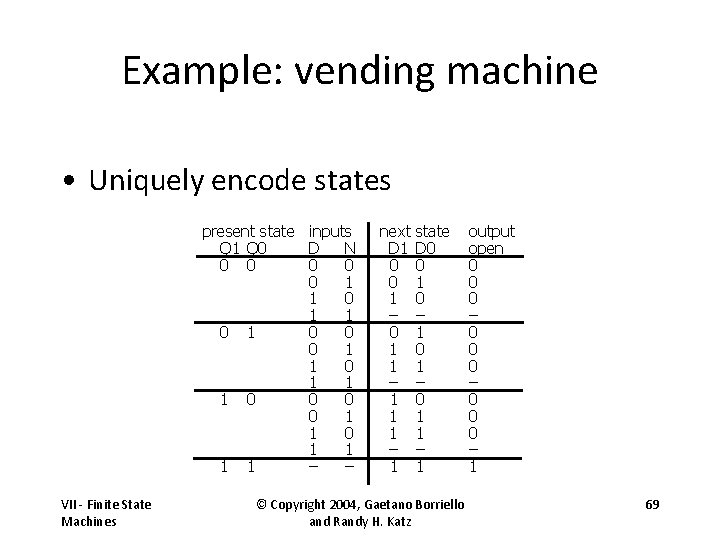

Example: vending machine • Uniquely encode states present state inputs Q 1 Q 0 D N 0 0 0 1 1 0 1 0 0 0 1 1 1 0 0 1 1 – – VII - Finite State Machines next D 1 0 0 1 – 0 1 1 – 1 state D 0 0 1 0 – 1 0 1 – 0 1 1 – 1 © Copyright 2004, Gaetano Borriello and Randy H. Katz output open 0 0 0 – 1 69

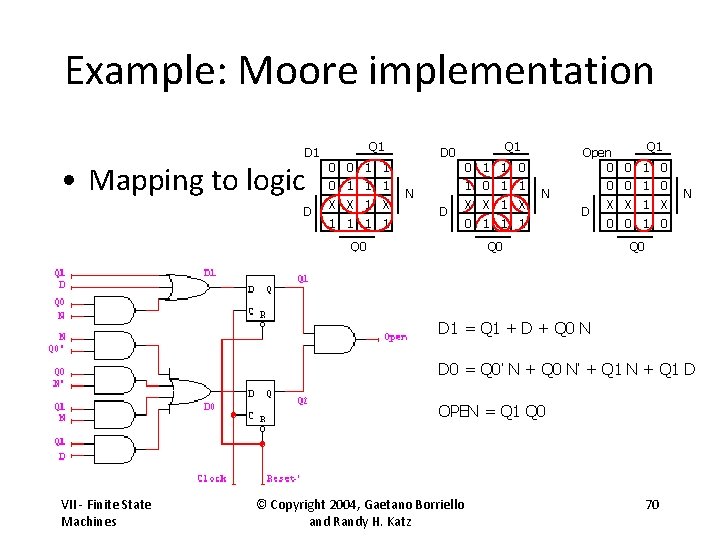

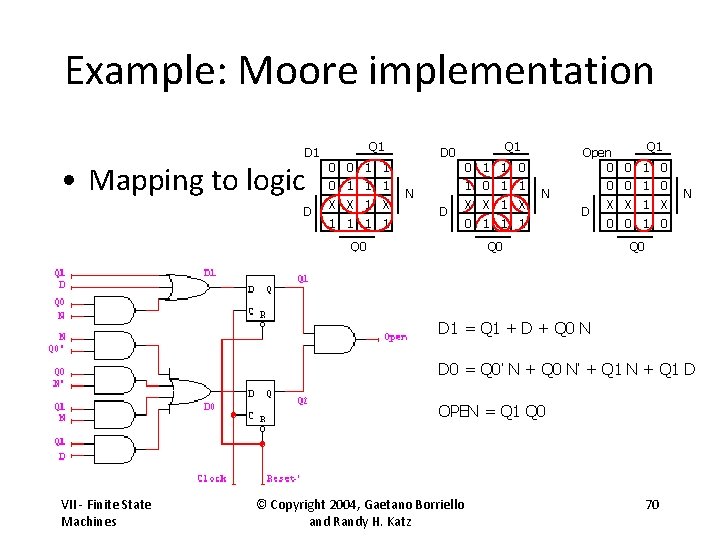

Example: Moore implementation Q 1 D 1 • Mapping to logic D 0 0 1 1 1 X X 1 1 1 1 Q 1 D 0 Q 1 Open 0 0 1 1 N D Q 0 X X 1 X 0 0 1 0 N 0 1 1 1 D Q 0 X X 1 X N 0 0 1 0 Q 0 D 1 = Q 1 + D + Q 0 N D 0 = Q 0’ N + Q 0 N’ + Q 1 N + Q 1 D OPEN = Q 1 Q 0 VII - Finite State Machines © Copyright 2004, Gaetano Borriello and Randy H. Katz 70

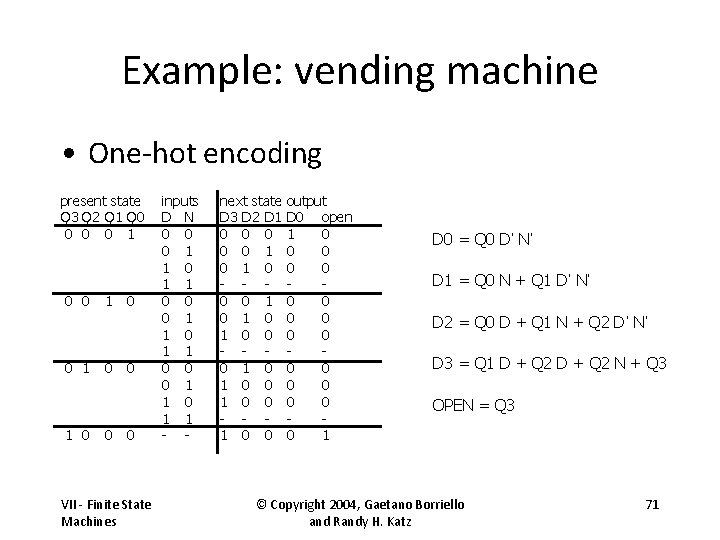

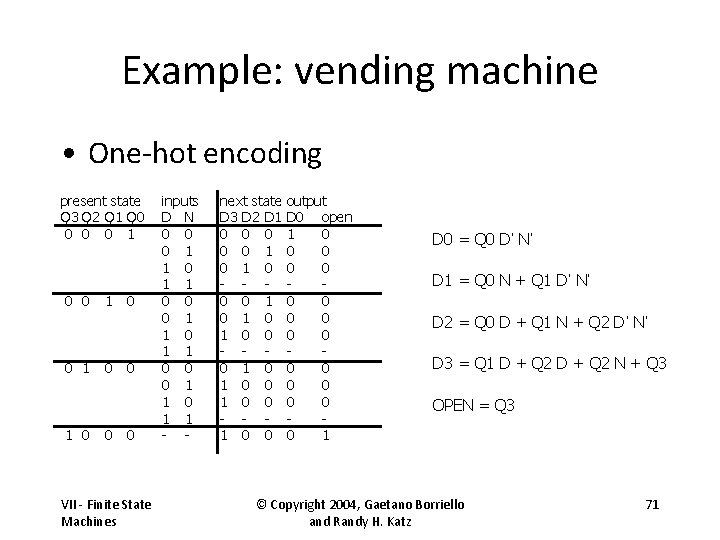

Example: vending machine • One-hot encoding present state Q 3 Q 2 Q 1 Q 0 0 1 0 0 0 1 1 0 0 0 VII - Finite State Machines inputs D N 0 0 0 1 1 0 0 0 1 1 - - next state D 3 D 2 D 1 0 0 0 1 0 - - 0 0 1 0 1 0 0 - - 0 1 0 0 - - 1 0 0 output D 0 open 1 0 0 0 0 0 1 D 0 = Q 0 D’ N’ D 1 = Q 0 N + Q 1 D’ N’ D 2 = Q 0 D + Q 1 N + Q 2 D’ N’ D 3 = Q 1 D + Q 2 N + Q 3 OPEN = Q 3 © Copyright 2004, Gaetano Borriello and Randy H. Katz 71

Types of FSMs inputs Moore combinational logic for next state reg logic for outputs state feedback inputs logic for outputs combinational logic for next state Mealy outputs reg state feedback inputs Synchronous Mealy logic for outputs combinational logic for next state feedback outputs reg 77

Sources Prof. Mark G. Faust John Wakerly