ECE 448 Lecture 7 Algorithmic State Machine ASM

- Slides: 32

ECE 448 Lecture 7 Algorithmic State Machine (ASM) Charts: VHDL Code & Timing Diagrams George Mason University

Required reading • P. Chu, FPGA Prototyping by VHDL Examples Chapter 5, FSM 2

Recommended reading • S. Brown and Z. Vranesic, Fundamentals of Digital Logic with VHDL Design Chapter 8, Synchronous Sequential Circuits Sections 8. 1 -8. 5 Section 8. 10, Algorithmic State Machine (ASM) Charts 3

Finite State Machines in VHDL 4

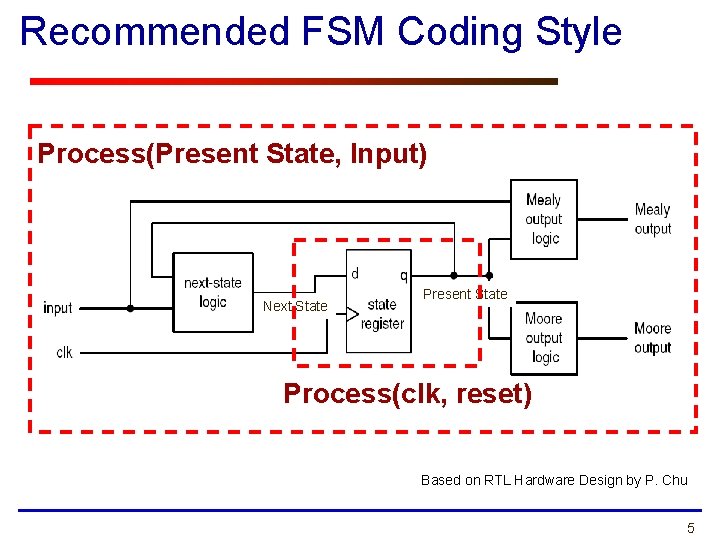

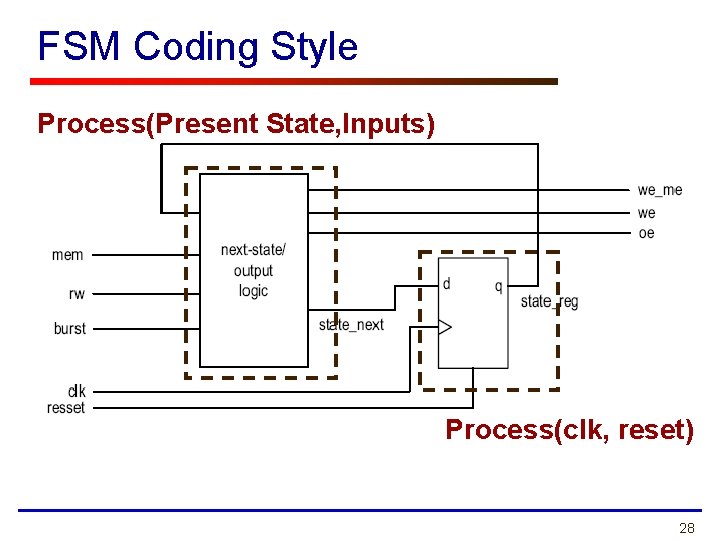

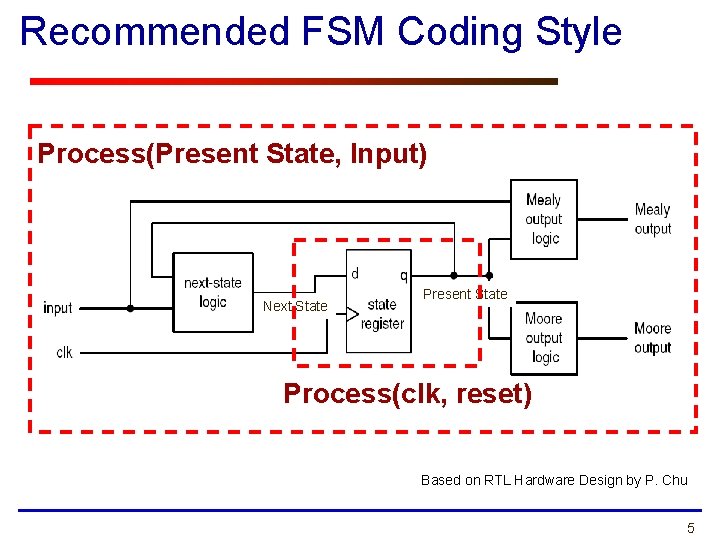

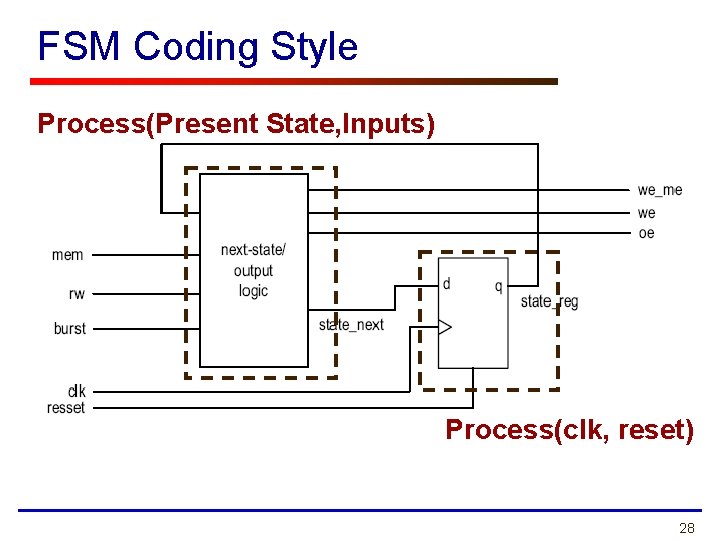

Recommended FSM Coding Style Process(Present State, Input) Next State Present State Process(clk, reset) Based on RTL Hardware Design by P. Chu 5

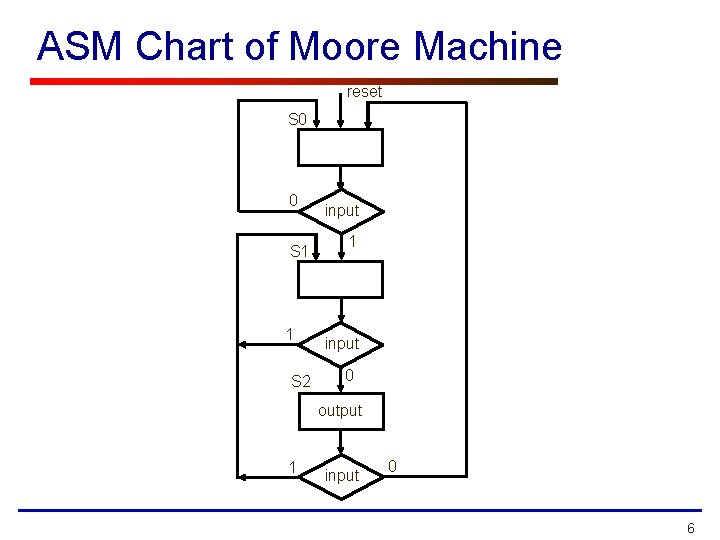

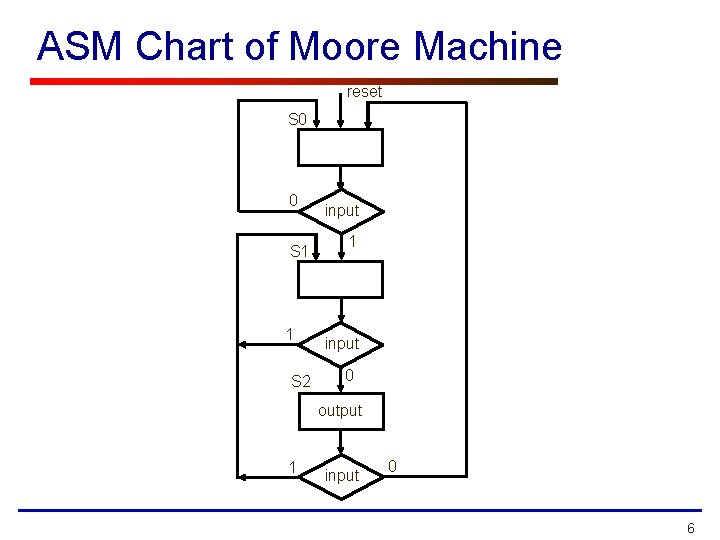

ASM Chart of Moore Machine reset S 0 0 S 1 1 S 2 input 1 input 0 output 1 input 0 6

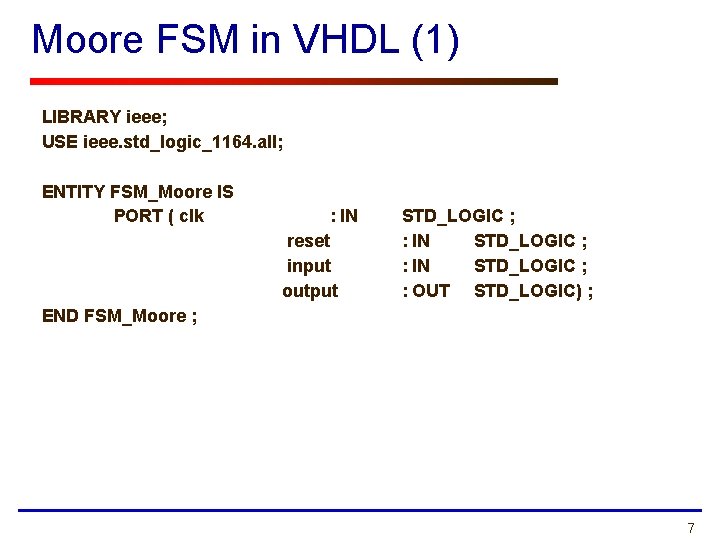

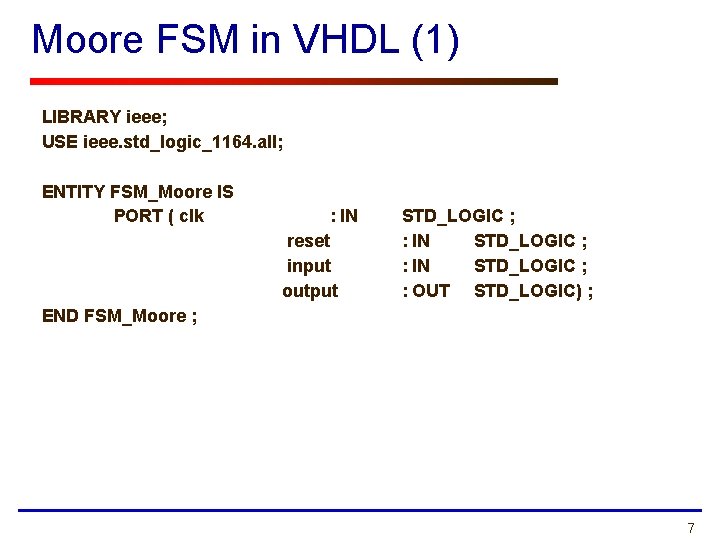

Moore FSM in VHDL (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY FSM_Moore IS PORT ( clk : IN reset input output STD_LOGIC ; : IN STD_LOGIC ; : OUT STD_LOGIC) ; END FSM_Moore ; 7

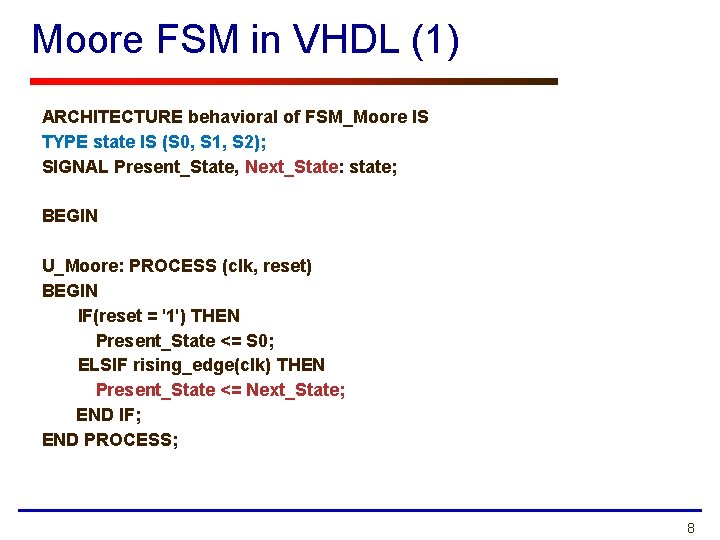

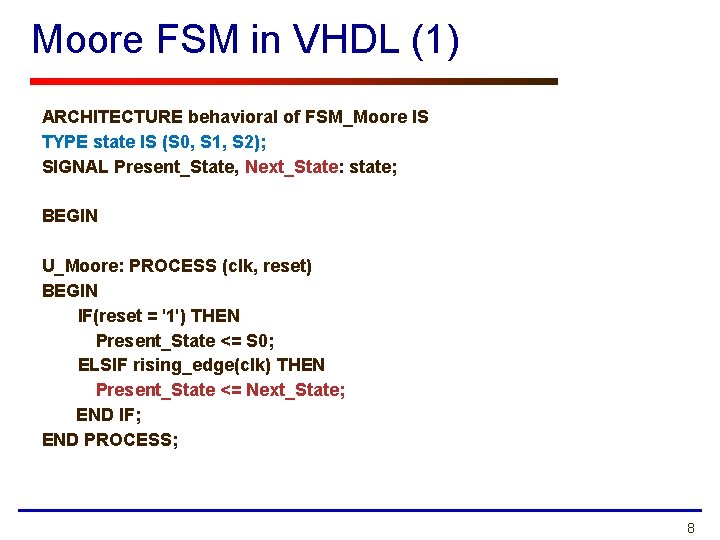

Moore FSM in VHDL (1) ARCHITECTURE behavioral of FSM_Moore IS TYPE state IS (S 0, S 1, S 2); SIGNAL Present_State, Next_State: state; BEGIN U_Moore: PROCESS (clk, reset) BEGIN IF(reset = '1') THEN Present_State <= S 0; ELSIF rising_edge(clk) THEN Present_State <= Next_State; END IF; END PROCESS; 8

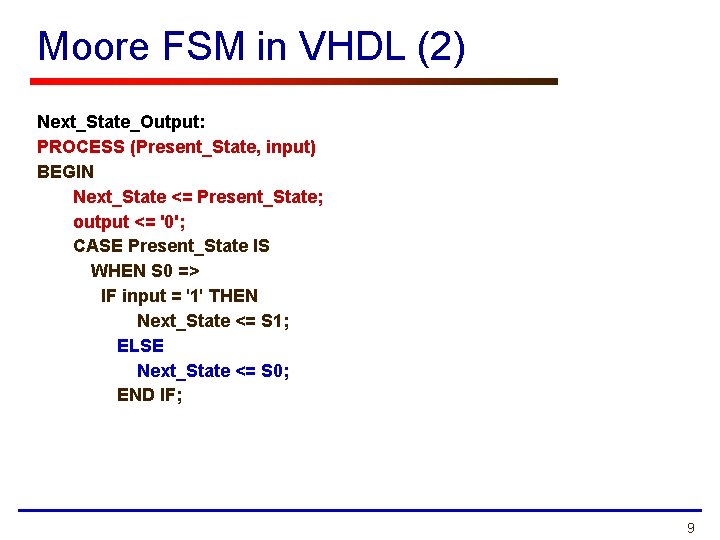

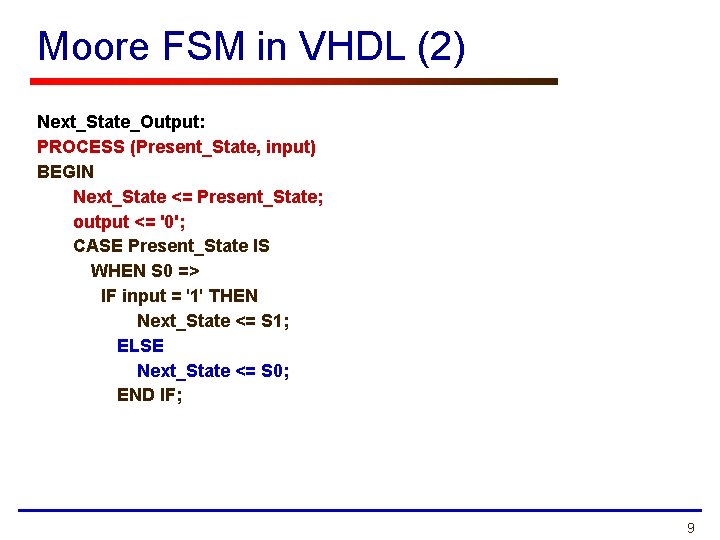

Moore FSM in VHDL (2) Next_State_Output: PROCESS (Present_State, input) BEGIN Next_State <= Present_State; output <= '0'; CASE Present_State IS WHEN S 0 => IF input = '1' THEN Next_State <= S 1; ELSE Next_State <= S 0; END IF; 9

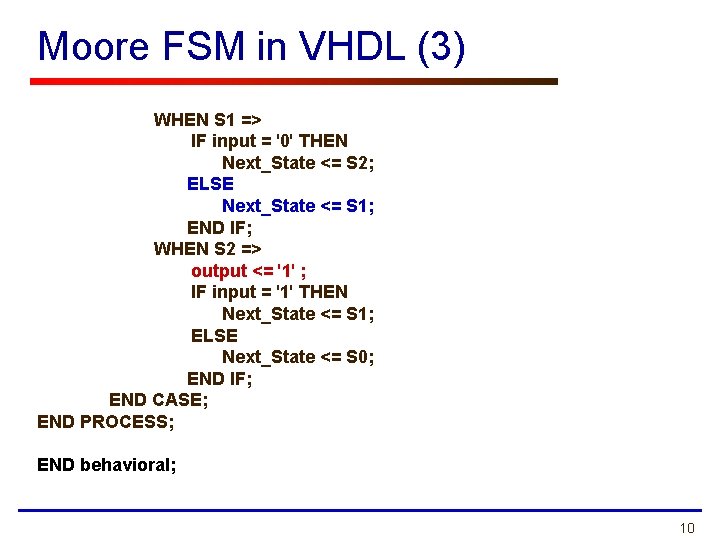

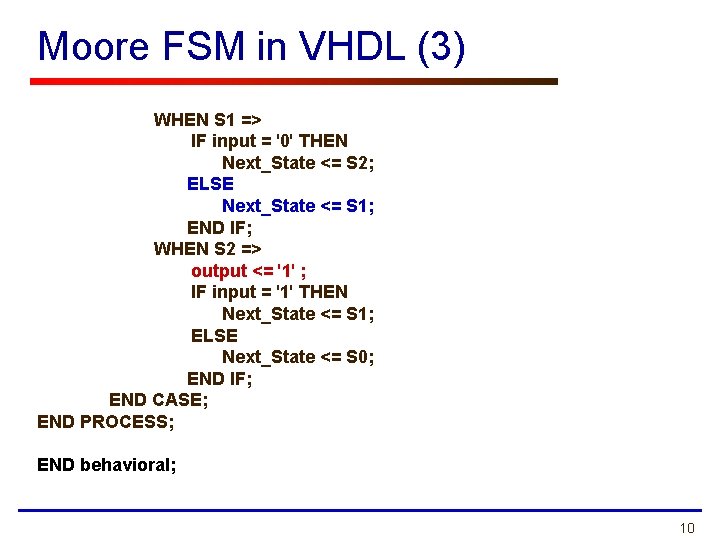

Moore FSM in VHDL (3) WHEN S 1 => IF input = '0' THEN Next_State <= S 2; ELSE Next_State <= S 1; END IF; WHEN S 2 => output <= '1' ; IF input = '1' THEN Next_State <= S 1; ELSE Next_State <= S 0; END IF; END CASE; END PROCESS; END behavioral; 10

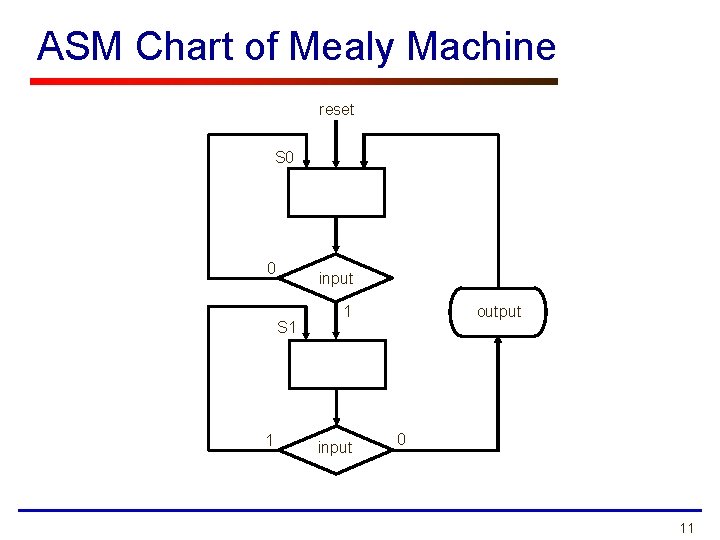

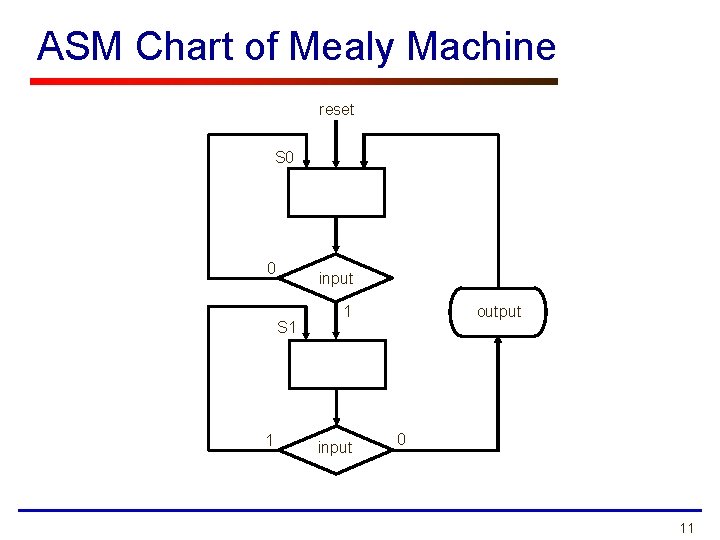

ASM Chart of Mealy Machine reset S 0 0 input S 1 1 1 input output 0 11

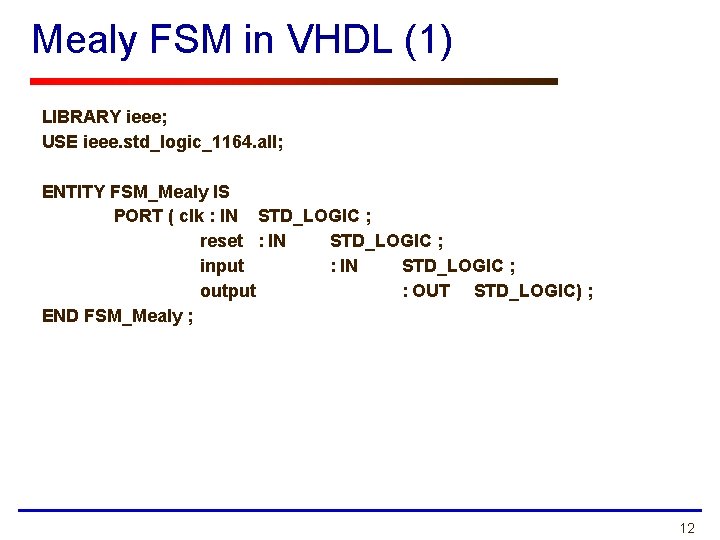

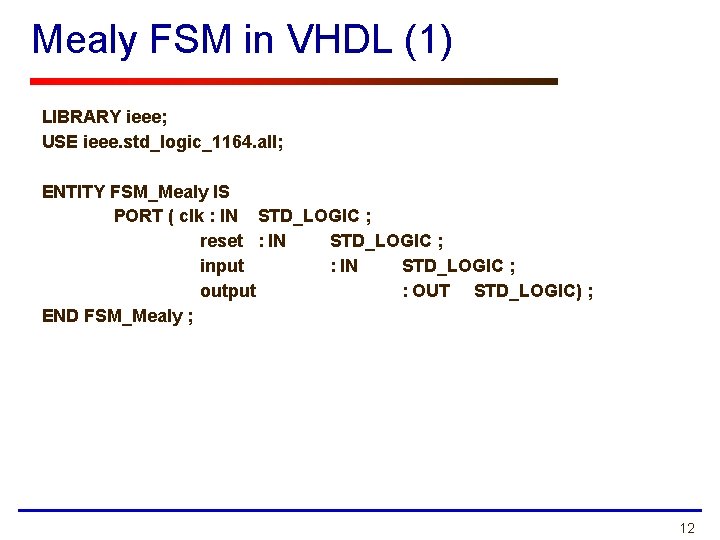

Mealy FSM in VHDL (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY FSM_Mealy IS PORT ( clk : IN STD_LOGIC ; reset : IN STD_LOGIC ; input : IN STD_LOGIC ; output : OUT STD_LOGIC) ; END FSM_Mealy ; 12

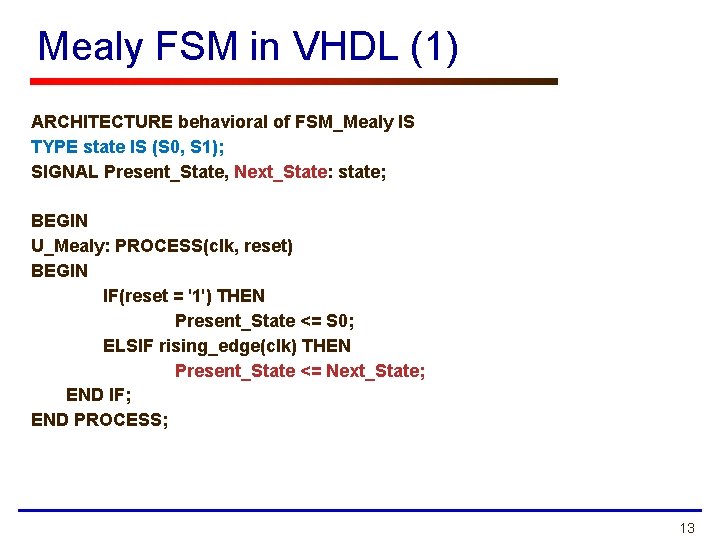

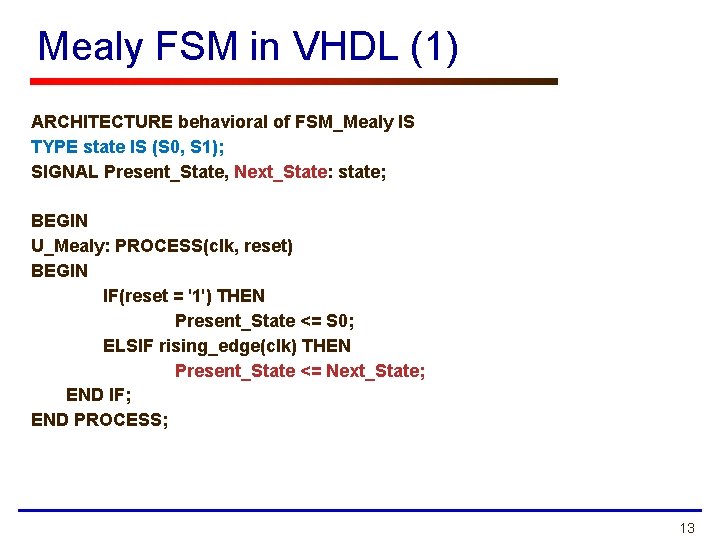

Mealy FSM in VHDL (1) ARCHITECTURE behavioral of FSM_Mealy IS TYPE state IS (S 0, S 1); SIGNAL Present_State, Next_State: state; BEGIN U_Mealy: PROCESS(clk, reset) BEGIN IF(reset = '1') THEN Present_State <= S 0; ELSIF rising_edge(clk) THEN Present_State <= Next_State; END IF; END PROCESS; 13

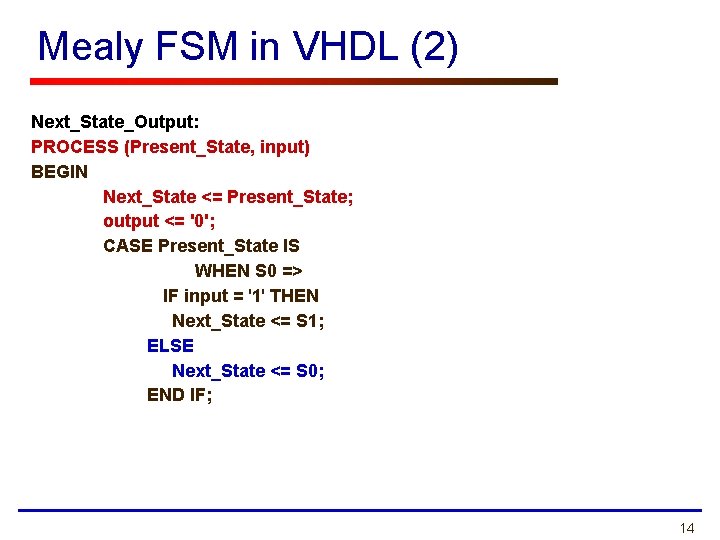

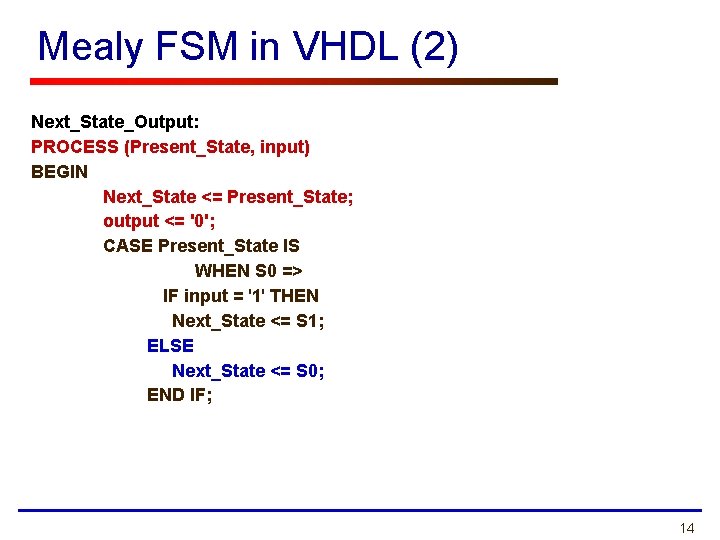

Mealy FSM in VHDL (2) Next_State_Output: PROCESS (Present_State, input) BEGIN Next_State <= Present_State; output <= '0'; CASE Present_State IS WHEN S 0 => IF input = '1' THEN Next_State <= S 1; ELSE Next_State <= S 0; END IF; 14

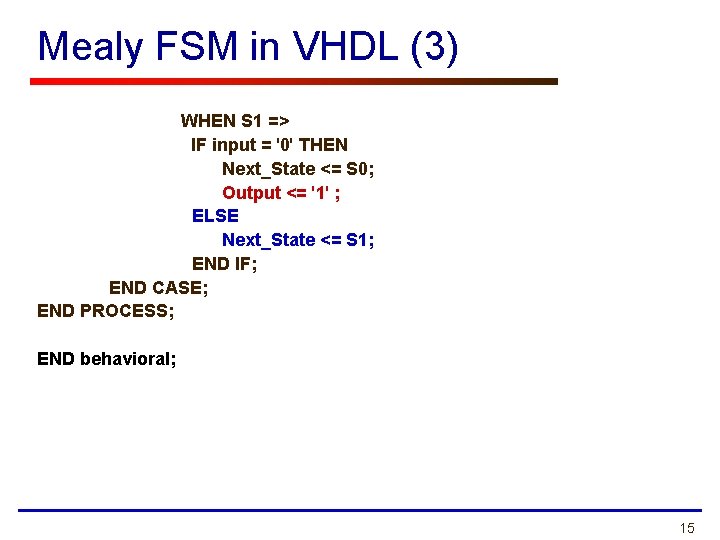

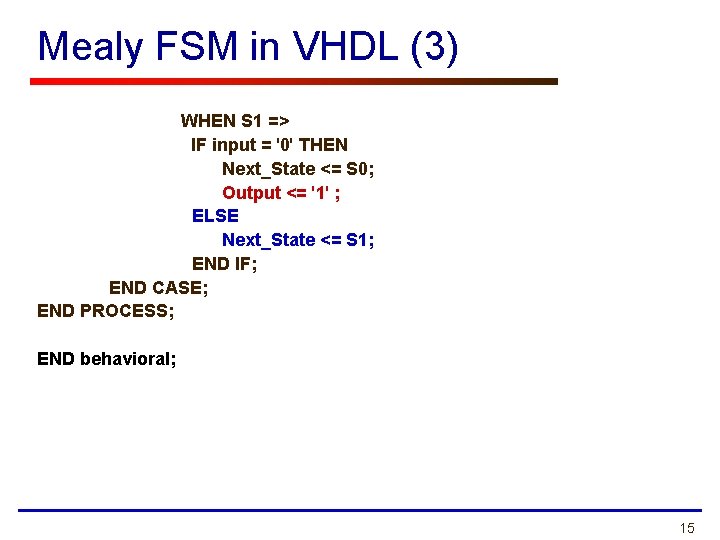

Mealy FSM in VHDL (3) WHEN S 1 => IF input = '0' THEN Next_State <= S 0; Output <= '1' ; ELSE Next_State <= S 1; END IF; END CASE; END PROCESS; END behavioral; 15

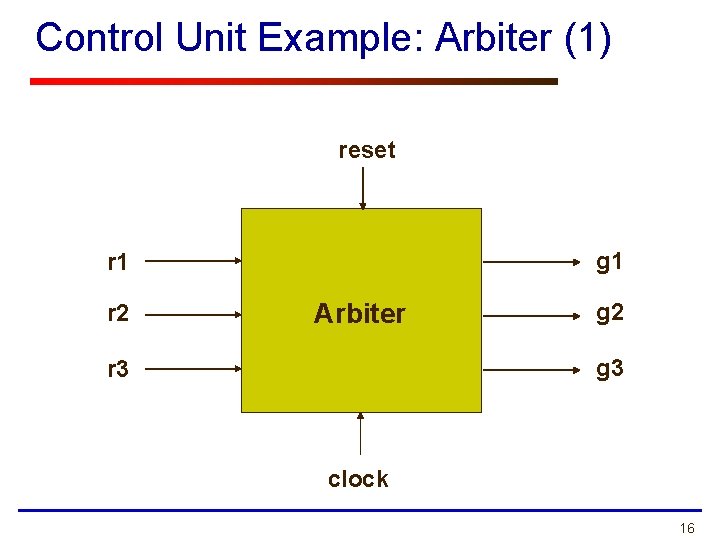

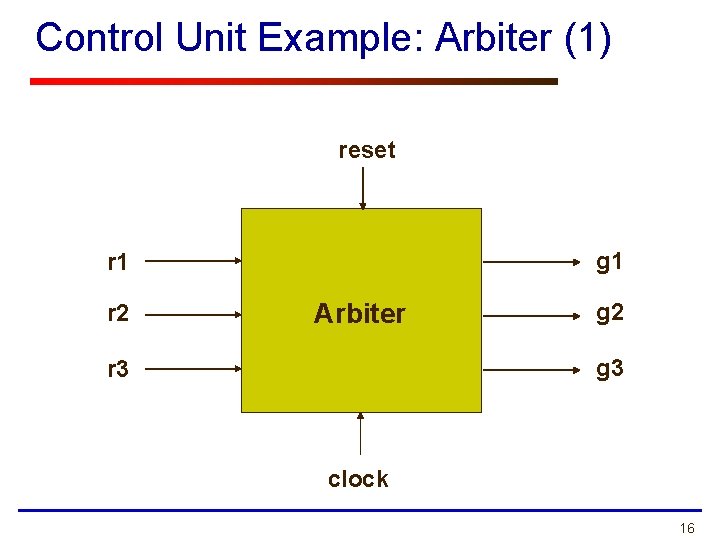

Control Unit Example: Arbiter (1) reset g 1 r 2 Arbiter g 2 g 3 r 3 clock 16

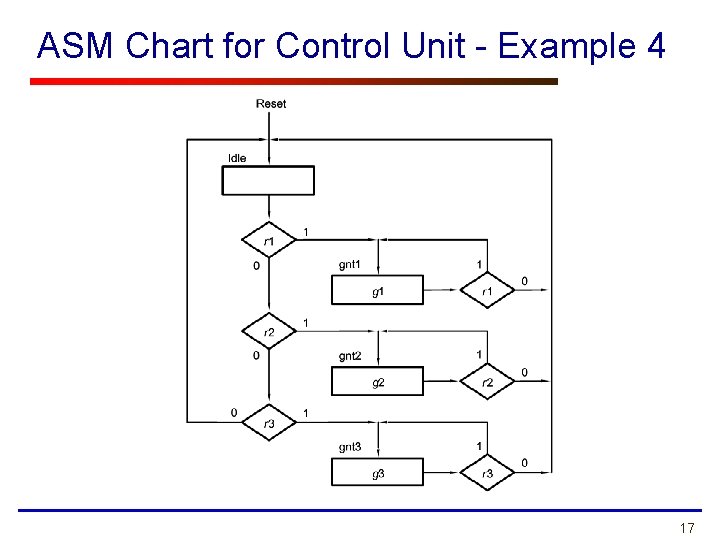

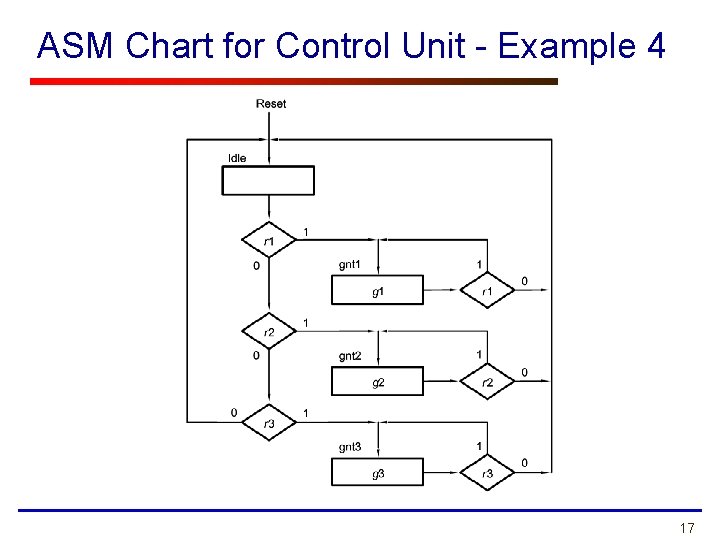

ASM Chart for Control Unit - Example 4 17

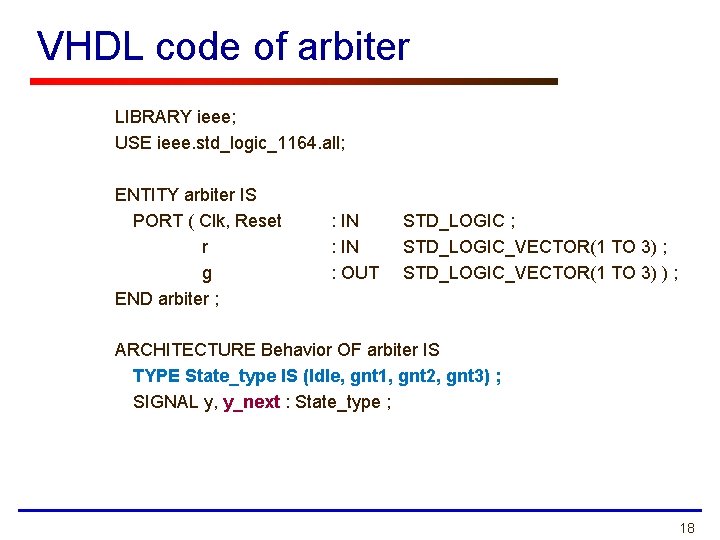

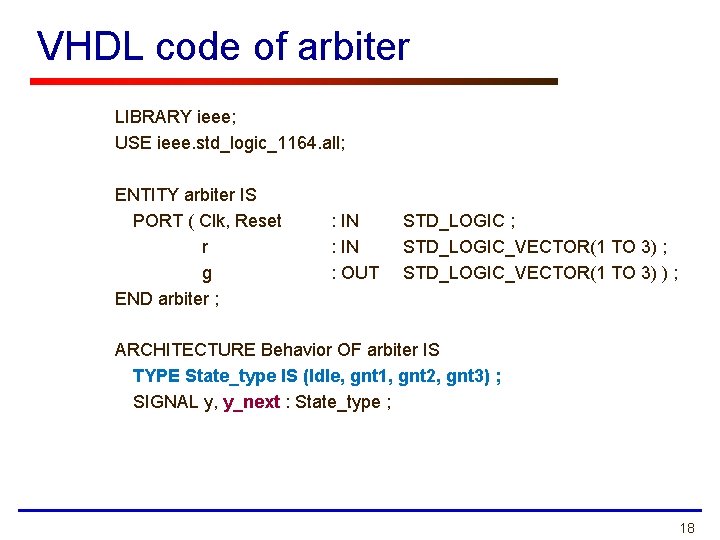

VHDL code of arbiter LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY arbiter IS PORT ( Clk, Reset r g END arbiter ; : IN : OUT STD_LOGIC ; STD_LOGIC_VECTOR(1 TO 3) ) ; ARCHITECTURE Behavior OF arbiter IS TYPE State_type IS (Idle, gnt 1, gnt 2, gnt 3) ; SIGNAL y, y_next : State_type ; 18

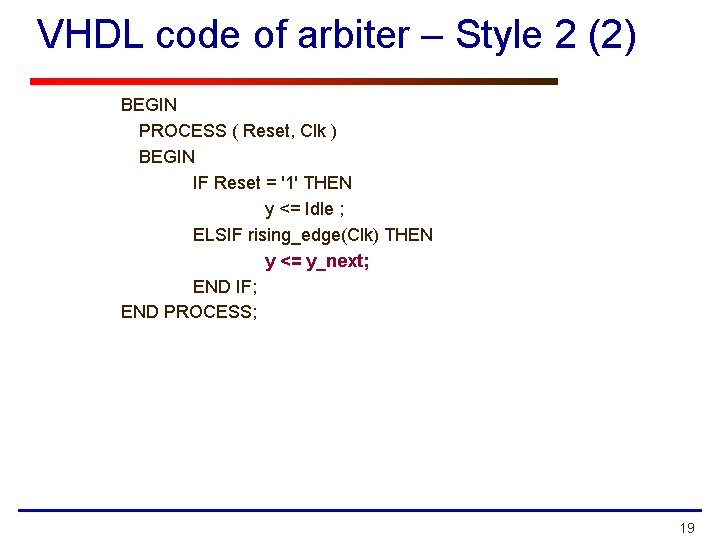

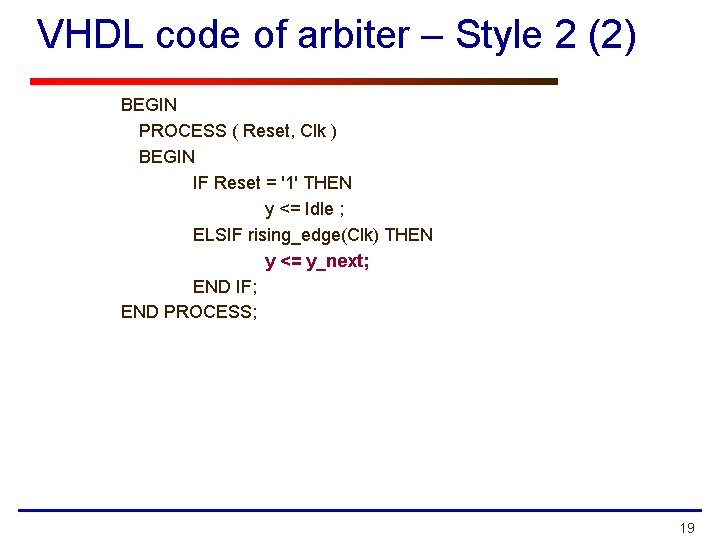

VHDL code of arbiter – Style 2 (2) BEGIN PROCESS ( Reset, Clk ) BEGIN IF Reset = '1' THEN y <= Idle ; ELSIF rising_edge(Clk) THEN y <= y_next; END IF; END PROCESS; 19

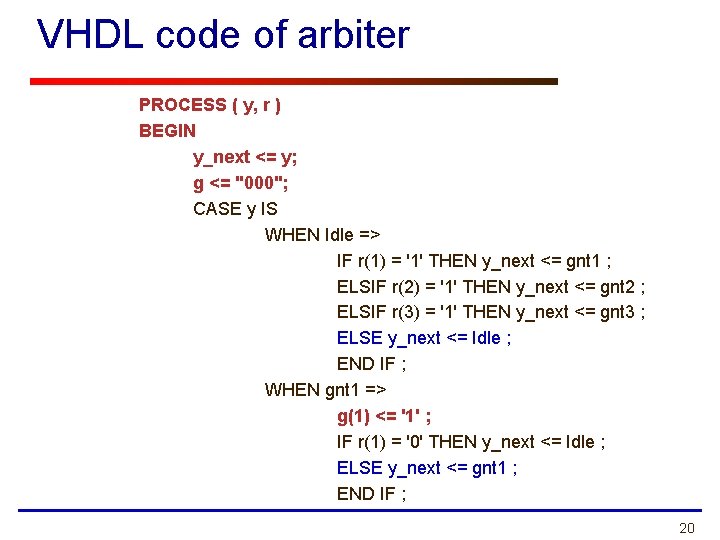

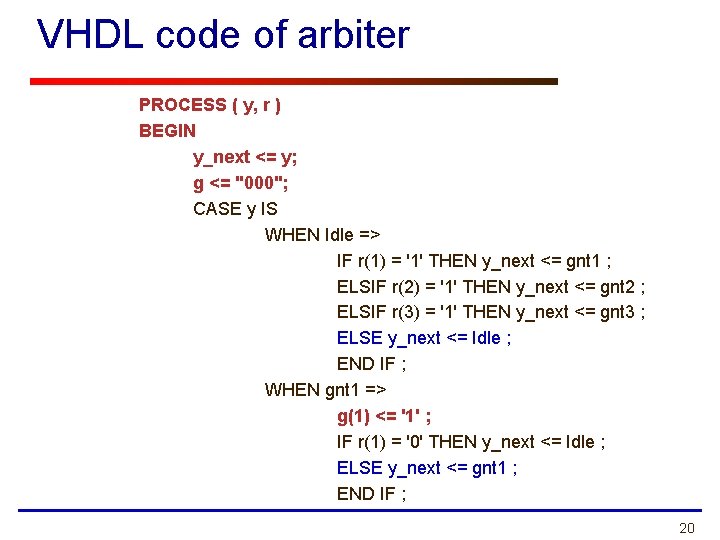

VHDL code of arbiter PROCESS ( y, r ) BEGIN y_next <= y; g <= "000"; CASE y IS WHEN Idle => IF r(1) = '1' THEN y_next <= gnt 1 ; ELSIF r(2) = '1' THEN y_next <= gnt 2 ; ELSIF r(3) = '1' THEN y_next <= gnt 3 ; ELSE y_next <= Idle ; END IF ; WHEN gnt 1 => g(1) <= '1' ; IF r(1) = '0' THEN y_next <= Idle ; ELSE y_next <= gnt 1 ; END IF ; 20

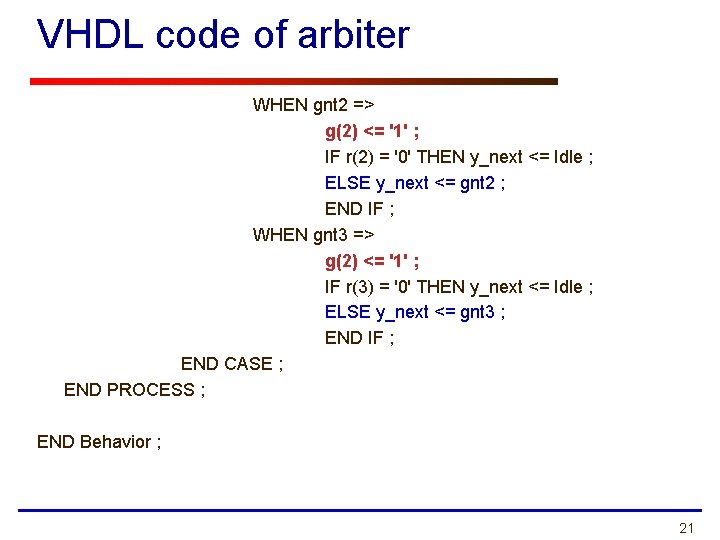

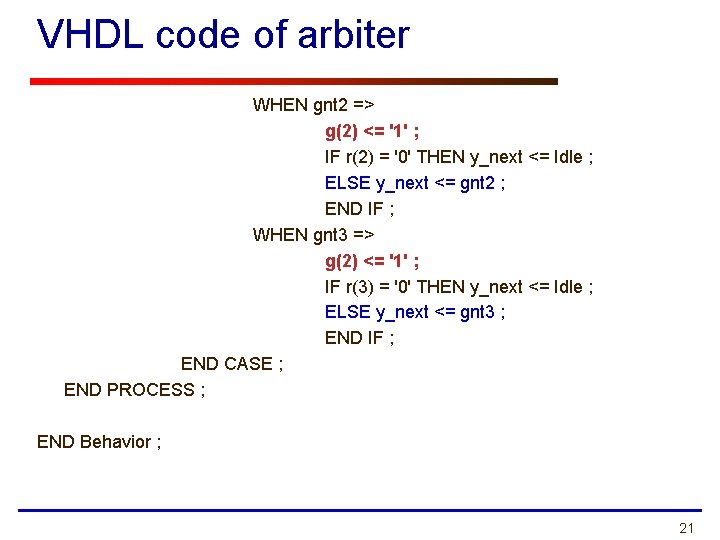

VHDL code of arbiter WHEN gnt 2 => g(2) <= '1' ; IF r(2) = '0' THEN y_next <= Idle ; ELSE y_next <= gnt 2 ; END IF ; WHEN gnt 3 => g(2) <= '1' ; IF r(3) = '0' THEN y_next <= Idle ; ELSE y_next <= gnt 3 ; END IF ; END CASE ; END PROCESS ; END Behavior ; 21

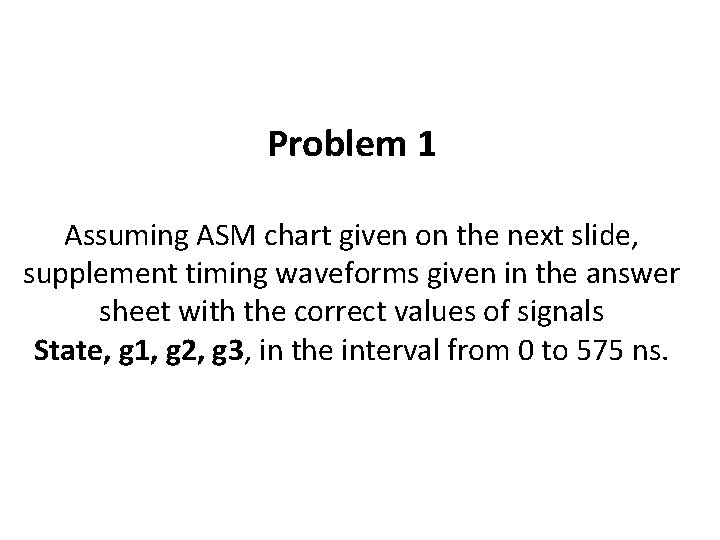

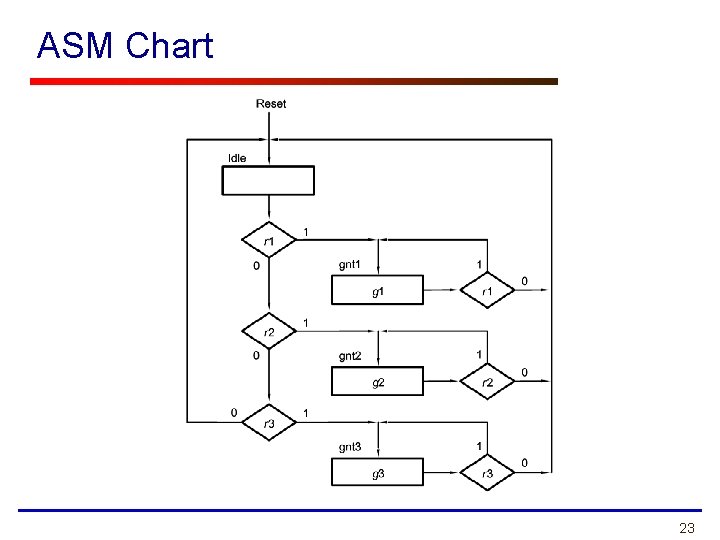

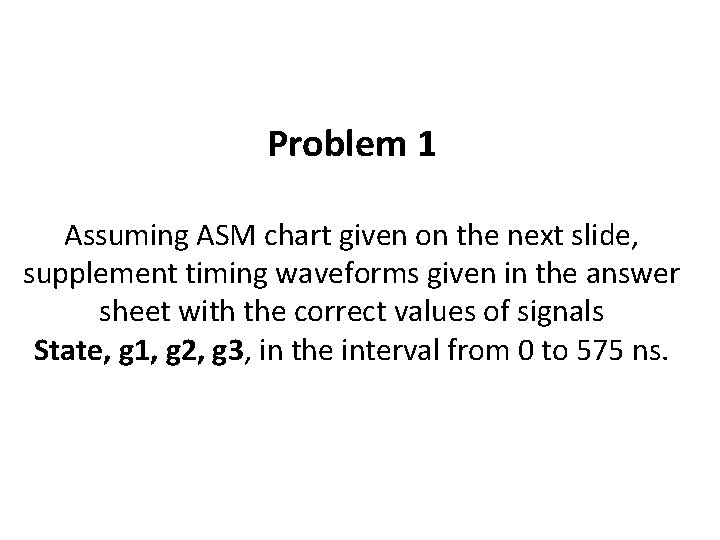

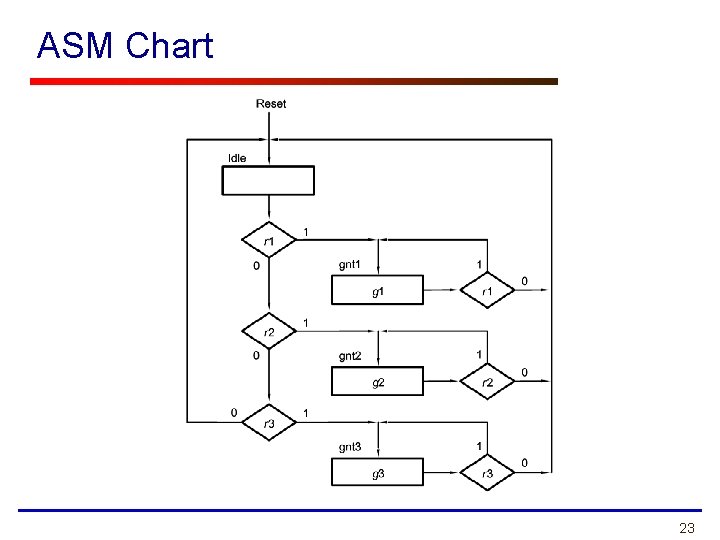

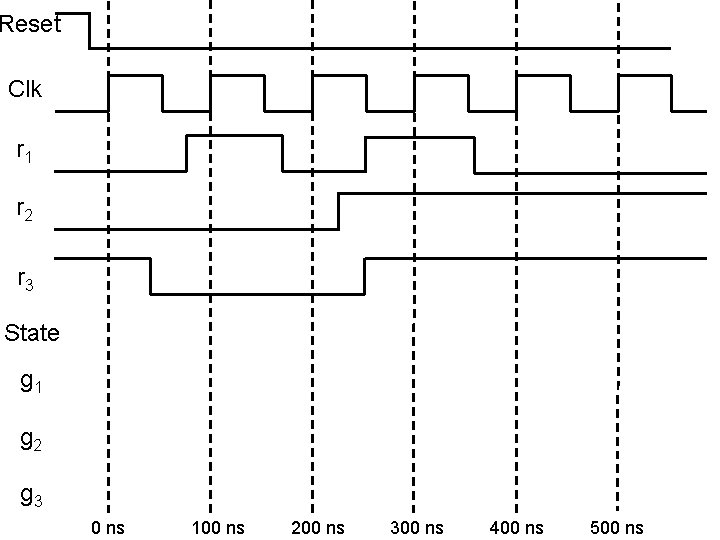

Problem 1 Assuming ASM chart given on the next slide, supplement timing waveforms given in the answer sheet with the correct values of signals State, g 1, g 2, g 3, in the interval from 0 to 575 ns.

ASM Chart 23

Reset Clk r 1 r 2 r 3 State g 1 g 2 g 3 0 ns 100 ns 200 ns 300 ns 400 ns 500 ns

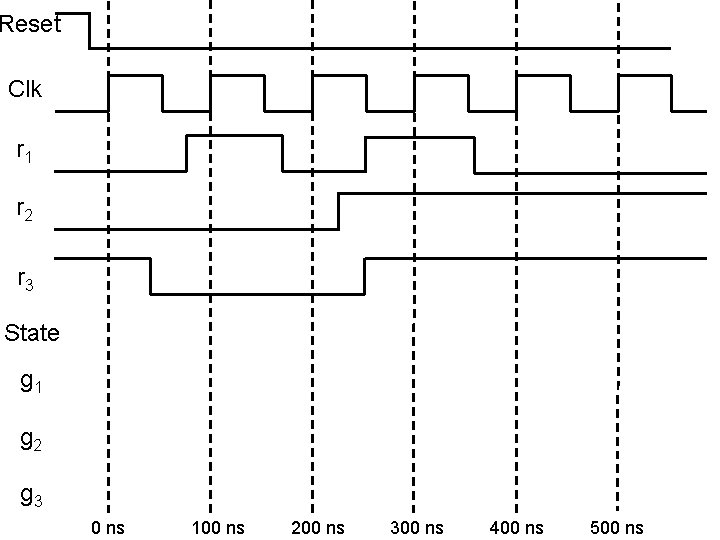

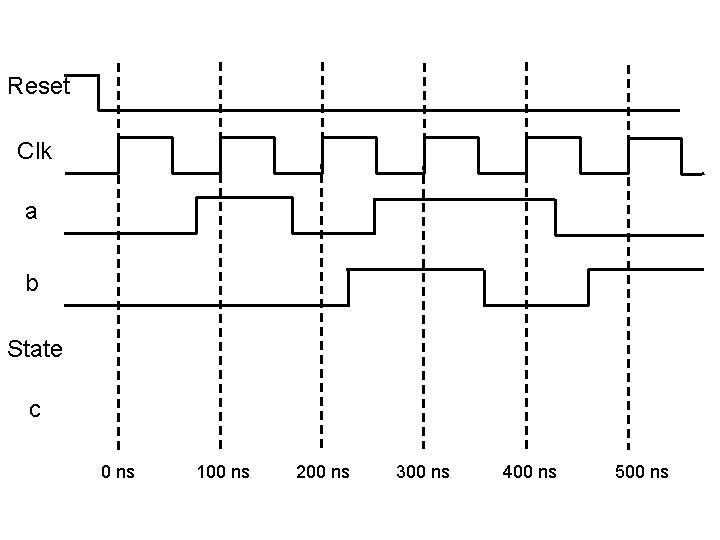

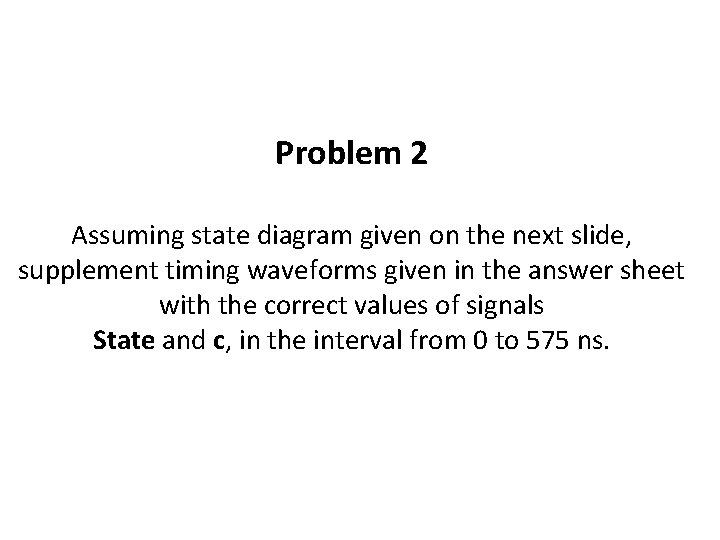

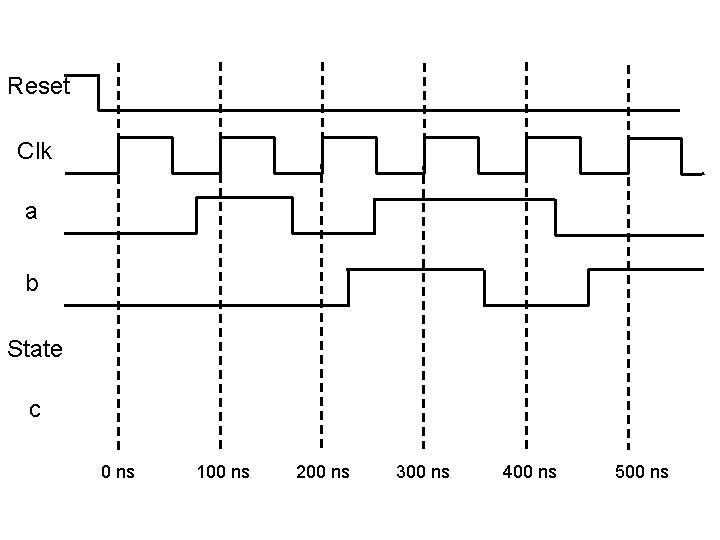

Problem 2 Assuming state diagram given on the next slide, supplement timing waveforms given in the answer sheet with the correct values of signals State and c, in the interval from 0 to 575 ns.

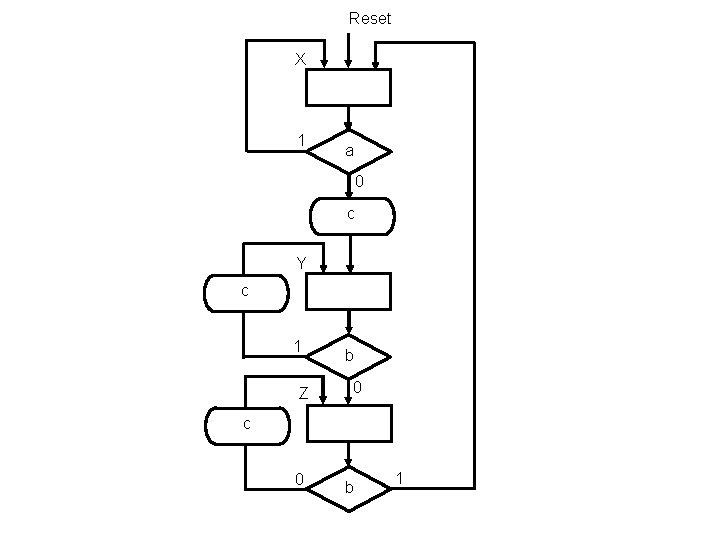

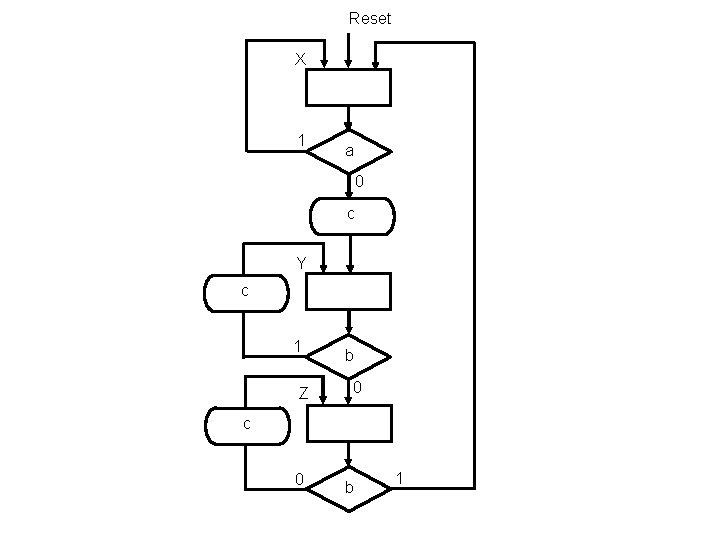

Reset X 1 a 0 c Y c 1 Z b 0 c 0 b 1

Reset Clk a b State c 0 ns 100 ns 200 ns 300 ns 400 ns 500 ns

FSM Coding Style Process(Present State, Inputs) Process(clk, reset) 28

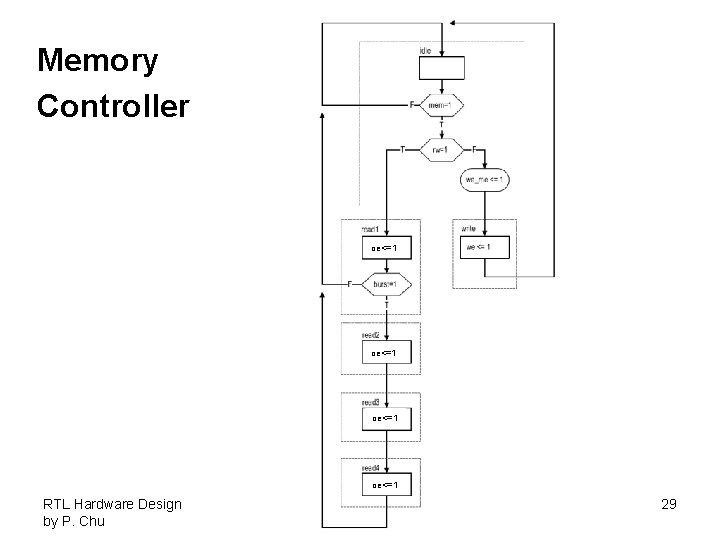

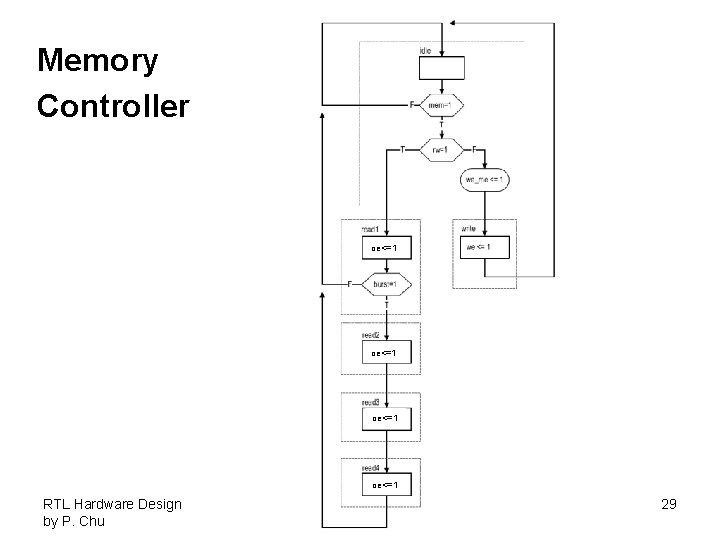

Memory Controller oe<=1 RTL Hardware Design by P. Chu Chapter 10 29

30

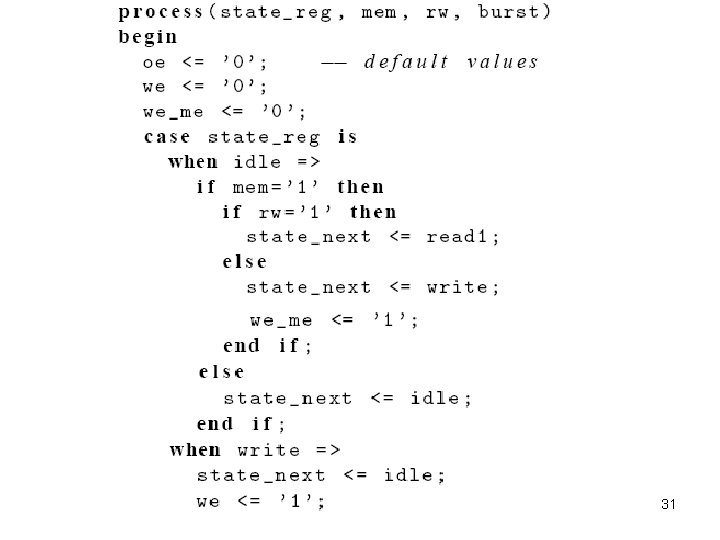

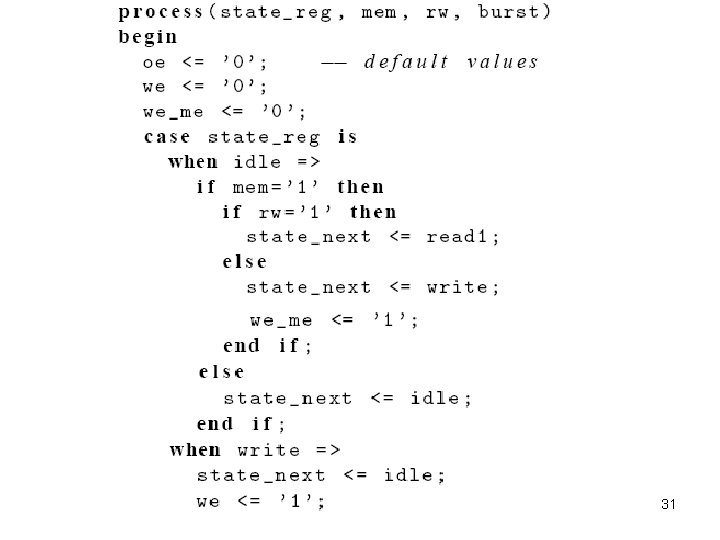

31

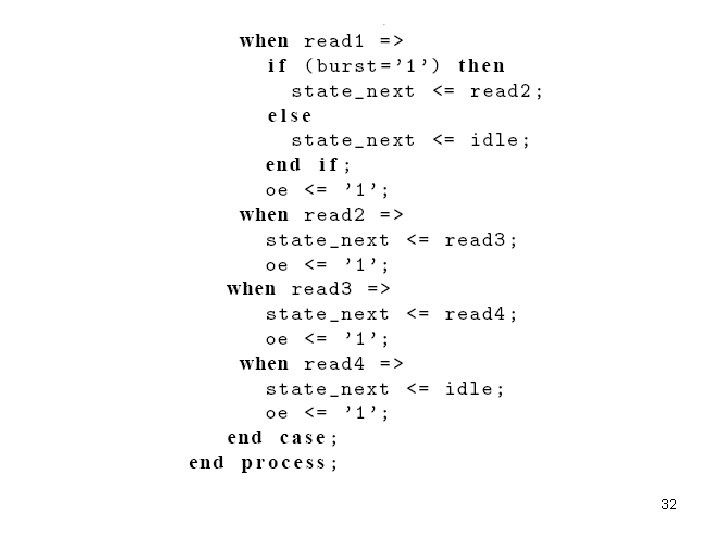

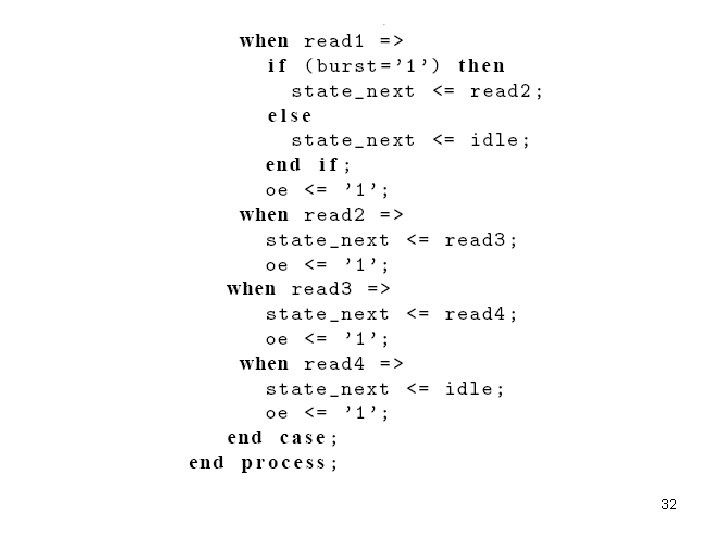

32