Combinational vs Sequential Logic Ungated Latches Gated Latches

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flops Chapter 11 Latches and Flip-Flops SKEE 1223 Digital Electronics Mun’im/Arif/Izam {munim, arif, e-izam}@utm. my FKE, Universiti Teknologi Malaysia February 10, 2017 Flip-Flop Chips Clock IC

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Types of Logic Circuits Combinational logic: Output depends solely on the present input. Has no memory. Sequential logic: Output depends not only on the present input and also on past history of inputs. Has memory. Synchronous sequential logic Use a ‘clock’ signal to regulate operations. Simpler to design Asynchronous sequential logic Does not use a clock. Clock IC

Combinational vs Sequential Logic Ungated Latches Gated Latches Types of Memory Elements Ungated Latches Gated Latches Flip-flops Flip-Flop Chips Clock IC

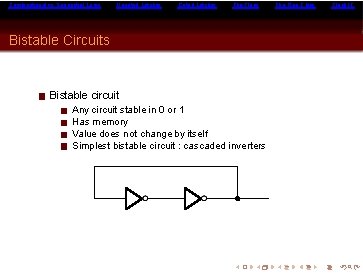

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flops Bistable Circuits Bistable circuit Any circuit stable in 0 or 1 Has memory Value does not change by itself Simplest bistable circuit : cascaded inverters Flip-Flop Chips Clock IC

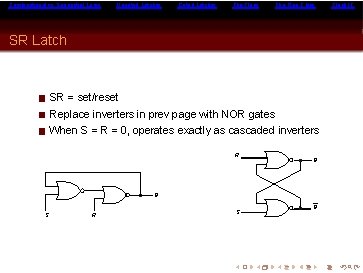

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips SR Latch SR = set/reset Replace inverters in prev page with NOR gates When S = R = 0, operates exactly as cascaded inverters R Q Q S R S Q Clock IC

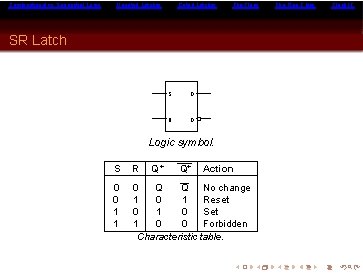

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flops SR Latch S Q R Q Logic symbol. Q+ Q+ S R Action 0 0 1 1 0 Q Q No change 1 0 1 Reset 0 1 0 Set 1 0 0 Forbidden Characteristic table. Flip-Flop Chips Clock IC

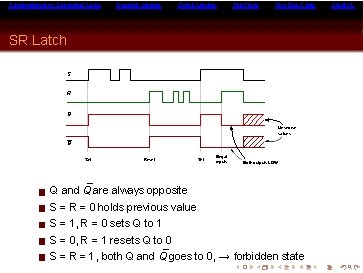

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips SR Latch S R Q Unknown values Q Set Reset Set Illegal inputs Both outputs LOW Q and Q¯are always opposite S = R = 0 holds previous value S = 1, R = 0 sets Q to 1 S = 0, R = 1 resets Q to 0 S = R = 1, both Q and Q¯goes to 0, → forbidden state Clock IC

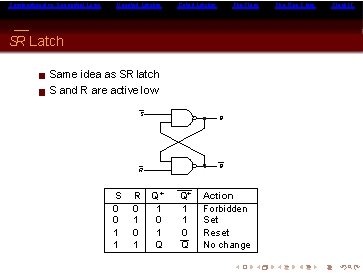

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flops S¯R¯Latch Same idea as SR latch S and R are active low S Q Q R S¯ 0 0 1 1 ¯ R 0 1 Q+ 1 0 1 Q Q+ 1 1 0 Q Action Forbidden Set Reset No change Flip-Flop Chips Clock IC

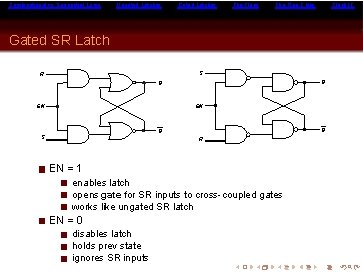

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Clock IC Gated SR Latch S R Q Q EN EN Q Q S R EN = 1 enables latch opens gate for SR inputs to cross-coupled gates works like ungated SR latch EN = 0 disables latch holds prev state ignores SR inputs

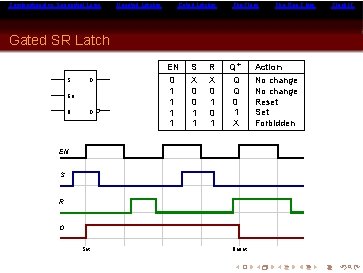

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Gated SR Latch S Q EN R Q EN 0 1 1 S X 0 0 1 1 R X 0 1 Q+ Q Q 0 1 X EN S R Q Set Reset Action No change Reset Set Forbidden Clock IC

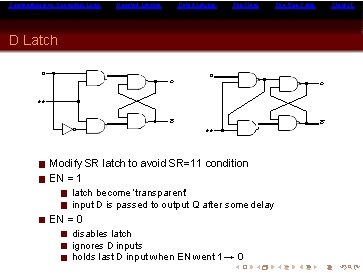

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Clock IC D Latch D D Q Q EN Modify SR latch to avoid SR=11 condition EN = 1 latch become ‘transparent’ input D is passed to output Q after some delay EN = 0 disables latch ignores D inputs holds last D input when EN went 1 → 0

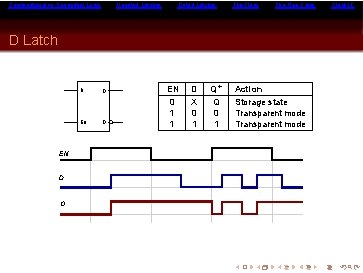

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips D Latch EN D Q EN 0 1 1 D X 0 1 Q+ Q 0 1 Action Storage state Transparent mode Clock IC

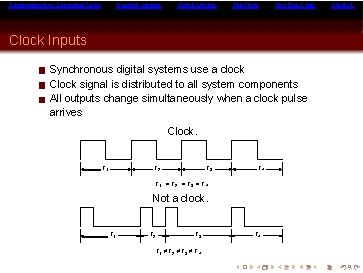

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Clock Inputs Synchronous digital systems use a clock Clock signal is distributed to all system components All outputs change simultaneously when a clock pulse arrives Clock. T 1 T 2 T 3 T 4 T 1 = T 2 = T 3 = T 4 Not a clock. T 1 T 2 T 3 T 1 ≠ T 2 ≠ T 3 ≠ T 4 Clock IC

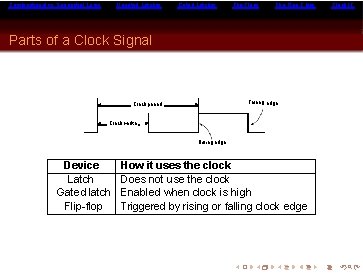

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Parts of a Clock Signal Falling edge Clock period Clock width Rising edge Device Latch Gated latch Flip-flop How it uses the clock Does not use the clock Enabled when clock is high Triggered by rising or falling clock edge Clock IC

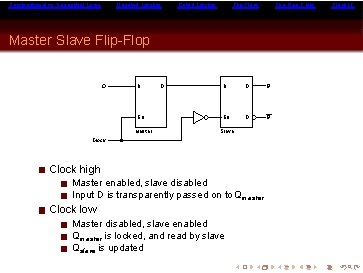

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Master Slave Flip-Flop D D EN Master Q D Q Q EN Q Q Slave Clock high Master enabled, slave disabled Input D is transparently passed on to Qmaster Clock low Master disabled, slave enabled Qmaster is locked, and read by slave Qslave is updated Clock IC

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips D Flip-Flop D Clk 0 1 ↑ ↑ Q Q D X X 0 1 Q+ Q Q 0 1 Set latch Output latch S Clock Q Reset latch Q R D Action No change Reset Set Clock IC

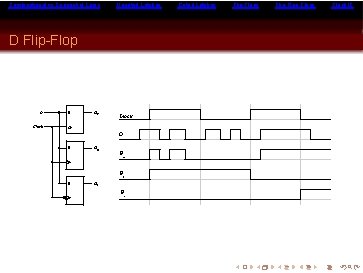

Combinational vs Sequential Logic Ungated Latches D Flip-Flop D Clock D Qa Clock Clk D D Qb Qa Q D b Qc Q c Gated Latches Flip-Flop Chips Clock IC

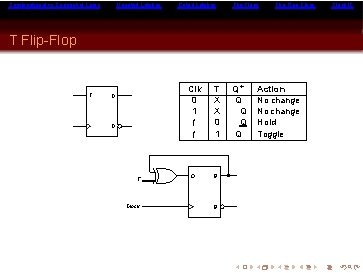

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips T Flip-Flop T Clk 0 1 ↑ ↑ Q Q T Clock D T X X 0 1 Q Q Q+ Q Q Action No change Hold Toggle Clock IC

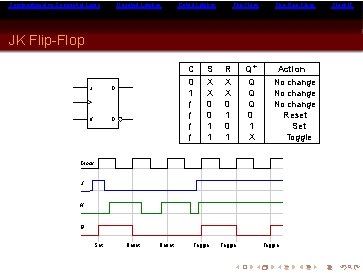

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Q+ Q Q Q 0 1 X Action No change Reset Set Toggle JK Flip-Flop J Q K Q C 0 1 ↑ ↑ S X X 0 0 1 1 R X X 0 1 Clock J K Q Set Reset Toggle Clock IC

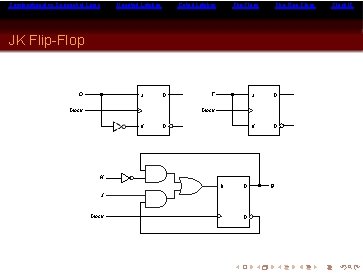

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips JK Flip-Flop D J Q T J Q K Q Clock K Q K D Q J Clock Q Q Clock IC

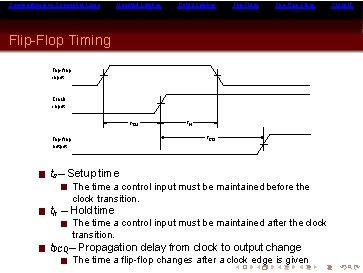

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips Flip-Flop Timing Flip-flop input Clock input t SU t. H t CO Flip-flop output ts – Setup time The time a control input must be maintained before the clock transition. th – Hold time The time a control input must be maintained after the clock transition. t. PCQ – Propagation delay from clock to output change The time a flip-flop changes after a clock edge is given Clock IC

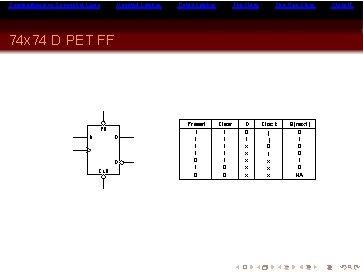

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips 74 x 74 D PET FF PR D Q Q CLR Preset 1 1 0 1 0 Clear 1 1 1 0 0 D 0 1 x x x Clock ↑ ↑ 0 1 x x x Q(next) 0 1 Q Q 1 0 NA Clock IC

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips 74 x 76 Master Slave JK FF PR Q J Q K CLR Preset 1 1 1 0 Clear 1 1 1 0 0 J 0 0 1 1 x x K 0 1 x x Clock ↑ ↑ 0 , 1 x x x Q(next) Q 0 1 ¯ Q Q 1 0 NA Clock IC

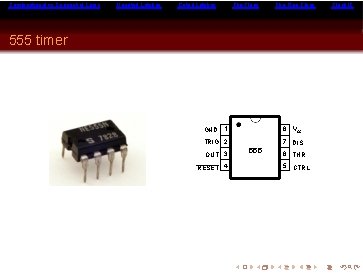

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips 555 timer 1 8 VCC TRIG 2 7 DIS GND OUT 3 RESET 4 555 6 THR 5 CTRL Clock IC

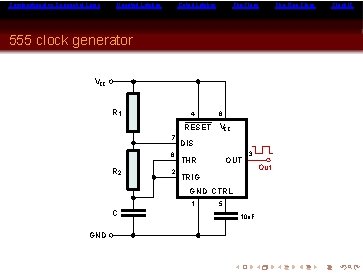

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flops 555 clock generator VCC R 1 4 RESET 7 6 R 2 2 8 VCC DIS OUT THR 3 TRIG GND CTRL 1 C GND 5 10 n. F Out Flip-Flop Chips Clock IC

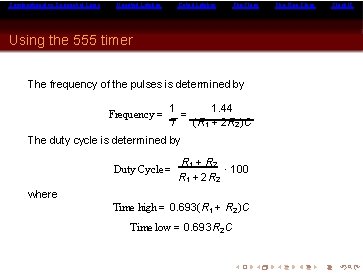

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flops Using the 555 timer The frequency of the pulses is determined by Frequency = 1 1. 44 = T (R 1 + 2 R 2)C The duty cycle is determined by Duty Cycle = R 1 + R 2 · 100 R 1 + 2 R 2 where Time high = 0. 693(R 1 + R 2)C Time low = 0. 693 R 2 C Flip-Flop Chips Clock IC

Combinational vs Sequential Logic Ungated Latches Gated Latches Flip-Flop Chips SKEE 1223 https: //www. openlearning. com/courses/SKEE 1223 x Clock IC

- Slides: 27