Modular sequential logic Use latches flipflops and combinational

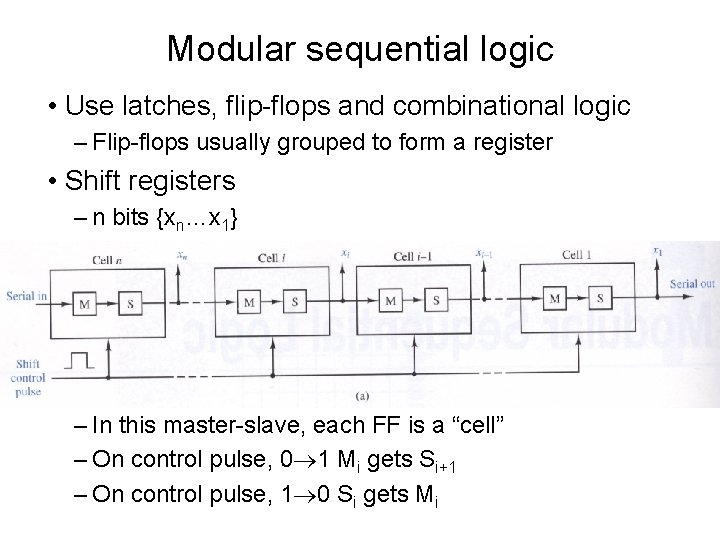

Modular sequential logic • Use latches, flip-flops and combinational logic – Flip-flops usually grouped to form a register • Shift registers – n bits {xn…x 1} – In this master-slave, each FF is a “cell” – On control pulse, 0 1 Mi gets Si+1 – On control pulse, 1 0 Si gets Mi

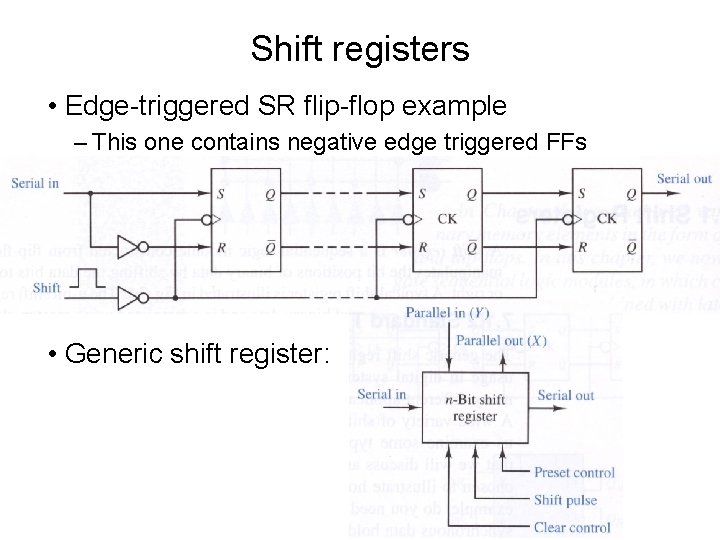

Shift registers • Edge-triggered SR flip-flop example – This one contains negative edge triggered FFs • Generic shift register:

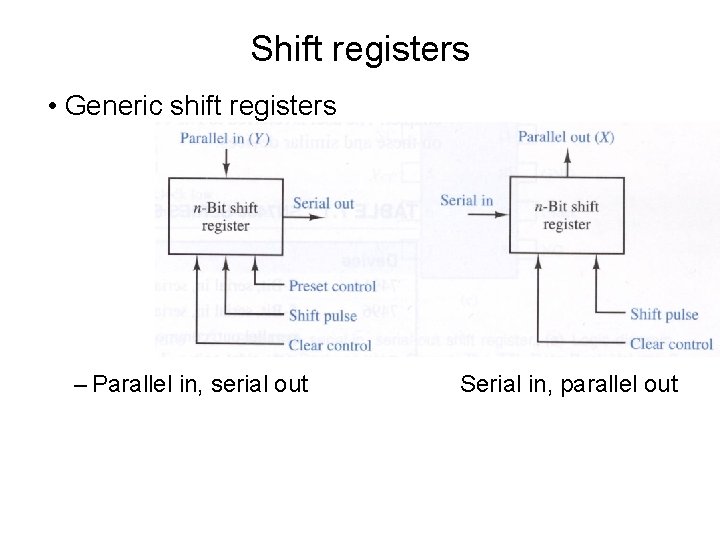

Shift registers • Generic shift registers – Parallel in, serial out Serial in, parallel out

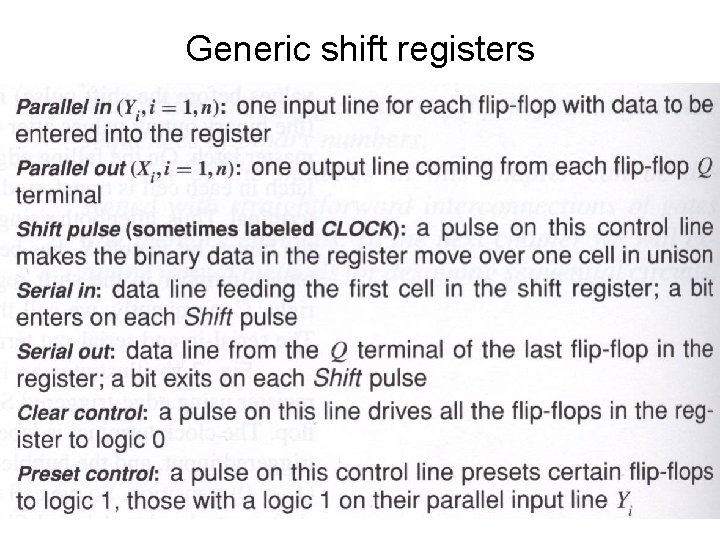

Generic shift registers

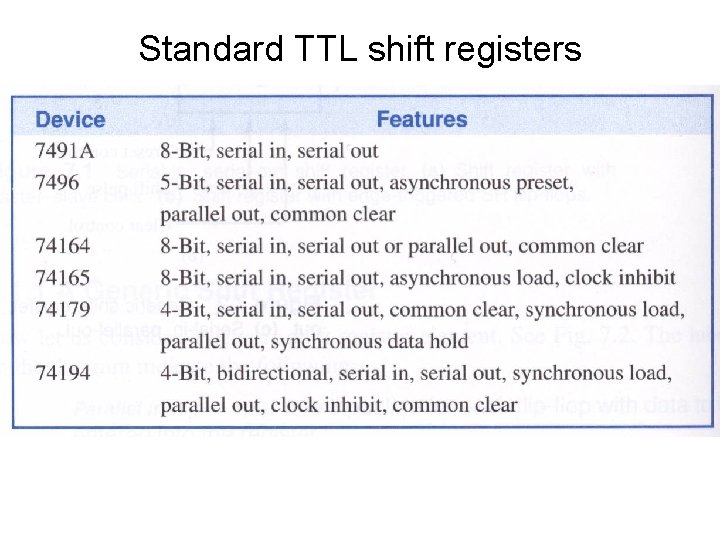

Standard TTL shift registers

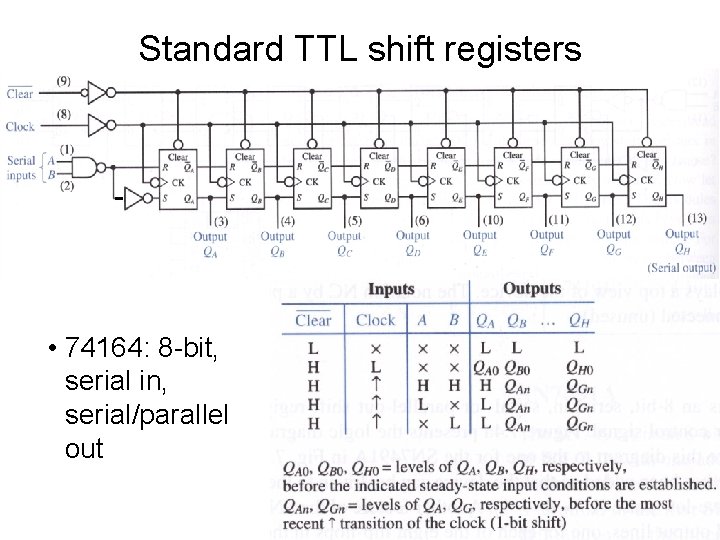

Standard TTL shift registers • 74164: 8 -bit, serial in, serial/parallel out

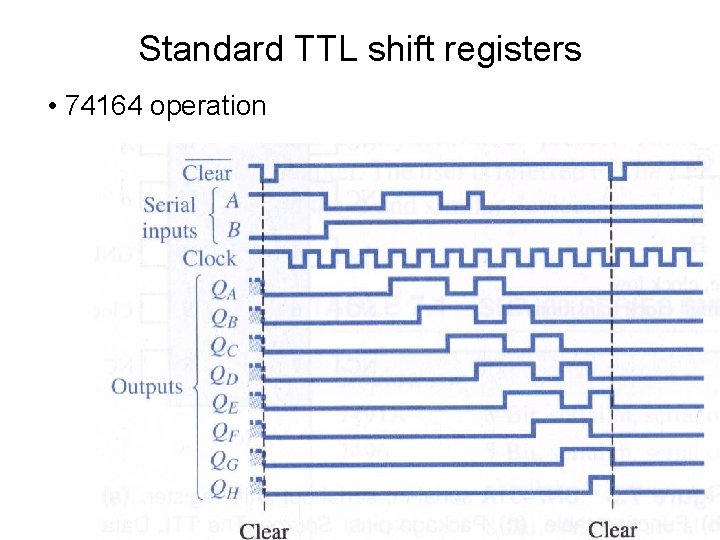

Standard TTL shift registers • 74164 operation

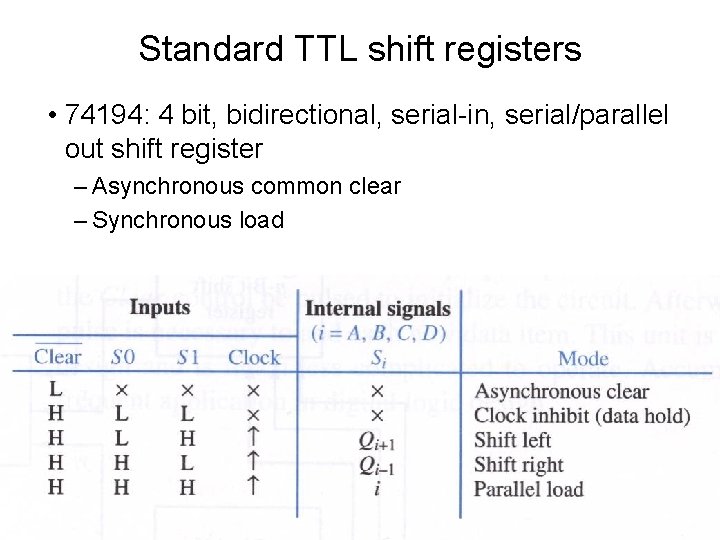

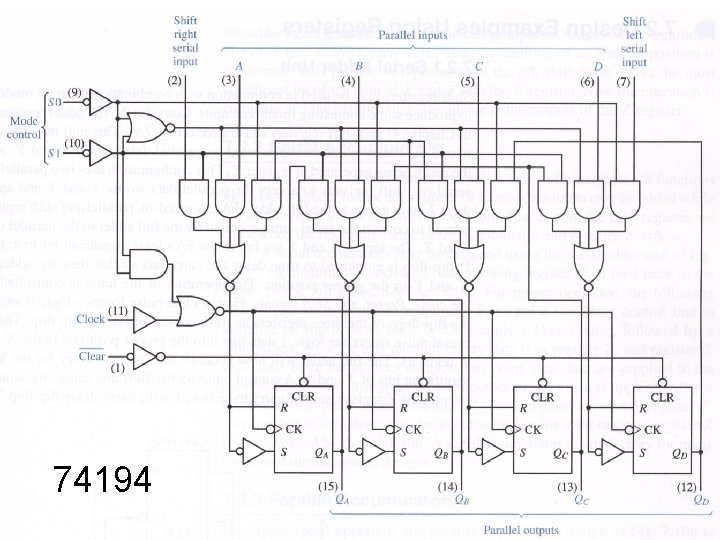

Standard TTL shift registers • 74194: 4 bit, bidirectional, serial-in, serial/parallel out shift register – Asynchronous common clear – Synchronous load

Standard TTL shift registers – 74194: 4 bit, bidirection al, serialin, serial/para llel out shift register 74194

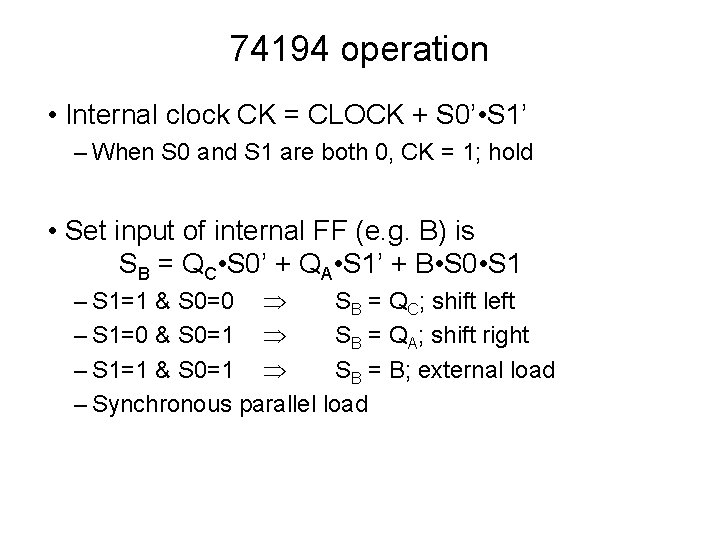

74194 operation • Internal clock CK = CLOCK + S 0’ • S 1’ – When S 0 and S 1 are both 0, CK = 1; hold • Set input of internal FF (e. g. B) is SB = QC • S 0’ + QA • S 1’ + B • S 0 • S 1 – S 1=1 & S 0=0 SB = QC; shift left – S 1=0 & S 0=1 SB = QA; shift right – S 1=1 & S 0=1 SB = B; external load – Synchronous parallel load

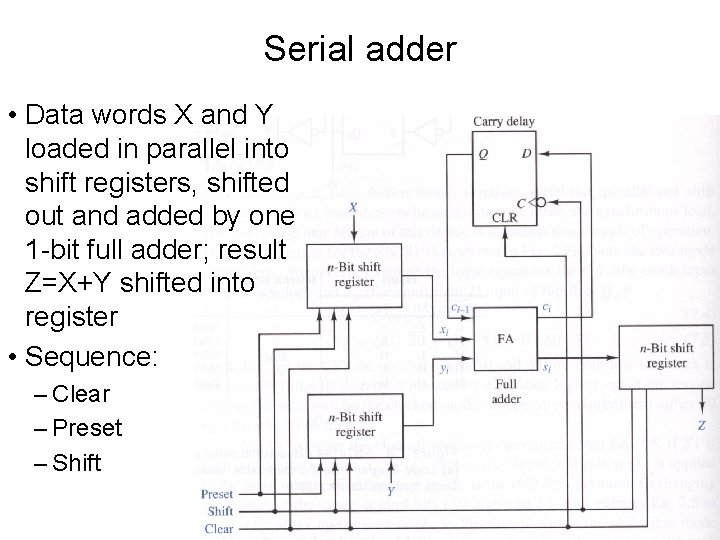

Serial adder • Data words X and Y loaded in parallel into shift registers, shifted out and added by one 1 -bit full adder; result Z=X+Y shifted into register • Sequence: – Clear – Preset – Shift

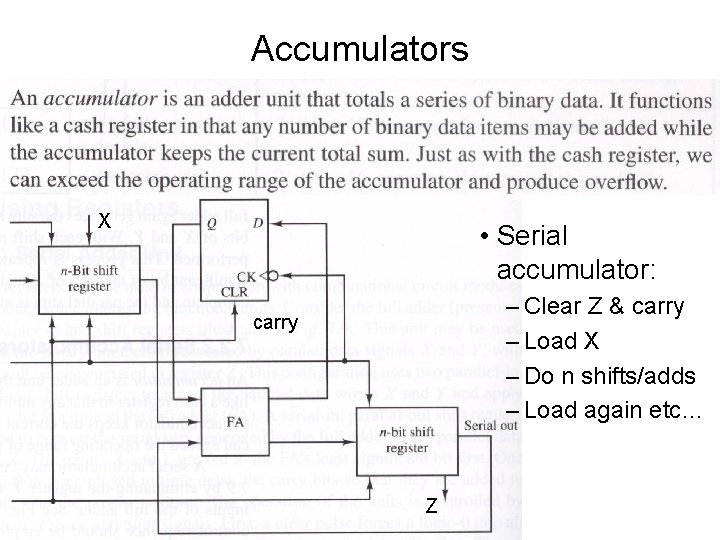

Accumulators X • Serial accumulator: – Clear Z & carry – Load X – Do n shifts/adds – Load again etc… carry Z

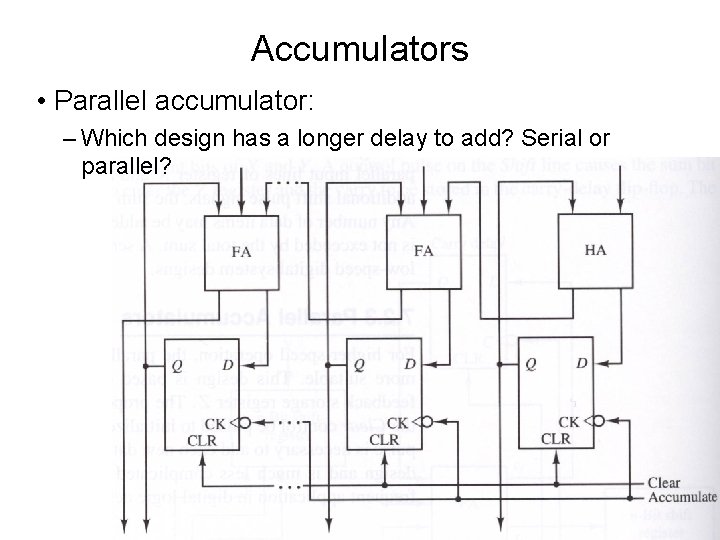

Accumulators • Parallel accumulator: – Which design has a longer delay to add? Serial or parallel?

- Slides: 13