Digital System Design Introduction to Verilog HDL Maziar

![Module Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 Module Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-17.jpg)

![Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-21.jpg)

![Vectors (cont’d) • Bit-select and part-select allowed: bus. A[7] // selects bit #7 of Vectors (cont’d) • Bit-select and part-select allowed: bus. A[7] // selects bit #7 of](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-47.jpg)

![Vectors( cont’d) Variable Vector Part Select reg [255: 0] data 1; //Little endian notation Vectors( cont’d) Variable Vector Part Select reg [255: 0] data 1; //Little endian notation](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-48.jpg)

![Arrays (cont’d) • Examples (cont’d) count[5] = 0; // Reset 5 th element of Arrays (cont’d) • Examples (cont’d) count[5] = 0; // Reset 5 th element of](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-50.jpg)

- Slides: 53

Digital System Design Introduction to Verilog® HDL Maziar Goudarzi

Today program • Hello World! • Hierarchical Modeling Concepts 2010 DSD 2

Verilog® HDL Hello World!

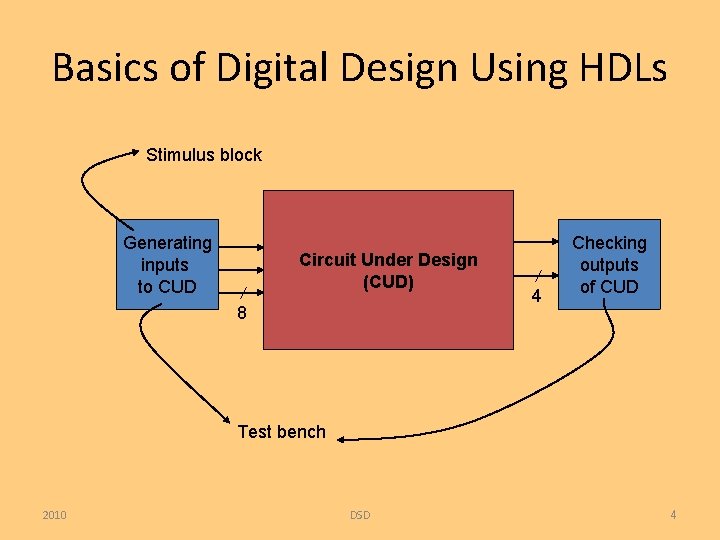

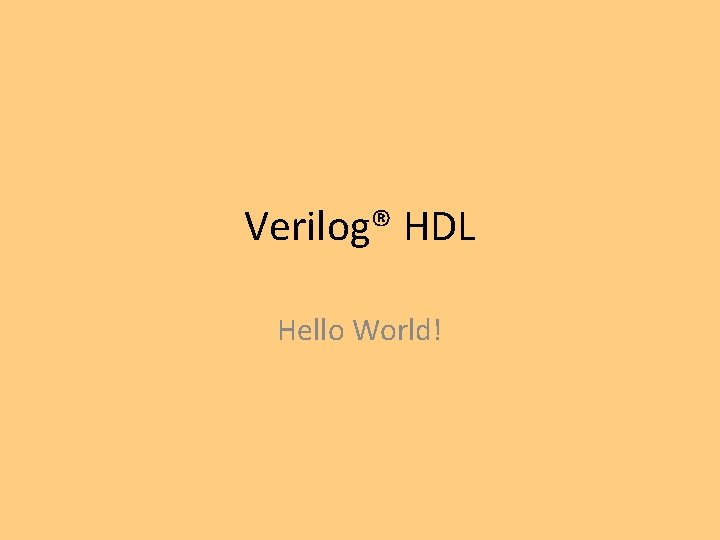

Basics of Digital Design Using HDLs Stimulus block Generating inputs to CUD Circuit Under Design (CUD) 8 4 Checking outputs of CUD Test bench 2010 DSD 4

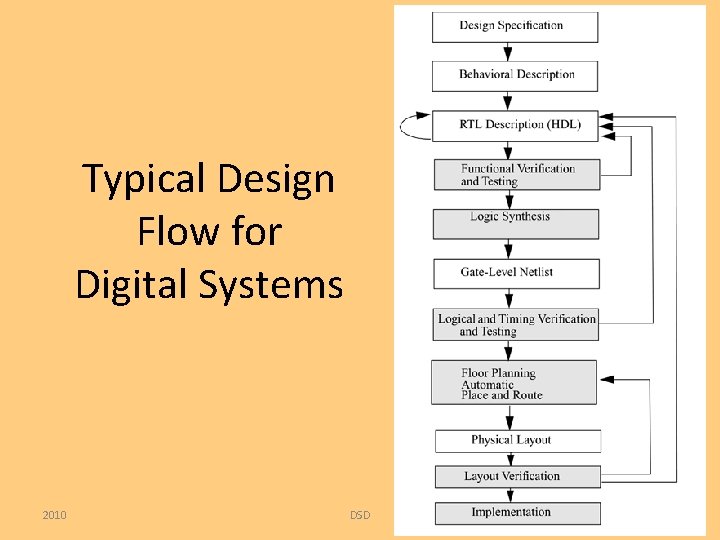

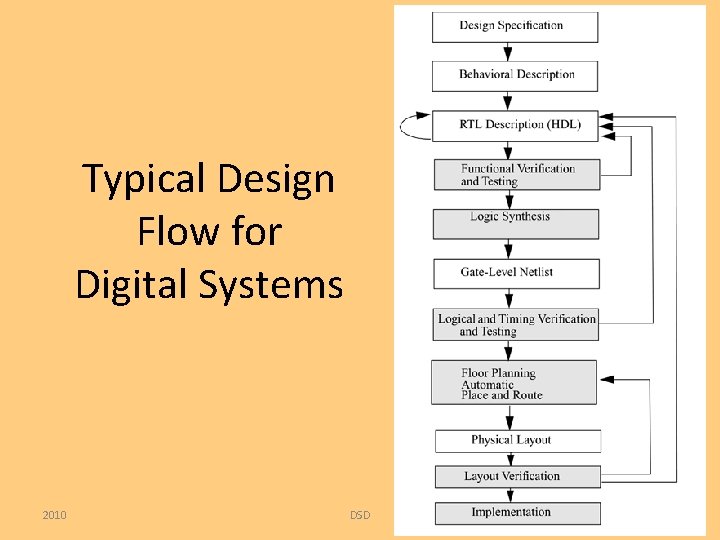

Typical Design Flow for Digital Systems 2010 DSD 5

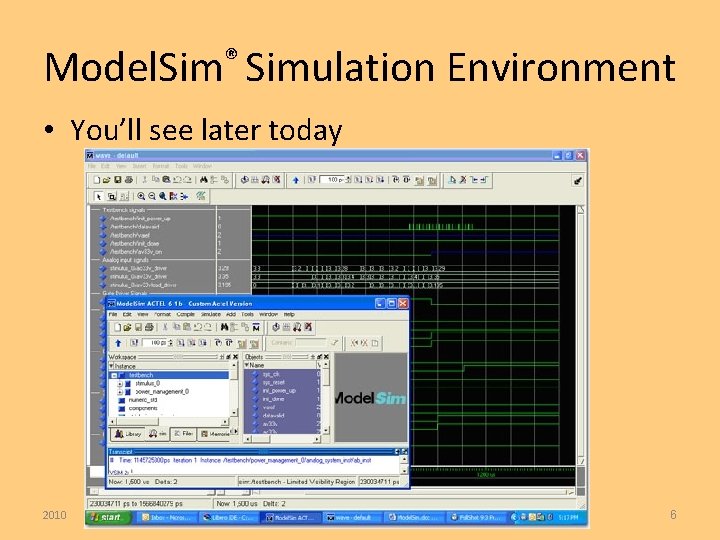

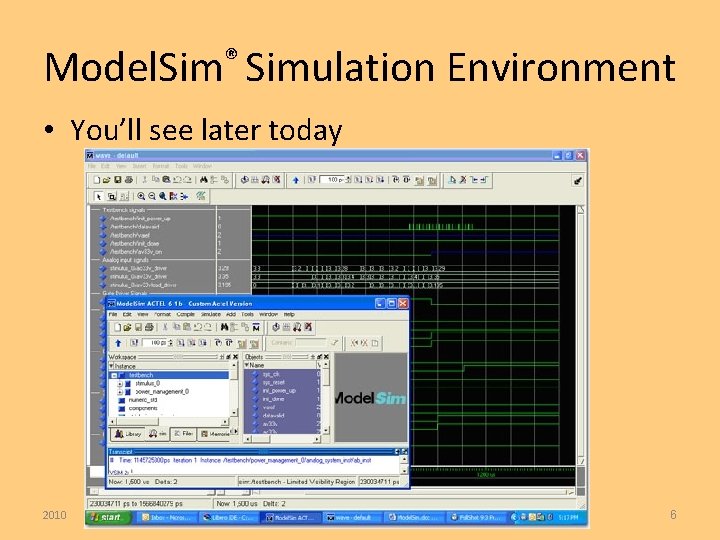

Model. Sim® Simulation Environment • You’ll see later today 2010 DSD 6

Verilog Basic Building Block: Module module not_gate(in, out); // module name+ports // comments: declaring port type input in; output out; // Defining circuit functionality assign out = ~in; endmodule 2010 DSD 7

useless Verilog Example module useless; initial $display(“Hello World!”); endmodule • Note the message-display statement – Compare to printf() in C 2010 DSD 8

Verilog® HDL Hierarchical Modeling Concepts

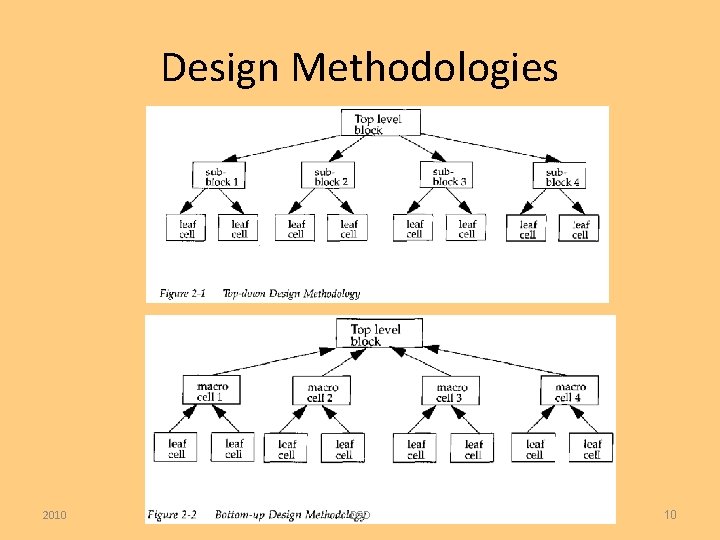

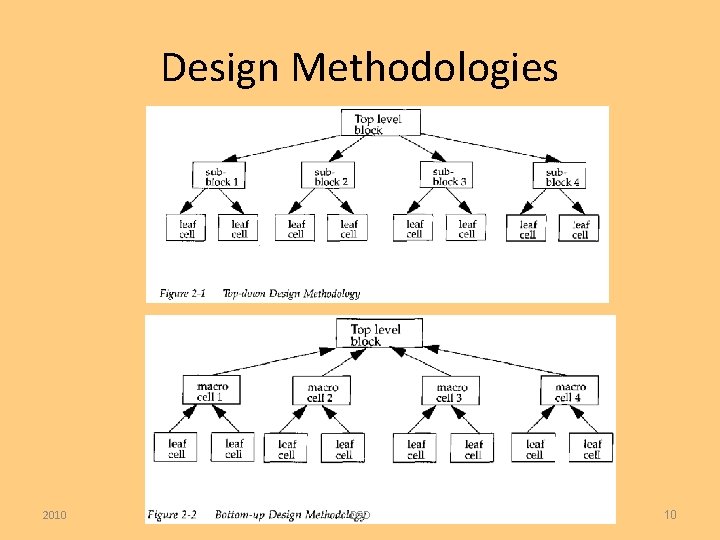

Design Methodologies 2010 DSD 10

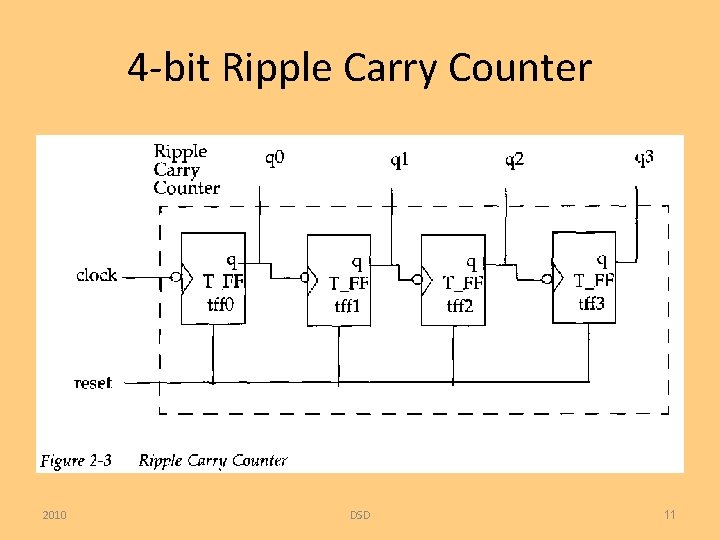

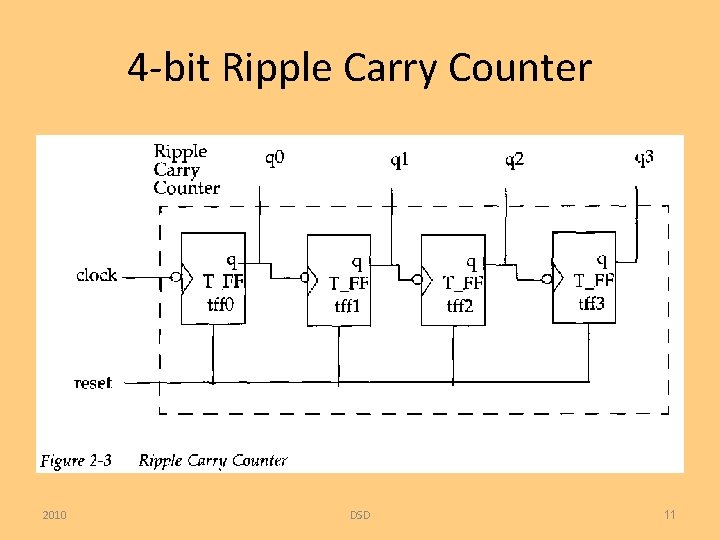

4 -bit Ripple Carry Counter 2010 DSD 11

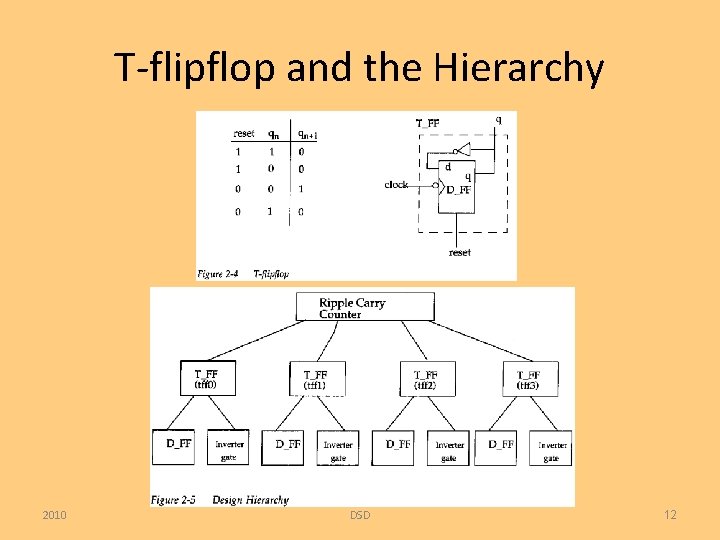

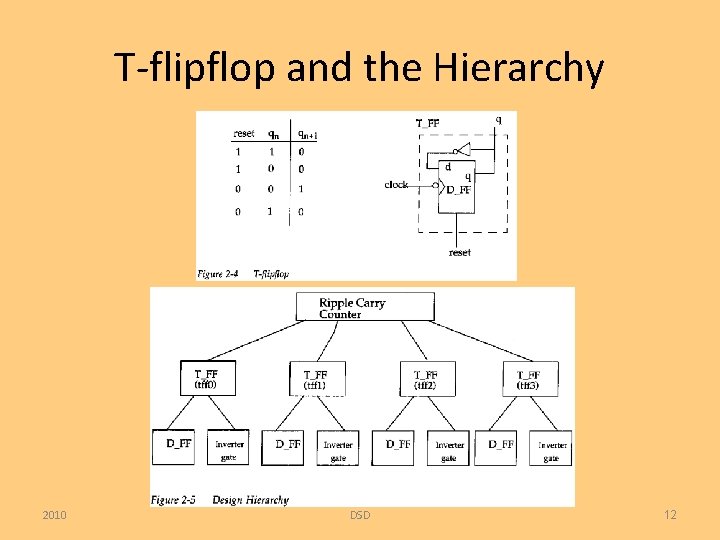

T-flipflop and the Hierarchy 2010 DSD 12

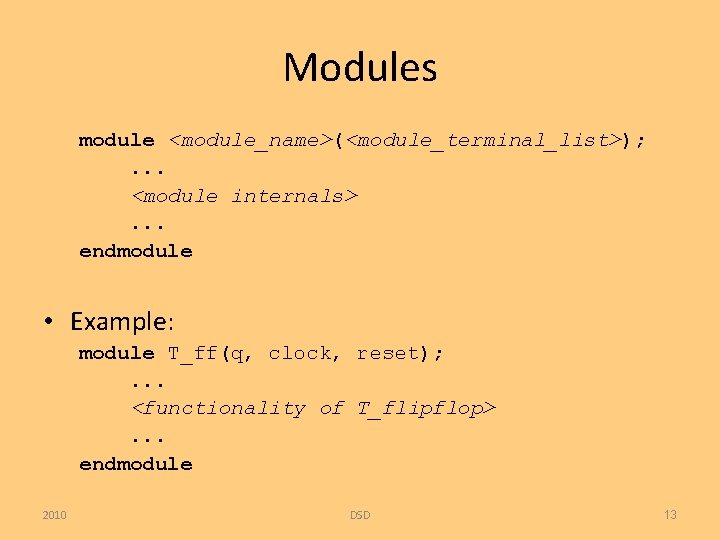

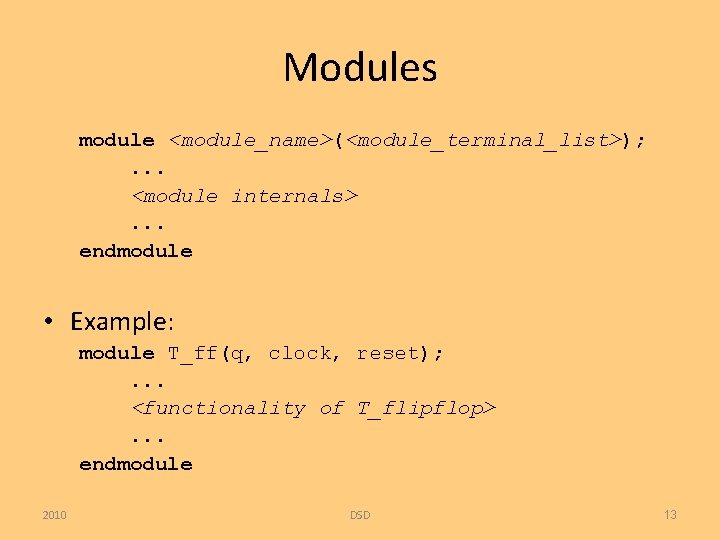

Modules module <module_name>(<module_terminal_list>); . . . <module internals>. . . endmodule • Example: module T_ff(q, clock, reset); . . . <functionality of T_flipflop>. . . endmodule 2010 DSD 13

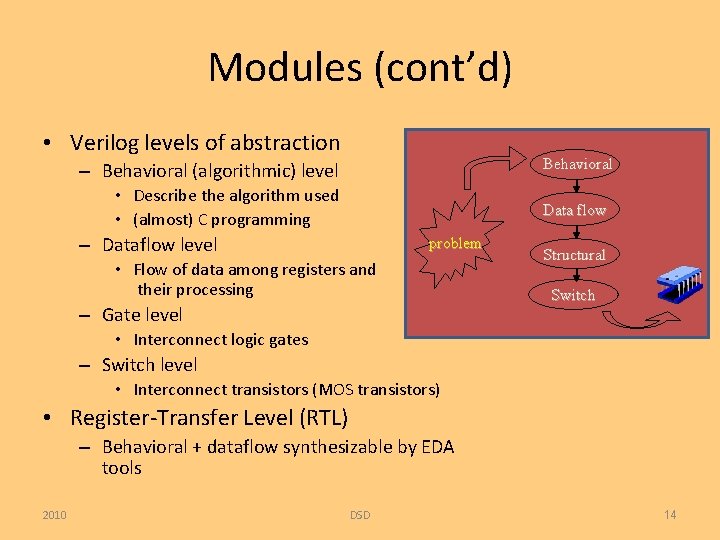

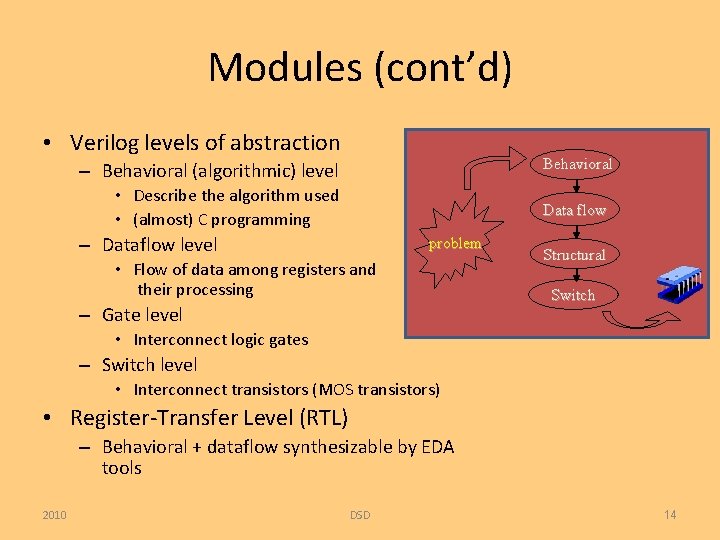

Modules (cont’d) • Verilog levels of abstraction Behavioral – Behavioral (algorithmic) level • Describe the algorithm used • (almost) C programming Data flow – Dataflow level problem • Flow of data among registers and their processing – Gate level Structural Switch • Interconnect logic gates – Switch level • Interconnect transistors (MOS transistors) • Register-Transfer Level (RTL) – Behavioral + dataflow synthesizable by EDA tools 2010 DSD 14

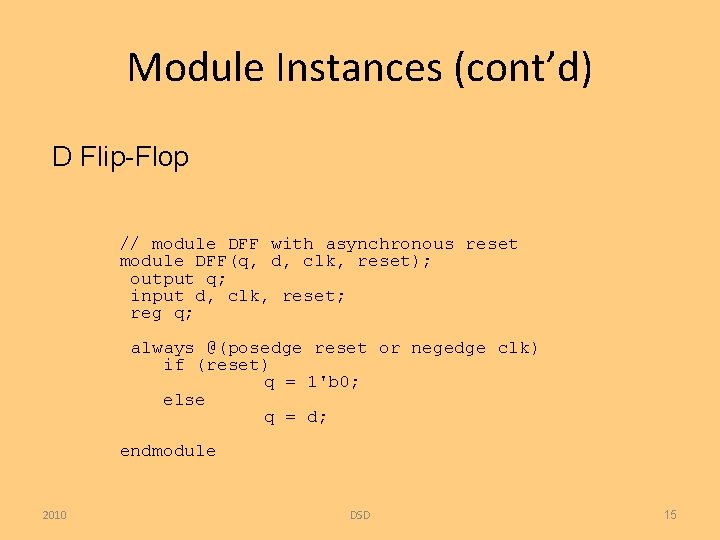

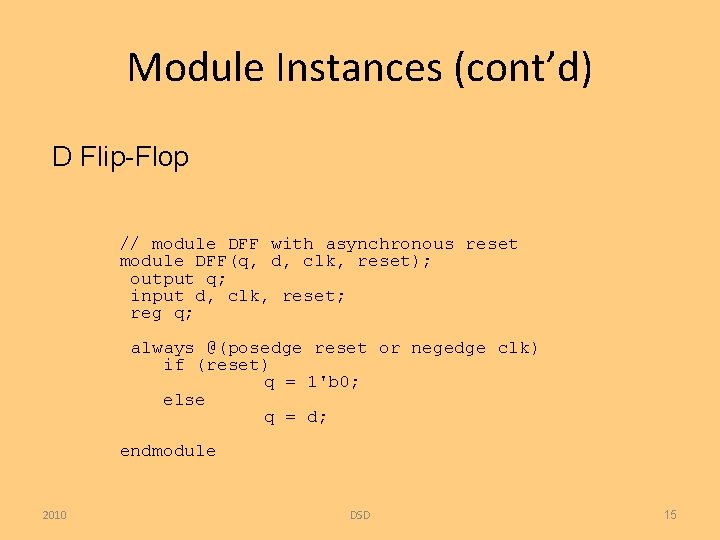

Module Instances (cont’d) D Flip-Flop // module DFF with asynchronous reset module DFF(q, d, clk, reset); output q; input d, clk, reset; reg q; always @(posedge reset or negedge clk) if (reset) q = 1'b 0; else q = d; endmodule 2010 DSD 15

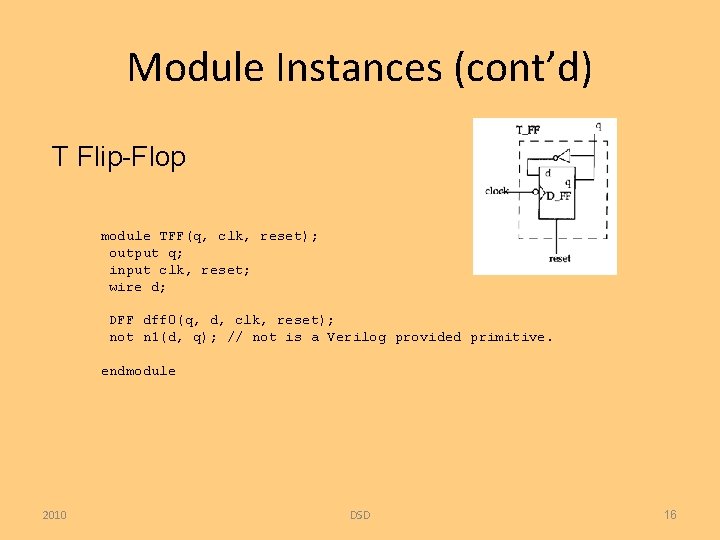

Module Instances (cont’d) T Flip-Flop module TFF(q, clk, reset); output q; input clk, reset; wire d; DFF dff 0(q, d, clk, reset); not n 1(d, q); // not is a Verilog provided primitive. endmodule 2010 DSD 16

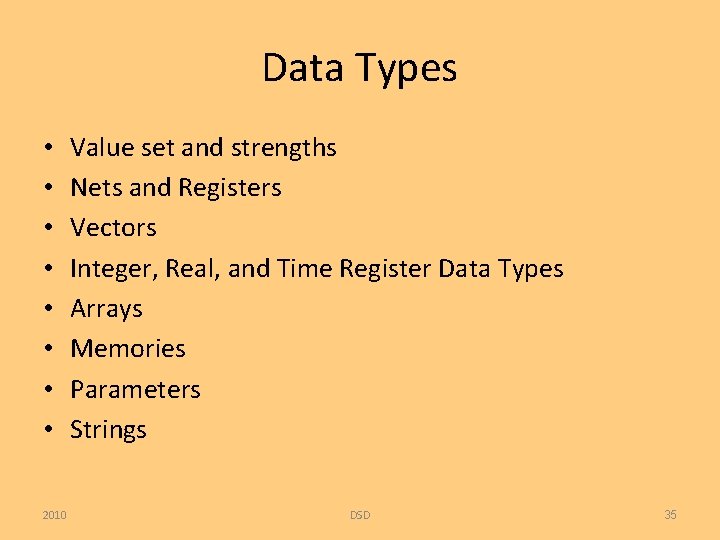

![Module Instances module ripplecarrycounterq clk reset output 3 0 q input clk reset 4 Module Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-17.jpg)

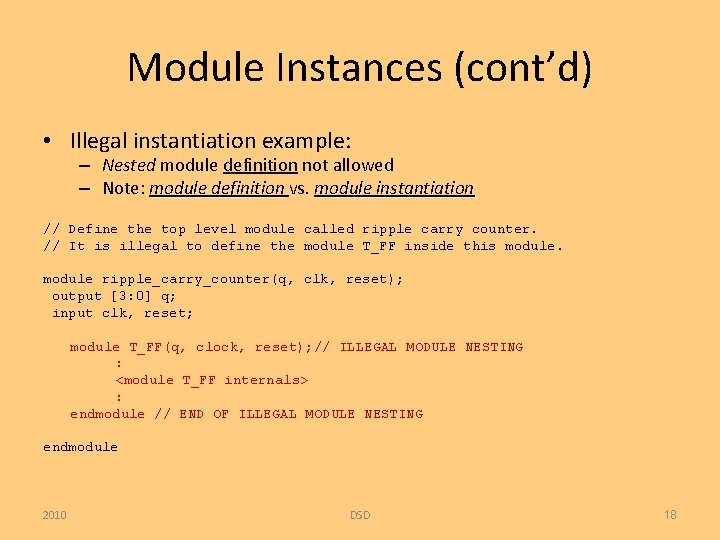

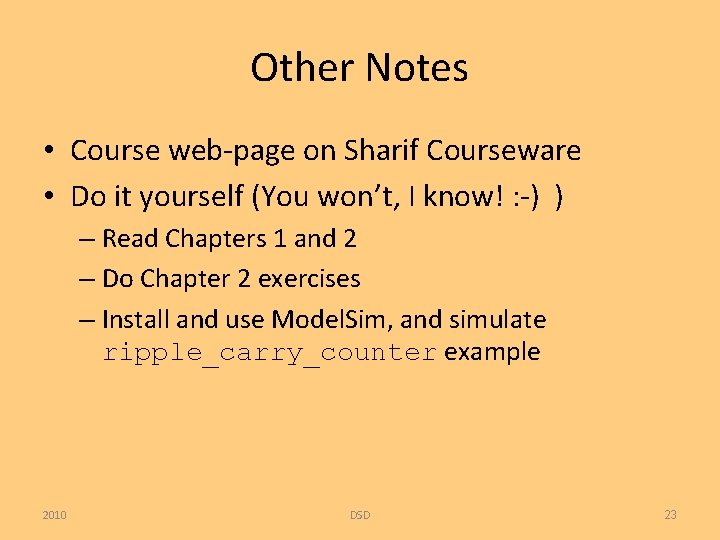

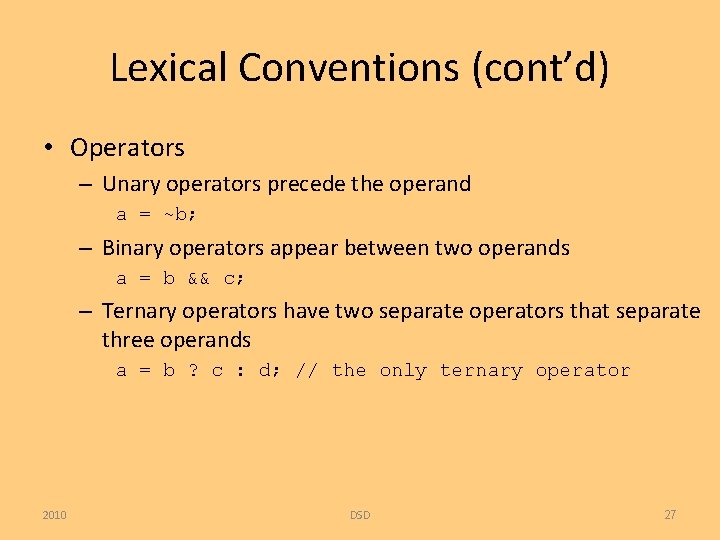

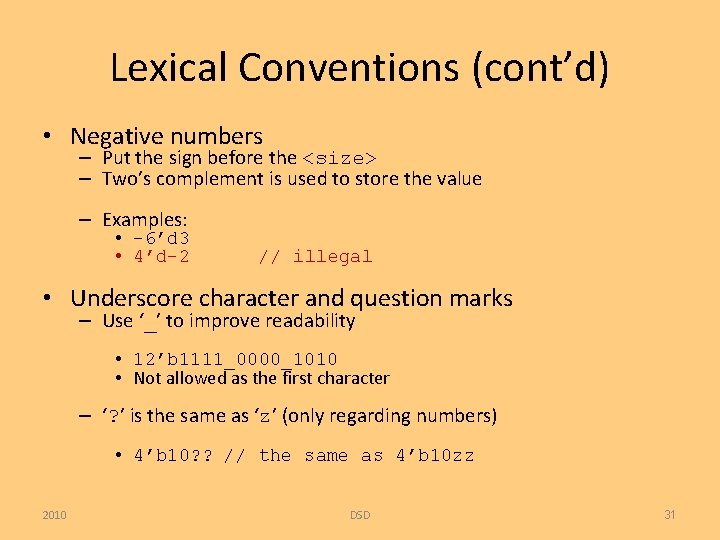

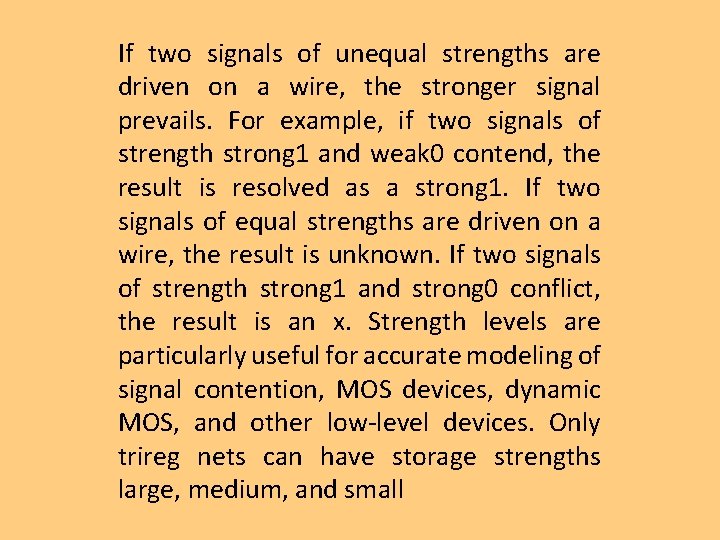

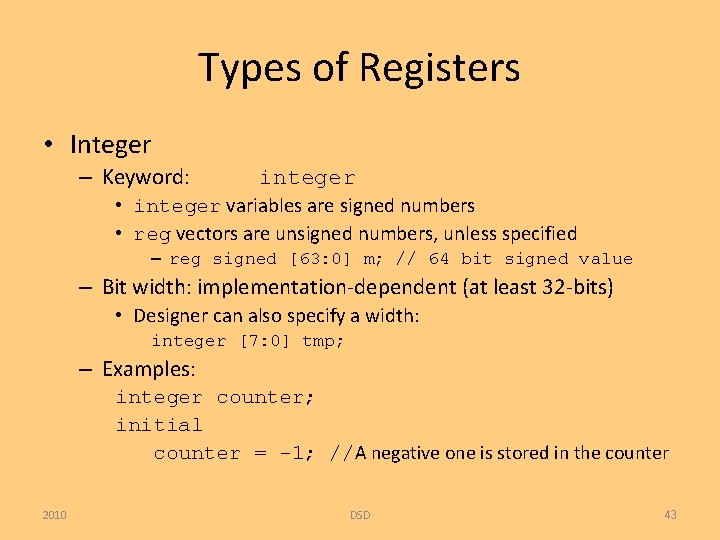

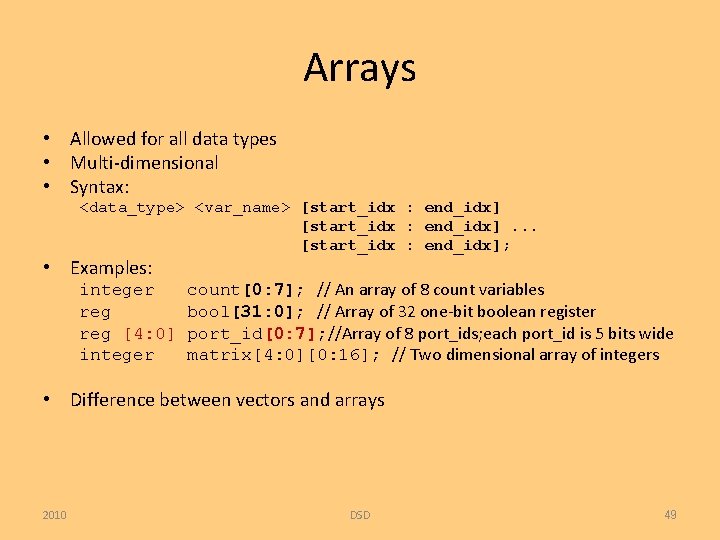

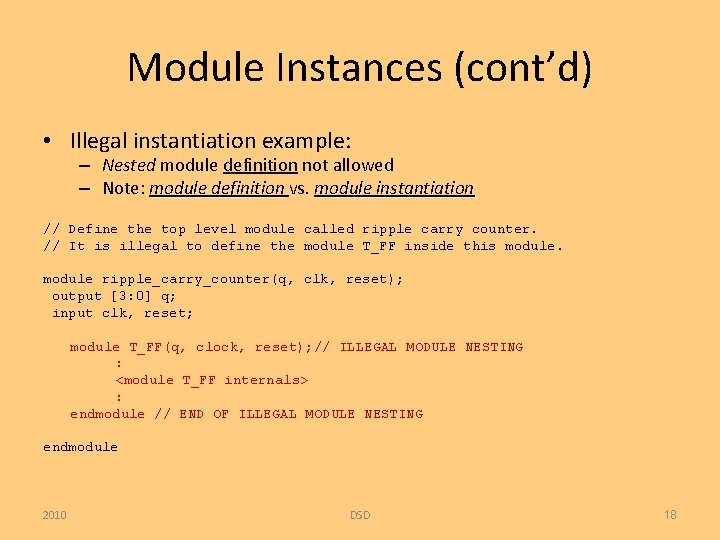

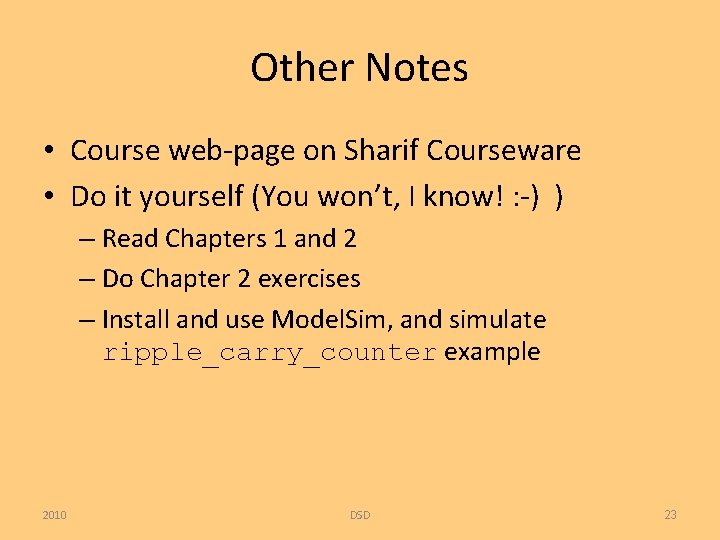

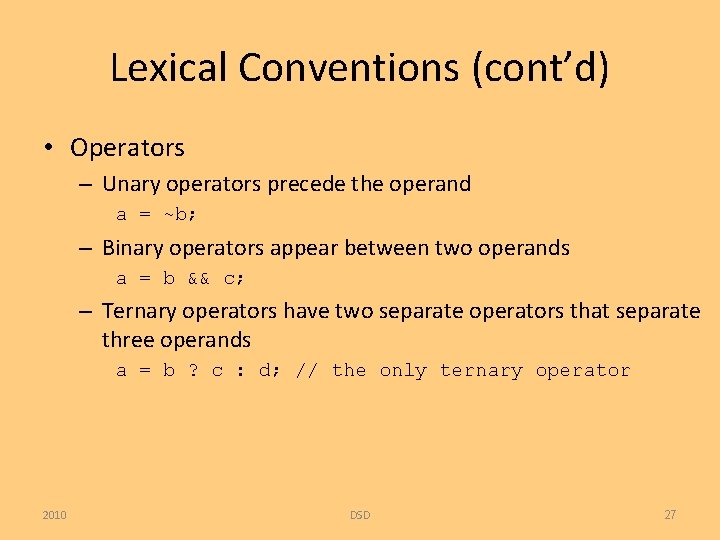

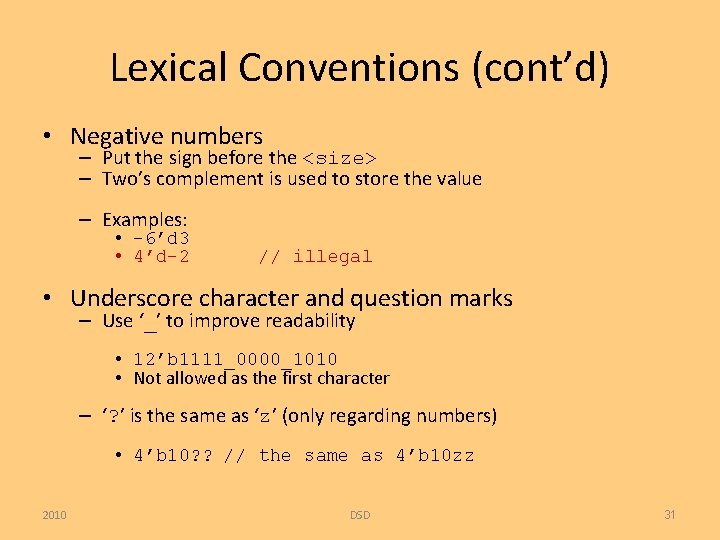

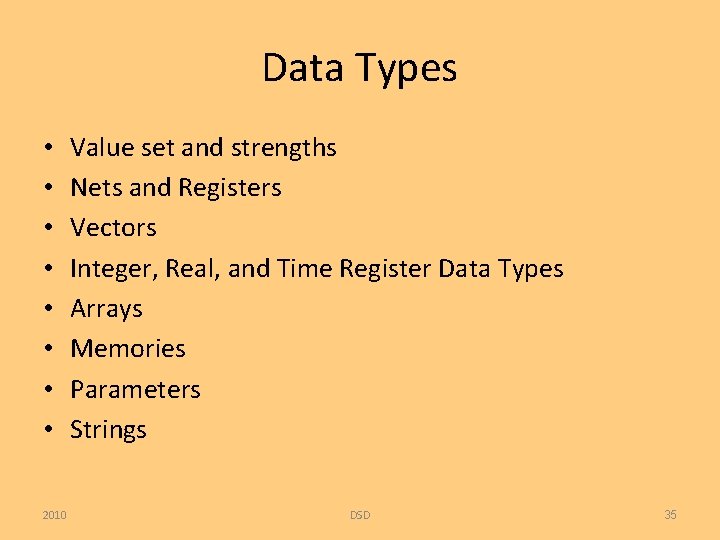

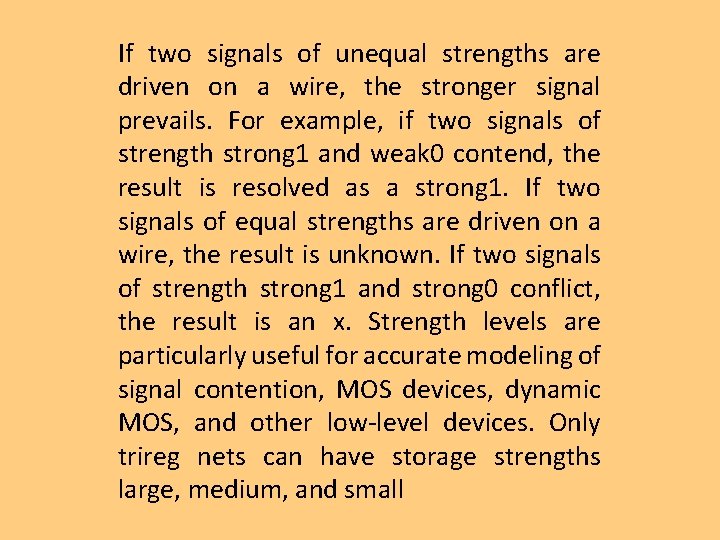

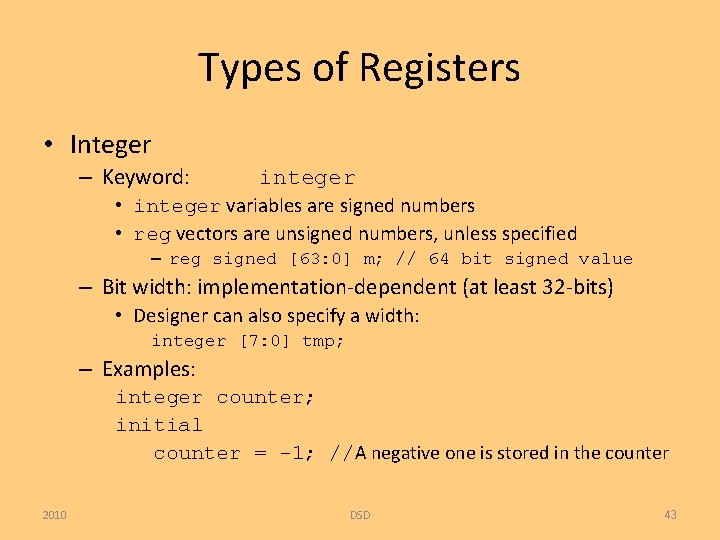

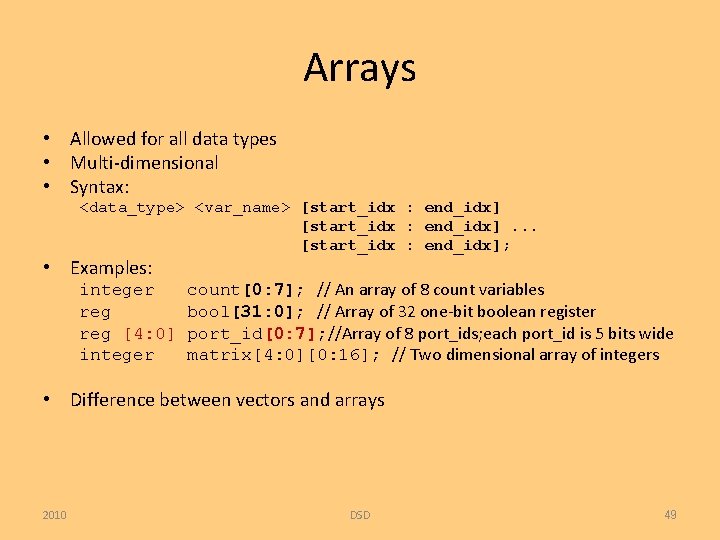

Module Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 TFF TFF instances of the module TFF are created. tff 0(q[0], clk, reset); tff 1(q[1], q[0], reset); tff 2(q[2], q[1], reset); tff 3(q[3], q[2], reset); endmodule 2010 DSD 17

Module Instances (cont’d) • Illegal instantiation example: – Nested module definition not allowed – Note: module definition vs. module instantiation // Define the top level module called ripple carry counter. // It is illegal to define the module T_FF inside this module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; module T_FF(q, clock, reset); // ILLEGAL MODULE NESTING : <module T_FF internals> : endmodule // END OF ILLEGAL MODULE NESTING endmodule 2010 DSD 18

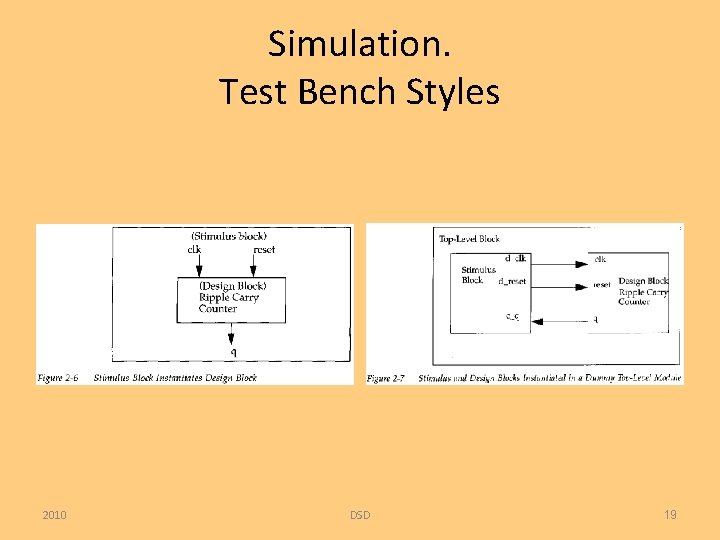

Simulation. Test Bench Styles 2010 DSD 19

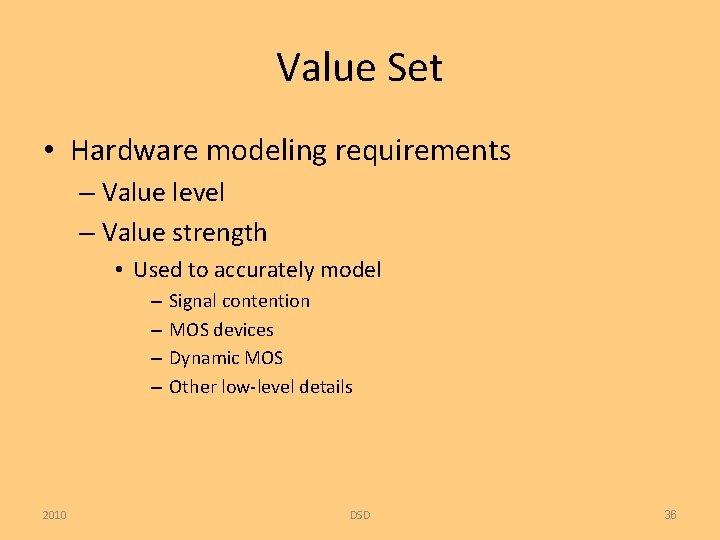

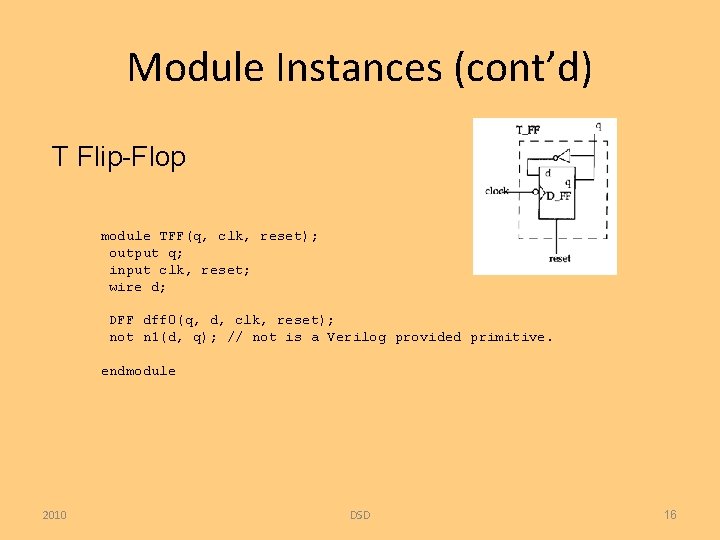

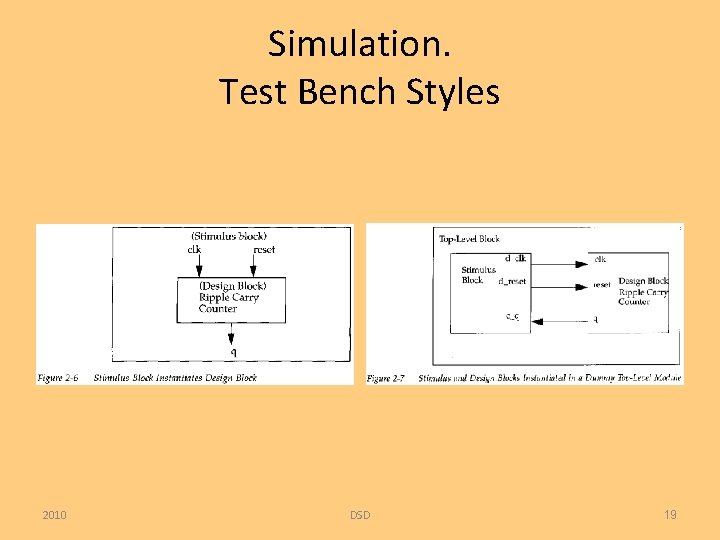

Example • Design block – ripple_carry_counter, T_FF, and D_FF modules • Stimulus block 2010 DSD 20

![Example contd module stimulus reg clk reg reset wire3 0 q instantiate the Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-21.jpg)

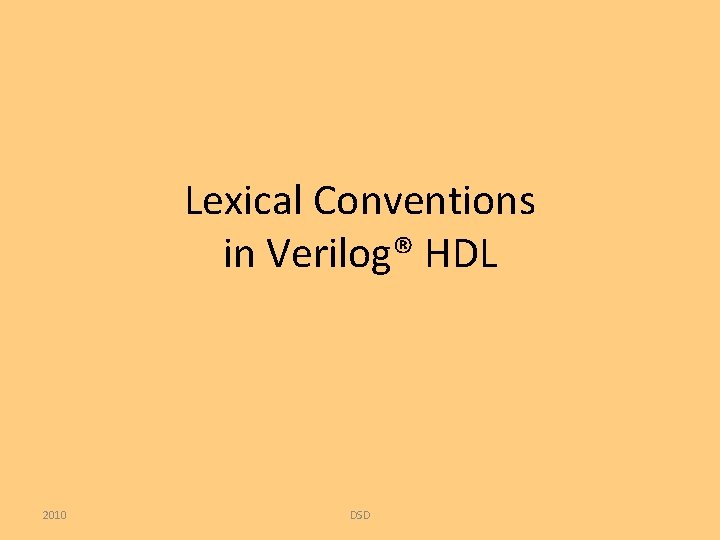

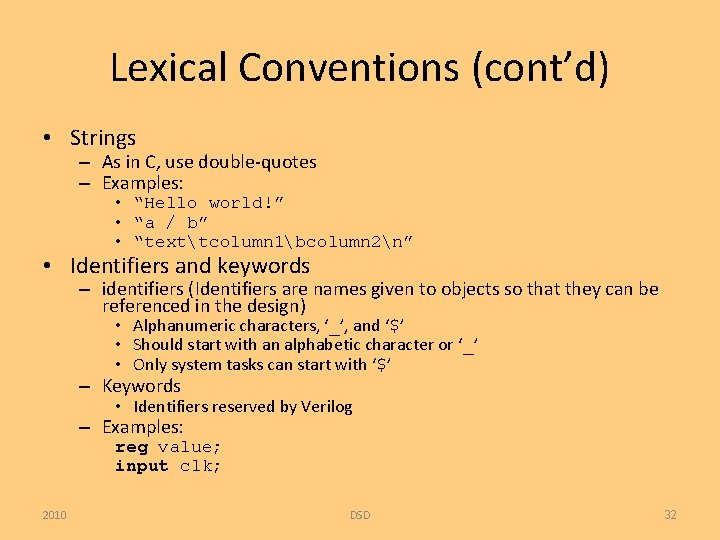

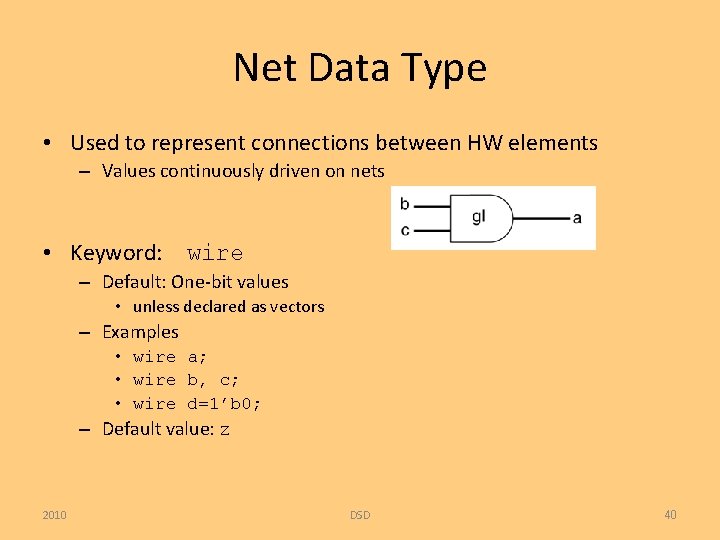

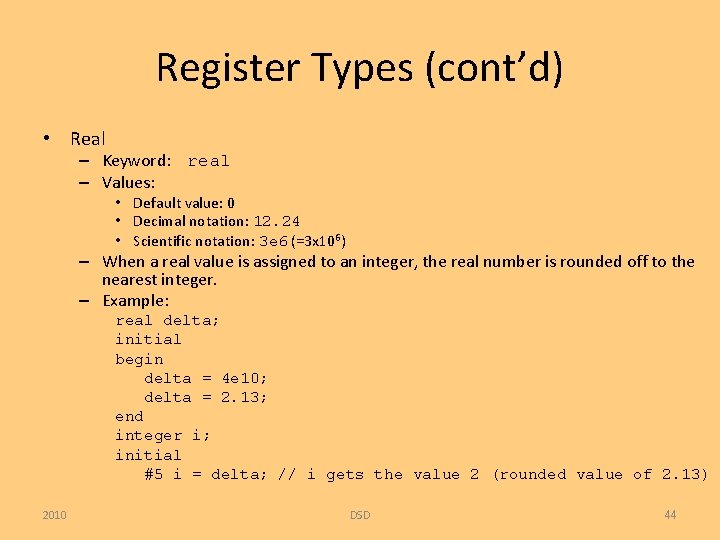

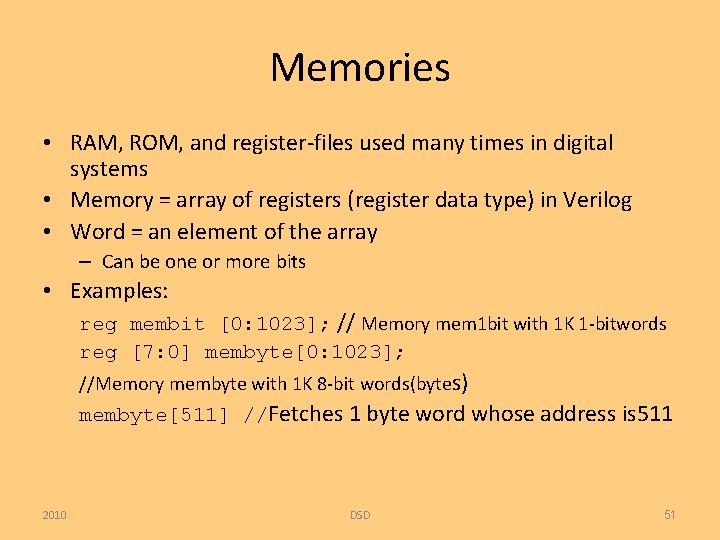

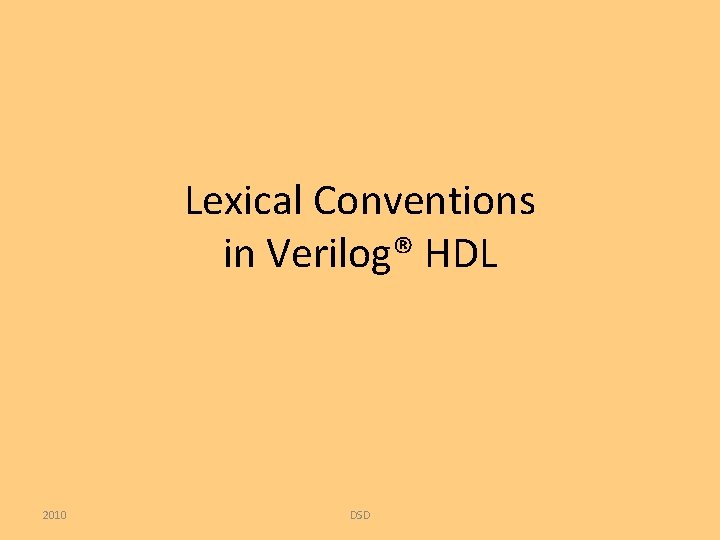

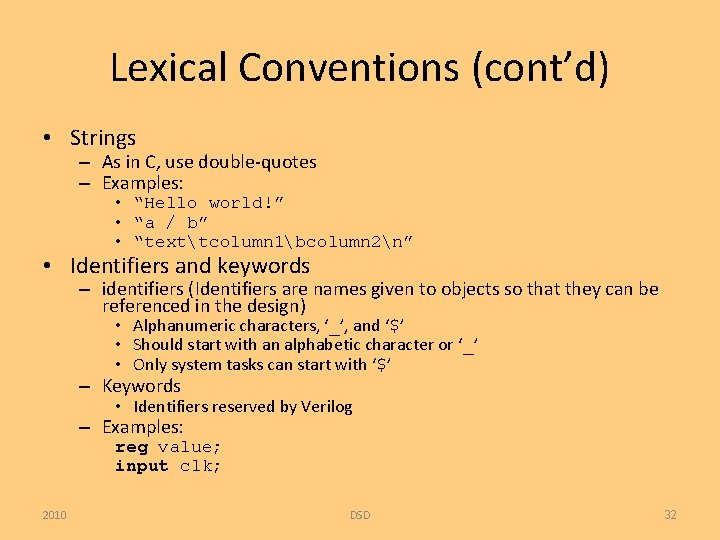

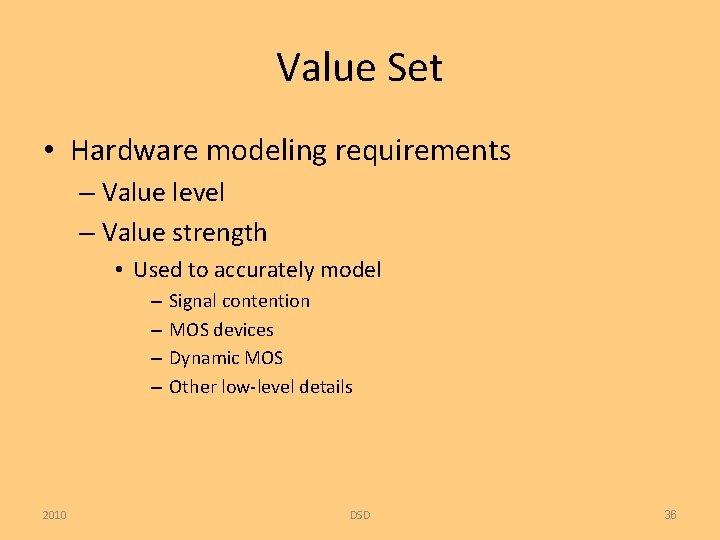

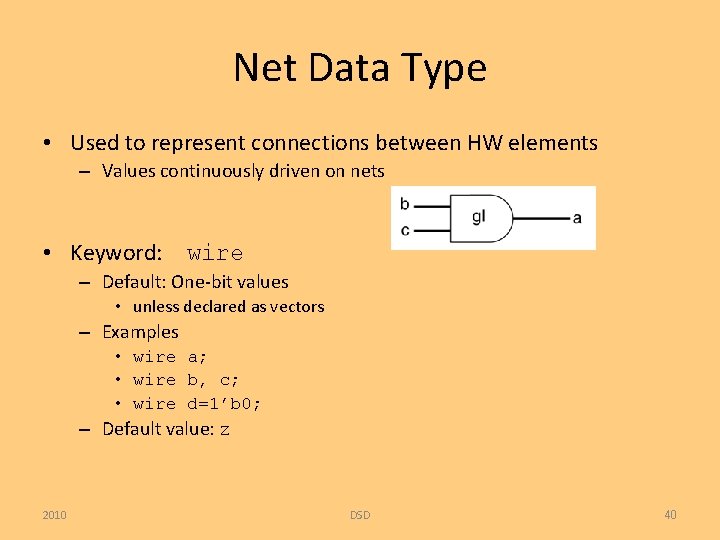

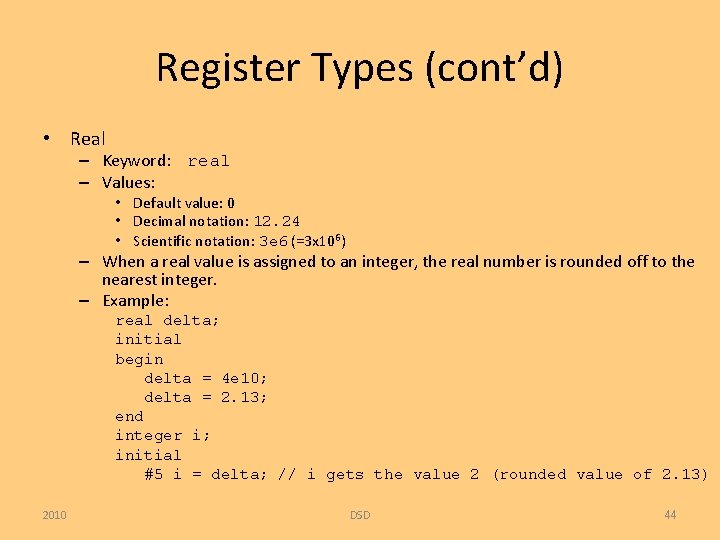

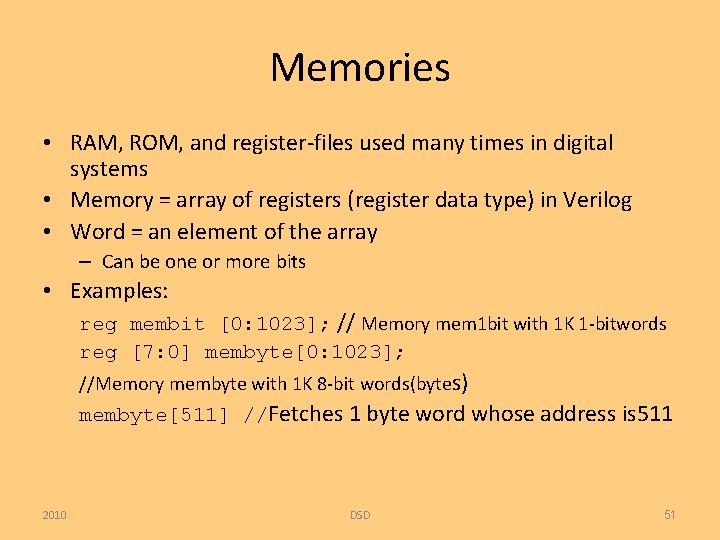

Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the design block ripple_carry_counter r 1(q, clk, reset); // Control the clk signal that drives the design block. initial clk = 1'b 0; always #5 clk = ~clk; // Control the reset signal that drives the design block initial begin reset = 1'b 1; #15 reset = 1'b 0; #180 reset = 1'b 1; #10 reset = 1'b 0; #20 $stop; end initial // Monitor the outputs $monitor($time, " Output q = %d", endmodule 2010 DSD q); 21

What we learned today • An overview of Verilog programming (design) concepts 2010 DSD 22

Other Notes • Course web-page on Sharif Courseware • Do it yourself (You won’t, I know! : -) ) – Read Chapters 1 and 2 – Do Chapter 2 exercises – Install and use Model. Sim, and simulate ripple_carry_counter example 2010 DSD 23

Lexical Conventions in Verilog® HDL 2010 DSD

Lexical Conventions • Very similar to C – Verilog is case-sensitive – All keywords are in lowercase – A Verilog program is a string of tokens • • • 2010 Whitespace Comments Numbers Strings Identifiers Keywords DSD 25

Lexical Conventions (cont’d) • Whitespace • Comments – Blank space (b) – Tab (t) – Newline (n) – Used for readability and documentation – Just like C: • Whitespace is ignored in Verilog except /* /* be on – In strings – When separating tokens 2010 DSD // single line comment /* multi-line comment */ Nested comments like this */ may not acceptable (depends Verilog compiler) */ 26

Lexical Conventions (cont’d) • Operators – Unary operators precede the operand a = ~b; – Binary operators appear between two operands a = b && c; – Ternary operators have two separate operators that separate three operands a = b ? c : d; // the only ternary operator 2010 DSD 27

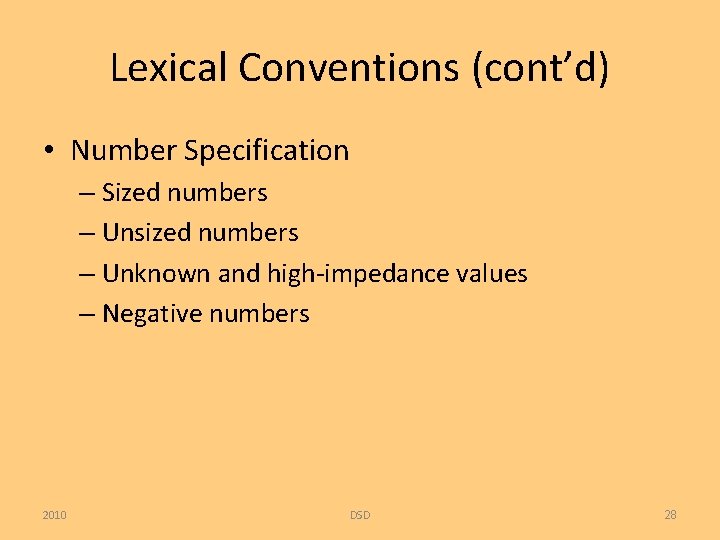

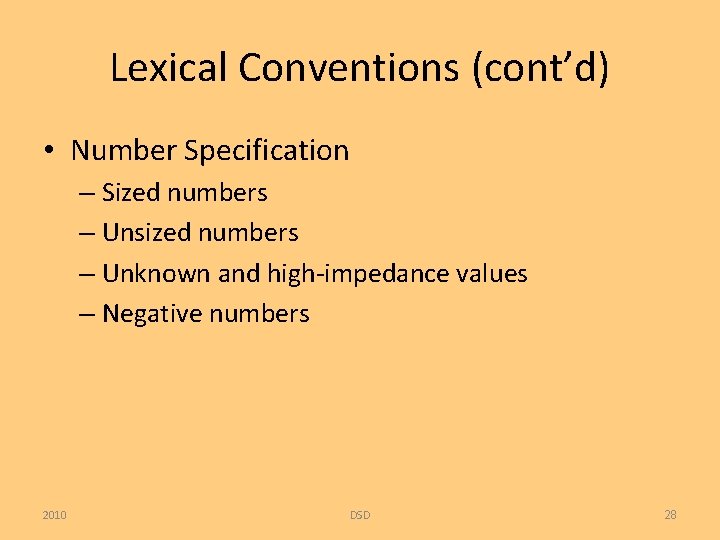

Lexical Conventions (cont’d) • Number Specification – Sized numbers – Unsized numbers – Unknown and high-impedance values – Negative numbers 2010 DSD 28

Lexical Conventions (cont’d) • Sized numbers • Unsized numbers – General syntax: <size>’<base><number> – Default base is decimal – Default size is at least 32 (depends on Verilog compiler) – Examples • <size> : number of bits (in decimal) • <base> : – – d or D for decimal (radix 10) b or B for binary (radix 2) o or O for octal (radix 8) h or H for hexadecimal (radix 16) • 23232 • ’habc • ’o 234 • <number> : is the number in radix <base> • Examples: – 4’b 1111 – 12’habc – 16’d 255 2010 DSD 29

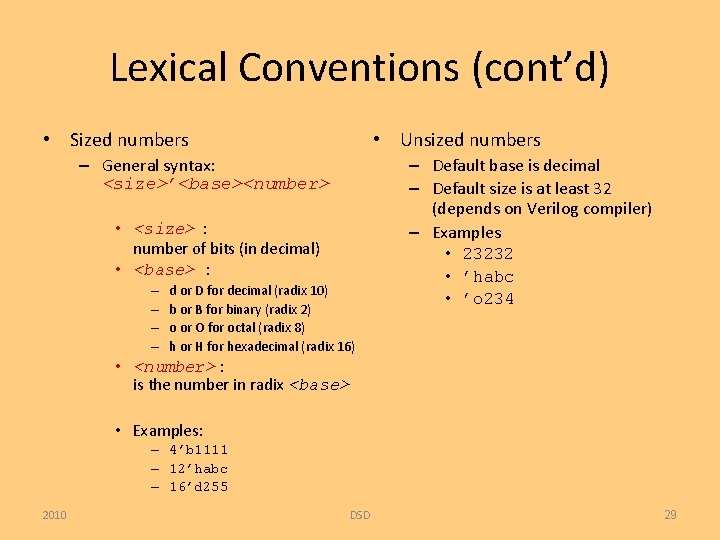

Lexical Conventions (cont’d) • X or Z values – Unknown value: lowercase x • 4 bits in hex, 3 bits in octal, 1 bit in binary – High-impedance value: lowercase z • 4 bits in hex, 3 bits in octal, 1 bit in binary – Examples • 12’h 13 x • 6’hx • 32’bz 2010 DSD 30

Lexical Conventions (cont’d) • Negative numbers – Put the sign before the <size> – Two’s complement is used to store the value – Examples: • -6’d 3 • 4’d-2 // illegal • Underscore character and question marks – Use ‘_’ to improve readability • 12’b 1111_0000_1010 • Not allowed as the first character – ‘? ’ is the same as ‘z’ (only regarding numbers) • 4’b 10? ? // the same as 4’b 10 zz 2010 DSD 31

Lexical Conventions (cont’d) • Strings – As in C, use double-quotes – Examples: • “Hello world!” • “a / b” • “texttcolumn 1bcolumn 2n” • Identifiers and keywords – identifiers (Identifiers are names given to objects so that they can be referenced in the design) • Alphanumeric characters, ‘_’, and ‘$’ • Should start with an alphabetic character or ‘_’ • Only system tasks can start with ‘$’ – Keywords • Identifiers reserved by Verilog – Examples: reg value; input clk; 2010 DSD 32

Lexical Conventions (cont’d) • Escaped identifiers – – – 2010 Start with ‘’ End with whitespace (space, tab, newline) Can have any printable character between start and end The ‘’ and whitespace are not part of the identifier Examples: • a+b-c // a+b-c is the identifier • **my_name** // **my_name** is the identifier • \n // ? ? ? DSD 33

Data Types in Verilog® HDL 2010 DSD

Data Types • • 2010 Value set and strengths Nets and Registers Vectors Integer, Real, and Time Register Data Types Arrays Memories Parameters Strings DSD 35

Value Set • Hardware modeling requirements – Value level – Value strength • Used to accurately model – – 2010 Signal contention MOS devices Dynamic MOS Other low-level details DSD 36

There are two types of strengths: drive strengths and charge strengths. The drive strengths can be used for nets (except trireg net) and gates. The charge strengths can be used only for trireg nets. The drive strength types are supply, strong, pull, weak, and highz strengths. The charge strength types are large, medium and small strengths. Drive strength is the capacity of a cell to drive a value to the cell connected to its output. Storage Strength is capacity to store charge.

Value Set and Strength Levels Value level HW Condition 2010 Strength level Type 0 Logic zero, false supply Driving 1 Logic one, true strong Driving pull Driving large Storage weak Driving medium Storage small Storage highz High Impedance x Unknown z High imp. , floating DSD 38

If two signals of unequal strengths are driven on a wire, the stronger signal prevails. For example, if two signals of strength strong 1 and weak 0 contend, the result is resolved as a strong 1. If two signals of equal strengths are driven on a wire, the result is unknown. If two signals of strength strong 1 and strong 0 conflict, the result is an x. Strength levels are particularly useful for accurate modeling of signal contention, MOS devices, dynamic MOS, and other low-level devices. Only trireg nets can have storage strengths large, medium, and small

Net Data Type • Used to represent connections between HW elements – Values continuously driven on nets • Keyword: wire – Default: One-bit values • unless declared as vectors – Examples • wire a; • wire b, c; • wire d=1’b 0; – Default value: z 2010 DSD 40

• Net data types are used to model physical connections. They do not store values (there is only one exception - trireg, which stores a previously assigned value). The net data types have the value of their drivers. If a net variable has no driver, then it has a high-impedance value (z). • 2010 For trireg, default value is x DSD 41

Register Data Types • Registers represent data storage elements – Retain value until next assignment – NOTE: this is not a hardware register or flipflop, In Verilog, the term register merely means a variable that can hold a value – Keyword: reg – Default value: x – Example: 2010 reg reset; initial // this will be explained later begin reset = 1’b 1; //initialize reset to 1 to reset the digital #100 reset=1’b 0; DSD end 42

Types of Registers • Integer – Keyword: integer • integer variables are signed numbers • reg vectors are unsigned numbers, unless specified – reg signed [63: 0] m; // 64 bit signed value – Bit width: implementation-dependent (at least 32 -bits) • Designer can also specify a width: integer [7: 0] tmp; – Examples: integer counter; initial counter = -1; //A negative one is stored in the counter 2010 DSD 43

Register Types (cont’d) • Real – Keyword: real – Values: • Default value: 0 • Decimal notation: 12. 24 • Scientific notation: 3 e 6 (=3 x 106) – When a real value is assigned to an integer, the real number is rounded off to the nearest integer. – Example: real delta; initial begin delta = 4 e 10; delta = 2. 13; end integer i; initial #5 i = delta; // i gets the value 2 (rounded value of 2. 13) 2010 DSD 44

Register Data Types (cont’d) • Time – – – Used to store values of simulation time Keyword: time Bit width: implementation-dependent (at least 64) $time system function gives current simulation time Example: time save_sim_time; // Define a time variable initial save_sim_time = $time; // Save the current simulation time 2010 DSD 45

Vectors • Nets or reg data types can be declared as vectors (multiple bit widths). If bit width is not specified, the default is scalar (1 -bit). Applicable to both net and register data types • Syntax: – wire/reg [msb_index : lsb_index] data_id; • Examples wire a; // scalar net variable, default wire [7: 0] bus; // 8 -bit bus wire [31: 0] bus. A, bus. B, bus. C; // 3 buses of 32 -bi reg clock; // scalar register, default reg [0: 40] virtual_addr; //virtual address 41 bits 2010 DSD 46

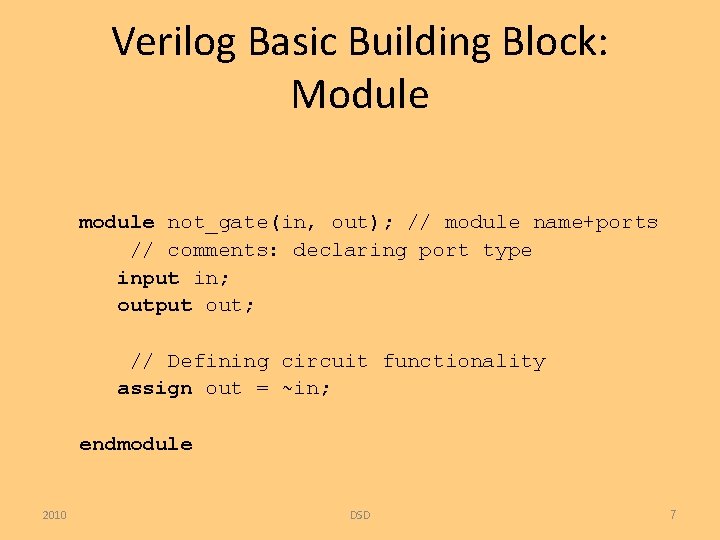

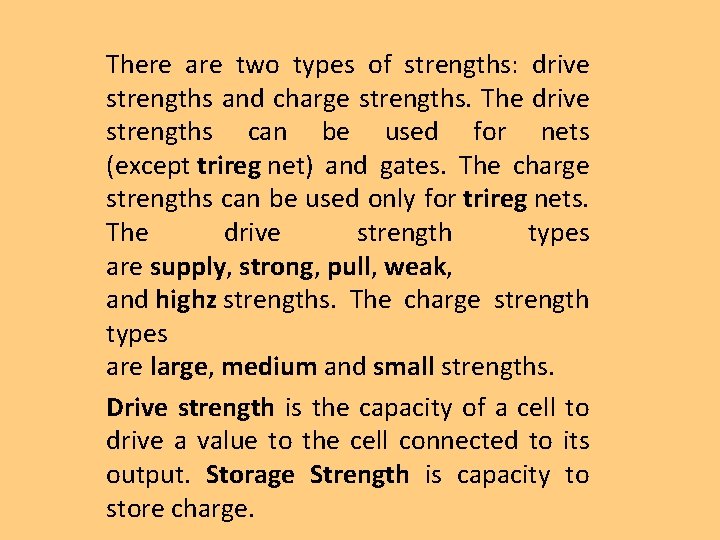

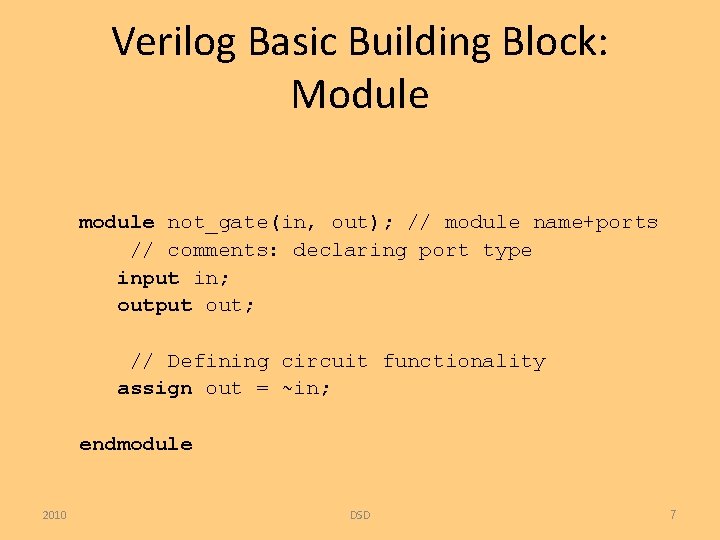

![Vectors contd Bitselect and partselect allowed bus A7 selects bit 7 of Vectors (cont’d) • Bit-select and part-select allowed: bus. A[7] // selects bit #7 of](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-47.jpg)

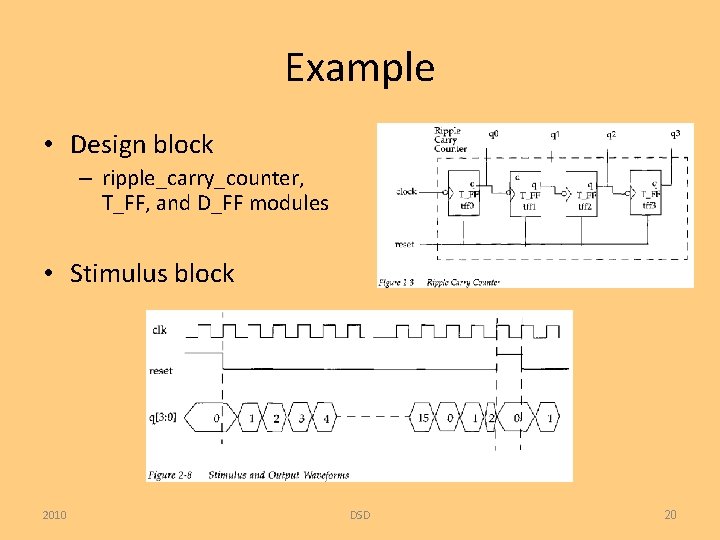

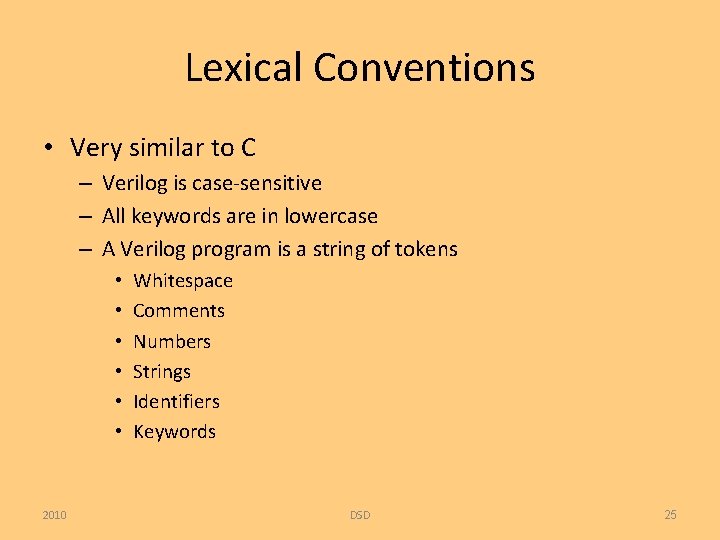

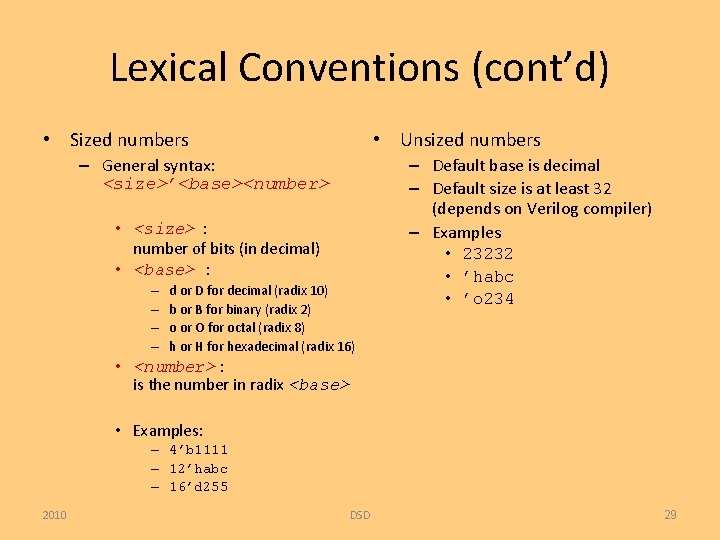

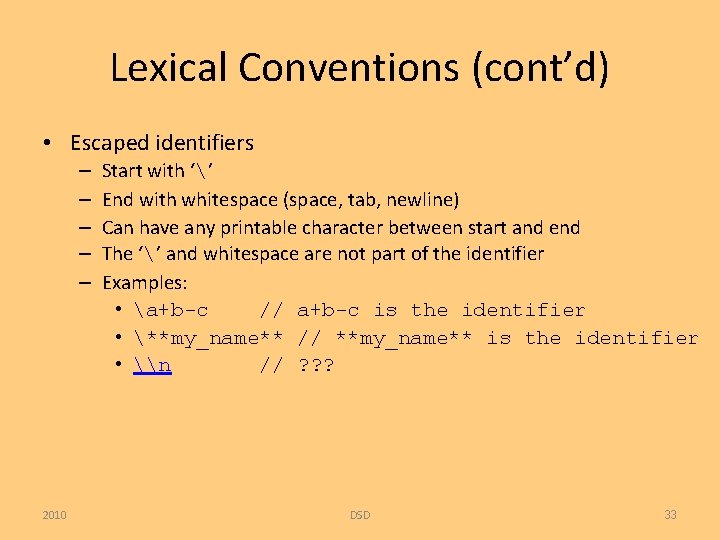

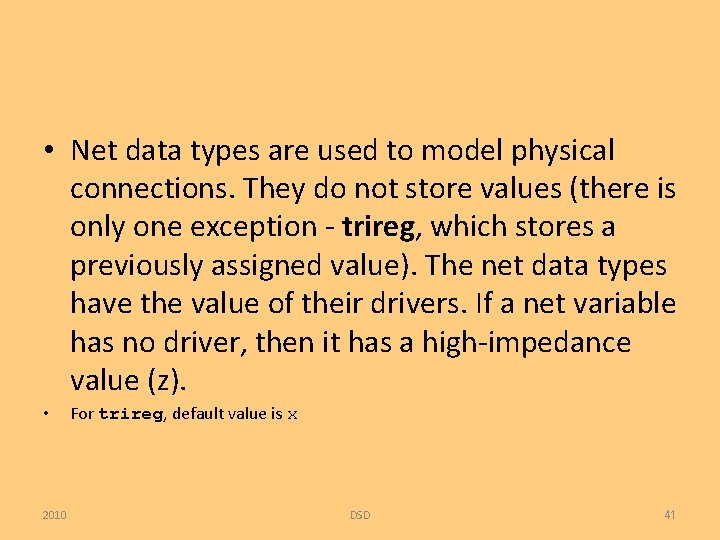

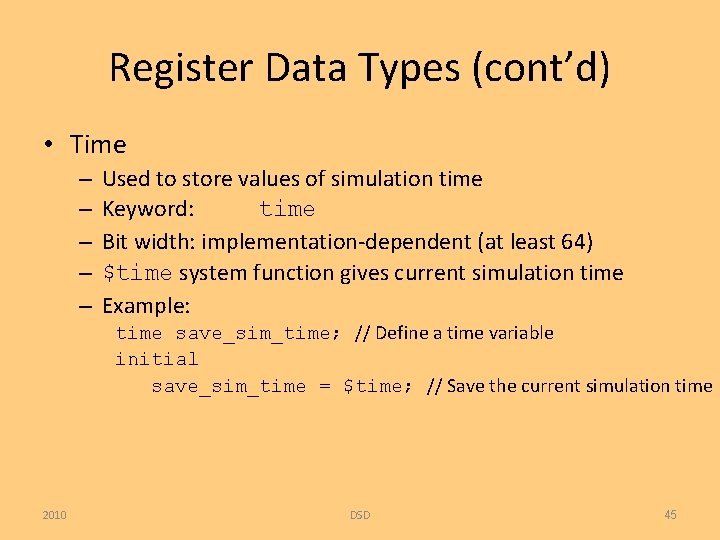

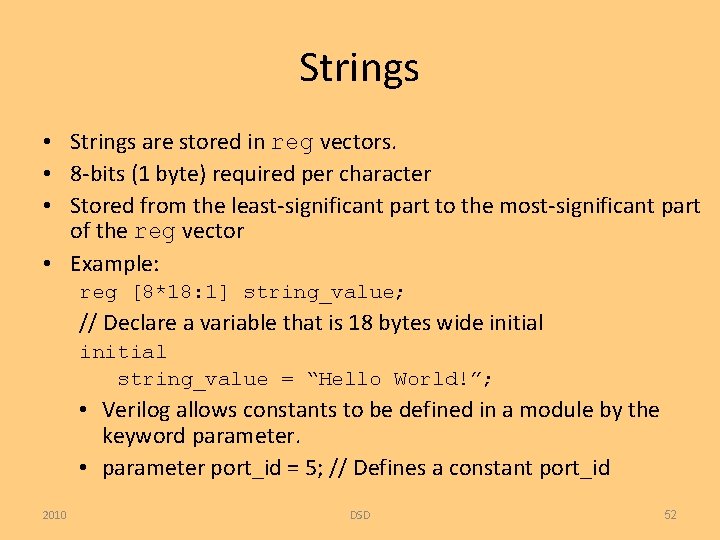

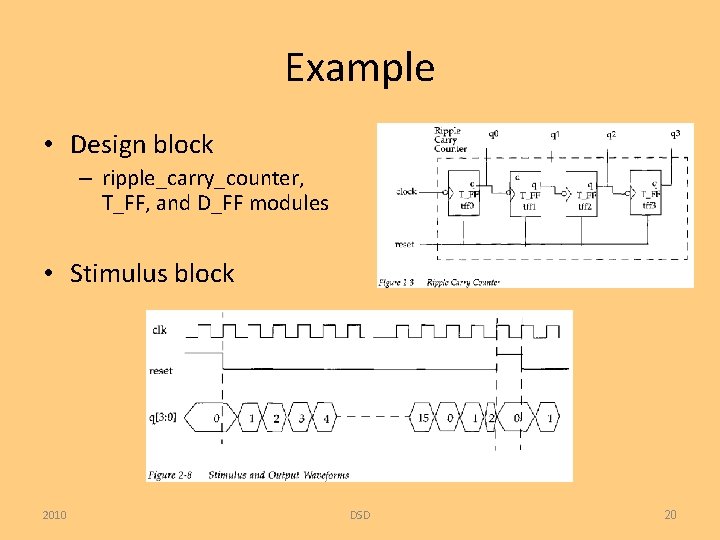

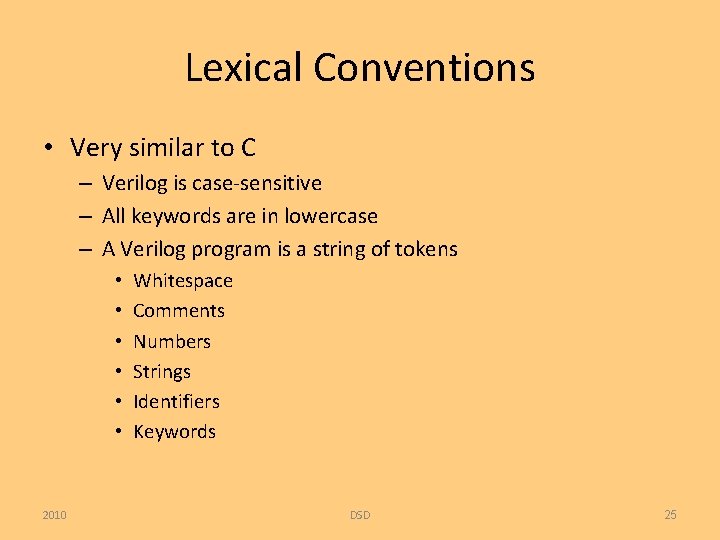

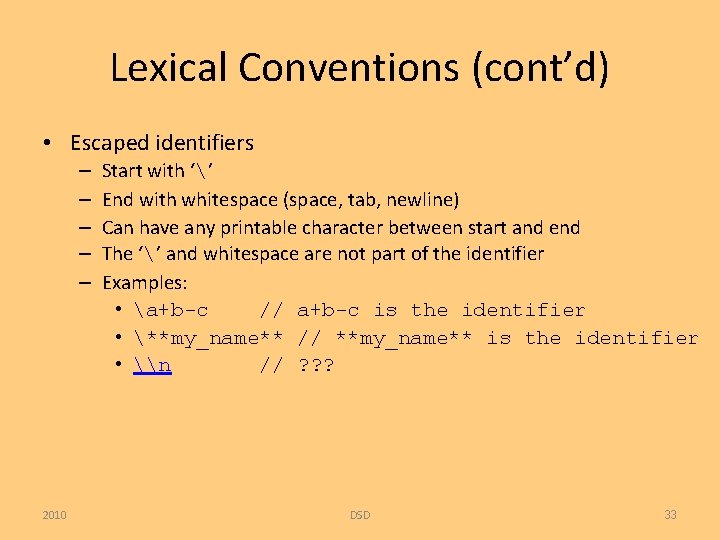

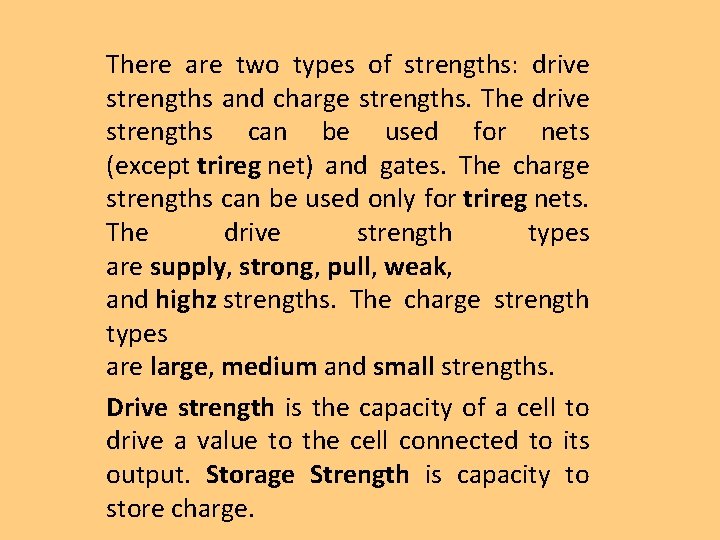

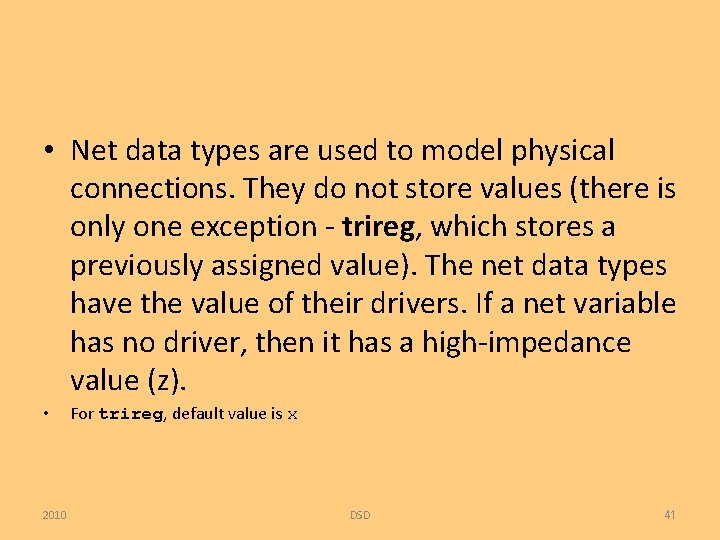

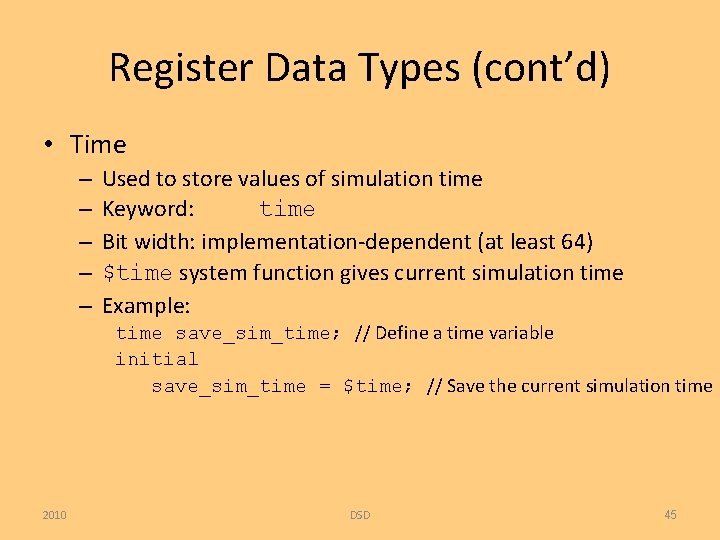

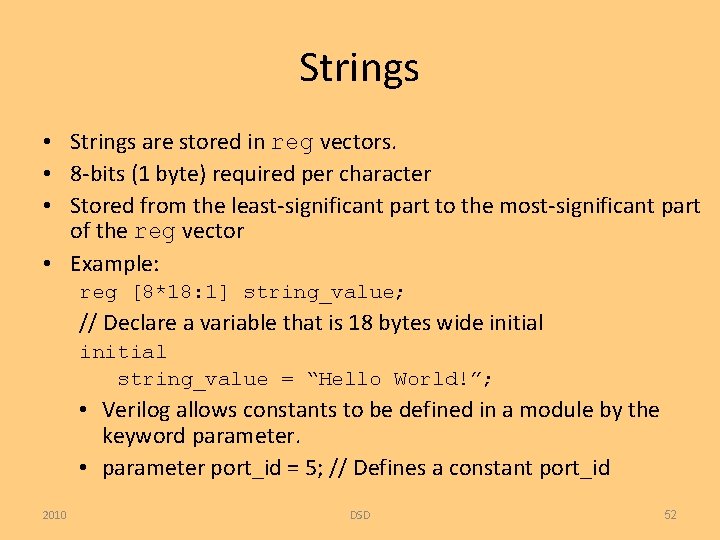

Vectors (cont’d) • Bit-select and part-select allowed: bus. A[7] // selects bit #7 of vectorbus A bus. B[2: 0] //three least-significant bits-ofbus. B bus[0: 2] // illegal virtual_addr[0: 1] /* two most-significant bits * of virtual_addr */ 2010 DSD 47

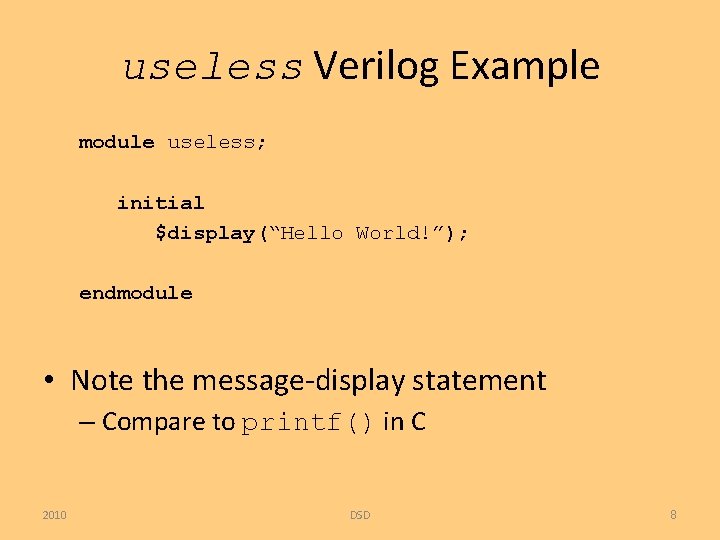

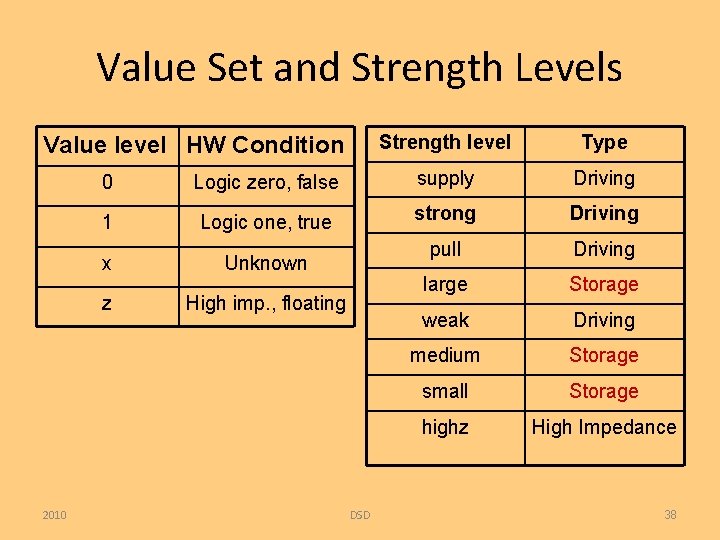

![Vectors contd Variable Vector Part Select reg 255 0 data 1 Little endian notation Vectors( cont’d) Variable Vector Part Select reg [255: 0] data 1; //Little endian notation](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-48.jpg)

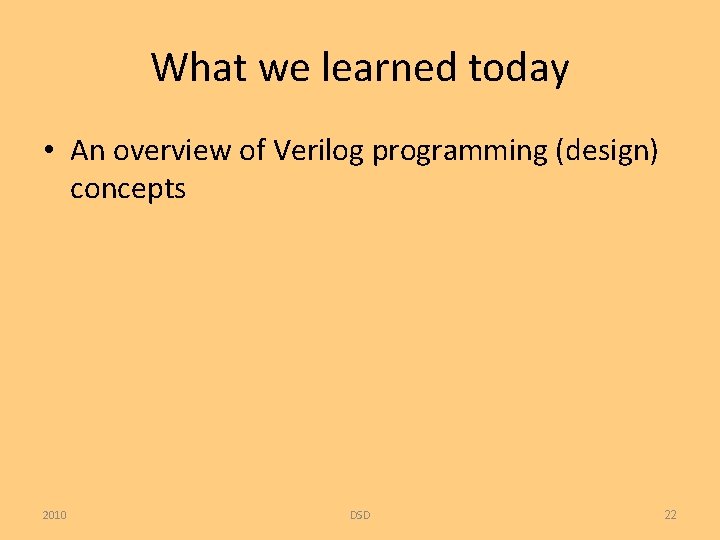

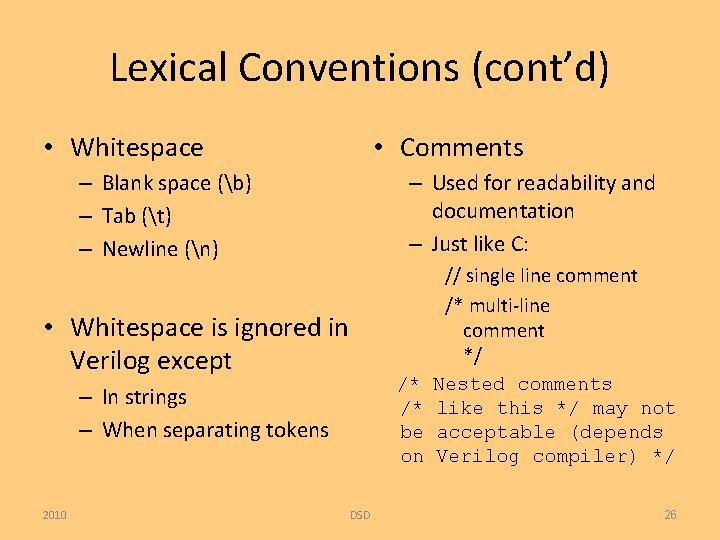

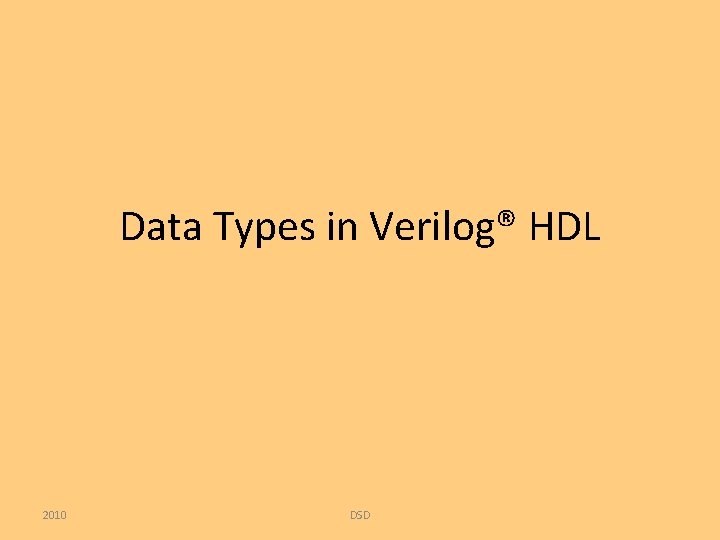

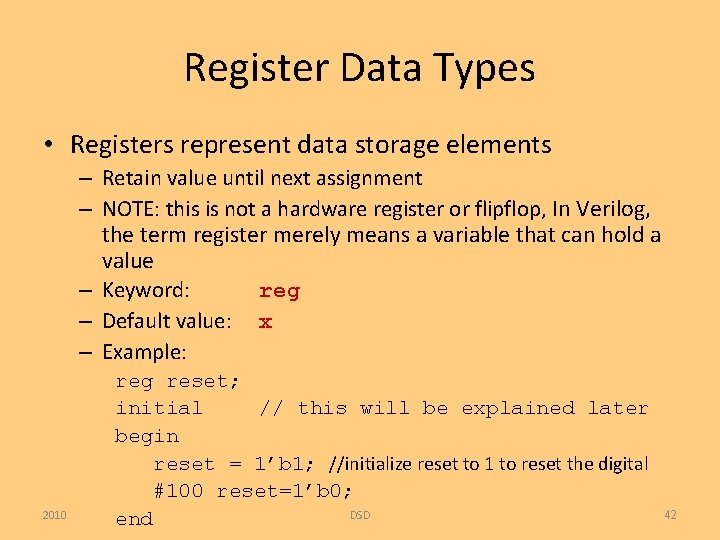

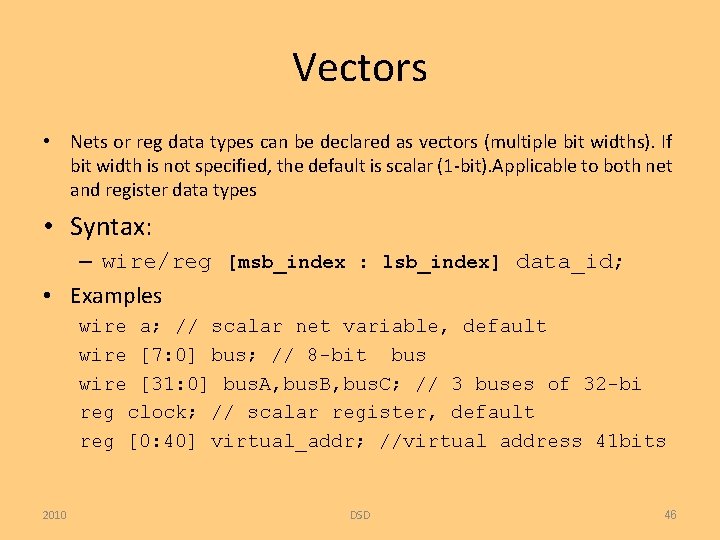

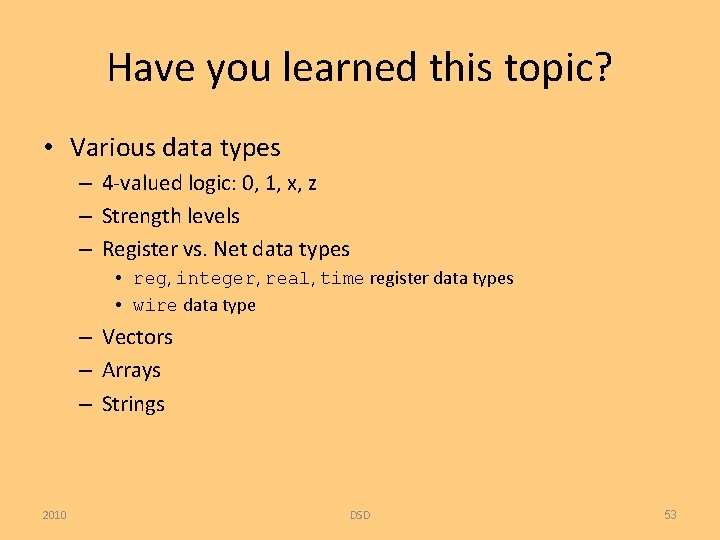

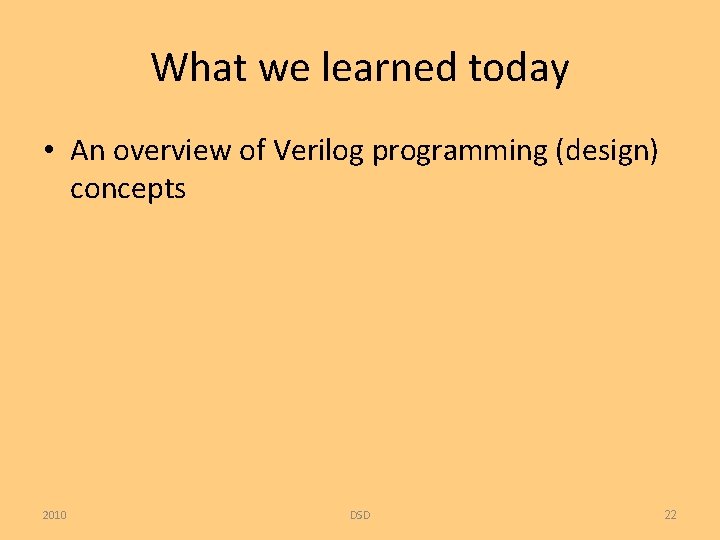

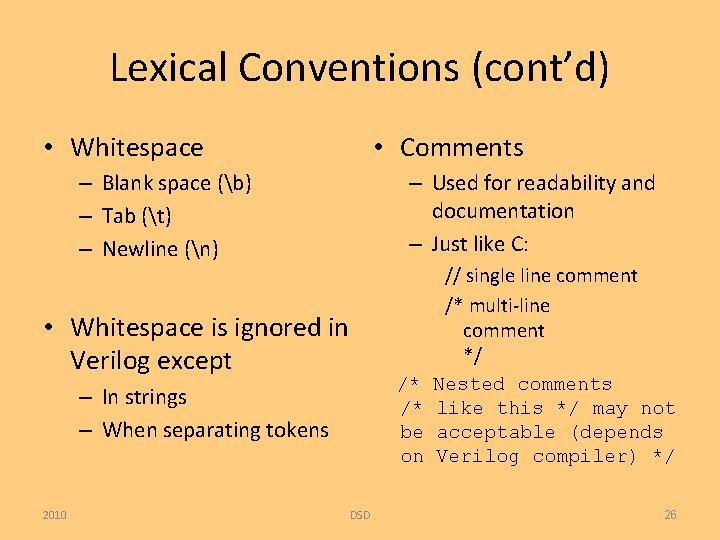

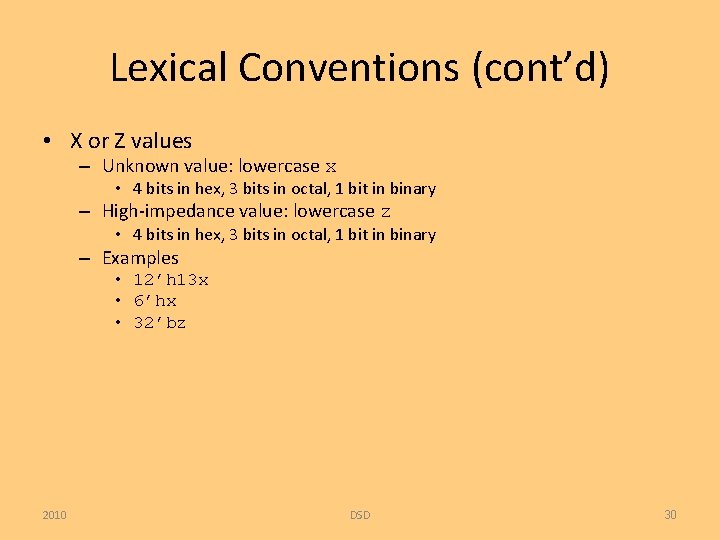

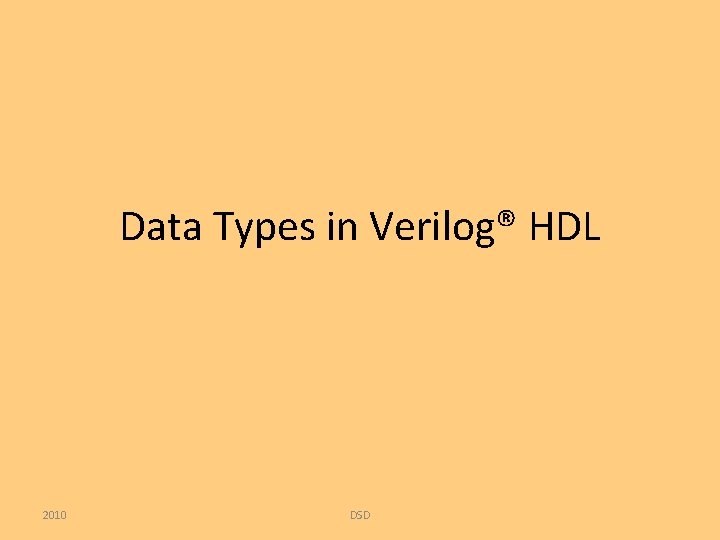

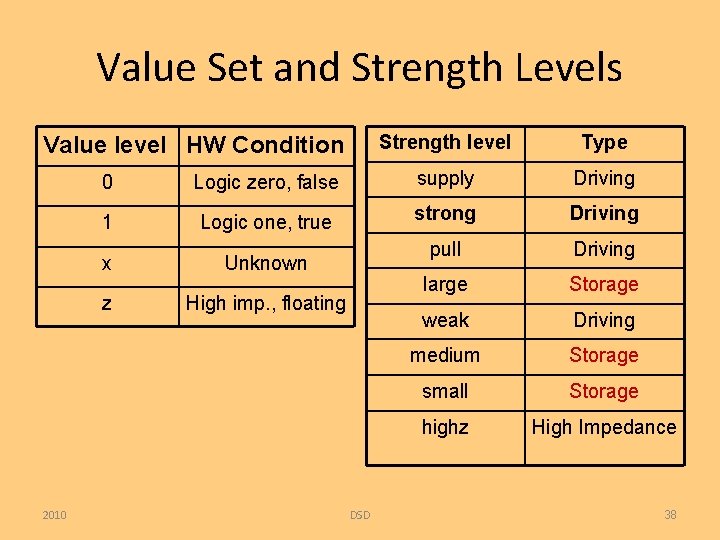

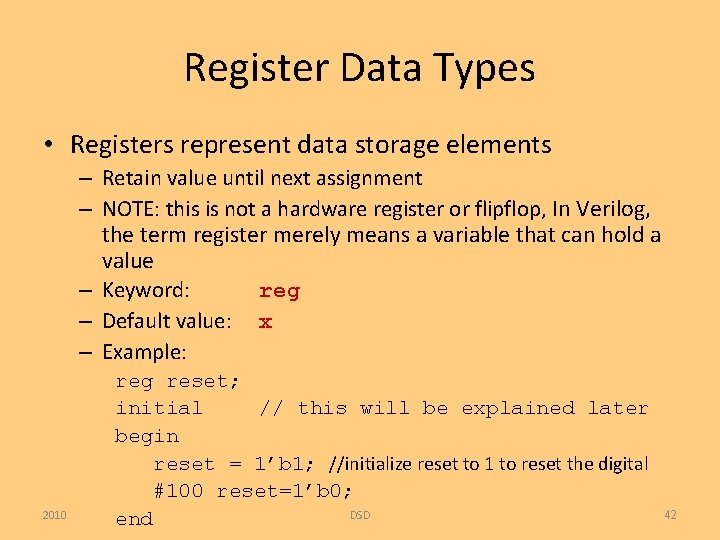

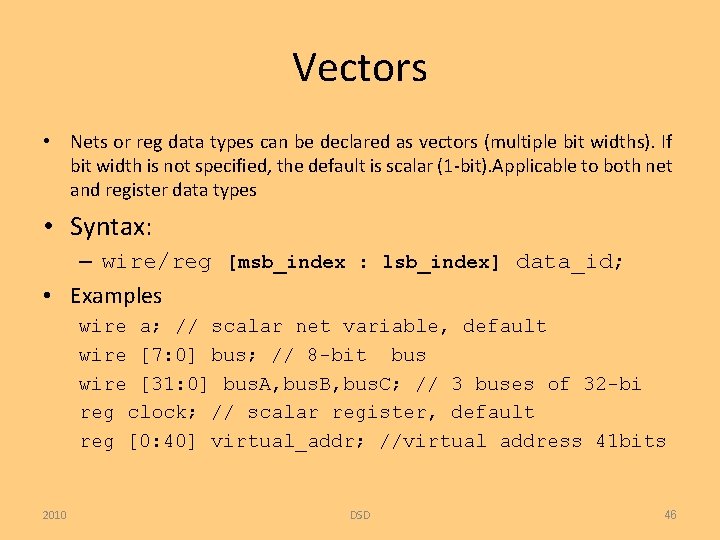

Vectors( cont’d) Variable Vector Part Select reg [255: 0] data 1; //Little endian notation reg [0: 255] data 2; //Big endian notation reg [7: 0] byte; //Using a variable part select, byte = data 1[31 -: 8]; //starting byte = data 1[24+: 8]; //starting byte = data 2[31 -: 8]; //starting byte = data 2[24+: 8]; //starting one bit bit can choose parts = 31, width =8 => = 24, width =8 => data 1[31: 24] data 2[24: 31] //The starting bit can also be a variable. The width has //to be constant. Therefore, one can use the variable part select //in a loop to select all bytes of the vector. for (j=0; j<=31; j=j+1) byte = data 1[(j*8)+: 8]; //Sequence is [7: 0], [15: 8]. . . [255: 248] 2010 DSD 48

Arrays • Allowed for all data types • Multi-dimensional • Syntax: <data_type> <var_name> [start_idx : end_idx]. . . [start_idx : end_idx]; • Examples: integer reg [4: 0] integer count[0: 7]; // An array of 8 count variables bool[31: 0]; // Array of 32 one-bit boolean register port_id[0: 7]; //Array of 8 port_ids; each port_id is 5 bits wide matrix[4: 0][0: 16]; // Two dimensional array of integers • Difference between vectors and arrays 2010 DSD 49

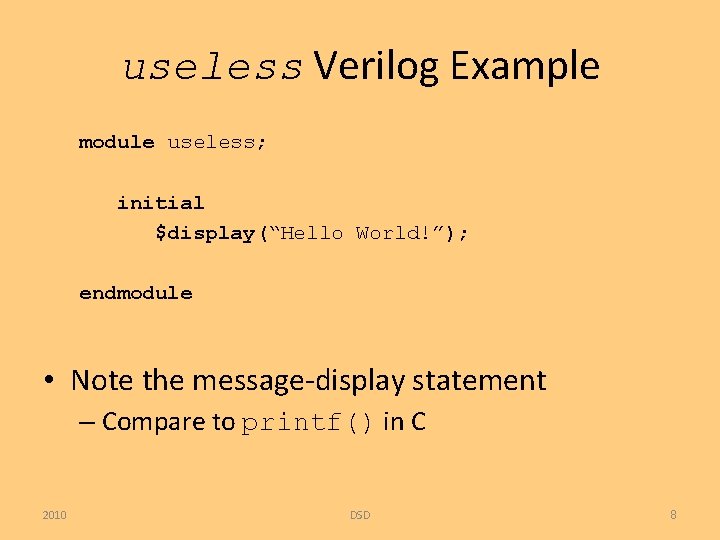

![Arrays contd Examples contd count5 0 Reset 5 th element of Arrays (cont’d) • Examples (cont’d) count[5] = 0; // Reset 5 th element of](https://slidetodoc.com/presentation_image_h2/fbfd8cbb398bfe2ad09b3b158e88959c/image-50.jpg)

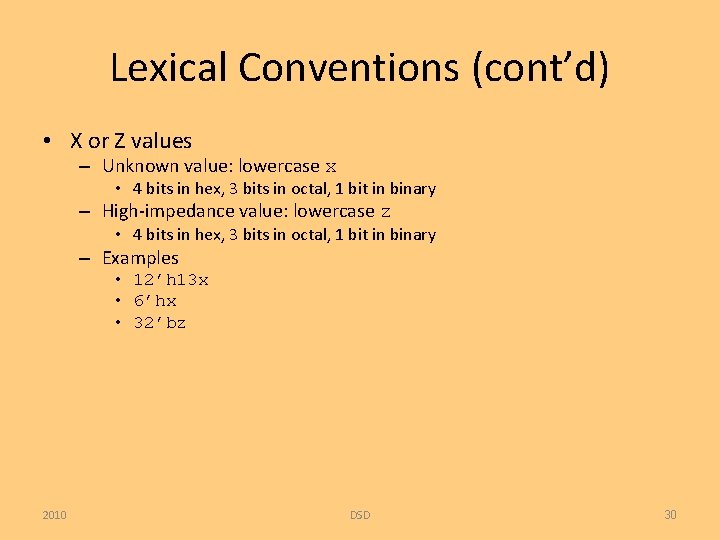

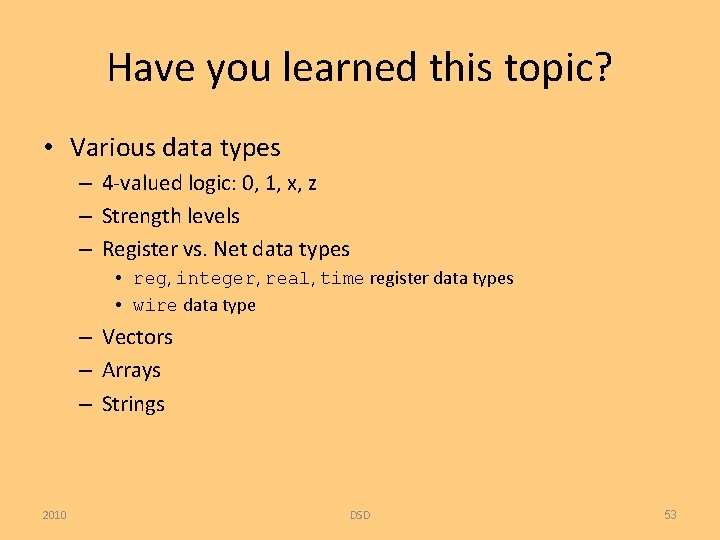

Arrays (cont’d) • Examples (cont’d) count[5] = 0; // Reset 5 th element of array of count variables chk_point[100] = 0; // Reset 100 th time check point value port_id[3] = 0; // Reset 3 rd element (a 5 -bit value) of port_id array. matrix[1][0] = 33559; // Set value of element indexed by [1][0] to 33559 port_id = 0; // Illegal matrix [1] = 0; // Illegal 2010 DSD 50

Memories • RAM, ROM, and register-files used many times in digital systems • Memory = array of registers (register data type) in Verilog • Word = an element of the array – Can be one or more bits • Examples: reg membit [0: 1023]; // Memory mem 1 bit with 1 K 1 -bitwords reg [7: 0] membyte[0: 1023]; //Memory membyte with 1 K 8 -bit words(bytes) membyte[511] //Fetches 1 byte word whose address is 511 2010 DSD 51

Strings • Strings are stored in reg vectors. • 8 -bits (1 byte) required per character • Stored from the least-significant part to the most-significant part of the reg vector • Example: reg [8*18: 1] string_value; // Declare a variable that is 18 bytes wide initial string_value = “Hello World!”; • Verilog allows constants to be defined in a module by the keyword parameter. • parameter port_id = 5; // Defines a constant port_id 2010 DSD 52

Have you learned this topic? • Various data types – 4 -valued logic: 0, 1, x, z – Strength levels – Register vs. Net data types • reg, integer, real, time register data types • wire data type – Vectors – Arrays – Strings 2010 DSD 53