Digital System Design Verilog HDL Behavioral Modeling 2

Digital System Design Verilog® HDL Behavioral Modeling (2) 2005 Verilog HDL Maziar Goudarzi

Today program l Behavioral Modeling ¡ Timing controls ¡ Other features 2005 Verilog HDL 2

Behavioral Modeling Timing Controls in Behavioral Modeling 2005 Verilog HDL

Introduction timing controls No advance in simulation time l Three methods of timing control l No ¡ delay-based ¡ event-based ¡ level-sensitive 2005 Verilog HDL 4

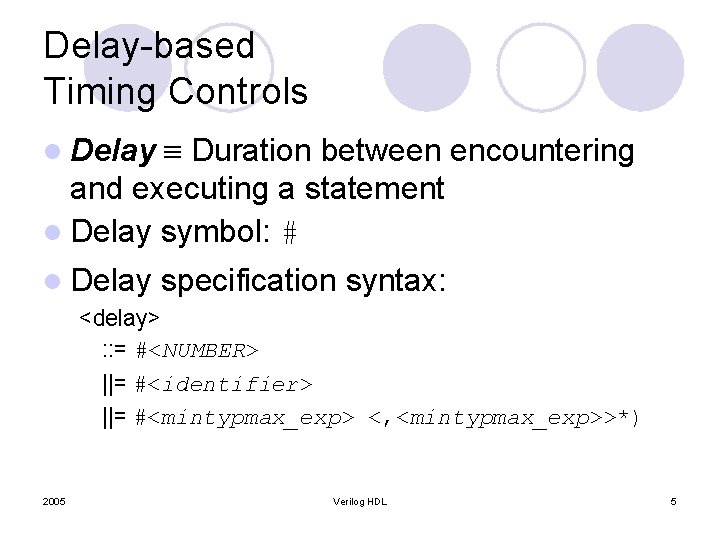

Delay-based Timing Controls Duration between encountering and executing a statement l Delay symbol: # l Delay specification syntax: <delay> : : = #<NUMBER> ||= #<identifier> ||= #<mintypmax_exp> <, <mintypmax_exp>>*) 2005 Verilog HDL 5

Delay-based Timing Controls (cont’d) l Types of delay-based timing controls 1. Regular delay control 2. Intra-assignment delay control 3. Zero-delay control 2005 Verilog HDL 6

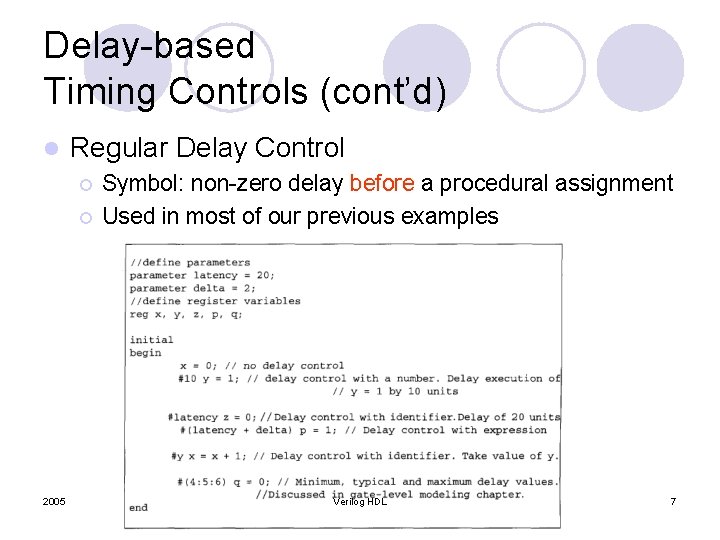

Delay-based Timing Controls (cont’d) l Regular Delay Control ¡ ¡ 2005 Symbol: non-zero delay before a procedural assignment Used in most of our previous examples Verilog HDL 7

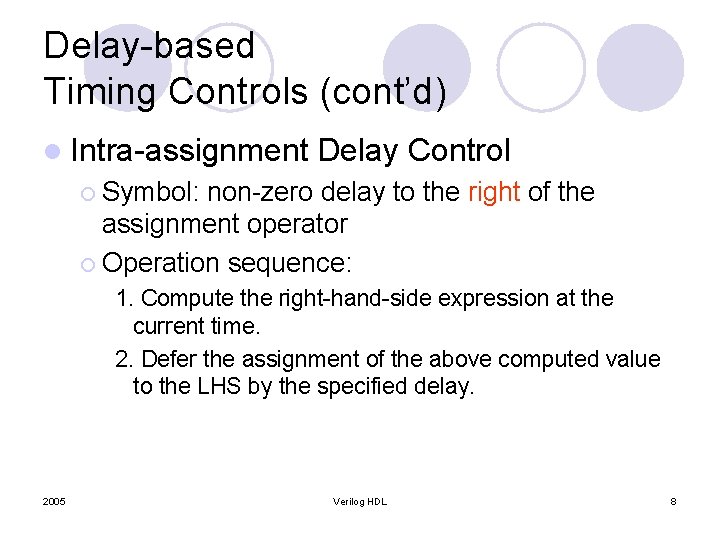

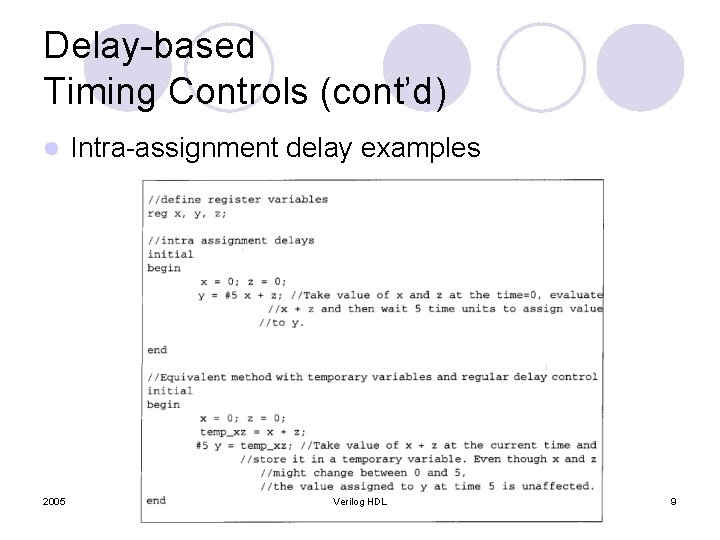

Delay-based Timing Controls (cont’d) l Intra-assignment Delay Control ¡ Symbol: non-zero delay to the right of the assignment operator ¡ Operation sequence: 1. Compute the right-hand-side expression at the current time. 2. Defer the assignment of the above computed value to the LHS by the specified delay. 2005 Verilog HDL 8

Delay-based Timing Controls (cont’d) l 2005 Intra-assignment delay examples Verilog HDL 9

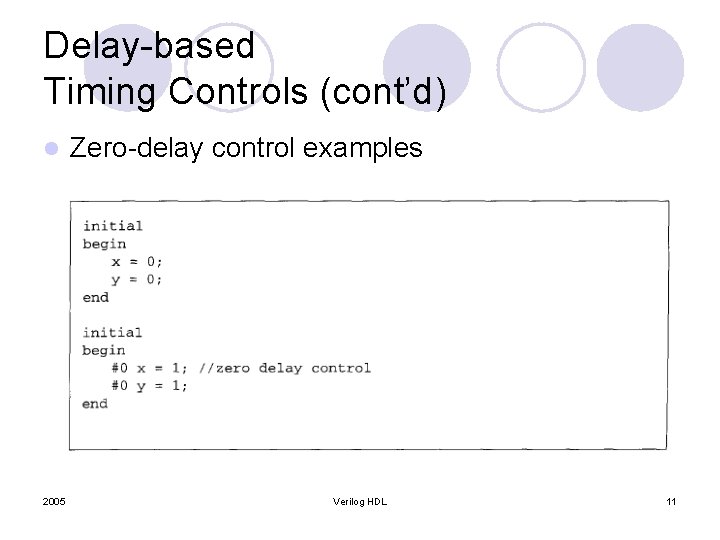

Delay-based Timing Controls (cont’d) l Zero-Delay Control ¡ Symbol: #0 ¡ Different initial/always blocks in the same simulation time l Execution order non-deterministic ¡ Zero-delay statements l Eliminates race conditions ¡ Multiple l 2005 ensures execution after all other zero-delay statements Non-deterministic execution order Verilog HDL 10

Delay-based Timing Controls (cont’d) l 2005 Zero-delay control examples Verilog HDL 11

Event-based Timing Control l Event ¡ Change in the value of a register or net ¡ Used to trigger execution of a statement or block (reactive behavior/reactivity) l Types of Event-based timing control 1. Regular event control 2. Named event control 3. Event OR control 4. Level-sensitive timing control (next section) 2005 Verilog HDL 12

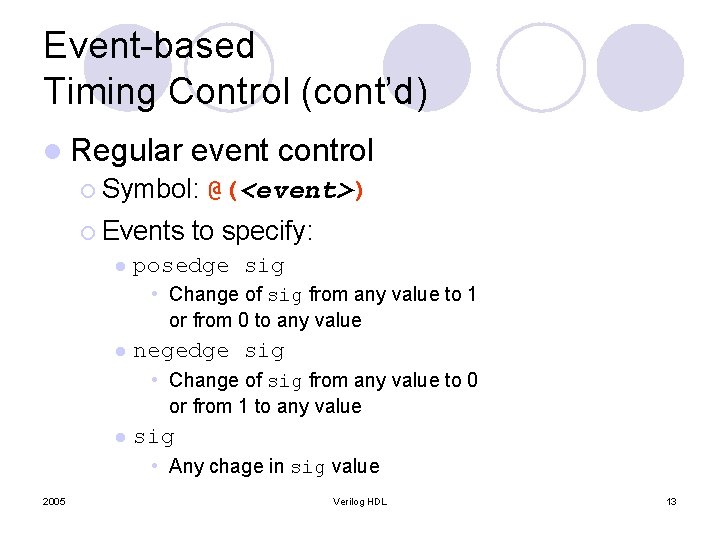

Event-based Timing Control (cont’d) l Regular event control ¡ Symbol: @(<event>) ¡ Events l to specify: posedge sig • Change of sig from any value to 1 or from 0 to any value l negedge sig • Change of sig from any value to 0 or from 1 to any value l sig • Any chage in sig value 2005 Verilog HDL 13

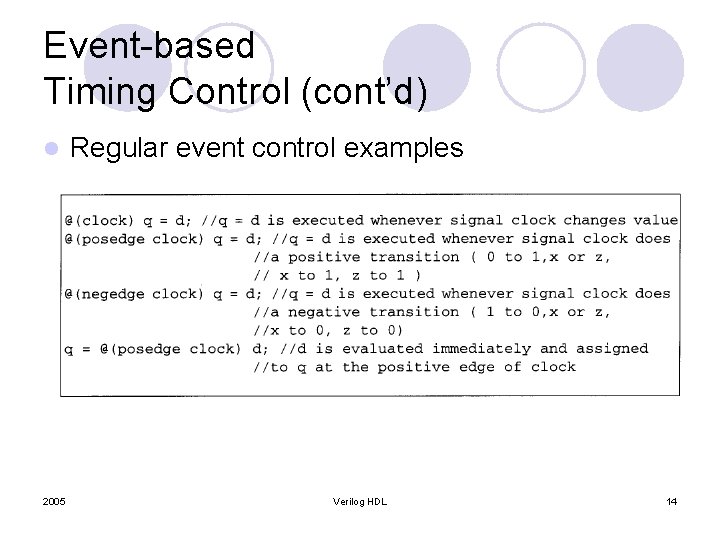

Event-based Timing Control (cont’d) l 2005 Regular event control examples Verilog HDL 14

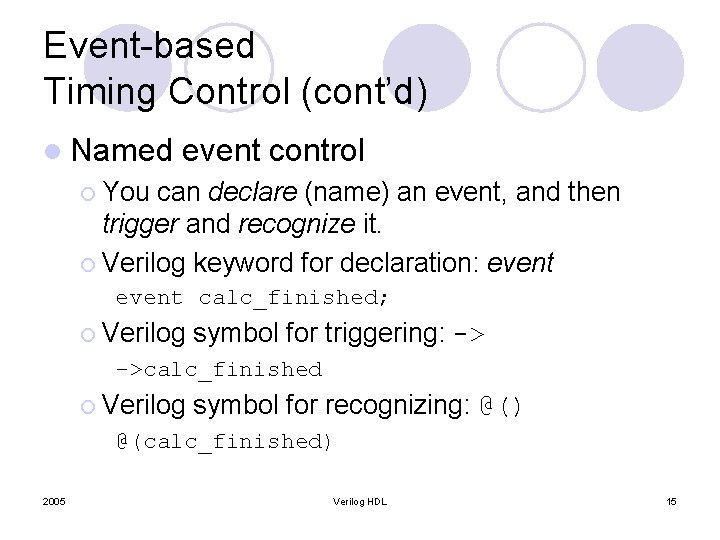

Event-based Timing Control (cont’d) l Named event control ¡ You can declare (name) an event, and then trigger and recognize it. ¡ Verilog keyword for declaration: event calc_finished; ¡ Verilog symbol for triggering: -> ->calc_finished ¡ Verilog symbol for recognizing: @() @(calc_finished) 2005 Verilog HDL 15

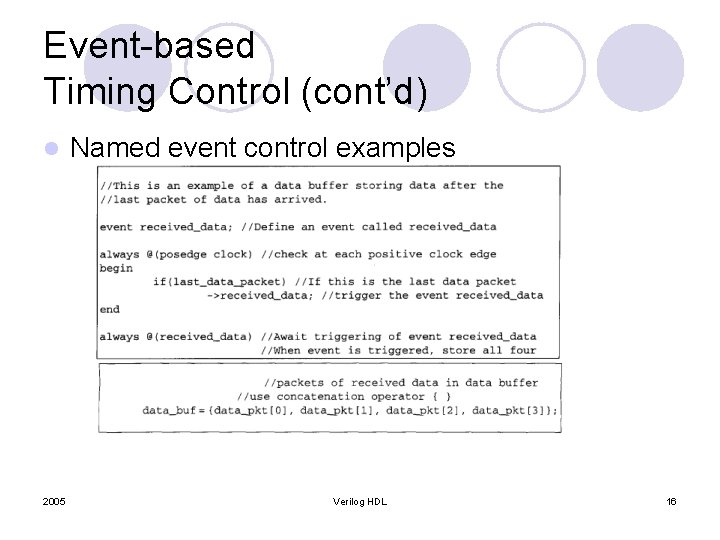

Event-based Timing Control (cont’d) l 2005 Named event control examples Verilog HDL 16

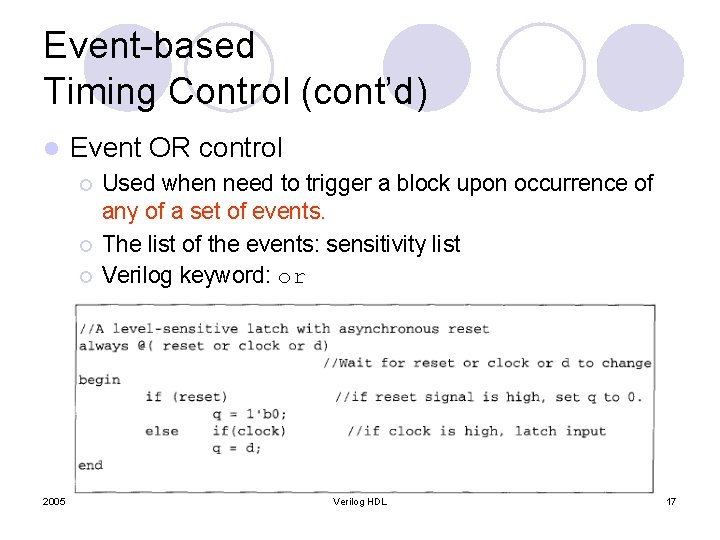

Event-based Timing Control (cont’d) l Event OR control ¡ ¡ ¡ 2005 Used when need to trigger a block upon occurrence of any of a set of events. The list of the events: sensitivity list Verilog keyword: or Verilog HDL 17

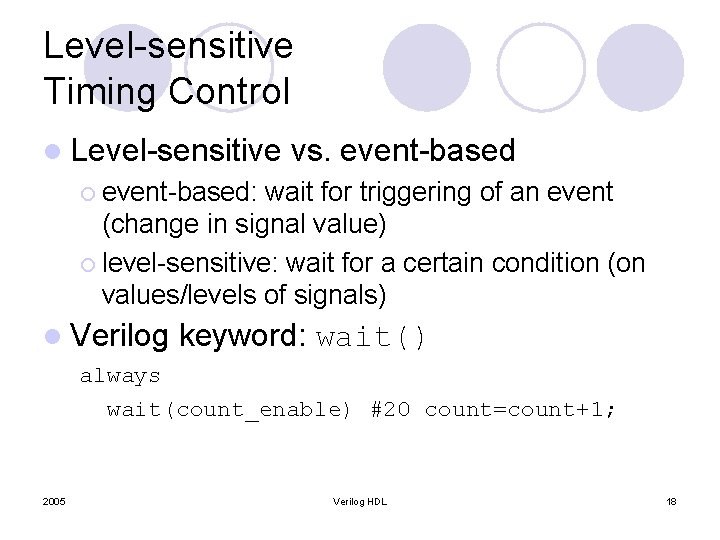

Level-sensitive Timing Control l Level-sensitive vs. event-based ¡ event-based: wait for triggering of an event (change in signal value) ¡ level-sensitive: wait for a certain condition (on values/levels of signals) l Verilog keyword: wait() always wait(count_enable) #20 count=count+1; 2005 Verilog HDL 18

Behavioral Modeling Other Features 2005 Verilog HDL

Contents l Sequential and Parallel Blocks l Special Features of Blocks 2005 Verilog HDL 20

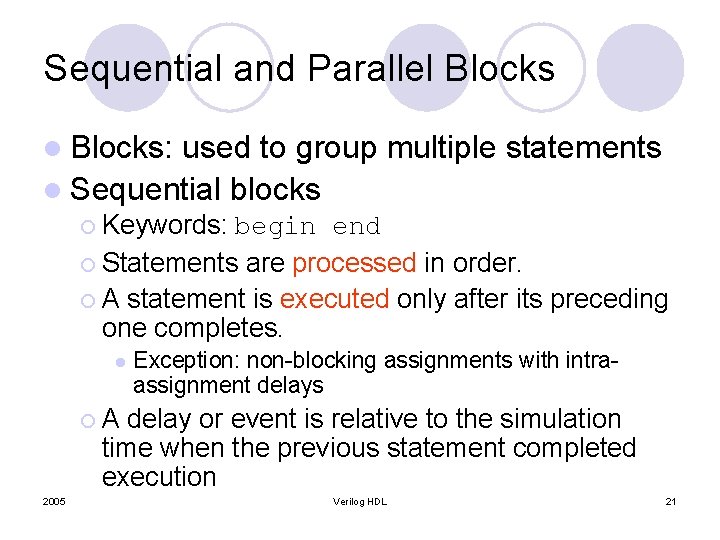

Sequential and Parallel Blocks: used to group multiple statements l Sequential blocks ¡ Keywords: begin end ¡ Statements are processed in order. ¡ A statement is executed only after its preceding one completes. l Exception: non-blocking assignments with intraassignment delays ¡A delay or event is relative to the simulation time when the previous statement completed execution 2005 Verilog HDL 21

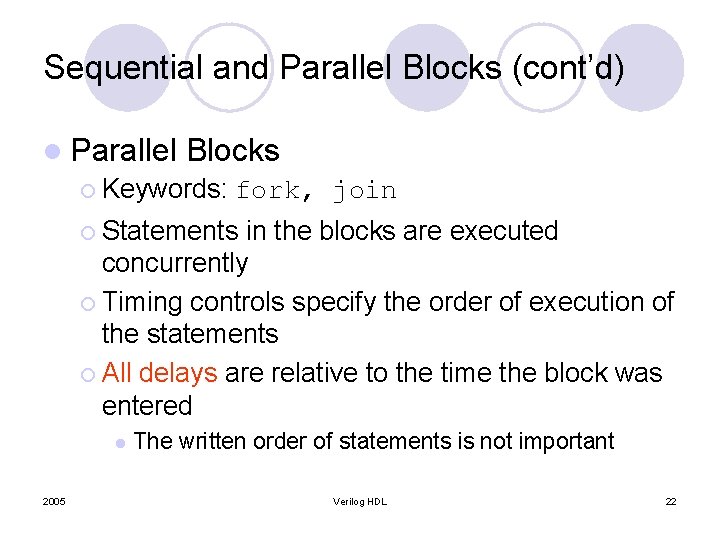

Sequential and Parallel Blocks (cont’d) l Parallel Blocks ¡ Keywords: fork, join ¡ Statements in the blocks are executed concurrently ¡ Timing controls specify the order of execution of the statements ¡ All delays are relative to the time the block was entered l 2005 The written order of statements is not important Verilog HDL 22

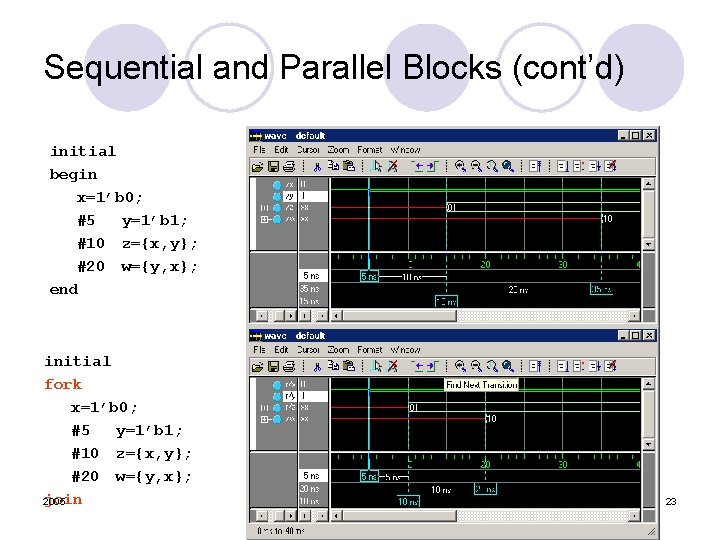

Sequential and Parallel Blocks (cont’d) initial begin x=1’b 0; #5 y=1’b 1; #10 z={x, y}; #20 w={y, x}; end initial fork x=1’b 0; #5 y=1’b 1; #10 z={x, y}; #20 w={y, x}; join 2005 Verilog HDL 23

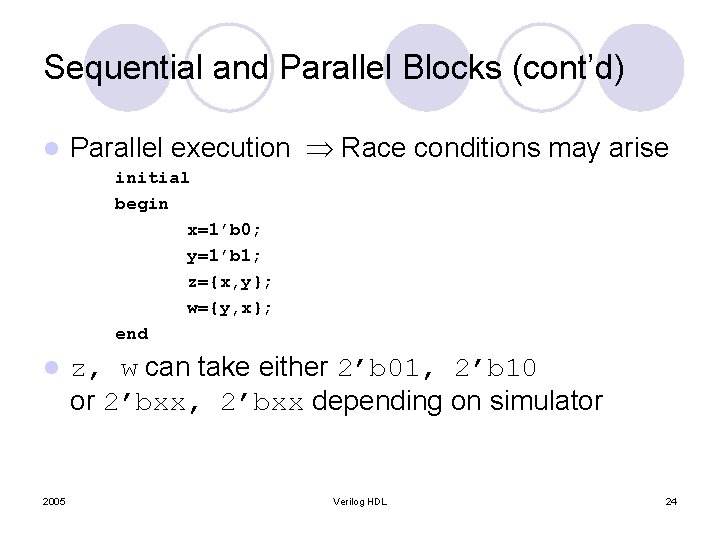

Sequential and Parallel Blocks (cont’d) l Parallel execution Race conditions may arise initial begin x=1’b 0; y=1’b 1; z={x, y}; w={y, x}; end l 2005 z, w can take either 2’b 01, 2’b 10 or 2’bxx, 2’bxx depending on simulator Verilog HDL 24

Special Features of Blocks l Contents ¡ Nested blocks ¡ Named blocks ¡ Disabling named blocks 2005 Verilog HDL 25

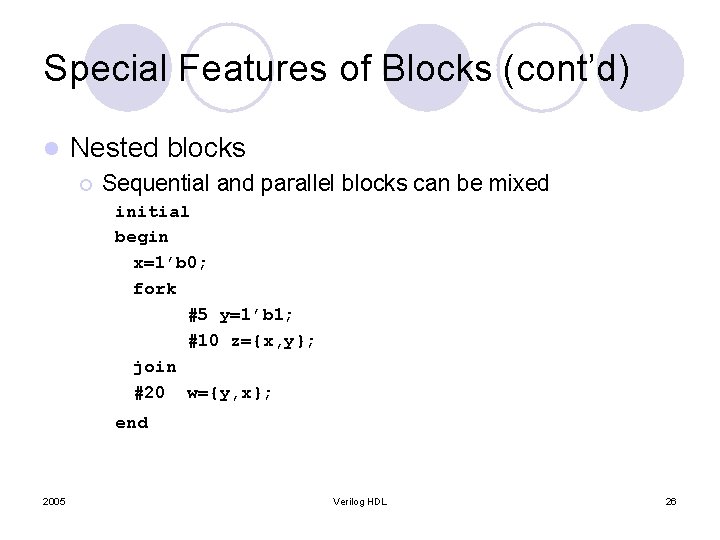

Special Features of Blocks (cont’d) l Nested blocks ¡ Sequential and parallel blocks can be mixed initial begin x=1’b 0; fork #5 y=1’b 1; #10 z={x, y}; join #20 w={y, x}; end 2005 Verilog HDL 26

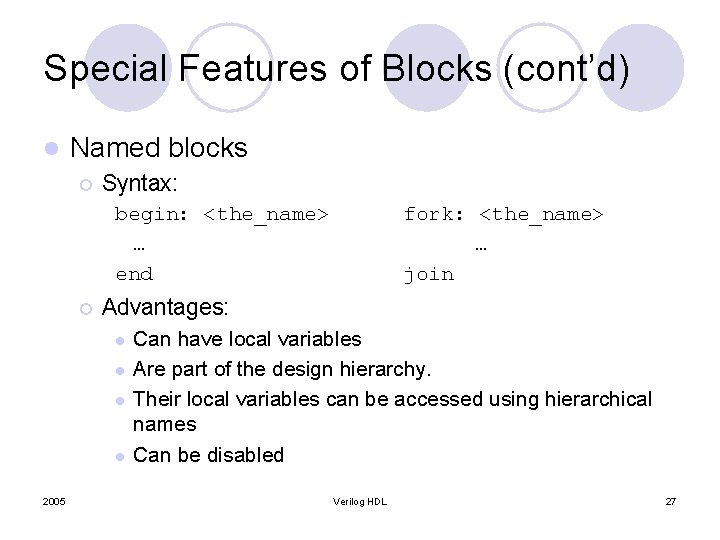

Special Features of Blocks (cont’d) l Named blocks ¡ Syntax: begin: <the_name> … end ¡ Advantages: l l 2005 fork: <the_name> … join Can have local variables Are part of the design hierarchy. Their local variables can be accessed using hierarchical names Can be disabled Verilog HDL 27

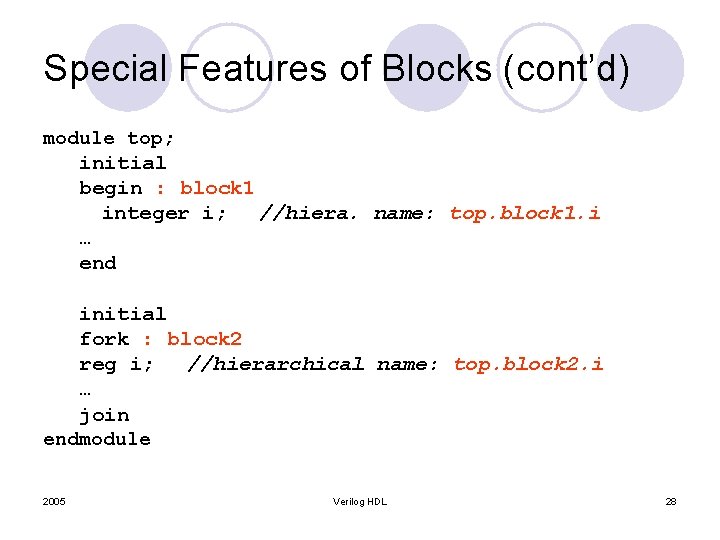

Special Features of Blocks (cont’d) module top; initial begin : block 1 integer i; //hiera. name: top. block 1. i … end initial fork : block 2 reg i; //hierarchical name: top. block 2. i … join endmodule 2005 Verilog HDL 28

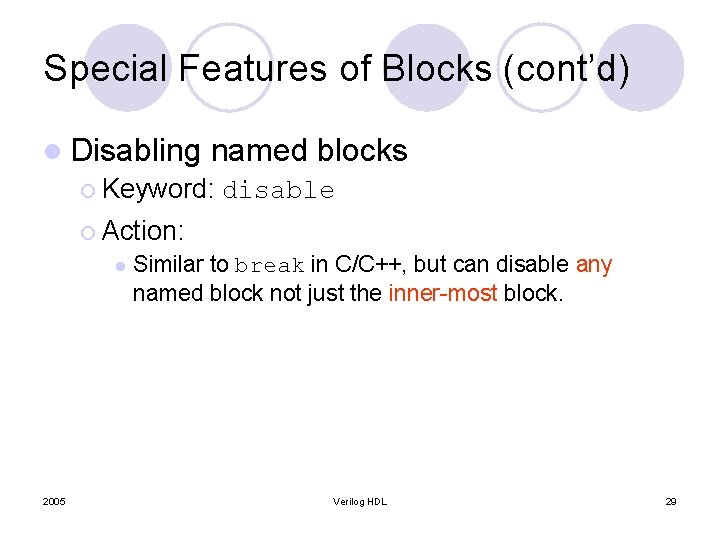

Special Features of Blocks (cont’d) l Disabling named blocks ¡ Keyword: disable ¡ Action: l 2005 Similar to break in C/C++, but can disable any named block not just the inner-most block. Verilog HDL 29

![Special Features of Blocks (cont’d) module find_true_bit; reg [15: 0] flag; integer i; initial Special Features of Blocks (cont’d) module find_true_bit; reg [15: 0] flag; integer i; initial](http://slidetodoc.com/presentation_image_h/c01253c0abd2fb3e55bd5ef834274f69/image-30.jpg)

Special Features of Blocks (cont’d) module find_true_bit; reg [15: 0] flag; integer i; initial begin flag = 16'b 0010_0000_0000; i = 0; begin: block 1 2005 while(i < 16) begin if (flag[i]) begin $display("Encountered TRUE bit at element number %d", i); a disable block 1; end // if i = i + 1; end // while end // block 1 end //initial endmodule Verilog HDL 30

Behavioral Modeling Examples 2005 Verilog HDL

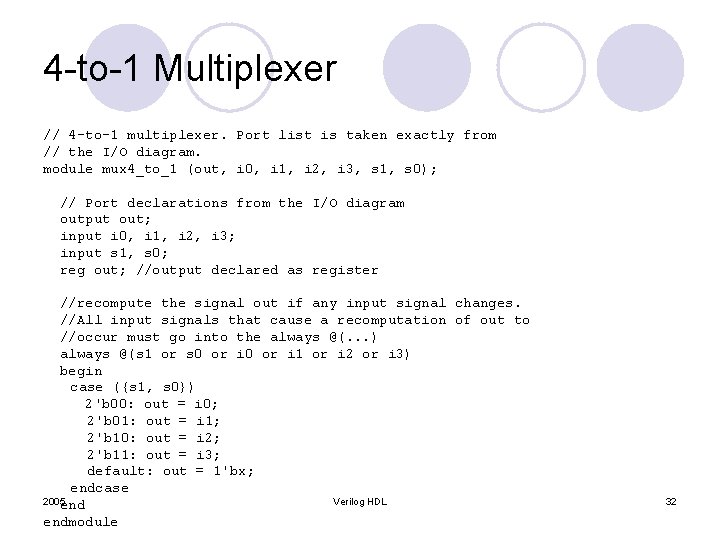

4 -to-1 Multiplexer // 4 -to-1 multiplexer. Port list is taken exactly from // the I/O diagram. module mux 4_to_1 (out, i 0, i 1, i 2, i 3, s 1, s 0); // Port declarations from the I/O diagram output out; input i 0, i 1, i 2, i 3; input s 1, s 0; reg out; //output declared as register //recompute the signal out if any input signal changes. //All input signals that cause a recomputation of out to //occur must go into the always @(. . . ) always @(s 1 or s 0 or i 1 or i 2 or i 3) begin case ({s 1, s 0}) 2'b 00: out = i 0; 2'b 01: out = i 1; 2'b 10: out = i 2; 2'b 11: out = i 3; default: out = 1'bx; endcase 2005 Verilog HDL endmodule 32

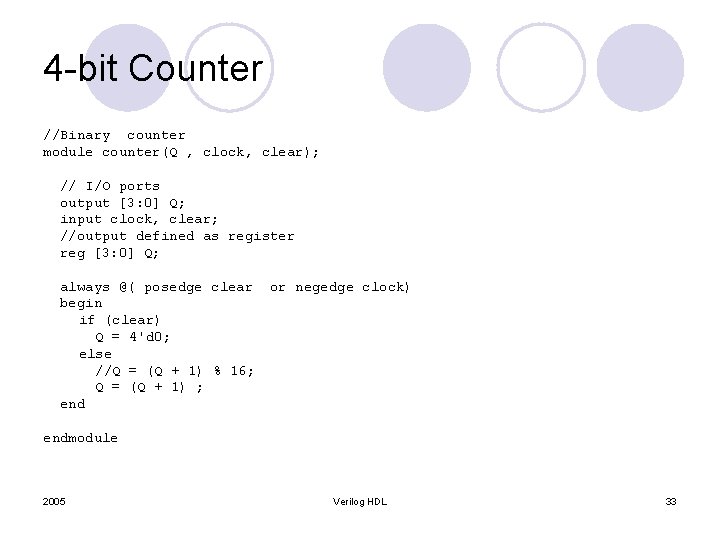

4 -bit Counter //Binary counter module counter(Q , clock, clear); // I/O ports output [3: 0] Q; input clock, clear; //output defined as register reg [3: 0] Q; always @( posedge clear begin if (clear) Q = 4'd 0; else //Q = (Q + 1) % 16; Q = (Q + 1) ; end or negedge clock) endmodule 2005 Verilog HDL 33

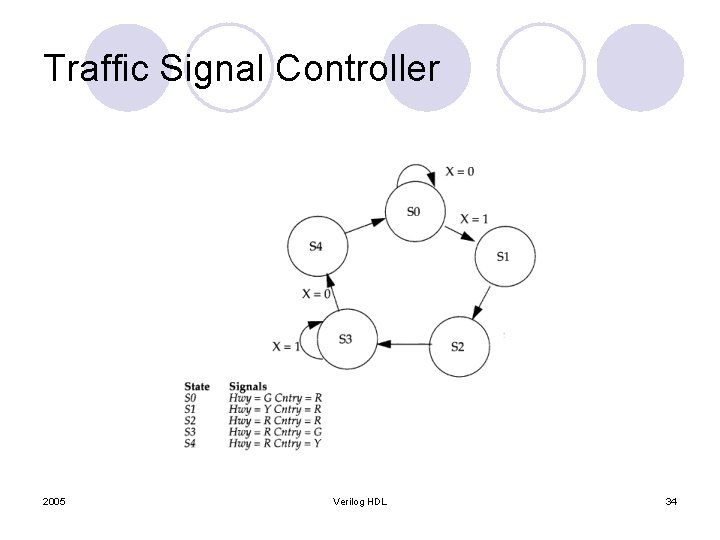

Traffic Signal Controller 2005 Verilog HDL 34

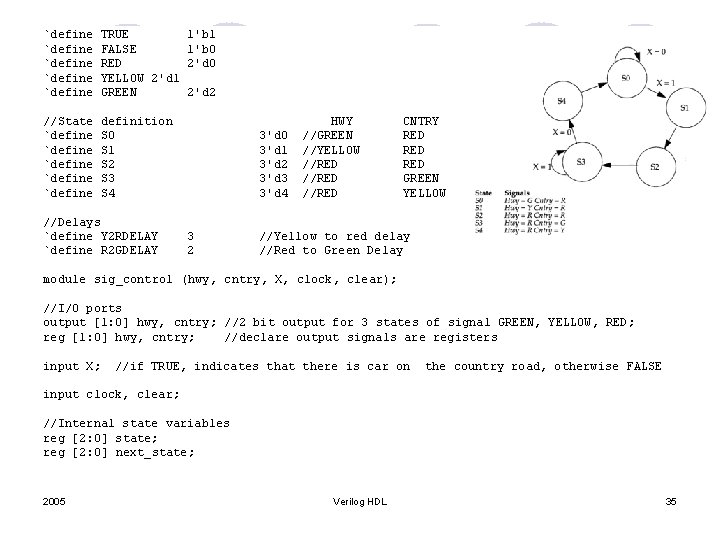

`define `define TRUE 1'b 1 FALSE 1'b 0 RED 2'd 0 YELLOW 2'd 1 GREEN 2'd 2 //State `define `define definition S 0 S 1 S 2 S 3 S 4 //Delays `define Y 2 RDELAY `define R 2 GDELAY 3'd 0 3'd 1 3'd 2 3'd 3 3'd 4 3 2 HWY //GREEN //YELLOW //RED CNTRY RED RED GREEN YELLOW //Yellow to red delay //Red to Green Delay module sig_control (hwy, cntry, X, clock, clear); //I/O ports output [1: 0] hwy, cntry; //2 bit output for 3 states of signal GREEN, YELLOW, RED; reg [1: 0] hwy, cntry; //declare output signals are registers input X; //if TRUE, indicates that there is car on the country road, otherwise FALSE input clock, clear; //Internal state variables reg [2: 0] state; reg [2: 0] next_state; 2005 Verilog HDL 35

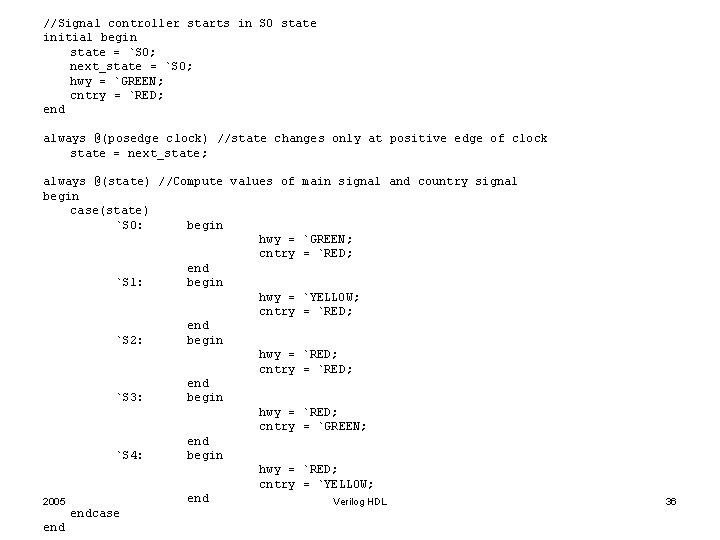

//Signal controller starts in S 0 state initial begin state = `S 0; next_state = `S 0; hwy = `GREEN; cntry = `RED; end always @(posedge clock) //state changes only at positive edge of clock state = next_state; always @(state) //Compute values of begin case(state) `S 0: begin hwy = cntry end `S 1: begin hwy = cntry end `S 2: begin hwy = cntry end `S 3: begin hwy = cntry end `S 4: begin hwy = cntry end 2005 endcase end main signal and country signal `GREEN; = `RED; `YELLOW; = `RED; = `GREEN; `RED; = `YELLOW; Verilog HDL 36

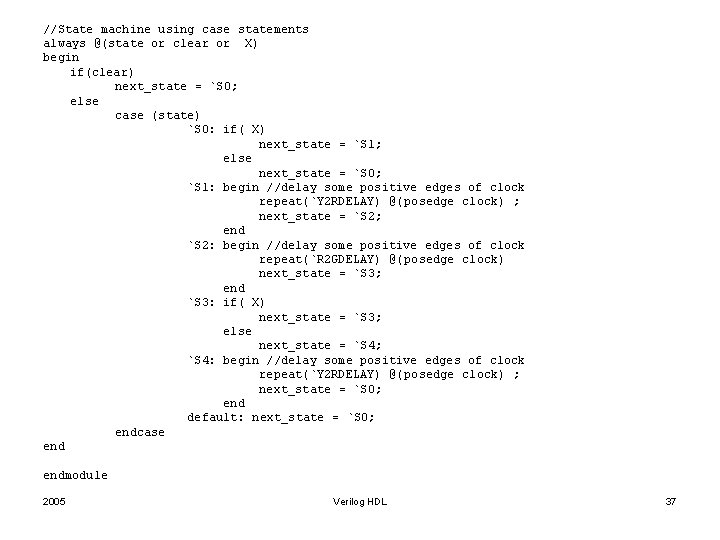

//State machine using case statements always @(state or clear or X) begin if(clear) next_state = `S 0; else case (state) `S 0: if( X) next_state = `S 1; else next_state = `S 0; `S 1: begin //delay some positive edges of clock repeat(`Y 2 RDELAY) @(posedge clock) ; next_state = `S 2; end `S 2: begin //delay some positive edges of clock repeat(`R 2 GDELAY) @(posedge clock) next_state = `S 3; end `S 3: if( X) next_state = `S 3; else next_state = `S 4; `S 4: begin //delay some positive edges of clock repeat(`Y 2 RDELAY) @(posedge clock) ; next_state = `S 0; end default: next_state = `S 0; endcase endmodule 2005 Verilog HDL 37

Today Summary l Timing control in behavioral statements ¡ ¡ Required to advance simulation time Different types l l l Delay-based Event-based Level-sensitive Sequential and Parallel Blocks l Special Features of Blocks l ¡ ¡ ¡ 2005 Nested blocks Named blocks Disabling named blocks Verilog HDL 38

Other Notes l Homework ¡ Chapter 6 7, the remaining exercises (no. 5 -9, 11, 16 -18) ¡ Due date: Next Sunday (Azar 13 th) 2005 Verilog HDL 39

- Slides: 39