Digital System Design Verilog HDL Dataflow Modeling Maziar

![Replication Operator reg A; reg [1: 0] B, C; reg [2: 0] D; A Replication Operator reg A; reg [1: 0] B, C; reg [2: 0] D; A](https://slidetodoc.com/presentation_image_h/84177b99ff38f28d5ae83493904211f3/image-18.jpg)

- Slides: 28

Digital System Design Verilog® HDL Dataflow Modeling Maziar Goudarzi

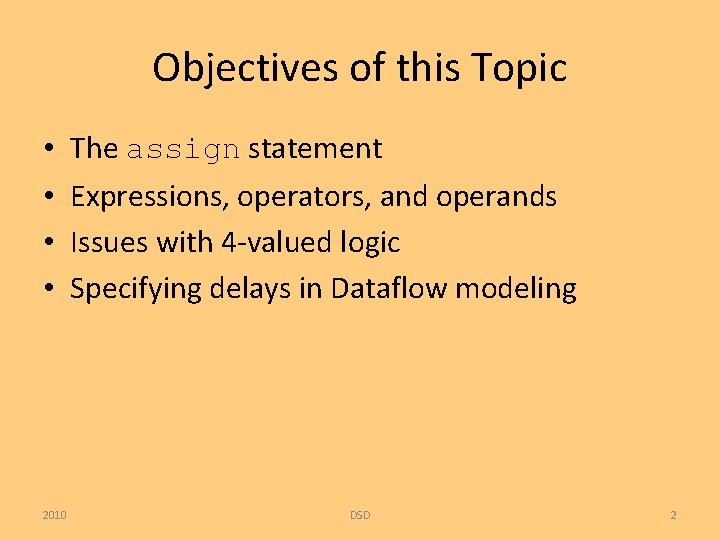

Objectives of this Topic • • 2010 The assign statement Expressions, operators, and operands Issues with 4 -valued logic Specifying delays in Dataflow modeling DSD 2

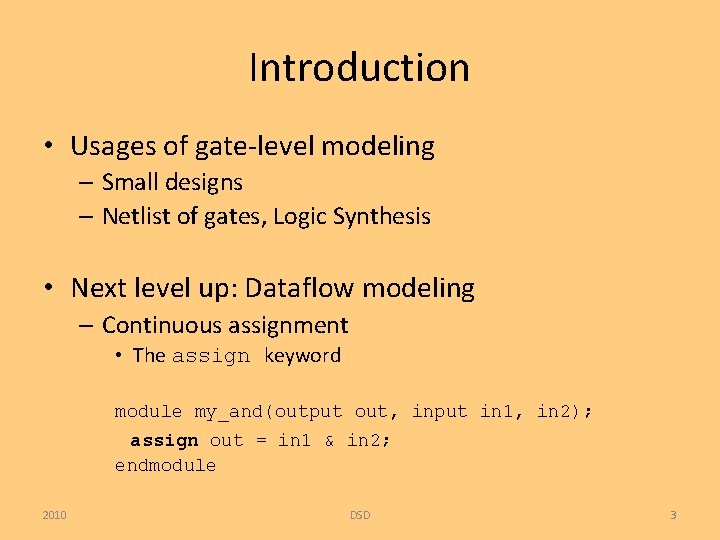

Introduction • Usages of gate-level modeling – Small designs – Netlist of gates, Logic Synthesis • Next level up: Dataflow modeling – Continuous assignment • The assign keyword module my_and(output out, input in 1, in 2); assign out = in 1 & in 2; endmodule 2010 DSD 3

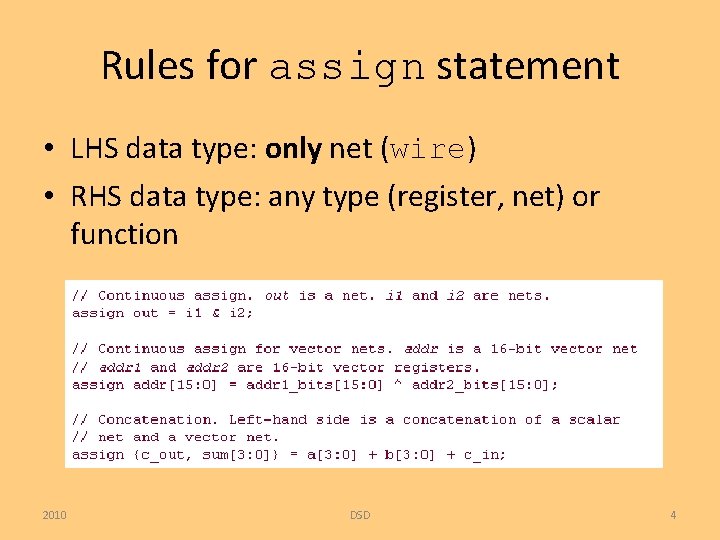

Rules for assign statement • LHS data type: only net (wire) • RHS data type: any type (register, net) or function 2010 DSD 4

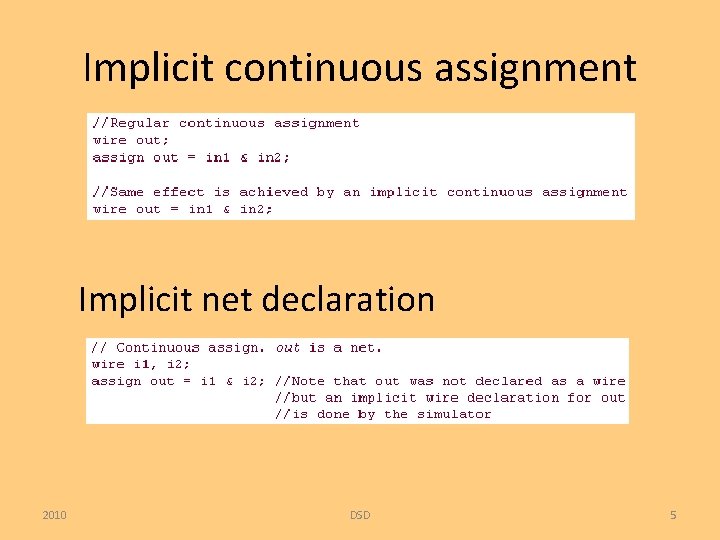

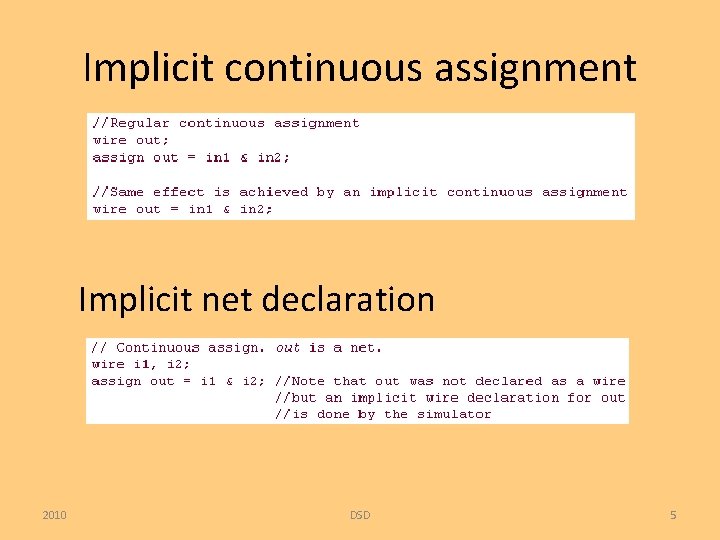

Implicit continuous assignment Implicit net declaration 2010 DSD 5

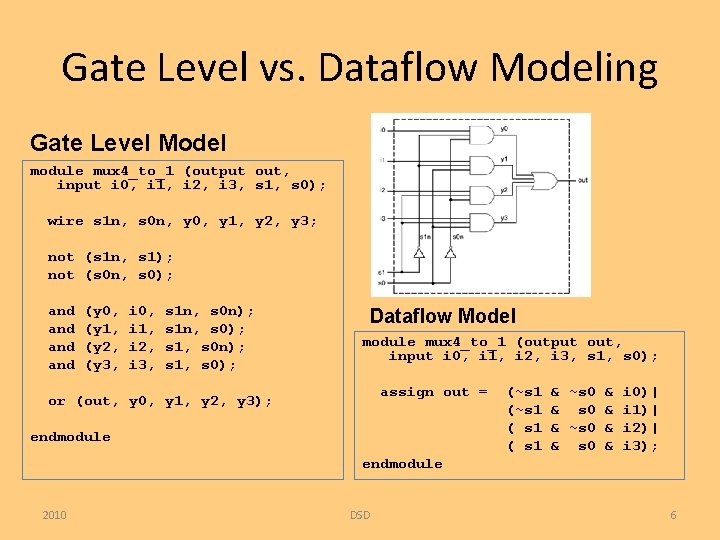

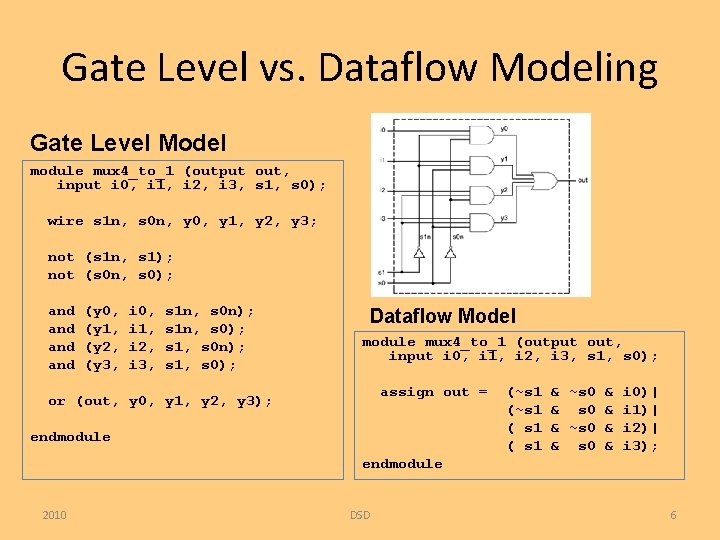

Gate Level vs. Dataflow Modeling Gate Level Model module mux 4_to_1 (output out, input i 0, i 1, i 2, i 3, s 1, s 0); wire s 1 n, s 0 n, y 0, y 1, y 2, y 3; not (s 1 n, s 1); not (s 0 n, s 0); and and (y 0, (y 1, (y 2, (y 3, i 0, i 1, i 2, i 3, s 1 n, s 0 n); s 1 n, s 0); s 1, s 0 n); s 1, s 0); Dataflow Model module mux 4_to_1 (output out, input i 0, i 1, i 2, i 3, s 1, s 0); assign out = or (out, y 0, y 1, y 2, y 3); endmodule (~s 1 ( s 1 & ~s 0 & i 0)| & s 0 & i 1)| & ~s 0 & i 2)| & s 0 & i 3); endmodule 2010 DSD 6

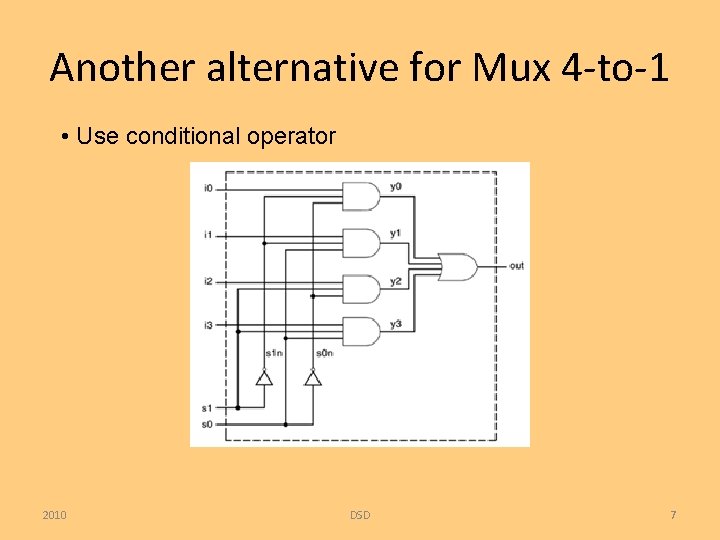

Another alternative for Mux 4 -to-1 • Use conditional operator 2010 DSD 7

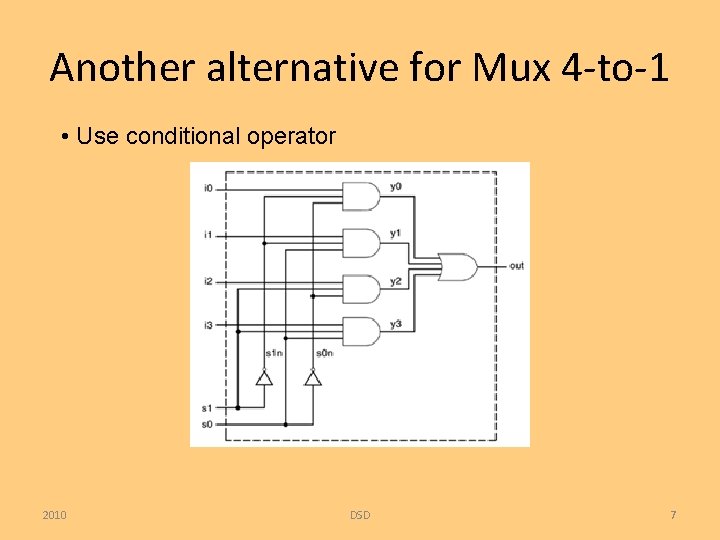

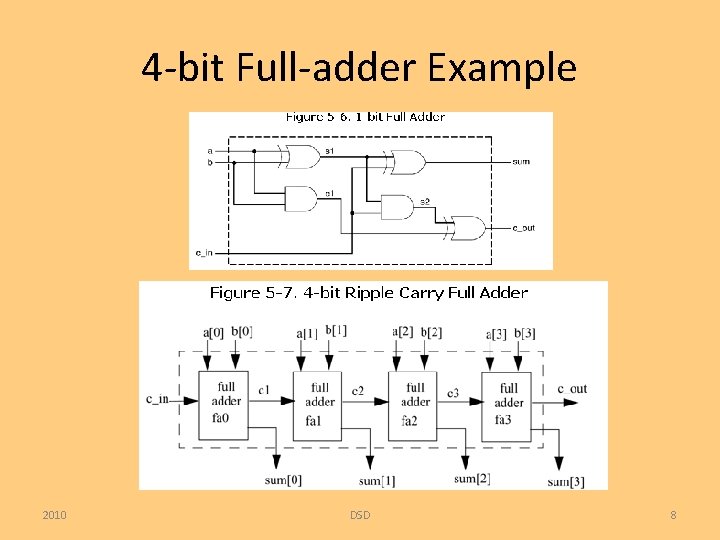

4 -bit Full-adder Example 2010 DSD 8

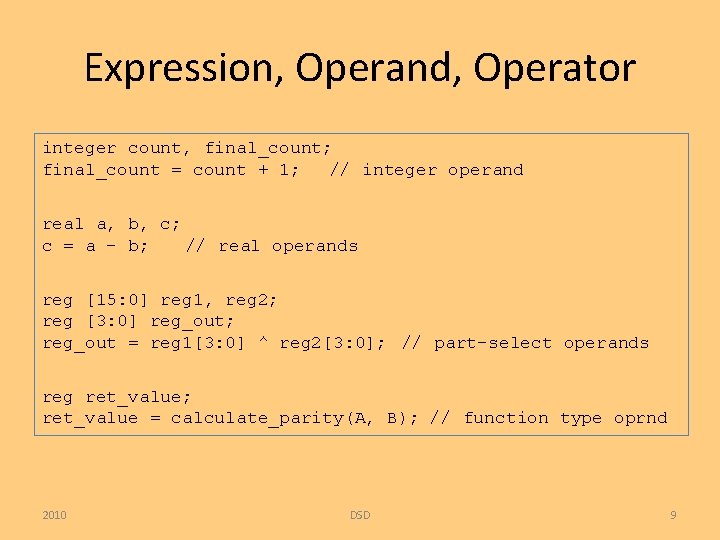

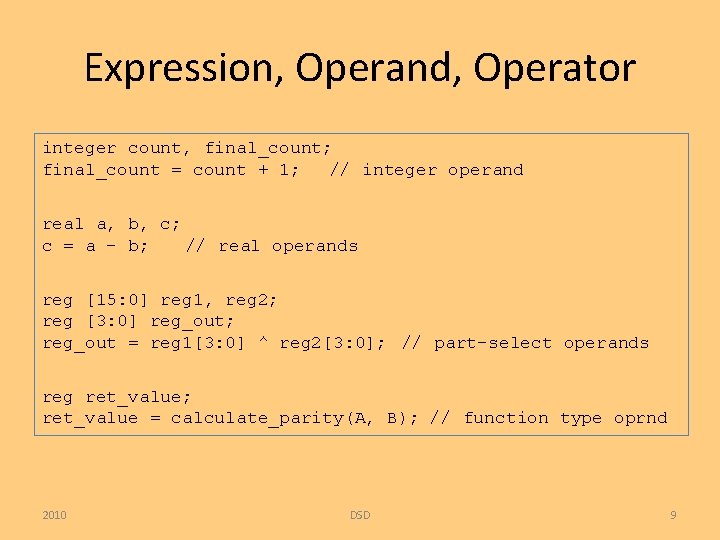

Expression, Operand, Operator integer count, final_count; final_count = count + 1; // integer operand real a, b, c; c = a - b; // real operands reg [15: 0] reg 1, reg 2; reg [3: 0] reg_out; reg_out = reg 1[3: 0] ^ reg 2[3: 0]; // part-select operands reg ret_value; ret_value = calculate_parity(A, B); // function type oprnd 2010 DSD 9

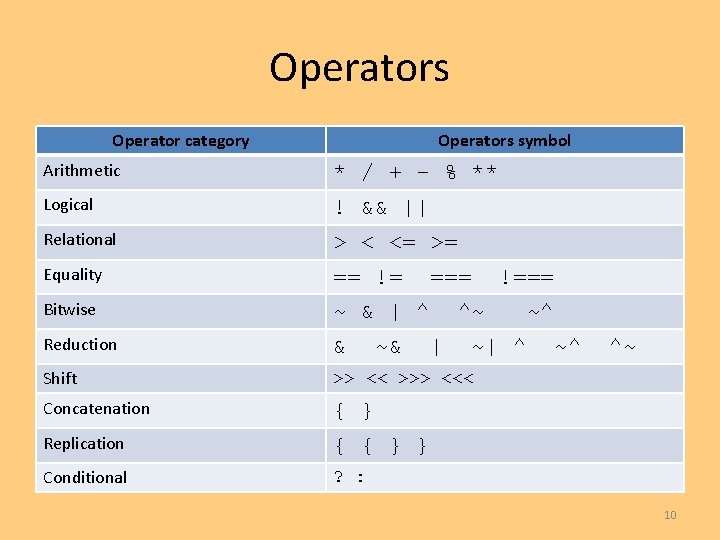

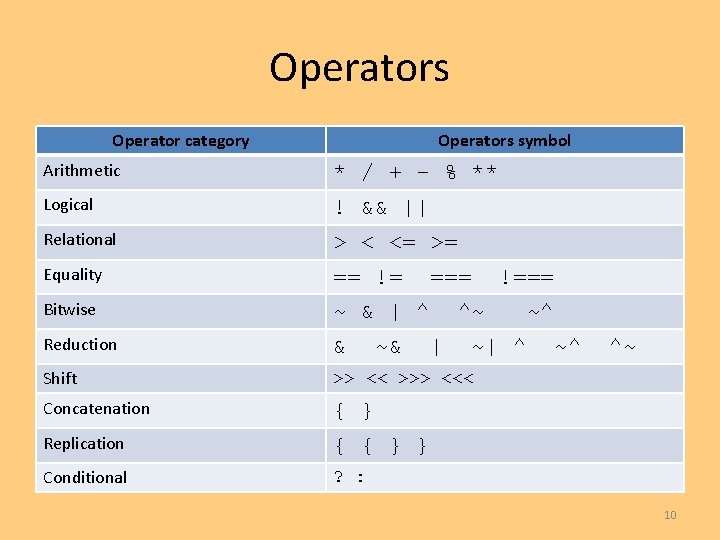

Operators Operator category Operators symbol Arithmetic * / + - % ** Logical ! && || Relational > < <= >= Equality == != Bitwise ~ & | ^ Reduction & Shift >> << >>> <<< Concatenation { } Replication { { } } Conditional ? : === !=== ~& ^~ | ~| ^ ~^ ~^ ^~ 10

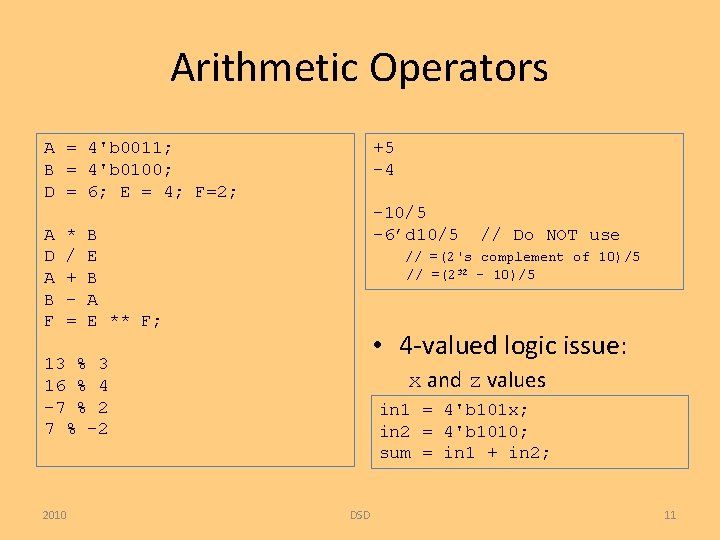

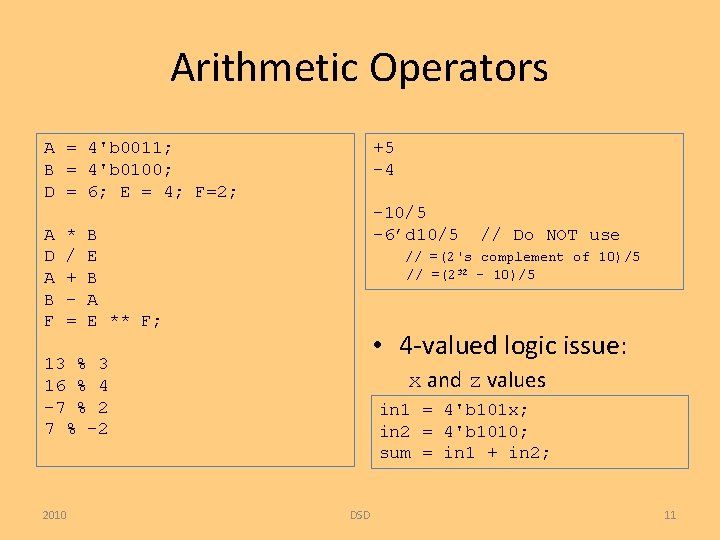

Arithmetic Operators A = 4'b 0011; B = 4'b 0100; D = 6; E = 4; F=2; A D A B F * / + = +5 -4 -10/5 -6’d 10/5 B E B A E ** F; // =(2's complement of 10)/5 // =(232 - 10)/5 • 4 -valued logic issue: 13 % 3 16 % 4 -7 % 2 7 % -2 2010 // Do NOT use x and z values in 1 = 4'b 101 x; in 2 = 4'b 1010; sum = in 1 + in 2; DSD 11

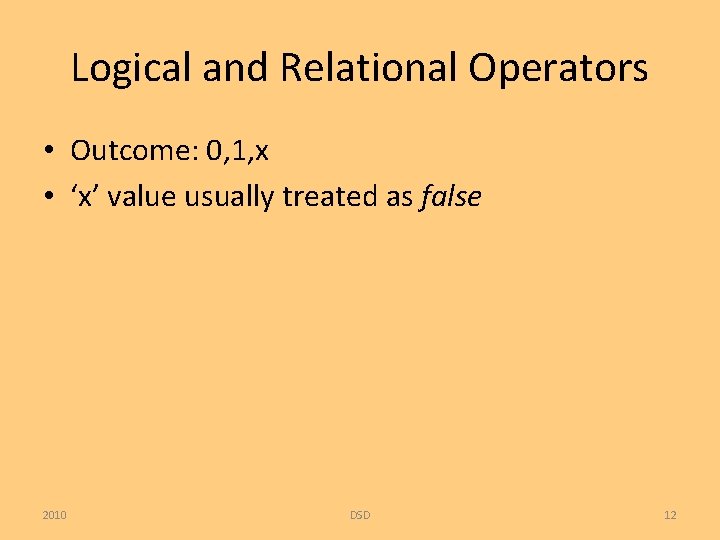

Logical and Relational Operators • Outcome: 0, 1, x • ‘x’ value usually treated as false 2010 DSD 12

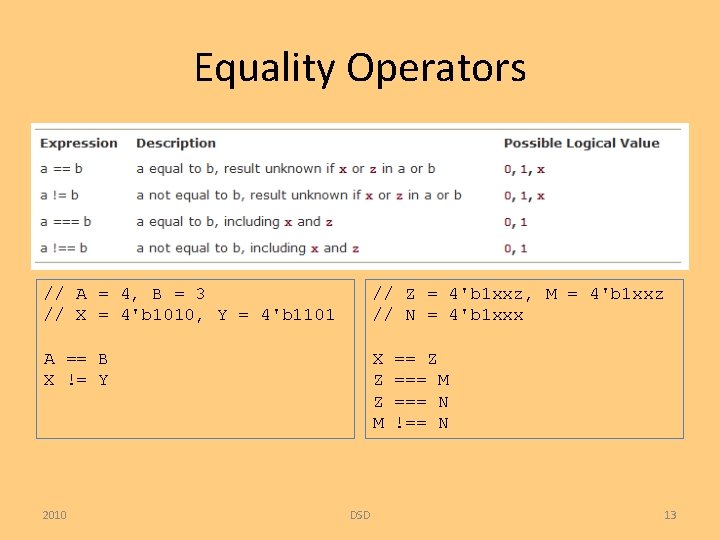

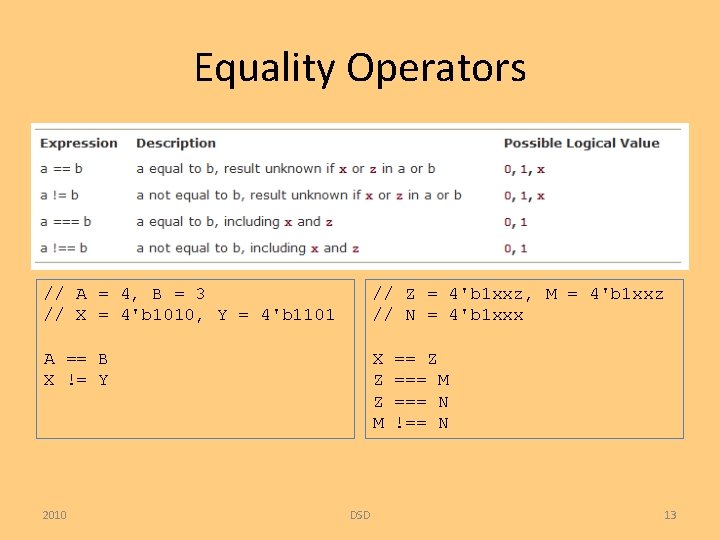

Equality Operators // A = 4, B = 3 // X = 4'b 1010, Y = 4'b 1101 // Z = 4'b 1 xxz, M = 4'b 1 xxz // N = 4'b 1 xxx A == B X != Y X Z Z M 2010 DSD == Z === M === N !== N 13

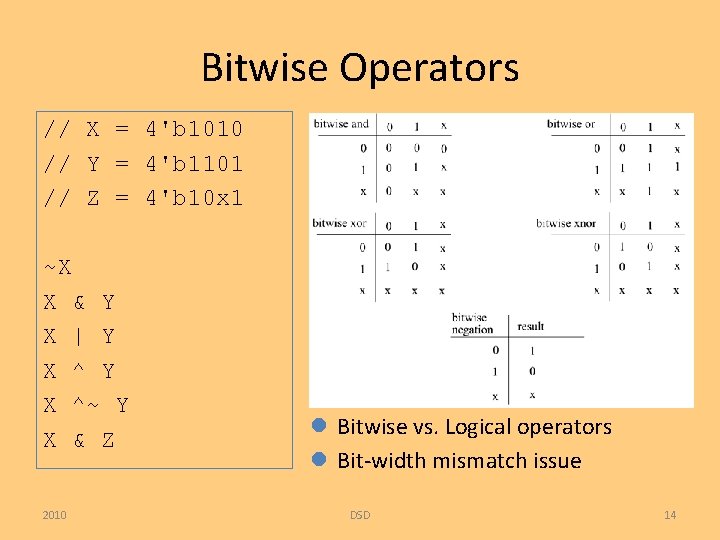

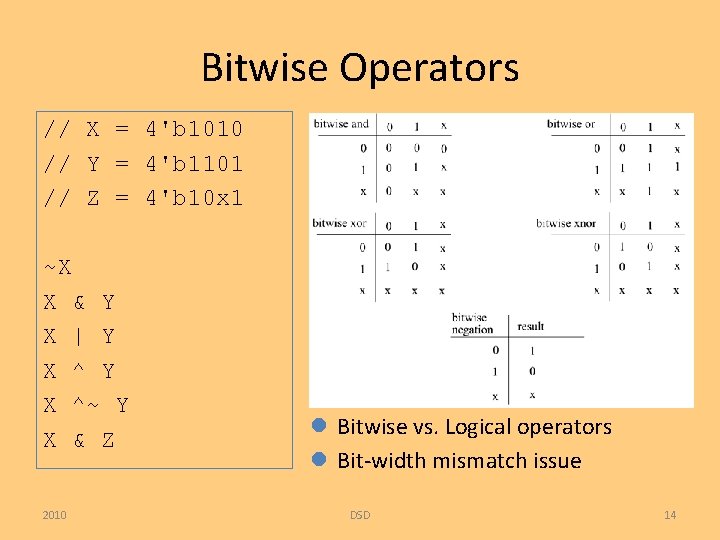

Bitwise Operators // X = 4'b 1010 // Y = 4'b 1101 // Z = 4'b 10 x 1 ~X X & Y X | Y X ^~ Y X & Z 2010 l Bitwise vs. Logical operators l Bit-width mismatch issue DSD 14

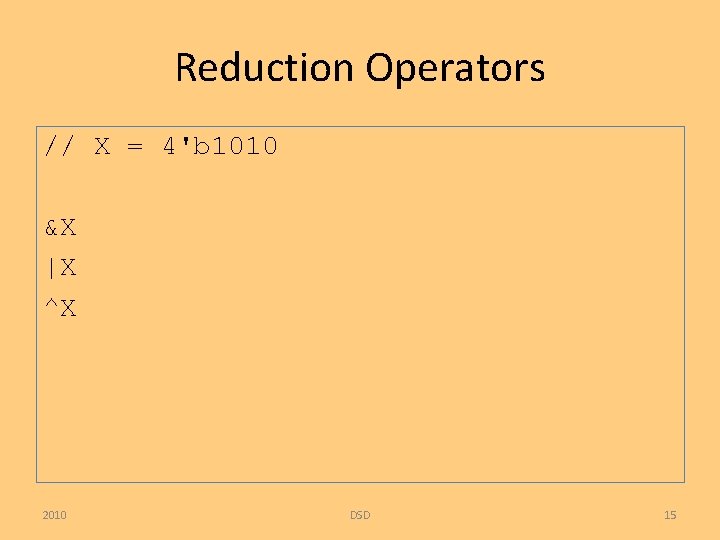

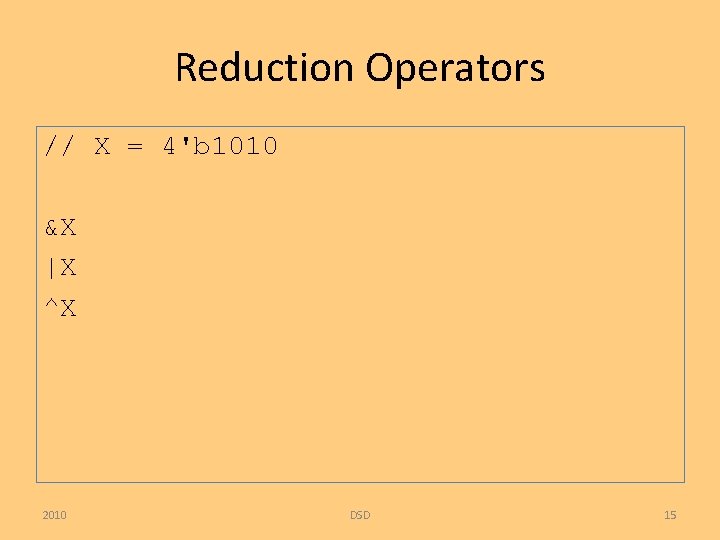

Reduction Operators // X = 4'b 1010 &X |X ^X 2010 DSD 15

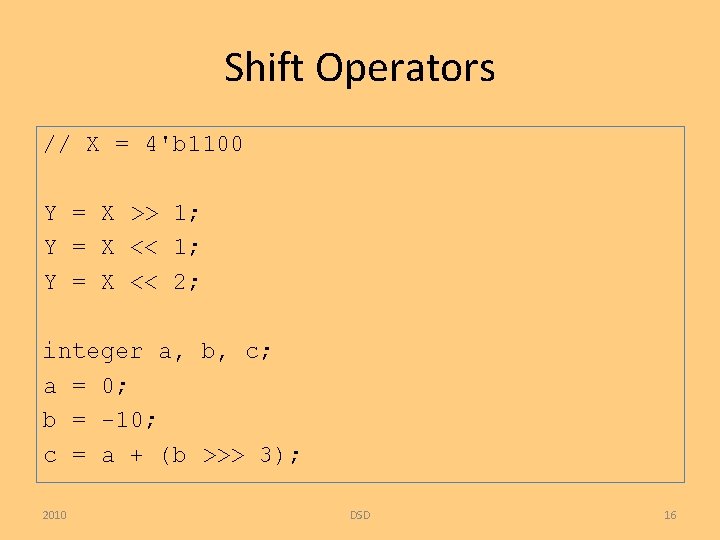

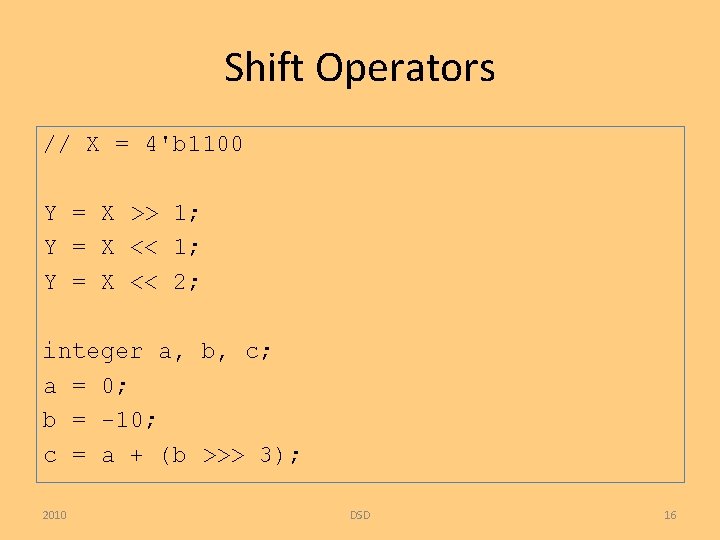

Shift Operators // X = 4'b 1100 Y = X >> 1; Y = X << 2; integer a, b, c; a = 0; b = -10; c = a + (b >>> 3); 2010 DSD 16

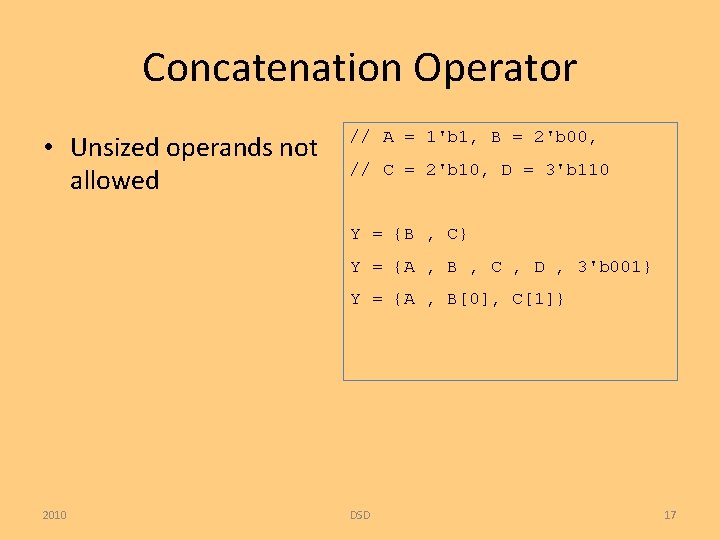

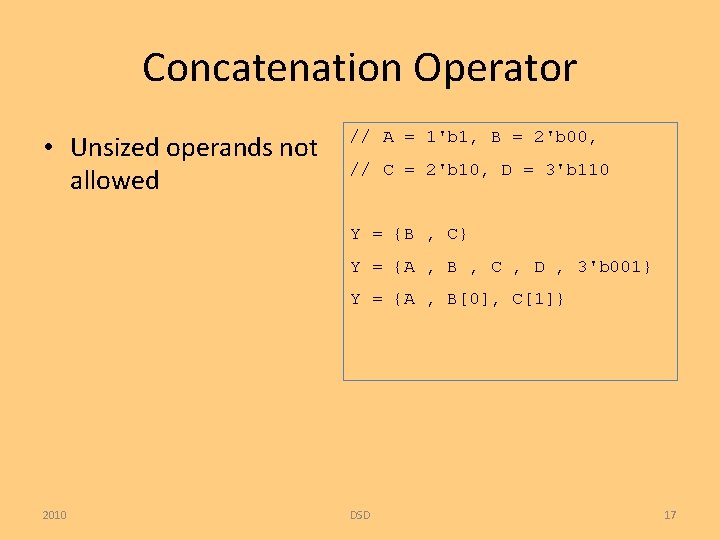

Concatenation Operator • Unsized operands not allowed // A = 1'b 1, B = 2'b 00, // C = 2'b 10, D = 3'b 110 Y = {B , C} Y = {A , B , C , D , 3'b 001} Y = {A , B[0], C[1]} 2010 DSD 17

![Replication Operator reg A reg 1 0 B C reg 2 0 D A Replication Operator reg A; reg [1: 0] B, C; reg [2: 0] D; A](https://slidetodoc.com/presentation_image_h/84177b99ff38f28d5ae83493904211f3/image-18.jpg)

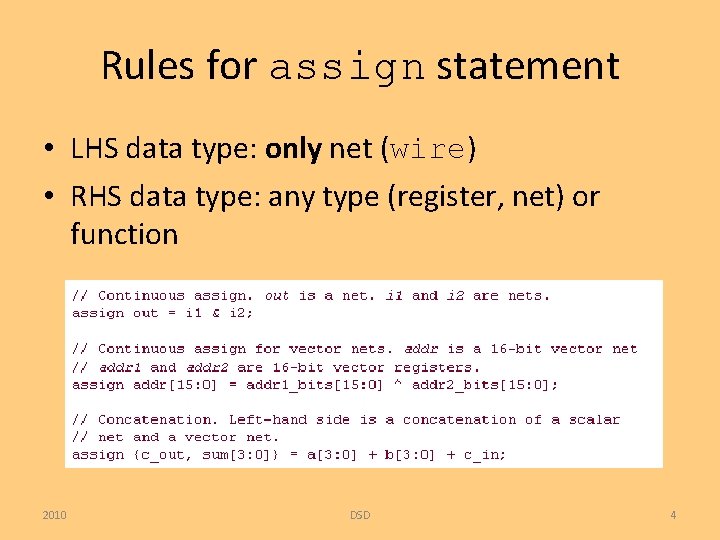

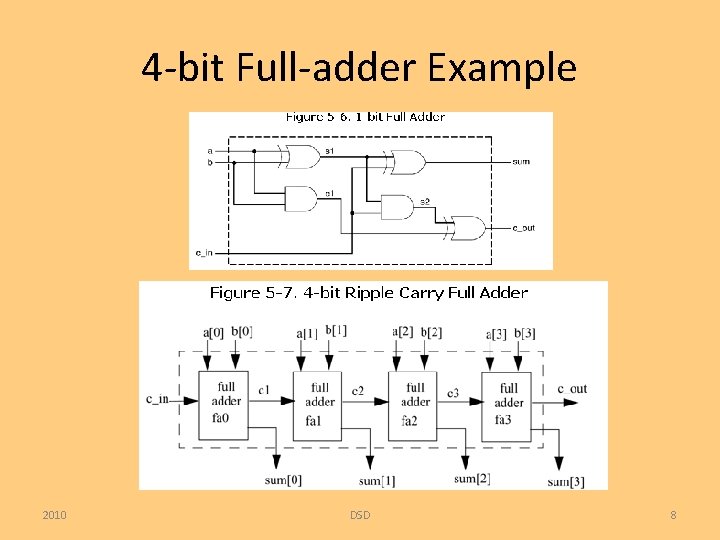

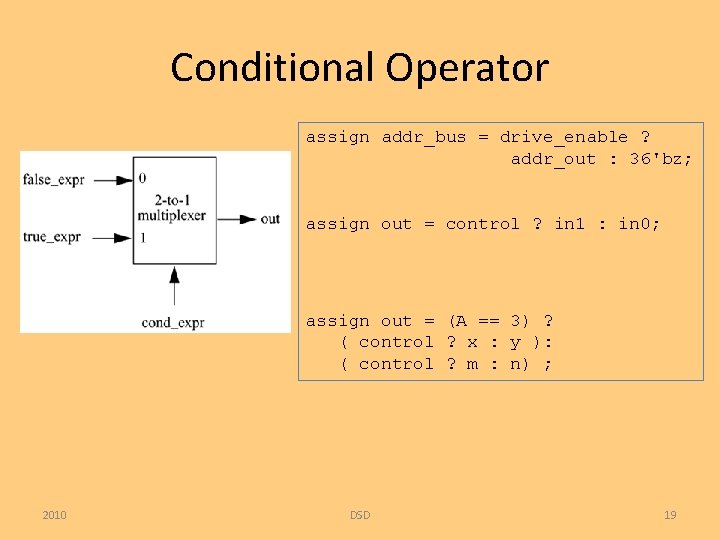

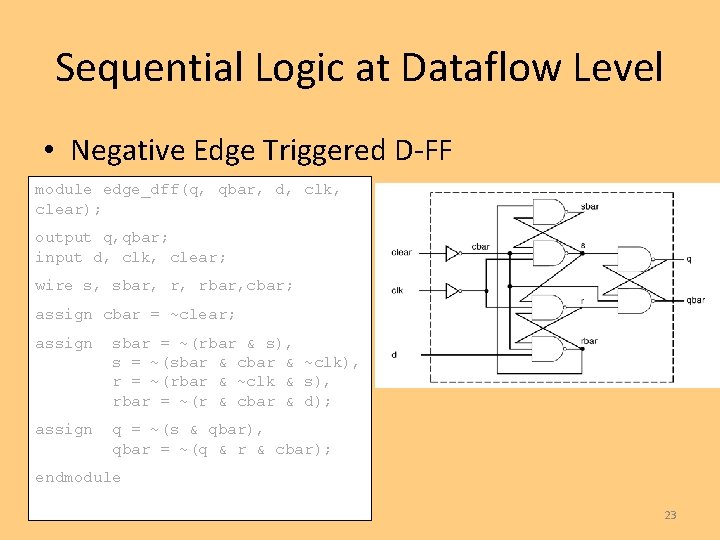

Replication Operator reg A; reg [1: 0] B, C; reg [2: 0] D; A B C D = = 1'b 1; 2'b 00; 2'b 10; 3'b 110; Y = { 4{A} } Y = { 4{A} , 2{B} , C } 2010 DSD 18

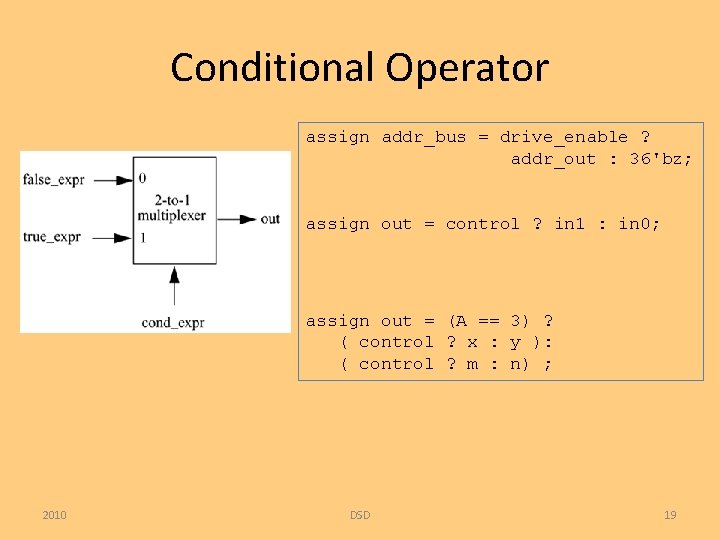

Conditional Operator assign addr_bus = drive_enable ? addr_out : 36'bz; assign out = control ? in 1 : in 0; assign out = (A == 3) ? ( control ? x : y ): ( control ? m : n) ; 2010 DSD 19

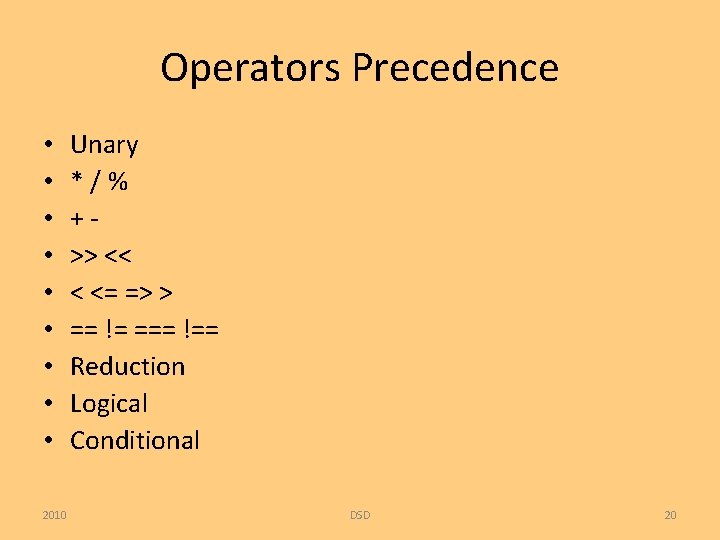

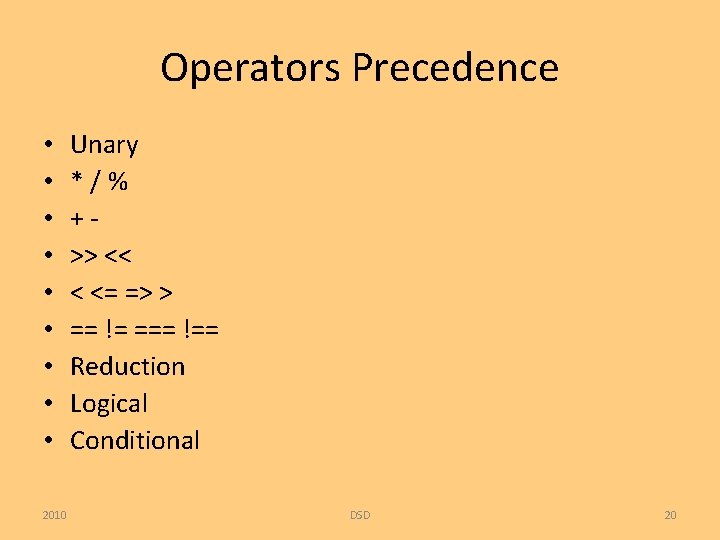

Operators Precedence • • • 2010 Unary */% +>> << < <= => > == != === !== Reduction Logical Conditional DSD 20

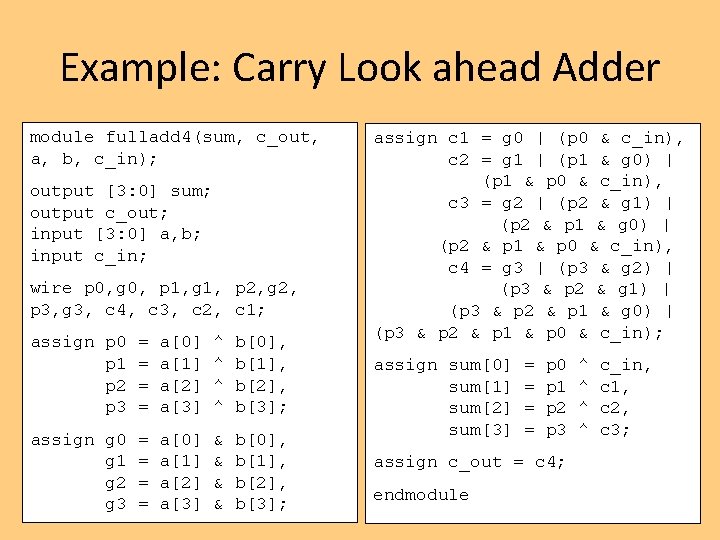

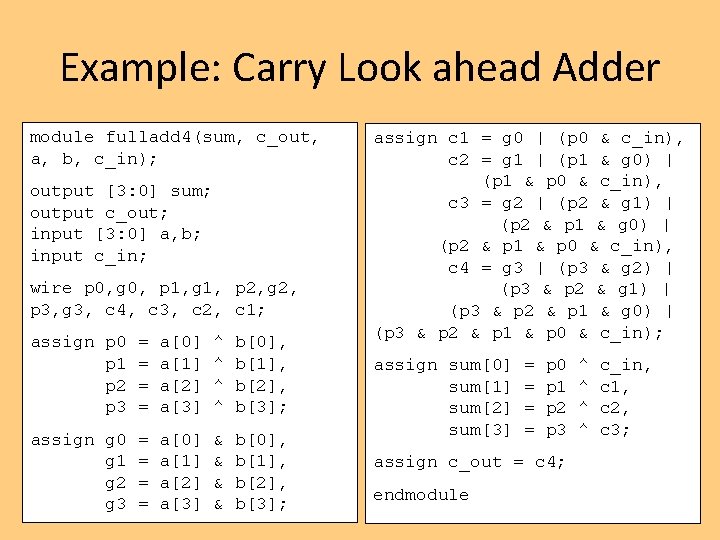

Example: Carry Look ahead Adder module fulladd 4(sum, c_out, a, b, c_in); output [3: 0] sum; output c_out; input [3: 0] a, b; input c_in; wire p 0, g 0, p 1, g 1, p 2, g 2, p 3, g 3, c 4, c 3, c 2, c 1; assign p 0 p 1 p 2 p 3 = = a[0] a[1] a[2] a[3] ^ ^ b[0], b[1], b[2], b[3]; assign g 0 g 1 g 2 g 3 = = a[0] a[1] a[2] a[3] & & b[0], b[1], b[2], b[3]; 2010 assign c 1 = g 0 | (p 0 & c_in), c 2 = g 1 | (p 1 & g 0) | (p 1 & p 0 & c_in), c 3 = g 2 | (p 2 & g 1) | (p 2 & p 1 & g 0) | (p 2 & p 1 & p 0 & c_in), c 4 = g 3 | (p 3 & g 2) | (p 3 & p 2 & g 1) | (p 3 & p 2 & p 1 & g 0) | (p 3 & p 2 & p 1 & p 0 & c_in); assign sum[0] sum[1] sum[2] sum[3] = = p 0 p 1 p 2 p 3 ^ ^ c_in, c 1, c 2, c 3; assign c_out = c 4; endmodule 21

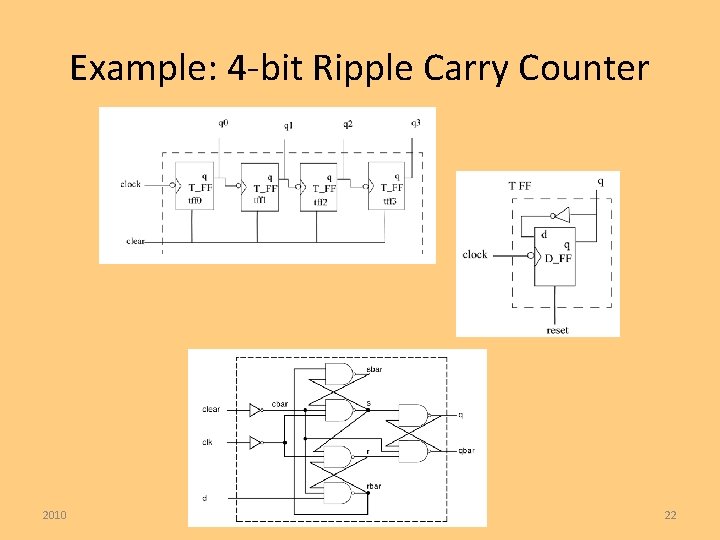

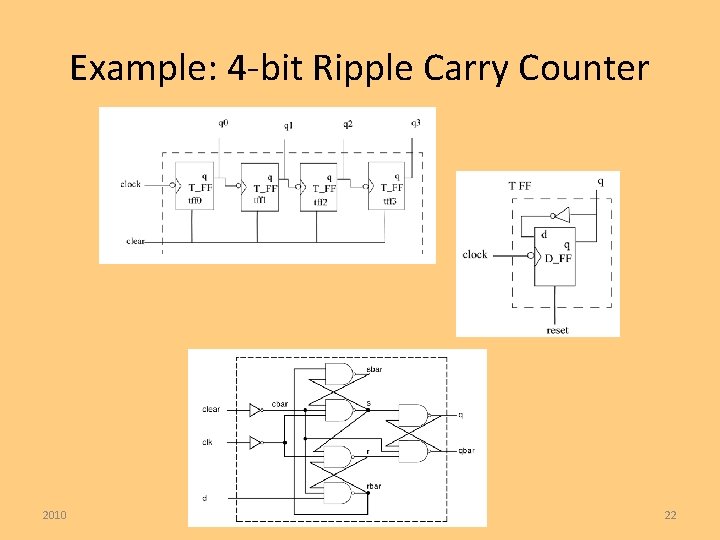

Example: 4 -bit Ripple Carry Counter 2010 DSD 22

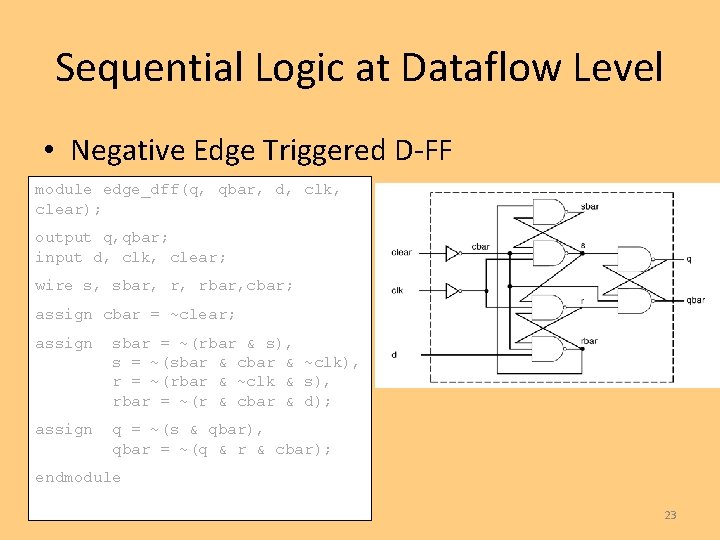

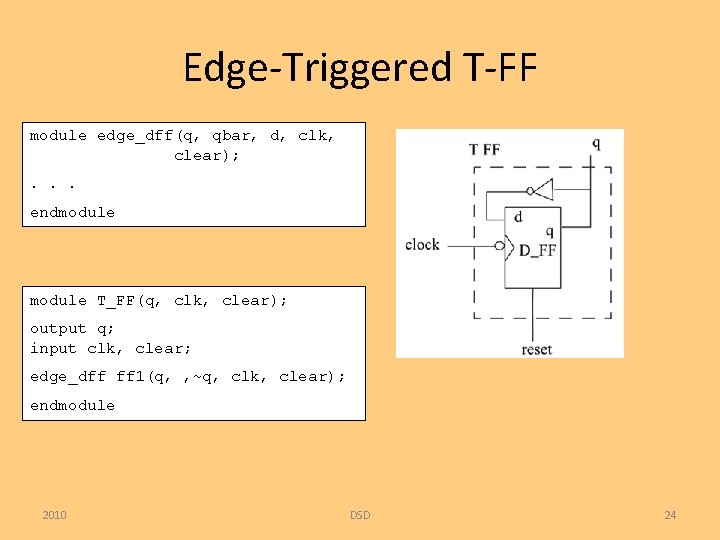

Sequential Logic at Dataflow Level • Negative Edge Triggered D-FF module edge_dff(q, qbar, d, clk, clear); output q, qbar; input d, clk, clear; wire s, sbar, r, rbar, cbar; assign cbar = ~clear; assign sbar = ~(rbar & s), s = ~(sbar & cbar & ~clk), r = ~(rbar & ~clk & s), rbar = ~(r & cbar & d); assign q = ~(s & qbar), qbar = ~(q & r & cbar); endmodule 2010 DSD 23

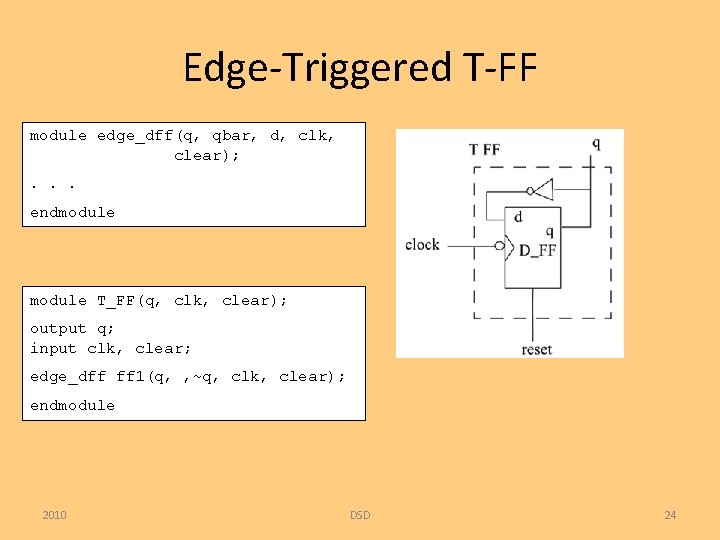

Edge-Triggered T-FF module edge_dff(q, qbar, d, clk, clear); . . . endmodule T_FF(q, clk, clear); output q; input clk, clear; edge_dff ff 1(q, , ~q, clk, clear); endmodule 2010 DSD 24

Design by Truth Table 2010 DSD 25

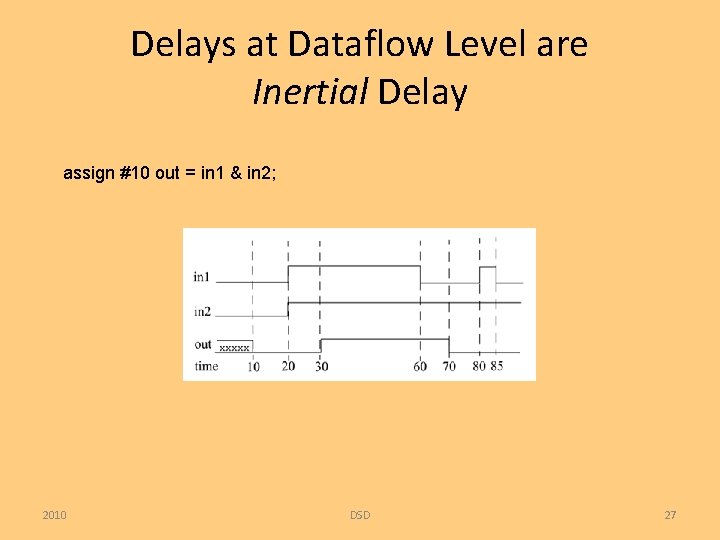

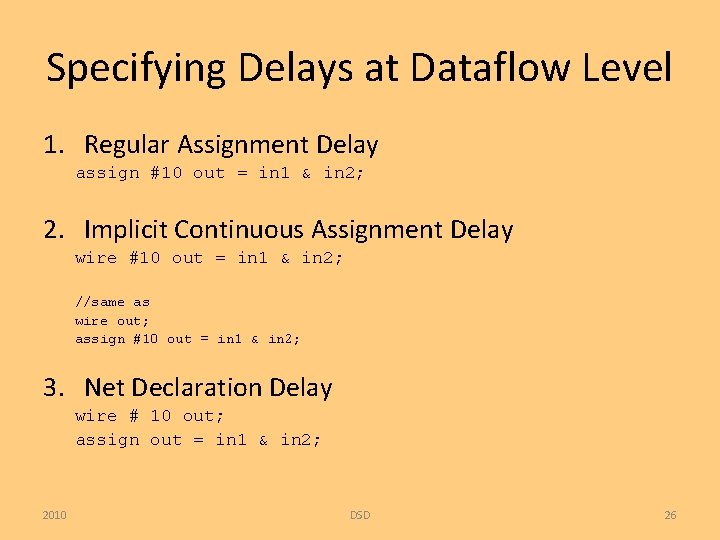

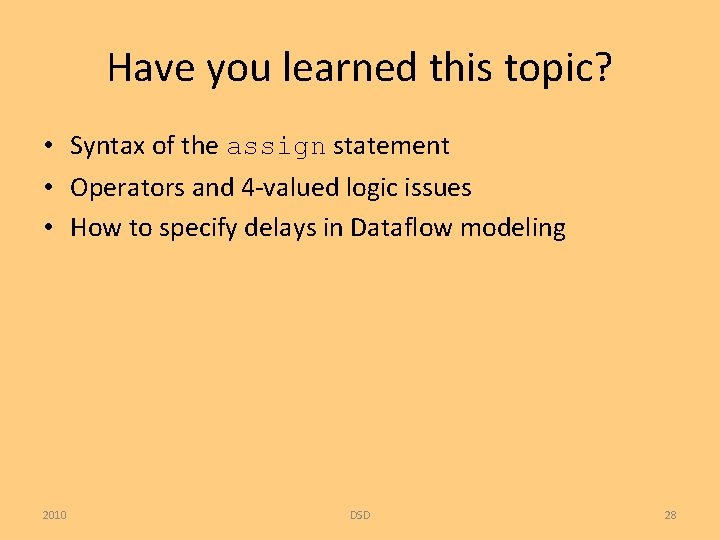

Specifying Delays at Dataflow Level 1. Regular Assignment Delay assign #10 out = in 1 & in 2; 2. Implicit Continuous Assignment Delay wire #10 out = in 1 & in 2; //same as wire out; assign #10 out = in 1 & in 2; 3. Net Declaration Delay wire # 10 out; assign out = in 1 & in 2; 2010 DSD 26

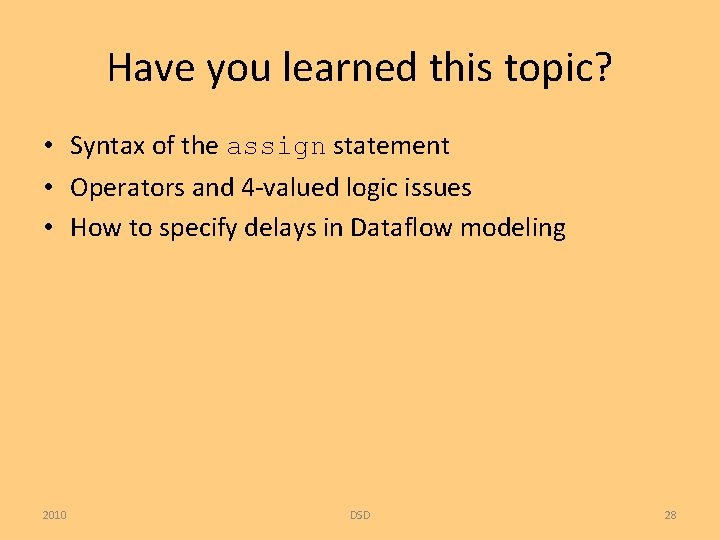

Delays at Dataflow Level are Inertial Delay assign #10 out = in 1 & in 2; 2010 DSD 27

Have you learned this topic? • Syntax of the assign statement • Operators and 4 -valued logic issues • How to specify delays in Dataflow modeling 2010 DSD 28