Sequential Hardware God created the integers all else

![Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC] Read Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC] Read](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-11.jpg)

![Stage Computation: popl r. A icode: ifun M 1[PC] Read instruction byte r. A: Stage Computation: popl r. A icode: ifun M 1[PC] Read instruction byte r. A:](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-15.jpg)

![Stage Computation: Jumps j. XX Dest Fetch icode: ifun M 1[PC] Read instruction byte Stage Computation: Jumps j. XX Dest Fetch icode: ifun M 1[PC] Read instruction byte](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-17.jpg)

![Stage Computation: call Dest icode: ifun M 1[PC] Read instruction byte val. C M Stage Computation: call Dest icode: ifun M 1[PC] Read instruction byte val. C M](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-19.jpg)

![Stage Computation: ret icode: ifun M 1[PC] Read instruction byte val. A R[%esp] Read Stage Computation: ret icode: ifun M 1[PC] Read instruction byte val. A R[%esp] Read](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-21.jpg)

![Review: Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC] Review: Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC]](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-23.jpg)

![A Source Decode OPl r. A, r. B val. A R[r. A] Read operand A Source Decode OPl r. A, r. B val. A R[r. A] Read operand](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-33.jpg)

![E Destination OPl r. A, r. B Write-back R[r. B] val. E Write back E Destination OPl r. A, r. B Write-back R[r. B] val. E Write back](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-34.jpg)

- Slides: 53

Sequential Hardware “God created the integers, all else is the work of man” Leopold Kronecker (He believed in the reduction of all mathematics to arguments involving only the integers and a finite number of steps) (link)

Review: Building Blocks fun ¢ Combinational logic § Compute Boolean functions of inputs § Continuously respond to input changes § Operate on data and implement A = A L U B 0 MUX control 1 ¢ Storage elements § § Store bits Addressable memories Non-addressable registers Loaded only as clock rises val. A src. A A Register file val. B src. B B val. W W dst. W Clock

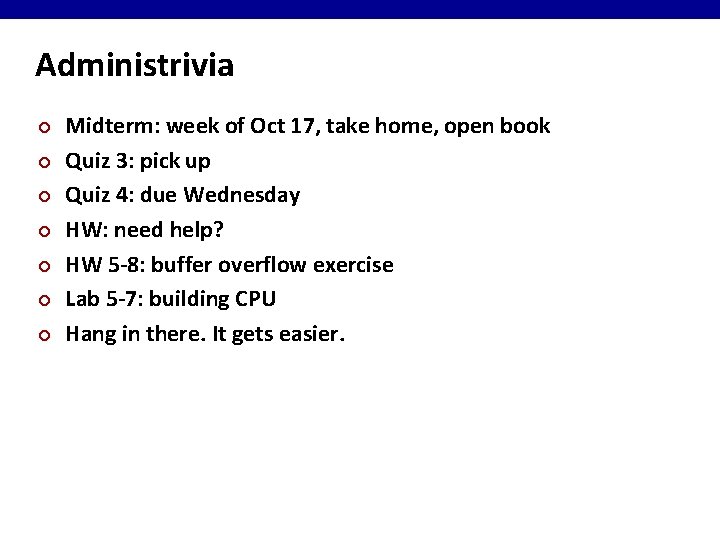

Administrivia ¢ ¢ ¢ ¢ Midterm: week of Oct 17, take home, open book Quiz 3: pick up Quiz 4: due Wednesday HW: need help? HW 5 -8: buffer overflow exercise Lab 5 -7: building CPU Hang in there. It gets easier.

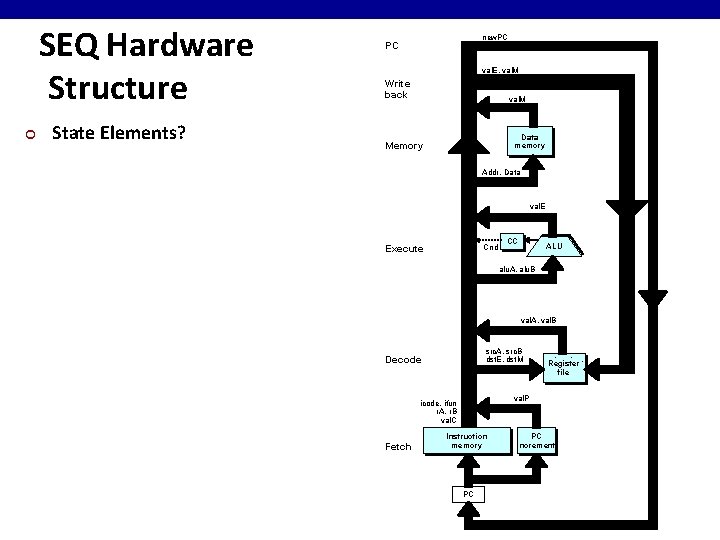

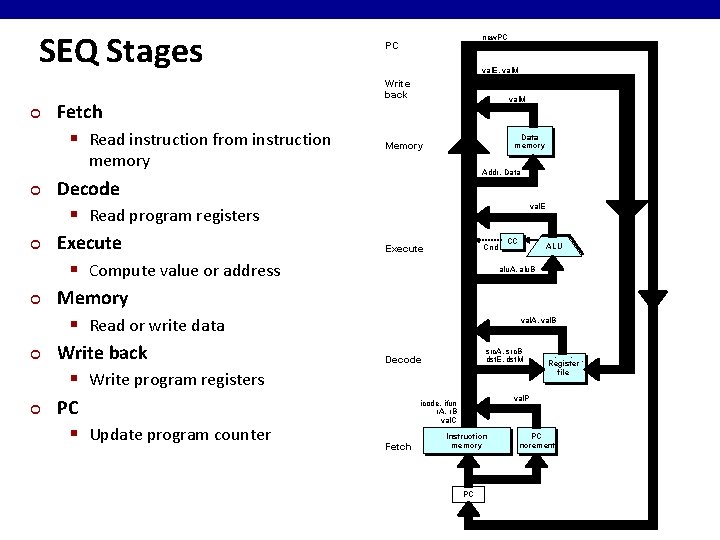

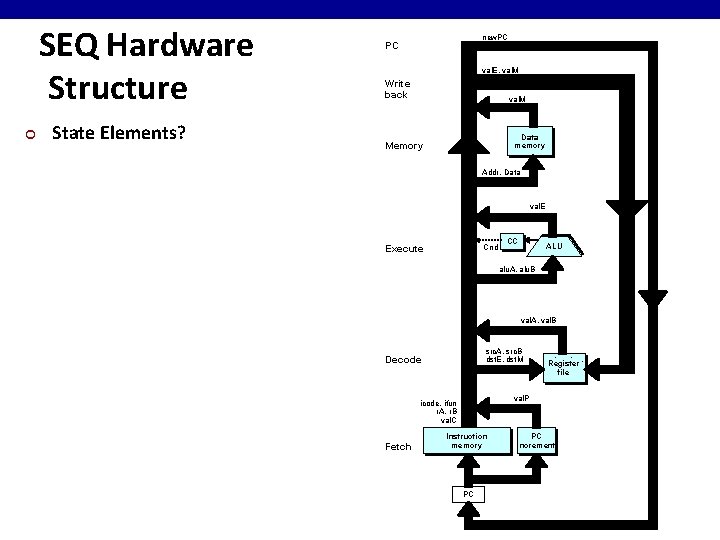

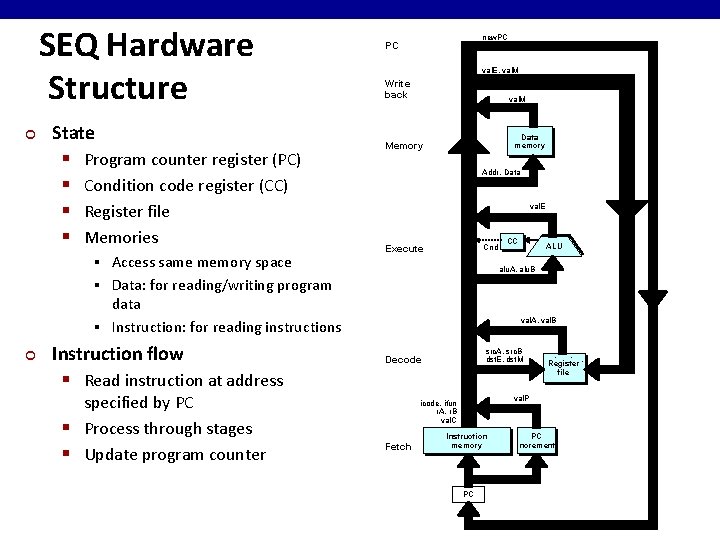

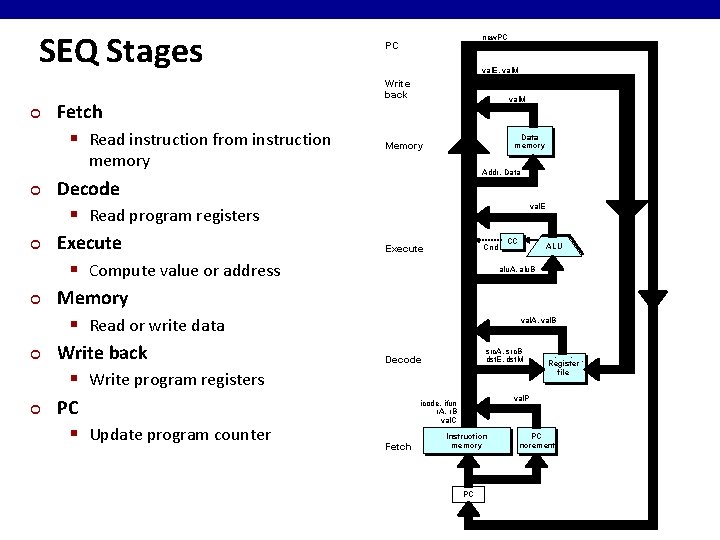

SEQ Hardware Structure ¢ State Elements? new. PC PC val. E, val. M Write back val. M Data memory Memory Addr, Data val. E Cnd Execute CC ALU alu. A, alu. B val. A, val. B src. A, src. B dst. E, dst. M Decode val. P icode, ifun r. A, r. B val. C Fetch A Instruction memory PC B Register file PC increment M E

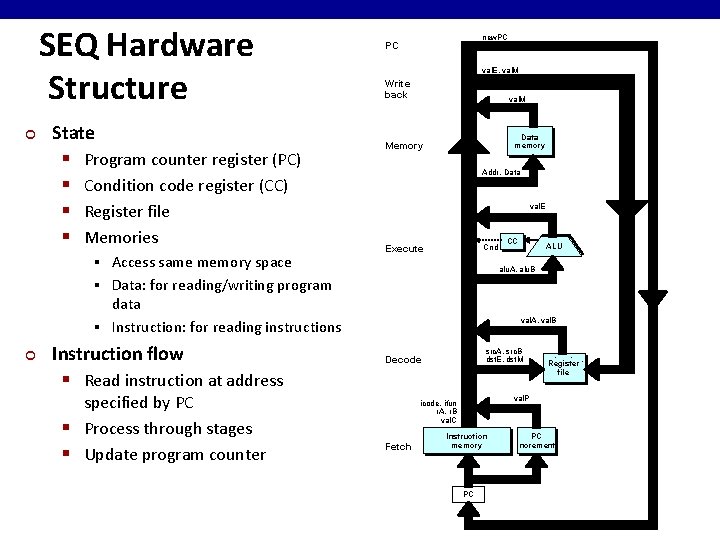

SEQ Hardware Structure ¢ State § Program counter register (PC) § Condition code register (CC) § Register file § Memories Access same memory space § Data: for reading/writing program data § Instruction: for reading instructions new. PC PC val. E, val. M Write back val. M Data memory Memory Addr, Data val. E Cnd Execute § ¢ Instruction flow § Read instruction at address specified by PC § Process through stages § Update program counter CC ALU alu. A, alu. B val. A, val. B src. A, src. B dst. E, dst. M Decode val. P icode, ifun r. A, r. B val. C Fetch A Instruction memory PC B Register file PC increment M E

SEQ Stages ¢ Fetch § Read instruction from instruction memory ¢ ¢ ¢ Decode § Read program registers Execute § Compute value or address Memory § Read or write data Write back § Write program registers PC § Update program counter new. PC PC val. E, val. M Write back val. M Data memory Memory Addr, Data val. E Cnd Execute CC ALU alu. A, alu. B val. A, val. B src. A, src. B dst. E, dst. M Decode val. P icode, ifun r. A, r. B val. C Fetch A Instruction memory PC B Register file PC increment M E

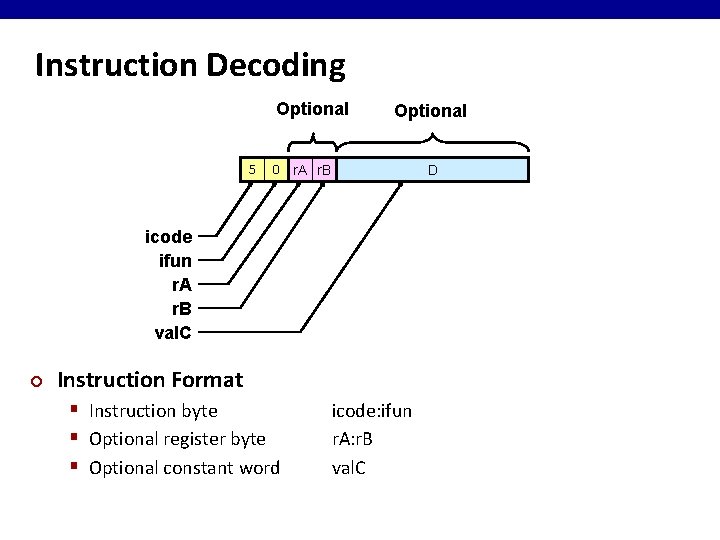

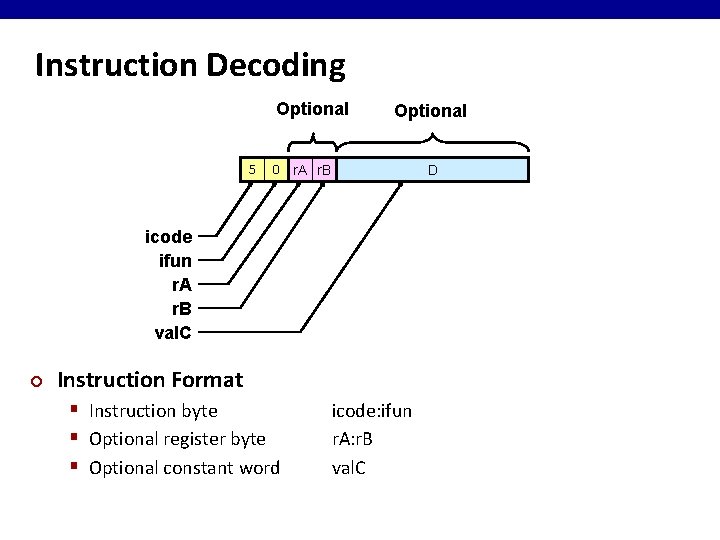

Instruction Decoding Optional 5 Optional 0 r. A r. B D icode ifun r. A r. B val. C ¢ Instruction Format § Instruction byte § Optional register byte § Optional constant word icode: ifun r. A: r. B val. C

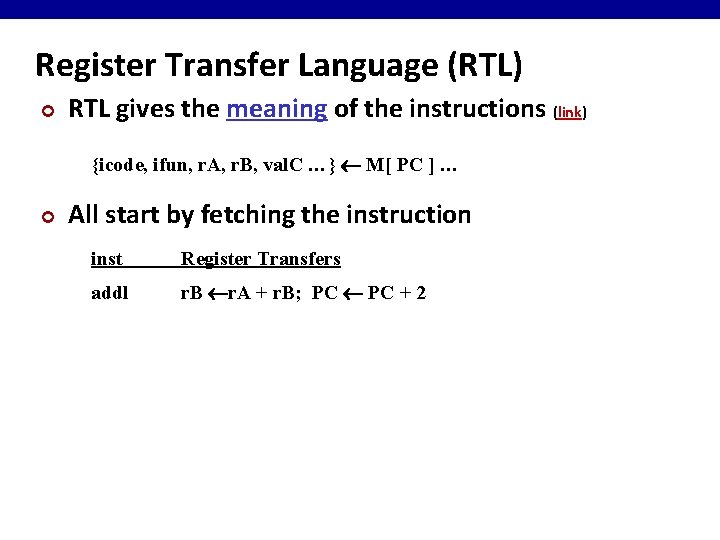

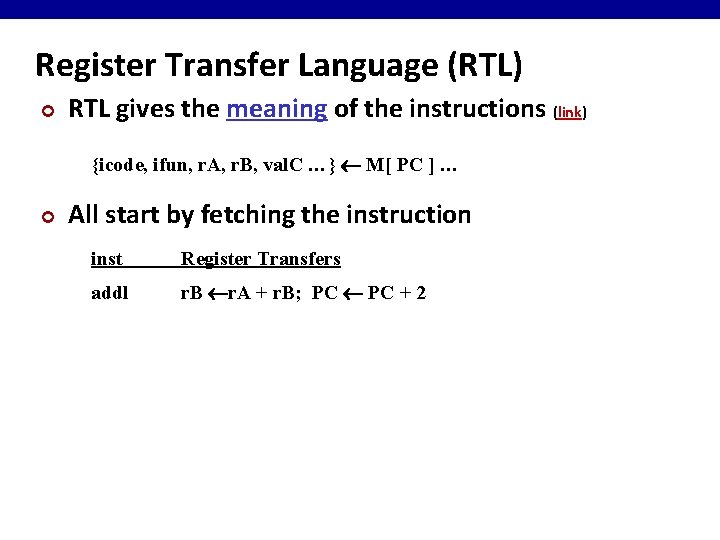

Register Transfer Language (RTL) ¢ RTL gives the meaning of the instructions (link) {icode, ifun, r. A, r. B, val. C …} M[ PC ] … ¢ All start by fetching the instruction inst Register Transfers addl r. B r. A + r. B; PC + 2

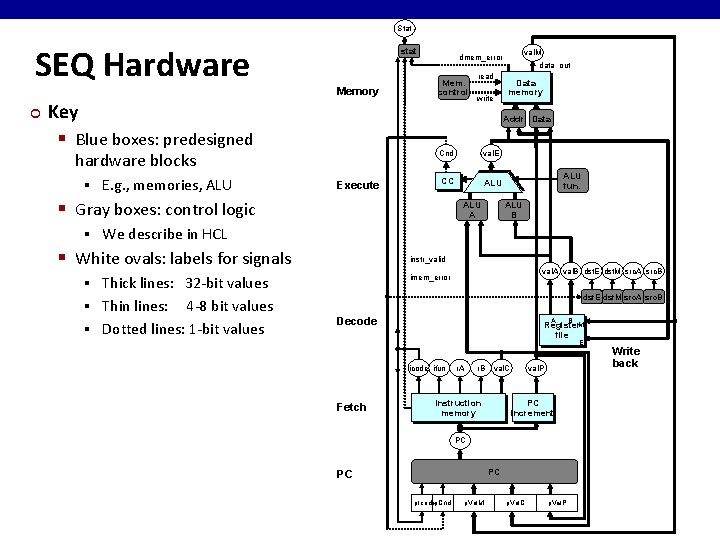

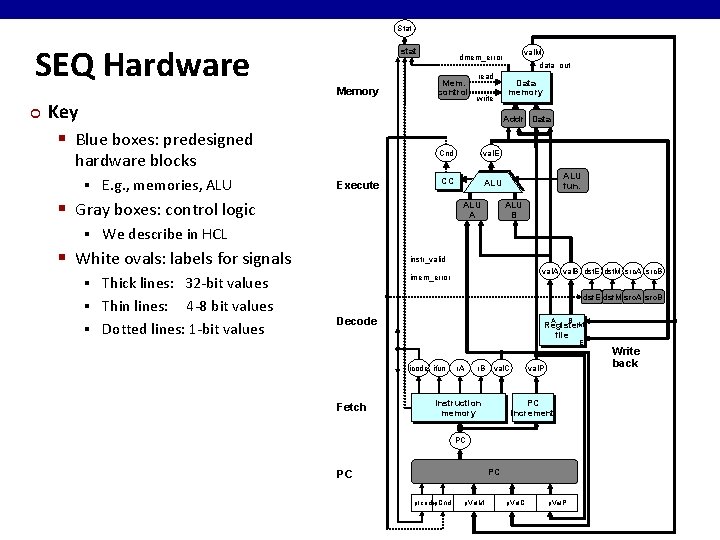

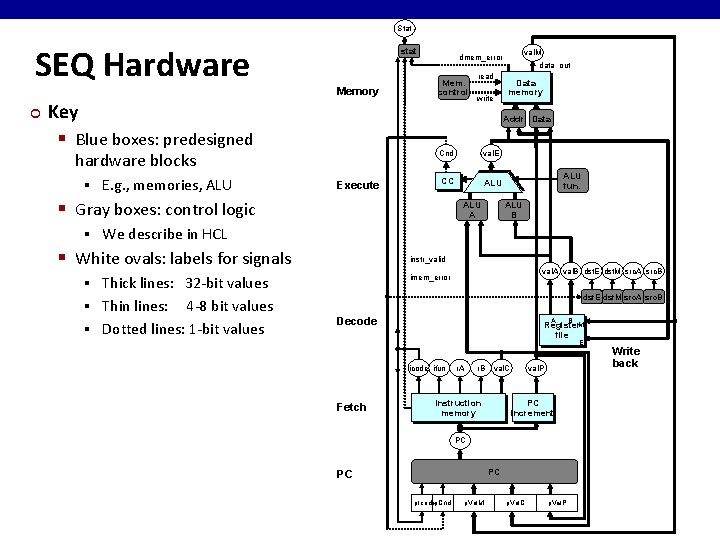

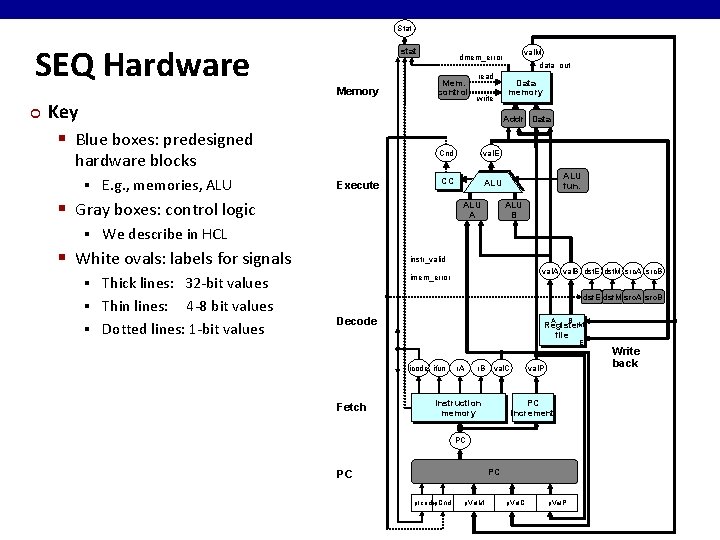

Stat SEQ Hardware ¢ stat Memory Key § Blue boxes: predesigned E. g. , memories, ALU Mem. control write Execute Cnd val. E CC ALU § Gray boxes: control logic § read data out Data memory Addr Data hardware blocks § val. M dmem_error ALU A ALU fun. ALU B We describe in HCL § White ovals: labels for signals Thick lines: 32 -bit values § Thin lines: 4 -8 bit values § Dotted lines: 1 -bit values instr_valid val. A val. B dst. E dst. M src. A src. B imem_error § dst. E dst. M src. A src. B Decode A B Register. M file E icode ifun Fetch r. A r. B val. C Instruction memory val. P PC increment PC PC PC p. Icodep. Cnd p. Val. M p. Val. C p. Val. P Write back

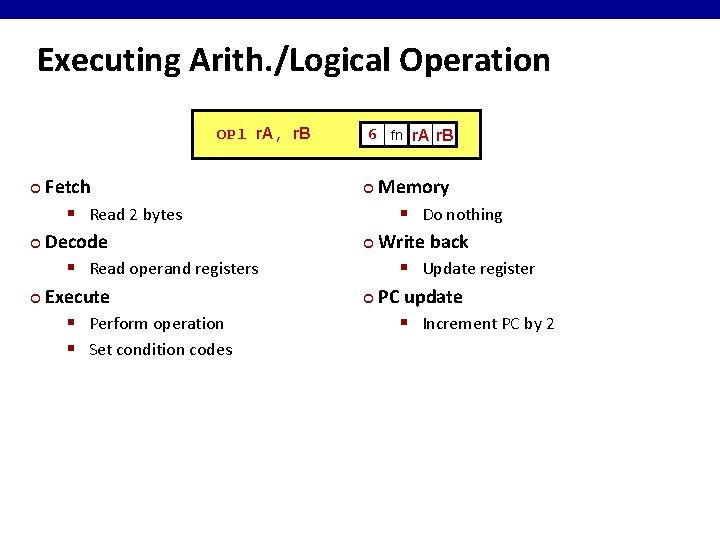

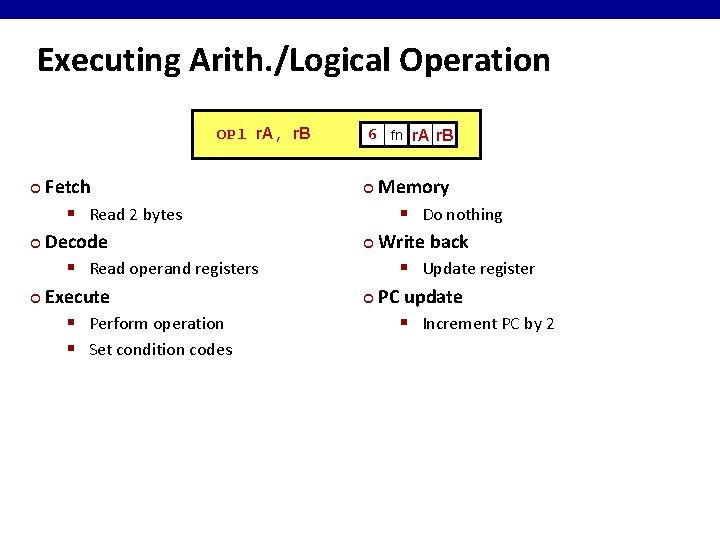

Executing Arith. /Logical Operation OPl r. A, r. B Fetch § Read 2 bytes ¢ Decode § Read operand registers ¢ Execute § Perform operation § Set condition codes ¢ 6 fn r. A r. B Memory § Do nothing ¢ Write back § Update register ¢ PC update § Increment PC by 2 ¢

![Stage Computation ArithLog Ops OPl r A r B icode ifun M 1PC Read Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC] Read](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-11.jpg)

Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC] Read instruction byte r. A: r. B M 1[PC+1] Read register byte val. P PC+2 Compute next PC val. A R[r. A] Read operand A val. B R[r. B] Read operand B val. E val. B OP val. A Set CC Perform ALU operation Set condition code register Memory Write R[r. B] val. E Write back result back PC update PC val. P Update PC Fetch Decode Execute § Formulate instruction execution as sequence of simple steps § Use same general form for all instructions

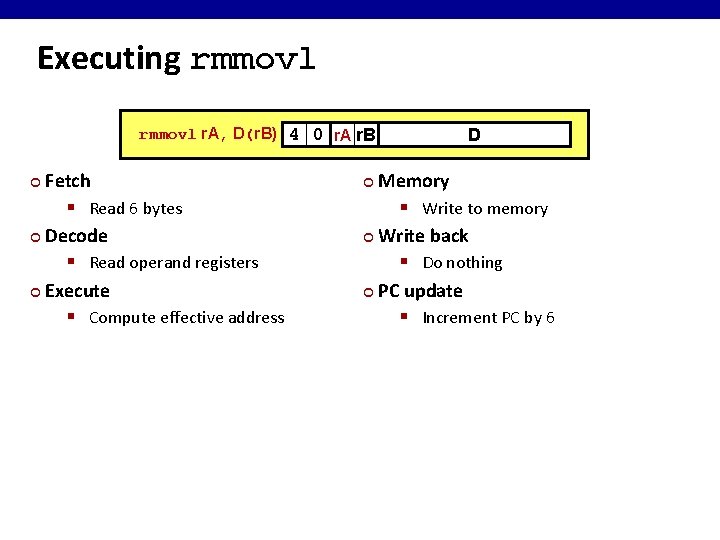

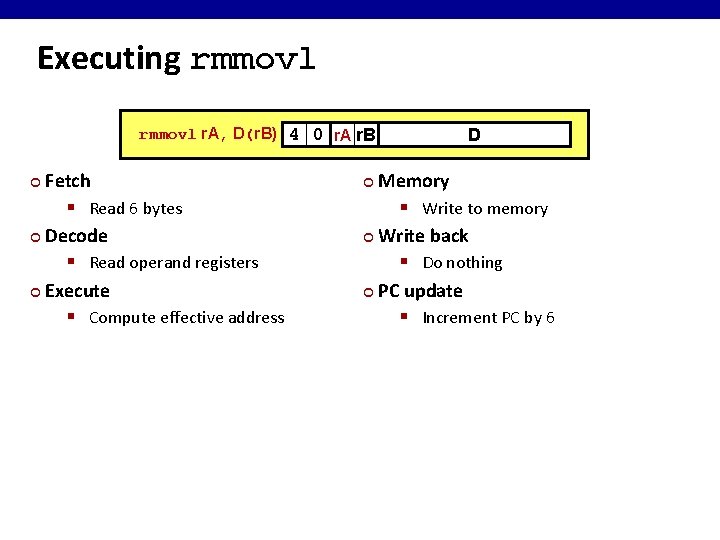

Executing rmmovl r. A, D(r. B) 4 0 r. A r. B Fetch § Read 6 bytes ¢ Decode § Read operand registers ¢ Execute § Compute effective address ¢ D Memory § Write to memory ¢ Write back § Do nothing ¢ PC update § Increment PC by 6 ¢

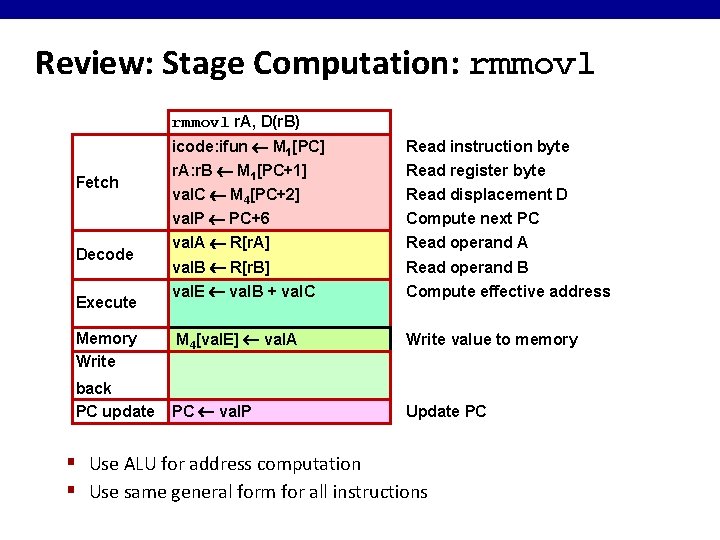

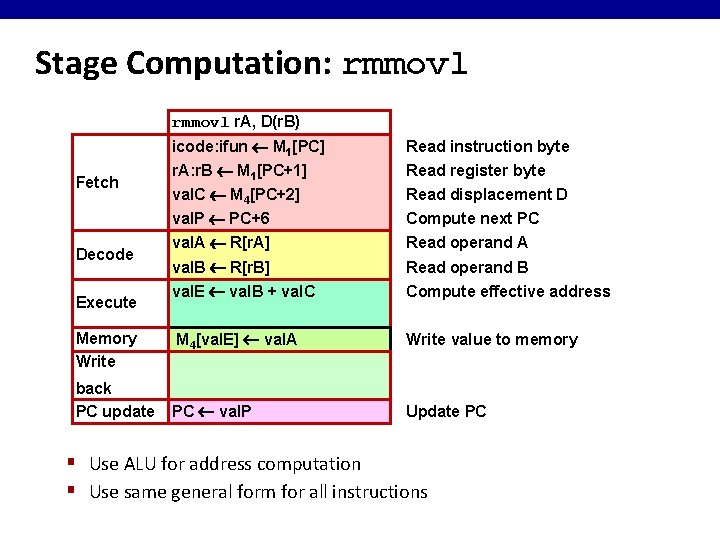

Stage Computation: rmmovl r. A, D(r. B) Fetch Decode Execute Memory Write back PC update icode: ifun M 1[PC] Read instruction byte r. A: r. B M 1[PC+1] Read register byte val. C M 4[PC+2] Read displacement D val. P PC+6 Compute next PC val. A R[r. A] Read operand A val. B R[r. B] Read operand B val. E val. B + val. C Compute effective address M 4[val. E] val. A Write value to memory PC val. P Update PC § Use ALU for address computation § Use same general form for all instructions

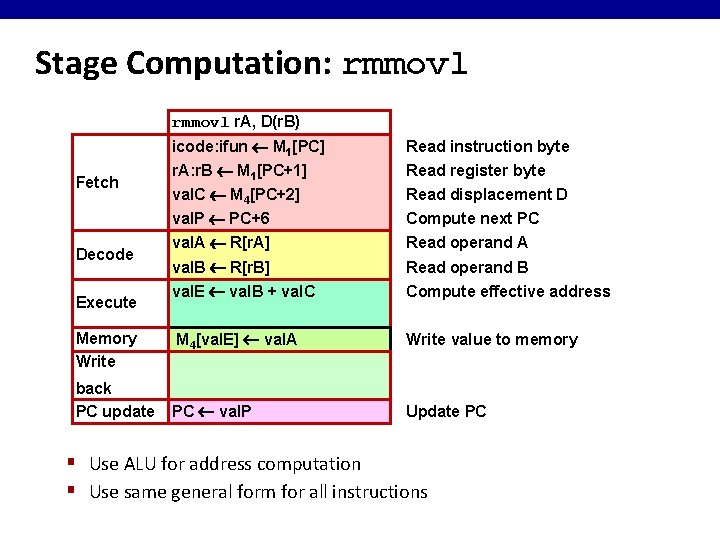

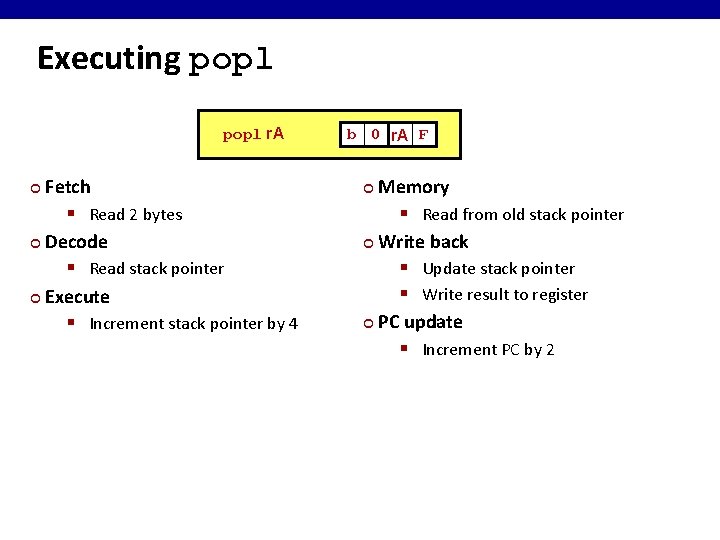

Executing popl r. A Fetch § Read 2 bytes ¢ Decode § Read stack pointer ¢ Execute § Increment stack pointer by 4 ¢ b 0 r. A F Memory § Read from old stack pointer ¢ Write back § Update stack pointer § Write result to register ¢ PC update § Increment PC by 2 ¢

![Stage Computation popl r A icode ifun M 1PC Read instruction byte r A Stage Computation: popl r. A icode: ifun M 1[PC] Read instruction byte r. A:](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-15.jpg)

Stage Computation: popl r. A icode: ifun M 1[PC] Read instruction byte r. A: r. B M 1[PC+1] Read register byte val. P PC+2 val. A R[%esp] Compute next PC Read stack pointer val. B R[%esp] Read stack pointer val. E val. B + 4 Increment stack pointer Memory Write val. M M 4[val. A] R[%esp] val. E Read from stack back PC update R[r. A] val. M PC val. P Fetch Decode Execute Update stack pointer Write back result Update PC § Use ALU to increment stack pointer § Must update two registers (popped value + stack pointer)

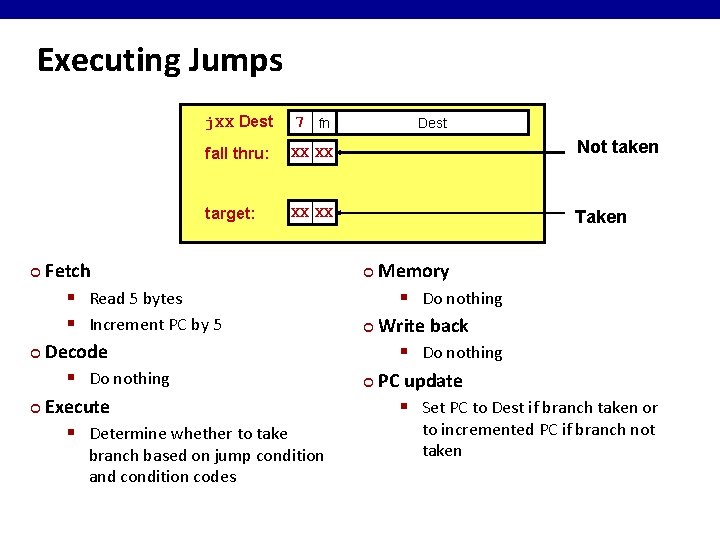

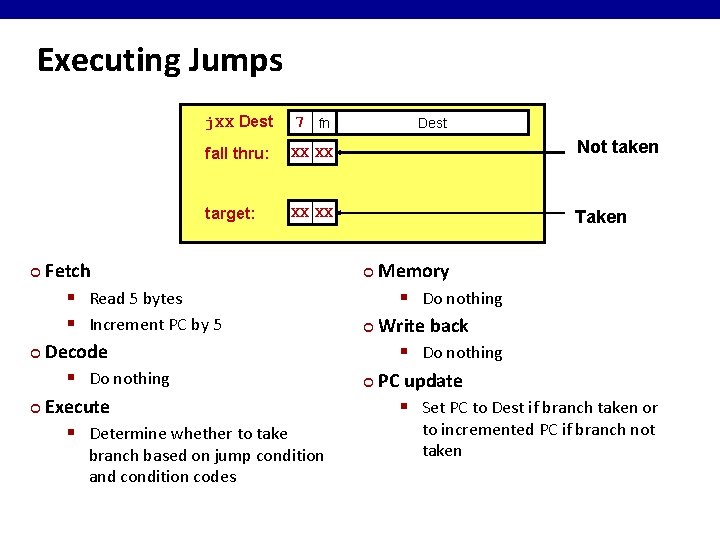

Executing Jumps j. XX Dest 7 fn fall thru: XX XX Not taken target: XX XX Taken Fetch § Read 5 bytes § Increment PC by 5 ¢ Decode § Do nothing ¢ Execute § Determine whether to take ¢ branch based on jump condition and condition codes Dest Memory § Do nothing ¢ Write back § Do nothing ¢ PC update § Set PC to Dest if branch taken or ¢ to incremented PC if branch not taken

![Stage Computation Jumps j XX Dest Fetch icode ifun M 1PC Read instruction byte Stage Computation: Jumps j. XX Dest Fetch icode: ifun M 1[PC] Read instruction byte](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-17.jpg)

Stage Computation: Jumps j. XX Dest Fetch icode: ifun M 1[PC] Read instruction byte val. C M 4[PC+1] Read destination address val. P PC+5 Fall through address Cnd Cond(CC, ifun) Take branch? PC Cnd? val. C : val. P Update PC Decode Execute Memory Write back PC update § Compute both addresses § Choose next PC based on setting of condition codes and branch condition

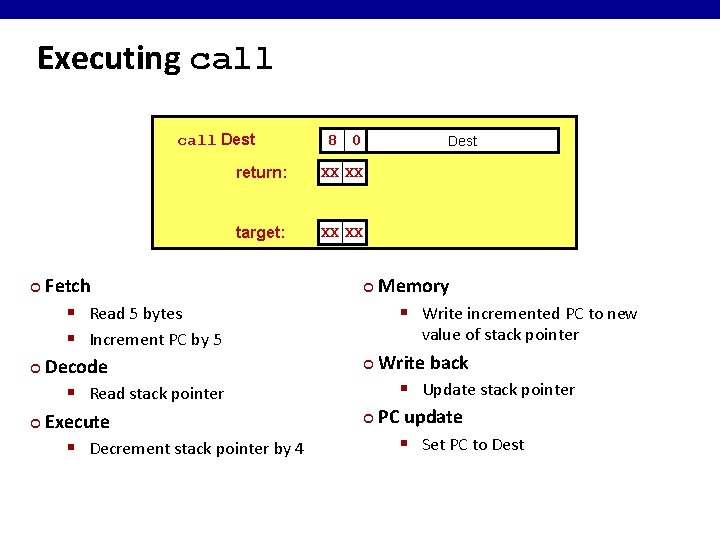

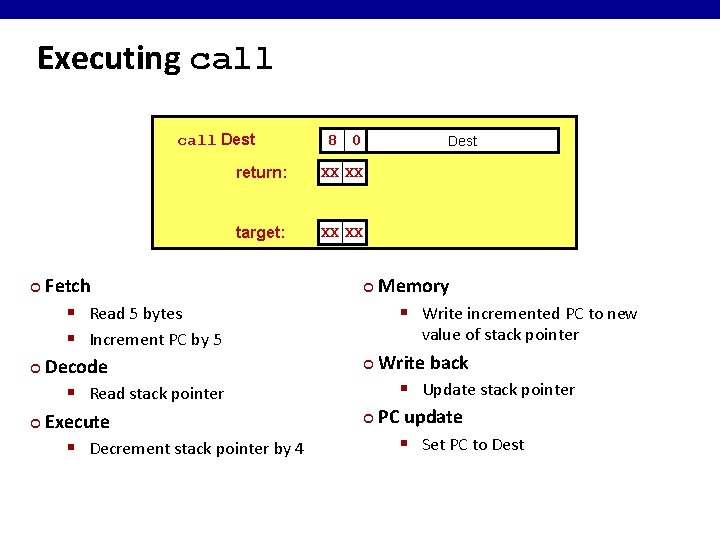

Executing call Dest return: XX XX target: XX XX Fetch § Read 5 bytes § Increment PC by 5 ¢ Decode § Read stack pointer ¢ Execute § Decrement stack pointer by 4 ¢ 8 0 ¢ Memory § Write incremented PC to new value of stack pointer Write back § Update stack pointer ¢ PC update § Set PC to Dest ¢

![Stage Computation call Dest icode ifun M 1PC Read instruction byte val C M Stage Computation: call Dest icode: ifun M 1[PC] Read instruction byte val. C M](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-19.jpg)

Stage Computation: call Dest icode: ifun M 1[PC] Read instruction byte val. C M 4[PC+1] Read destination address val. P PC+5 Compute return point val. B R[%esp] Read stack pointer val. E val. B + – 4 Decrement stack pointer Memory Write M 4[val. E] val. P R[%esp] val. E Write return addr on stack back PC update PC val. C Set PC to destination Fetch Decode Execute § Use ALU to decrement stack pointer § Store incremented PC Update stack pointer

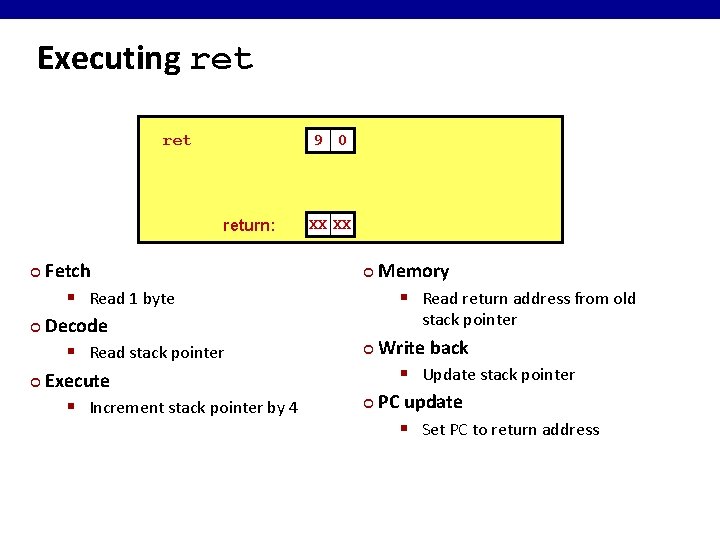

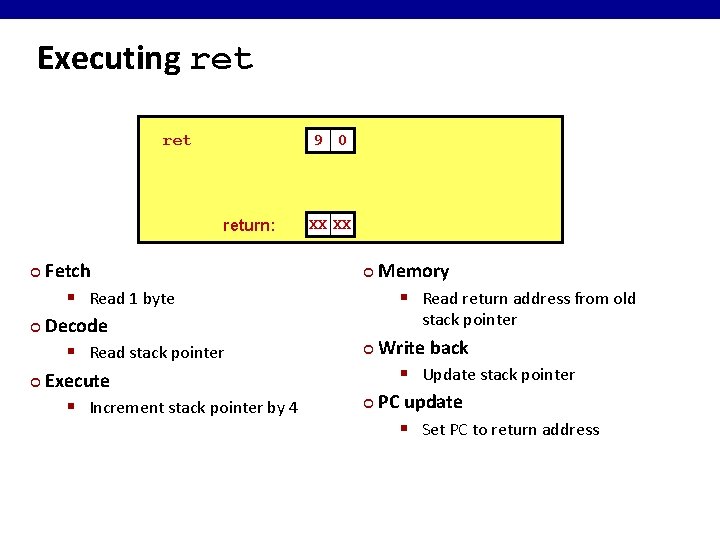

Executing ret 9 0 return: Fetch § Read 1 byte ¢ Decode § Read stack pointer ¢ Execute § Increment stack pointer by 4 ¢ XX XX ¢ Memory § Read return address from old stack pointer Write back § Update stack pointer ¢ PC update § Set PC to return address ¢

![Stage Computation ret icode ifun M 1PC Read instruction byte val A Resp Read Stage Computation: ret icode: ifun M 1[PC] Read instruction byte val. A R[%esp] Read](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-21.jpg)

Stage Computation: ret icode: ifun M 1[PC] Read instruction byte val. A R[%esp] Read operand stack pointer val. B R[%esp] Read operand stack pointer val. E val. B + 4 Increment stack pointer Memory Write val. M M 4[val. A] R[%esp] val. E Read return address back PC update PC val. M Set PC to return address Fetch Decode Execute § Use ALU to increment stack pointer § Read return address from memory Update stack pointer

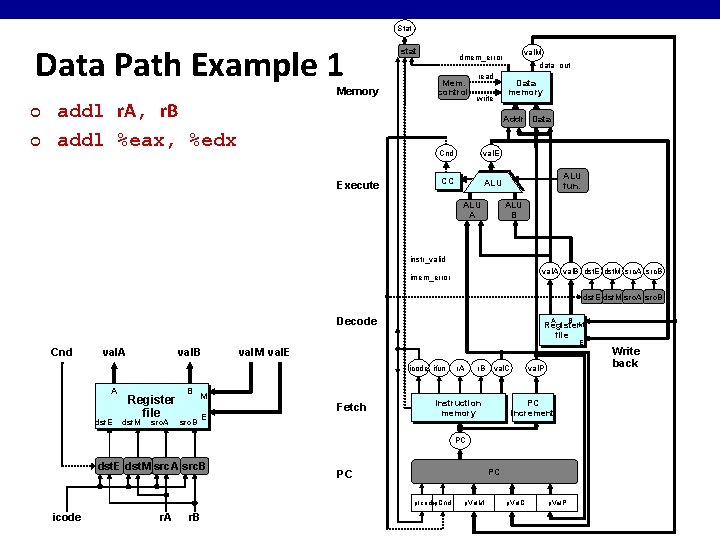

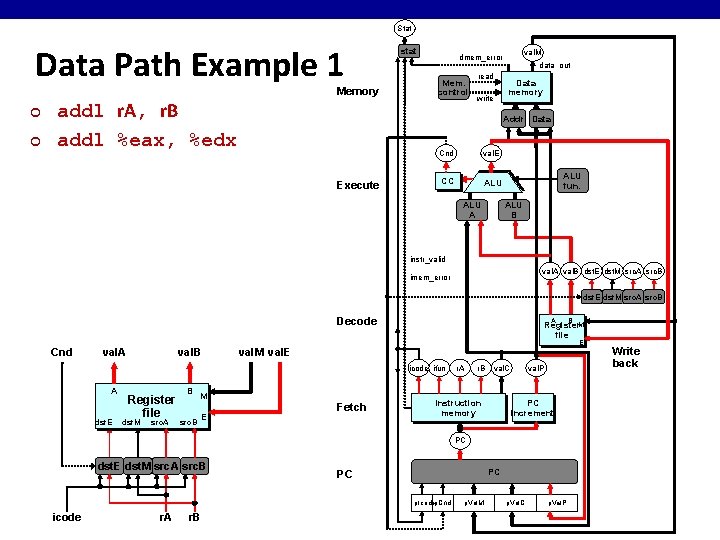

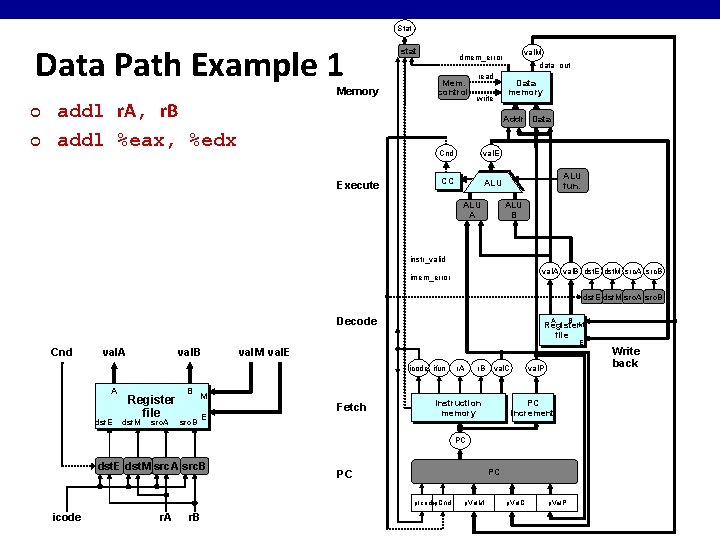

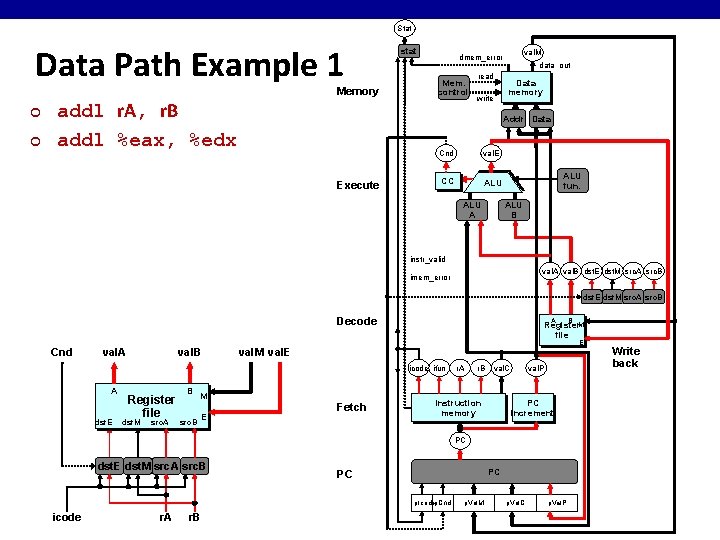

Stat Data Path Example 1 Memory ¢ ¢ addl r. A, r. B addl %eax, %edx stat val. M dmem_error Mem. control read write data out Data memory Addr Data Execute Cnd val. E CC ALU A ALU fun. ALU B instr_valid val. A val. B dst. E dst. M src. A src. B imem_error dst. E dst. M src. A src. B Decode Cnd val. A val. B A E val. M val. E icode ifun A dst. E Register file dst. M src. A B M src. B E Fetch r. A r. B val. C Instruction memory val. P PC increment PC dst. E dst. M src. A src. B PC PC p. Icodep. Cnd icode r. A r. B B Register. M file p. Val. M p. Val. C p. Val. P Write back

![Review Stage Computation ArithLog Ops OPl r A r B icode ifun M 1PC Review: Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC]](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-23.jpg)

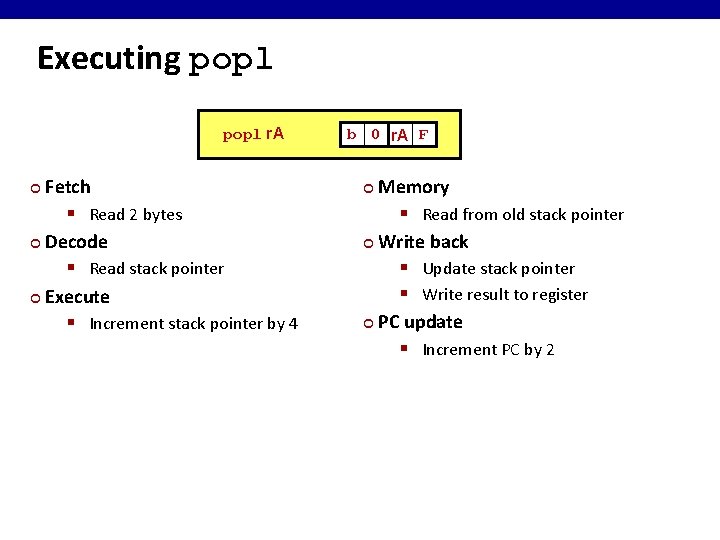

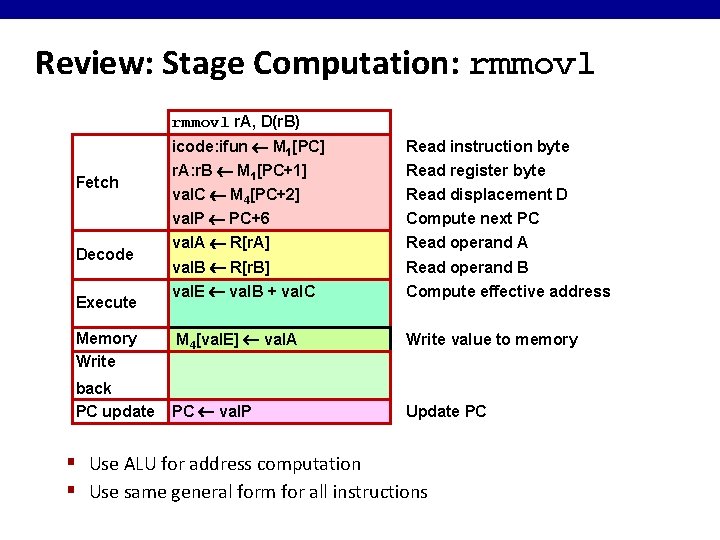

Review: Stage Computation: Arith/Log. Ops OPl r. A, r. B icode: ifun M 1[PC] Read instruction byte r. A: r. B M 1[PC+1] Read register byte val. P PC+2 Compute next PC val. A R[r. A] Read operand A val. B R[r. B] Read operand B val. E val. B OP val. A Set CC Perform ALU operation Set condition code register Memory Write R[r. B] val. E Write back result back PC update PC val. P Update PC Fetch Decode Execute § Formulate instruction execution as sequence of simple steps § Use same general form for all instructions

Stat Data Path Example 1 Memory ¢ ¢ addl r. A, r. B addl %eax, %edx stat val. M dmem_error Mem. control read write data out Data memory Addr Data Execute Cnd val. E CC ALU A ALU fun. ALU B instr_valid val. A val. B dst. E dst. M src. A src. B imem_error dst. E dst. M src. A src. B Decode Cnd val. A val. B A E val. M val. E icode ifun A dst. E Register file dst. M src. A B M src. B E Fetch r. A r. B val. C Instruction memory val. P PC increment PC dst. E dst. M src. A src. B PC PC p. Icodep. Cnd icode r. A r. B B Register. M file p. Val. M p. Val. C p. Val. P Write back

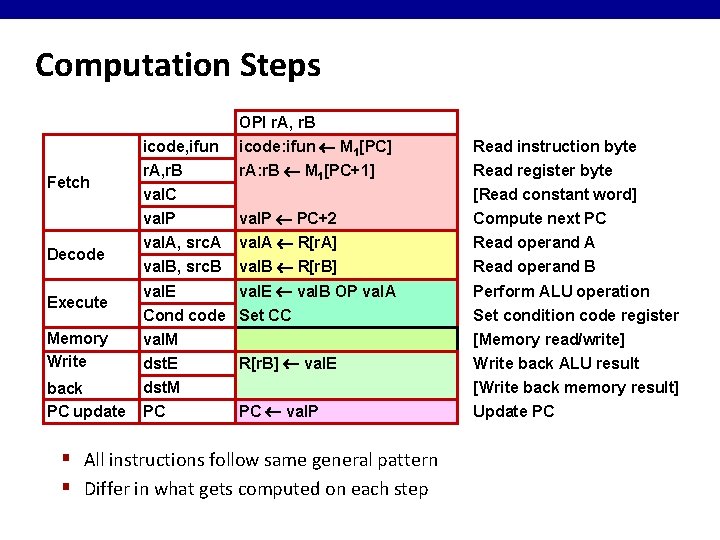

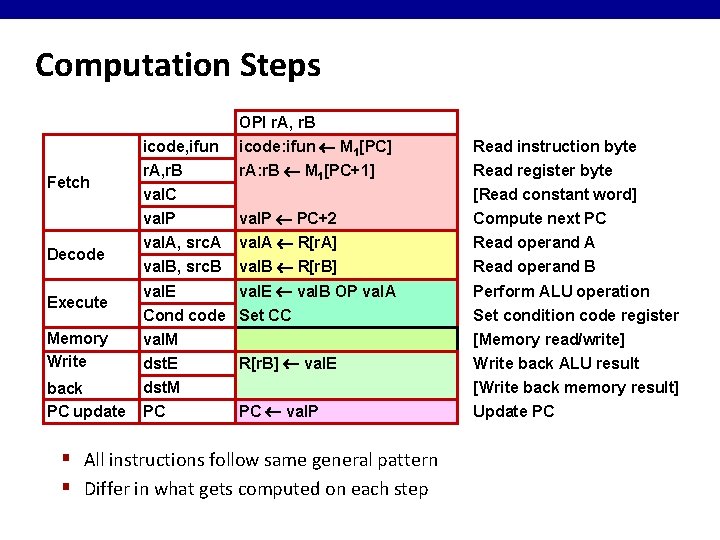

Computation Steps OPl r. A, r. B Fetch Decode Execute Memory Write back PC update icode, ifun r. A, r. B val. C icode: ifun M 1[PC] r. A: r. B M 1[PC+1] Read instruction byte Read register byte [Read constant word] val. P val. A, src. A val. B, src. B val. P PC+2 val. A R[r. A] val. B R[r. B] Compute next PC Read operand A Read operand B val. E val. B OP val. A Cond code Set CC val. M dst. E dst. M PC R[r. B] val. E PC val. P § All instructions follow same general pattern § Differ in what gets computed on each step Perform ALU operation Set condition code register [Memory read/write] Write back ALU result [Write back memory result] Update PC

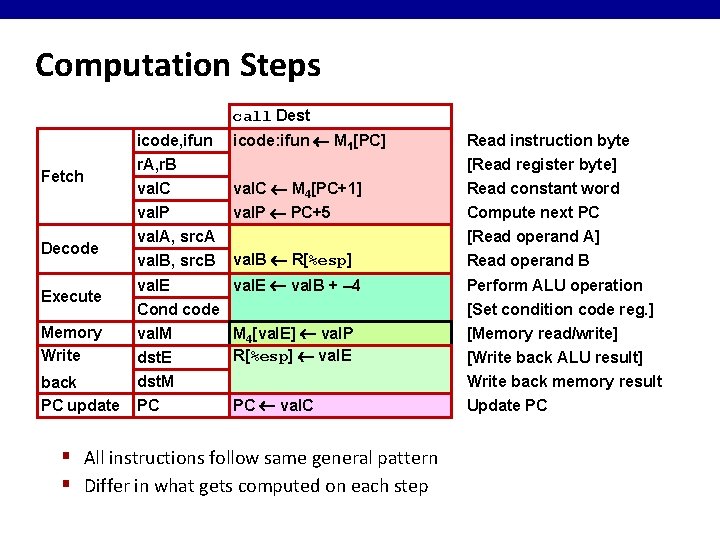

Computation Steps call Dest Fetch Decode icode, ifun r. A, r. B val. C icode: ifun M 1[PC] val. P val. A, src. A val. B, src. B val. P PC+5 val. C M 4[PC+1] val. B R[%esp] Memory Write val. E val. B + – 4 Cond code val. M M 4[val. E] val. P R[%esp] val. E dst. E back PC update dst. M PC Execute PC val. C § All instructions follow same general pattern § Differ in what gets computed on each step Read instruction byte [Read register byte] Read constant word Compute next PC [Read operand A] Read operand B Perform ALU operation [Set condition code reg. ] [Memory read/write] [Write back ALU result] Write back memory result Update PC

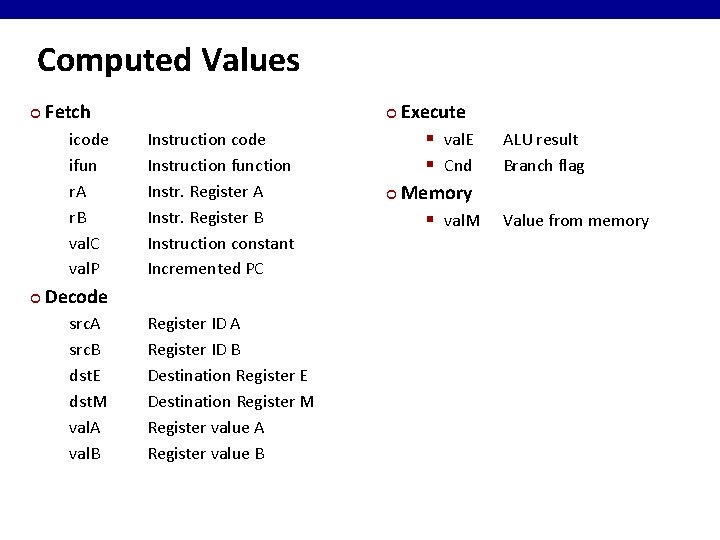

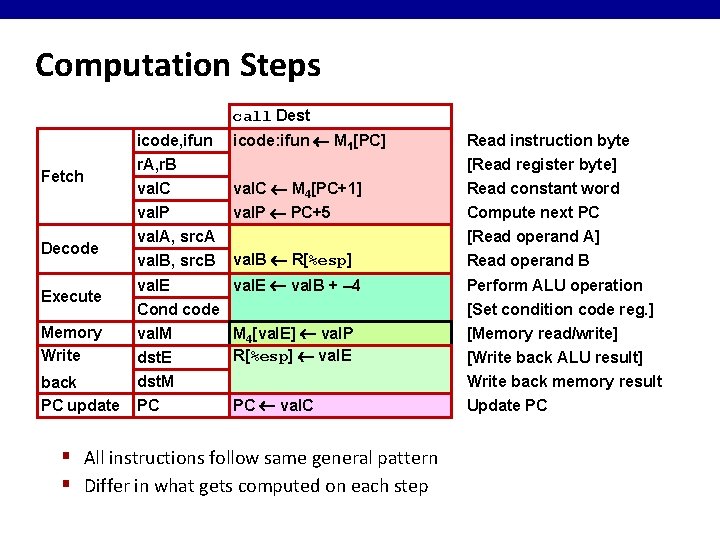

Computed Values ¢ Fetch icode ifun r. A r. B val. C val. P ¢ Instruction code Instruction function Instr. Register A Instr. Register B Instruction constant Incremented PC Decode src. A src. B dst. E dst. M val. A val. B Execute § val. E § Cnd ¢ Memory § val. M ¢ Register ID A Register ID B Destination Register E Destination Register M Register value A Register value B ALU result Branch flag Value from memory

Stat SEQ Hardware ¢ stat Memory Key § Blue boxes: predesigned E. g. , memories, ALU Mem. control write Execute Cnd val. E CC ALU § Gray boxes: control logic § read data out Data memory Addr Data hardware blocks § val. M dmem_error ALU A ALU fun. ALU B We describe in HCL § White ovals: labels for signals Thick lines: 32 -bit values § Thin lines: 4 -8 bit values § Dotted lines: 1 -bit values instr_valid val. A val. B dst. E dst. M src. A src. B imem_error § dst. E dst. M src. A src. B Decode A B Register. M file E icode ifun Fetch r. A r. B val. C Instruction memory val. P PC increment PC PC PC p. Icodep. Cnd p. Val. M p. Val. C p. Val. P Write back

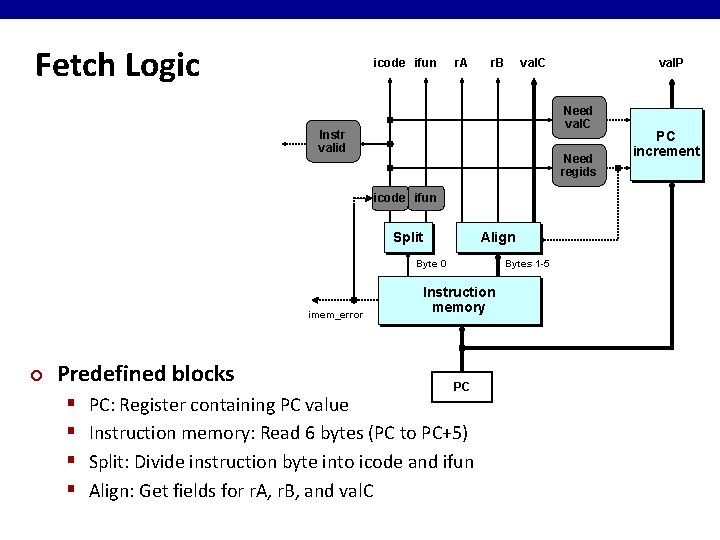

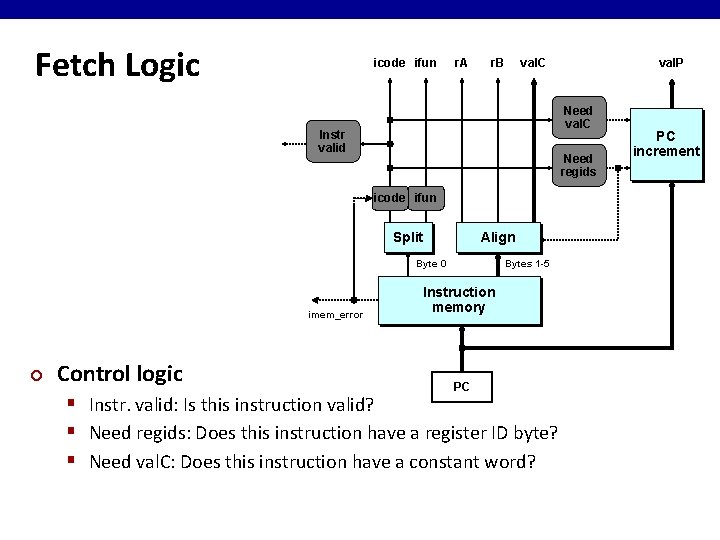

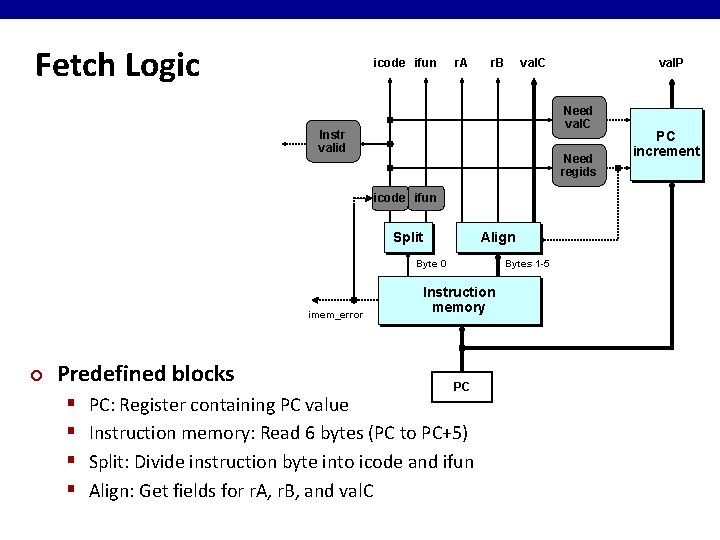

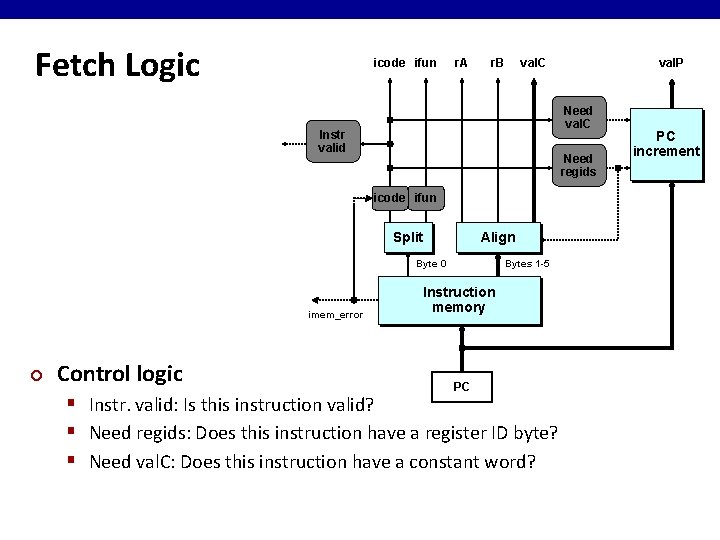

Fetch Logic icode ifun r. A r. B val. C Need val. C Instr valid Need regids icode ifun Split Align Byte 0 imem_error ¢ Predefined blocks § § val. P Bytes 1 -5 Instruction memory PC PC: Register containing PC value Instruction memory: Read 6 bytes (PC to PC+5) Split: Divide instruction byte into icode and ifun Align: Get fields for r. A, r. B, and val. C PC increment

Fetch Logic icode ifun r. A r. B val. C Need val. C Instr valid Need regids icode ifun Split Align Byte 0 imem_error ¢ Control logic val. P Bytes 1 -5 Instruction memory PC § Instr. valid: Is this instruction valid? § Need regids: Does this instruction have a register ID byte? § Need val. C: Does this instruction have a constant word? PC increment

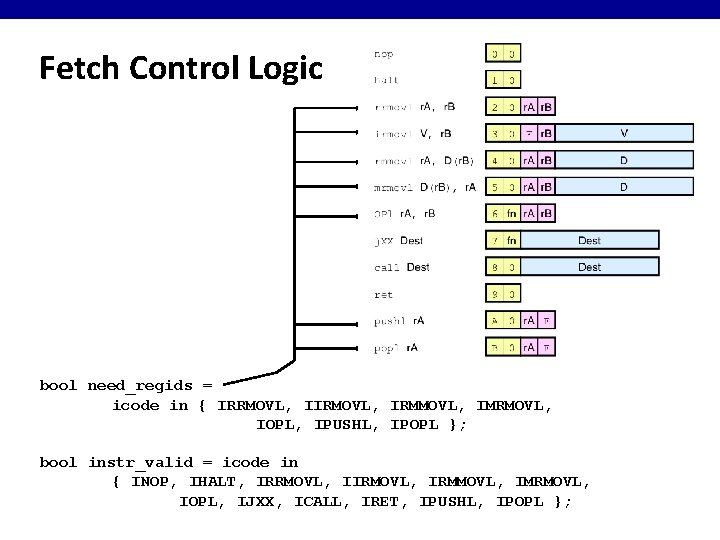

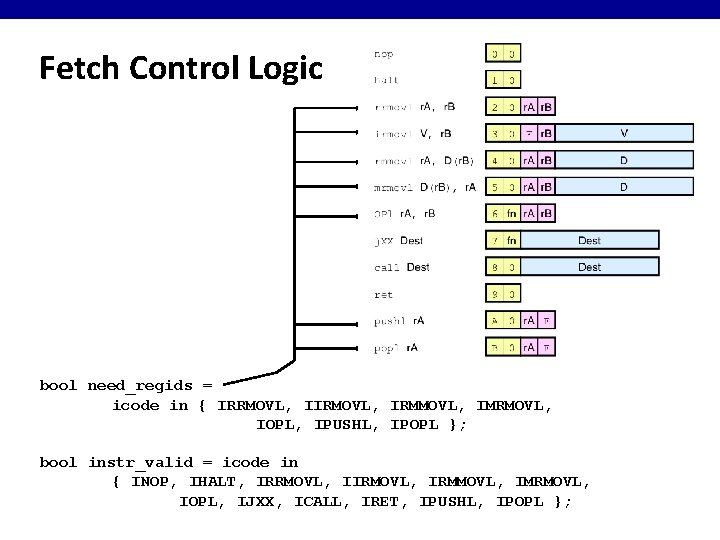

Fetch Control Logic bool need_regids = icode in { IRRMOVL, IIRMOVL, IRMMOVL, IMRMOVL, IOPL, IPUSHL, IPOPL }; bool instr_valid = icode in { INOP, IHALT, IRRMOVL, IIRMOVL, IRMMOVL, IMRMOVL, IOPL, IJXX, ICALL, IRET, IPUSHL, IPOPL };

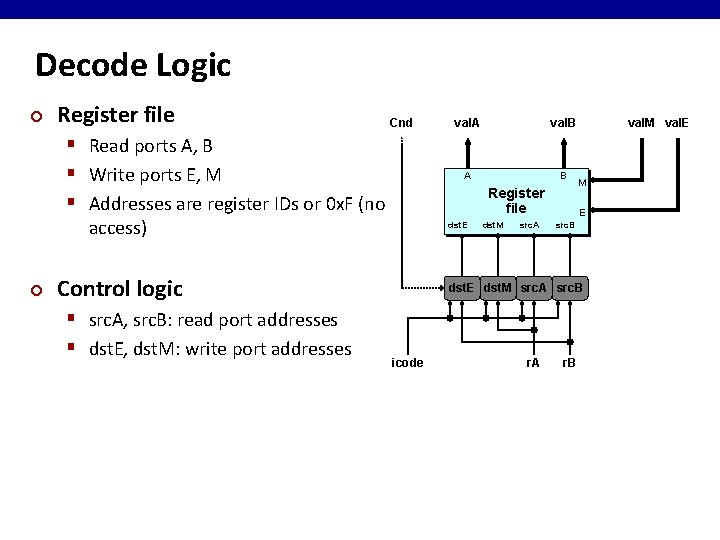

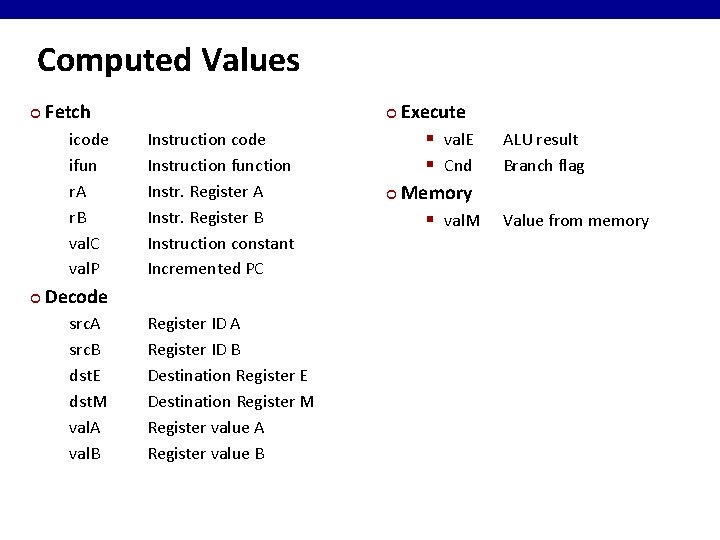

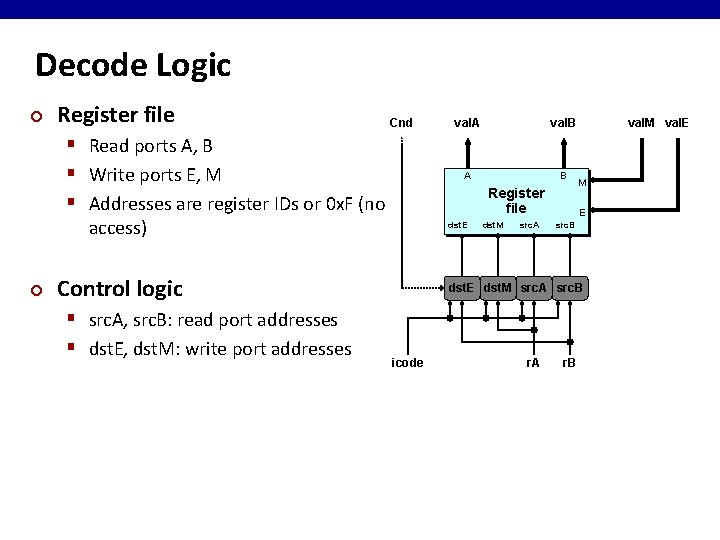

Decode Logic ¢ Register file Cnd § Read ports A, B § Write ports E, M § Addresses are register IDs or 0 x. F (no A B dst. E Control logic § src. A, src. B: read port addresses § dst. E, dst. M: write port addresses val. B Register file access) ¢ val. A dst. M src. A val. M val. E M E src. B dst. E dst. M src. A src. B icode r. A r. B

![A Source Decode OPl r A r B val A Rr A Read operand A Source Decode OPl r. A, r. B val. A R[r. A] Read operand](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-33.jpg)

A Source Decode OPl r. A, r. B val. A R[r. A] Read operand A rmmovl r. A, D(r. B) Decode val. A R[r. A] Read operand A popl r. A Decode val. A R[%esp] Read stack pointer j. XX Dest Decode No operand call Dest Decode No operand ret Decode val. A R[%esp] Read stack pointer int src. A = [ icode in { IRRMOVL, IRMMOVL, IOPL, IPUSHL icode in { IPOPL, IRET } : RESP; 1 : RNONE; # Don't need register ]; } : r. A;

![E Destination OPl r A r B Writeback Rr B val E Write back E Destination OPl r. A, r. B Write-back R[r. B] val. E Write back](https://slidetodoc.com/presentation_image/43b9a58044bc2939984b240924ca5f7c/image-34.jpg)

E Destination OPl r. A, r. B Write-back R[r. B] val. E Write back result rmmovl r. A, D(r. B) Write-back None popl r. A Write-back R[%esp] val. E Update stack pointer j. XX Dest Write-back None call Dest Write-back R[%esp] val. E Update stack pointer ret Write-back R[%esp] val. E Update stack pointer int dst. E = [ icode in { IRRMOVL, IIRMOVL, IOPL} : r. B; icode in { IPUSHL, IPOPL, ICALL, IRET } : RESP; 1 : RNONE; # Don't need register ];

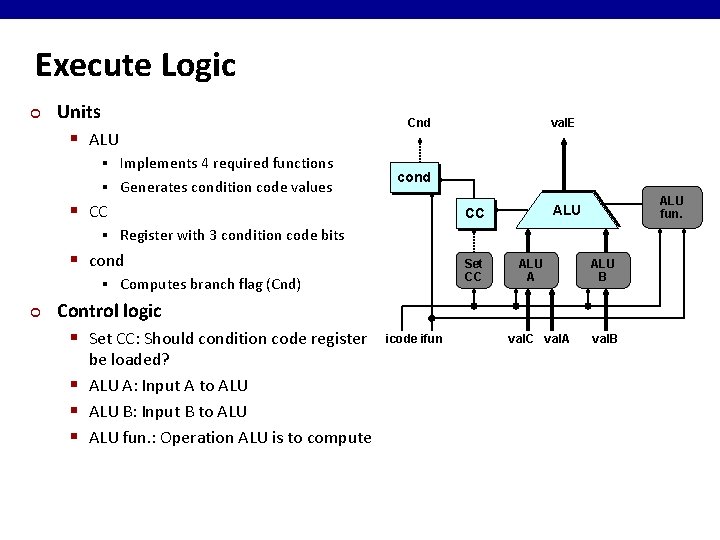

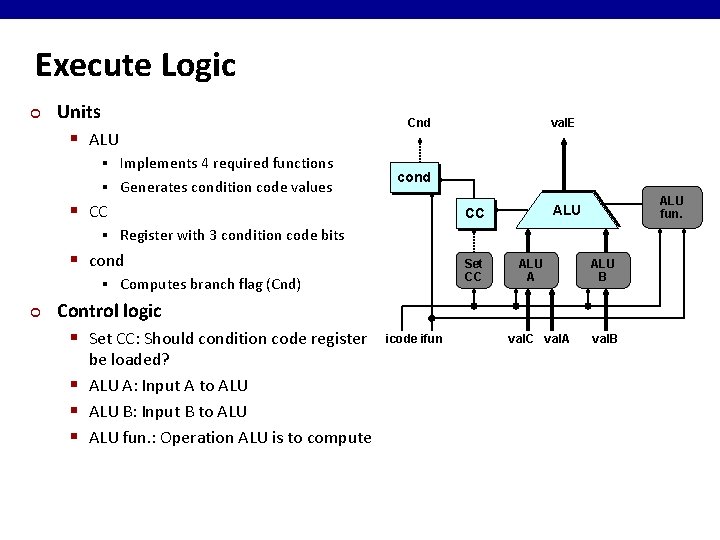

Execute Logic ¢ Units § ALU Cnd Implements 4 required functions § Generates condition code values § cond § CC § ¢ ALU fun. ALU CC Register with 3 condition code bits § cond § val. E Set CC Computes branch flag (Cnd) Control logic § Set CC: Should condition code register be loaded? § ALU A: Input A to ALU § ALU B: Input B to ALU § ALU fun. : Operation ALU is to compute icode ifun ALU A val. C val. A ALU B val. B

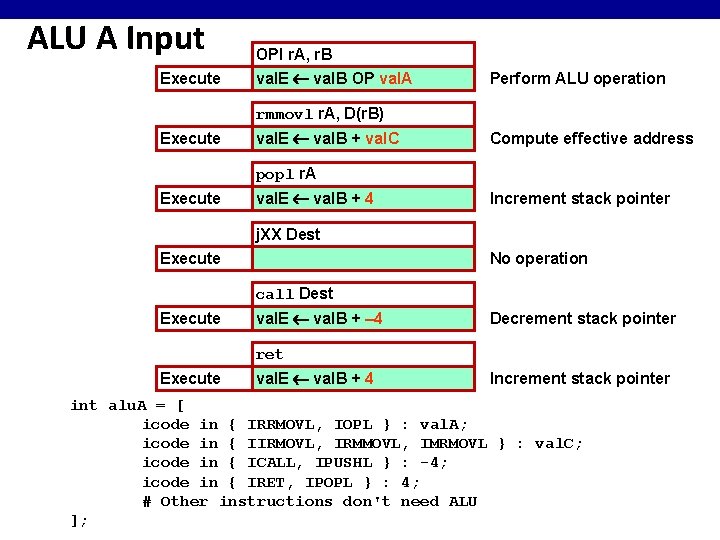

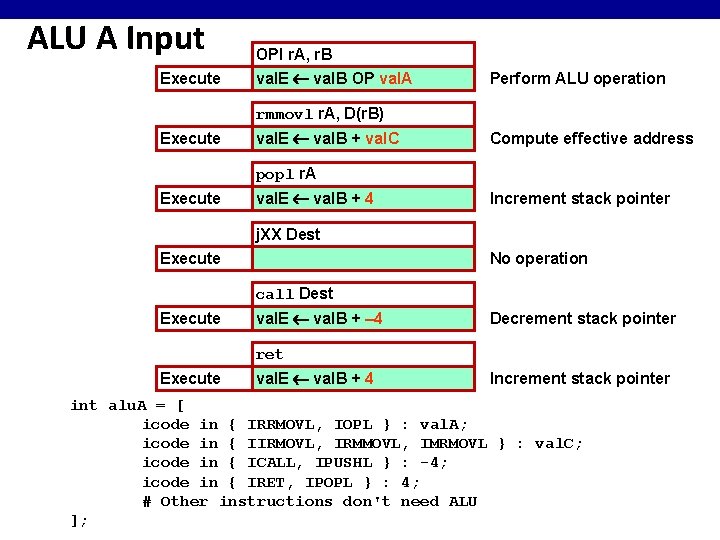

ALU A Input Execute OPl r. A, r. B val. E val. B OP val. A Perform ALU operation rmmovl r. A, D(r. B) Execute val. E val. B + val. C Compute effective address popl r. A Execute val. E val. B + 4 Increment stack pointer j. XX Dest Execute No operation call Dest Execute val. E val. B + – 4 Decrement stack pointer ret Execute val. E val. B + 4 Increment stack pointer int alu. A = [ icode in { IRRMOVL, IOPL } : val. A; icode in { IIRMOVL, IRMMOVL, IMRMOVL } : val. C; icode in { ICALL, IPUSHL } : -4; icode in { IRET, IPOPL } : 4; # Other instructions don't need ALU ];

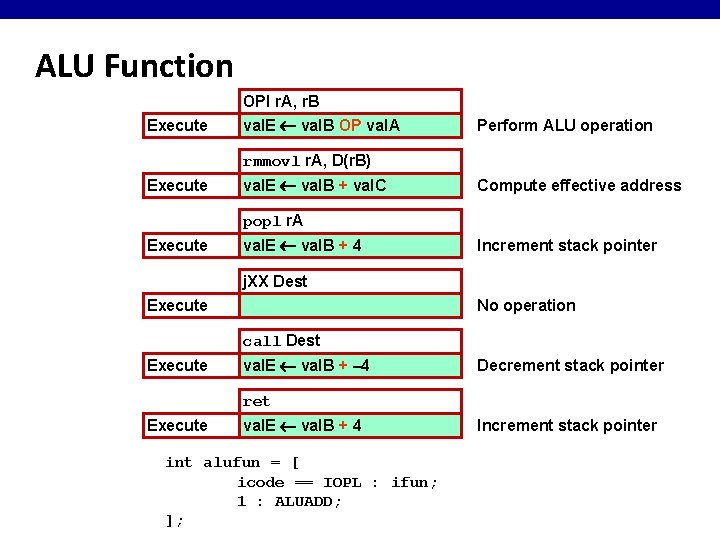

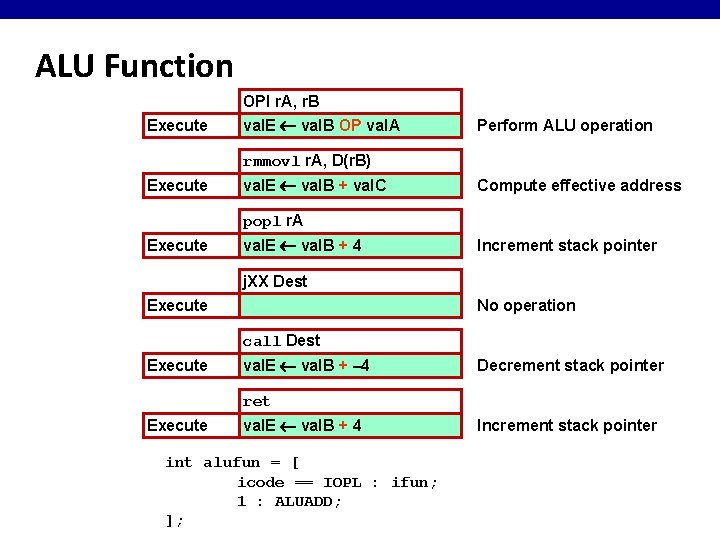

ALU Function OPl r. A, r. B Execute val. E val. B OP val. A Perform ALU operation rmmovl r. A, D(r. B) Execute val. E val. B + val. C Compute effective address popl r. A Execute val. E val. B + 4 Increment stack pointer j. XX Dest Execute No operation call Dest Execute val. E val. B + – 4 Decrement stack pointer ret Execute val. E val. B + 4 int alufun = [ icode == IOPL : ifun; 1 : ALUADD; ]; Increment stack pointer

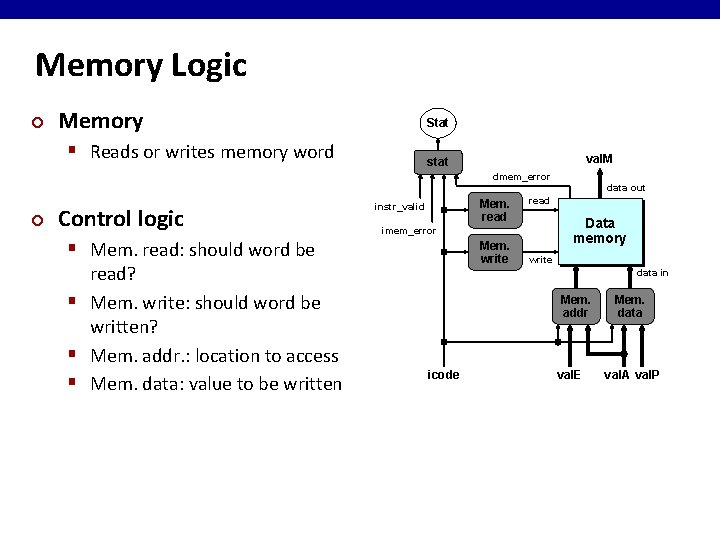

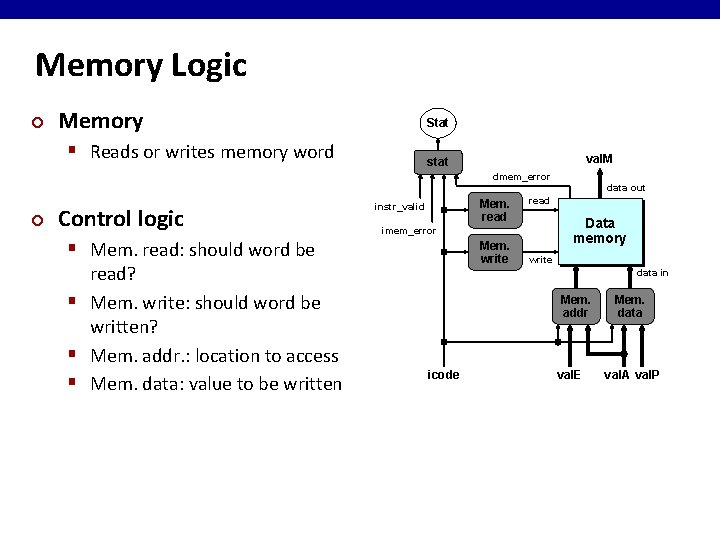

Memory Logic ¢ Memory Stat § Reads or writes memory word val. M stat dmem_error ¢ Control logic § Mem. read: should word be read? § Mem. write: should word be written? § Mem. addr. : location to access § Mem. data: value to be written Mem. read instr_valid read Data memory imem_error Mem. write data out write data in Mem. addr icode val. E Mem. data val. A val. P

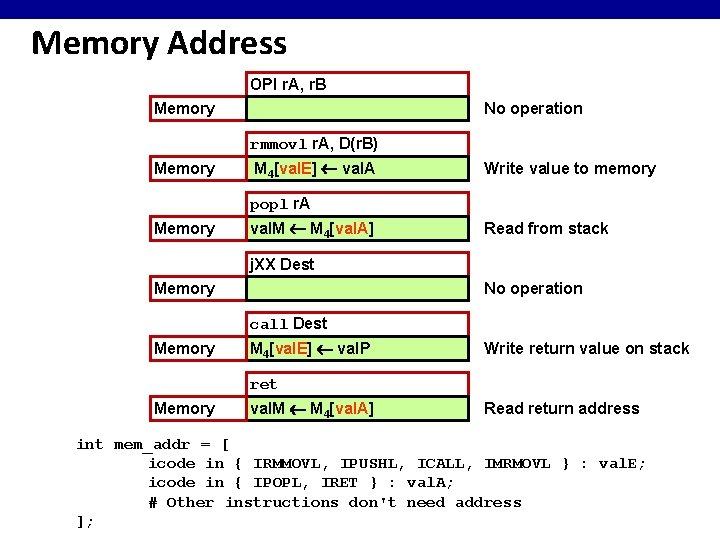

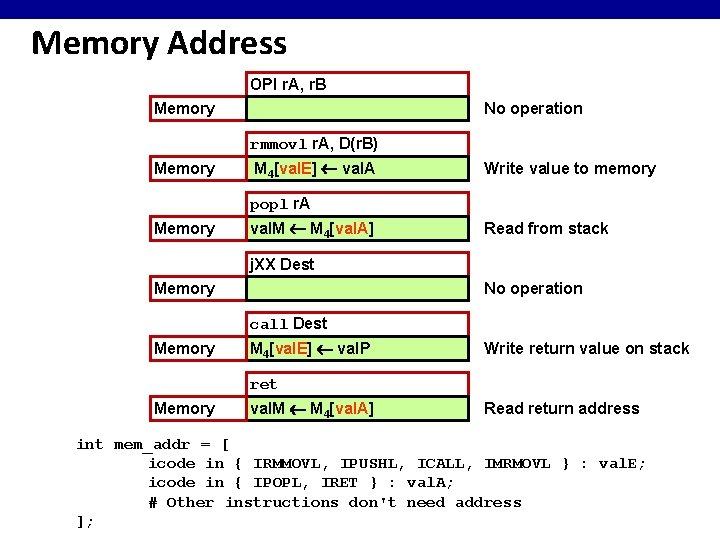

Memory Address OPl r. A, r. B Memory No operation rmmovl r. A, D(r. B) Memory M 4[val. E] val. A Write value to memory popl r. A Memory val. M M 4[val. A] Read from stack j. XX Dest Memory No operation call Dest Memory M 4[val. E] val. P Write return value on stack ret Memory val. M M 4[val. A] Read return address int mem_addr = [ icode in { IRMMOVL, IPUSHL, ICALL, IMRMOVL } : val. E; icode in { IPOPL, IRET } : val. A; # Other instructions don't need address ];

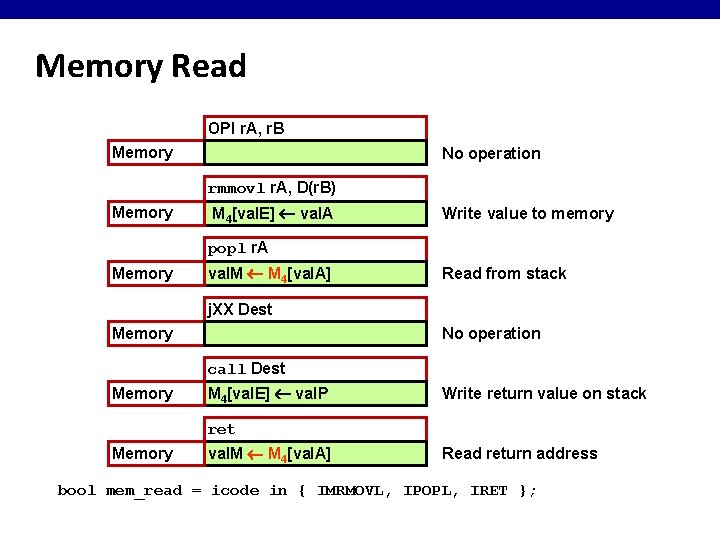

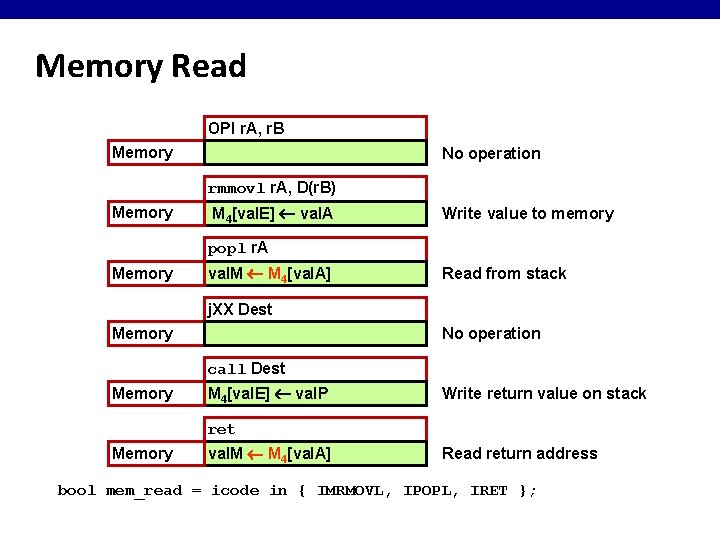

Memory Read OPl r. A, r. B Memory No operation rmmovl r. A, D(r. B) Memory M 4[val. E] val. A Write value to memory popl r. A Memory val. M M 4[val. A] Read from stack j. XX Dest Memory No operation call Dest Memory M 4[val. E] val. P Write return value on stack ret Memory val. M M 4[val. A] Read return address bool mem_read = icode in { IMRMOVL, IPOPL, IRET };

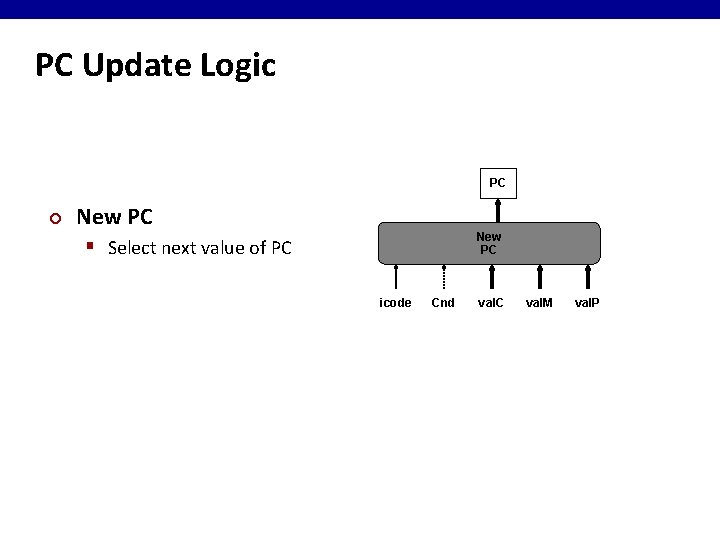

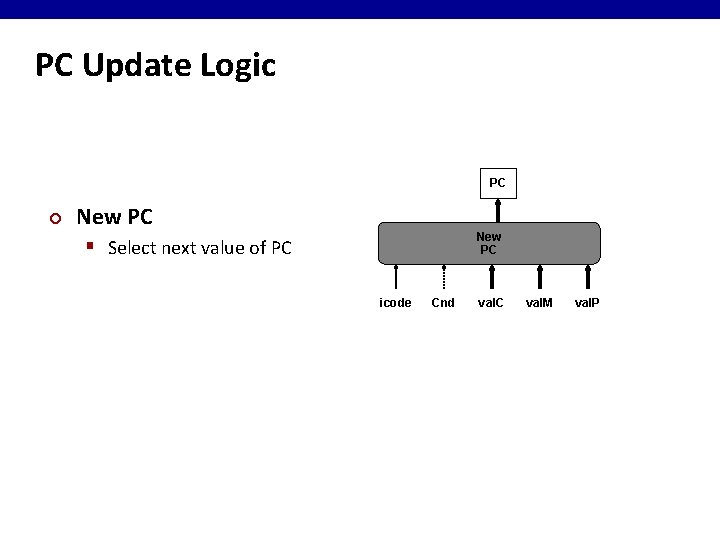

PC Update Logic PC ¢ New PC § Select next value of PC icode Cnd val. C val. M val. P

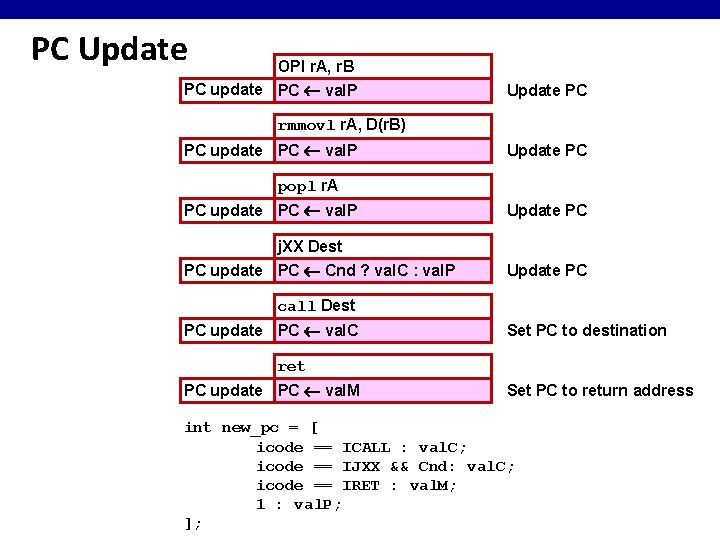

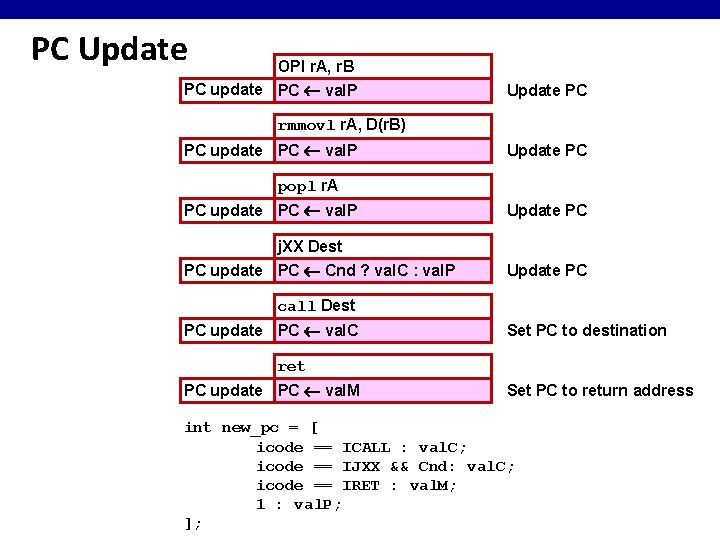

PC Update OPl r. A, r. B PC update PC val. P Update PC rmmovl r. A, D(r. B) PC update PC val. P Update PC popl r. A PC update PC val. P Update PC j. XX Dest PC update PC Cnd ? val. C : val. P Update PC call Dest PC update PC val. C Set PC to destination ret PC update PC val. M Set PC to return address int new_pc = [ icode == ICALL : val. C; icode == IJXX && Cnd: val. C; icode == IRET : val. M; 1 : val. P; ];

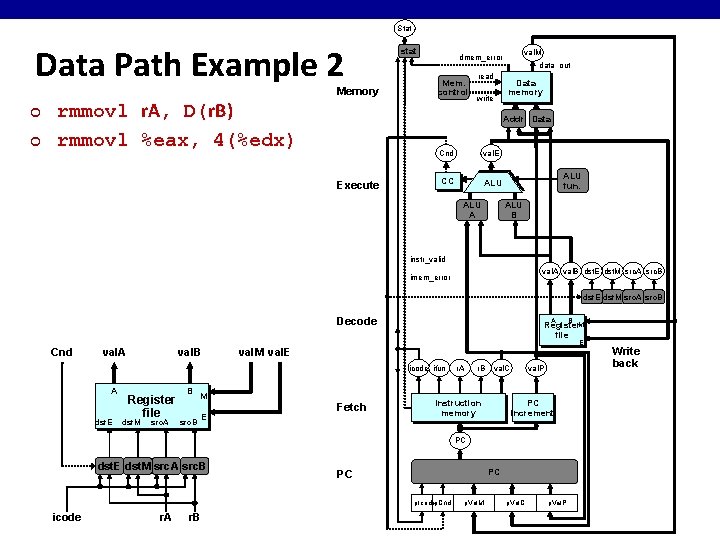

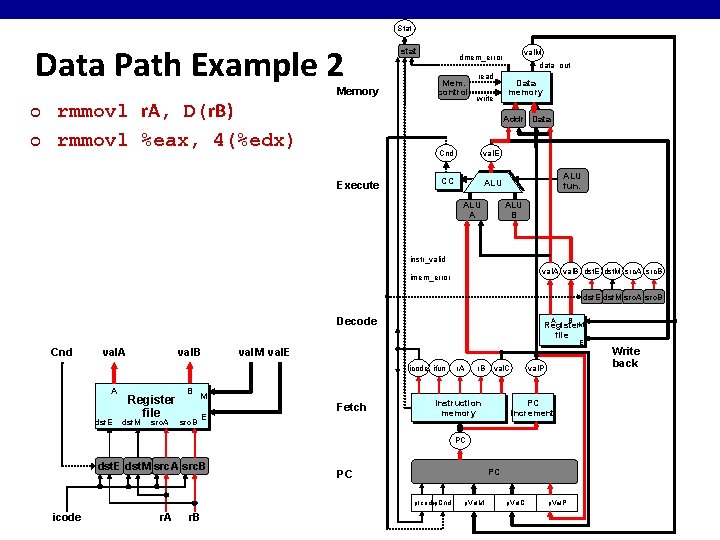

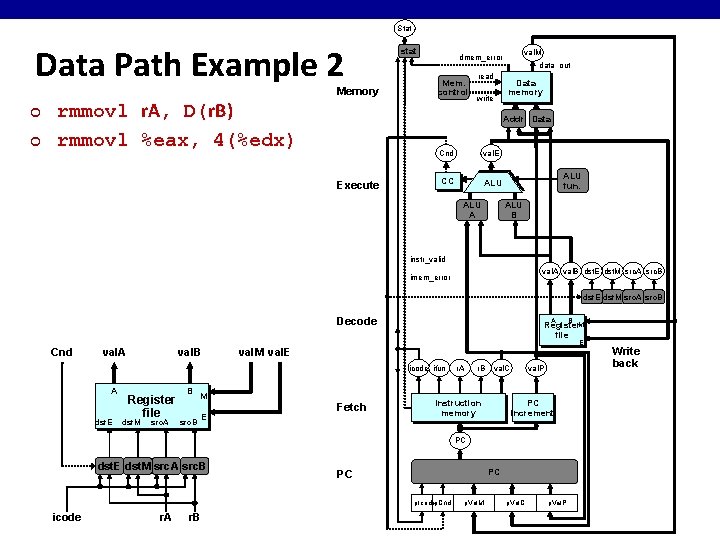

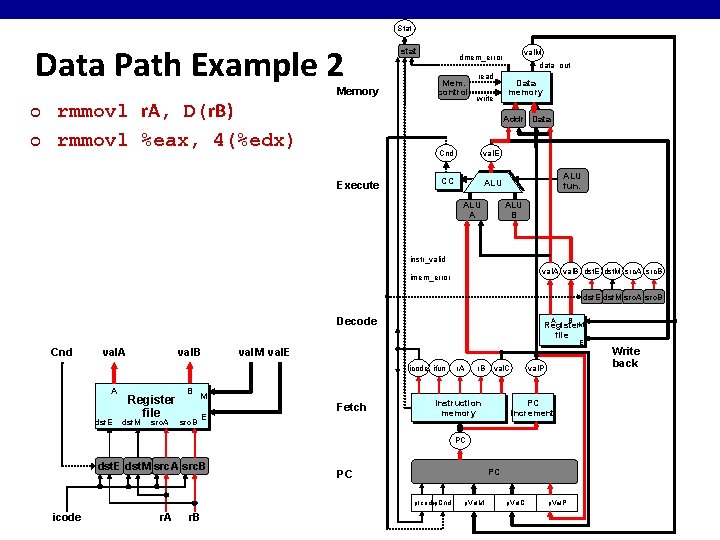

Stat Data Path Example 2 Memory ¢ ¢ rmmovl r. A, D(r. B) rmmovl %eax, 4(%edx) stat val. M dmem_error Mem. control read write data out Data memory Addr Data Execute Cnd val. E CC ALU A ALU fun. ALU B instr_valid val. A val. B dst. E dst. M src. A src. B imem_error dst. E dst. M src. A src. B Decode Cnd val. A val. B A E val. M val. E icode ifun A dst. E Register file dst. M src. A B M src. B E Fetch r. A r. B val. C Instruction memory val. P PC increment PC dst. E dst. M src. A src. B PC PC p. Icodep. Cnd icode r. A r. B B Register. M file p. Val. M p. Val. C p. Val. P Write back

Review: Stage Computation: rmmovl r. A, D(r. B) Fetch Decode Execute Memory Write back PC update icode: ifun M 1[PC] Read instruction byte r. A: r. B M 1[PC+1] Read register byte val. C M 4[PC+2] Read displacement D val. P PC+6 Compute next PC val. A R[r. A] Read operand A val. B R[r. B] Read operand B val. E val. B + val. C Compute effective address M 4[val. E] val. A Write value to memory PC val. P Update PC § Use ALU for address computation § Use same general form for all instructions

Stat Data Path Example 2 Memory ¢ ¢ rmmovl r. A, D(r. B) rmmovl %eax, 4(%edx) stat val. M dmem_error Mem. control read write data out Data memory Addr Data Execute Cnd val. E CC ALU A ALU fun. ALU B instr_valid val. A val. B dst. E dst. M src. A src. B imem_error dst. E dst. M src. A src. B Decode Cnd val. A val. B A E val. M val. E icode ifun A dst. E Register file dst. M src. A B M src. B E Fetch r. A r. B val. C Instruction memory val. P PC increment PC dst. E dst. M src. A src. B PC PC p. Icodep. Cnd icode r. A r. B B Register. M file p. Val. M p. Val. C p. Val. P Write back

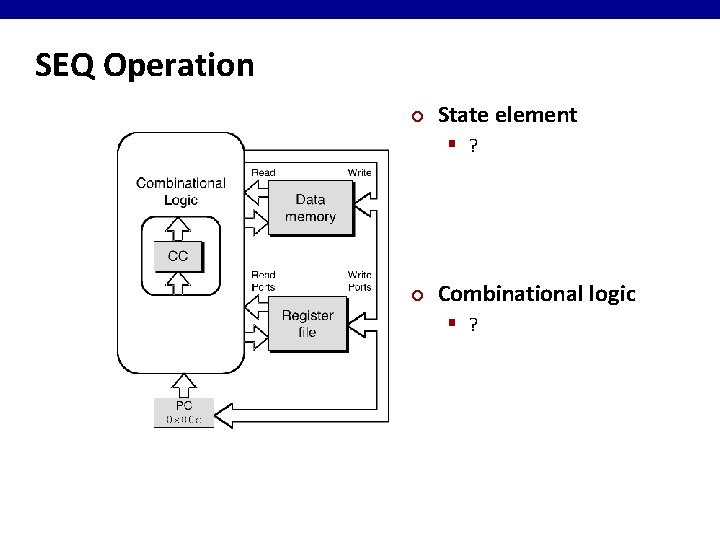

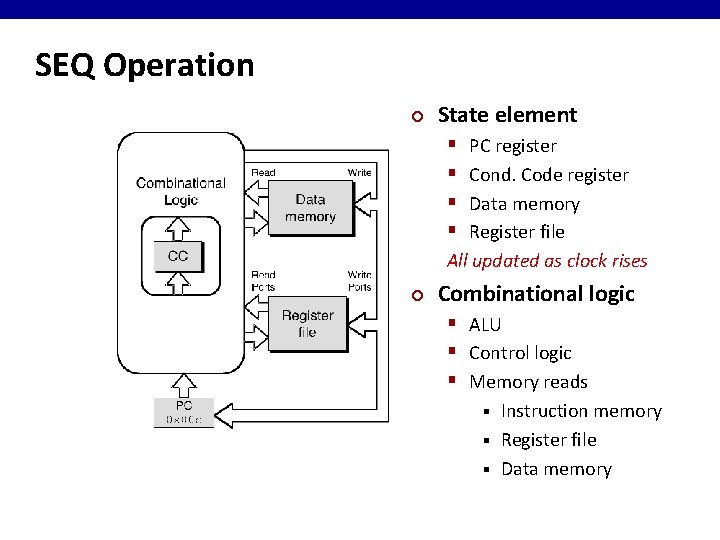

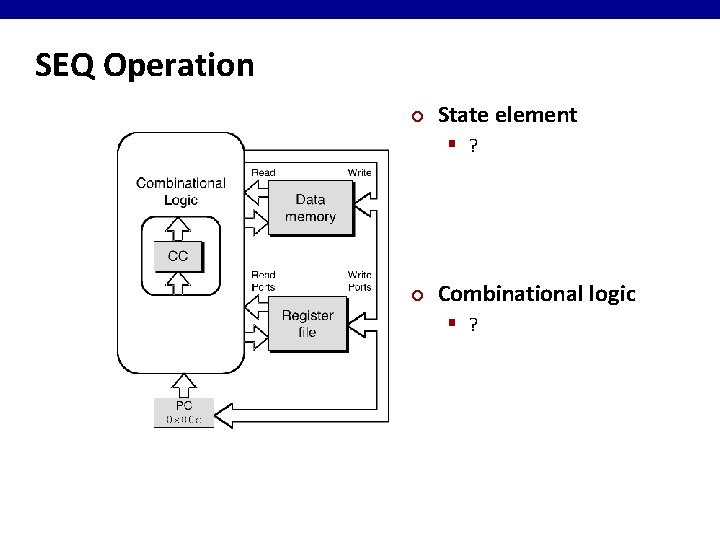

SEQ Operation ¢ State element § ? ¢ Combinational logic § ?

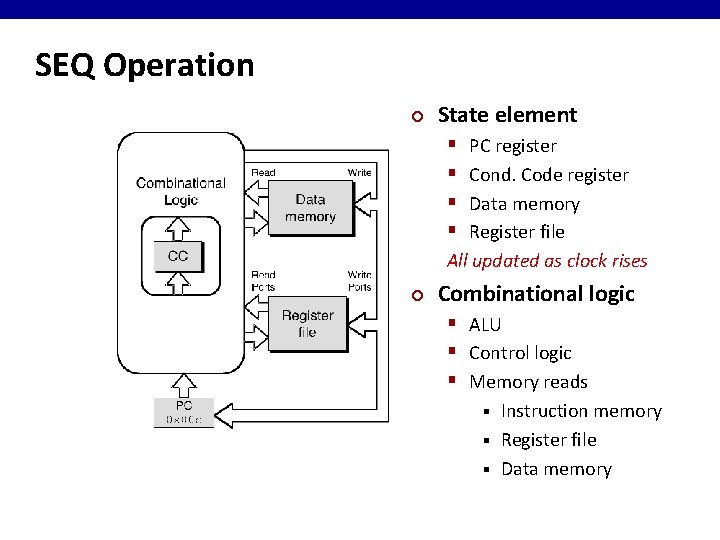

SEQ Operation ¢ State element § § PC register Cond. Code register Data memory Register file All updated as clock rises ¢ Combinational logic § ALU § Control logic § Memory reads Instruction memory § Register file § Data memory §

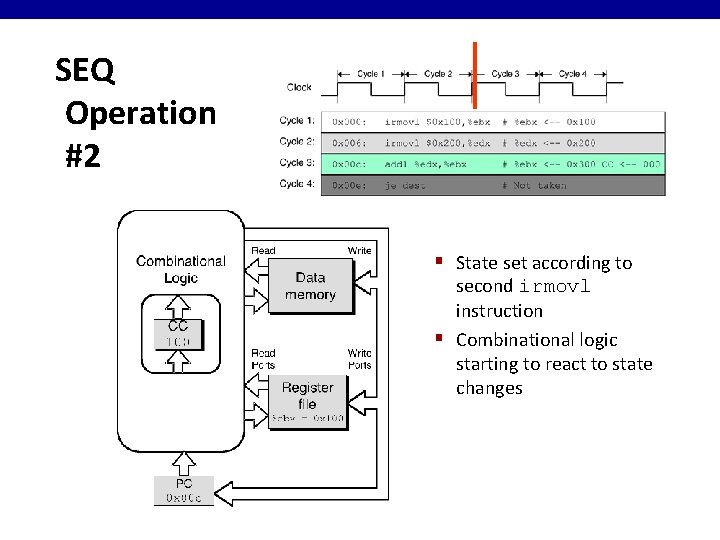

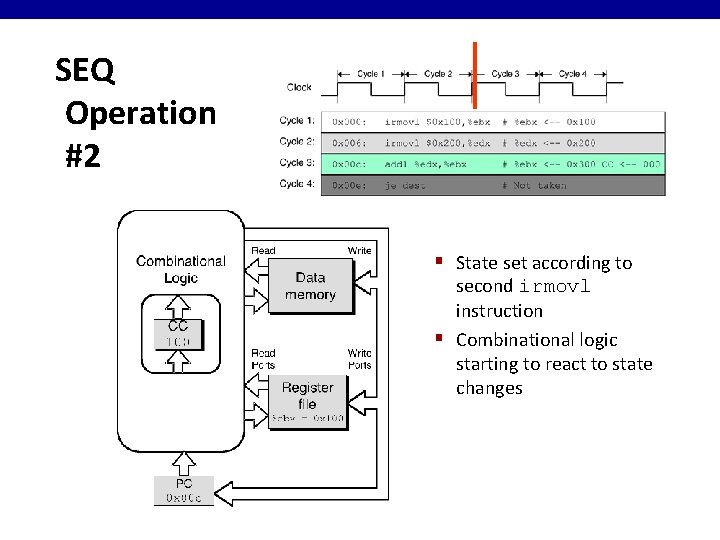

SEQ Operation #2 § State set according to second irmovl instruction § Combinational logic starting to react to state changes

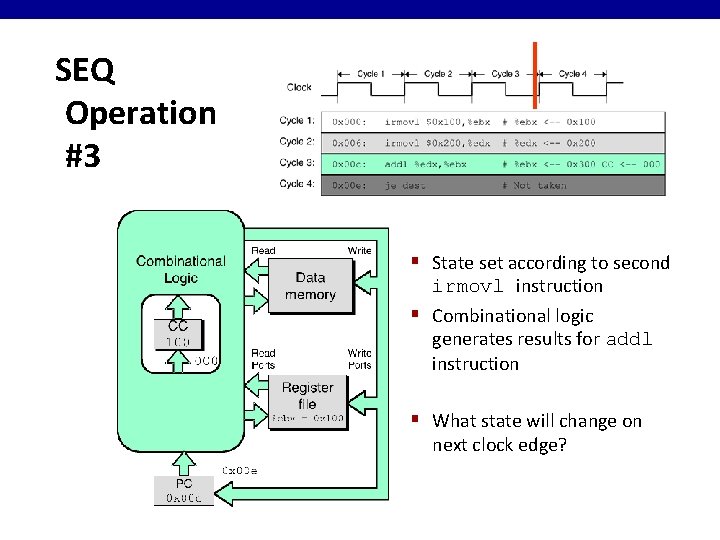

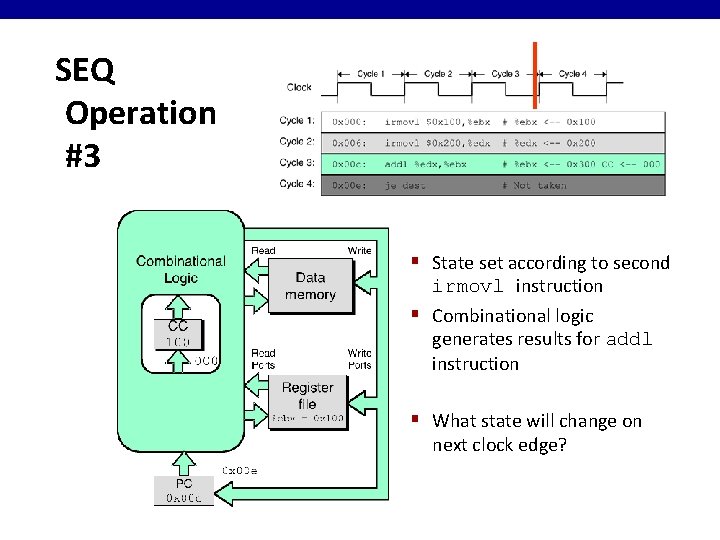

SEQ Operation #3 § State set according to second irmovl instruction § Combinational logic generates results for addl instruction § What state will change on next clock edge?

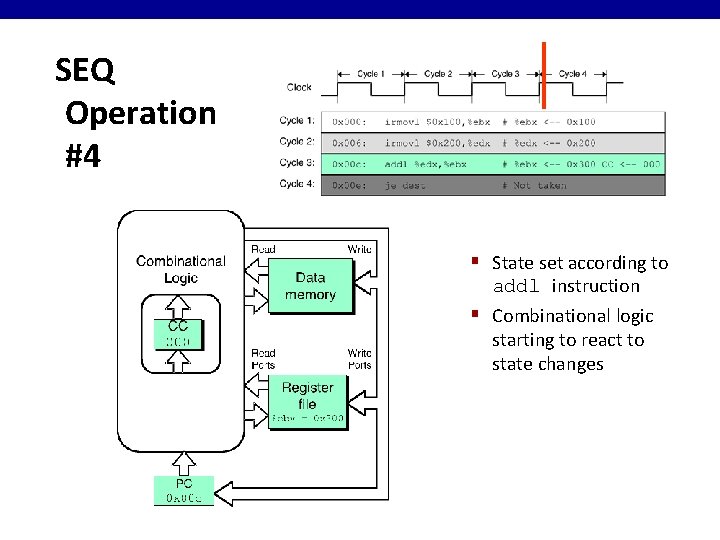

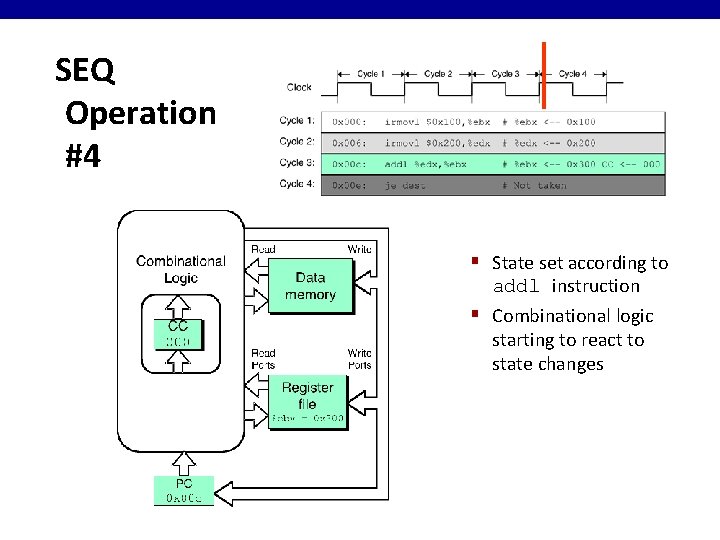

SEQ Operation #4 § State set according to addl instruction § Combinational logic starting to react to state changes

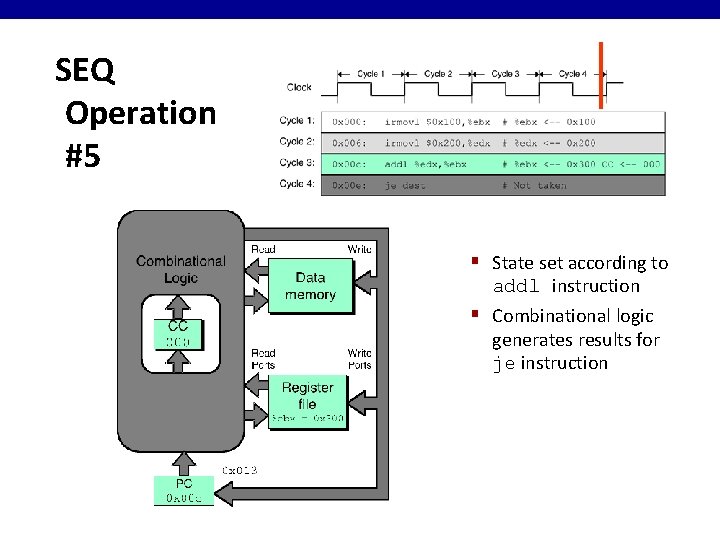

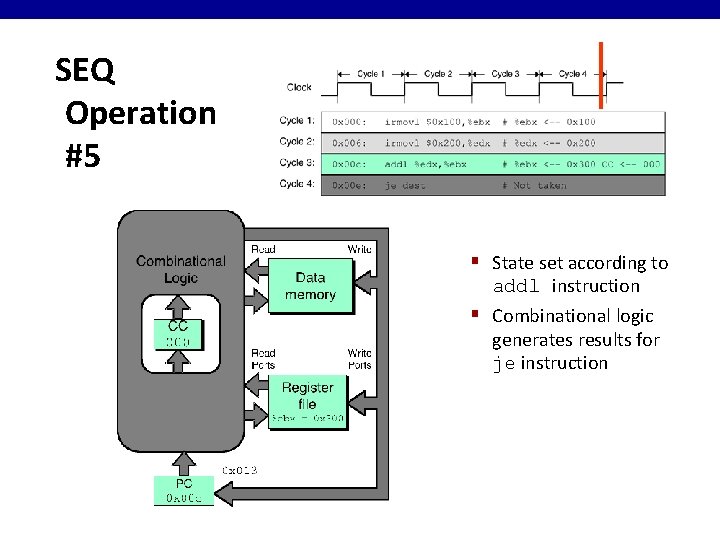

SEQ Operation #5 § State set according to addl instruction § Combinational logic generates results for je instruction

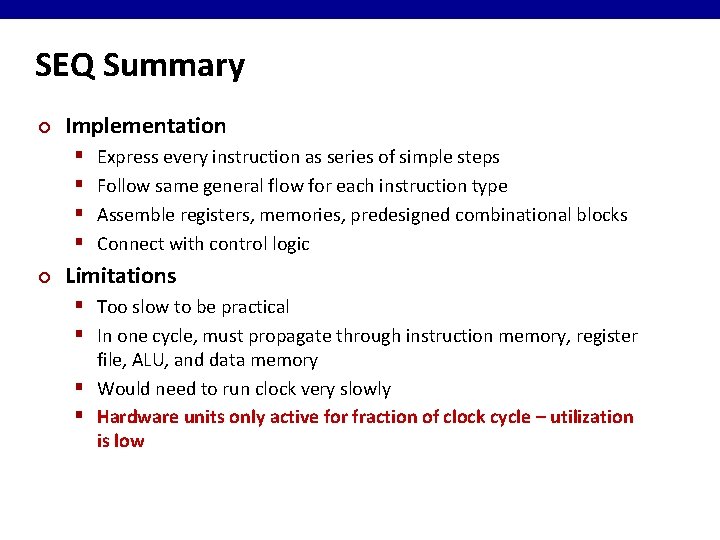

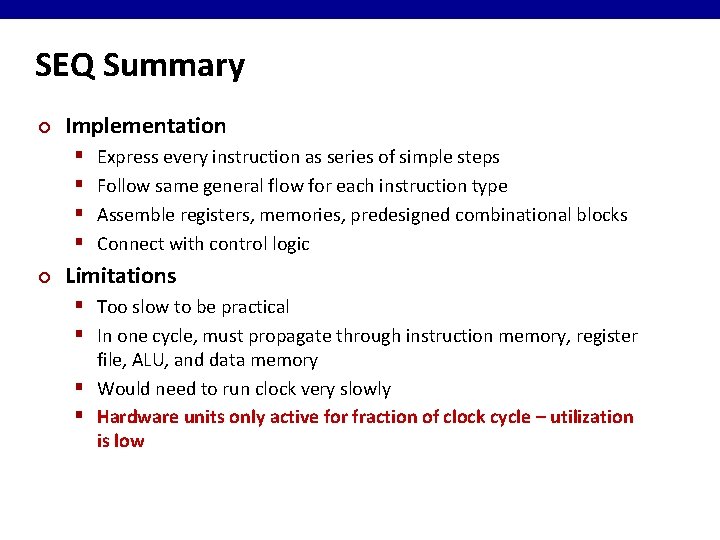

SEQ Summary ¢ Implementation § § ¢ Express every instruction as series of simple steps Follow same general flow for each instruction type Assemble registers, memories, predesigned combinational blocks Connect with control logic Limitations § Too slow to be practical § In one cycle, must propagate through instruction memory, register file, ALU, and data memory § Would need to run clock very slowly § Hardware units only active for fraction of clock cycle – utilization is low

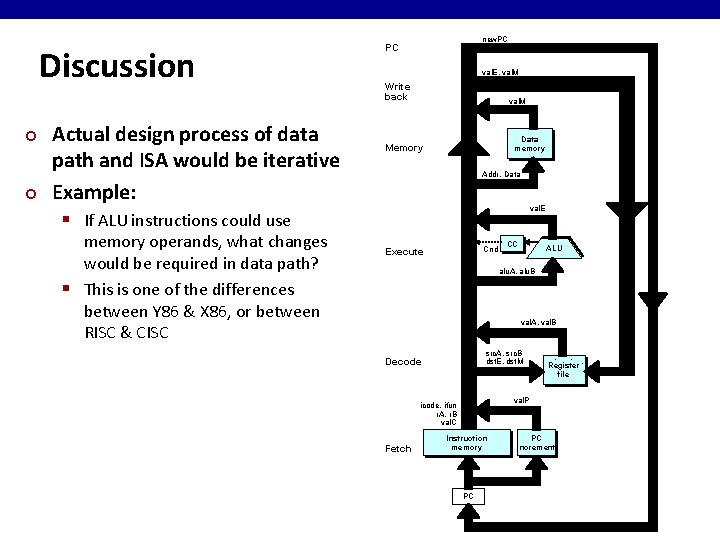

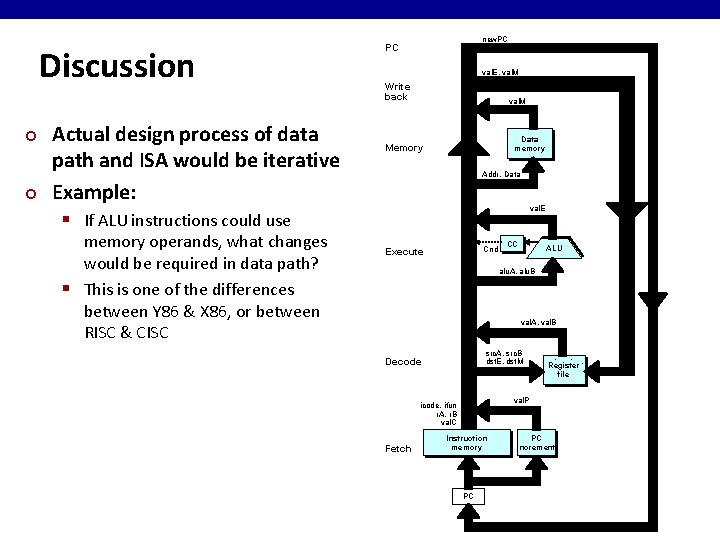

Discussion ¢ ¢ Actual design process of data path and ISA would be iterative Example: new. PC PC val. E, val. M Write back val. M Data memory Memory Addr, Data val. E § If ALU instructions could use memory operands, what changes would be required in data path? § This is one of the differences between Y 86 & X 86, or between RISC & CISC Cnd Execute CC ALU alu. A, alu. B val. A, val. B src. A, src. B dst. E, dst. M Decode val. P icode, ifun r. A, r. B val. C Fetch A Instruction memory PC B Register file PC increment M E