Semiconductor IC Processing at Agilent An Overview L

- Slides: 46

Semiconductor IC Processing at Agilent An Overview L. Zavieh Integration and Visual Engineering Agilent Technologies December 11, 2003

Outline SAgilent – what do we make, and who do we make it for? S Microwave Technology – What does my division make? SHow do we make it? The processing toolbox SLithography SMetal deposition SLitho and dep – an application SDielectric Deposition SIsolation SOhmic Contacts SEtching and various applications SCreative combinations STesting SAcknowledgements SQuestions? Lisa Zavieh pg. 2

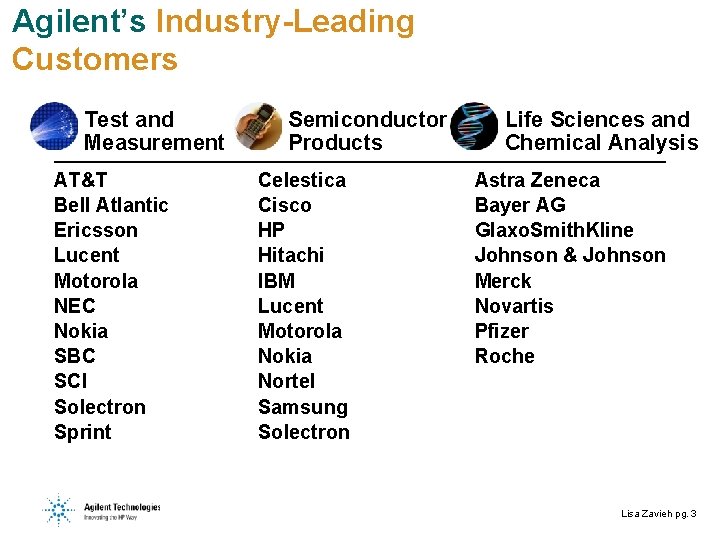

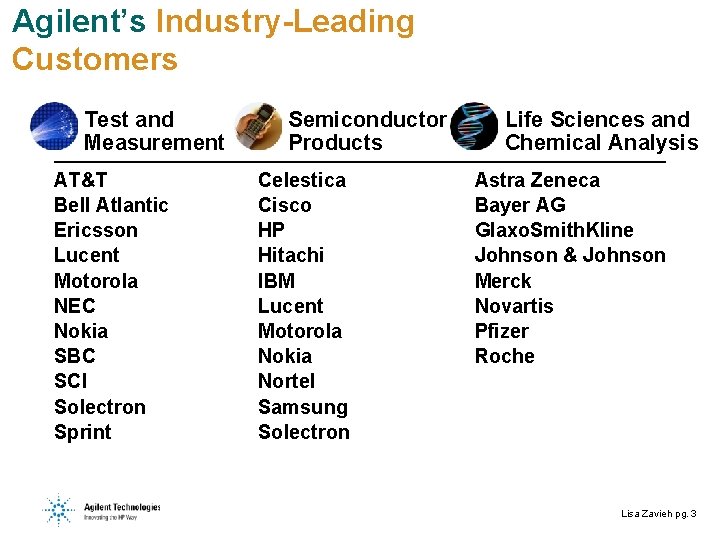

Agilent’s Industry-Leading Customers Test and Measurement AT&T Bell Atlantic Ericsson Lucent Motorola NEC Nokia SBC SCI Solectron Sprint Semiconductor Products Celestica Cisco HP Hitachi IBM Lucent Motorola Nokia Nortel Samsung Solectron Life Sciences and Chemical Analysis Astra Zeneca Bayer AG Glaxo. Smith. Kline Johnson & Johnson Merck Novartis Pfizer Roche Lisa Zavieh pg. 3

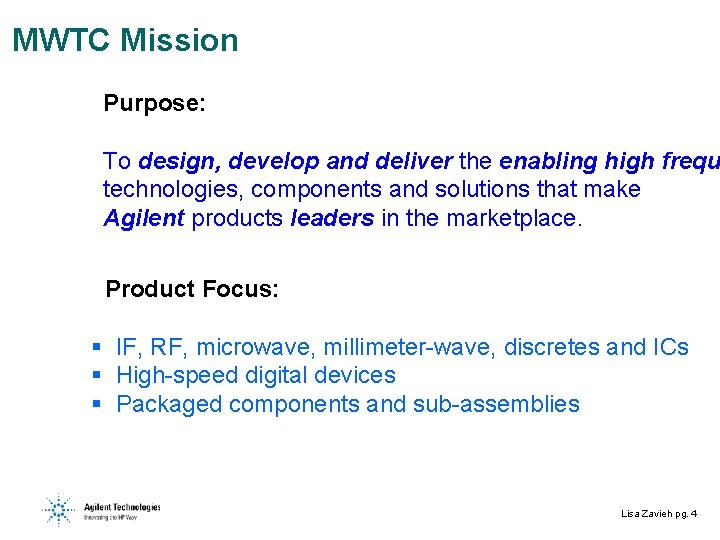

MWTC Mission Purpose: To design, develop and deliver the enabling high frequ technologies, components and solutions that make Agilent products leaders in the marketplace. Product Focus: § IF, RF, microwave, millimeter-wave, discretes and ICs § High-speed digital devices § Packaged components and sub-assemblies Lisa Zavieh pg. 4

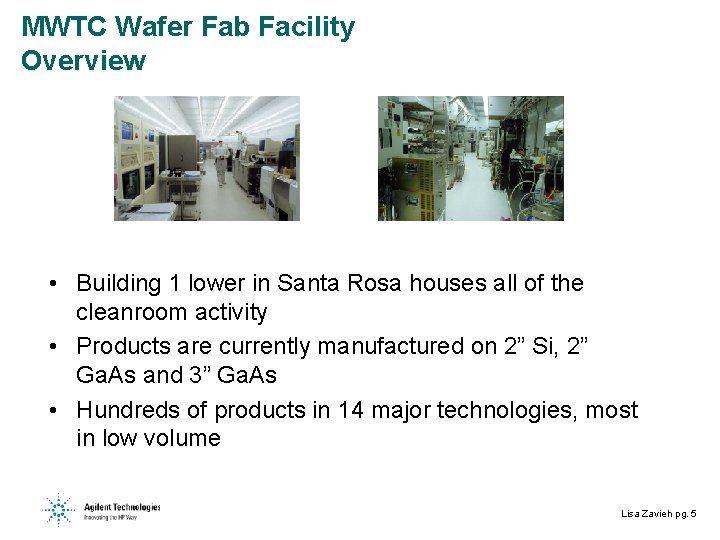

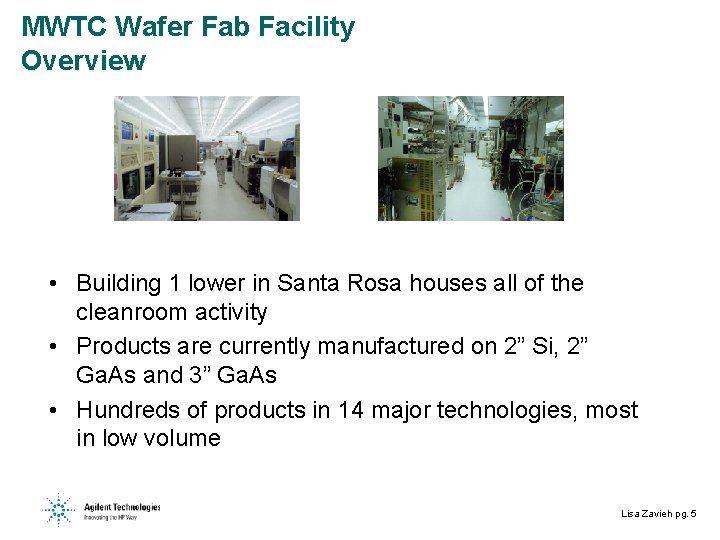

MWTC Wafer Fab Facility Overview • Building 1 lower in Santa Rosa houses all of the cleanroom activity • Products are currently manufactured on 2” Si, 2” Ga. As and 3” Ga. As • Hundreds of products in 14 major technologies, most in low volume Lisa Zavieh pg. 5

Two Technologies: HBT and PHEMT • HBT or Heterojunction Bipolar Transistor • FET or Field Effect Transistor (We actually make something called a PHEMT which is the same as a FET except that the device is pushed to peak design and performance through highly doped lattice mismatched channel, tiny channel length, et cetera) We’re not going to delve into the world of device physics – but we WILL take a look at how these things are made Lisa Zavieh pg. 6

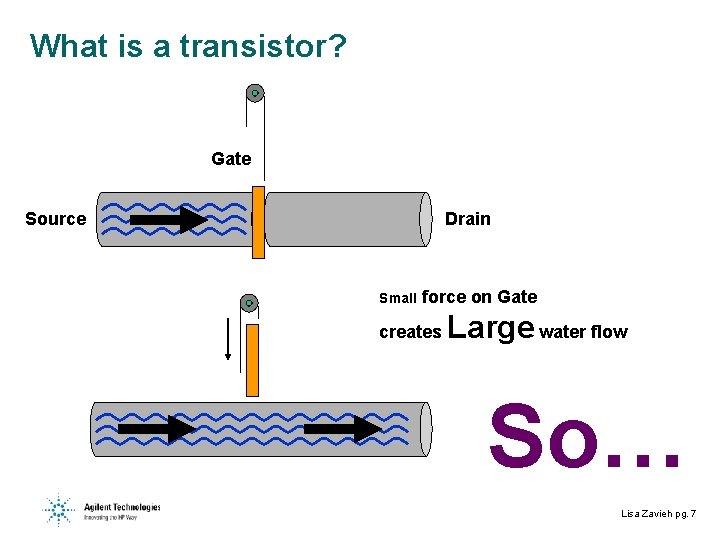

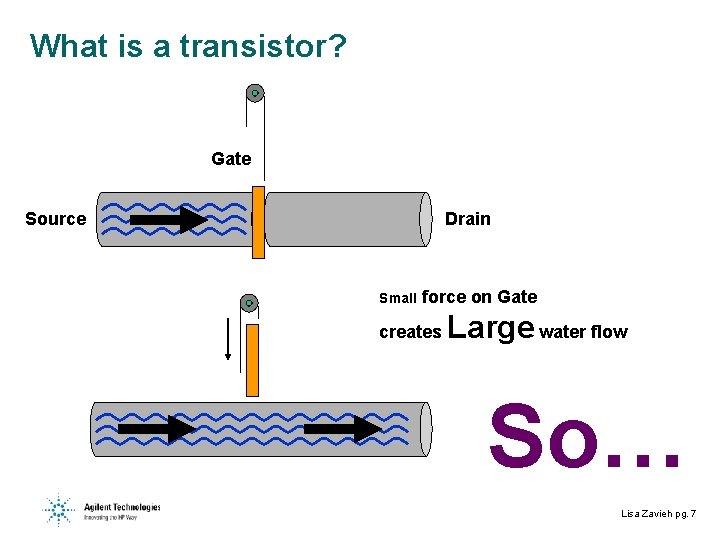

What is a transistor? Gate Source Drain Small force on Gate creates Large water flow So… Lisa Zavieh pg. 7

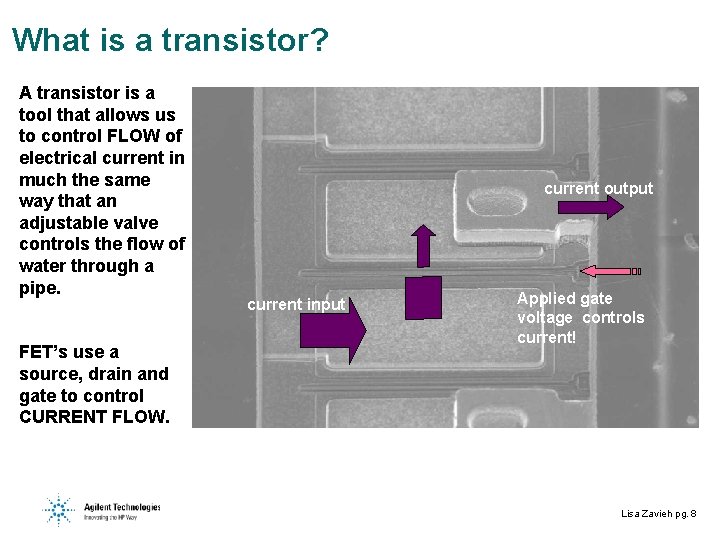

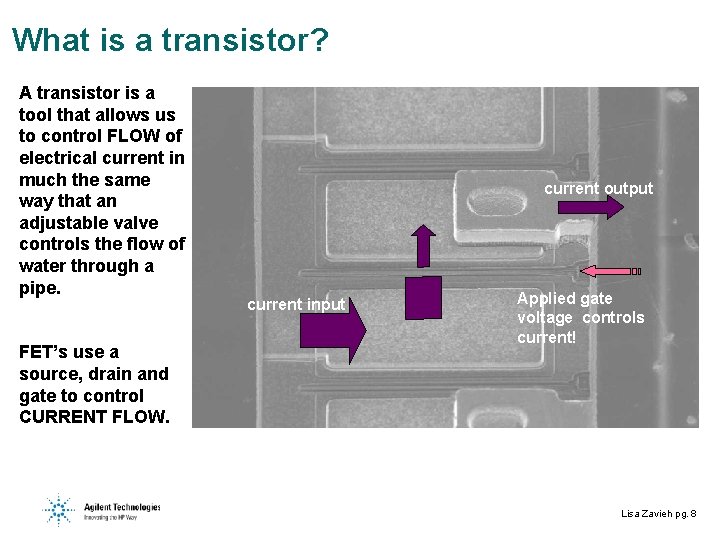

What is a transistor? A transistor is a tool that allows us to control FLOW of electrical current in much the same way that an adjustable valve controls the flow of water through a pipe. FET’s use a source, drain and gate to control CURRENT FLOW. current output current input Applied gate voltage controls current! Lisa Zavieh pg. 8

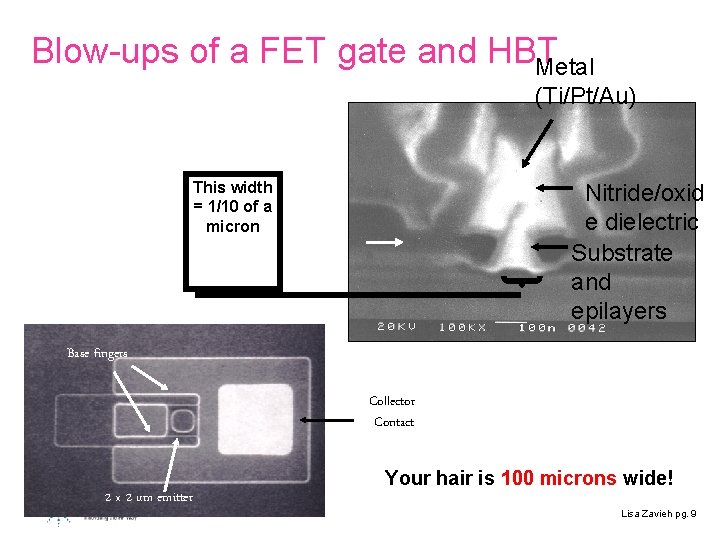

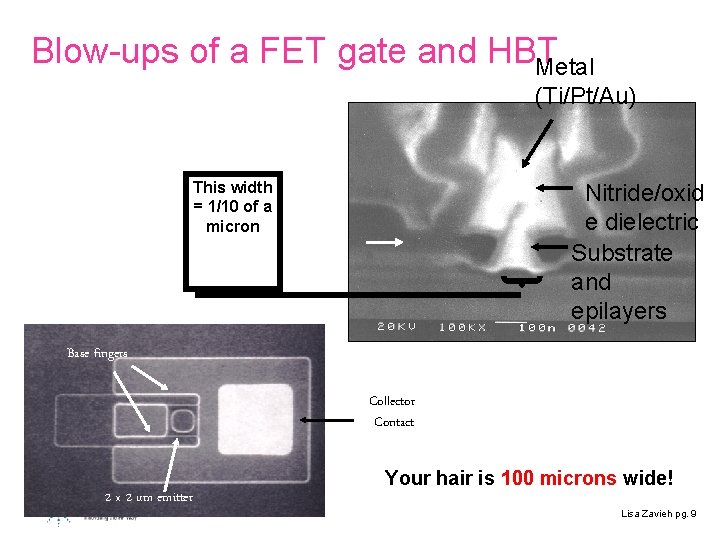

Blow-ups of a FET gate and HBT Metal (Ti/Pt/Au) This width = 1/10 of a micron Nitride/oxid e dielectric Substrate and epilayers Base fingers Collector Contact 2 x 2 um emitter Your hair is 100 microns wide! Lisa Zavieh pg. 9

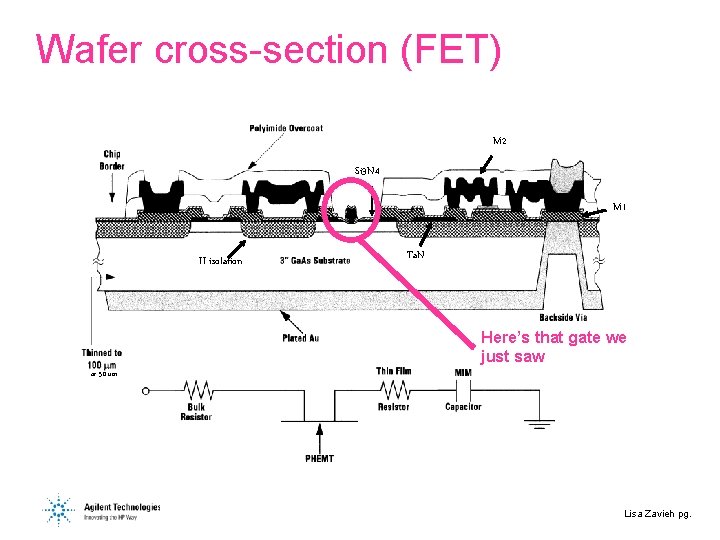

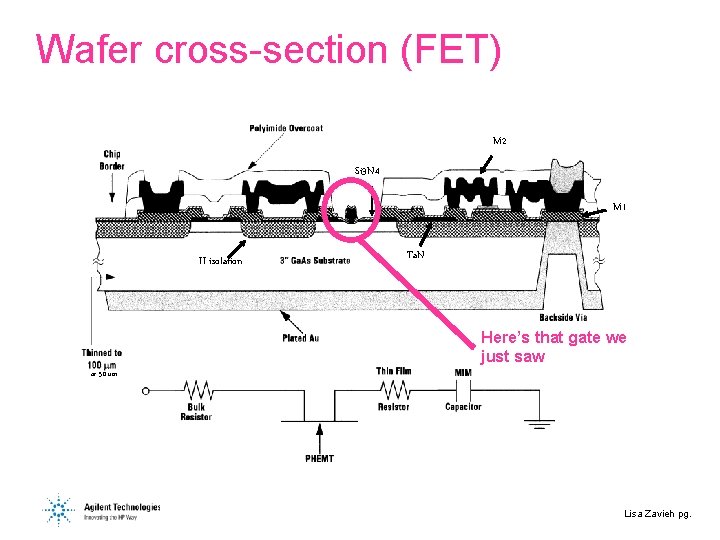

Wafer cross-section (FET) M 2 Si 3 N 4 M 1 II isolation Ta. N Here’s that gate we just saw or 50 um Lisa Zavieh pg.

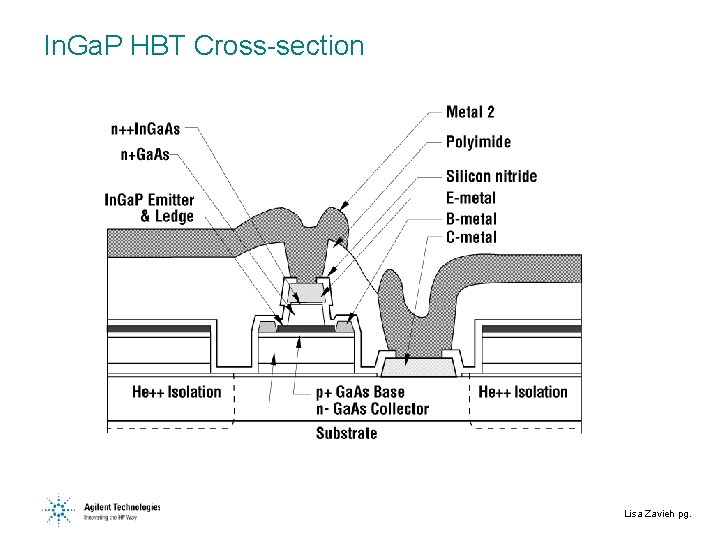

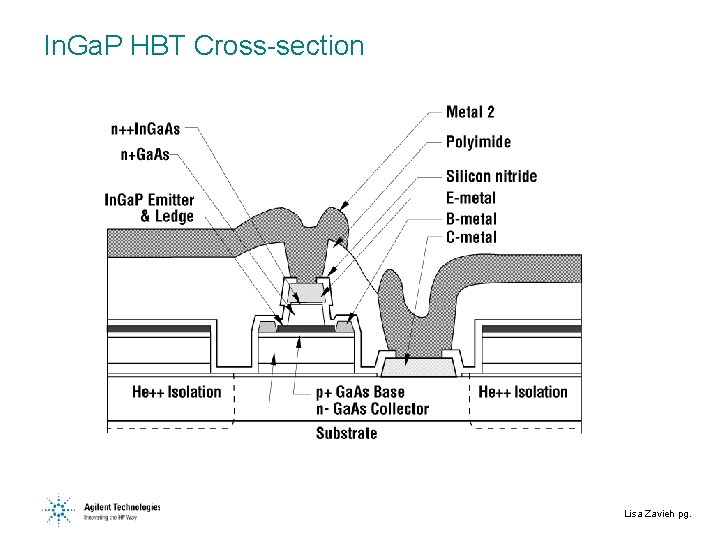

In. Ga. P HBT Cross-section Lisa Zavieh pg.

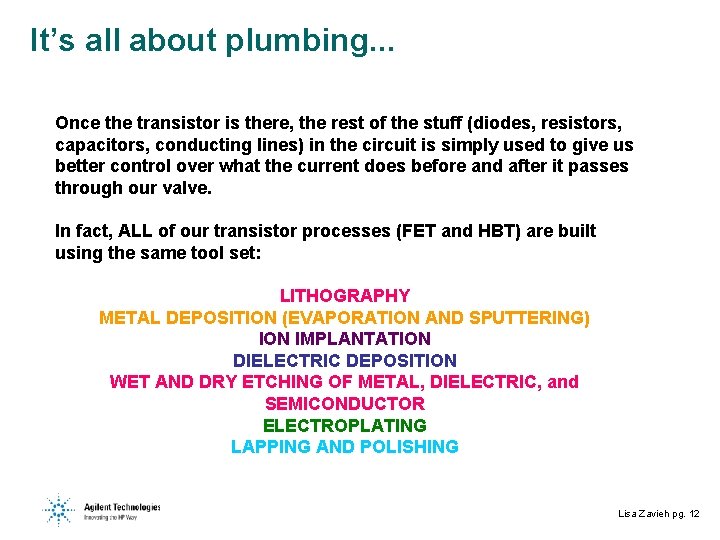

It’s all about plumbing. . . Once the transistor is there, the rest of the stuff (diodes, resistors, capacitors, conducting lines) in the circuit is simply used to give us better control over what the current does before and after it passes through our valve. In fact, ALL of our transistor processes (FET and HBT) are built using the same tool set: LITHOGRAPHY METAL DEPOSITION (EVAPORATION AND SPUTTERING) ION IMPLANTATION DIELECTRIC DEPOSITION WET AND DRY ETCHING OF METAL, DIELECTRIC, and SEMICONDUCTOR ELECTROPLATING LAPPING AND POLISHING Lisa Zavieh pg. 12

Lithography Lisa Zavieh pg. 13

Lithography All of these devices are constructed layer by layer In some cases there as many as 20 layers per circuit!!! Each layer has a “mask” defining the regions of interest. This mask is transferred to the wafer using a process called “lithography” Lisa Zavieh pg. 14

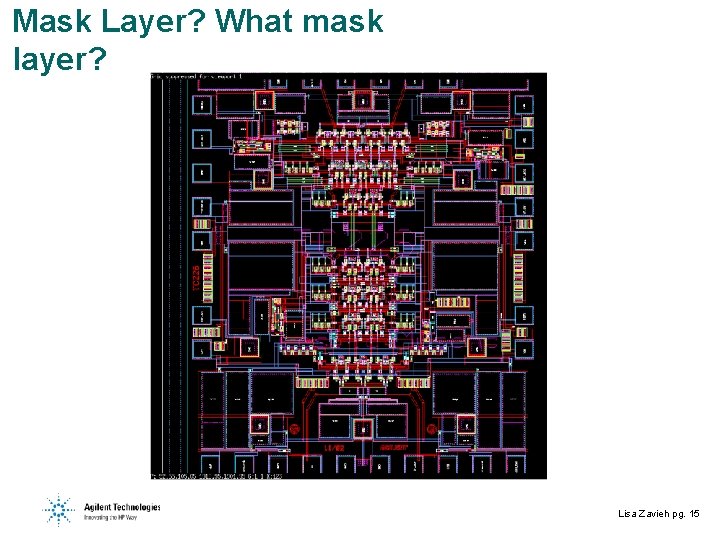

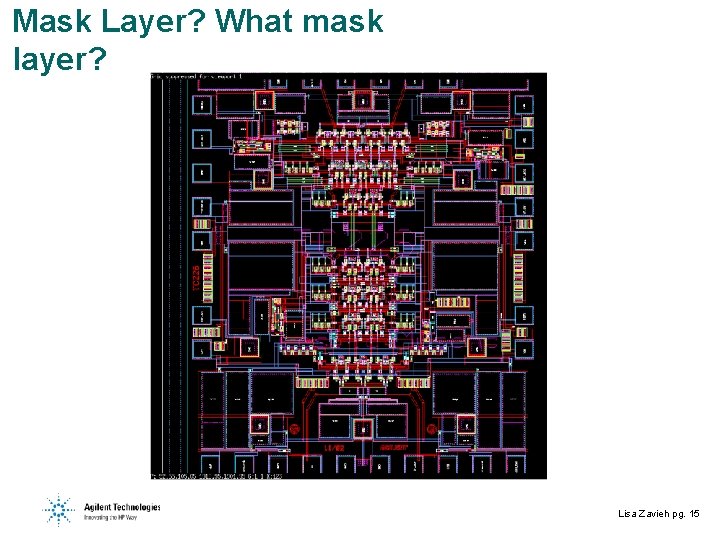

Mask Layer? What mask layer? Lisa Zavieh pg. 15

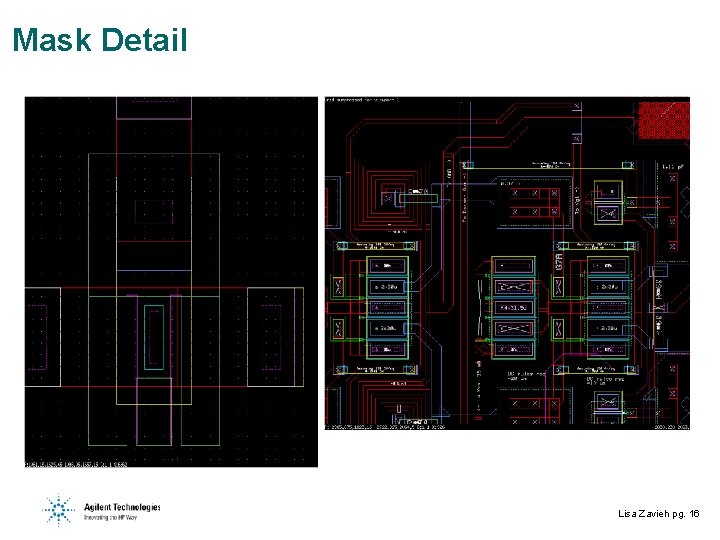

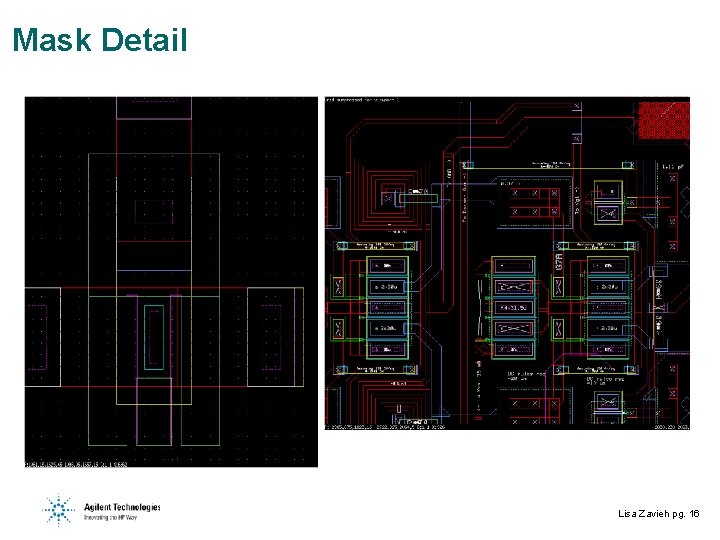

Mask Detail Lisa Zavieh pg. 16

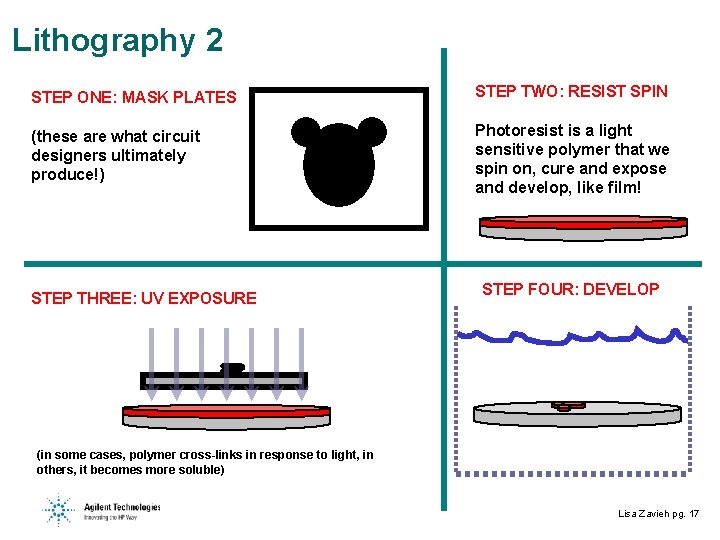

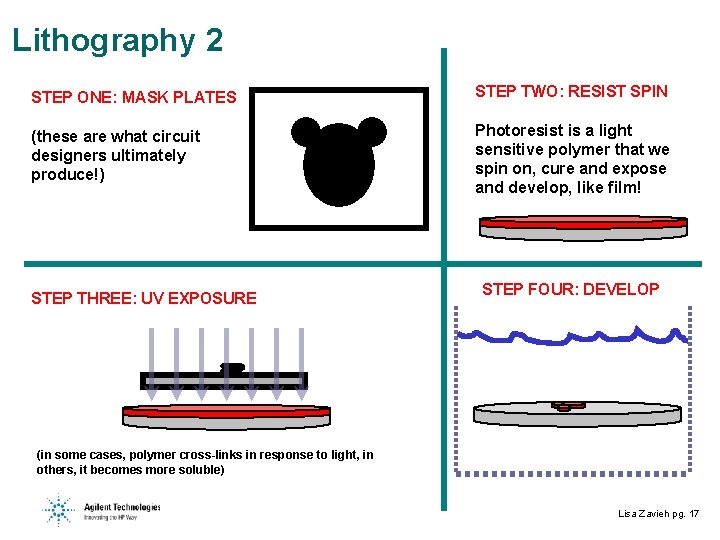

Lithography 2 STEP ONE: MASK PLATES STEP TWO: RESIST SPIN (these are what circuit designers ultimately produce!) Photoresist is a light sensitive polymer that we spin on, cure and expose and develop, like film! STEP THREE: UV EXPOSURE STEP FOUR: DEVELOP (in some cases, polymer cross-links in response to light, in others, it becomes more soluble) Lisa Zavieh pg. 17

Metal Deposition Lisa Zavieh pg. 18

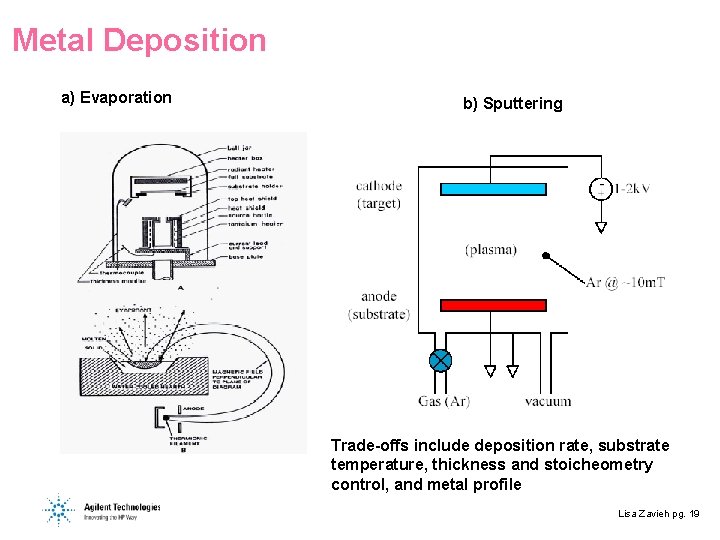

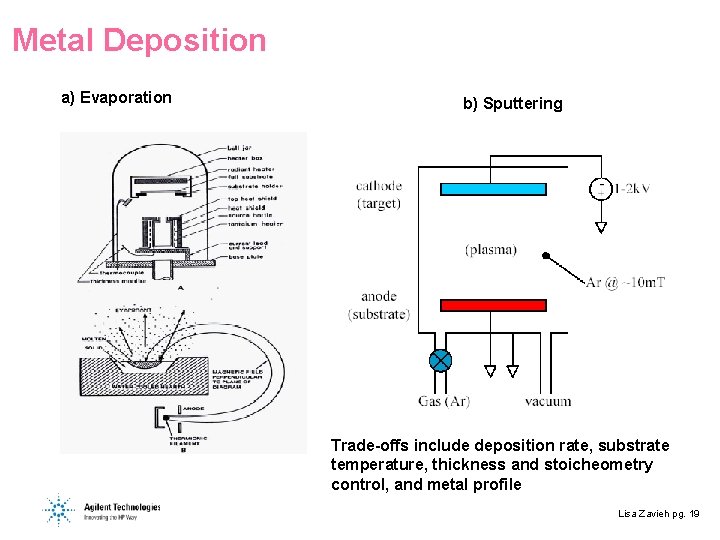

Metal Deposition a) Evaporation b) Sputtering Trade-offs include deposition rate, substrate temperature, thickness and stoicheometry control, and metal profile Lisa Zavieh pg. 19

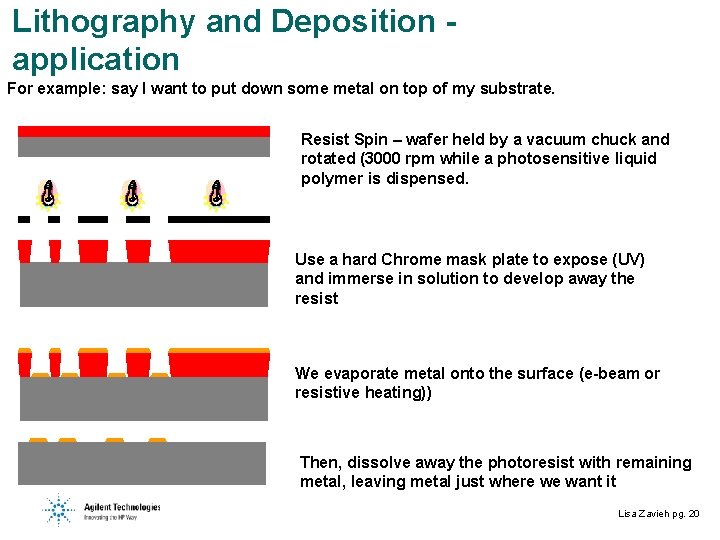

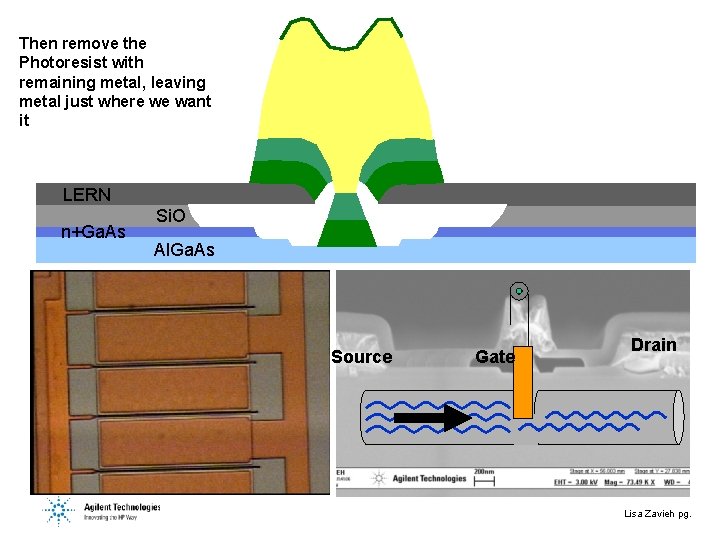

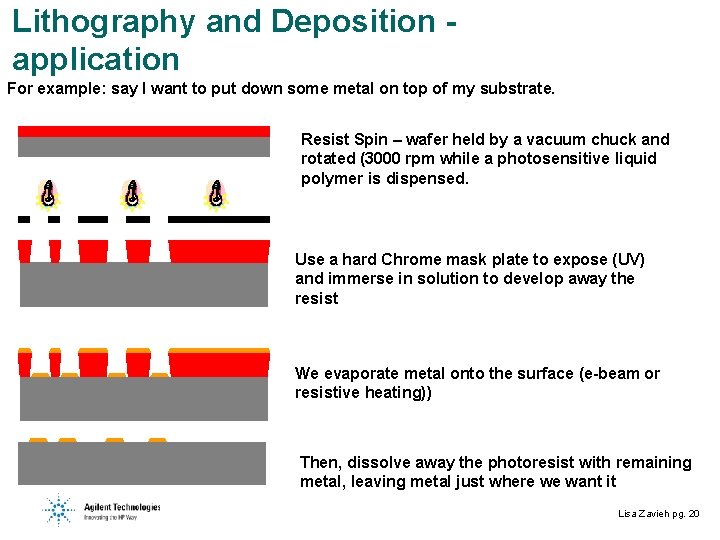

Lithography and Deposition application For example: say I want to put down some metal on top of my substrate. Resist Spin – wafer held by a vacuum chuck and rotated (3000 rpm while a photosensitive liquid polymer is dispensed. Use a hard Chrome mask plate to expose (UV) and immerse in solution to develop away the resist We evaporate metal onto the surface (e-beam or resistive heating)) Then, dissolve away the photoresist with remaining metal, leaving metal just where we want it Lisa Zavieh pg. 20

Dielectric Deposition Lisa Zavieh pg. 21

See more about this on the next page! Dielectric Deposition (PECVD) You’ll see both OXIDE and NITRIDE throughout the fab processes. These two layers are very important, mostly because we can use both of them to STOP current from flowing between metal layers. Often we use dielectrics to keep current from “leaking!” E D XI O “Just a little leak folks!” We’ll have ya all fixed up in a jiffy!” Lisa Zavieh pg. 22

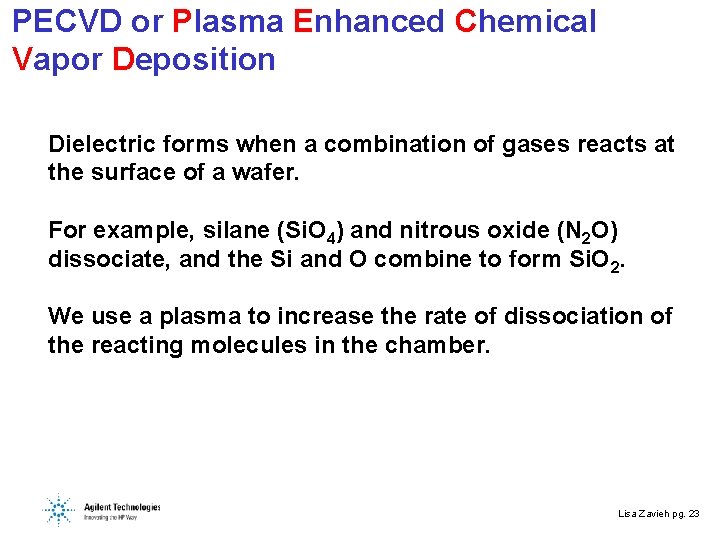

PECVD or Plasma Enhanced Chemical Vapor Deposition Dielectric forms when a combination of gases reacts at the surface of a wafer. For example, silane (Si. O 4) and nitrous oxide (N 2 O) dissociate, and the Si and O combine to form Si. O 2. We use a plasma to increase the rate of dissociation of the reacting molecules in the chamber. Lisa Zavieh pg. 23

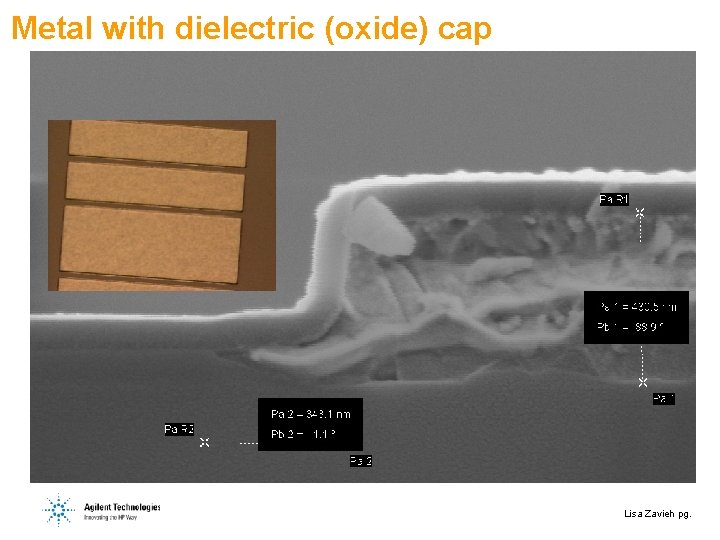

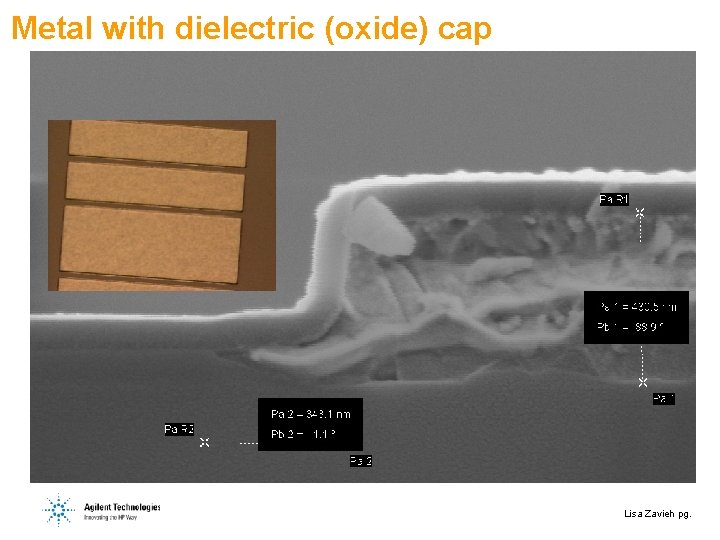

Metal with dielectric (oxide) cap Lisa Zavieh pg.

Isolation Lisa Zavieh pg. 25

Isolation As you know, METALS are REALLY good at conducting electricity. INSULATORS or DIELECTRICS are bad at conducting electricity. Si, Ge, and Ga. As are semiconductors. That means they conduct … just not very well. We can use proton isolation to turn semiconductors into insulators in specific regions. Lisa Zavieh pg. 26

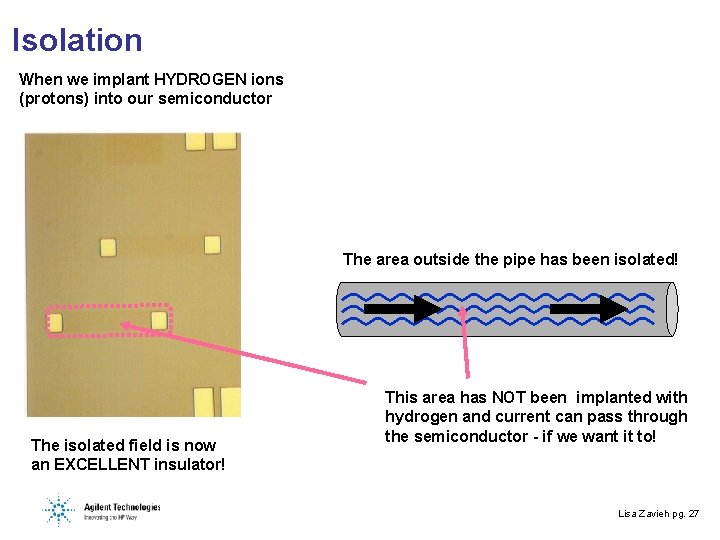

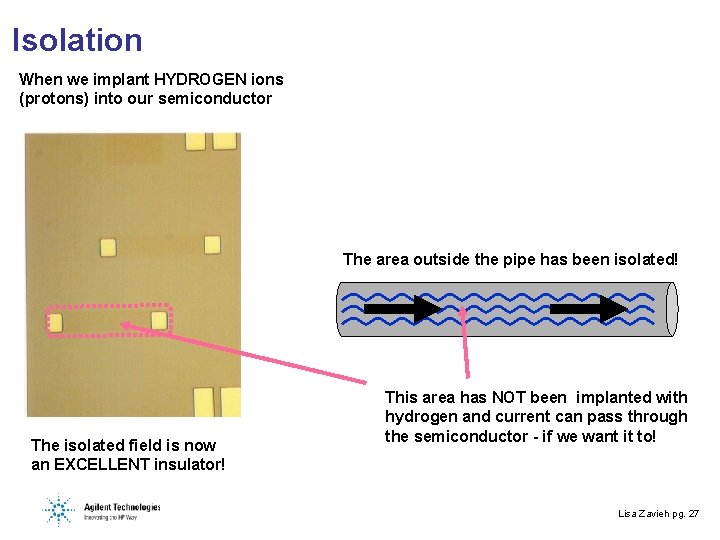

Isolation When we implant HYDROGEN ions (protons) into our semiconductor The area outside the pipe has been isolated! The isolated field is now an EXCELLENT insulator! This area has NOT been implanted with hydrogen and current can pass through the semiconductor - if we want it to! Lisa Zavieh pg. 27

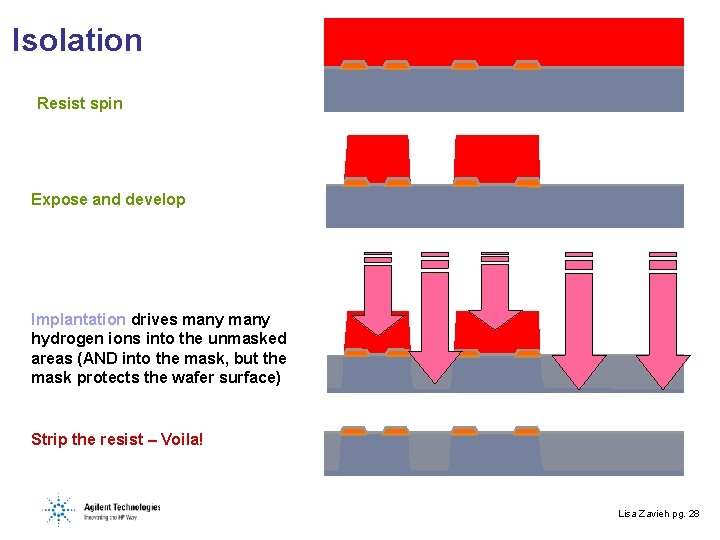

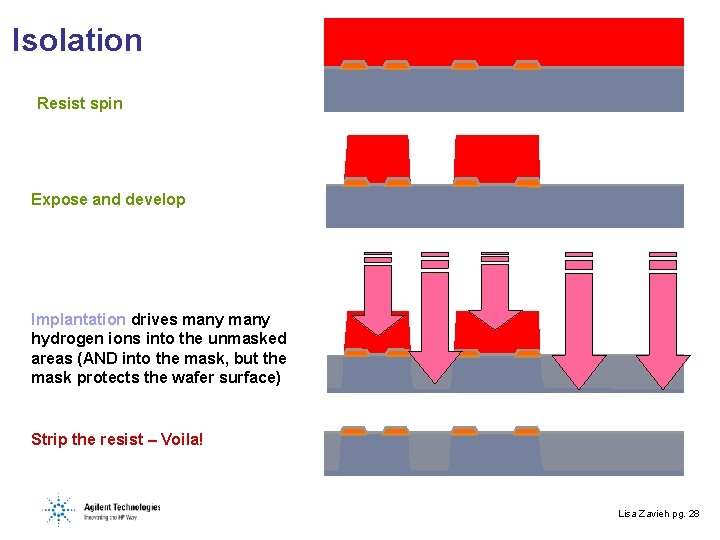

Isolation Resist spin Expose and develop Implantation drives many hydrogen ions into the unmasked areas (AND into the mask, but the mask protects the wafer surface) Strip the resist – Voila! Lisa Zavieh pg. 28

Ohmic Contacts Lisa Zavieh pg. 29

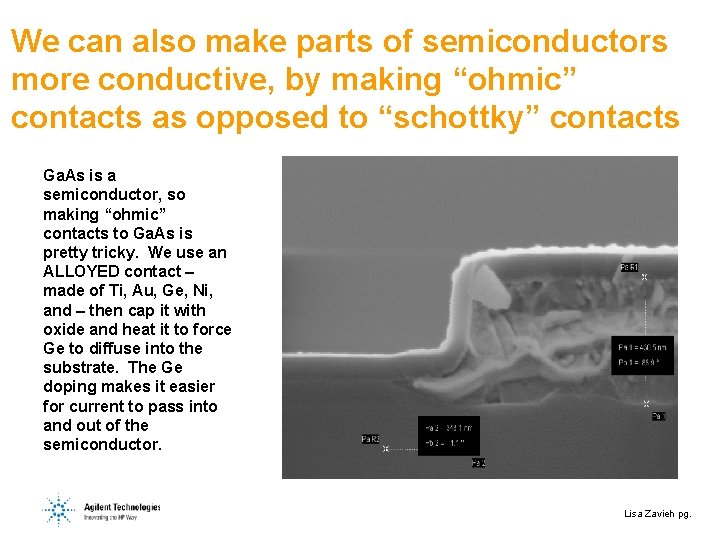

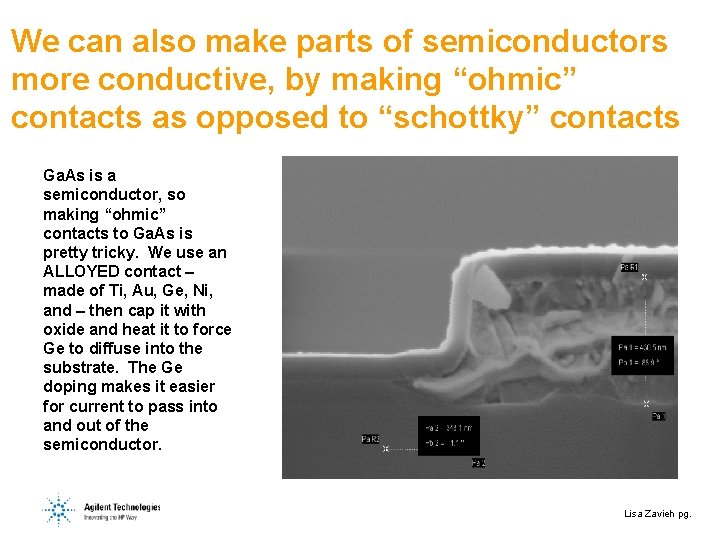

We can also make parts of semiconductors more conductive, by making “ohmic” contacts as opposed to “schottky” contacts Ga. As is a semiconductor, so making “ohmic” contacts to Ga. As is pretty tricky. We use an ALLOYED contact – made of Ti, Au, Ge, Ni, and – then cap it with oxide and heat it to force Ge to diffuse into the substrate. The Ge doping makes it easier for current to pass into and out of the semiconductor. Lisa Zavieh pg.

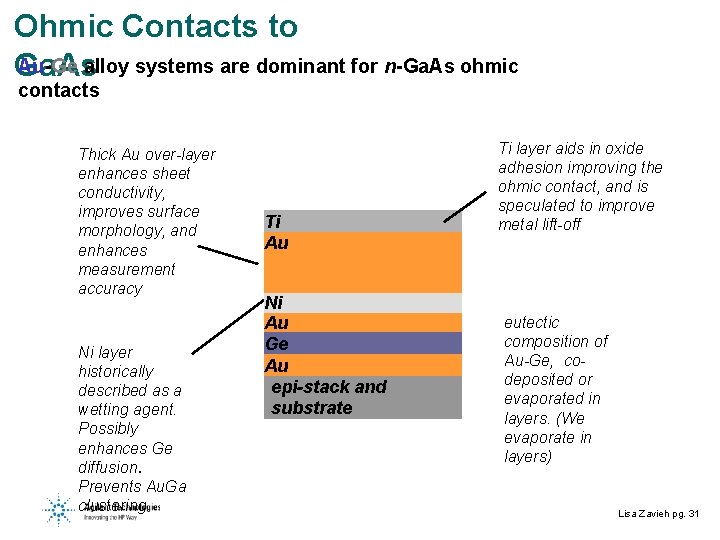

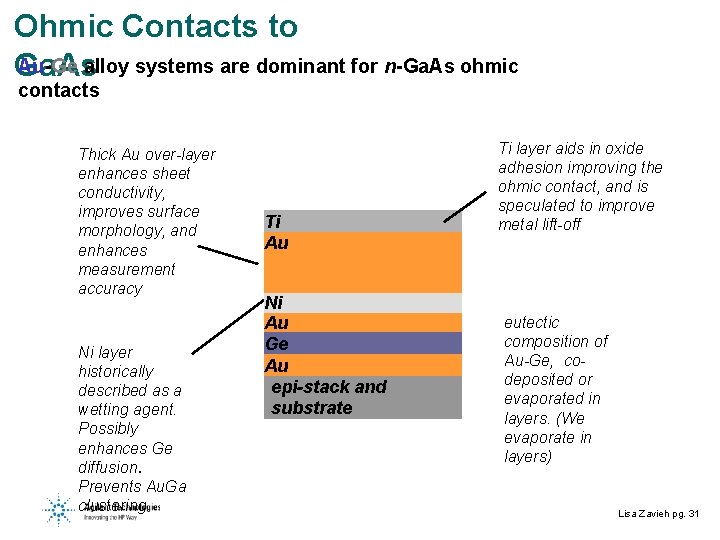

Ohmic Contacts to Au-Ge alloy systems are dominant for n-Ga. As ohmic Ga. As contacts Thick Au over-layer enhances sheet conductivity, improves surface morphology, and enhances measurement accuracy Ni layer historically described as a wetting agent. Possibly enhances Ge diffusion. Prevents Au. Ga clustering. Ti Au Ni Au Ge Au epi-stack and substrate Ti layer aids in oxide adhesion improving the ohmic contact, and is speculated to improve metal lift-off eutectic composition of Au-Ge, codeposited or evaporated in layers. (We evaporate in layers) Lisa Zavieh pg. 31

Etching Lisa Zavieh pg. 32

Etching Wet Etching vs Dry Etching Wet Etching: the etch reactants come form a liquid source Dry Etching: the etch reactants come form a gas or vapor phase source and are typically ionized. Atoms or ions from the gas are the reactive species that etch the exposed film • Selectivity : In general, dry etching has less selectivity than wet etching • Anisotropy: In general, dry etching has higher degree of anisotropy than wet etching (exception being certain crystallographic etches) • Etch Rate: In general, dry etch has lower etch rate than wet etching • Etch Control: Dry etching is much easier to start and stop than wet etching NOTE: Dry etching is $$$$, but absolutely essential for high resolution or if you need deep vertical sidewalls. Lisa Zavieh pg. 33

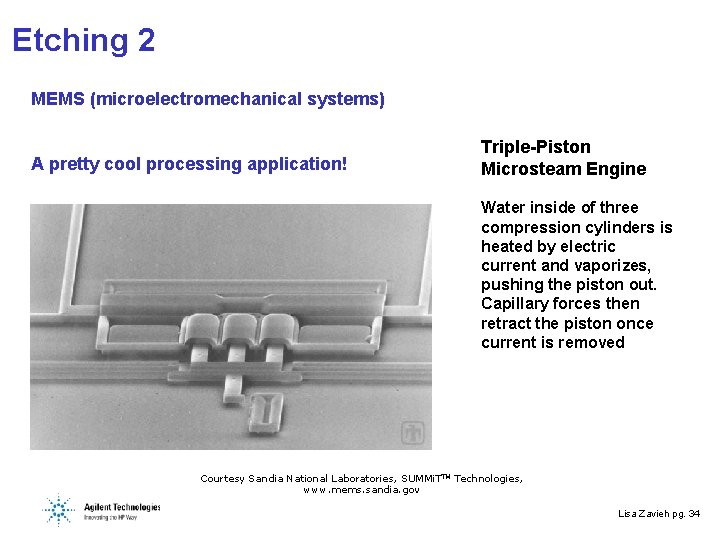

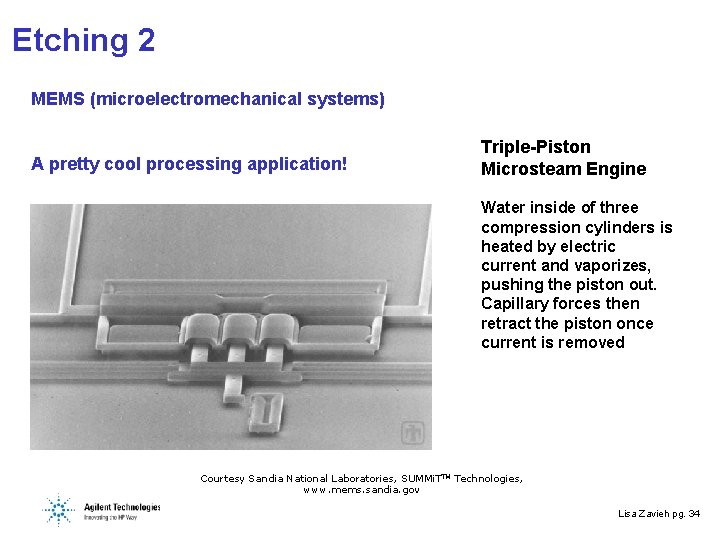

Etching 2 MEMS (microelectromechanical systems) A pretty cool processing application! Triple-Piston Microsteam Engine Water inside of three compression cylinders is heated by electric current and vaporizes, pushing the piston out. Capillary forces then retract the piston once current is removed Courtesy Sandia National Laboratories, SUMMi. TTM Technologies, www. mems. sandia. gov Lisa Zavieh pg. 34

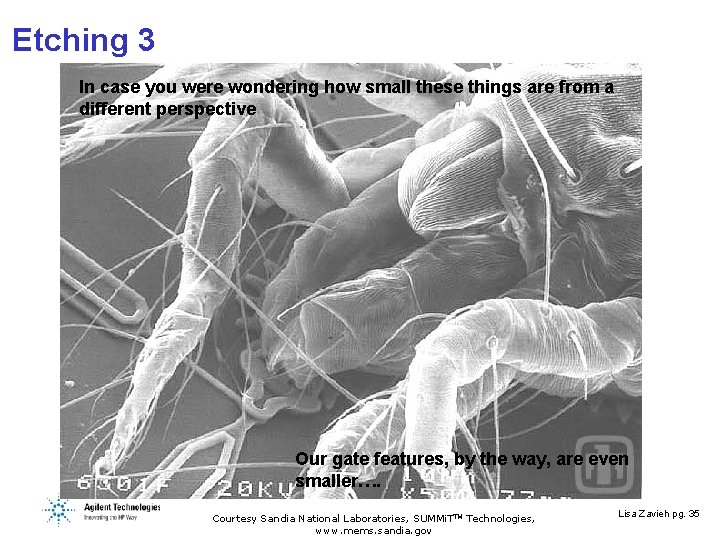

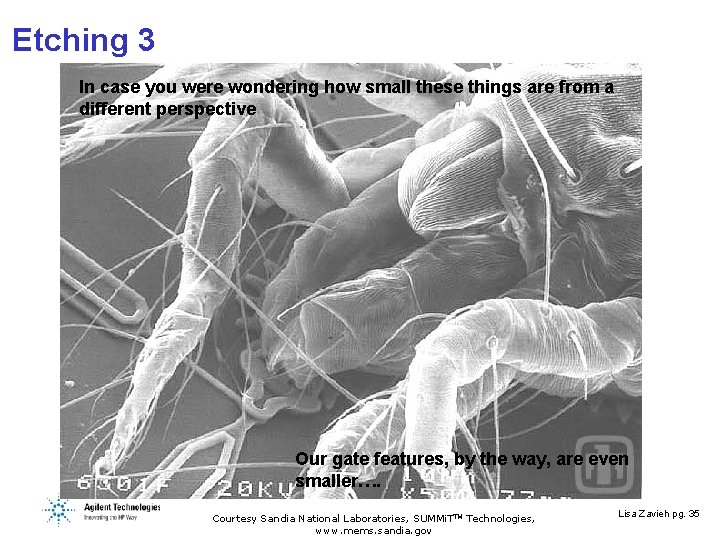

Etching 3 In case you were wondering how small these things are from a different perspective Our gate features, by the way, are even smaller…. Courtesy Sandia National Laboratories, SUMMi. TTM Technologies, www. mems. sandia. gov Lisa Zavieh pg. 35

The individual processes may seem straightforward, but we have to do some pretty crafty things to make them all come together! To make “gates” for example… Lisa Zavieh pg. 36

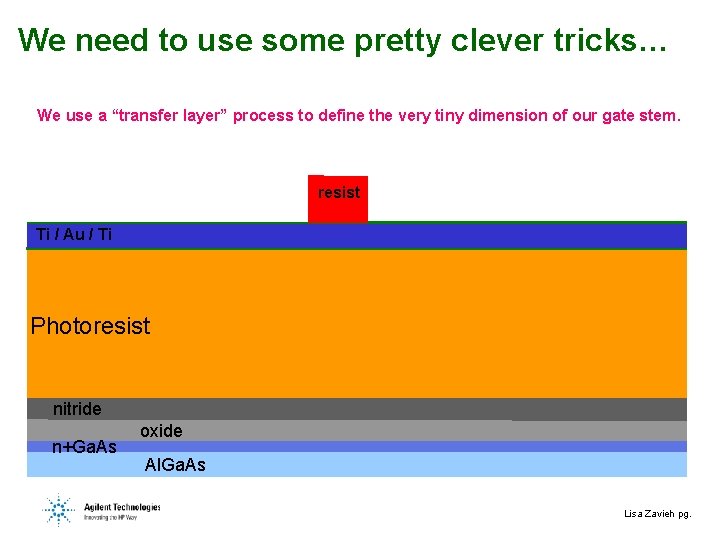

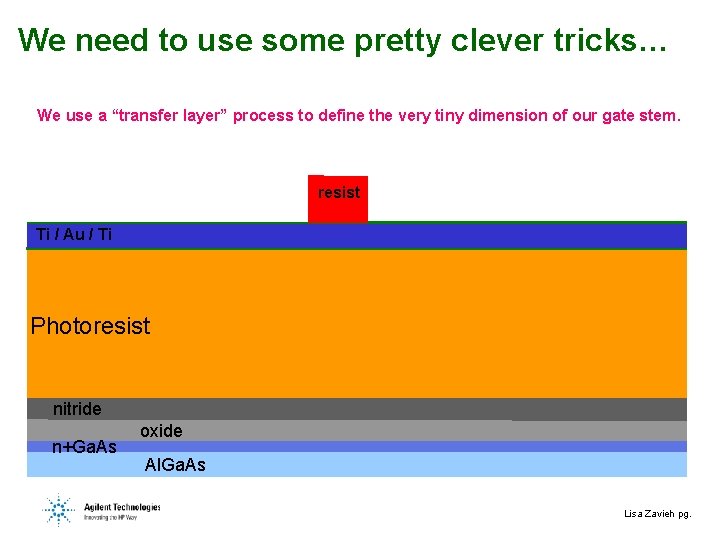

We need to use some pretty clever tricks… We use a “transfer layer” process to define the very tiny dimension of our gate stem. resist Ti / Au / Ti Photoresist nitride n+Ga. As oxide Al. Ga. As Lisa Zavieh pg.

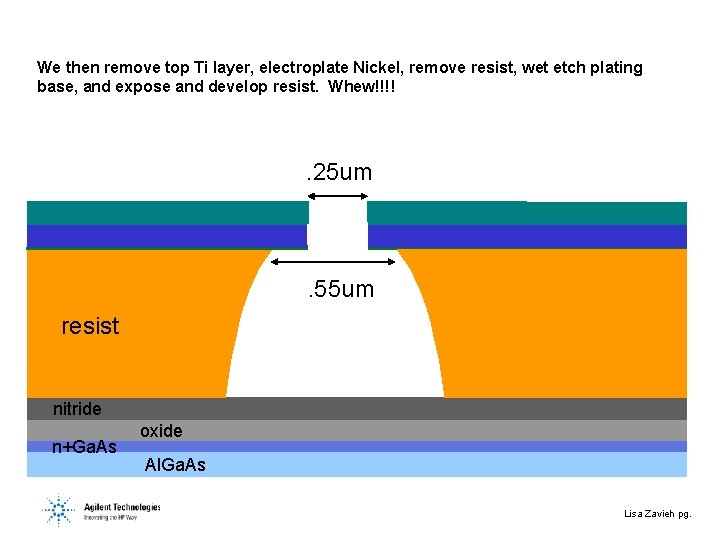

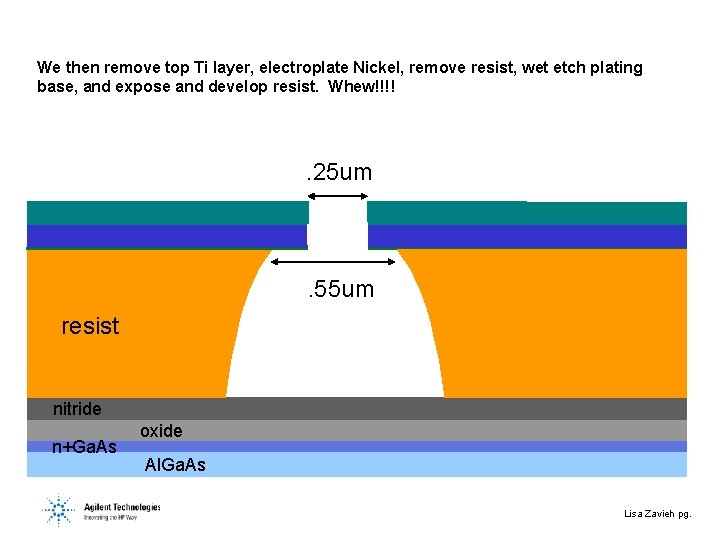

We then remove top Ti layer, electroplate Nickel, remove resist, wet etch plating base, and expose and develop resist. Whew!!!! . 25 um . 55 um resist nitride n+Ga. As oxide Al. Ga. As Lisa Zavieh pg.

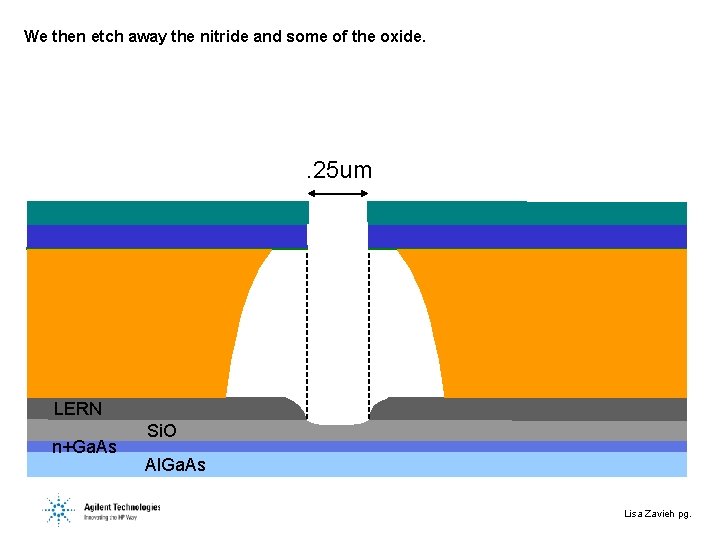

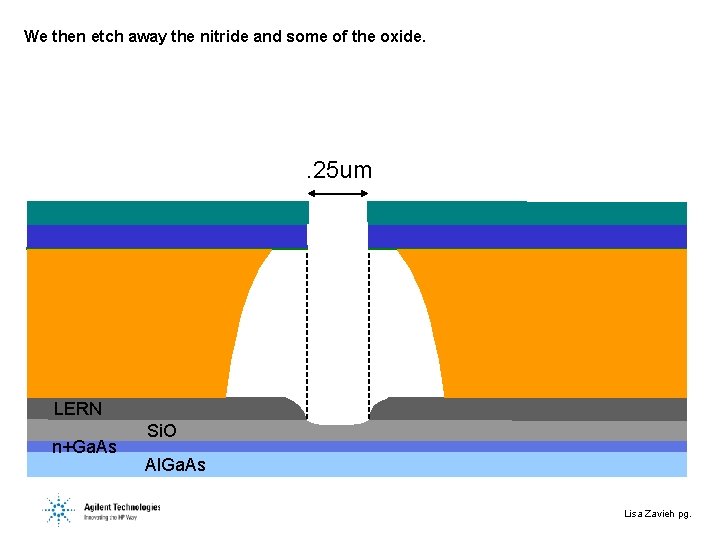

We then etch away the nitride and some of the oxide. . 25 um PMGI LERN n+Ga. As Si. O Al. Ga. As Lisa Zavieh pg.

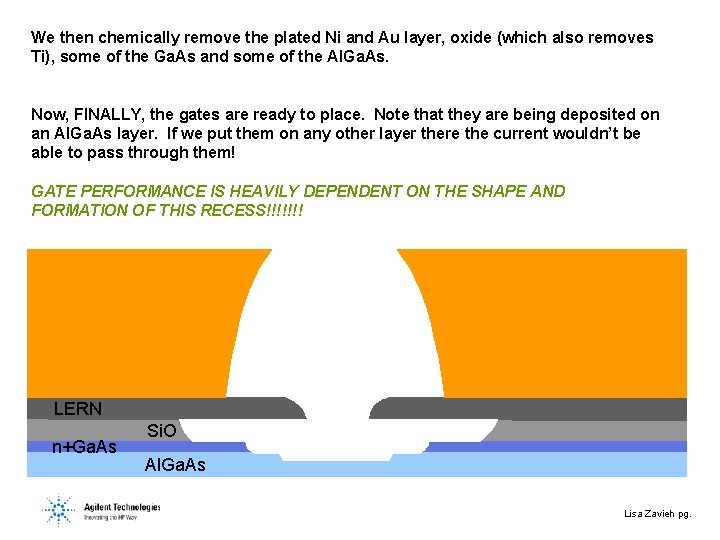

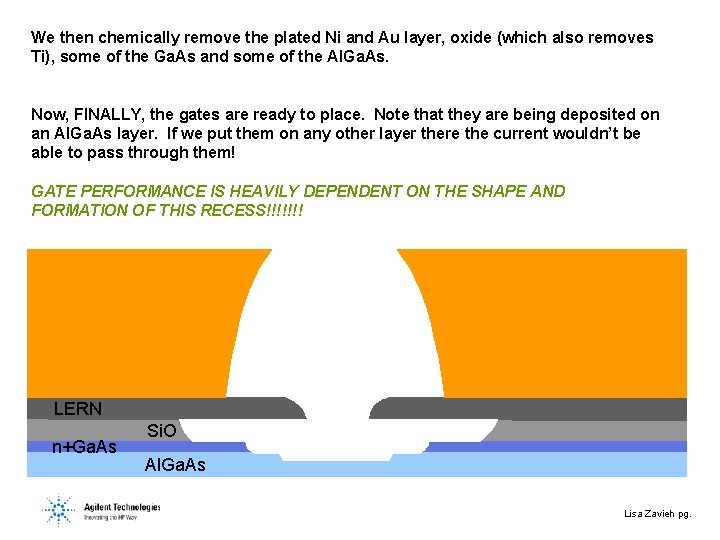

We then chemically remove the plated Ni and Au layer, oxide (which also removes Ti), some of the Ga. As and some of the Al. Ga. As. Now, FINALLY, the gates are ready to place. Note that they are being deposited on an Al. Ga. As layer. If we put them on any other layer there the current wouldn’t be able to pass through them! GATE PERFORMANCE IS HEAVILY DEPENDENT ON THE SHAPE AND FORMATION OF THIS RECESS!!!!!!! PMGI LERN n+Ga. As Si. O Al. Ga. As Lisa Zavieh pg.

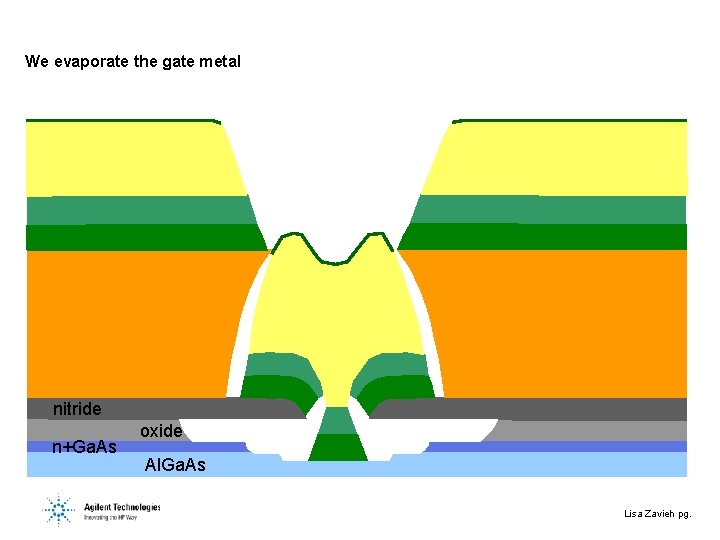

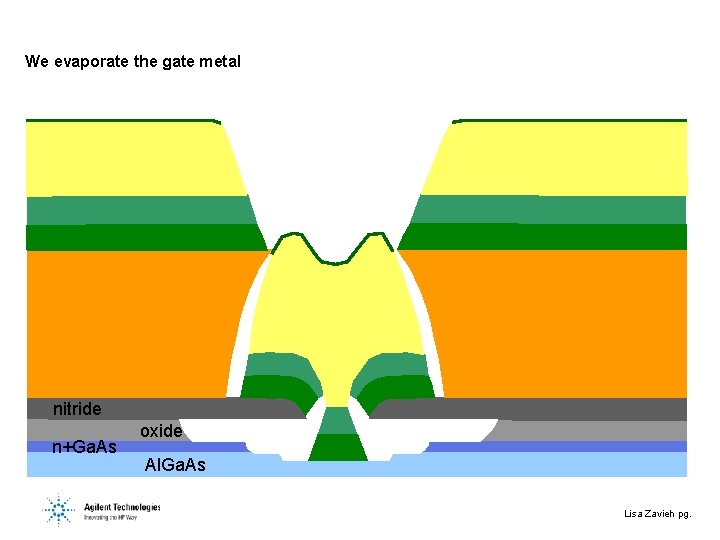

We evaporate the gate metal PMGI nitride n+Ga. As oxide Al. Ga. As Lisa Zavieh pg.

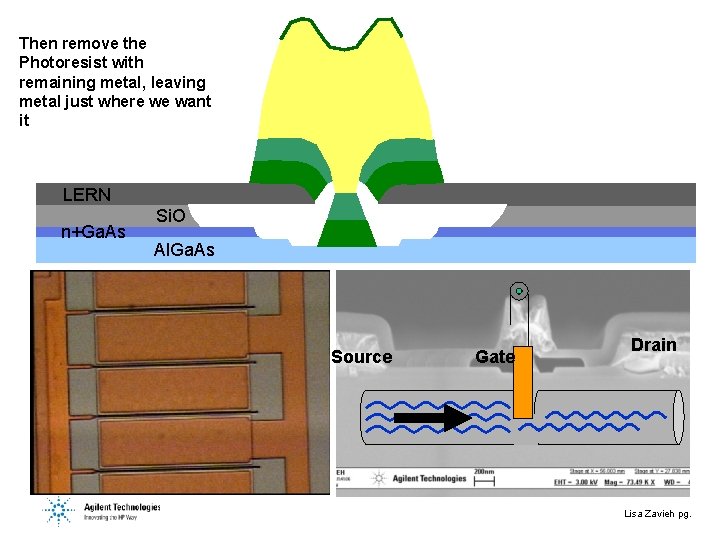

Then remove the Photoresist with remaining metal, leaving metal just where we want it LERN n+Ga. As Si. O Al. Ga. As Source Gate Drain Lisa Zavieh pg.

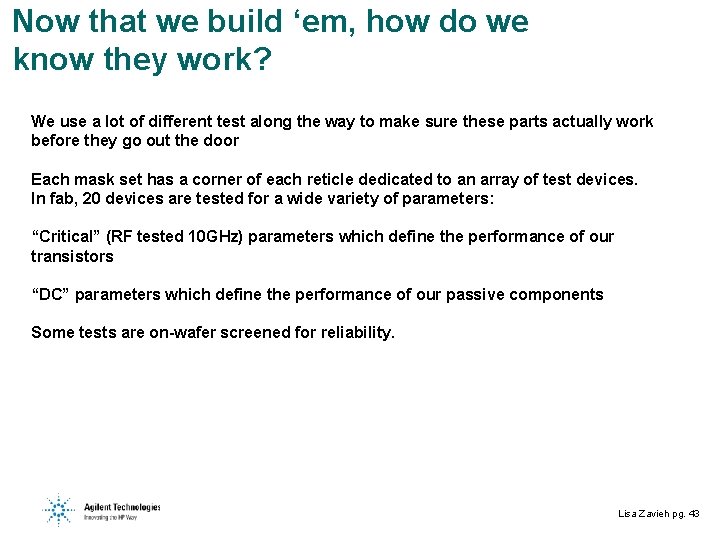

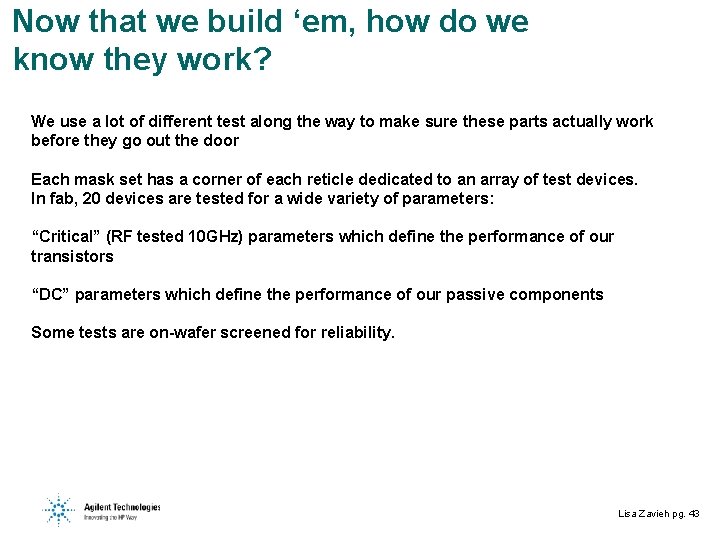

Now that we build ‘em, how do we know they work? We use a lot of different test along the way to make sure these parts actually work before they go out the door Each mask set has a corner of each reticle dedicated to an array of test devices. In fab, 20 devices are tested for a wide variety of parameters: “Critical” (RF tested 10 GHz) parameters which define the performance of our transistors “DC” parameters which define the performance of our passive components Some tests are on-wafer screened for reliability. Lisa Zavieh pg. 43

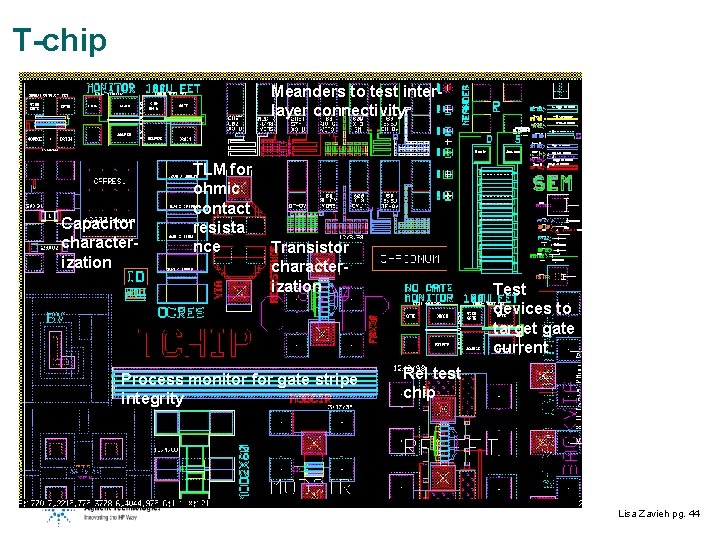

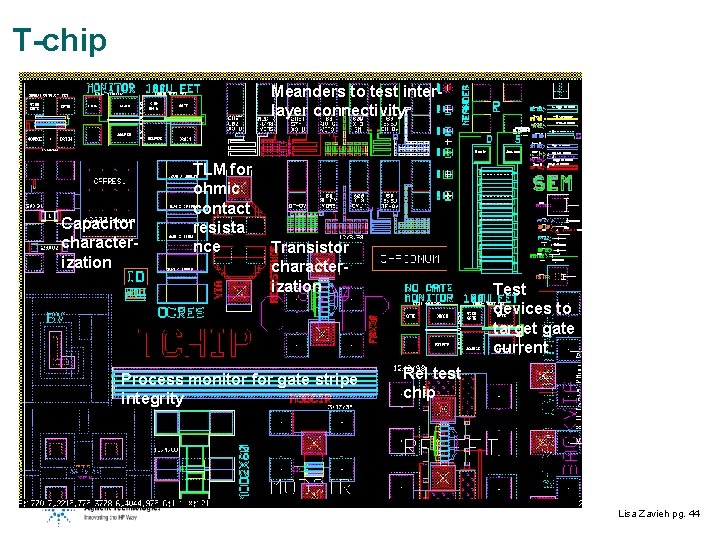

T-chip Meanders to test interlayer connectivity Capacitor characterization TLM for ohmic contact resista nce Transistor characterization Process monitor for gate stripe integrity Test devices to target gate current Rel test chip Lisa Zavieh pg. 44

Conclusion We use a HUGE array of people to make and characterize devices: Electrical engineers Materials Engineers Chemical Engineers Mechanical Engineers Physicists Chemists Design Engineers A vast array of technicians and operators Managers Supervisors Planners Procurement experts Maintenance teams We all have our specialties, and we all work together! Lisa Zavieh pg. 45

Acknowledgements Agilent MWTC Don D’Avanzo Mathias Bonse Dan Thomasson Lisa Zavieh pg. 46