The Advanced Power Semiconductor Laboratory at ETH Zurich

The Advanced Power Semiconductor Laboratory at ETH Zurich – from semiconductor materials to module reliability Ulrike Grossner | 19 Apr 2018 | 1

The Advanced Power Semiconductor Laboratory APS § Established in 2015 § Based on an departmental initiative to strengthen the Research Area “Energy” § Start-up phase supported by ETH Foundation Ulrike Grossner | 19 Apr 2018 | 2

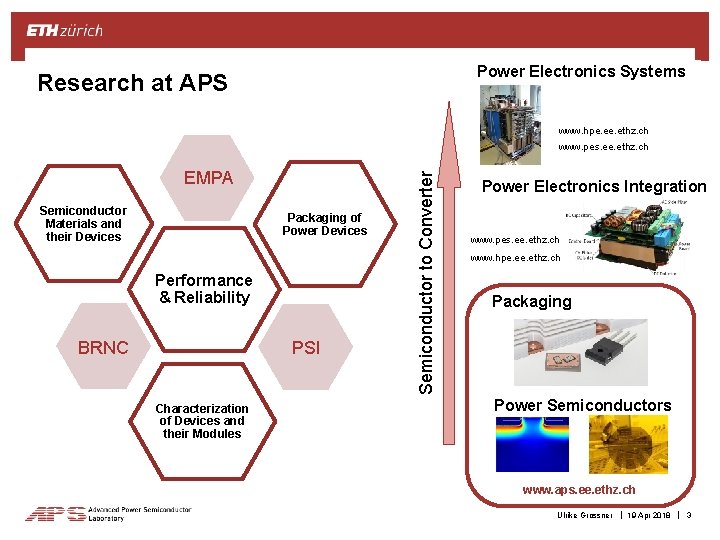

Power Electronics Systems Research at APS www. hpe. ethz. ch EMPA Semiconductor Materials and their Devices Packaging of Power Devices Performance & Reliability BRNC PSI Characterization of Devices and their Modules Semiconductor to Converter www. pes. ee. ethz. ch Power Electronics Integration www. pes. ee. ethz. ch www. hpe. ethz. ch Packaging Power Semiconductors www. aps. ee. ethz. ch Ulrike Grossner | 19 Apr 2018 | 3

Establishing the research infrastructure § Simulation tools from material to circuit level § Introducing Si. C to ETH cleanroom facilities § Setup of electrical characterization laboratory § Partnering within ETH domain PSI, EMPA – large scale facilities at PSI, radiation hardness, advanced bonding technologies Ulrike Grossner | 19 Apr 2018 | 4

First projects 2015 – 2017 T E F § Understanding Si. C TCAD simulation § Si. C MOSFET manufacturing m 0 § Si. O 2 -Si. C interface with PSI 8 V k 2 . § Bonding technologies with EMPA : 1 e ee r C S O M n eli s a b § Module design for high-voltage devices g in h lis b § Setting upstmodule simulation tools – Ansys Q 3 D… a E Ulrike Grossner | 19 Apr 2018 | 5

Deep-Level Transient Spectroscopy (DLTS) § Determination of energy levels § PN junctions § Schottky junctions § MIS capacitors § Characteristics § Bias voltage [-100 V, 100 V] § Res. of 0. 3 m. V § Min. pulse width 20 ns § Max. current 15 m. A § Res. of 10 p. A § Temperature range [20 K, 800 K] Ulrike Grossner | 19 Apr 2018 | 6

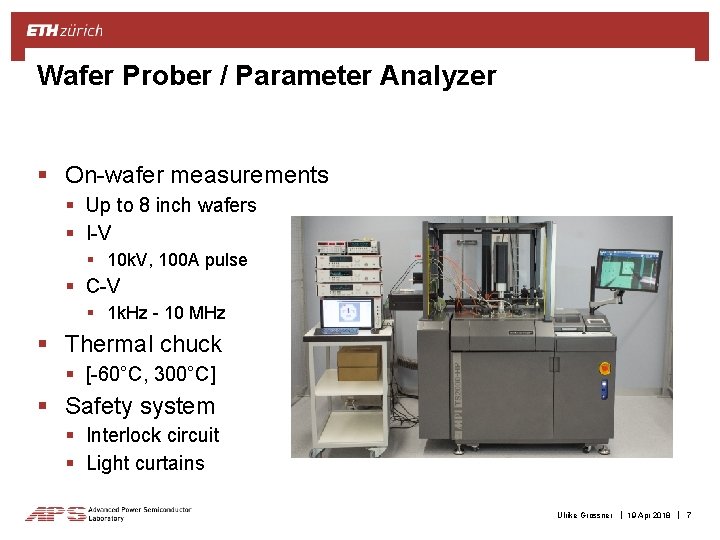

Wafer Prober / Parameter Analyzer § On-wafer measurements § Up to 8 inch wafers § I-V § 10 k. V, 100 A pulse § C-V § 1 k. Hz - 10 MHz § Thermal chuck § [-60°C, 300°C] § Safety system § Interlock circuit § Light curtains Ulrike Grossner | 19 Apr 2018 | 7

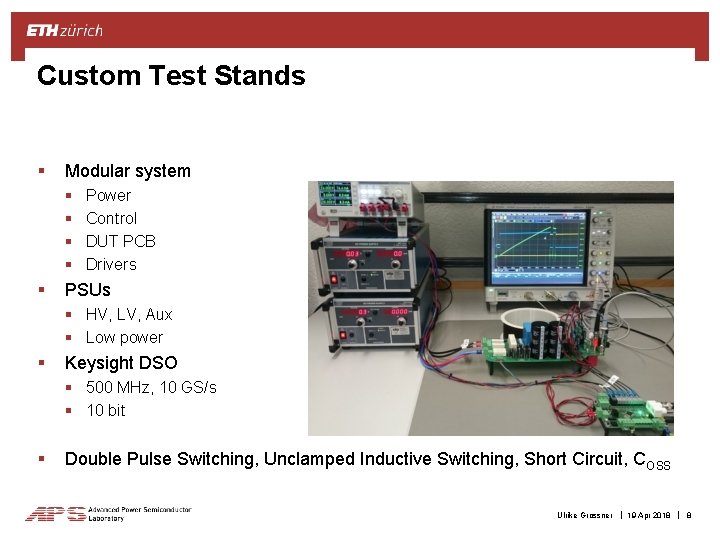

Custom Test Stands § Modular system § § § Power Control DUT PCB Drivers PSUs § HV, LV, Aux § Low power § Keysight DSO § 500 MHz, 10 GS/s § 10 bit § Double Pulse Switching, Unclamped Inductive Switching, Short Circuit, COSS Ulrike Grossner | 19 Apr 2018 | 8

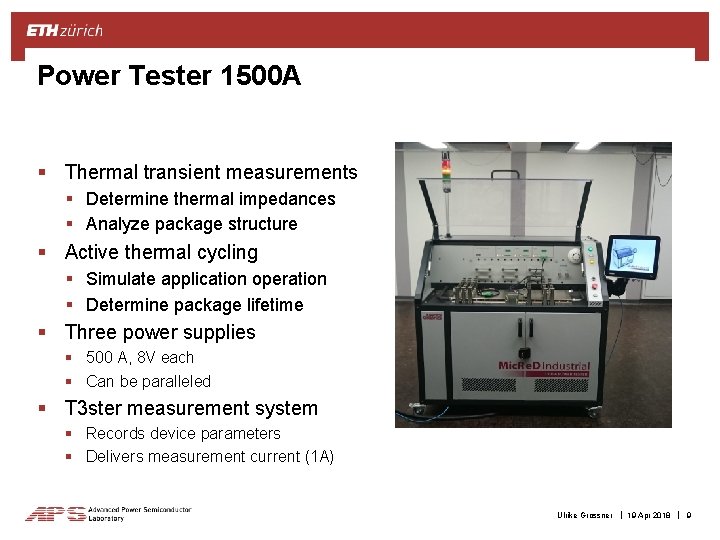

Power Tester 1500 A § Thermal transient measurements § Determine thermal impedances § Analyze package structure § Active thermal cycling § Simulate application operation § Determine package lifetime § Three power supplies § 500 A, 8 V each § Can be paralleled § T 3 ster measurement system § Records device parameters § Delivers measurement current (1 A) Ulrike Grossner | 19 Apr 2018 | 9

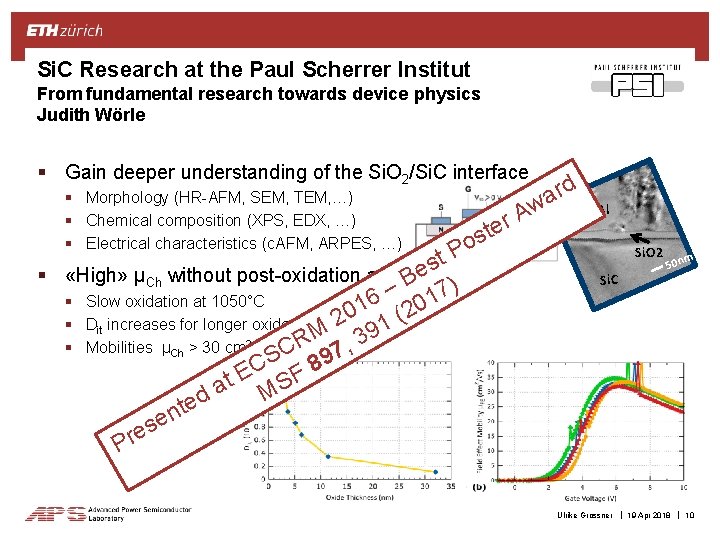

Si. C Research at the Paul Scherrer Institut From fundamental research towards device physics Judith Wörle § Gain deeper understanding of the Si. O 2/Si. C interface § Morphology (HR-AFM, SEM, TEM, …) § Chemical composition (XPS, EDX, …) § Electrical characteristics (c. AFM, ARPES, …) t. P s e § «High» μCh without post-oxidation annealing B – 17) § Slow oxidation at 1050°C 6 1 (20 0 2 § Dit increases for longer oxidation times 1 M 39 2 -1 -1 R § Mobilities μCh > 30 cm V s C 7, S 9 C F 8 E t S a M d e t en s Pre te s o rd a w A r Al Si. O 2 Si. C 50 n m Ulrike Grossner | 19 Apr 2018 | 10

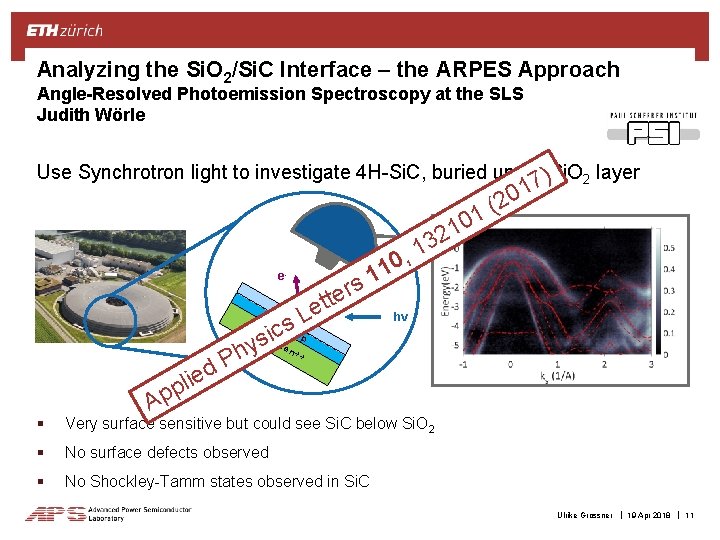

Analyzing the Si. O 2/Si. C Interface – the ARPES Approach Angle-Resolved Photoemission Spectroscopy at the SLS Judith Wörle Use Synchrotron light to investigate 4 H-Si. C, buried under )Si. O 2 layer 7 1 0 21 e- s y h Ap P d plie 13 , 0 1 1 s er t t Le o ep xide ita xia su bs lp tra te n+ + ics 1 0 2 ( hν § Very surface sensitive but could see Si. C below Si. O 2 § No surface defects observed § No Shockley-Tamm states observed in Si. C Ulrike Grossner | 19 Apr 2018 | 11

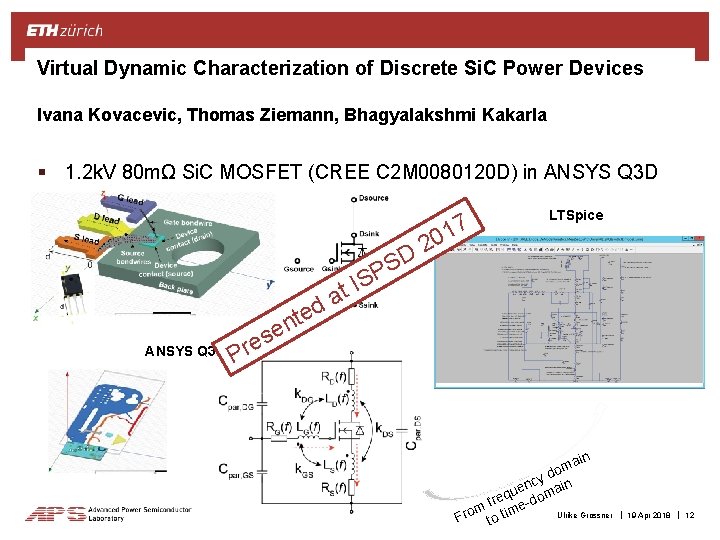

Virtual Dynamic Characterization of Discrete Si. C Power Devices Ivana Kovacevic, Thomas Ziemann, Bhagyalakshmi Kakarla § 1. 2 k. V 80 mΩ Si. C MOSFET (CREE C 2 M 0080120 D) in ANSYS Q 3 D 17 0 D 2 LTSpice S P IS t da ANSYS Q 3 D te n e s e r P ain m o yd n c n ue omai q e r d m f timeo Ulrike Grossner r F to | 19 Apr 2018 | 12

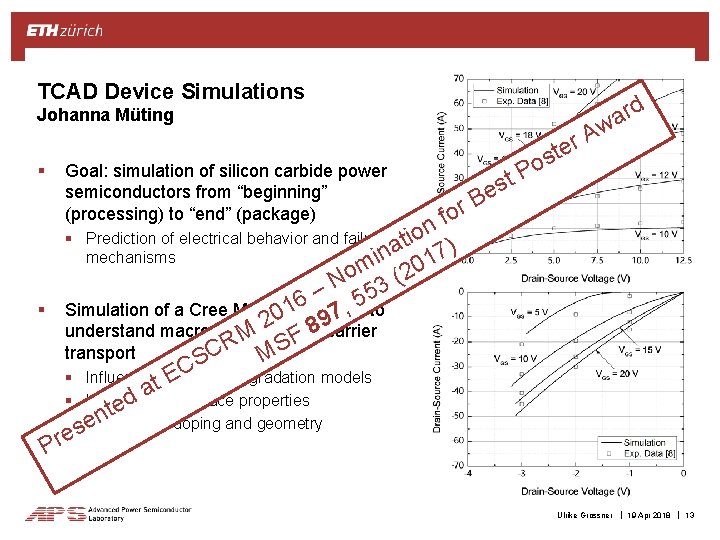

TCAD Device Simulations rd a w Johanna Müting § Goal: simulation of silicon carbide power semiconductors from “beginning” (processing) to “end” (package) t es B r s o P A r te fo n § Prediction of electrical behavior and failure tio na 17) mechanisms i m (20 o N 3 – 55 to 6 device , 1 § Simulation of a Cree MOSFET 0 97 2 8 carrier understand macroscopic charge M F R transport C MS S C degradation models § Influence of mobility E t a § Influence d of interface properties e t § s. Influence of doping and geometry en e Pr Ulrike Grossner | 19 Apr 2018 | 13

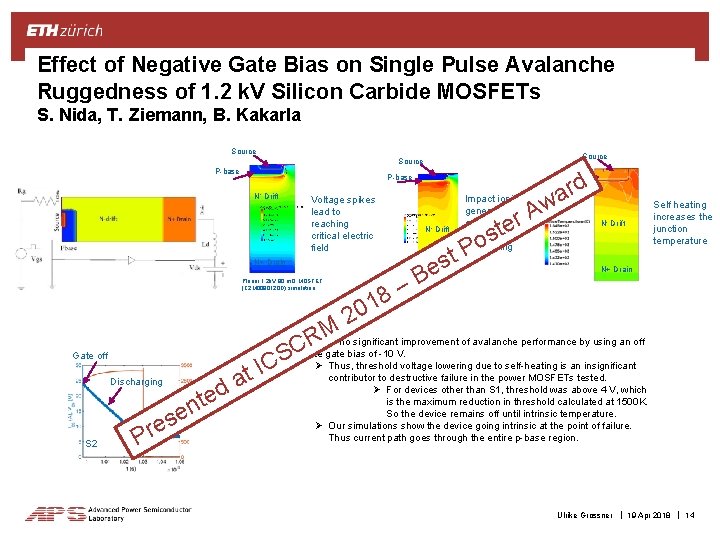

Effect of Negative Gate Bias on Single Pulse Avalanche Ruggedness of 1. 2 k. V Silicon Carbide MOSFETs S. Nida, T. Ziemann, B. Kakarla Source P-base N- Drift Voltage spikes lead to reaching critical electric field – 8 1 Planar 1. 2 k. V 80 mΩ MOSFET (C 2 M 0080120 D) simulation t a d e t n Discharging failure S 2 e s e r P N- Drift s e B Impact ionization generates carriers and the device starts conducting rd a w o P t ste r. A N- Drift Self heating increases the junction temperature N+ Drain Gate off P-base M R C S IC N+ Drain 20 There is no significant improvement of avalanche performance by using an off state gate bias of -10 V. Ø Thus, threshold voltage lowering due to self-heating is an insignificant contributor to destructive failure in the power MOSFETs tested. Ø For devices other than S 1, threshold was above 4 V, which is the maximum reduction in threshold calculated at 1500 K. So the device remains off until intrinsic temperature. Ø Our simulations show the device going intrinsic at the point of failure. Thus current path goes through the entire p-base region. Ulrike Grossner | 19 Apr 2018 | 14

APS @ ICSCRM 2017 § Continuous Compact Model of a Si. C VDMOSFET Based on Surface Potential Theory B. Jäger, Y. Ju, R. Stark § Planar to Trench: Short Circuit Capability Analysis of State-of-the-Art 1. 2 k. V Si. C MOSFETs B. Kakarla, T. Ziemann, S. Nida, E. Dönni § Improvement in Single Pulse Avalanche Ruggedness of 1. 2 k. V Silicon Carbide Trench MOSFETs by Applying a Negative Gate Bias S. Nida, B. Kakarla, T. Ziemann § Simulation-Based Sensitivity Analysis of Conduction and Switching Losses for Silicon Carbide Power MOSFETs J. Müting § Exploring the Buried Si. O 2/Si. C Interface by Soft X-Ray ARPES J. Wörle, V. N. Strokov, H. Sigg, Jens Gobrecht, M. Camarda Ulrike Grossner | 19 Apr 2018 | 15

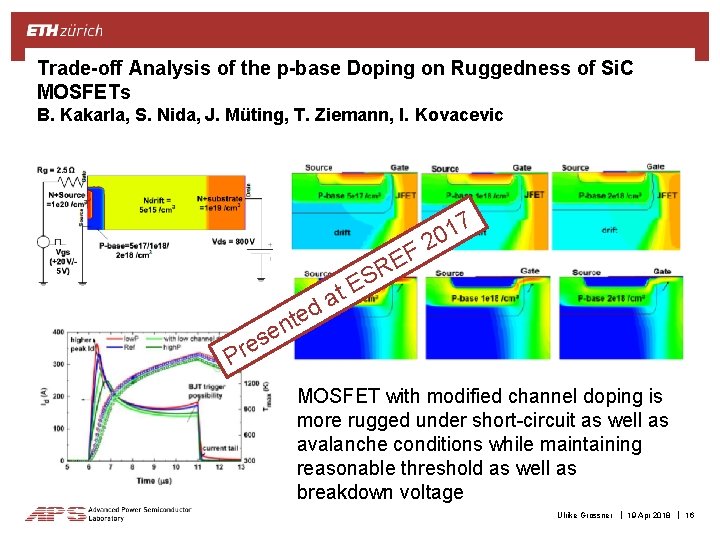

Trade-off Analysis of the p-base Doping on Ruggedness of Si. C MOSFETs B. Kakarla, S. Nida, J. Müting, T. Ziemann, I. Kovacevic F E R 7 1 20 S E t a d te n se Pre MOSFET with modified channel doping is more rugged under short-circuit as well as avalanche conditions while maintaining reasonable threshold as well as breakdown voltage Ulrike Grossner | 19 Apr 2018 | 16

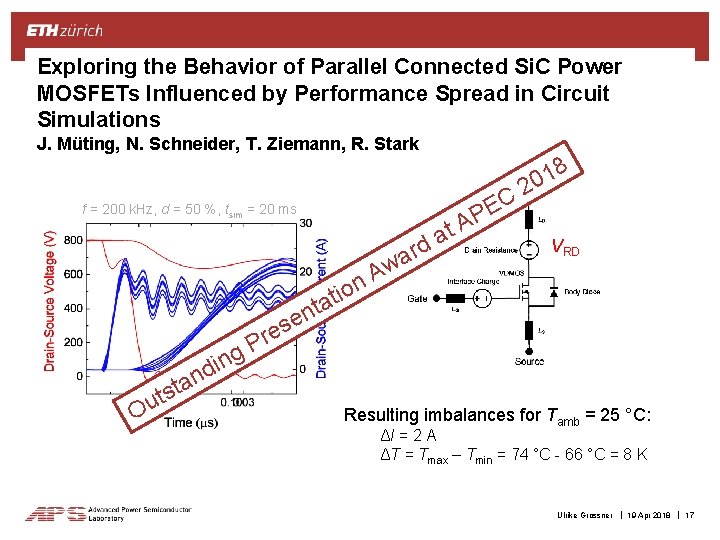

Exploring the Behavior of Parallel Connected Si. C Power MOSFETs Influenced by Performance Spread in Circuit Simulations J. Müting, N. Schneider, T. Ziemann, R. Stark C E P f = 200 k. Hz, d = 50 %, tsim = 20 ms ard w A n A t a 8 1 20 VRD io t a t n se ts u O in d tan re P g Resulting imbalances for Tamb = 25 °C: ΔI = 2 A ΔT = Tmax – Tmin = 74 °C - 66 °C = 8 K Ulrike Grossner | 19 Apr 2018 | 17

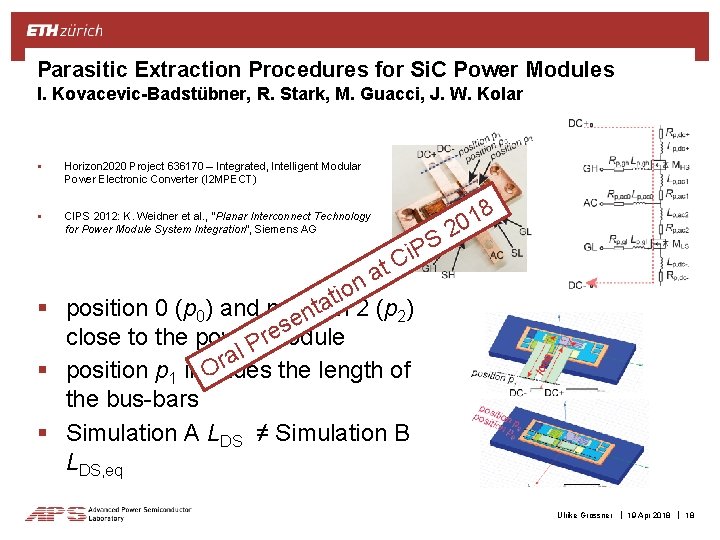

Parasitic Extraction Procedures for Si. C Power Modules I. Kovacevic-Badstübner, R. Stark, M. Guacci, J. W. Kolar § Horizon 2020 Project 636170 – Integrated, Intelligent Modular Power Electronic Converter (I 2 MPECT) § CIPS 2012: K. Weidner et al. , “Planar Interconnect Technology for Power Module System Integration”, Siemens AG S P i C 18 0 2 t a on i t ta 2 (p 2) § position 0 (p 0) and position n e s e close to the power. Prmodule al r § position p 1 includes the length of O the bus-bars § Simulation A LDS ≠ Simulation B LDS, eq Ulrike Grossner | 19 Apr 2018 | 18

Selected Student Projects 2015 – now § Sentaurus TCAD Device Simulation Model for Si. C Power MOSFETs – Michael Haider, Friedrich Thöny F 2015 § Influence of Geometry and Doping of Field Rings on Termination Ruggedness of a 1. 2 k. V Si. C MOSFET – Armando Piasko F 2016 § Coss Related Energy Loss of MOSFET's in Zero-Voltage Switching Applications – Morris Heller F 2016 § Comparative Study of Mobility Models Using Comsol Multiphysics – Beat Jäger F 2016 § Development of a Circuit Simulation Model for Silicon Carbide Power MOSFETs - Nick Schneider S 2017 § Design and Construction of a Short Circuit Tester – Elias Dönni S 2017 § Development of Control Software for a Power Semiconductor Switching Loss Test Stand – Marc Herzog S 2017 § New Technology for 4 H-Si. C MOSFETs – Yandong Zhou S 2017 § Simulation of Si. C XBPM Devices in Synchrotron Applications – Elias Passerini S 2017 § Development of a Si. C MOSFET compact model based on the Surface Potential Model – Beat Jäger MSc thesis 2017 Ulrike Grossner | 19 Apr 2018 | 19

Research Strategy § Ruggedness of power devices and modules Ø Design for reliability – understanding parameter spaces Ø Radiation hardness § Device and module manufacturing Ø Device manufacturing enabling advanced bonding technologies Ø Manufacturability Ø Low inductance, intelligent/integrated power modules § Multi-domain, multi-physics modeling from material to virtual prototyping § Strong focus on wide bandgap semiconductors Ulrike Grossner | 19 Apr 2018 | 20

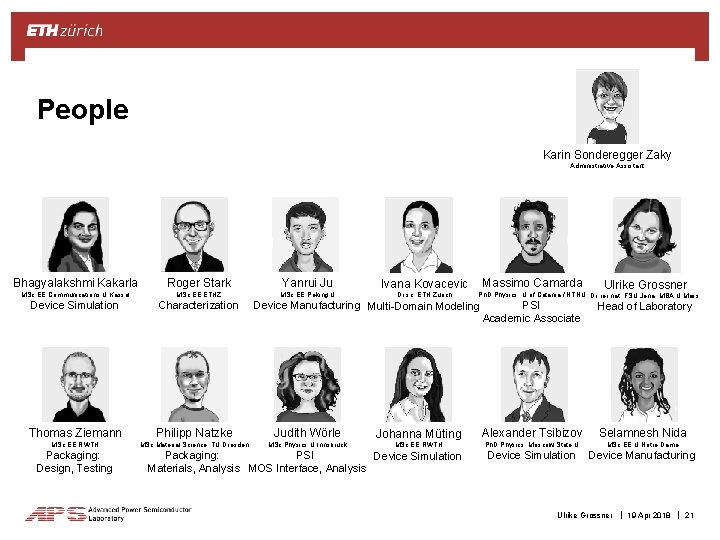

People Karin Sonderegger Zaky Administrative Assistant Bhagyalakshmi Kakarla Roger Stark Yanrui Ju Ivana Kovacevic MSc EE Communications U Kassel MSc EE ETHZ MSc EE Peking U Dr. sc. ETH Zurich Device Simulation Characterization Massimo Camarda Ulrike Grossner Ph. D Physics. U of Catania / NTNU Dr. rer. nat. FSU Jena, MBA U Mass Device Manufacturing Multi-Domain Modeling PSI Academic Associate Head of Laboratory Selamnesh Nida Thomas Ziemann Philipp Natzke Judith Wörle Johanna Müting Alexander Tsibizov MSc EE RWTH MSc Material Science, TU Dresden MSc Physics U Innsbruck MSc EE RWTH Ph. D Physics. Moscow State U MSc EE U Notre Dame Device Simulation Device Manufacturing Packaging: Design, Testing Packaging: PSI Device Simulation Materials, Analysis MOS Interface, Analysis Ulrike Grossner | 19 Apr 2018 | 21

Thank you for your attention! | |

- Slides: 22