Getting the chip fabricated and tested Dr K

Getting the chip fabricated and tested • Dr. K. S. Gurumurthy, Bangalore University • Mr. Senthil Kumar, Kongu Engg College, Erode • Dr. Tilak, GEC, AP • Dr. Bhanu Bhaskara, JNTU, Hyderabad • Dr. B. P. Harish, Bangalore University • B. kalivaraprasad SVECWbhimavaram(A. P)

AGENDA • Motivation • What are the foundries available • Semiconductor Complex Ltd. , Chandigarh • Summary 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 2

Motivation • To present an overview of the IC fabrication facilities available to Universities in India. • To encourage faculty/students to tape out designs, for fabrication and characaterization, to demonstrate proof of concept. 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 3

What are the foundries available? • Semiconductor Complex Ltd. , Chandigarh • MOSIS, US • Europractice, EU - AMIS - TSMC - Austria Microsystems - UMC 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 4

Semiconductor Complex Ltd , Chandigarh • The ‘India Chip Program’ is a program of Multi. Product Wafer runs at regular intervals at SCL. • The program envisages to put different circuits from various designers on a common mask set and wafers, to reduce the cost of prototyping per design. 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 5

Who can use India Chip Program? • The India Chip Program is ideally suited for validating small circuit concepts being done by – Academic Institutions – Research Institutions – Entrepreneurs – Commercial Organisations 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 6

• IC Designers in the country can design circuits using SCL’s Design Kit that includes SCL’s Cell Library, Design Rules and Model Parameters. • Using SCL’s Design Kit, IC Designers can do complete design of the circuit and generate GDSII data for mask fabrication. • Mask fabrication, wafer fabrication and parametric testing shall be taken up by SCL. 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 7

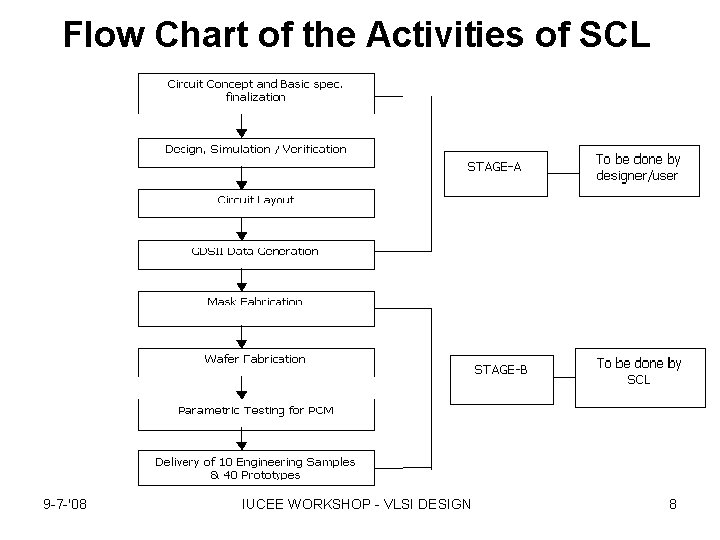

Flow Chart of the Activities of SCL 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 8

How to send your design data to SCL? • On conceptualization of the designer will send details about the design concept to SCL in a Preliminary Product Description Document. • Once your design is complete SCL will accept design data in GDSII format. (If Cadence is used, please perform a stream-out with library version 3. 0. Data may please be sent on CD or through email or through FTP). 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 9

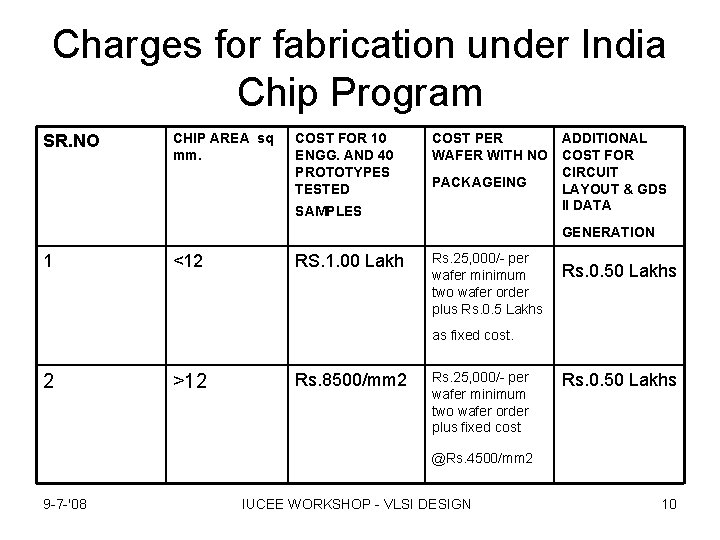

Charges for fabrication under India Chip Program SR. NO CHIP AREA sq mm. COST FOR 10 ENGG. AND 40 PROTOTYPES TESTED SAMPLES COST PER ADDITIONAL WAFER WITH NO COST FOR CIRCUIT PACKAGEING LAYOUT & GDS II DATA GENERATION 1 <12 RS. 1. 00 Lakh Rs. 25, 000/- per wafer minimum two wafer order plus Rs. 0. 5 Lakhs as fixed cost. 2 >12 Rs. 8500/mm 2 Rs. 25, 000/- per wafer minimum two wafer order plus fixed cost IUCEE WORKSHOP - VLSI DESIGN Rs. 0. 50 Lakhs @Rs. 4500/mm 2 9 -7 -'08 Rs. 0. 50 Lakhs 10

Summary • Fabrication facilities are explored for IC prototyping and characterization. • SCL’s India Chip program is taken as case study and it seems to be viable. 9 -7 -'08 IUCEE WORKSHOP - VLSI DESIGN 11

- Slides: 11