New VerilogA capability available in Agilent simulators Based

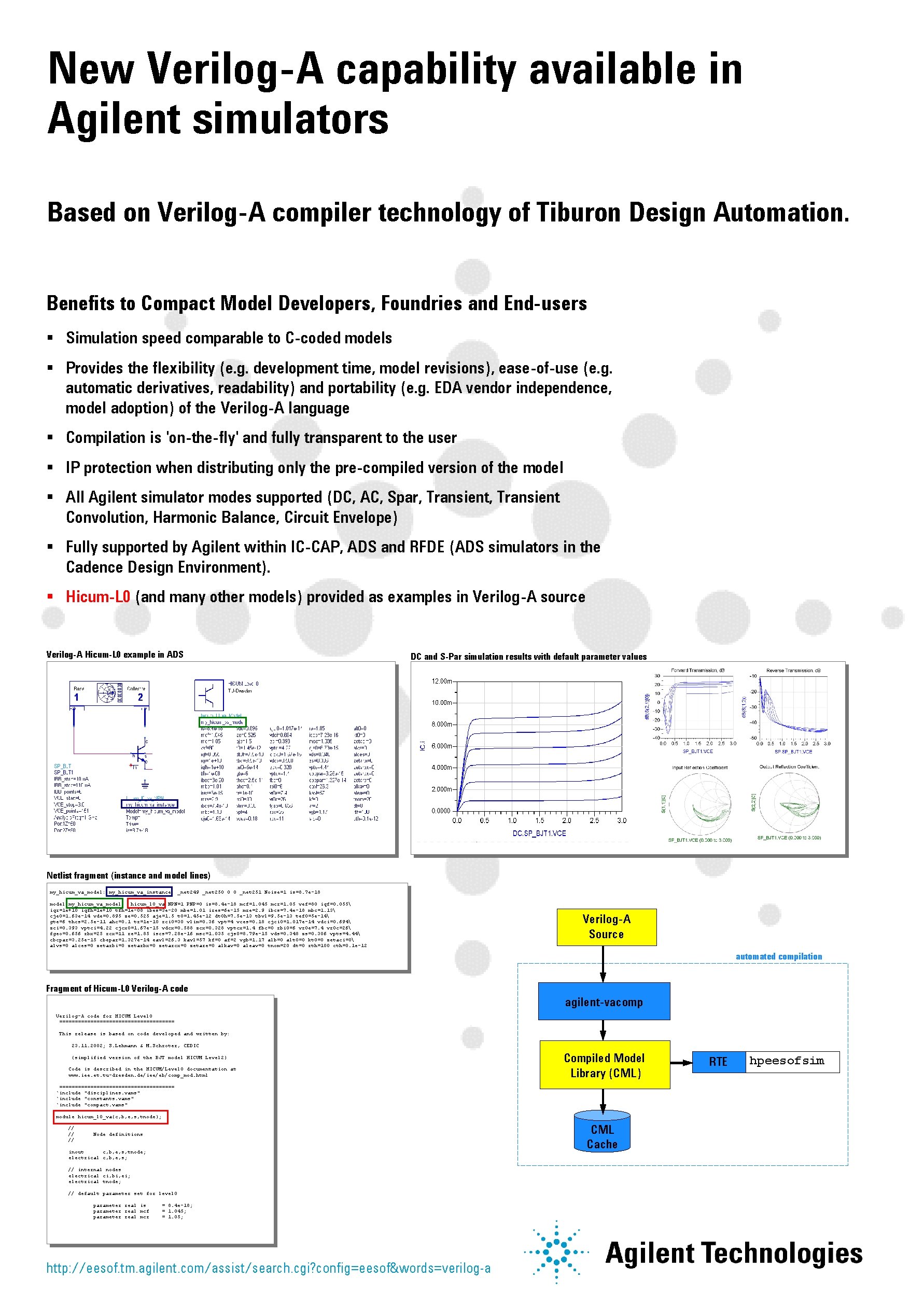

New Verilog-A capability available in Agilent simulators Based on Verilog-A compiler technology of Tiburon Design Automation. Benefits to Compact Model Developers, Foundries and End-users § Simulation speed comparable to C-coded models § Provides the flexibility (e. g. development time, model revisions), ease-of-use (e. g. automatic derivatives, readability) and portability (e. g. EDA vendor independence, model adoption) of the Verilog-A language § Compilation is 'on-the-fly' and fully transparent to the user § IP protection when distributing only the pre-compiled version of the model § All Agilent simulator modes supported (DC, AC, Spar, Transient Convolution, Harmonic Balance, Circuit Envelope) § Fully supported by Agilent within IC-CAP, ADS and RFDE (ADS simulators in the Cadence Design Environment). § Hicum-L 0 (and many other models) provided as examples in Verilog-A source Verilog-A Hicum-L 0 example in ADS DC and S-Par simulation results with default parameter values Netlist fragment (instance and model lines) my_hicum_va_model: my_hicum_va_instance _net 249 _net 250 0 0 _net 251 Noise=1 is=8. 7 e-18 model my_hicum_va_model hicum_l 0_va NPN=1 PNP=0 is=8. 4 e-18 mcf=1. 045 mcr=1. 05 vef=80 iqf=0. 055 iqr=1 e+10 iqfh=1 e+10 tfh=1 e-08 ibes=3 e-20 mbe=1. 01 ires=6 e-15 mre=2. 9 ibcs=7. 4 e-18 mbc=1. 13 cje 0=1. 63 e-14 vde=0. 895 ze=0. 525 aje=1. 5 t 0=1. 45 e-12 dt 0 h=7. 5 e-13 tbvl=9. 5 e-13 tef 0=5 e-14 gte=6 thcs=2. 5 e-11 ahc=0. 1 tr=1 e-10 rci 0=30 vlim=0. 36 vpt=4 vces=0. 18 cjci 0=1. 017 e-14 vdci=0. 694 zci=0. 393 vptci=4. 22 cjcx 0=1. 67 e-15 vdcx=0. 588 zcx=0. 328 vptcx=1. 4 fbc=0 rbi 0=6 vr 0 e=7. 4 vr 0 c=26 fgeo=0. 656 rbx=25 rcx=11 re=1. 85 iscs=7. 28 e-16 msc=1. 035 cjs 0=8. 79 e-15 vds=0. 348 zs=0. 306 vpts=4. 44 cbcpar=3. 25 e-15 cbepar=1. 327 e-14 eavl=26. 3 kavl=57 kf=0 af=2 vgb=1. 17 alb=0 alt 0=0 kt 0=0 zetaci=0 alvs=0 alces=0 zetarbi=0 zetarbx=0 zetarcx=0 zetare=0 alkav=0 aleav=0 tnom=20 dt=0 rth=100 cth=0. 1 e-12 Verilog-A Source automated compilation Fragment of Hicum-L 0 Verilog-A code agilent-vacomp Verilog-A code for HICUM Level 0 =================== This release is based on code developed and written by: 23. 11. 2002; S. Lehmann & M. Schroter, CEDIC (simplified version of the BJT model HICUM Level 2) Code is described in the HICUM/Level 0 documentation at www. iee. et. tu-dresden. de/iee/eb/comp_mod. html Compiled Model Library (CML) =================== `include "disciplines. vams" `include "constants. vams" `include "compact. vams" module hicum_l 0_va(c, b, e, s, tnode); // // // CML Cache Node definitions inout c, b, e, s, tnode; electrical c, b, e, s; // internal nodes electrical ci, bi, ei; electrical tnode; // default parameter set for level 0 parameter real is parameter real mcf parameter real mcr = 8. 4 e-18; = 1. 045; = 1. 05; http: //eesof. tm. agilent. com/assist/search. cgi? config=eesof&words=verilog-a RTE hpeesofsim

- Slides: 1