IO Organization popo IO Organization interfacing Techniques IO

- Slides: 40

I/O Organization popo

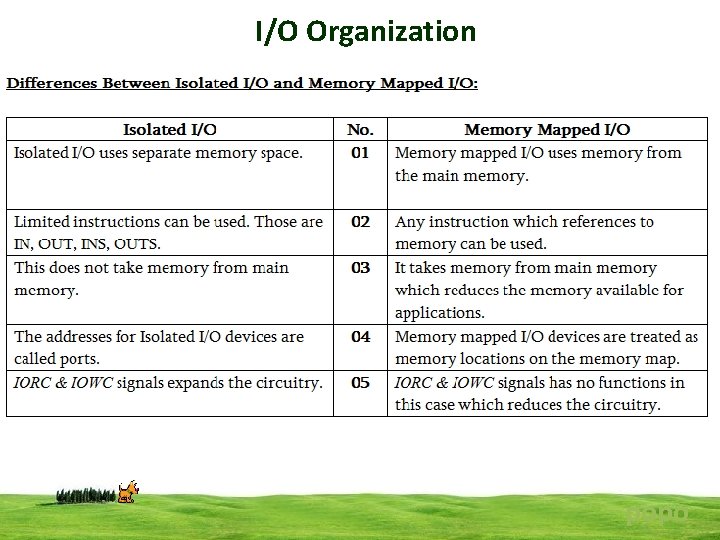

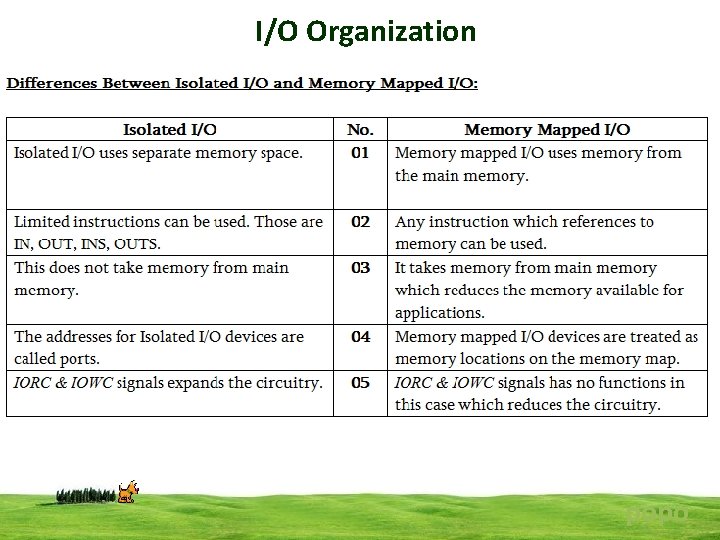

I/O Organization interfacing Techniques • I/O interfacing Techniques • I/O devices can be interfaced to a computer system in two ways • 1) Memory mapped I/O • 2) I/O mapped I/O (Isolated I/O) popo

I/O Organization • • • I/O interfacing Techniques Memory Mapped I/O In this technique the total memory address space is partitioned A part of this space is devoted to I/O addressing In memory mapped I/O, all peripherals are treated as memory locations. This means that a memory addresses are assigned to I/O ports. The CPU just reads and writes data to a memory location, i. e. transferring data from memory to port and from port to memory. This way of mapping used in CISC computer Such systems do not have I/O specific instructions. popo

I/O Organization • I/O interfacing Techniques • In I/O mapped I/O, the peripheral devices are addressed directly by the CPU using the port addresses. • The length of port address is generally less than the length of a memory address. • There are specific instructions for carrying out input and output tasks at the ports. popo

I/O Organization popo

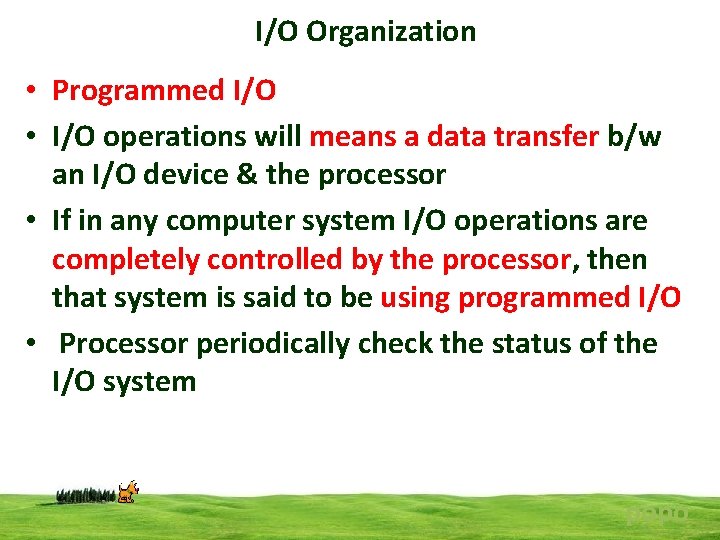

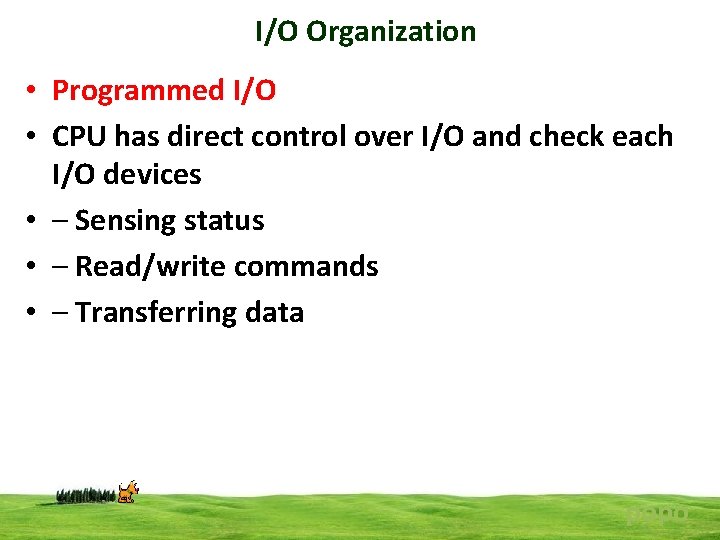

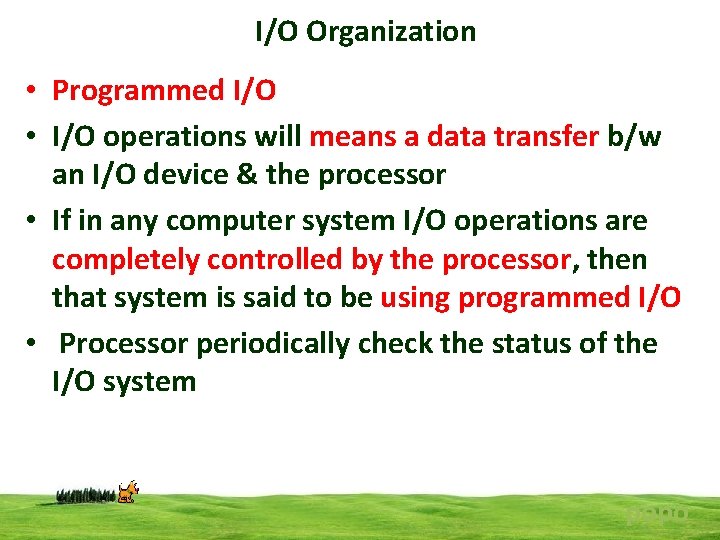

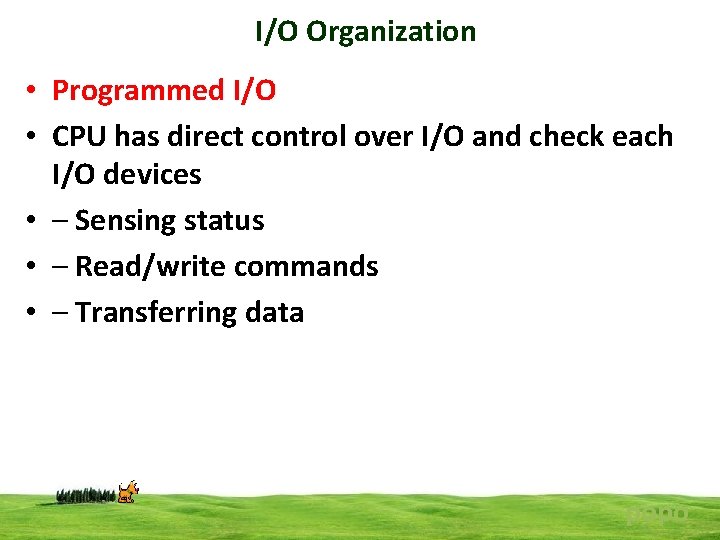

I/O Organization • Programmed I/O • I/O operations will means a data transfer b/w an I/O device & the processor • If in any computer system I/O operations are completely controlled by the processor, then that system is said to be using programmed I/O • Processor periodically check the status of the I/O system popo

I/O Organization • Programmed I/O • CPU has direct control over I/O and check each I/O devices • – Sensing status • – Read/write commands • – Transferring data popo

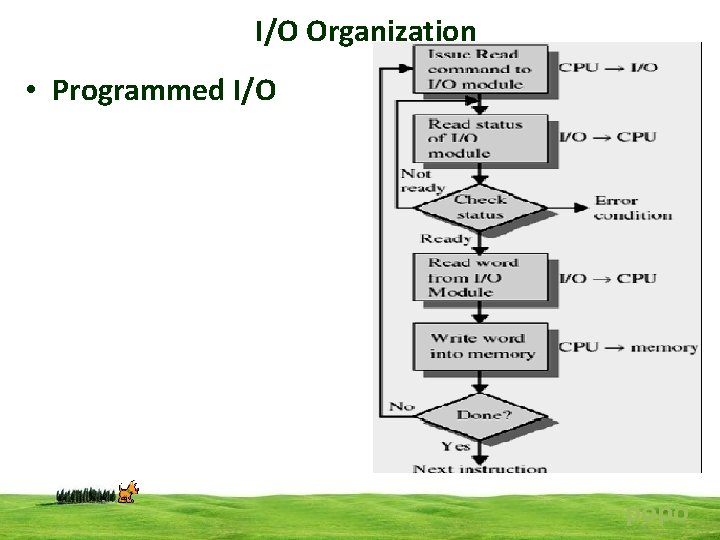

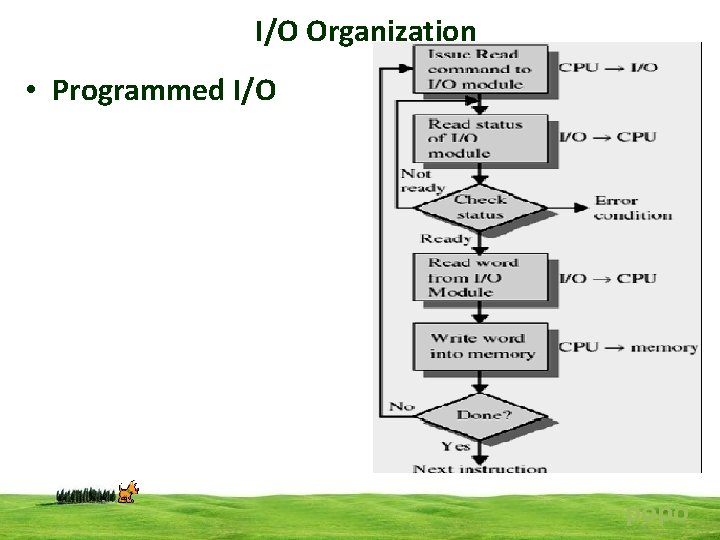

I/O Organization • Programmed I/O popo

I/O Organization • Programmed I/O • In this case, use dedicated I/O instructions in the processor. • These I/O instructions can specify both the device number and the command word (or the location of the command word in memory). • Eg IN 01 H IN}-command, 01}device no H}hexa popo

I/O Organization • Programmed I/O • The process of periodically checking status bits to see if it is time for the next I/O operation, is called polling. • Polling is the simplest way for an I/O device to communicate with the processor. • The I/O device simply puts the information in a Status register, and the processor must come and get the information. • The processor is totally in control and does all the work. popo

I/O Organization • Programmed I/O • The disadvantage of polling is that it can waste a lot of processor time because processors are so much faster than I/O devices. • The processor may read the Status register many times, only to find that the device has not yet completed a slow I/O operation, popo

I/O Organization • Programmed I/O • Overhead in a polling interface lead to the invention of interrupts to notify the processor when an I/O device requires attention from the processor. • Interrupt-driven I/O, employs I/O interrupts to indicate to the processor that an I/O device needs attention. • When a device wants to notify the processor that it has completed some operation or needs attention, it causes the processor to be interrupted. popo

I/O Organization • Interrupts • In program-controlled I/O, the program enters a wait loop in which it repeatedly tests the device status. • During the period, the processor is not performing any useful computation. • However, in many situations other tasks can be performed while waiting for an I/O device to become ready. • Let the device alert the processor. popo

I/O Organization • Interrupts • one of the bus control lines, called an interruptrequest line, is usually dedicated for this purpose • An interrupt-service routine usually is needed and is executed when an interrupt request is issued • On the other hand, the processor must inform the device that its request has been recognized so that it may remove its interrupt-request signal. • An interrupt-acknowledge signal serves this function popo

I/O Organization • Interrupts • When I/O Device is ready, it sends the INTERRUPT signal to processor via a dedicated controller line • Using interrupt we can eliminating WAIT period • In response to the interrupt, the processor executes the Interrupt Service Routine (ISR) • All the registers, flags, program counter values are saved by the processor before running ISR • The time required to save status & restore to execution overhead called “Interrupt Latency” popo

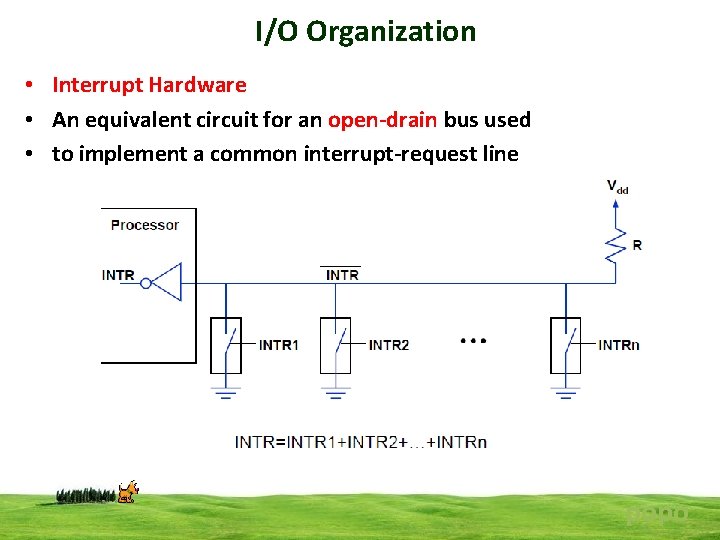

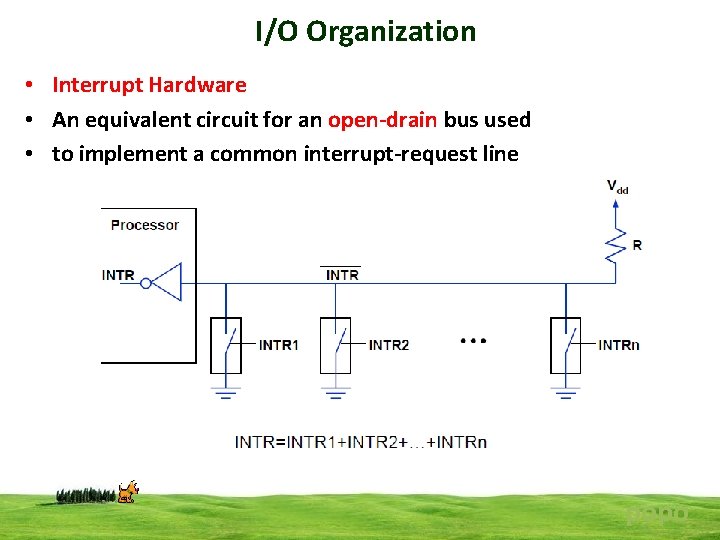

I/O Organization • Interrupt Hardware • An equivalent circuit for an open-drain bus used • to implement a common interrupt-request line popo

I/O Organization • Direct Memory Access • To transfer large blocks of data at high speed, a special control unit may be provided between an external device and the main memory, without continuous intervention by the processor. • This approach is called direct memory access (DMA) • DMA transfers are performed by a control circuit that is part of the I/O device interface. • Called DMA controller. popo

I/O Organization • Direct Memory Access • Removing the CPU from the path and letting the peripheral device to manage the memory buses directly would improve the speed of transfer. • This transfer technique is called direct memory access (DMA). • During DMA transfer, the CPU is idle and has no control of the memory buses. • A DMA controller takes over the buses to manage the transfer directly between the I/O device and memory. popo

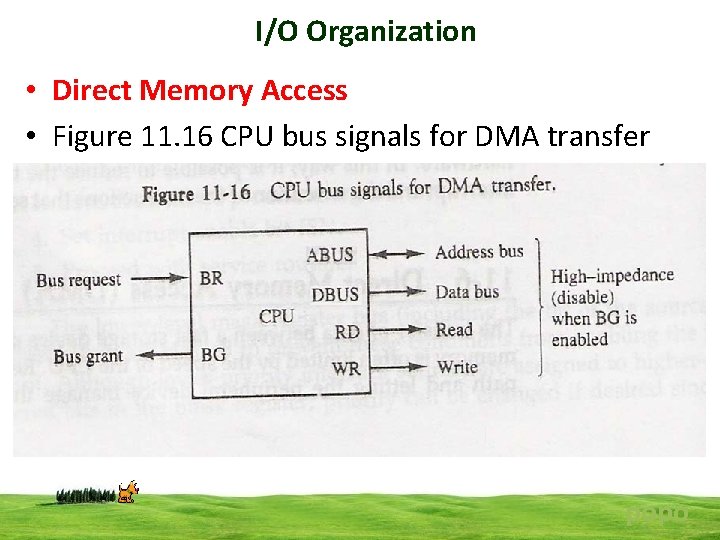

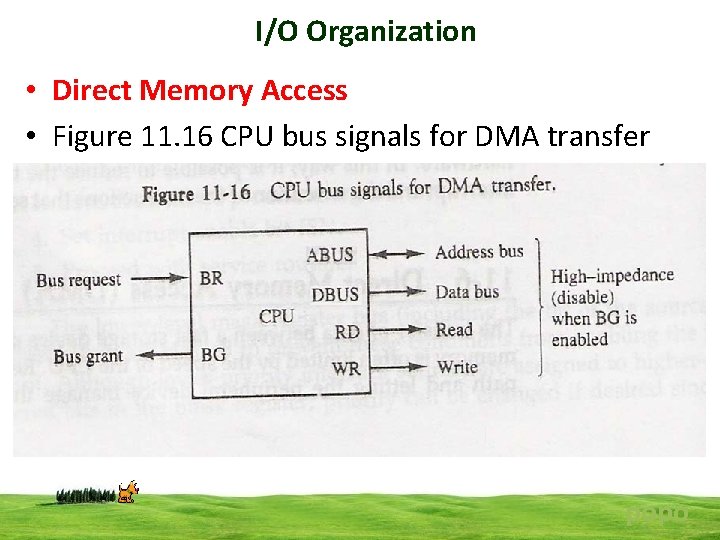

I/O Organization • Direct Memory Access • Bus request • One common method used in microprocessors is to disable the buses through special control signals. • Figure 11 -16 shows two control signals in the CPU that bus request facilitate the DMA transfer. • The bus request (BR) input is used by the DMA controller to request the CPU to control of the buses. • When this input is active, the CPU terminates the execution of the current instruction and places the address bus, the data bus, and the read and write lines into a high-impedance state. • The high-impedance state behaves like an open circuit, which means that the output is disconnected and does not have a logic significance. popo

I/O Organization • Direct Memory Access • Bus grant • CPU activates the bus grant (BG) output to inform the external DMA that the buses are in the highimpedance state. • The DMA that originated the bus request can now take control of the buses to conduct memory transfers without processor intervention. • When the DMA terminates the transfer, it disables the bus request line. • The CPU disables the bus grant, takes control of the buses, and returns to its normal operation. popo

I/O Organization • Direct Memory Access • Burst transfer • When the DMA takes control of the bus system, it communicates directly with the memory. • The transfer can be made in several ways. • In DMA burst transfer, a block sequence consisting of a number of memory words is transferred in a continuous burst while the DMA controller is master of the memory buses. • This mode of transfer is needed for fast devices such as magnetic disks, where data transmission cannot be stopped or slowed down until an entire cycle stealing block is transferred. • An alternative technique called cycle stealing allows the DMA controller to transfer one data word at a time, after which it must return control of the buses to the CPU. • The CPU delays its operation for one memory cycle to allow the direct memory I/O transfer to “steal” one memory cycle. popo

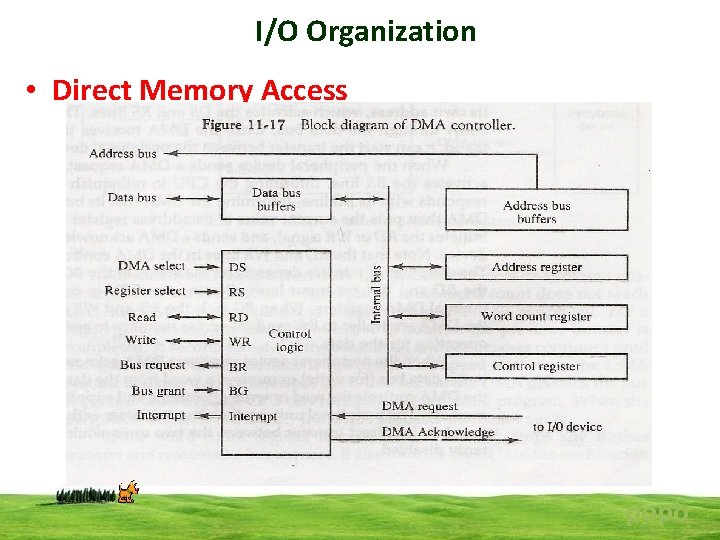

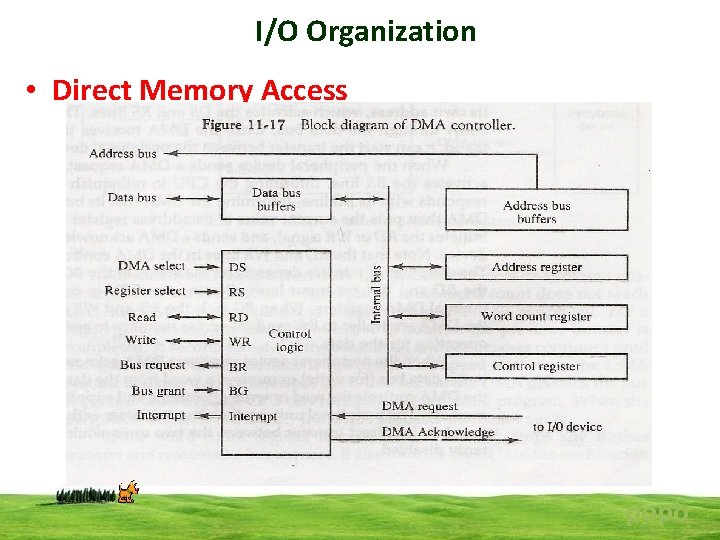

I/O Organization • Direct Memory Access • DMA Controller • The DMA controller needs the usual circuits of an interface to communicate with the CPU and I/O device. • In addition, it needs an address register, a word count register, and a set of address lines • The address register and address are used for direct communication with the memory. popo

I/O Organization • Direct Memory Access • Figure 11. 16 CPU bus signals for DMA transfer popo

I/O Organization • Direct Memory Access • The word count register specifies the number of words that must be transferred. • The data transfer may be done directly between the device and memory under control of the DMA. • Figure 11 -17 shows the block diagram of a typical DMA controller popo

I/O Organization • Direct Memory Access popo

I/O Organization • Direct Memory Access • The unit communicates with the CPU via the data bus and control lines. • The registers in the DMA are selected by the CPU through the address bus by enabling the DS (DMA select) and RS (register select) inputs. • The RD (read) and WR (write) inputs are bidirectional. • When the BG (bus grant) input is 0, the CPU can communicate with the DMA registers through the data bus to read from or write to the DMA registers. • When BG =1. • DMA can communicate directly with the memory by specifying an address in the address bus and activating the RD or WR control. popo

I/O Organization • Direct Memory Access • The DMA communicates with the external peripheral through the request and acknowledge lines by using a prescribed handshaking procedure. • The DMA controller has three registers: an address register. a word count register, and a control register. • The address register contains an address to specify the desired location in memory. • The address bits go through bus buffers into the address bus. • The address register is incremented after each word that is transferred to memory. popo

I/O Organization • Direct Memory Access • The word count register holds the number of words to be transferred. • This register is decremented by one after each word transfer and internally tested for zero. • The control register specifies the mode of transfer. • All registers in the DMA appear to the CPU as I/O interface registers. • Thus the CPU can read from or write into the DMA registers under program control via the data bus. • The DMA is first initialized by the CPU. • After that, the DMA starts and continues to transfer data between memory and peripheral unit until an entire block is transferred. • The initialization process is essentially a program consisting of I/O instructions that include the address for selecting particular DMA registers. popo

I/O Organization • Direct Memory Access • The CPU initializes the DMA by sending the following information through the data bus: • 1. The starting address of the memory block where data are available (for read) or where data are to be stored (for write) • 2. The word count, which is the number of words In the memory block • 3. Control to specify the mode of transfer such as read or write • A control to start the DMA transfer • The starting address is stored in the address register. • The word count is stored in the word count register, and the control Information in the control register. • Once the DMA Is initialized, the CPU stops communicating with the DMA unless it receives an interrupt signal or If it wants to check how many words have been transferred. popo

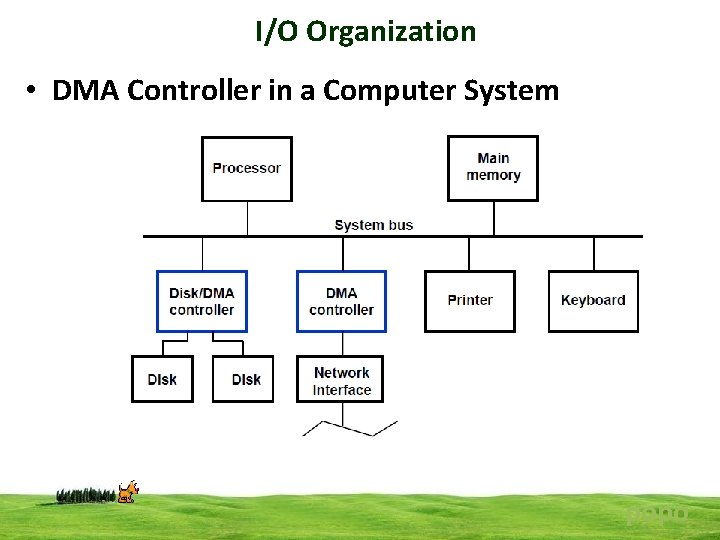

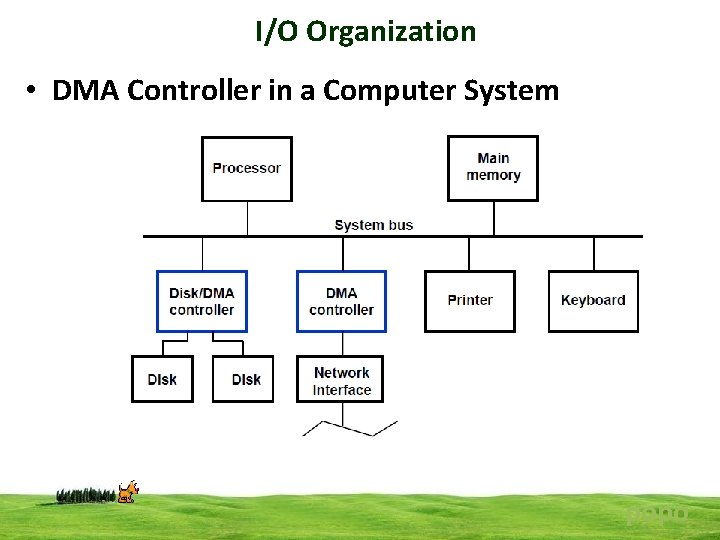

I/O Organization • DMA Controller in a Computer System popo

I/O Organization • Bus Arbitration • A conflict may arise if both the processor and a DMA controller or two DMA controllers try to use the bus at the same time to access the main memory. • To resolve this problem, an arbitration procedure on bus is needed • The device that is allowed to initiate data transfer on the bus at any given time is called the bus master. • When the current master release control of the bus, another device can acquire this status • Bus arbitration is the process by which the next device to become the bus master take into account the needs of various devices by establishing a priority system for gaining access to the bus popo

I/O Organization • Bus Arbitration • There are two approaches to bus arbitration Centralized and distributed • In centralized arbitration, a single bus arbiter performs the required arbitration • In distributed arbitration, all devices participate in the selection of the next bus master popo

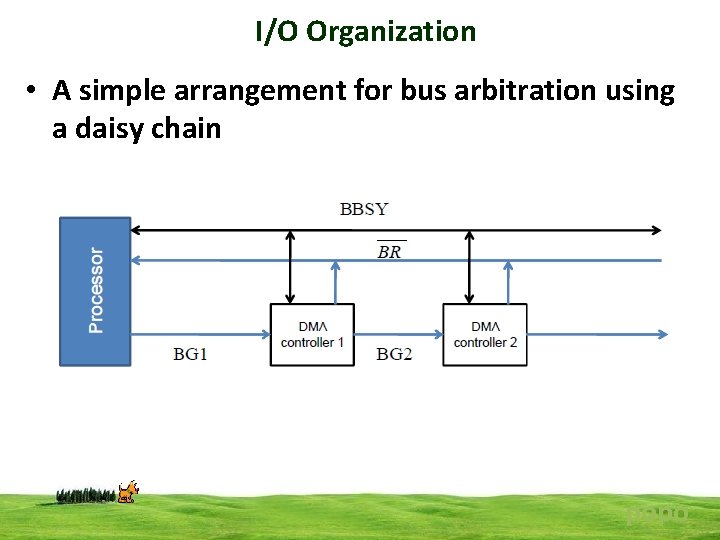

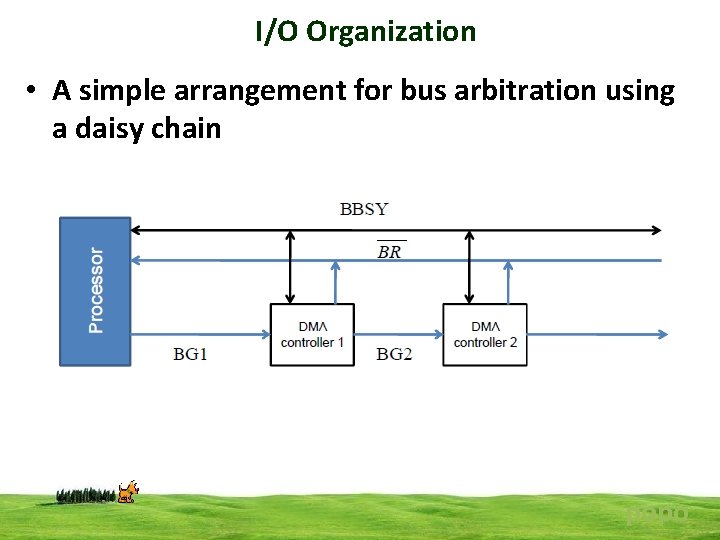

I/O Organization • A simple arrangement for bus arbitration using a daisy chain popo

Parallel Port • A parallel port transfers data in the form of a number of bits, typically 8 or 16, simultaneously to or from the device. • For faster communications popo 34

Parallel Port – Input Interface (Keyboard to Processor Connection) popo 35

Parallel Port – Input Interface (Keyboard to Processor Connection) • When a key is pressed its switch closes and establishes a path for an electric signal • This signal is detected by an encoder circuit that generates ASCII code for the corresponding character. • The input interface consists of a data register DATAIN and status flag SIN • When key is pressed the valid signal activates and causes the ASCII coed to be loaded into DATAIN and • SIN to beset to 1 popo

Parallel Port – Input Interface (Keyboard to Processor Connection) • The status flag SIN is cleared to 0 when the processor reads the content of DATAIN register • Address decoder is used to select the input interface popo

Parallel Port – Output Interface (Printer to Processor Connection) popo 38

Parallel Port – Output Interface (Printer to Processor Connection) • The output port contains a data register, DATAOUT and a status flag SOUT • SOUT set to 1 when the printer is ready to accept another character • SOUT is 0 when a new character is loaded into DATAOUT by the processor popo

Serial Port • A serial port is used to connect the processor to I/O devices that require transmission of data one bit at a time. • The key feature of an interface circuit for a serial port is that it is capable of communicating in bit-serial fashion on the device side and in a bit-parallel fashion on the bus side. • Capable of longer distance communication than parallel transmission. popo 40