Interfacing RealTime Embedded Systems Khalid Abu Muhaimeed Nouh

Interfacing Real-Time Embedded Systems Khalid Abu Muhaimeed Nouh Kh. Toolitch Supervisor: Dr. Lo`ai Tawalbeh

Outline Ø Ø Interfacing basics. Microprocessor interfacing § § § I/O addressing. Interrupts. Direct Memory Access (DMA). Real-time Embedded Systems/Interfacing 2

Introduction Processor process data. memory storage buses communication • Communication: transfer of data among processors and memories. • This communication is known as interfacing. l Real-time Embedded Systems/Interfacing 3

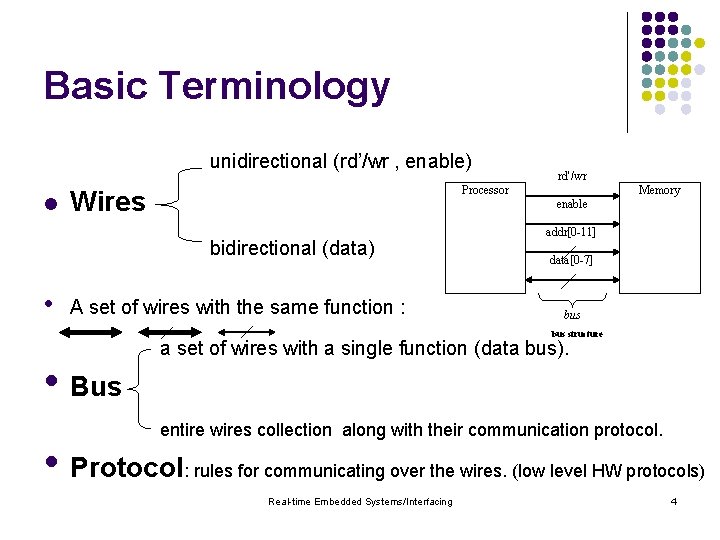

Basic Terminology unidirectional (rd’/wr , enable) l Processor Wires Memory enable bidirectional (data) • rd'/wr A set of wires with the same function : addr[0 -11] data[0 -7] bus structure • Bus a set of wires with a single function (data bus). entire wires collection along with their communication protocol. • Protocol : rules for communicating over the wires. (low level HW protocols) Real-time Embedded Systems/Interfacing 4

Basic Terminology l Port: the actual conducting device (metal) on the processor (or memory) through which the signal is input to, or output from. l We could use the term pin to refer to a port on a processor. l Pin is also a term referring to the extending pins from the processor ( as own IC package). They are designed to be plugged into a socket on a printed-circuit board. l Small metallic balls could be used rather than pins( if the processor is packaged in its own IC ). l If the processor coexists on a single IC with other processors and memories, pads of metal are used in the IC. Real-time Embedded Systems/Interfacing 5

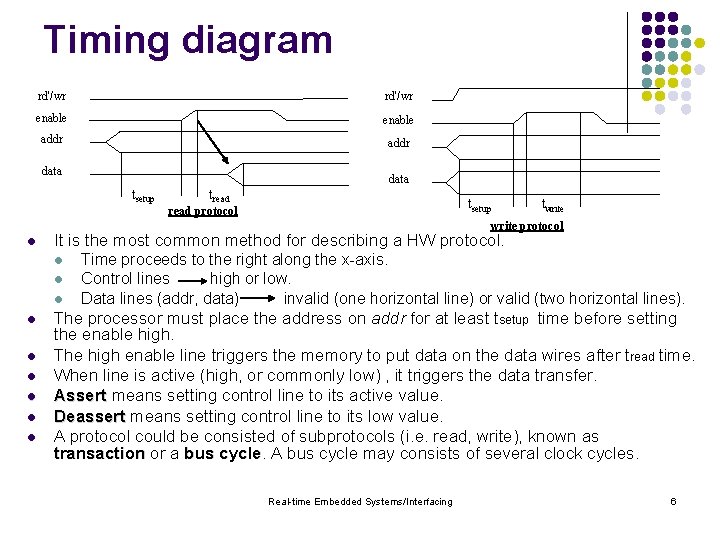

Timing diagram rd'/wr enable addr data tsetup tread tsetup read protocol twrite protocol l It is the most common method for describing a HW protocol. l l l l l Time proceeds to the right along the x-axis. Control lines high or low. Data lines (addr, data) invalid (one horizontal line) or valid (two horizontal lines). The processor must place the address on addr for at least tsetup time before setting the enable high. The high enable line triggers the memory to put data on the data wires after tread time. When line is active (high, or commonly low) , it triggers the data transfer. Assert means setting control line to its active value. Deassert means setting control line to its low value. A protocol could be consisted of subprotocols (i. e. read, write), known as transaction or a bus cycle A bus cycle may consists of several clock cycles. Real-time Embedded Systems/Interfacing 6

Basic protocol concepts l l l Actor: Actor is the processor or memory involved in data transfer. A protocol involves two actors: a master, and a servant (slave). A master initiates the data transfer (usually general-purpose processor), and the servant responds to the initiation request (usually memories and peripherals). Data direction: direction the direction that the transferred data moves btw. actors( receiving or sending data). Addresses: Addresses a special type of data used to indicate where regular data should go to or come from (used to address memory locations , peripherals and peripheral's registers). Real-time Embedded Systems/Interfacing 7

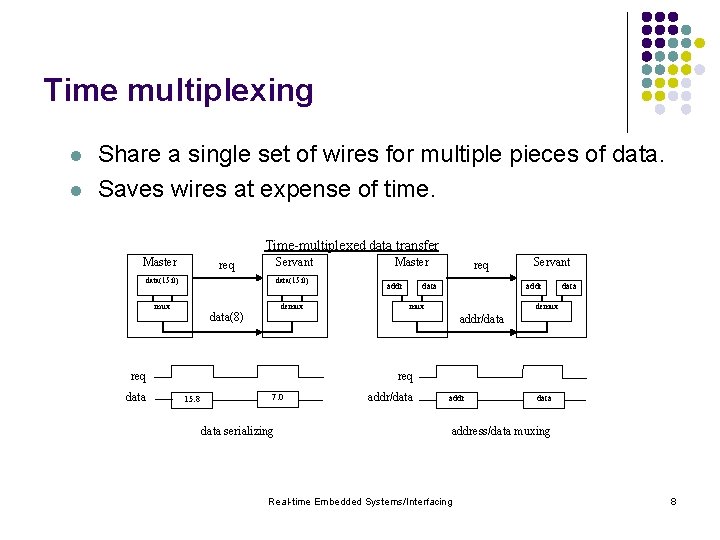

Time multiplexing l l Share a single set of wires for multiple pieces of data. Saves wires at expense of time. Time-multiplexed data transfer Master Servant req data(15: 0) mux demux data(8) addr req data Servant addr mux data demux addr/data req data Master req 15: 8 7: 0 data serializing addr/data address/data muxing Real-time Embedded Systems/Interfacing 8

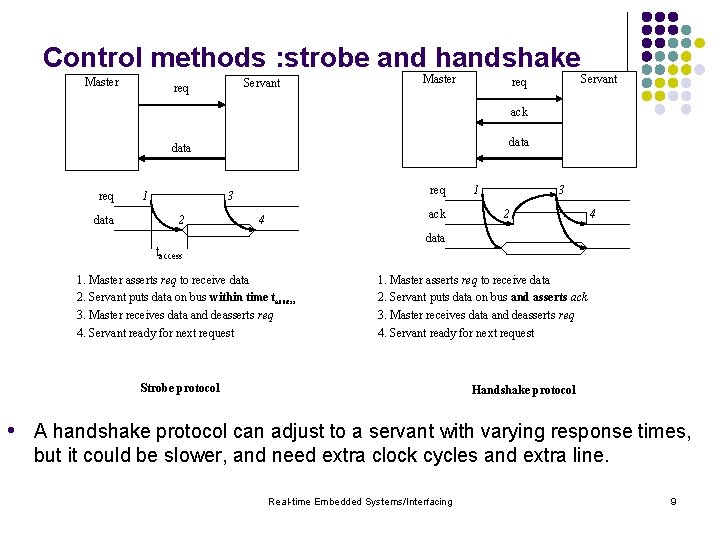

Control methods : strobe and handshake Master Servant req Master req Servant ack data req data 1 req 3 2 ack 4 1 3 2 4 data taccess 1. Master asserts req to receive data 2. Servant puts data on bus within time taccess 3. Master receives data and deasserts req 4. Servant ready for next request 1. Master asserts req to receive data 2. Servant puts data on bus and asserts ack 3. Master receives data and deasserts req 4. Servant ready for next request Strobe protocol Handshake protocol • A handshake protocol can adjust to a servant with varying response times, but it could be slower, and need extra clock cycles and extra line. Real-time Embedded Systems/Interfacing 9

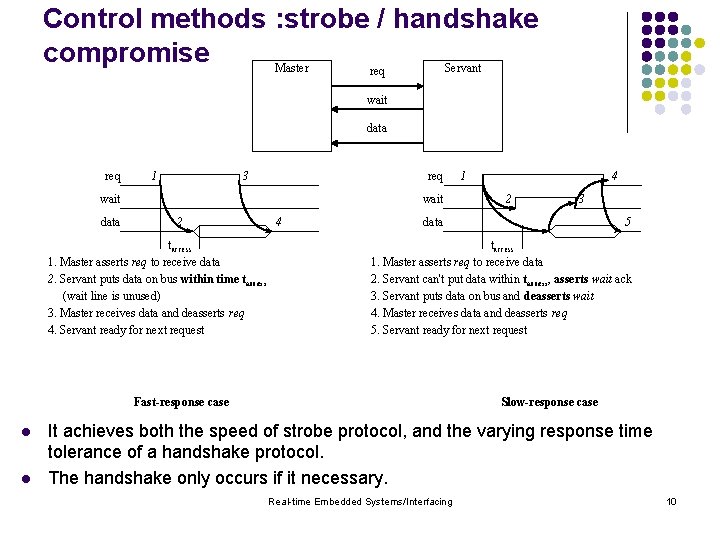

Control methods : strobe / handshake compromise Master Servant req wait data req 1 req 3 wait data wait 2 taccess 1. Master asserts req to receive data 2. Servant puts data on bus within time taccess (wait line is unused) 3. Master receives data and deasserts req 4. Servant ready for next request 4 l 4 2 3 data 5 taccess 1. Master asserts req to receive data 2. Servant can't put data within taccess, asserts wait ack 3. Servant puts data on bus and deasserts wait 4. Master receives data and deasserts req 5. Servant ready for next request Fast-response case l 1 Slow-response case It achieves both the speed of strobe protocol, and the varying response time tolerance of a handshake protocol. The handshake only occurs if it necessary. Real-time Embedded Systems/Interfacing 10

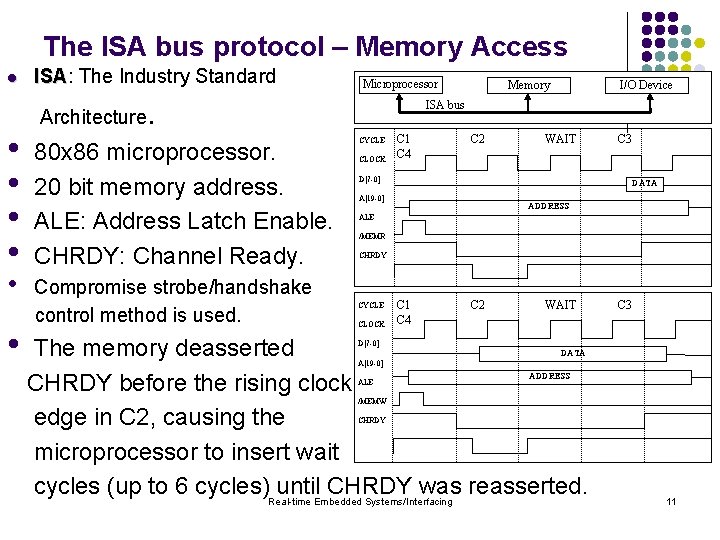

The ISA bus protocol – Memory Access l • • • ISA: ISA The Industry Standard Microprocessor Architecture. 80 x 86 microprocessor. 20 bit memory address. ALE: Address Latch Enable. CHRDY: Channel Ready. Compromise strobe/handshake control method is used. Memory I/O Device ISA bus CYCLE CLOCK C 1 C 4 C 2 WAIT C 3 D[7 -0] DATA A[19 -0] ADDRESS ALE /MEMR CHRDY CYCLE CLOCK C 1 C 4 C 2 WAIT The memory deasserted CHRDY before the rising clock edge in C 2, causing the microprocessor to insert wait cycles (up to 6 cycles)Real-time until. Embedded CHRDY was reasserted. Systems/Interfacing D[7 -0] C 3 DATA A[19 -0] ALE ADDRESS /MEMW CHRDY 11

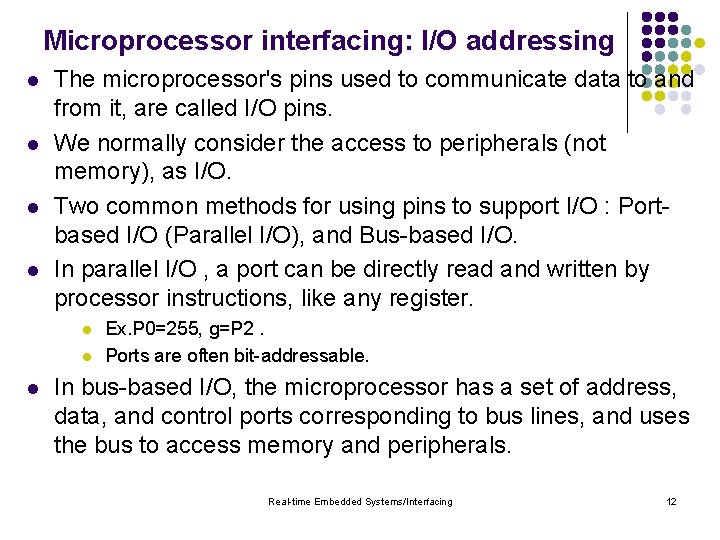

Microprocessor interfacing: I/O addressing l l The microprocessor's pins used to communicate data to and from it, are called I/O pins. We normally consider the access to peripherals (not memory), as I/O. Two common methods for using pins to support I/O : Portbased I/O (Parallel I/O), and Bus-based I/O. In parallel I/O , a port can be directly read and written by processor instructions, like any register. l l l Ex. P 0=255, g=P 2. Ports are often bit-addressable. In bus-based I/O, the microprocessor has a set of address, data, and control ports corresponding to bus lines, and uses the bus to access memory and peripherals. Real-time Embedded Systems/Interfacing 12

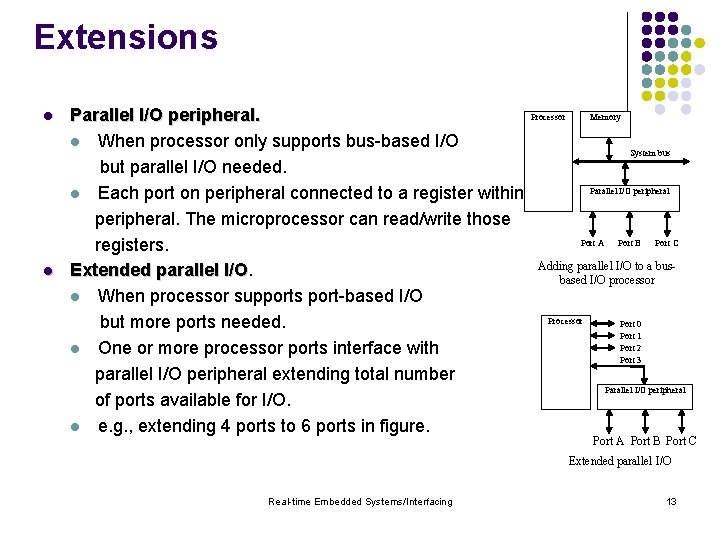

Extensions l l Parallel I/O peripheral. l When processor only supports bus-based I/O but parallel I/O needed. l Each port on peripheral connected to a register within peripheral. The microprocessor can read/write those registers. Extended parallel I/O l When processor supports port-based I/O but more ports needed. l One or more processor ports interface with parallel I/O peripheral extending total number of ports available for I/O. l e. g. , extending 4 ports to 6 ports in figure. Memory Processor System bus Parallel I/O peripheral Port A Port B Port C Adding parallel I/O to a busbased I/O processor Port 0 Port 1 Port 2 Port 3 Parallel I/O peripheral Port A Port B Port C Extended parallel I/O Real-time Embedded Systems/Interfacing 13

Memory-Mapped I/O and Standard I/O l They are two bus-based methods for microprocessor to communicate with peripherals. l In memory-mapped I/O, peripherals occupy specific addresses in the existing address space. l l e. g. , Bus has 16 -bit address, lower 32 K addresses may correspond to memory, and upper 32 k addresses may correspond to peripherals. In standard I/O (I/O-mapped I/O), the bus includes an additional pin (M`/IO), to include whether the access is to memory or peripheral. l e. g. , Bus has 16 -bit address, all of them for memory addressing if M`/IO=0, and all of them for I/O addressing if M`/IO=1. Real-time Embedded Systems/Interfacing 14

Memory-Mapped I/O Vs. Standard I/O l Memory-mapped I/O l l Requires no special instructions l Assembly instructions involving memory like MOV and ADD work with peripherals as well. l Standard I/O requires special instructions (e. g. , IN, OUT) to move data between peripheral registers and memory. Standard I/O l l No loss of memory addresses to peripherals. Simpler address decoding logic in peripherals possible. l When number of peripherals much smaller than address space then high-order address bits can be ignored § smaller and/or faster comparators. Real-time Embedded Systems/Interfacing 15

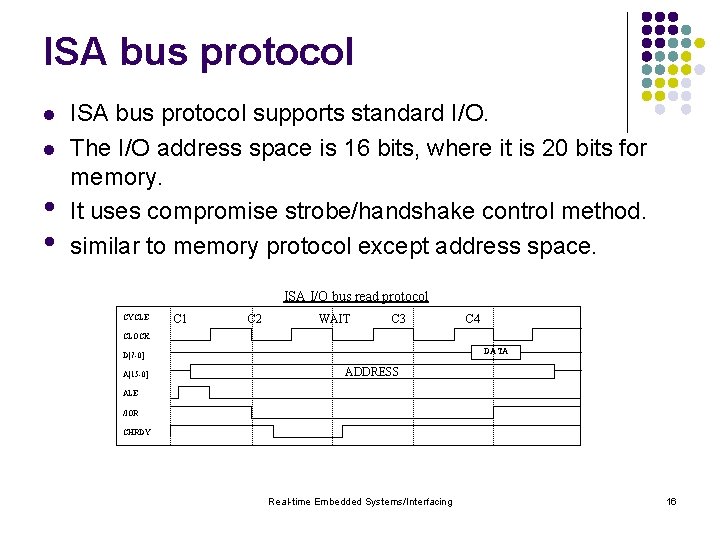

ISA bus protocol l l • • ISA bus protocol supports standard I/O. The I/O address space is 16 bits, where it is 20 bits for memory. It uses compromise strobe/handshake control method. similar to memory protocol except address space. ISA I/O bus read protocol CYCLE C 1 C 2 WAIT C 3 C 4 CLOCK DATA D[7 -0] A[15 -0] ADDRESS ALE /IOR CHRDY Real-time Embedded Systems/Interfacing 16

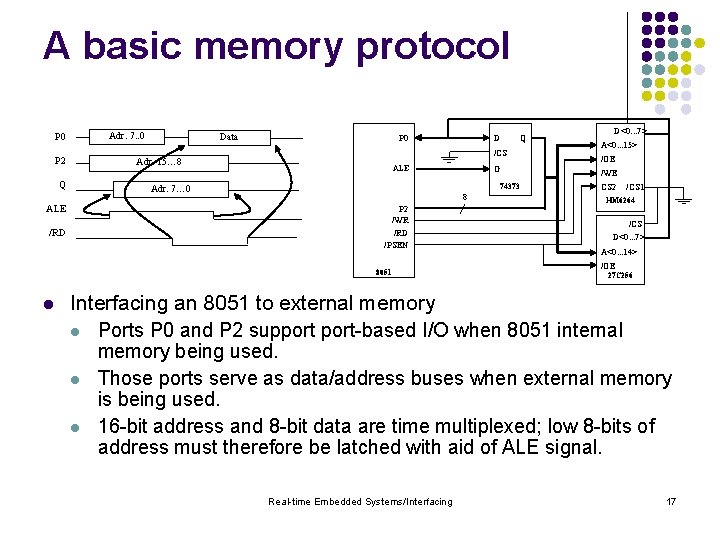

A basic memory protocol P 0 P 2 Q ALE /RD Adr. 7. . 0 Data P 0 /CS Adr. 15… 8 ALE G 8 P 2 /WR /RD /PSEN D<0. . . 7> A<0. . . 15> /OE /WE 74373 Adr. 7… 0 8051 l Q D CS 2 /CS 1 HM 6264 /CS D<0. . . 7> A<0. . . 14> /OE 27 C 256 Interfacing an 8051 to external memory l Ports P 0 and P 2 support-based I/O when 8051 internal memory being used. l Those ports serve as data/address buses when external memory is being used. l 16 -bit address and 8 -bit data are time multiplexed; low 8 -bits of address must therefore be latched with aid of ALE signal. Real-time Embedded Systems/Interfacing 17

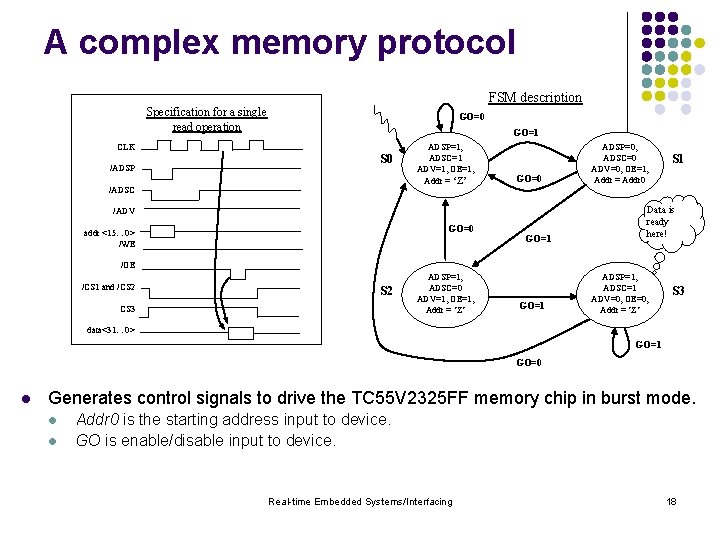

A complex memory protocol FSM description Specification for a single read operation GO=0 GO=1 CLK /ADSP S 0 /ADSC ADSP=1, ADSC=1 ADV=1, OE=1, Addr = ‘Z’ GO=0 /ADV GO=0 addr <15… 0> /WE GO=1 ADSP=0, ADSC=0 ADV=0, OE=1, Addr = Addr 0 S 1 Data is ready here! /OE /CS 1 and /CS 2 CS 3 ADSP=1, ADSC=0 ADV=1, OE=1, Addr = ‘Z’ GO=1 ADSP=1, ADSC=1 ADV=0, OE=0, Addr = ‘Z’ S 3 data<31… 0> GO=1 GO=0 l Generates control signals to drive the TC 55 V 2325 FF memory chip in burst mode. l l Addr 0 is the starting address input to device. GO is enable/disable input to device. Real-time Embedded Systems/Interfacing 18

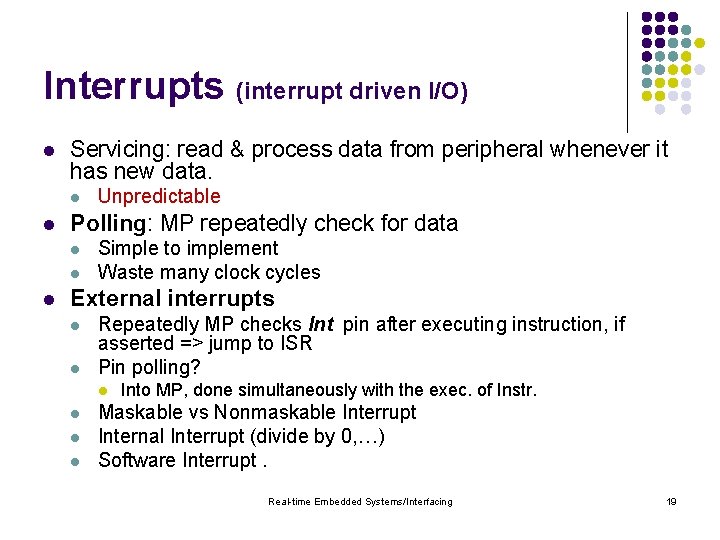

Interrupts (interrupt driven I/O) l Servicing: read & process data from peripheral whenever it has new data. l l Polling: MP repeatedly check for data l l l Unpredictable Simple to implement Waste many clock cycles External interrupts l l Repeatedly MP checks Int pin after executing instruction, if asserted => jump to ISR Pin polling? l l Into MP, done simultaneously with the exec. of Instr. Maskable vs Nonmaskable Interrupt Internal Interrupt (divide by 0, …) Software Interrupt. Real-time Embedded Systems/Interfacing 19

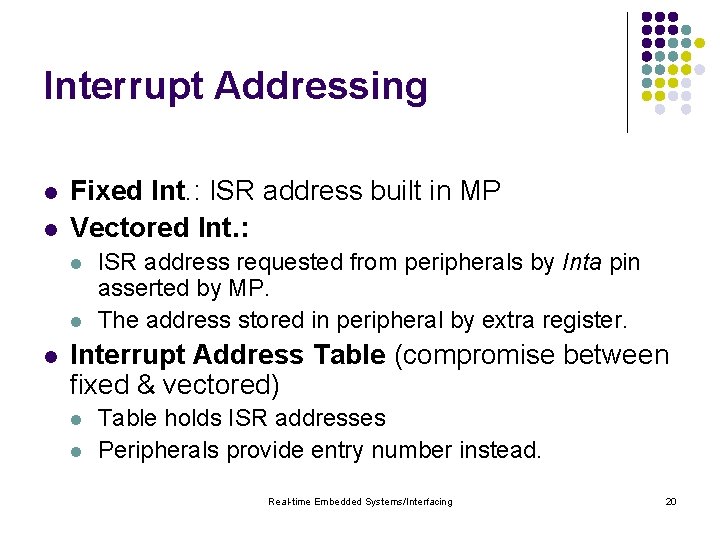

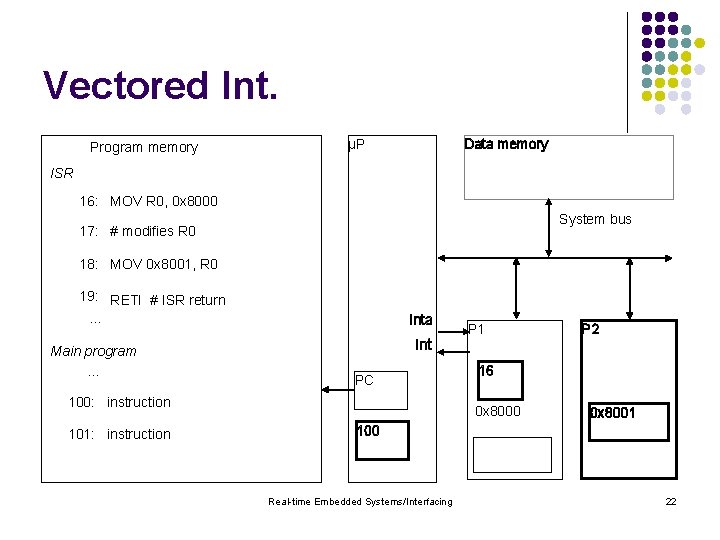

Interrupt Addressing l l Fixed Int. : ISR address built in MP Vectored Int. : l l l ISR address requested from peripherals by Inta pin asserted by MP. The address stored in peripheral by extra register. Interrupt Address Table (compromise between fixed & vectored) l l Table holds ISR addresses Peripherals provide entry number instead. Real-time Embedded Systems/Interfacing 20

Fixed Int. 1. 2. 3. 4. 5. MP is executing its main program. Peripheral_1 receives input data in a register and assert Int to request servicing. After completing Instr. Execution, MP detect Int , saves current PC value and set PC = ISR fixed address. ISR reads Peripheral_1 data & processed it, then deasserts Int. ISR return, restoring PC and MP resume execution. Real-time Embedded Systems/Interfacing 21

Vectored Int. Program memory μP Data memory ISR 16: MOV R 0, 0 x 8000 System bus 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . Inta Int PC 100: instruction 101: instruction P 1 P 2 16 0 x 8000 0 x 8001 100 Real-time Embedded Systems/Interfacing 22

DMA l l Buffering: temporary storage of data that is awaiting processing. Using Interrupt: l l l Storing & restoring MP states => consuming many clock cycles (inefficient) No execution during data moving. I/O of DMA: separate single-purpose processor (DMA controller). l Purpose: transfer data between memories and peripherals Real-time Embedded Systems/Interfacing 23

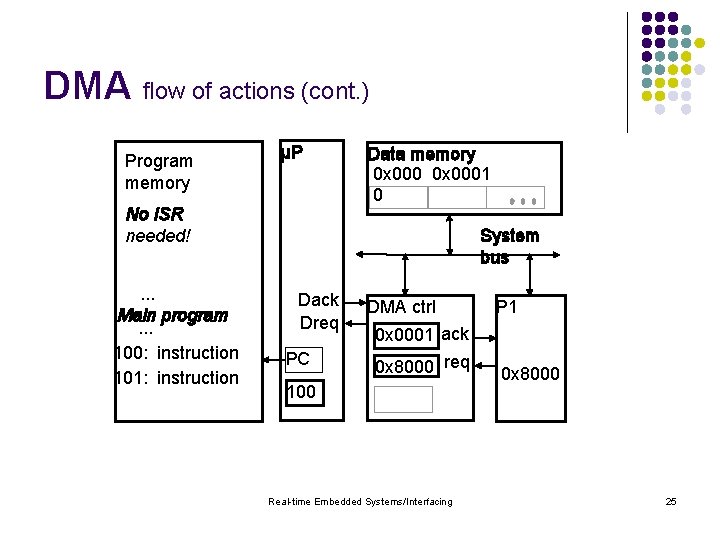

DMA flow of actions 1. 2. 3. 4. 5. 6. 7. 8. MP is executing its main program. It has already configured the DMA ctrl registers. Peripheral_1 receives input data in a register, and asserts req to request servicing by DMA ctrl asserts Dreq to request control of system bus. After executing instruction, MP sees Dreq asserted, releases the system bus, asserts Dack, and resumes execution. MP stalls only if it needs the system bus to continue executing. DMA ctrl asserts ack reads data and (b) writes that data to memory. DMA de-asserts Dreq and ack completing handshake with Peripheral_1. MP de-asserts Dack and resumes control of the bus. Peripheral_1 de-asserts req. Real-time Embedded Systems/Interfacing 24

DMA flow of actions (cont. ) Program memory μP No ISR needed!. . . Main program. . . 100: instruction 101: instruction Data memory 0 x 0001 0 System bus Dack Dreq PC DMA ctrl 0 x 0001 ack 0 x 8000 req 100 Real-time Embedded Systems/Interfacing P 1 0 x 8000 25

Arbitration l l Multiple peripherals request service simultaneously from single MP or single DMA Arbitration: decide which one get services. l l l Priority Arbiter. Daisy-Chain Arbitration. Network-Oriented Arbitration Methods. Real-time Embedded Systems/Interfacing 26

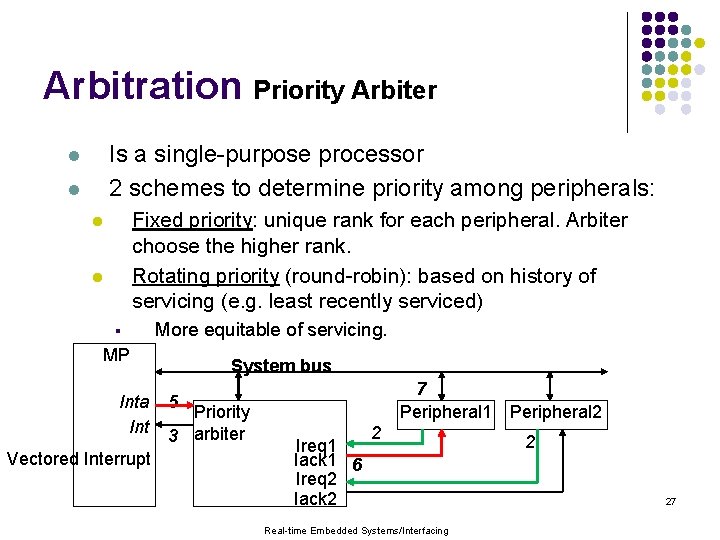

Arbitration Priority Arbiter Is a single-purpose processor 2 schemes to determine priority among peripherals: l l Fixed priority: unique rank for each peripheral. Arbiter choose the higher rank. Rotating priority (round-robin): based on history of servicing (e. g. least recently serviced) l l § More equitable of servicing. MP Inta Int Vectored Interrupt System bus 7 Peripheral 1 5 Priority 3 arbiter Ireq 1 Iack 1 6 Ireq 2 Iack 2 2 Real-time Embedded Systems/Interfacing Peripheral 2 2 27

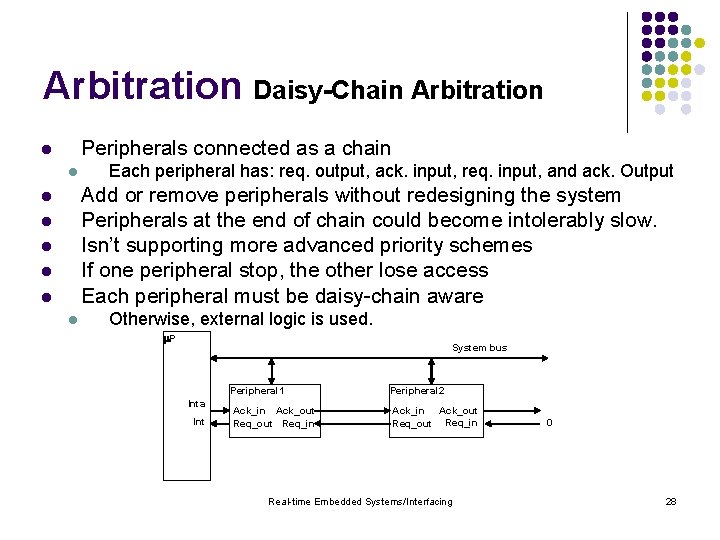

Arbitration Daisy-Chain Arbitration Peripherals connected as a chain l l Each peripheral has: req. output, ack. input, req. input, and ack. Output Add or remove peripherals without redesigning the system Peripherals at the end of chain could become intolerably slow. Isn’t supporting more advanced priority schemes If one peripheral stop, the other lose access Each peripheral must be daisy-chain aware l l l Otherwise, external logic is used. P System bus Peripheral 1 Inta Int Ack_in Ack_out Req_in Peripheral 2 Ack_in Ack_out Req_in Real-time Embedded Systems/Interfacing 0 28

Arbitration Network-Oriented Multiple MP connected by a shared bus (network). Arbitration among processors. l l l Typically built right into the bus protocol The protocol must ensure that no contending processors sending at the same time Examples: I 2 C, Ethernet, CAN … Real-time Embedded Systems/Interfacing 29

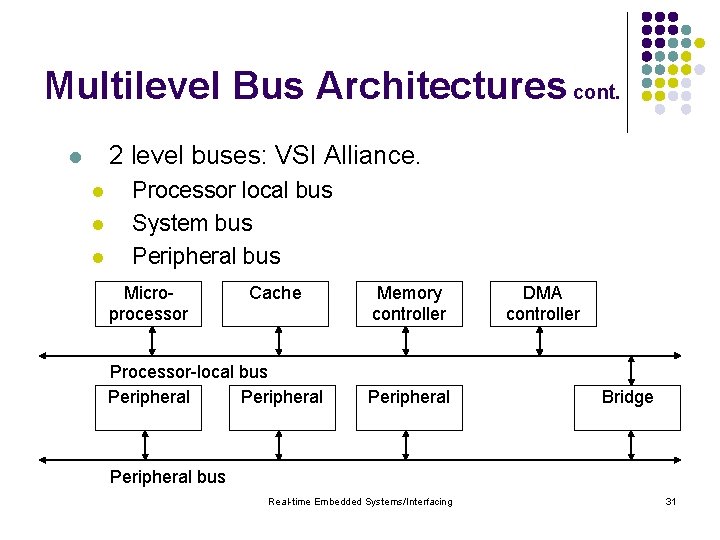

Multilevel Bus Architectures Numerous type of communications: l Most frequent and high speed (between MPs). Less frequent and low speed (between MP and Peripherals like UART) l l Single high speed bus: l Required each peripheral to have high-speed bus interface l § Extra gates , Power consumption and cost. May not be very portable. May result in slower bus. l l 2 level buses: l Processor local bus: connects MP, cache, memory controllers … Peripheral bus: ISA, PCI … l l § l emphasize portability, low power or low gate count. Bridge (single-purpose processor) connect two bus levels Real-time Embedded Systems/Interfacing 30

Multilevel Bus Architectures cont. 2 level buses: VSI Alliance. l l Processor local bus System bus Peripheral bus Microprocessor Cache Processor-local bus Peripheral Memory controller Peripheral DMA controller Bridge Peripheral bus Real-time Embedded Systems/Interfacing 31

Advanced Communication Principles Physical layer: the medium that is used to carry data from one device to another. l l l Single wire, a set of wires, radio waves, or infrared waves. Parallel communication Serial Communication Wireless Communication Real-time Embedded Systems/Interfacing 32

Parallel communication Multiple data wires + control and possibly power wires. Each wire carries one of the bits. l l l Long parallel wires: l l l High data throughput, if the length is short. High capacitance values => more time to charge or discharge Misalignment. Costly to construct. May be bulky In general, used when connect devices reside on the same IC or circuit board. Real-time Embedded Systems/Interfacing 33

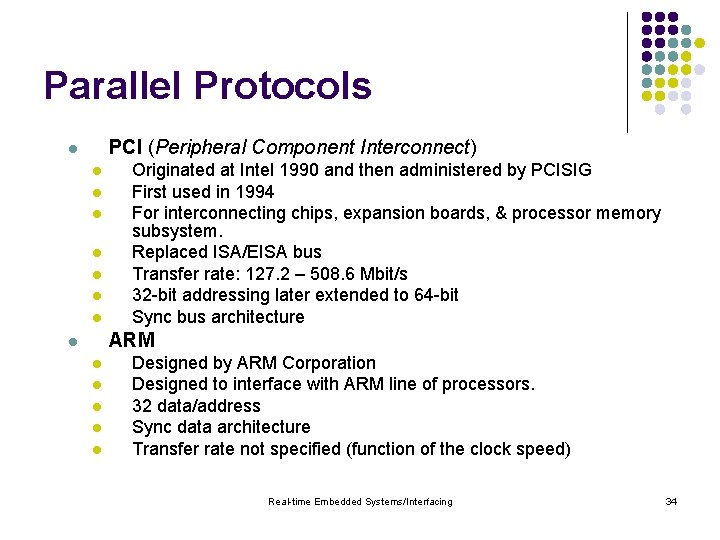

Parallel Protocols PCI (Peripheral Component Interconnect) l l l l Originated at Intel 1990 and then administered by PCISIG First used in 1994 For interconnecting chips, expansion boards, & processor memory subsystem. Replaced ISA/EISA bus Transfer rate: 127. 2 – 508. 6 Mbit/s 32 -bit addressing later extended to 64 -bit Sync bus architecture ARM l l l Designed by ARM Corporation Designed to interface with ARM line of processors. 32 data/address Sync data architecture Transfer rate not specified (function of the clock speed) Real-time Embedded Systems/Interfacing 34

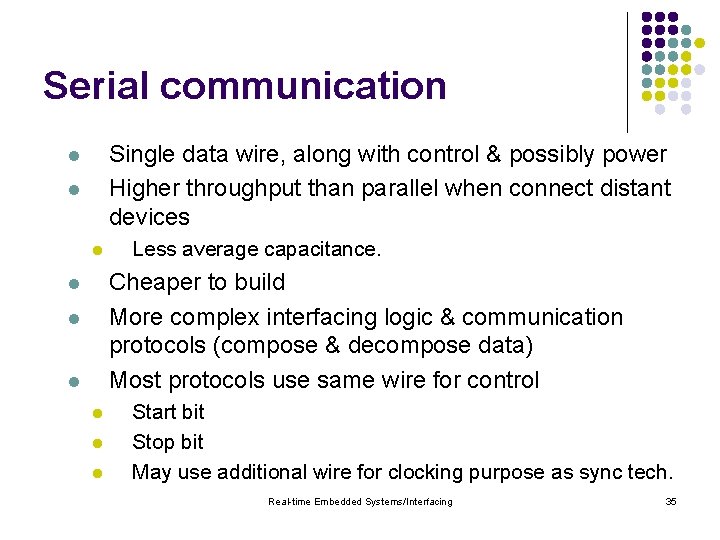

Serial communication Single data wire, along with control & possibly power Higher throughput than parallel when connect distant devices l l l Less average capacitance. Cheaper to build More complex interfacing logic & communication protocols (compose & decompose data) Most protocols use same wire for control l l l Start bit Stop bit May use additional wire for clocking purpose as sync tech. Real-time Embedded Systems/Interfacing 35

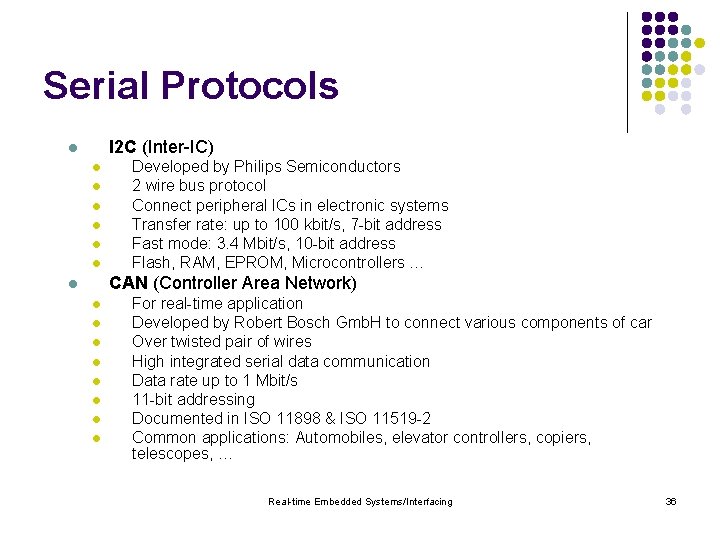

Serial Protocols I 2 C (Inter-IC) l l l l Developed by Philips Semiconductors 2 wire bus protocol Connect peripheral ICs in electronic systems Transfer rate: up to 100 kbit/s, 7 -bit address Fast mode: 3. 4 Mbit/s, 10 -bit address Flash, RAM, EPROM, Microcontrollers … CAN (Controller Area Network) l l l l l For real-time application Developed by Robert Bosch Gmb. H to connect various components of car Over twisted pair of wires High integrated serial data communication Data rate up to 1 Mbit/s 11 -bit addressing Documented in ISO 11898 & ISO 11519 -2 Common applications: Automobiles, elevator controllers, copiers, telescopes, … Real-time Embedded Systems/Interfacing 36

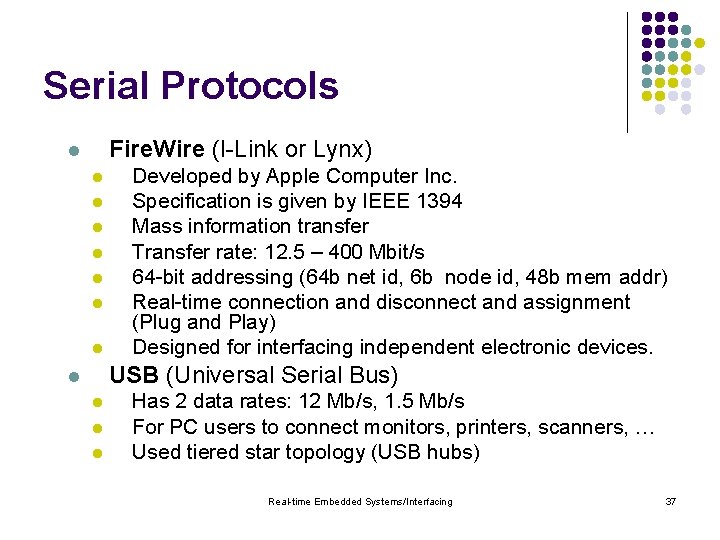

Serial Protocols Fire. Wire (I-Link or Lynx) l l l l Developed by Apple Computer Inc. Specification is given by IEEE 1394 Mass information transfer Transfer rate: 12. 5 – 400 Mbit/s 64 -bit addressing (64 b net id, 6 b node id, 48 b mem addr) Real-time connection and disconnect and assignment (Plug and Play) Designed for interfacing independent electronic devices. USB (Universal Serial Bus) l l Has 2 data rates: 12 Mb/s, 1. 5 Mb/s For PC users to connect monitors, printers, scanners, … Used tiered star topology (USB hubs) Real-time Embedded Systems/Interfacing 37

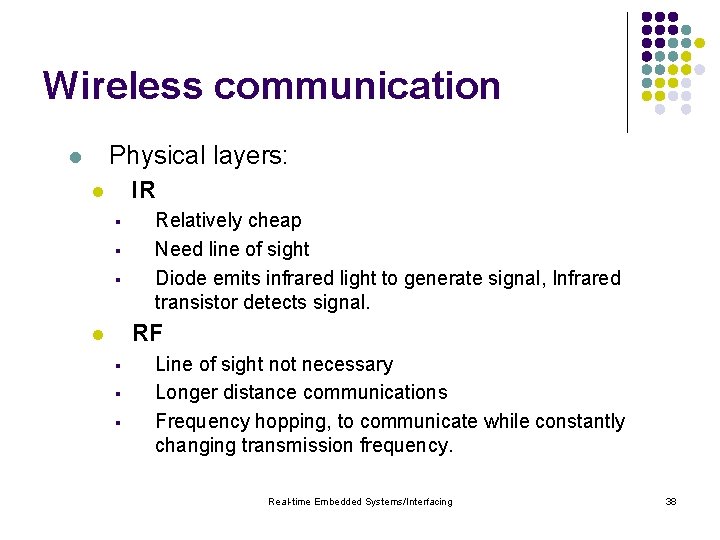

Wireless communication Physical layers: l IR l § § § Relatively cheap Need line of sight Diode emits infrared light to generate signal, Infrared transistor detects signal. RF l § § § Line of sight not necessary Longer distance communications Frequency hopping, to communicate while constantly changing transmission frequency. Real-time Embedded Systems/Interfacing 38

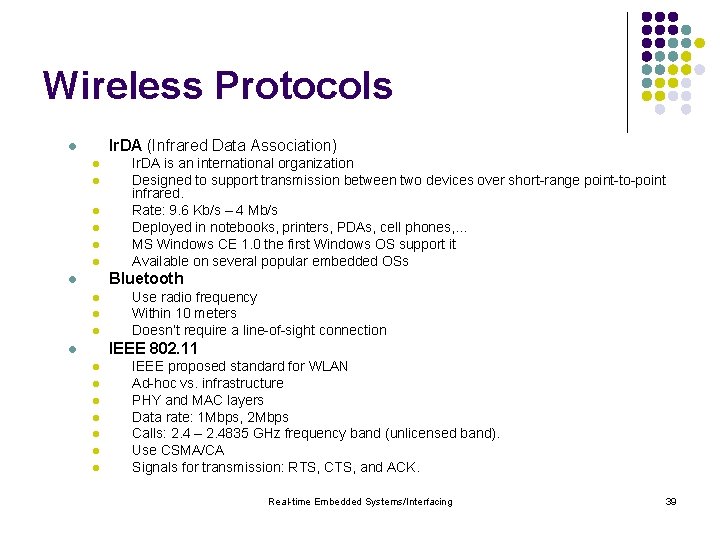

Wireless Protocols Ir. DA (Infrared Data Association) l l l l Ir. DA is an international organization Designed to support transmission between two devices over short-range point-to-point infrared. Rate: 9. 6 Kb/s – 4 Mb/s Deployed in notebooks, printers, PDAs, cell phones, … MS Windows CE 1. 0 the first Windows OS support it Available on several popular embedded OSs Bluetooth l l Use radio frequency Within 10 meters Doesn’t require a line-of-sight connection IEEE 802. 11 l l l l IEEE proposed standard for WLAN Ad-hoc vs. infrastructure PHY and MAC layers Data rate: 1 Mbps, 2 Mbps Calls: 2. 4 – 2. 4835 GHz frequency band (unlicensed band). Use CSMA/CA Signals for transmission: RTS, CTS, and ACK. Real-time Embedded Systems/Interfacing 39

Reference l “Embedded system Design: A unified Hardware/Software Introduction”, Frank Vahid, Tony Givarrgis, Wiley, 2002 Real-time Embedded Systems/Interfacing 40

Questions? Real-time Embedded Systems/Interfacing 41

- Slides: 41