CONTROL UNIT ORGANIZATION popo CONTROL UNIT ORGANIZATION Instruction

- Slides: 31

CONTROL UNIT ORGANIZATION popo

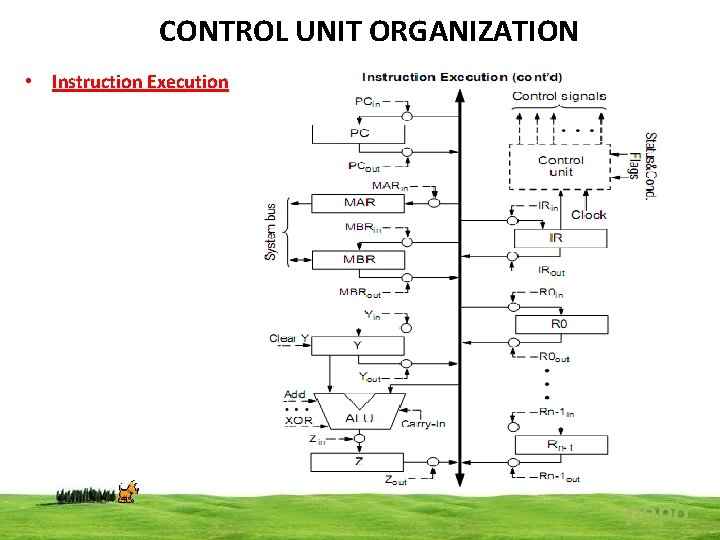

CONTROL UNIT ORGANIZATION • Instruction Execution • The CPU executes a sequence of instructions. • The execution of an instruction is organized as an instruction cycle: it is performed in several steps; • Each step is executed as a set of several micro operations. • The task performed by any micro operation falls in one of the following categories: • - Transfer data from one register to another; • - Transfer data from a register to an external interface (system bus); • - Transfer data from an external interface to a register; • - Perform an arithmetic or logic operation, using registers for input and output. popo

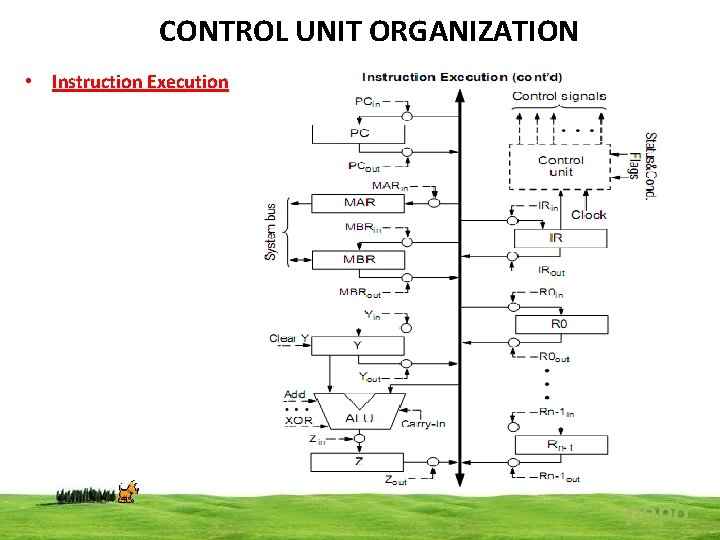

CONTROL UNIT ORGANIZATION • Instruction Execution popo

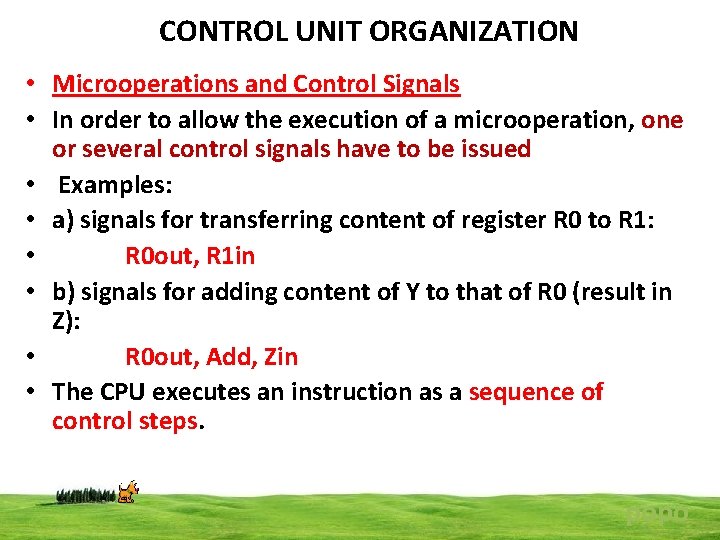

CONTROL UNIT ORGANIZATION • Microoperations and Control Signals • In order to allow the execution of a microoperation, one or several control signals have to be issued • Examples: • a) signals for transferring content of register R 0 to R 1: • R 0 out, R 1 in • b) signals for adding content of Y to that of R 0 (result in Z): • R 0 out, Add, Zin • The CPU executes an instruction as a sequence of control steps. popo

CONTROL UNIT ORGANIZATION • Microoperations and Control Signals • Instruction: • Add (R 3), R 1 popo

CONTROL UNIT ORGANIZATION • The first (three) control steps are identical for each instruction; they perform instruction fetch and increment the PC. • The following steps depend on the actual instruction (stored in the IR). • If a control step issues a read, the value will be available in the MDR after one additional step. • Several micro operations can be performed in the same control step if they don’t conflict • (for example, only one of them is allowed to output on the bus) popo

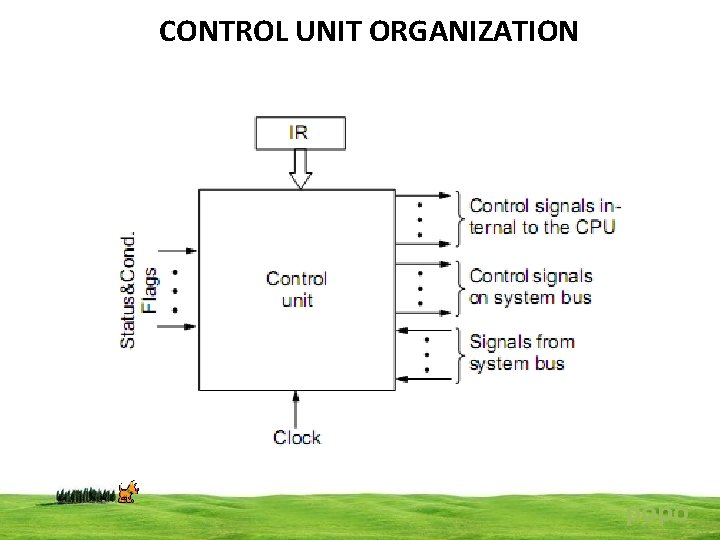

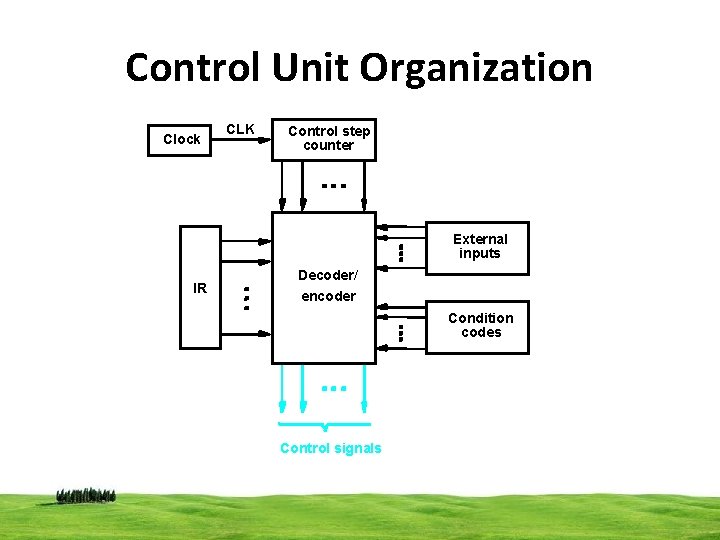

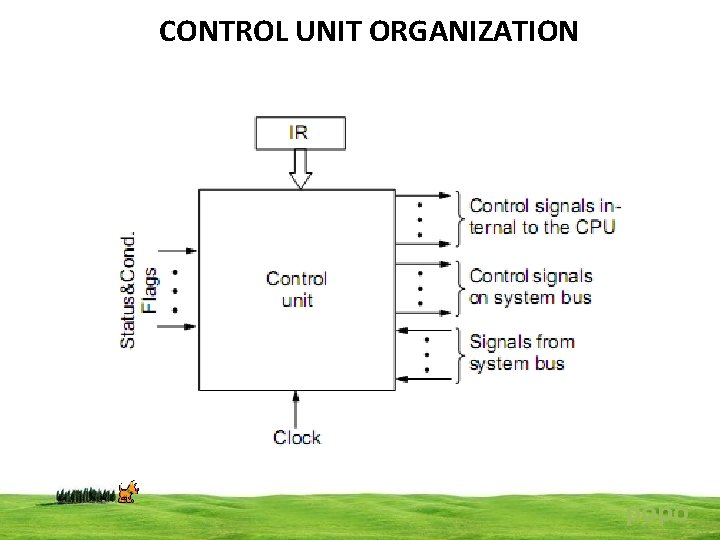

CONTROL UNIT ORGANIZATION • Control Unit • The basic task of the control unit : • - For each instruction the control unit causes the CPU to go through a sequence of control steps; • - in each control step the control unit issues a set of signals • The control unit is driven by the processor clock. • The signals to be generated at a certain moment depend on: • - the actual step to be executed; • - the condition and status flags of the processor; • - the actual instruction executed; • - external signals received on the system bus (e. g. interrupt signal) popo

CONTROL UNIT ORGANIZATION popo

CONTROL UNIT ORGANIZATION • To execute instructions, the processor must have some means of generating the control signals needed in the proper sequence. • Three Techniques : • Hardwired control , • Microprogrammed control and • PLA control • Hardwired system can operate at high speed; but with little flexibility.

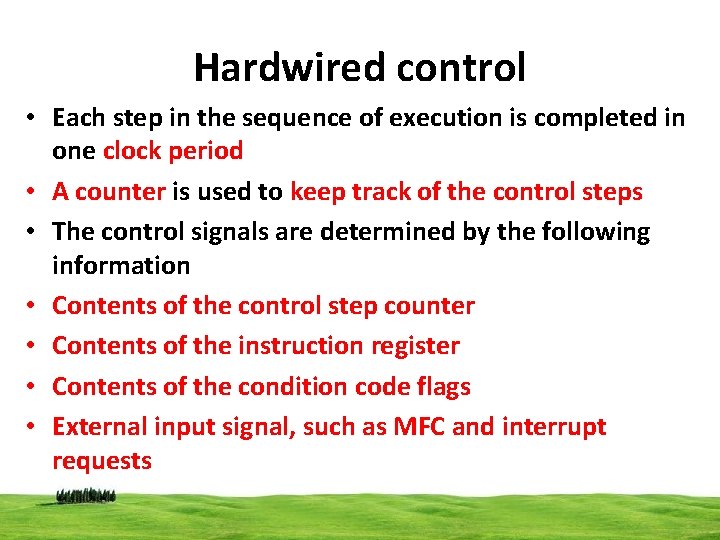

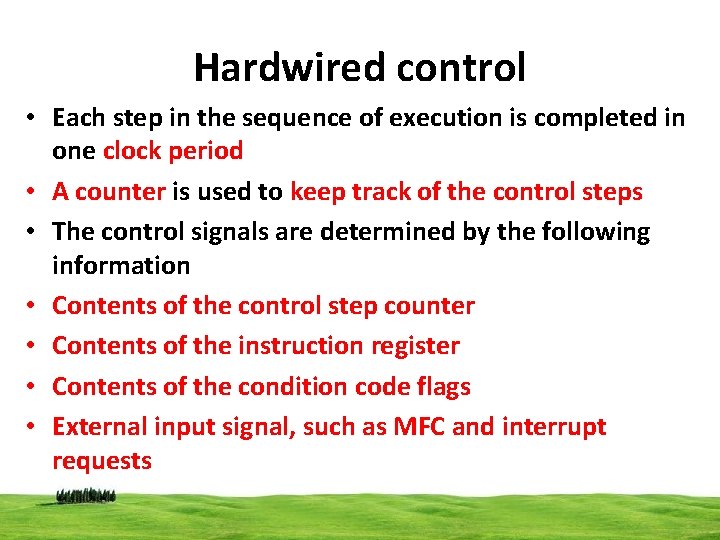

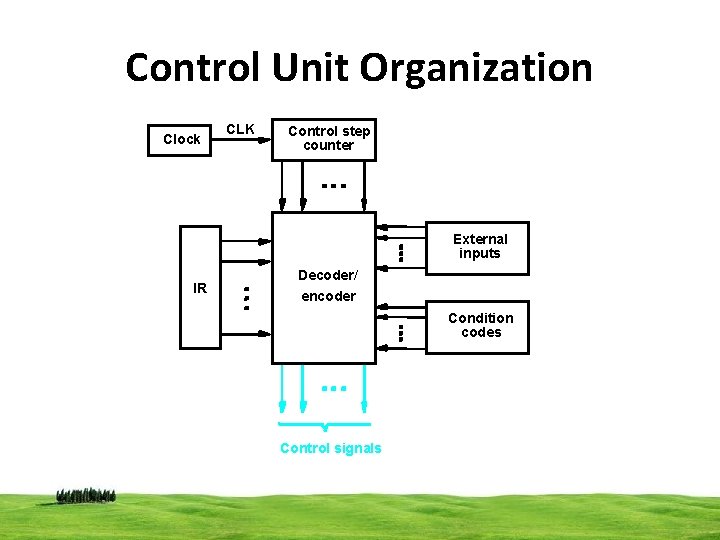

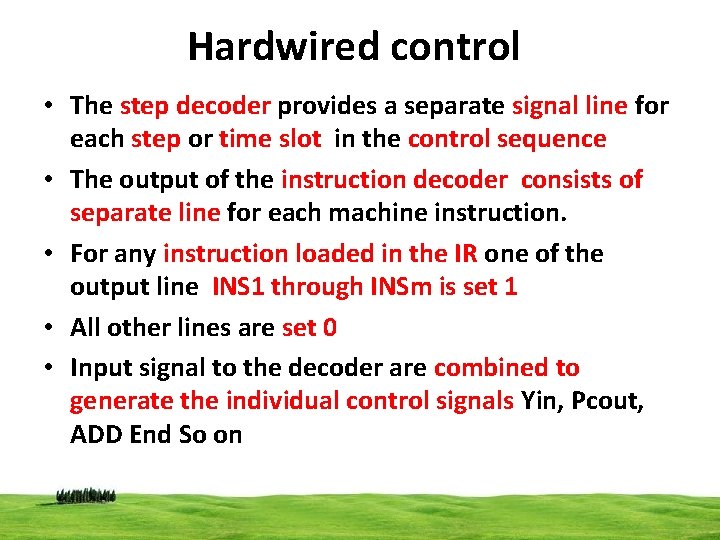

Hardwired control • Each step in the sequence of execution is completed in one clock period • A counter is used to keep track of the control steps • The control signals are determined by the following information • Contents of the control step counter • Contents of the instruction register • Contents of the condition code flags • External input signal, such as MFC and interrupt requests

Control Unit Organization Clock CLK Control step counter External inputs IR Decoder/ encoder Condition codes Control signals Figure 7. 10. Control unit organization.

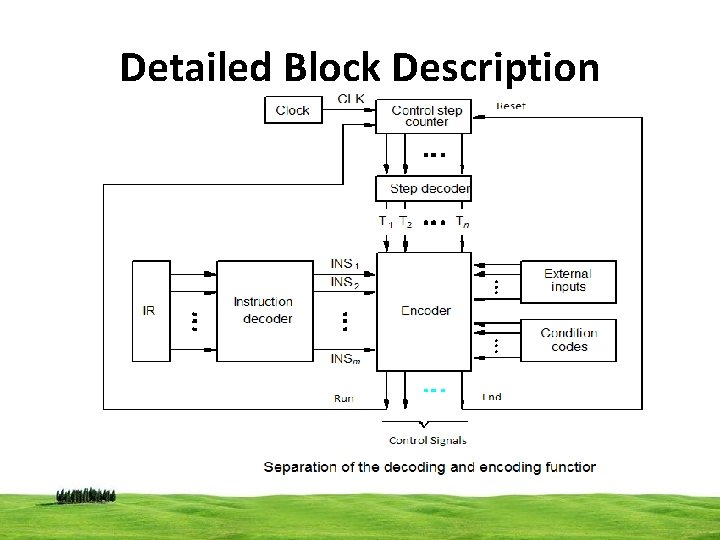

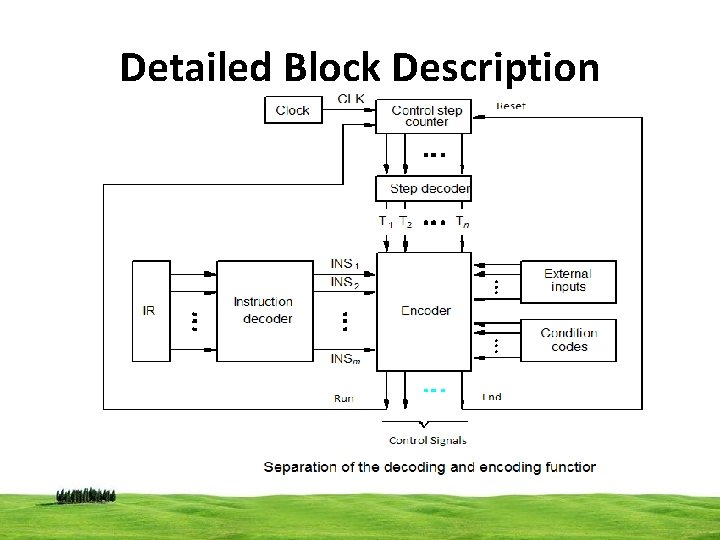

Detailed Block Description

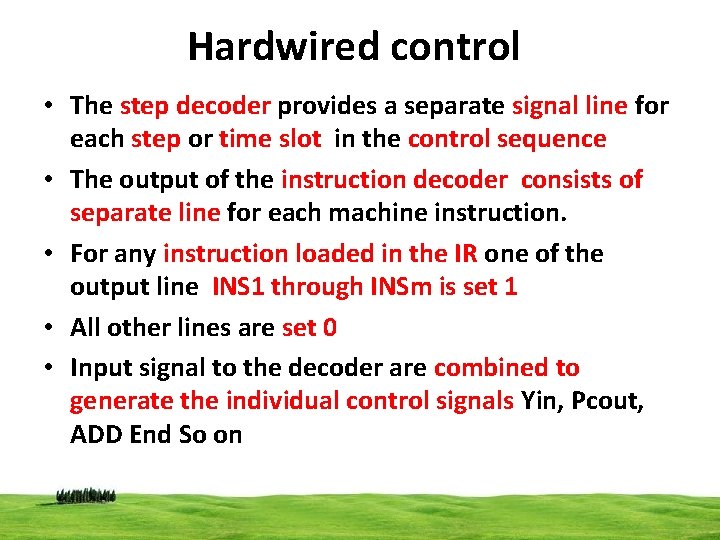

Hardwired control • The step decoder provides a separate signal line for each step or time slot in the control sequence • The output of the instruction decoder consists of separate line for each machine instruction. • For any instruction loaded in the IR one of the output line INS 1 through INSm is set 1 • All other lines are set 0 • Input signal to the decoder are combined to generate the individual control signals Yin, Pcout, ADD End So on

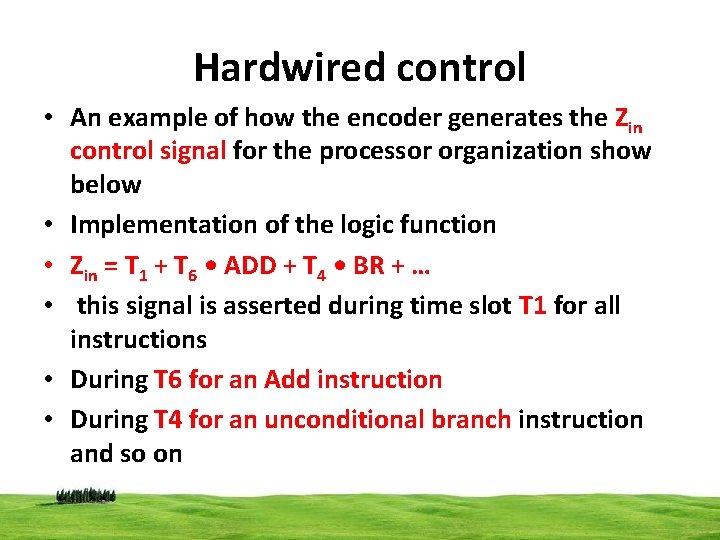

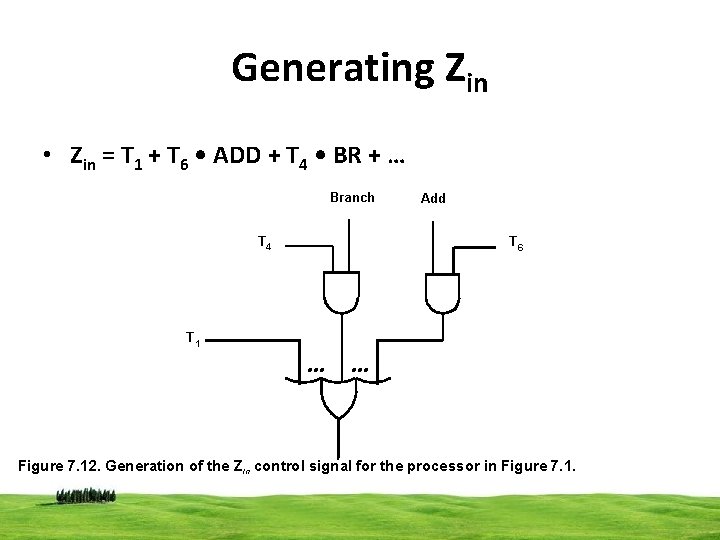

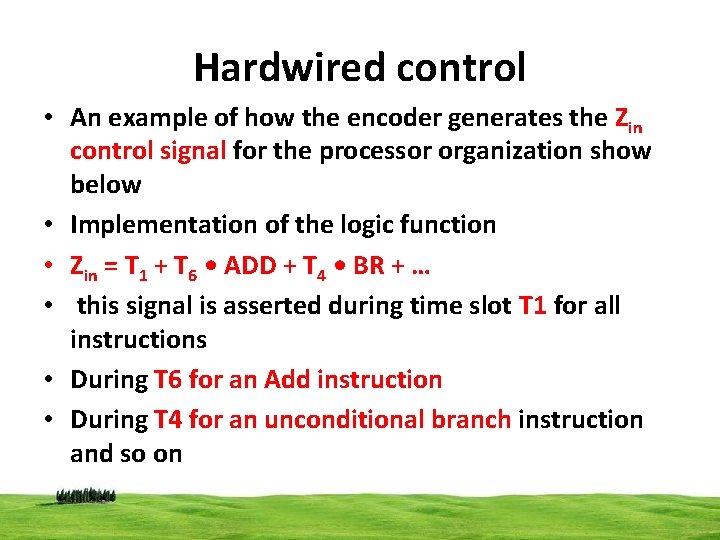

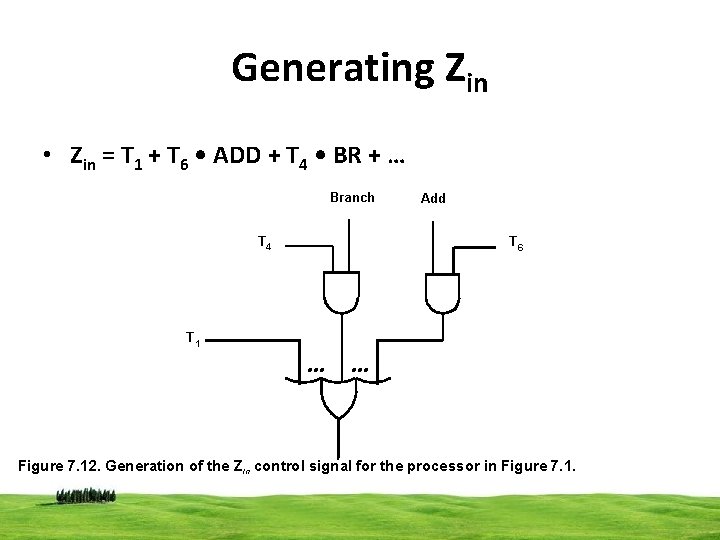

Hardwired control • An example of how the encoder generates the Zin control signal for the processor organization show below • Implementation of the logic function • Zin = T 1 + T 6 • ADD + T 4 • BR + … • this signal is asserted during time slot T 1 for all instructions • During T 6 for an Add instruction • During T 4 for an unconditional branch instruction and so on

Generating Zin • Zin = T 1 + T 6 • ADD + T 4 • BR + … Branch T 4 Add T 6 T 1 Figure 7. 12. Generation of the Zin control signal for the processor in Figure 7. 1.

Hardwired control • Another example shown below • A circuit that generate the End control signal from the logic function • End = T 7 • ADD + T 5 • BR + (T 5 • N + T 4 • N) • BRN +…

Generating End • End = T 7 • ADD + T 5 • BR + (T 5 • N + T 4 • N) • BRN +…

Hardwired control • The End instruction starts a new instruction fetch cycle by resetting the control signal step counter to its starting value • The RUN set to 1 causes the counter to be incremented by one at the end of every clock cycle • When RUN=0 the counter stops counting • It is needed when ever WMFC signal is issued, the processor to wait the reply from memory

Microprogrammed Control

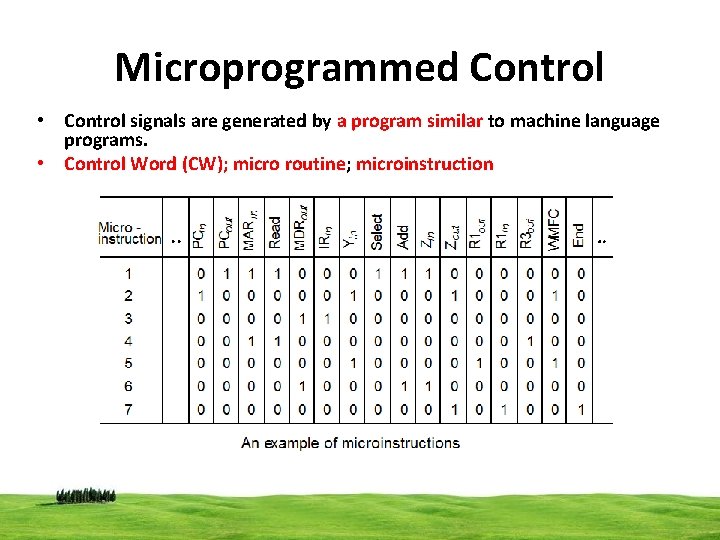

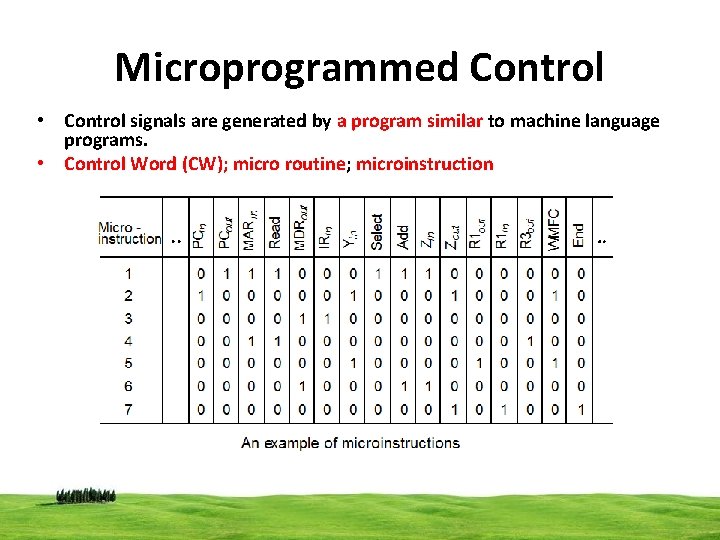

Microprogrammed Control • Control signals are generated by a program similar to machine language programs. • Control Word (CW); micro routine; microinstruction

Microprogrammed Control

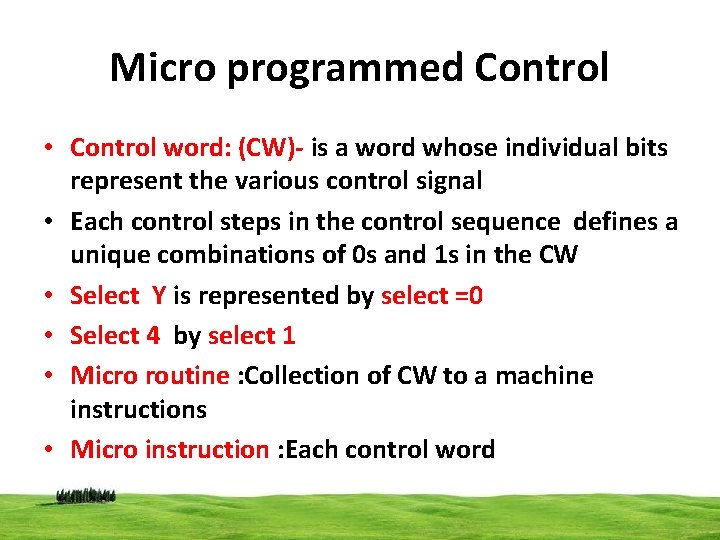

Micro programmed Control • Control word: (CW)- is a word whose individual bits represent the various control signal • Each control steps in the control sequence defines a unique combinations of 0 s and 1 s in the CW • Select Y is represented by select =0 • Select 4 by select 1 • Micro routine : Collection of CW to a machine instructions • Micro instruction : Each control word

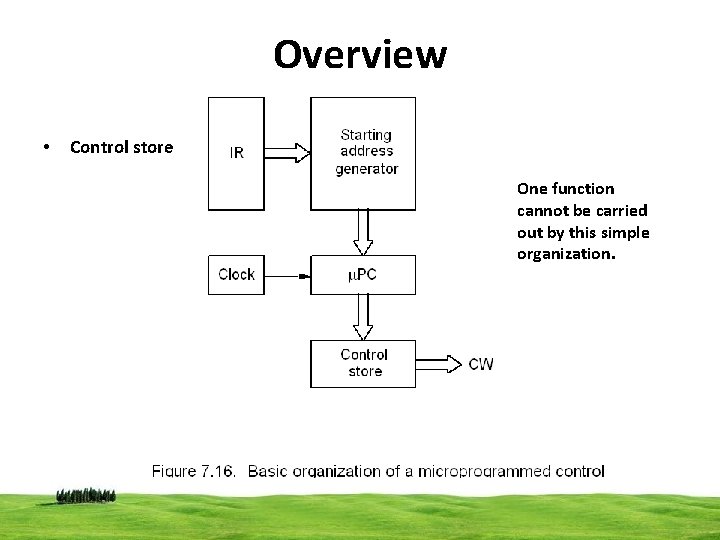

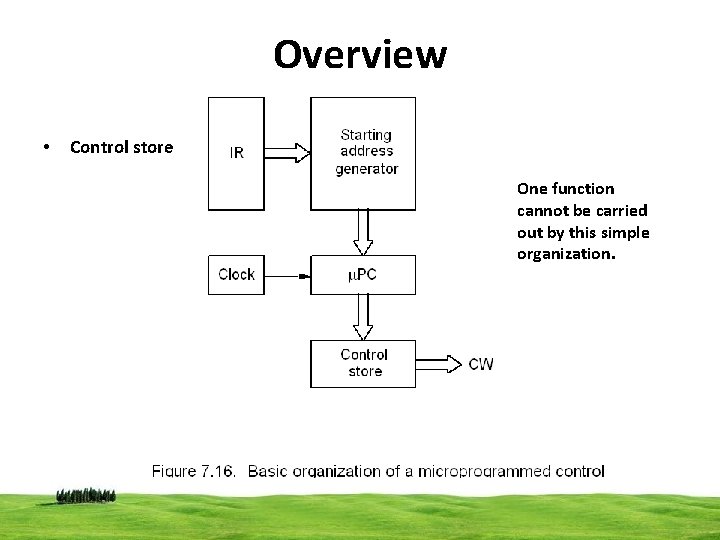

Overview • Control store One function cannot be carried out by this simple organization.

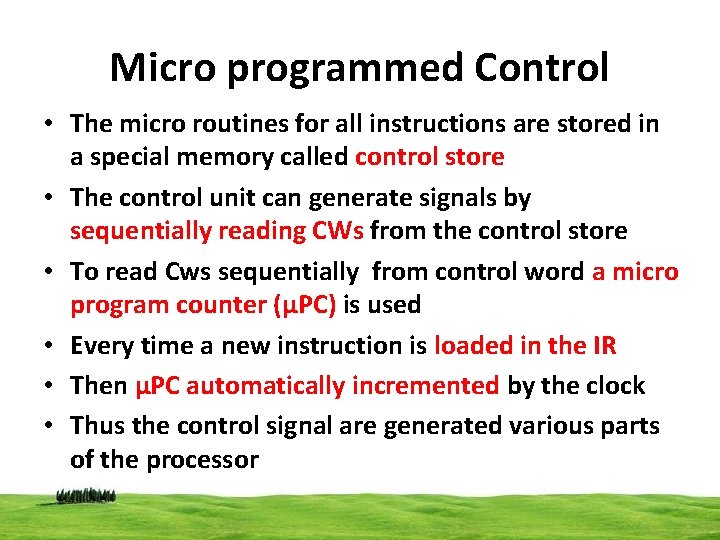

Micro programmed Control • The micro routines for all instructions are stored in a special memory called control store • The control unit can generate signals by sequentially reading CWs from the control store • To read Cws sequentially from control word a micro program counter (μPC) is used • Every time a new instruction is loaded in the IR • Then μPC automatically incremented by the clock • Thus the control signal are generated various parts of the processor

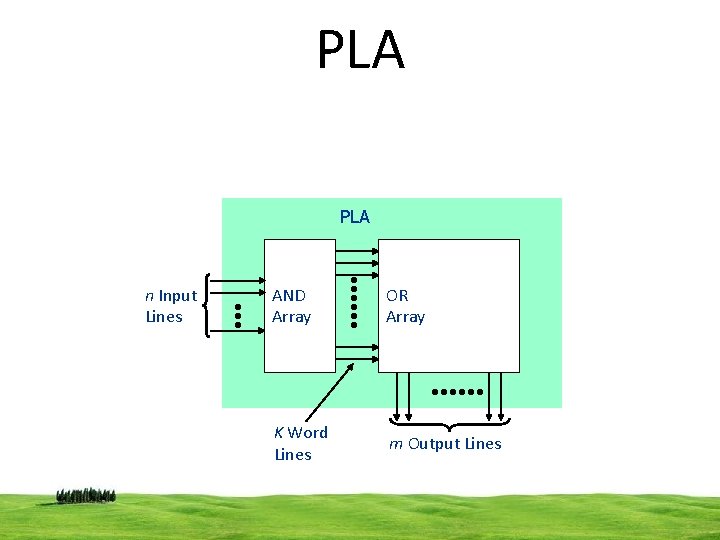

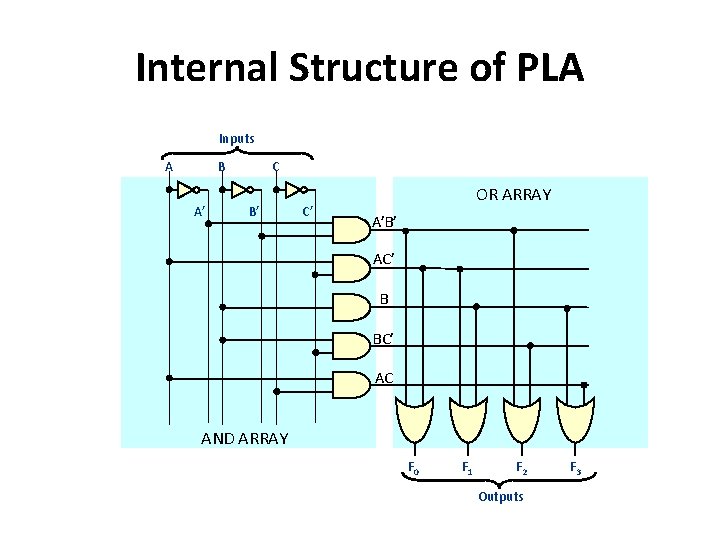

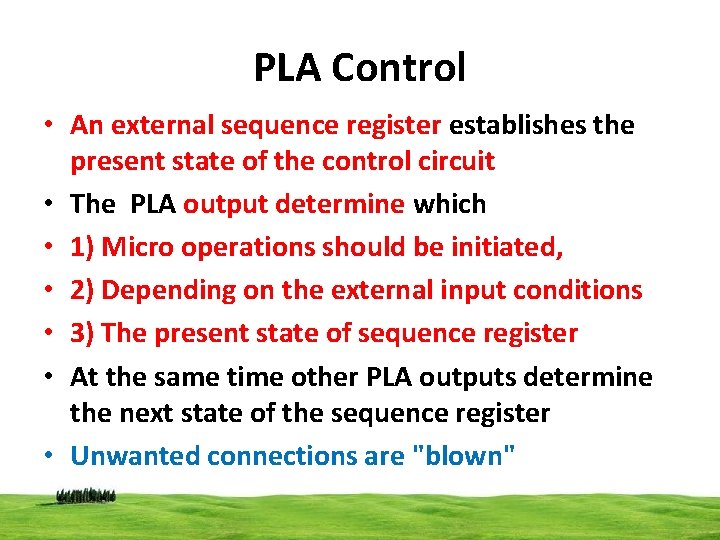

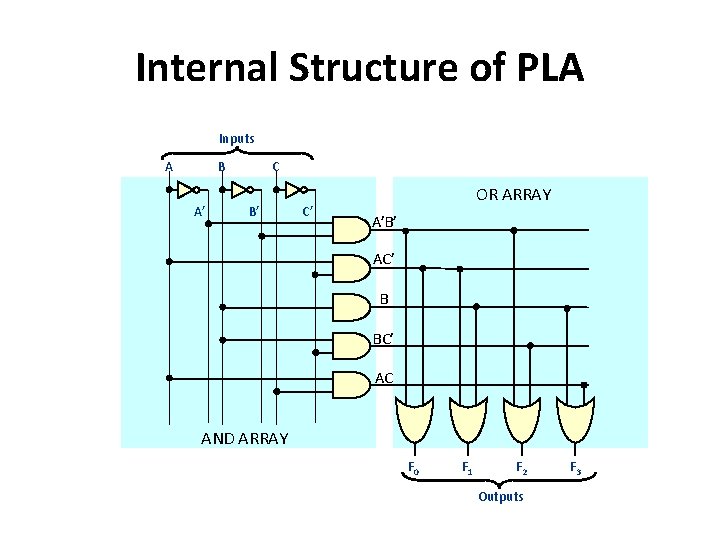

PLA Control • Programmable logic array PLA • PLA is LSI device that can implemented any complex combinational circuits • It is used to reduce the number of Ics and the no of interconnection wires

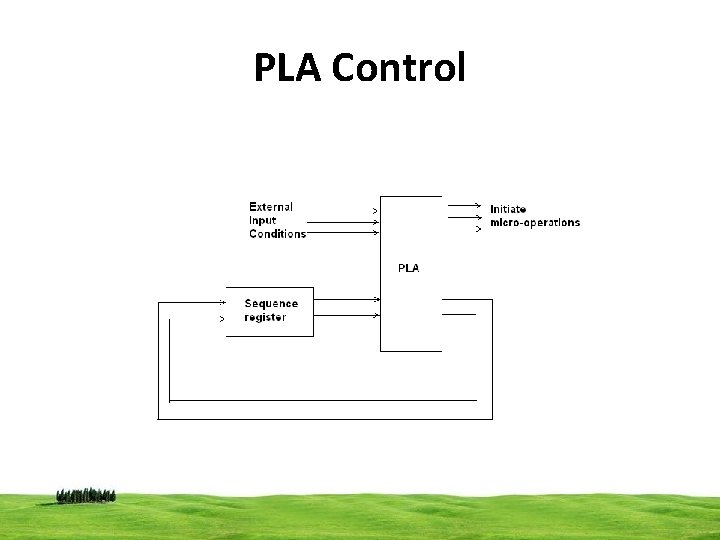

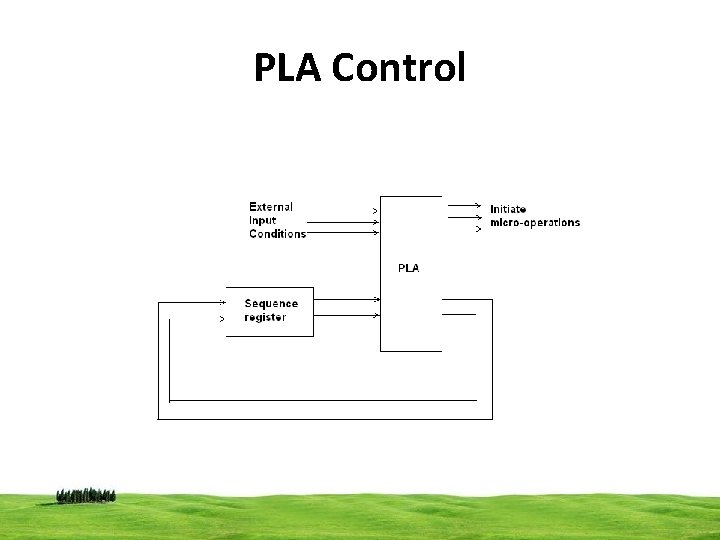

PLA Control

PLA Control • An external sequence register establishes the present state of the control circuit • The PLA output determine which • 1) Micro operations should be initiated, • 2) Depending on the external input conditions • 3) The present state of sequence register • At the same time other PLA outputs determine the next state of the sequence register • Unwanted connections are "blown"

CONTROL UNIT ORGANIZATION popo

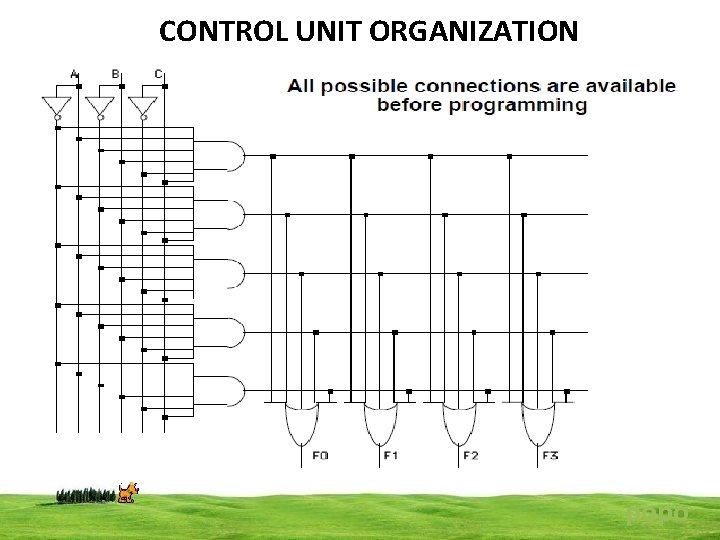

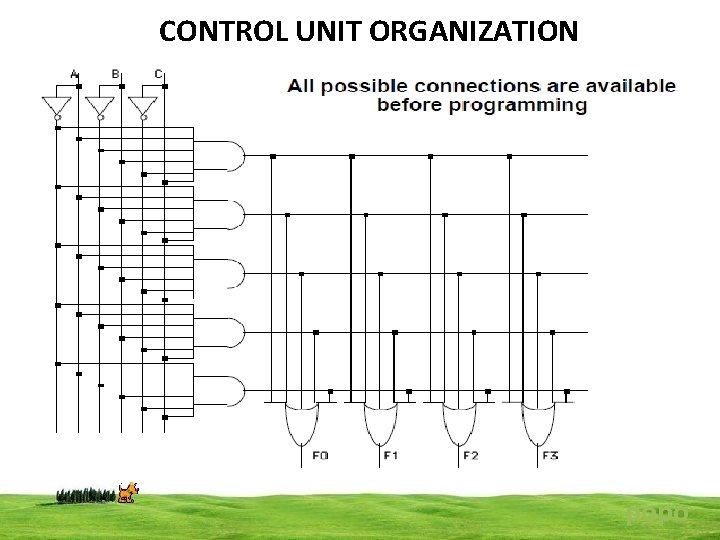

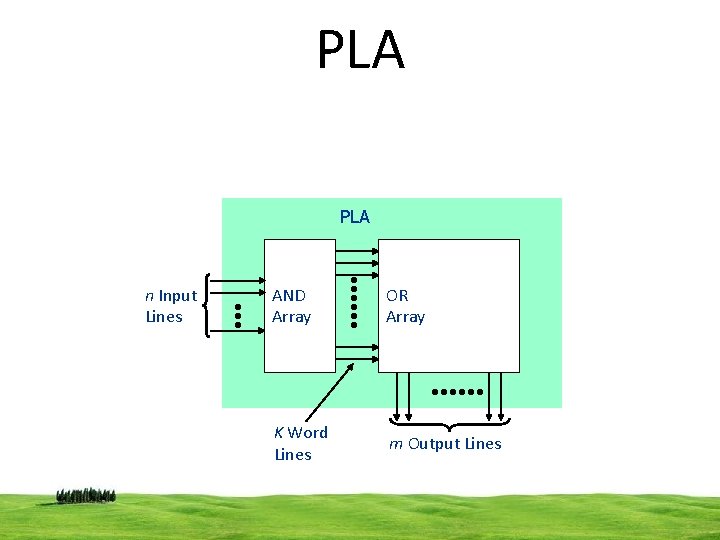

PLA • • • n Input Lines AND Array • • • PLA OR Array • • • K Word Lines m Output Lines

Internal Structure of PLA Inputs A B A’ C B’ C’ OR ARRAY A’B’ AC’ B BC’ AC AND ARRAY F 0 F 1 F 2 Outputs F 3

CONTROL UNIT ORGANIZATION popo