Introduction to Computer Organization and Architecture Lecture 1

![Introduction p Course Outline n Introduction [chap 1] (2) Brief History p Overview of Introduction p Course Outline n Introduction [chap 1] (2) Brief History p Overview of](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-4.jpg)

![Introduction p Course Outline, cont’d n Case Studies of Instruction Set Architecture [chap. 3] Introduction p Course Outline, cont’d n Case Studies of Instruction Set Architecture [chap. 3]](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-5.jpg)

![Introduction p Course Outline, cont’d n n Verilog / VHDL Tutorials [Supplemental material] (6) Introduction p Course Outline, cont’d n n Verilog / VHDL Tutorials [Supplemental material] (6)](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-6.jpg)

![Introduction p Course Outline, cont’d n Processor Design [chap 7] (6) Datapath design p Introduction p Course Outline, cont’d n Processor Design [chap 7] (6) Datapath design p](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-7.jpg)

- Slides: 48

Introduction to Computer Organization and Architecture Lecture 1 By Juthawut Chantharamalee http: //dusithost. dusit. ac. th/~juthawut_cha/ home. htm

Introduction p Introduction n n Description Course Outline Administrative p Brief History of Computers p Overview of Computer Organization p Overview of Computer Performance p Case Study: Intel Processors p Introduction to Computer Organization and Architecture 2

Introduction p Description from ISIS n Basic concepts; computer evolution, register transfer level design, simulation techniques, instruction sets (CISC and RISC), assembly language programming, ALU design, arithmetic algorithms and realization of arithmetic functions, hardwired and microprogrammed control, memory hierarchies, virtual memory, cache memory, interrupts and DMA, input/output; introduction to high-performance techniques, pipelining, multiprocessing; introduction to hardware description languages (Verilog, VHDL); students design and simulate a simple processor. Introduction to Computer Organization and Architecture 3

![Introduction p Course Outline n Introduction chap 1 2 Brief History p Overview of Introduction p Course Outline n Introduction [chap 1] (2) Brief History p Overview of](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-4.jpg)

Introduction p Course Outline n Introduction [chap 1] (2) Brief History p Overview of Computer Organization p n Architecture: Instruction Set Design [chap 2] (6) Information representation & arithmetic operations p Instruction Formats, Addressing Modes p Assembly language Programming p Basic input/output operations p Subroutine linkage p Introduction to Computer Organization and Architecture 4

![Introduction p Course Outline contd n Case Studies of Instruction Set Architecture chap 3 Introduction p Course Outline, cont’d n Case Studies of Instruction Set Architecture [chap. 3]](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-5.jpg)

Introduction p Course Outline, cont’d n Case Studies of Instruction Set Architecture [chap. 3] (4) Motorola M 68000 p ARM p Intel Pentium p n Computer Arithmetic and ALU Design [chap. 6] (6) Addition (Subtraction) p Multiplication (Division) p Shifting and Rotating p Floating Point Arithmetic p Introduction to Computer Organization and Architecture 5

![Introduction p Course Outline contd n n Verilog VHDL Tutorials Supplemental material 6 Introduction p Course Outline, cont’d n n Verilog / VHDL Tutorials [Supplemental material] (6)](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-6.jpg)

Introduction p Course Outline, cont’d n n Verilog / VHDL Tutorials [Supplemental material] (6) Memory [chap 5] (6) Semiconductor Memory Technology p Cache Memory p Virtual Memory p Memory Management and Case Studies p Introduction to Computer Organization and Architecture 6

![Introduction p Course Outline contd n Processor Design chap 7 6 Datapath design p Introduction p Course Outline, cont’d n Processor Design [chap 7] (6) Datapath design p](https://slidetodoc.com/presentation_image/1ad189cab8ad1a97e6ba9f74a74b59b2/image-7.jpg)

Introduction p Course Outline, cont’d n Processor Design [chap 7] (6) Datapath design p Control Unit Design p Microprogramming p Exception Handling p n Input/Output [chap 4] (4) Device Interfacing and Addressing p Interrupts p Bus Design p n Additional topics [selected from chapters 8 -12] Introduction to Computer Organization and Architecture 7

Administrative n Lectures Time: M/W/F 8: 30 - 9: 20 AM p Room: 4030 SC p n Instructor James Maxted: jmaxted@engineering. uiowa. edu p Design engineer for Rockwell Collins (35 years) p Office: 1126 SC, hours M/W/F 9: 30 - 10: 20 AM p n TA Dakai Jin: dakai-jin@uiowa. edu p Office: 1313 SC, hours p Introduction to Computer Organization and Architecture 8

Administrative (cont’d) p Grading n n Approximately 1 homework per week 1 multi-part project 2 exams (1 mid-term, final) Weighting Attendance 10% p Project and Assignment 40% p Midterm 20% p Final 30% p Introduction to Computer Organization and Architecture 9

Administrative (cont’d) p Course webpage n n n Place to find syllabus, lecture notes, homework, etc http: //dusithost. dusit. ac. th/~juthawut_cha/home. htm Project Design and simulate a simple processor Mentor Graphics tools Verilog. HDL Introduction to Computer Organization and Architecture 10

Administrative (cont’d) p Collaboration n n p Discussion of the material is encouraged, but… All students are expected to do their own work Disabilities n Please contact me (office hours or email) Introduction to Computer Organization and Architecture 11

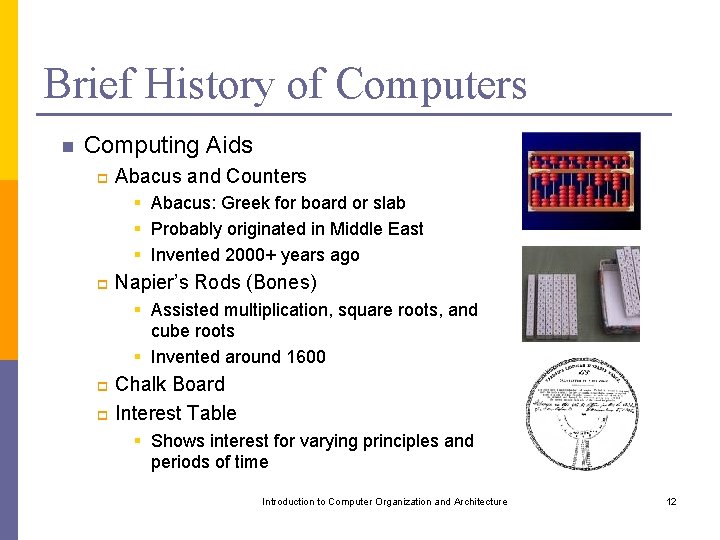

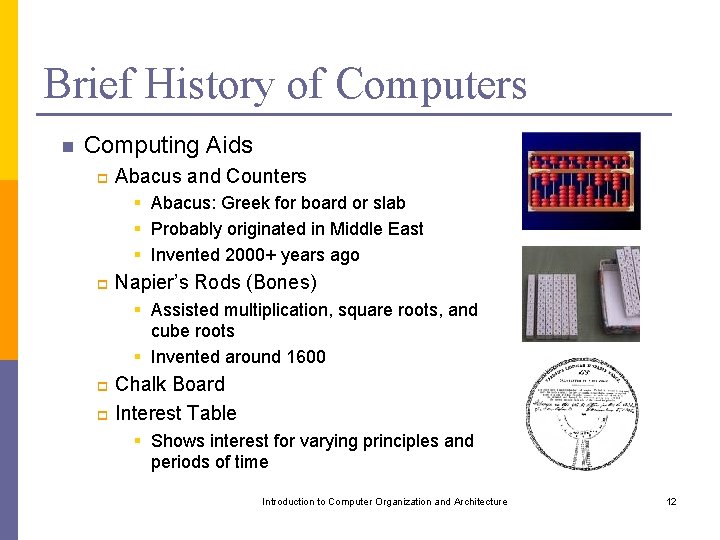

Brief History of Computers n Computing Aids p Abacus and Counters § Abacus: Greek for board or slab § Probably originated in Middle East § Invented 2000+ years ago p Napier’s Rods (Bones) § Assisted multiplication, square roots, and cube roots § Invented around 1600 Chalk Board p Interest Table p § Shows interest for varying principles and periods of time Introduction to Computer Organization and Architecture 12

Brief History of Computers n Machines that Calculate or Control p Adding machines § Blaise Pascal’s “Pascaline” § 1642 p Automatic loom § Punch cards used to control a manufacturing process § 1800 p Cash register § “Incorruptible cashier” § 1900 Introduction to Computer Organization and Architecture 13

Brief History of Computers n Electromechanical Devices p Hollerith 1890 Census Tabulator § Punch, tabulator and sorting box p International Business Machines (IBM) § Accounting Machines § Changed circuits by moving cables in plugboards § Early 1900 s p Ciphering and deciphering § Encode and decode secret messages during World War II § Enigma and Bombe Introduction to Computer Organization and Architecture 14

Brief History of Computers n Electronic Computers p Vacuum tube § ENIAC: 17, 000 tubes, 30 tons, 1800 ft 2 § 1945 p Transistor § IBM System/360 Family § Compatible processors, Standardized peripherals and connections § 1962 p Integrated circuit § IBM PC § Intel 8088 § 1981 Introduction to Computer Organization and Architecture 15

Brief History of Computers The First Programmer n n Ada Augusta or Charles Babbage Robert Campbell, Richard Bloch, Grace Murray Hopper, or Howard Aiken Introduction to Computer Organization and Architecture 16

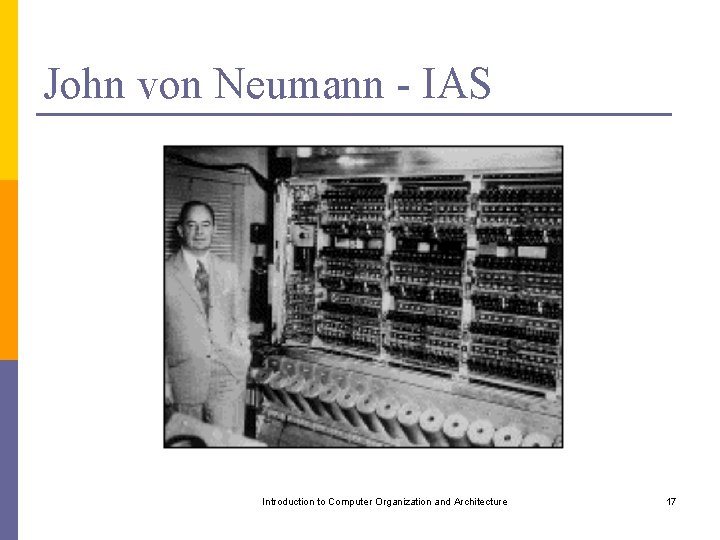

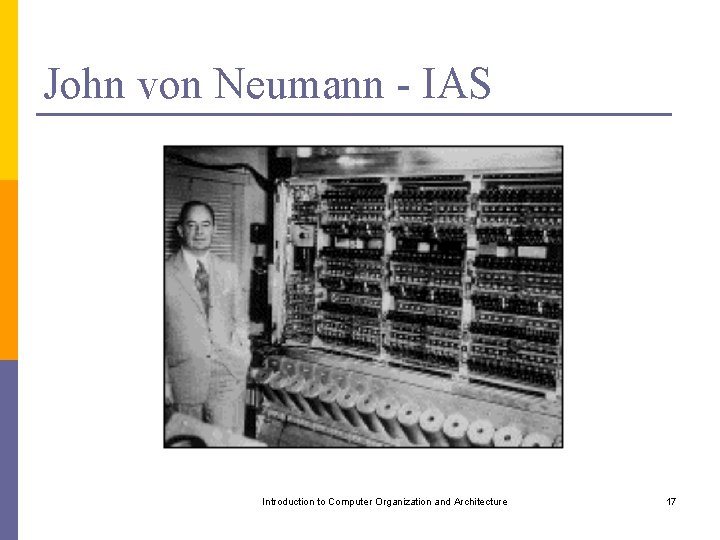

John von Neumann - IAS Introduction to Computer Organization and Architecture 17

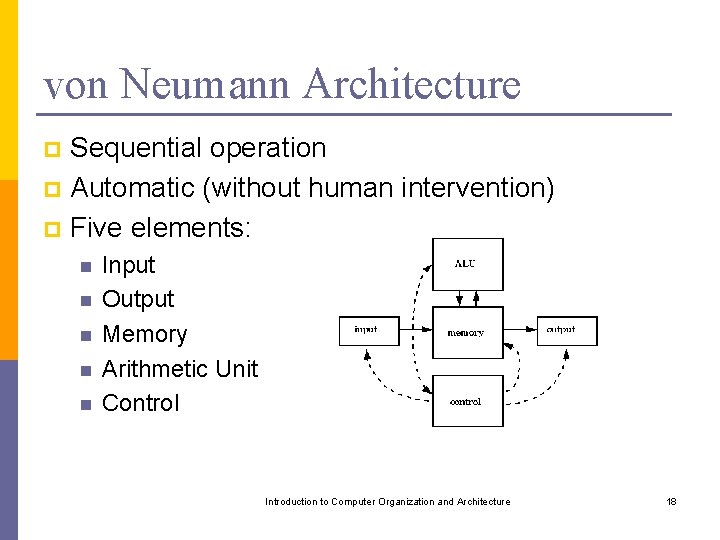

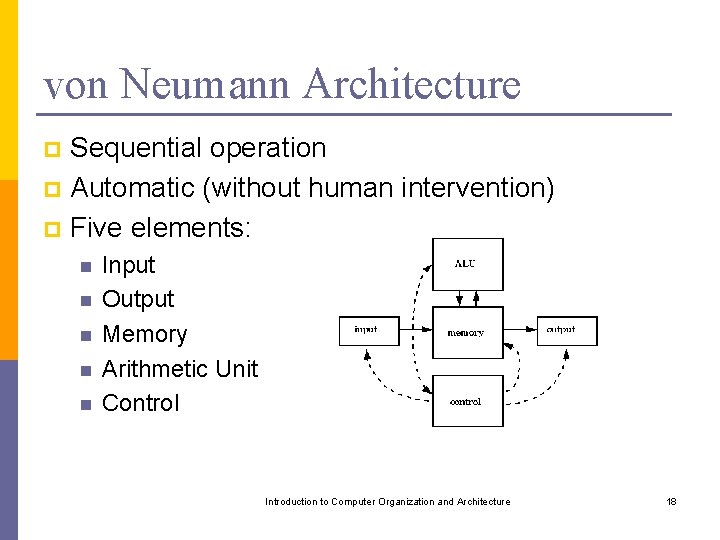

von Neumann Architecture Sequential operation p Automatic (without human intervention) p Five elements: p n n n Input Output Memory Arithmetic Unit Control Introduction to Computer Organization and Architecture 18

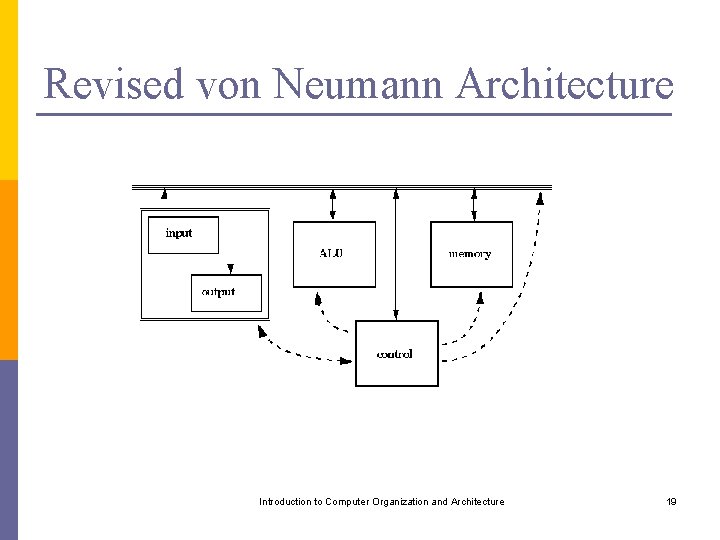

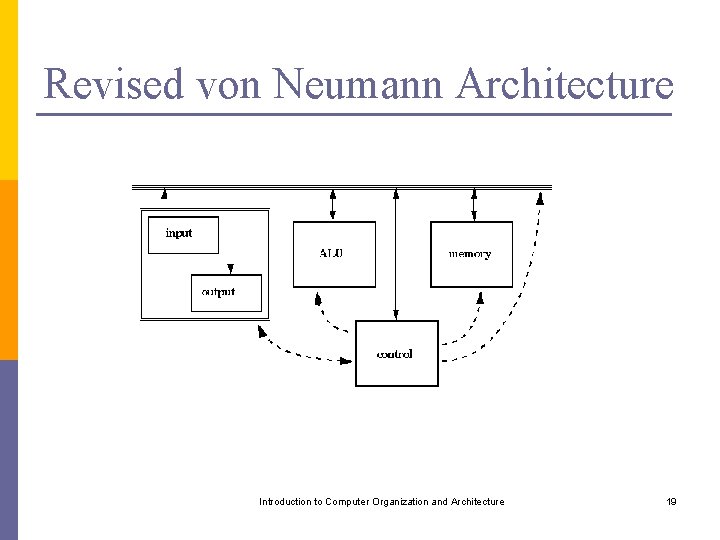

Revised von Neumann Architecture Introduction to Computer Organization and Architecture 19

The Stored Program Concept Programming the Harvard Mark I was by external paper tape p The ENIAC was “programmed” by rewiring it completely! p Introduction to Computer Organization and Architecture 20

The First Business Computer p LEO — Lyons Electronic Office — 1950 n p UNIVAC — Universal Automatic Computer — 1951 for the Census Bureau n p Modeled after the EDSAC Perhaps the first mass produced machine ERMA — Electronic Recording Means of Accounting — 1957 for Bank of America Introduction to Computer Organization and Architecture 21

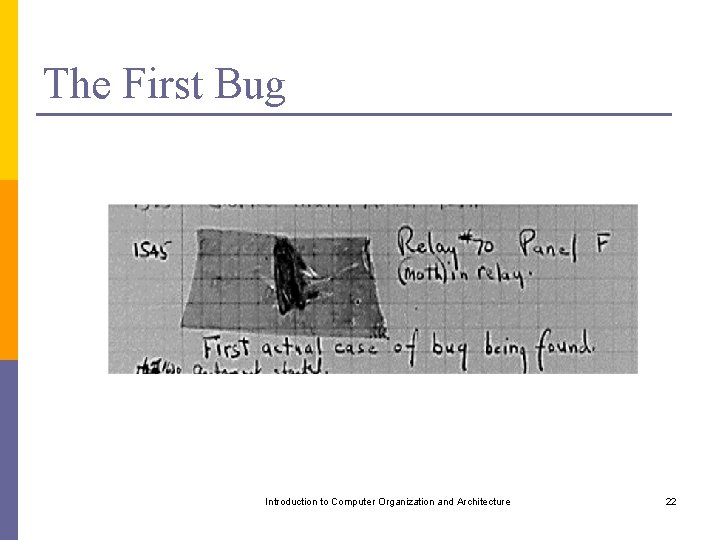

The First Bug Introduction to Computer Organization and Architecture 22

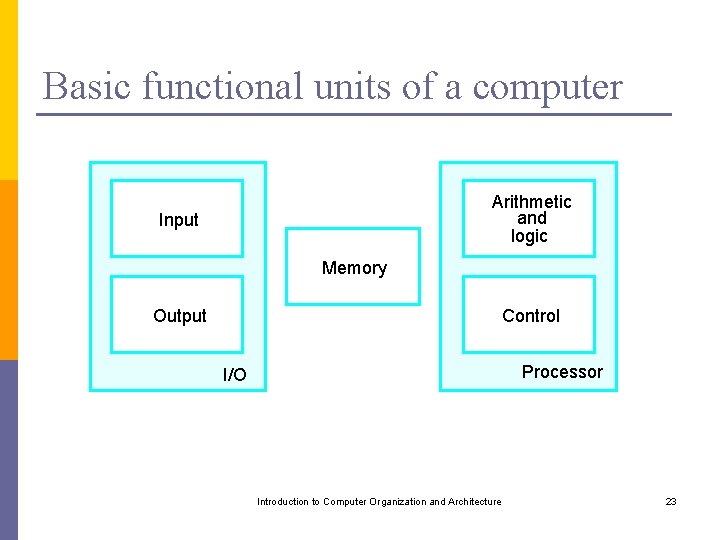

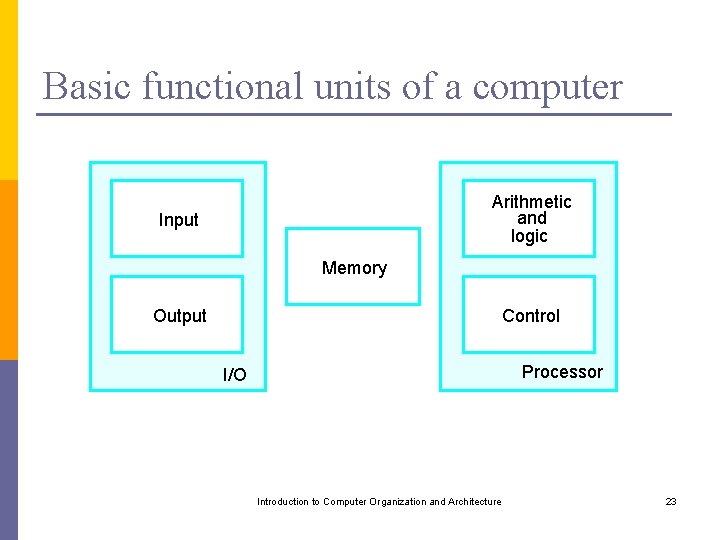

Basic functional units of a computer Arithmetic and logic Input Memory Output Control Processor I/O Introduction to Computer Organization and Architecture 23

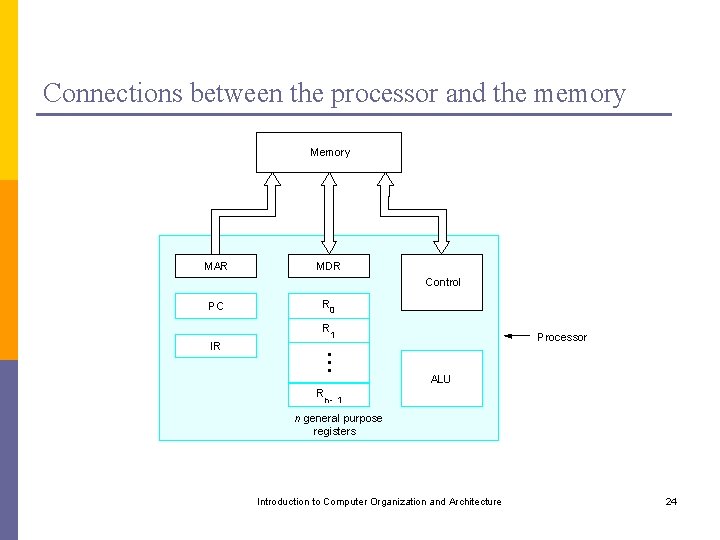

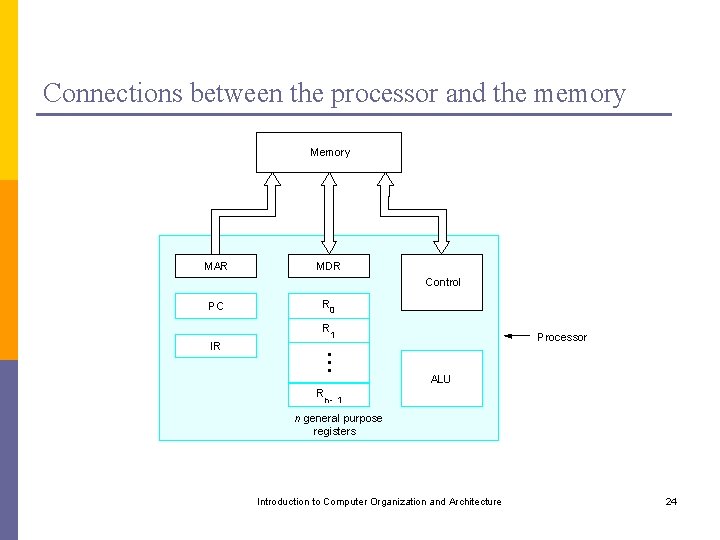

Connections between the processor and the memory MAR MDR Control PC R 0 R 1 Processor IR ALU R n- 1 n general purpose registers Introduction to Computer Organization and Architecture 24

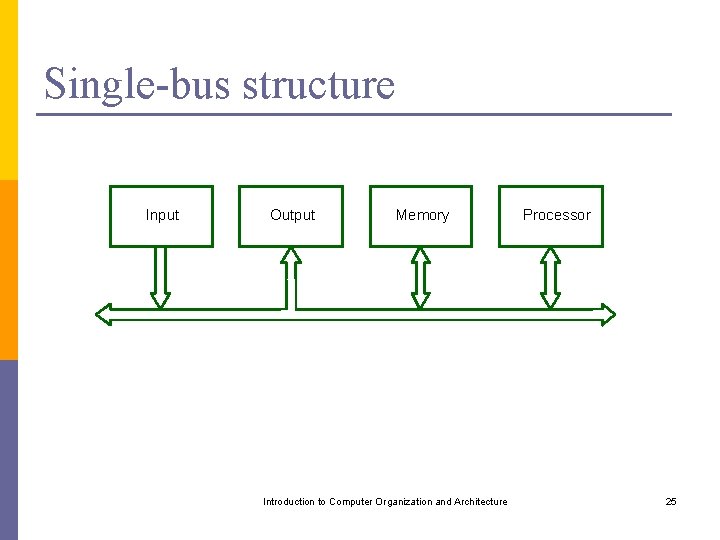

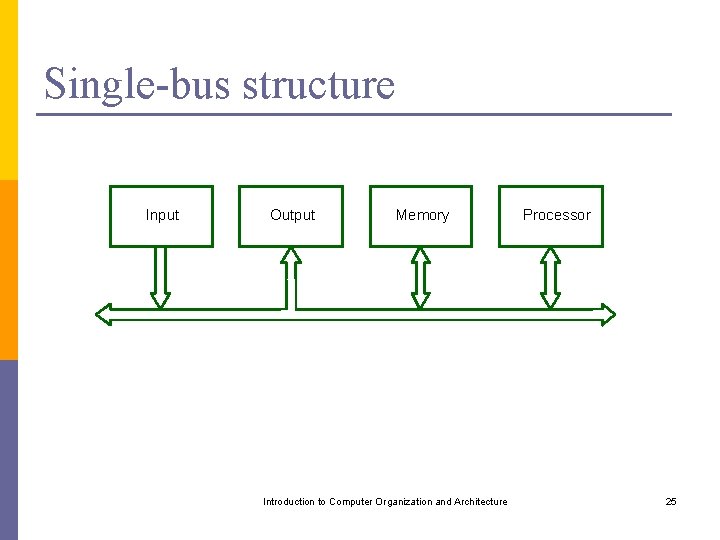

Single-bus structure Input Output Memory Introduction to Computer Organization and Architecture Processor 25

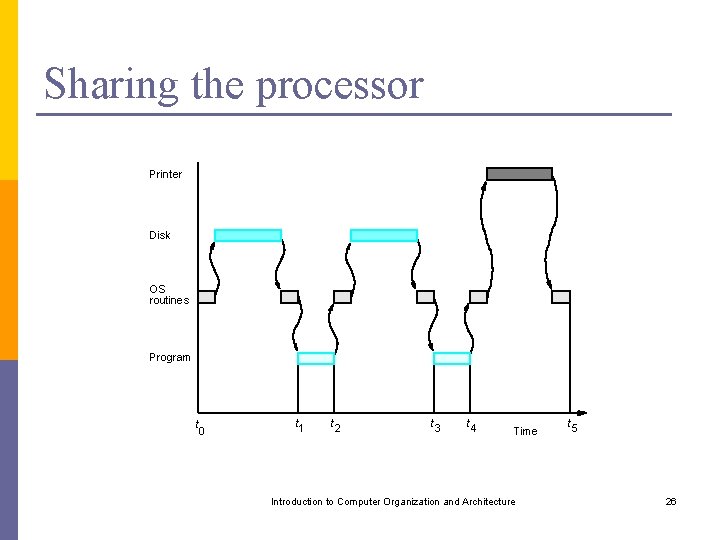

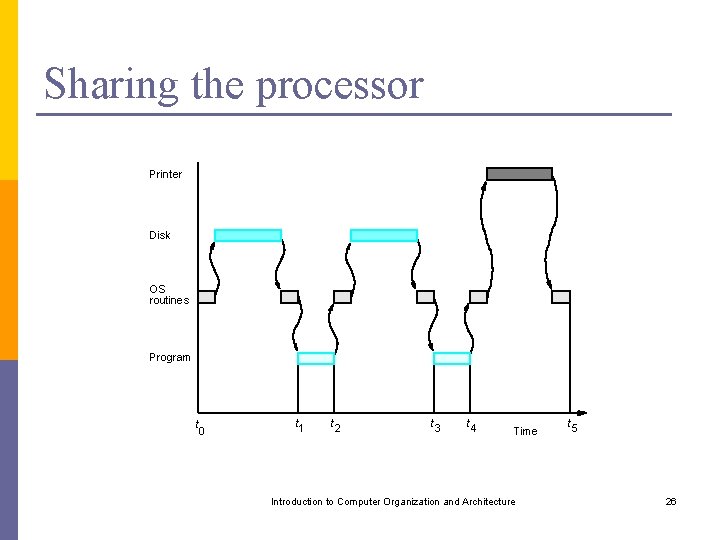

Sharing the processor Printer Disk OS routines Program t 0 t 1 t 2 t 3 t 4 Time Introduction to Computer Organization and Architecture t 5 26

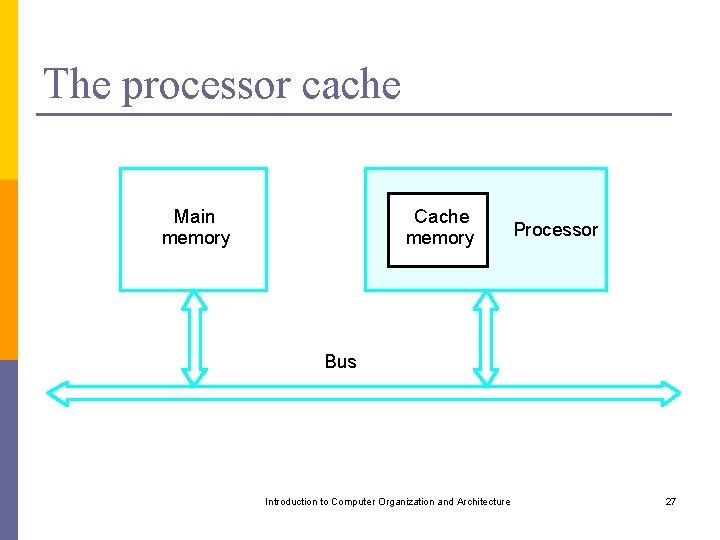

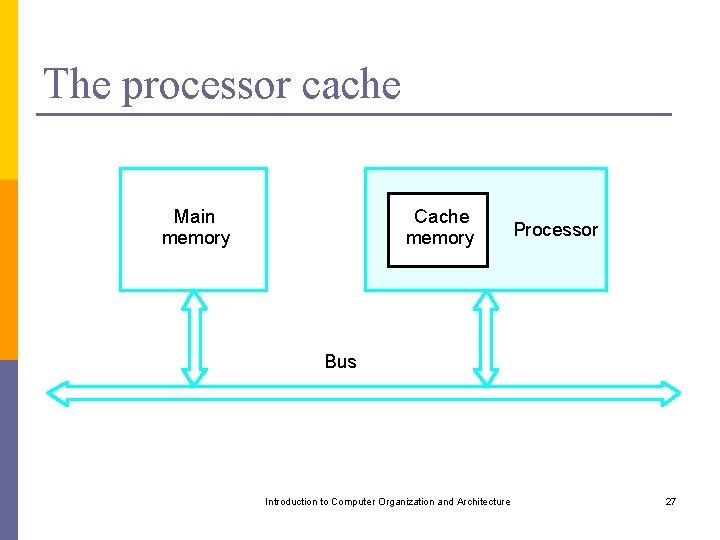

The processor cache Main memory Cache memory Processor Bus Introduction to Computer Organization and Architecture 27

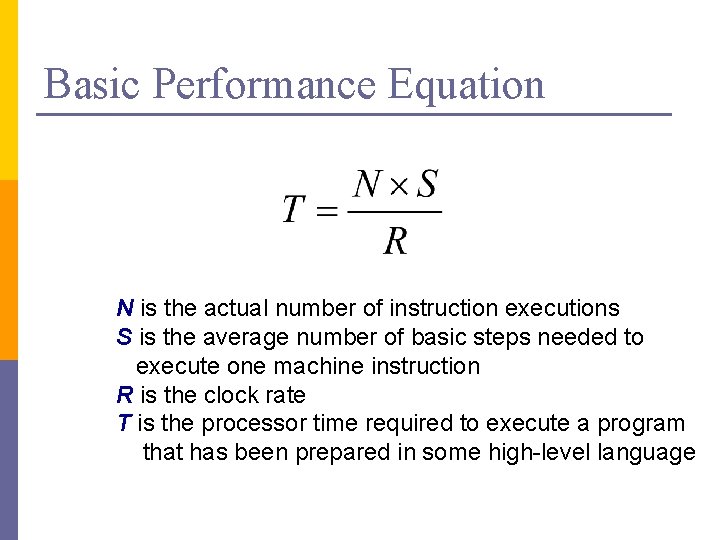

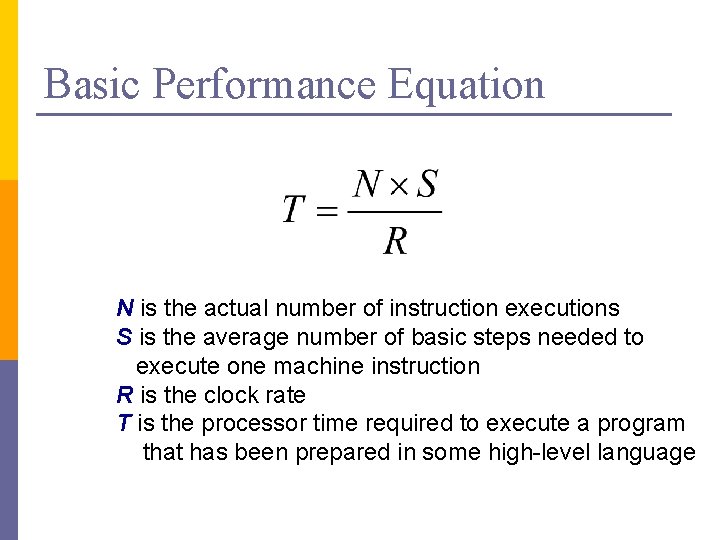

Basic Performance Equation N is the actual number of instruction executions S is the average number of basic steps needed to execute one machine instruction R is the clock rate T is the processor time required to execute a program that has been prepared in some high-level language

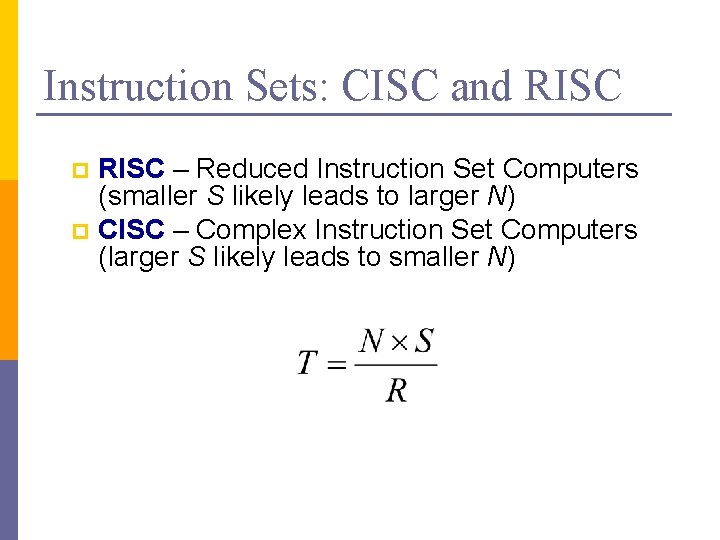

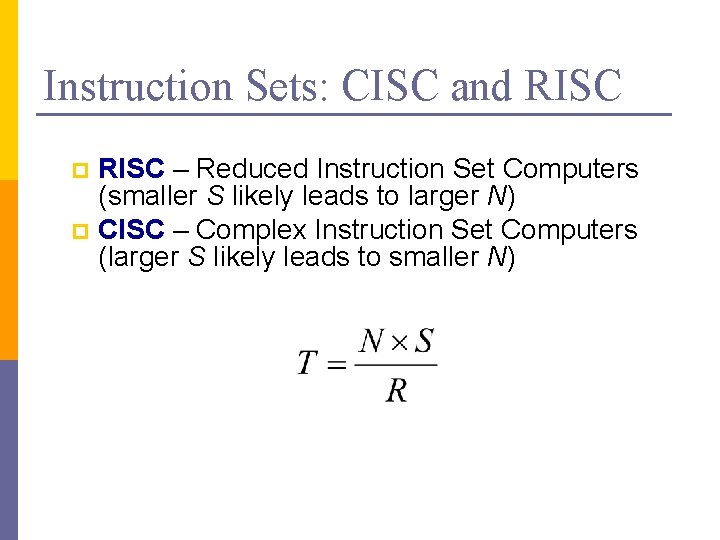

Instruction Sets: CISC and RISC – Reduced Instruction Set Computers (smaller S likely leads to larger N) p CISC – Complex Instruction Set Computers (larger S likely leads to smaller N) p

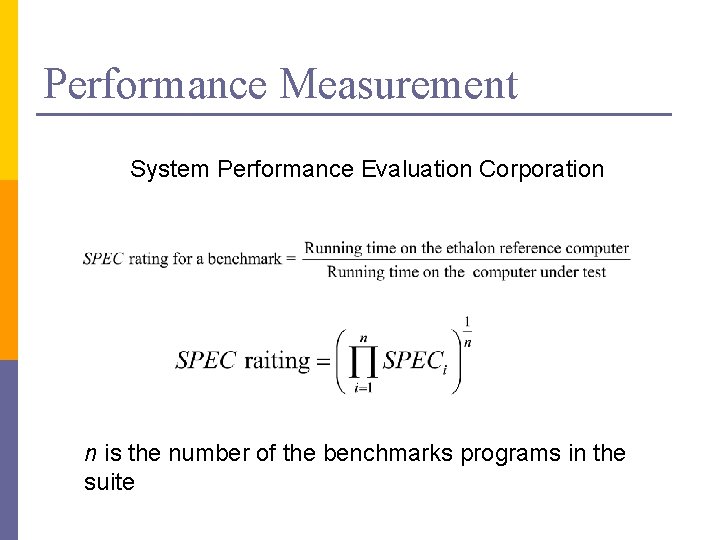

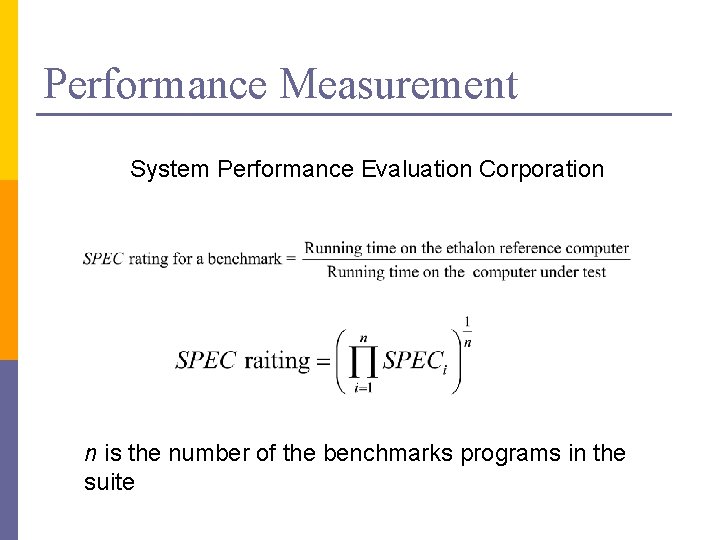

Performance Measurement System Performance Evaluation Corporation n is the number of the benchmarks programs in the suite

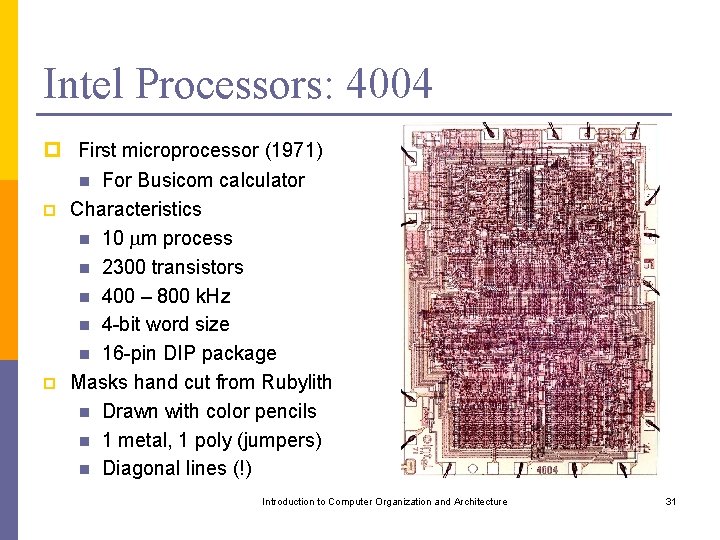

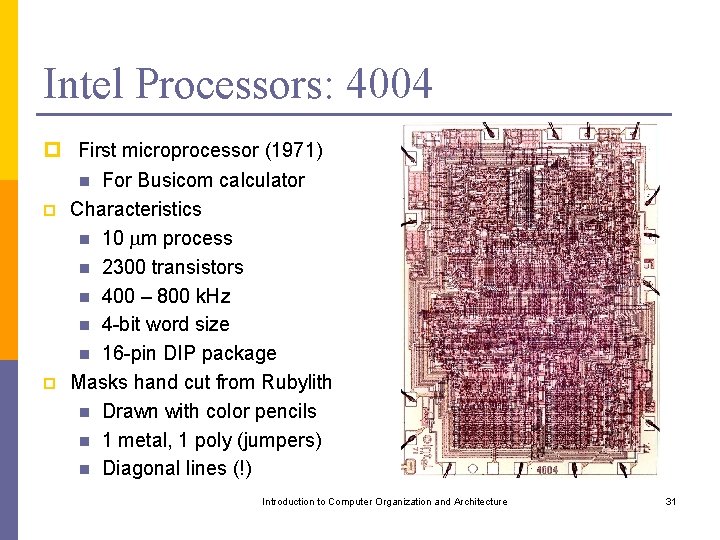

Intel Processors: 4004 p First microprocessor (1971) For Busicom calculator Characteristics n 10 mm process n 2300 transistors n 400 – 800 k. Hz n 4 -bit word size n 16 -pin DIP package Masks hand cut from Rubylith n Drawn with color pencils n 1 metal, 1 poly (jumpers) n Diagonal lines (!) n p p Introduction to Computer Organization and Architecture 31

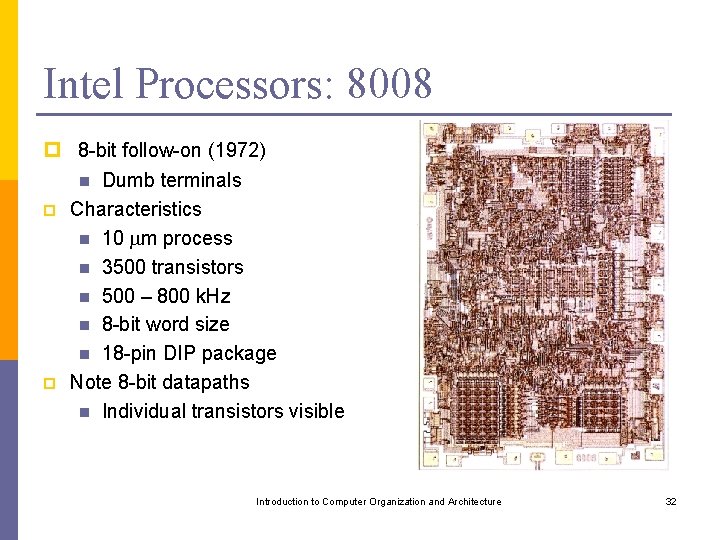

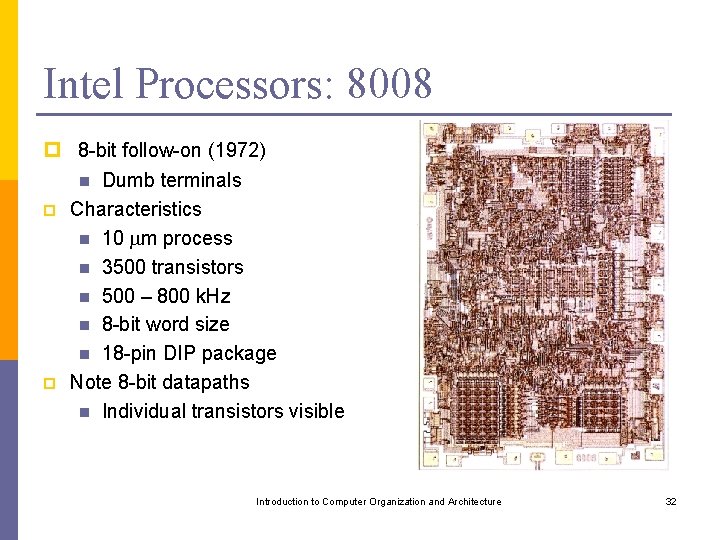

Intel Processors: 8008 p 8 -bit follow-on (1972) Dumb terminals Characteristics n 10 mm process n 3500 transistors n 500 – 800 k. Hz n 8 -bit word size n 18 -pin DIP package Note 8 -bit datapaths n Individual transistors visible n p p Introduction to Computer Organization and Architecture 32

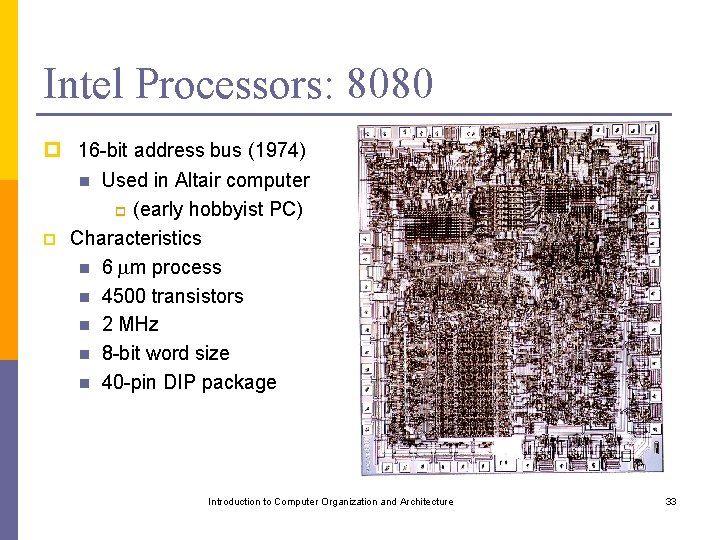

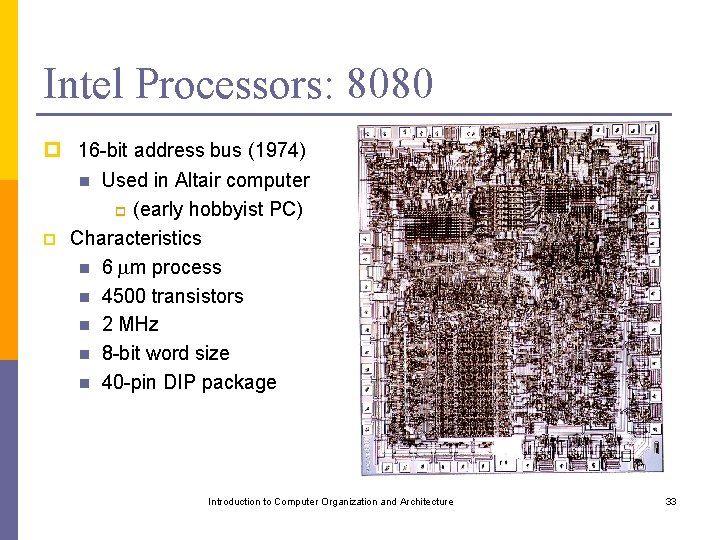

Intel Processors: 8080 p 16 -bit address bus (1974) Used in Altair computer p (early hobbyist PC) Characteristics n 6 mm process n 4500 transistors n 2 MHz n 8 -bit word size n 40 -pin DIP package n p Introduction to Computer Organization and Architecture 33

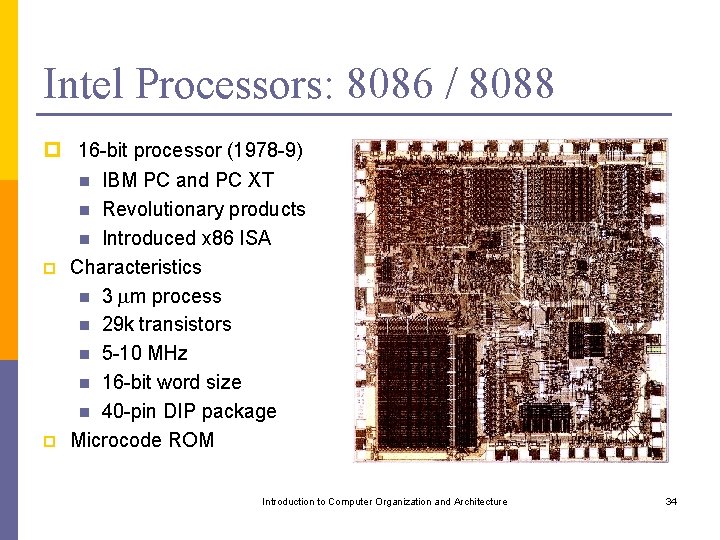

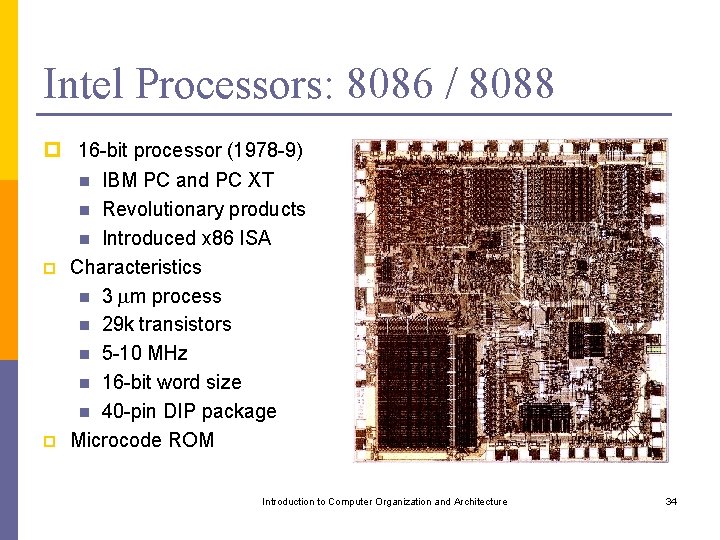

Intel Processors: 8086 / 8088 p 16 -bit processor (1978 -9) IBM PC and PC XT n Revolutionary products n Introduced x 86 ISA Characteristics n 3 mm process n 29 k transistors n 5 -10 MHz n 16 -bit word size n 40 -pin DIP package Microcode ROM n p p Introduction to Computer Organization and Architecture 34

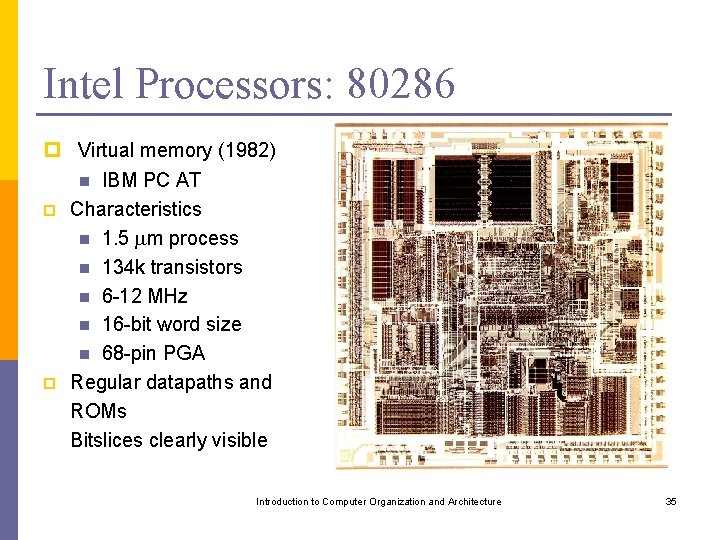

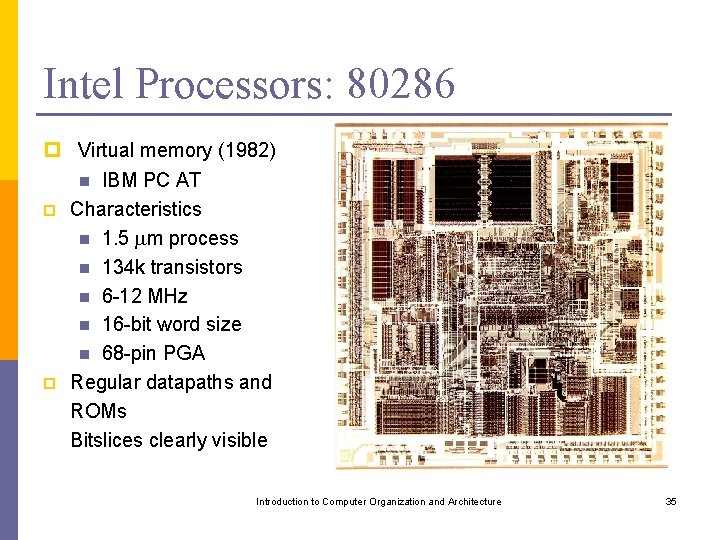

Intel Processors: 80286 p Virtual memory (1982) IBM PC AT Characteristics n 1. 5 mm process n 134 k transistors n 6 -12 MHz n 16 -bit word size n 68 -pin PGA Regular datapaths and ROMs Bitslices clearly visible n p p Introduction to Computer Organization and Architecture 35

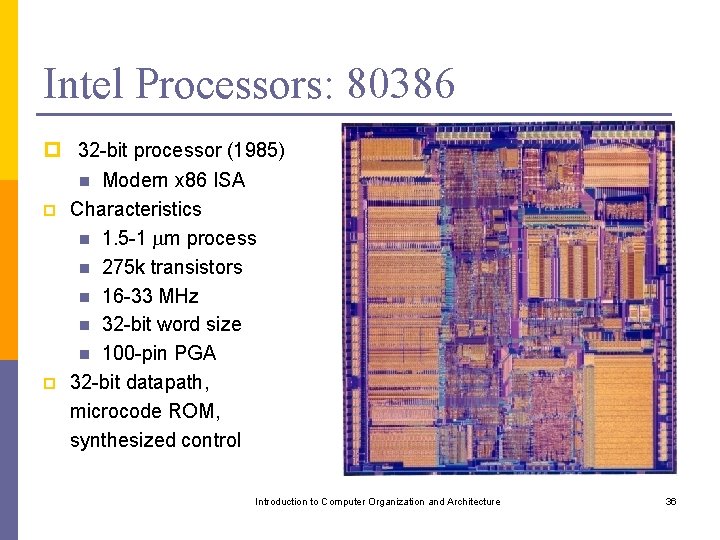

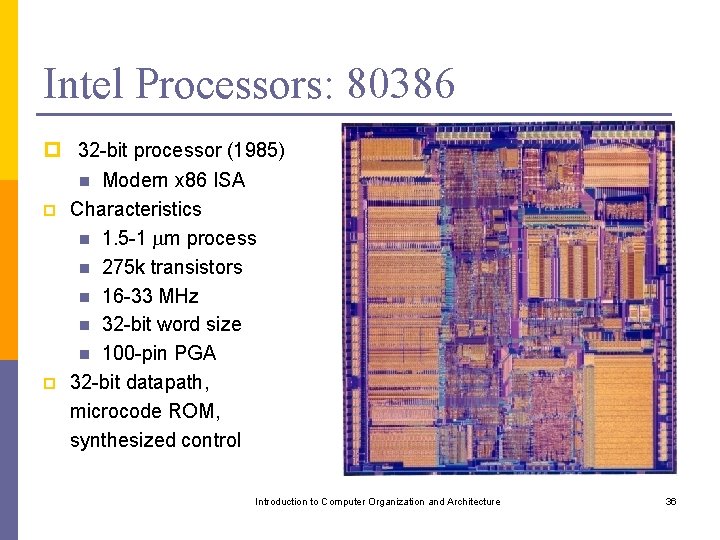

Intel Processors: 80386 p 32 -bit processor (1985) Modern x 86 ISA Characteristics n 1. 5 -1 mm process n 275 k transistors n 16 -33 MHz n 32 -bit word size n 100 -pin PGA 32 -bit datapath, microcode ROM, synthesized control n p p Introduction to Computer Organization and Architecture 36

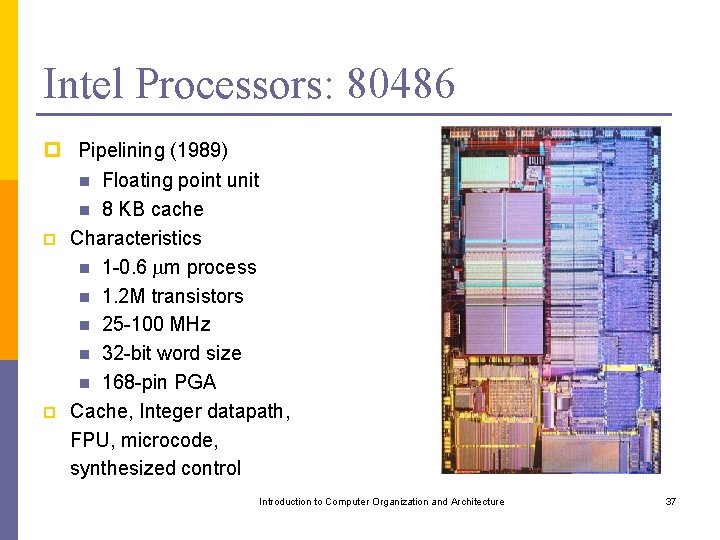

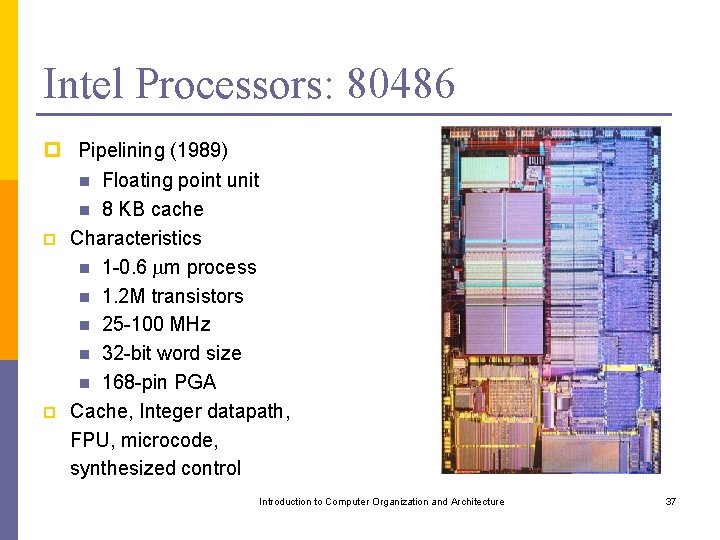

Intel Processors: 80486 p Pipelining (1989) Floating point unit n 8 KB cache Characteristics n 1 -0. 6 mm process n 1. 2 M transistors n 25 -100 MHz n 32 -bit word size n 168 -pin PGA Cache, Integer datapath, FPU, microcode, synthesized control n p p Introduction to Computer Organization and Architecture 37

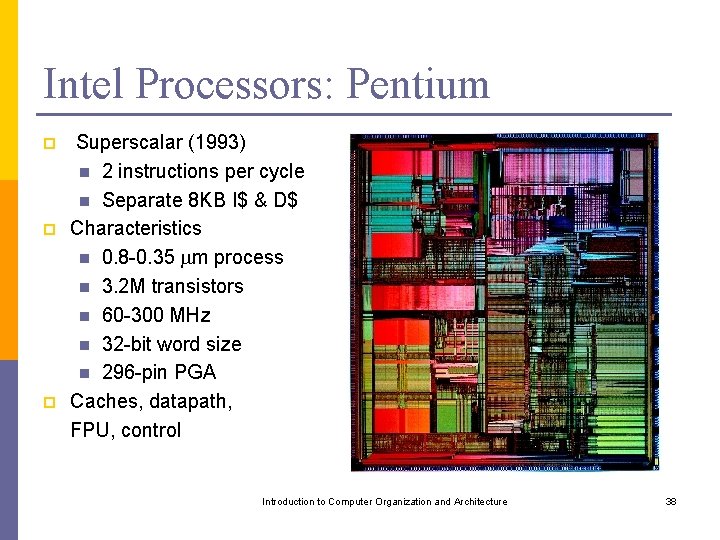

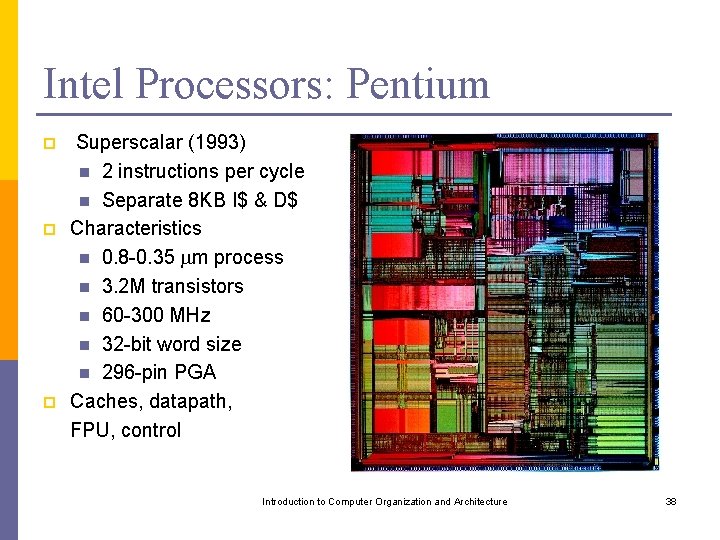

Intel Processors: Pentium p p p Superscalar (1993) n 2 instructions per cycle n Separate 8 KB I$ & D$ Characteristics n 0. 8 -0. 35 mm process n 3. 2 M transistors n 60 -300 MHz n 32 -bit word size n 296 -pin PGA Caches, datapath, FPU, control Introduction to Computer Organization and Architecture 38

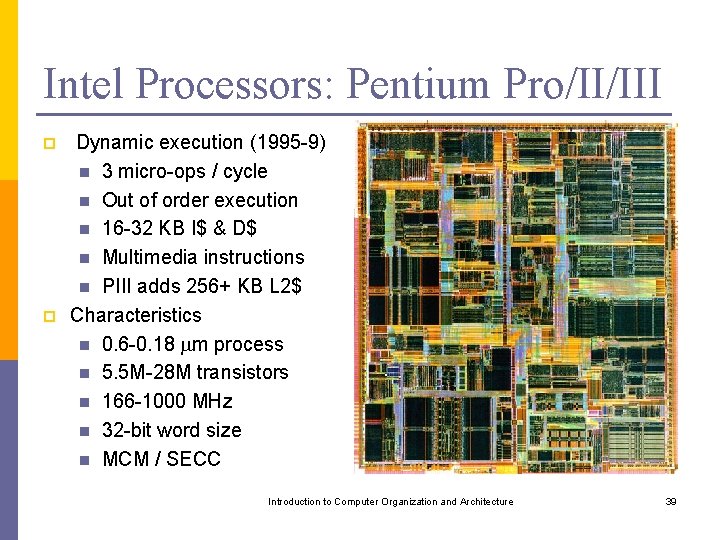

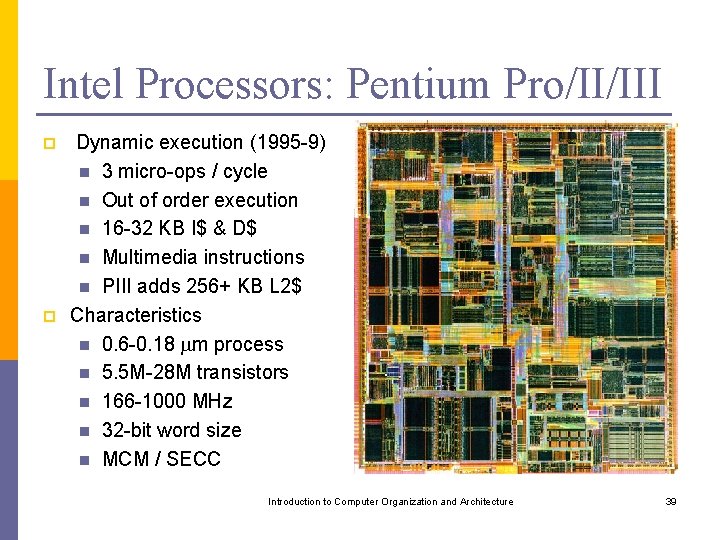

Intel Processors: Pentium Pro/II/III p p Dynamic execution (1995 -9) n 3 micro-ops / cycle n Out of order execution n 16 -32 KB I$ & D$ n Multimedia instructions n PIII adds 256+ KB L 2$ Characteristics n 0. 6 -0. 18 mm process n 5. 5 M-28 M transistors n 166 -1000 MHz n 32 -bit word size n MCM / SECC Introduction to Computer Organization and Architecture 39

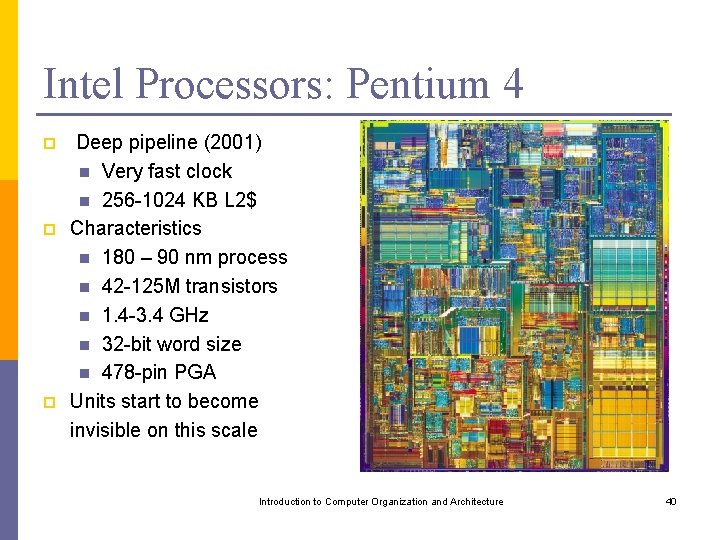

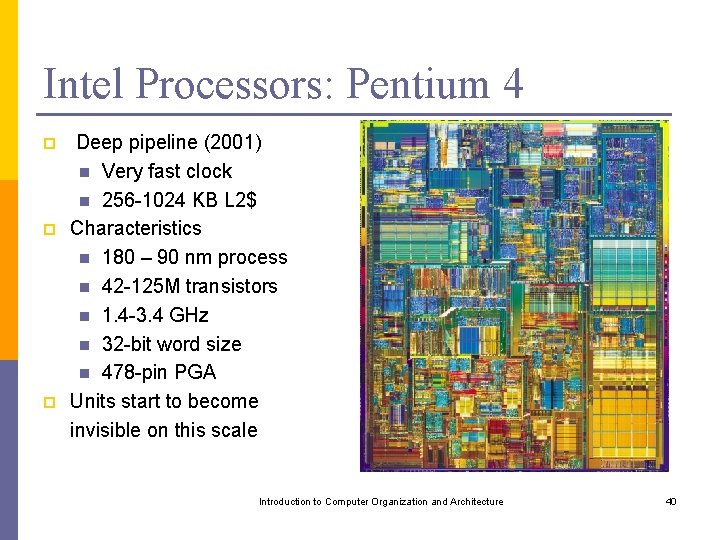

Intel Processors: Pentium 4 p p p Deep pipeline (2001) n Very fast clock n 256 -1024 KB L 2$ Characteristics n 180 – 90 nm process n 42 -125 M transistors n 1. 4 -3. 4 GHz n 32 -bit word size n 478 -pin PGA Units start to become invisible on this scale Introduction to Computer Organization and Architecture 40

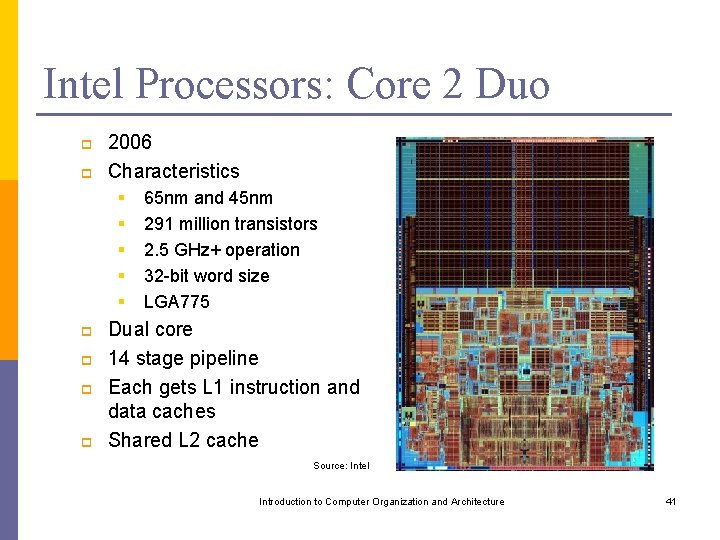

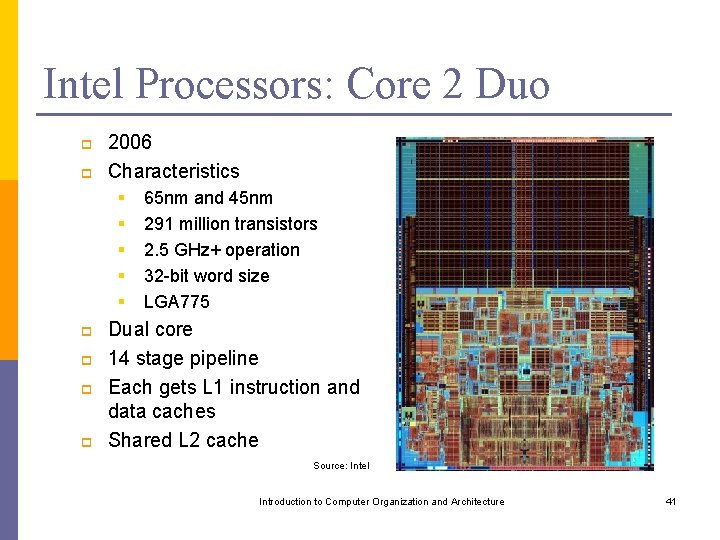

Intel Processors: Core 2 Duo p p 2006 Characteristics § § § p p 65 nm and 45 nm 291 million transistors 2. 5 GHz+ operation 32 -bit word size LGA 775 Dual core 14 stage pipeline Each gets L 1 instruction and data caches Shared L 2 cache Source: Intel Introduction to Computer Organization and Architecture 41

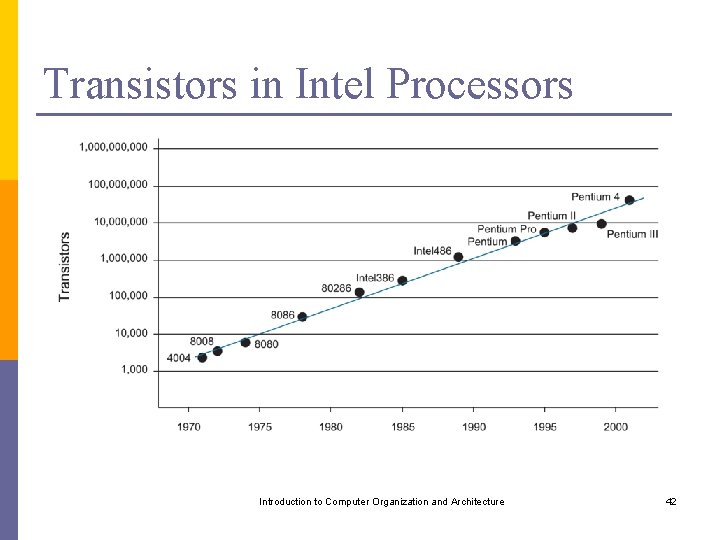

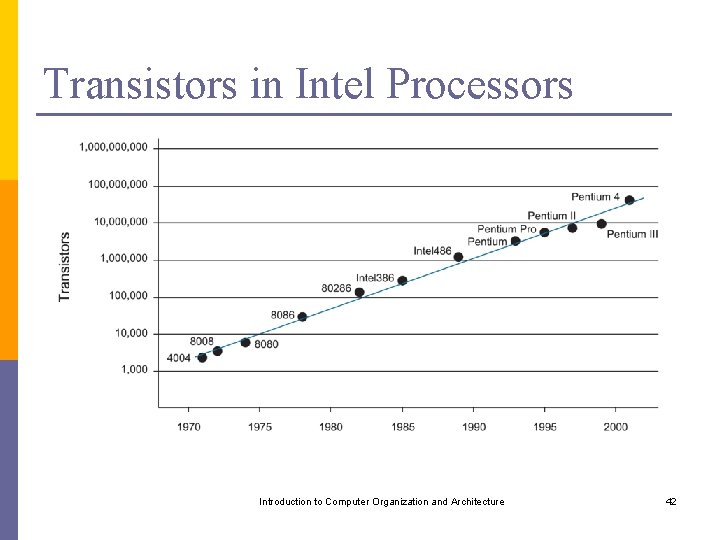

Transistors in Intel Processors Introduction to Computer Organization and Architecture 42

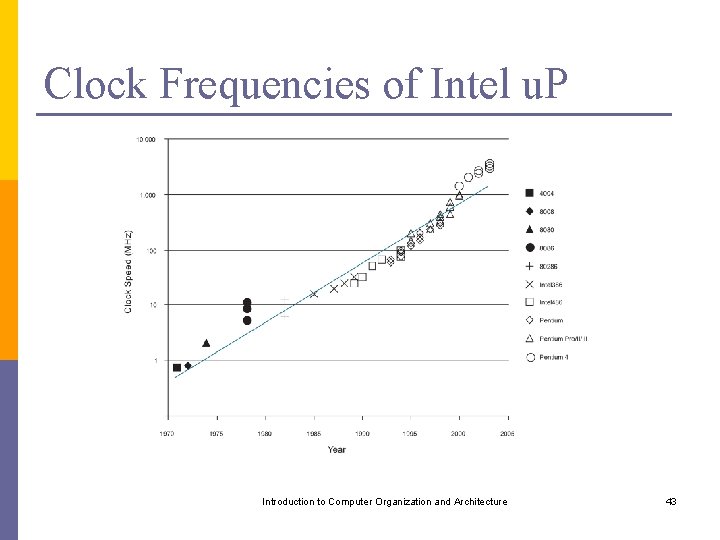

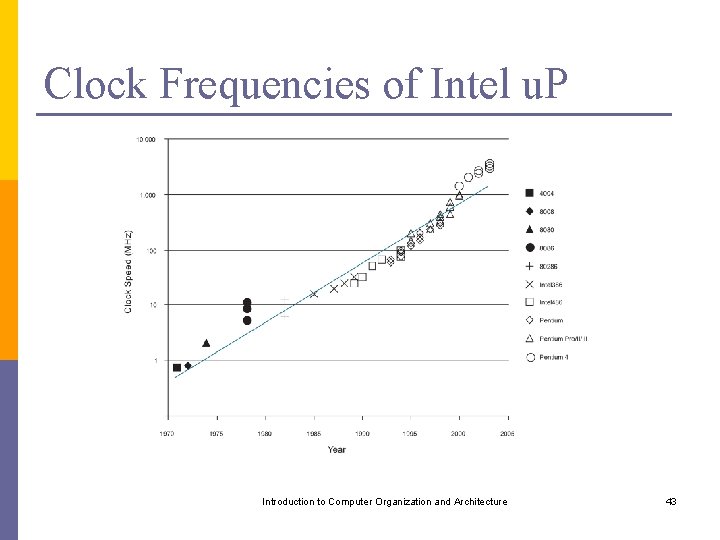

Clock Frequencies of Intel u. P Introduction to Computer Organization and Architecture 43

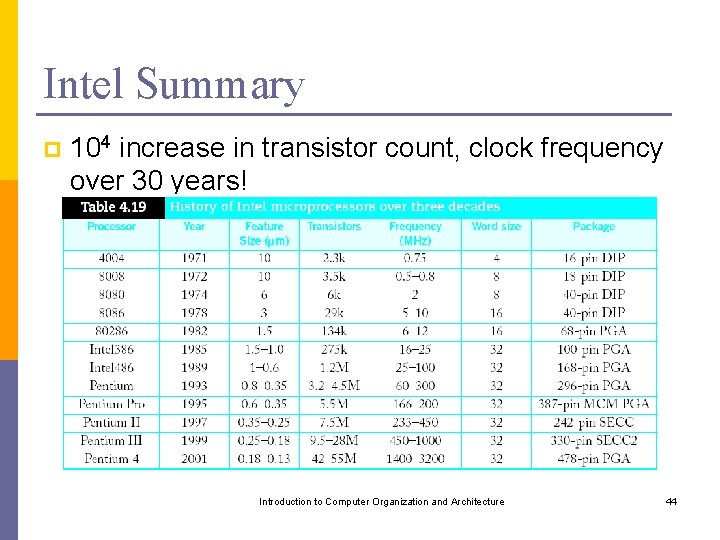

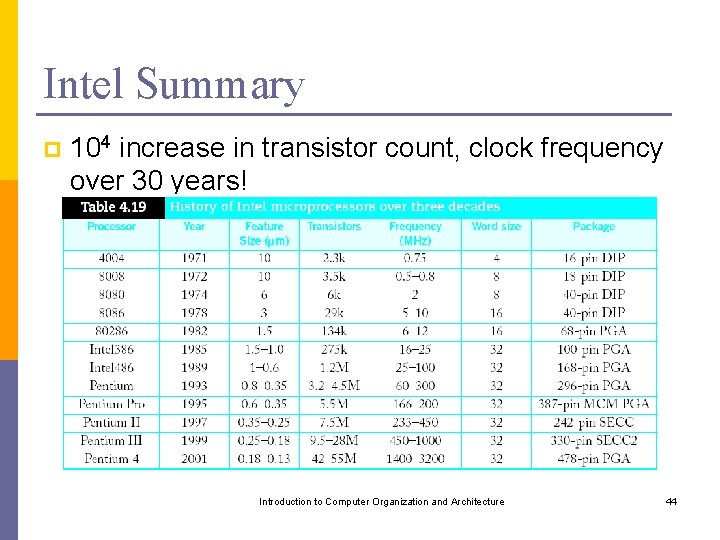

Intel Summary p 104 increase in transistor count, clock frequency over 30 years! Introduction to Computer Organization and Architecture 44

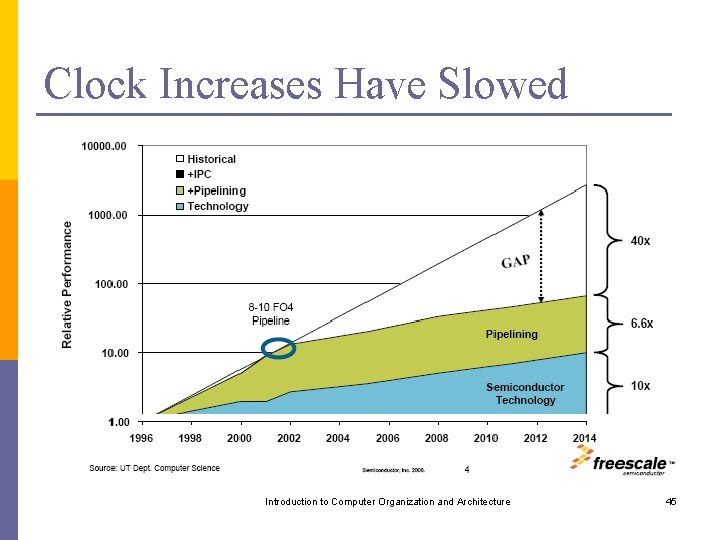

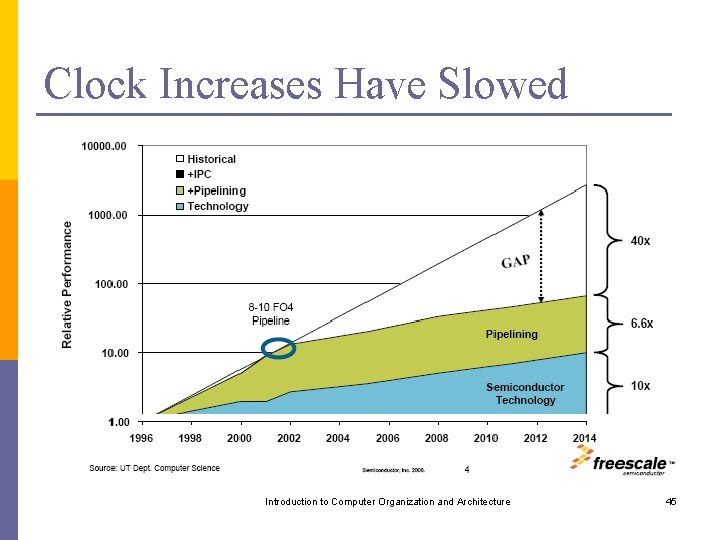

Clock Increases Have Slowed Introduction to Computer Organization and Architecture 45

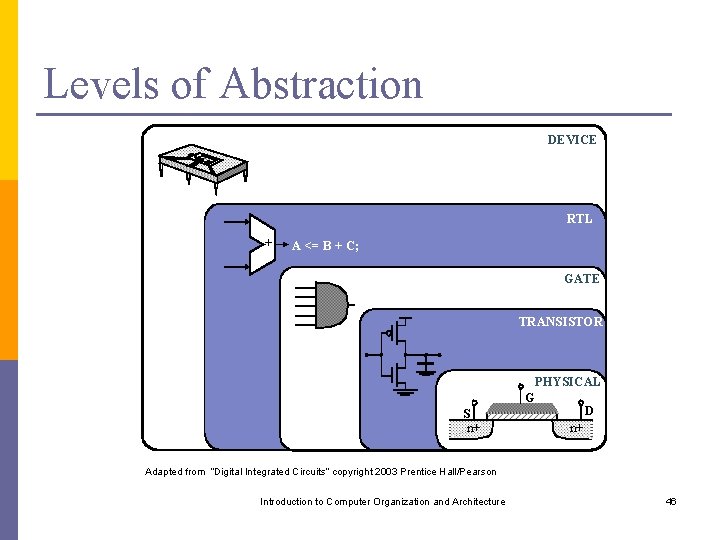

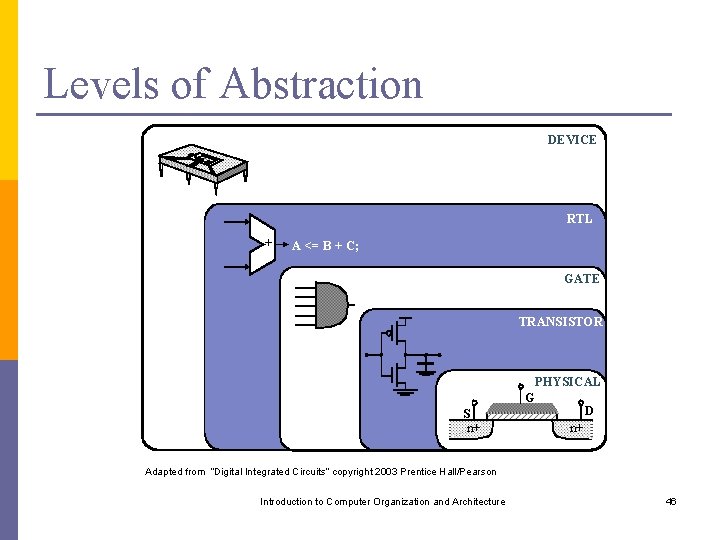

Levels of Abstraction DEVICE RTL + A <= B + C; GATE TRANSISTOR S n+ PHYSICAL G D n+ Adapted from “Digital Integrated Circuits” copyright 2003 Prentice Hall/Pearson Introduction to Computer Organization and Architecture 46

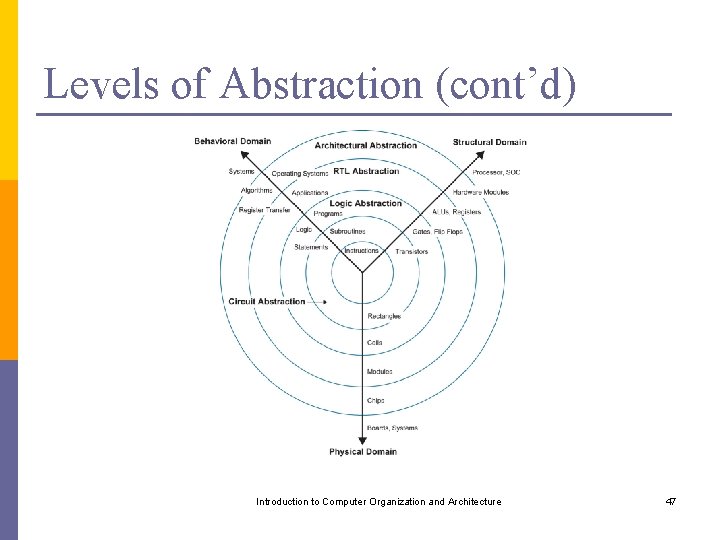

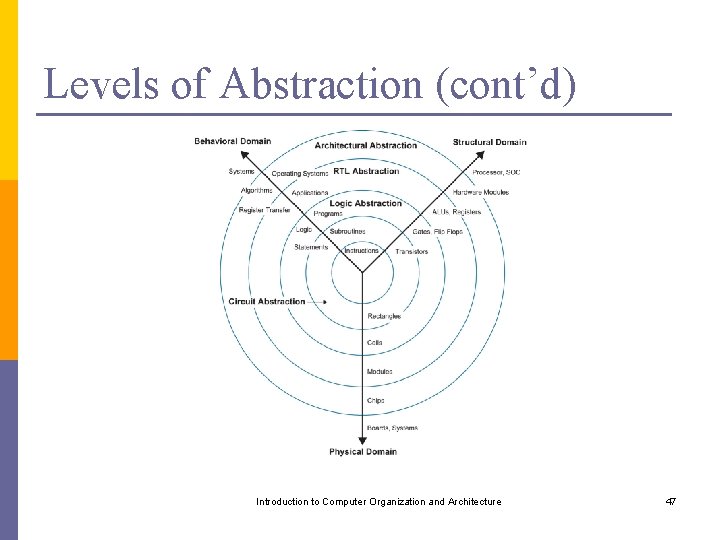

Levels of Abstraction (cont’d) Introduction to Computer Organization and Architecture 47

The End Lecture 1