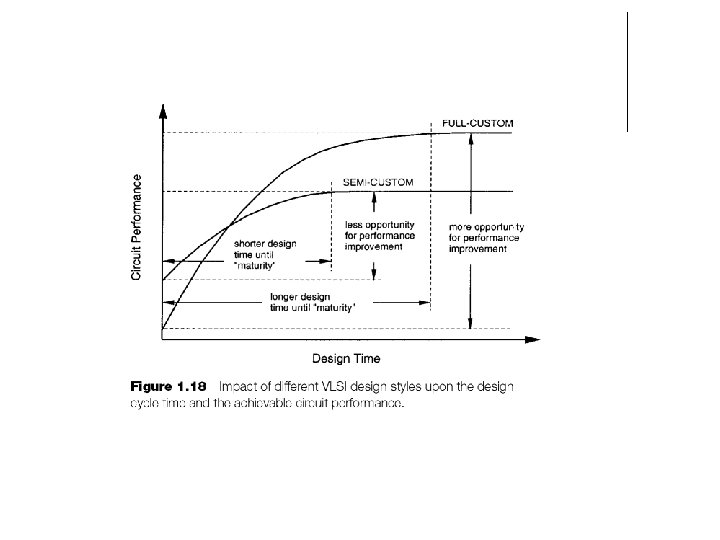

Design Methodology Semi Custom ASIC FPGA VLSI Design

- Slides: 31

Design Methodology Semi Custom ASIC FPGA

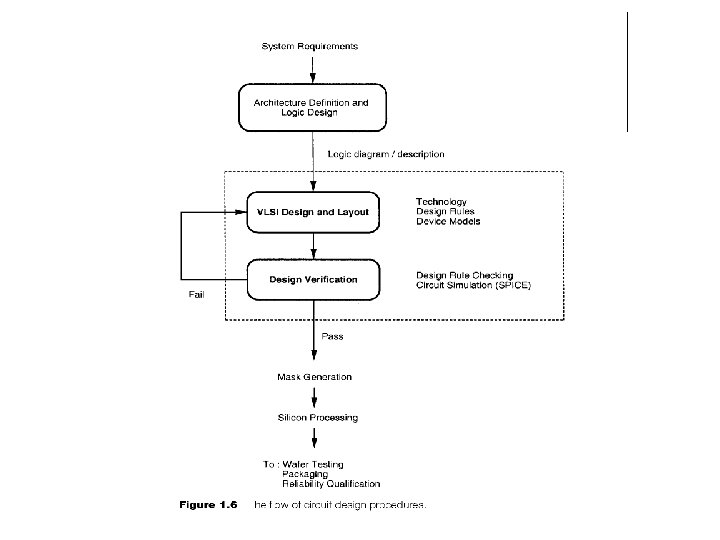

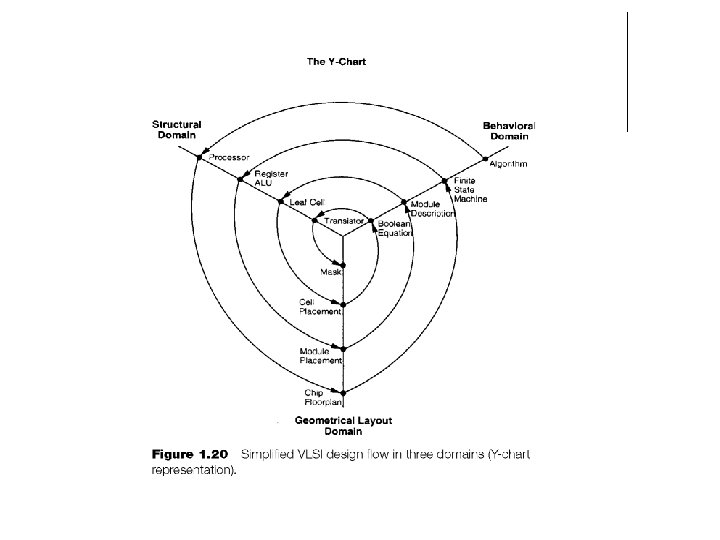

VLSI Design Methodology Relationship between a silicon foundry, an IC design team and a CAD tool provider

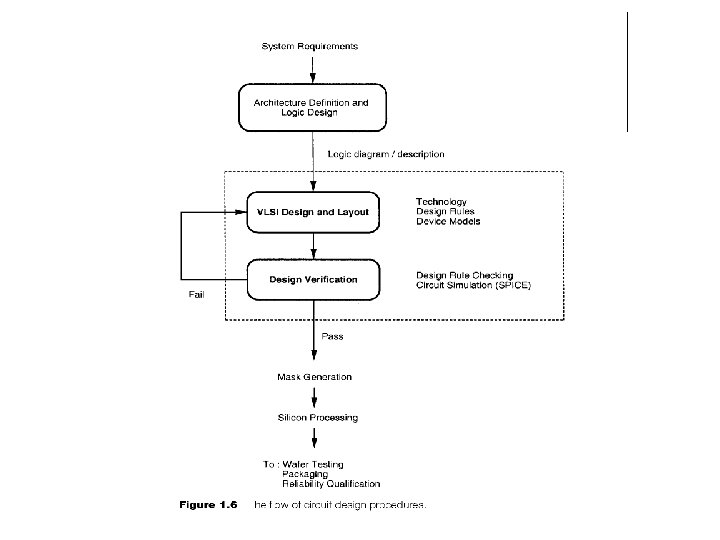

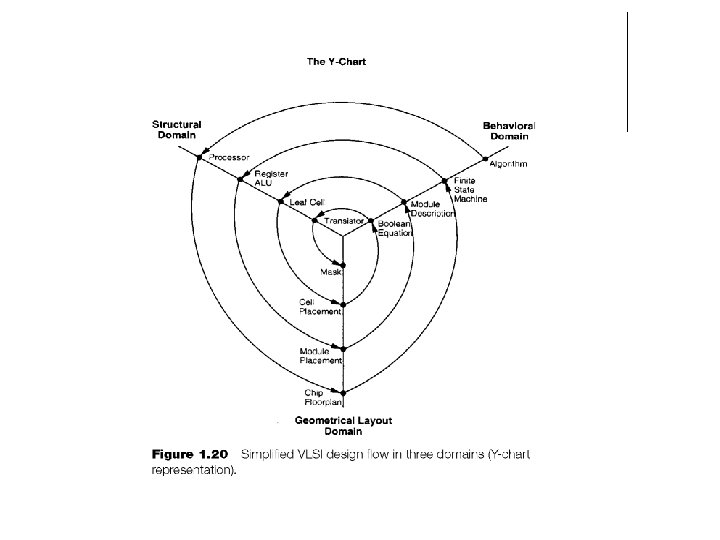

Top Down (algorithm) Bottom Up (physical)

Application Specific Integrated Circuits (ASICs) ASSPs : Application Specific Standard Products

ASIC Design Methodologies

ASIC-Benefit • Improve performance • Reduce power consumption • Mix Analog and Digital Designs • Design optimization through IC manufacturing process • Development Tools support HDL and Schematic design approach

ASIC-Drawbacks • Inflexible design • Deployed systems can not be upgraded • Mistakes in product development are costly • Updates requires a redesign • Complex and expensive development tools

Session Outline (FPGA) Technology/price breakthrough in FPGA devices Case Studies Why should Windows hardware developers care? Survey of new technologies/vendors Business comparison of FPGA with alternative solutions Advantages/requirements for FPGA development Pleora i. Port Pinnacle Studio Movie Box Deluxe Summary/Conclusions 11

Technology Breakthrough Impacts Windows-Compatible Hardware Market Field Programmable Gate Arrays (FPGAs) break through price/capability barriers 1 million gates drop from $200+ to <$20 90 nm will offer another >2 X improvement 32 bit RISC processors “for free” Embedded “soft” 32 -bit processors debut allowing complete Systemon-Chip designs Previously relegated to high-margin/low-volume applications 12

Why Should We Care? Cost-effective FPGAs Enable New Windows. Compatible Products Greater product differentiation Functionality and performance never available at this price point Shorter development cycles = faster time to market Improved product flexibility = longer market life Reduced part inventory More product variants 13

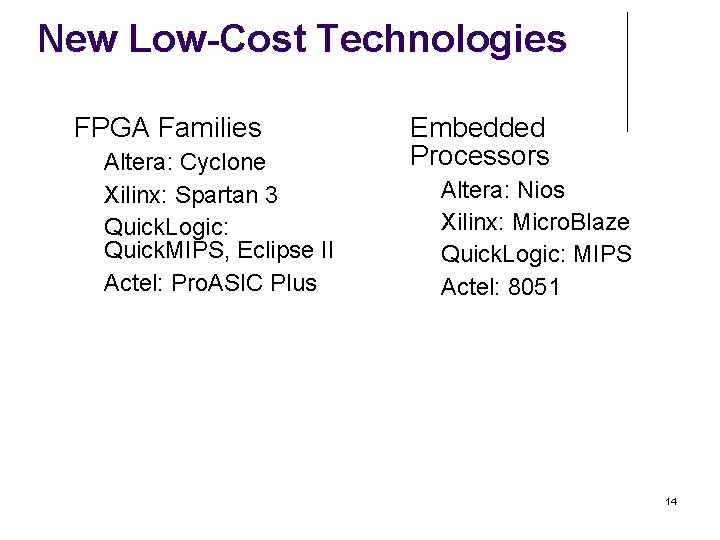

New Low-Cost Technologies FPGA Families Altera: Cyclone Xilinx: Spartan 3 Quick. Logic: Quick. MIPS, Eclipse II Actel: Pro. ASIC Plus Embedded Processors Altera: Nios Xilinx: Micro. Blaze Quick. Logic: MIPS Actel: 8051 14

Three Choices For Windows. Compatible Hardware Development 1. Develop conservative products based on standard chipsets Little differentiation Minimal margin Straight to commodity Develop an ASIC 3. Use new FPGA technologies Let’s compare options 2 and 3… 2. 15

ASIC Versus FPGA Comparison Tooling cost Non-recurring engineering costs (NRE) Time to market Product risk Product flexibility Inventory simplification 16

ASIC Versus FPGA Tools ASIC Requirements Average seat of EDA tools $200 K/engineer HDL Simulation, Synthesis, Timing analysis, Test insertion, Place-and route, Formal verification, Floorplanning, DRC… Usually involves multiple EDA vendors FPGA Requirements Average seat $2 K-$3 K/yr Simulation, Synthesis, Place-and-route Adequate tools provided by FPGA vendors Value-added tools from EDA vendors ~$20 -30 K 17

Non-Recurring Engineering (NRE) ASIC Designs FPGA Designs NRE for ASIC Designs ~$500 K/run for. 13µ Each subsequent re-spin costs another NRE For new 90 nm technology NRE >$1 M High-risk methodology requiring massive volume to recoup costs No NRE charges Some cost-reduction available by ASIC conversion with minimal (<$100 K) NRE Cost of FPGA device is offset by NRE in all but the highest volume applications 18

Time To Market ASIC Designs Typical design cycle 12 -18 months, minimum 9 months Additional re-spins add 8 -10 weeks each FPGA Designs Typical design cycle 4 months Re-spins not an issue 19

Extremely Fast Time-To-Prototype Software-based prototype in days System assembly on FPGA in minutes with processor, memory, bus, interfaces, peripherals C/C++ based application (with RTOS if needed) running in minutes using actual hardware Iterative development/refinement flow Performance-critical routines easily migrated to “hardware” implementations Software development in parallel with working hardware Embedded “virtual instrumentation” offers in-circuit debugging Allows evolutionary design style 20

Benefits Of FPGA-Based Design Improved product flexibility Changes hardware/software up to (and even after) deployment Inventoried parts can be re-deployed in multiple applications More product variants on single platform Upgrade/enhance in the field Reduce inventory Single part for multiple variations and versions of product 21

What’s Needed For FPGA-Based Product Development? Complete toolsets provided by FPGA vendors Robust libraries of pre-tested IP components Processor cores (8, 16, 32 bit configurable) Peripherals (USB, PCI, I/O, DSP, ethernet, Memory…) Ready-to-use development prototyping boards for a variety of application types Development environments are PC/Windowsbased, no UNIX workstations required 22

Case Study: Pleora i. Port (~USD 500) High-speed video-over-ethernet peripheral with Altera Cyclone FPGA ~10 X price/performance improvement over frame-grabber solutions Gigabit ethernet versus expensive video cabling Multiple video sources to single PC, or many-to-many Longer reach 23

Case Study: Pleora i. Port FPGA-based frame grabber low-cost, high-speed processing standardized (Ethernet) interfaces Low cost-per-gate at high performance Flexible memory architecture for buffering Drop-in PCI core for interface with Intel Network I/F 24

FPGA Benefits To Pleora Reduced system cost Dramatically shorter design cycle Multiple product variants with single board Sub-$20 FPGA is 20% of product cost Inventory one part and deliver variations based on product mix Enabler – ASIC-based solution not an option at target volumes 25

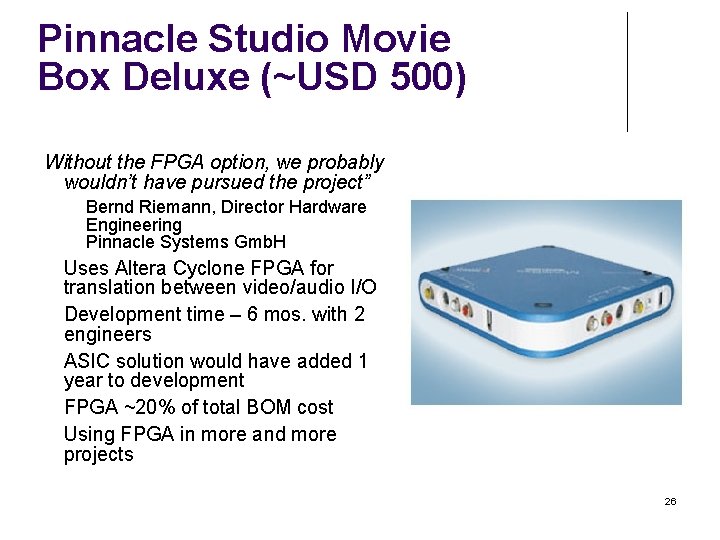

Pinnacle Studio Movie Box Deluxe (~USD 500) “Without the FPGA option, we probably wouldn’t have pursued the project” - Bernd Riemann, Director Hardware Engineering Pinnacle Systems Gmb. H Uses Altera Cyclone FPGA for translation between video/audio I/O Development time – 6 mos. with 2 engineers ASIC solution would have added 1 year to development FPGA ~20% of total BOM cost Using FPGA in more and more projects 26

Pinnacle Studio Movie Box Deluxe Remarkable leverage of FPGA reprogrammability 3 FPGAs in 1 Changes made right up to (and after) shipment Hardware design loaded at runtime from Windows drivers Device hardware reconfigures itself based on operating mode Embedded memory sufficient for buffering – no external I/O required Device shipped with no configuration on board User updates possible by downloading new drivers/patches Feature set could be modified with no hardware changes Separate versions possible for NTSC, PAL, etc. Follow-on improvements could be added in future versions Business immunity from hardware design errors (and marketing errors as well) 27

What Applications Benefit From FPGA? Windows-compatible applications that challenge performance barriers… High computational load: Digital Signal Processing (DSP) Video Digital TV Speech recognition High embedded software content Embedded soft-cores offer unprecedented capability 28

What Does The Future Hold? Tomorrow’s “Systems Designer” is today’s “Software Engineer” Example: Nallatech, Ltd. of Scotland Prototyped entire system in C on embedded Xilinx Micro. Blaze SW engineer ran project Performance-critical modules moved into hardware (FPGA fabric) New tools rolling out for C-based HW compilation Windows-compatible hardware becomes an extension of SW applications development 29

Summary FPGAs offer significant benefits to PC-based hardware development projects Reduced/more predictable development schedules Earlier prototypes Lower development cost More flexible, upgradeable products with longer market life Greater capability/performance at lower price point Reduced BOM, more flexible inventory Reduced product risk 30

Community Resources Community Sites List of Newsgroups http: //www. microsoft. com/communities/chats/default. mspx http: //www. microsoft. com/seminar/events/webcasts/default. mspx Locate a local user group(s) http: //communities 2. microsoft. com/communities/newsgroups/enus/default. aspx Attend a free chat or webcast http: //www. microsoft. com/communities/default. mspx http: //www. microsoft. com/communities/usergroups/default. mspx Non-Microsoft Community Sites http: //www. microsoft. com/communities/related/default. mspx 31