PCB DEVELOPMENTS AT IPNL PCB and ASIC PCB

PCB DEVELOPMENTS AT IPNL (PCB and ASIC) • PCB for 1 m 2 of RPC with HR 1 -HR 2 b William TROMEUR, Hervé MATHEZ, Yannick ZOCCARATO, Luigi CAPONETTO Imad LAKTINEH, Christophe COMBARET, Rodolphe DELLA-NEGRA, Didier BON (CNRS IN 2 P 3 IPNL) Collaboration with LAL CALICE electronics meeting LLR January 2010, Hervé MATHEZ 1

1 m 2 PCB MAIN SPECIFICATIONS (HR 1 -HR 2 b) ASU PCB Design • 24 x 64 1 sq cm pads • 24 Hardrocs Asics chained in plastic package (very thin 1. 2 mm) 1 m 2 PCB board : • 6 ASUs • 144 Hardroc Asics DIF boards : • 1 DIF for 2 ASU : 3 DIFs HR 2 : ü All modifications are implemented ü SC bypass ü SC Clocking and so on CALICE electronics meeting LLR January 2010, Hervé MATHEZ 2

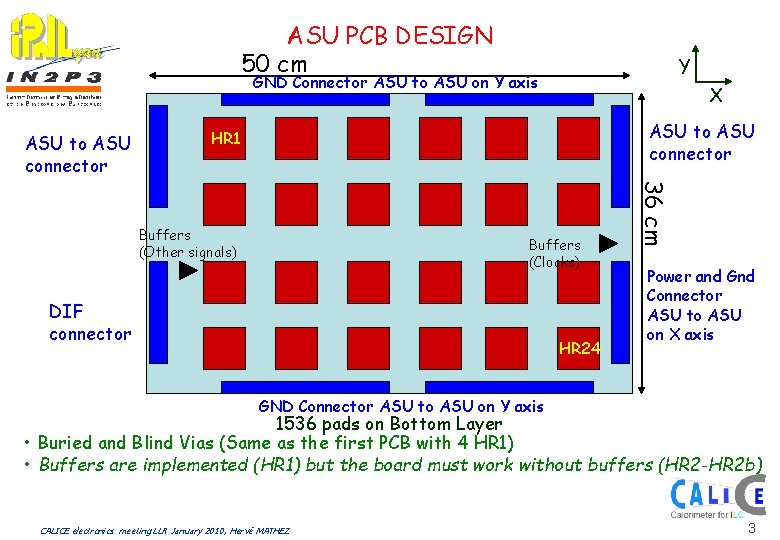

ASU PCB DESIGN 50 cm Y GND Connector ASU to ASU on Y axis ASU to ASU connector X ASU to ASU connector HR 1 Buffers (Clocks) DIF connector HR 24 36 cm Buffers (Other signals) Power and Gnd Connector ASU to ASU on X axis GND Connector ASU to ASU on Y axis 1536 pads on Bottom Layer • Buried and Blind Vias (Same as the first PCB with 4 HR 1) • Buffers are implemented (HR 1) but the board must work without buffers (HR 2 -HR 2 b) CALICE electronics meeting LLR January 2010, Hervé MATHEZ 3

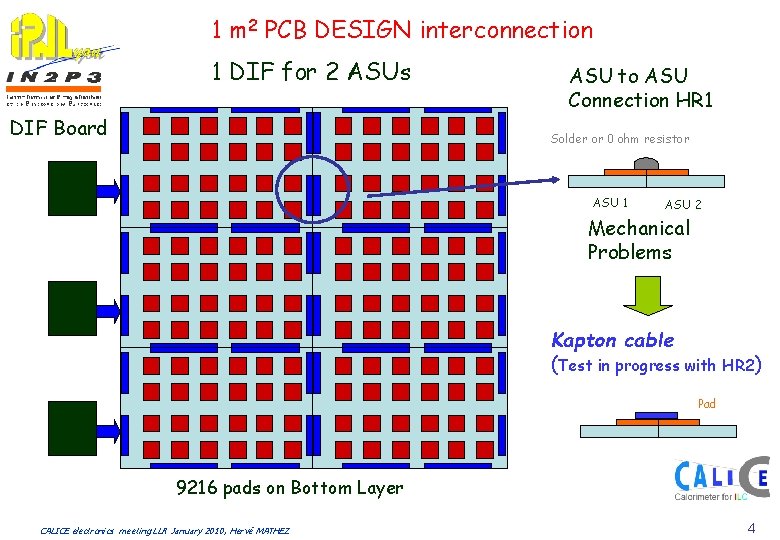

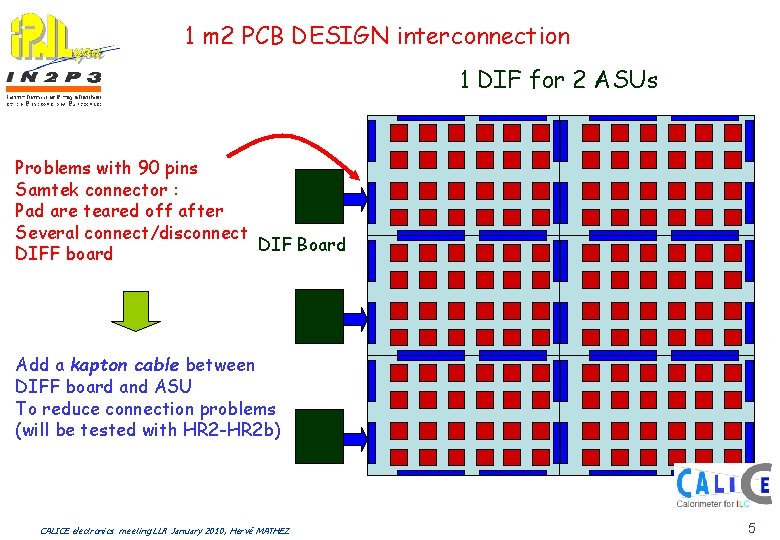

1 m 2 PCB DESIGN interconnection 1 DIF for 2 ASUs DIF Board ASU to ASU Connection HR 1 Solder or 0 ohm resistor ASU 1 ASU 2 Mechanical Problems Kapton cable (Test in progress with HR 2) Pad 9216 pads on Bottom Layer CALICE electronics meeting LLR January 2010, Hervé MATHEZ 4

1 m 2 PCB DESIGN interconnection 1 DIF for 2 ASUs Problems with 90 pins Samtek connector : Pad are teared off after Several connect/disconnect DIF Board DIFF board Add a kapton cable between DIFF board and ASU To reduce connection problems (will be tested with HR 2 -HR 2 b) CALICE electronics meeting LLR January 2010, Hervé MATHEZ 5

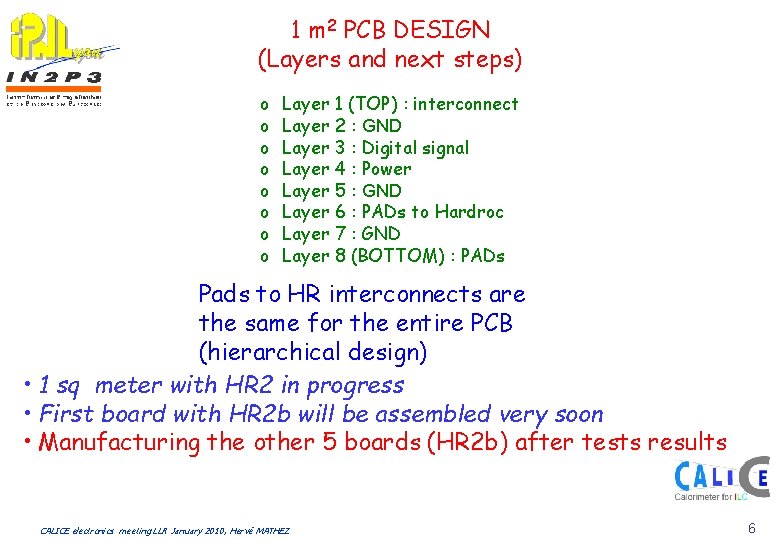

1 m 2 PCB DESIGN (Layers and next steps) o o o o Layer 1 (TOP) : interconnect Layer 2 : GND Layer 3 : Digital signal Layer 4 : Power Layer 5 : GND Layer 6 : PADs to Hardroc Layer 7 : GND Layer 8 (BOTTOM) : PADs Pads to HR interconnects are the same for the entire PCB (hierarchical design) • 1 sq meter with HR 2 in progress • First board with HR 2 b will be assembled very soon • Manufacturing the other 5 boards (HR 2 b) after tests results CALICE electronics meeting LLR January 2010, Hervé MATHEZ 6

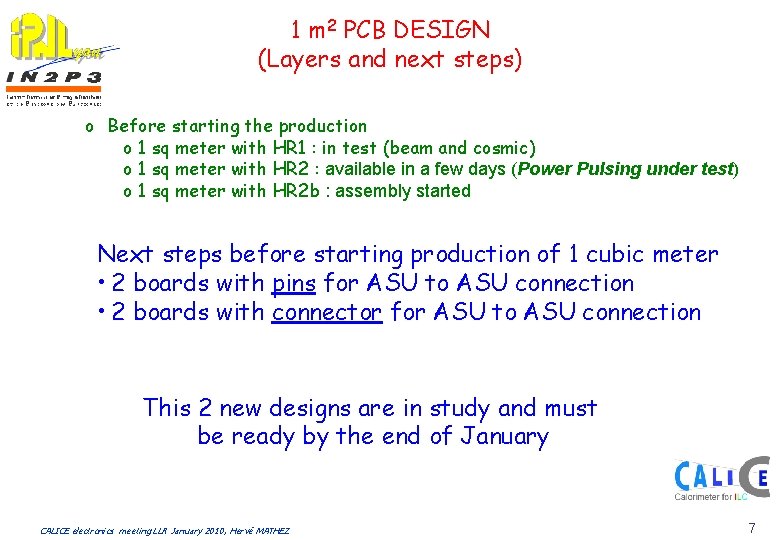

1 m 2 PCB DESIGN (Layers and next steps) o Before starting the production o 1 sq meter with HR 1 : in test (beam and cosmic) o 1 sq meter with HR 2 : available in a few days (Power Pulsing under test) o 1 sq meter with HR 2 b : assembly started Next steps before starting production of 1 cubic meter • 2 boards with pins for ASU to ASU connection • 2 boards with connector for ASU to ASU connection This 2 new designs are in study and must be ready by the end of January CALICE electronics meeting LLR January 2010, Hervé MATHEZ 7

ASIC DEVELOPMENT IN LYON Hervé MATHEZ, Yannick ZOCCARATO, Luigi CAPONETTO (CNRS IN 2 P 3 IPNL) Collaboration with LAL/LAPP CALICE electronics meeting LLR January 2010, Hervé MATHEZ 8

Mixed signal Asic design This ASIC include : (for details see talk on previous Calice meeting in Lyon) • Digital part for DIRAC design • I 2 C serial link for slow control parameters • CSA : • same analog block as DIRAC 3 • slow control parameters (4 gains) controlled through I 2 C AMS 0. 35 µm in CMOS process Cadence design flow for digital and analog parts CALICE electronics meeting LLR January 2010, Hervé MATHEZ 9

Advantages of the serial interface vs a shift register o Individually addressed readout and slow control. o More flexibility for the user o Easier for the driver firmware design (DIF board) o The readout of the sent parameters is possible without rewriting them. o Easier board routing (without chips chaining). o Less sensitive to the risk of failure propagation. CALICE electronics meeting LLR January 2010, Hervé MATHEZ 10

CSA for RPC/µMEGAS o Switched integrator o Folded cascode with feed forward compensation technique o 4 gains (10 p. F 200 f. F 100 f. F 50 f. F) o 100 m. V/p. C, 4 m. V/f. C, 7 m. V/f. C, 10 m. V/f. C o Main goal is to detect pulses as low as 2 f. C o Return from fab in October 2009 o Tests will be performed with standard comparator CALICE electronics meeting LLR January 2010, Hervé MATHEZ 11

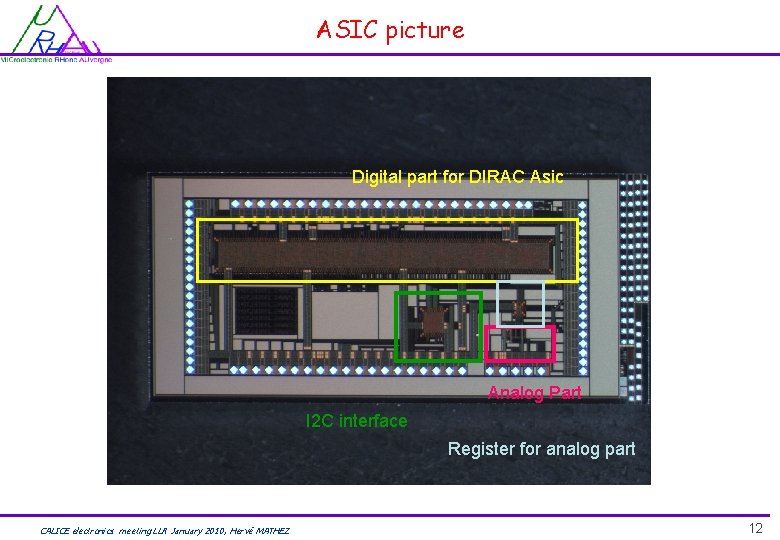

ASIC picture Digital part for DIRAC Asic Analog Part I 2 C interface Register for analog part CALICE electronics meeting LLR January 2010, Hervé MATHEZ 12

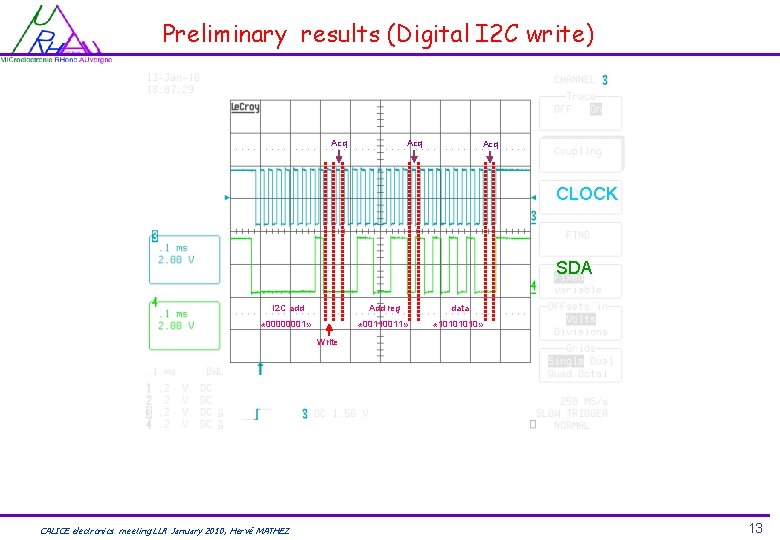

Preliminary results (Digital I 2 C write) Acq Acq CLOCK SDA I 2 C add Add reg data « 00000001» « 0011» « 1010» Write CALICE electronics meeting LLR January 2010, Hervé MATHEZ 13

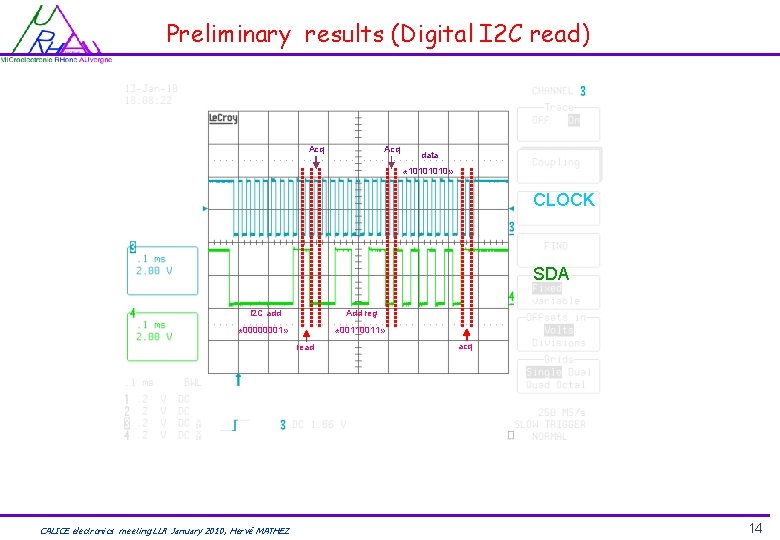

Preliminary results (Digital I 2 C read) Acq data « 1010» CLOCK SDA I 2 C add Add reg « 00000001» « 0011» read CALICE electronics meeting LLR January 2010, Hervé MATHEZ acq 14

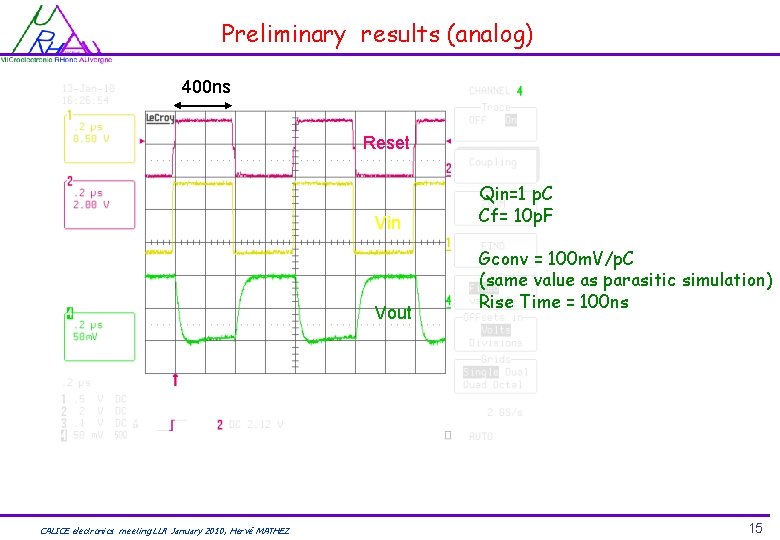

Preliminary results (analog) 400 ns Reset Vin Vout CALICE electronics meeting LLR January 2010, Hervé MATHEZ Qin=1 p. C Cf= 10 p. F Gconv = 100 m. V/p. C (same value as parasitic simulation) Rise Time = 100 ns 15

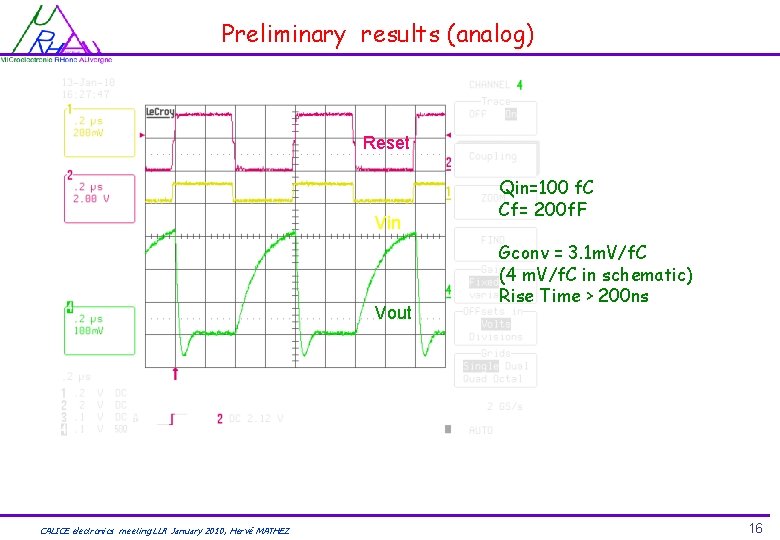

Preliminary results (analog) Reset Vin Vout CALICE electronics meeting LLR January 2010, Hervé MATHEZ Qin=100 f. C Cf= 200 f. F Gconv = 3. 1 m. V/f. C (4 m. V/f. C in schematic) Rise Time > 200 ns 16

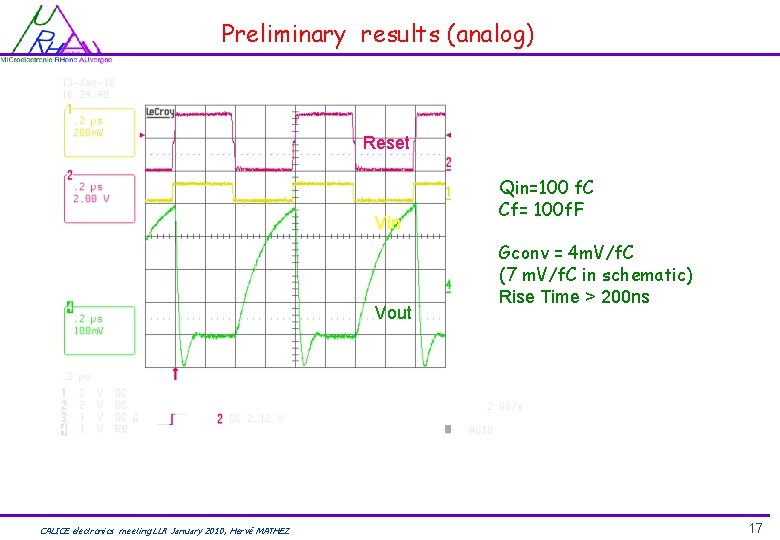

Preliminary results (analog) Reset Vin Vout CALICE electronics meeting LLR January 2010, Hervé MATHEZ Qin=100 f. C Cf= 100 f. F Gconv = 4 m. V/f. C (7 m. V/f. C in schematic) Rise Time > 200 ns 17

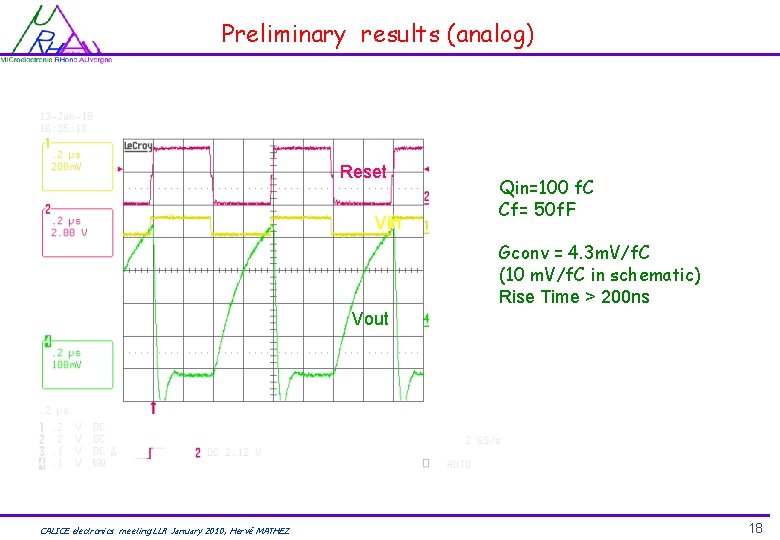

Preliminary results (analog) Reset Vin Qin=100 f. C Cf= 50 f. F Gconv = 4. 3 m. V/f. C (10 m. V/f. C in schematic) Rise Time > 200 ns Vout CALICE electronics meeting LLR January 2010, Hervé MATHEZ 18

Conclusion ASIC : o Return from fab : October 2009 o Test is started since 1 week o Digital part : o. I 2 C is working : CSA can be controlled by I 2 C • Power, max frequency : still to be measured o. Digital part for DIRAC will be tested soon o Analog part : • Close to parasitic simulation (Gconv) • To be be measured : • Noise • Linearity • Minimum pulse detection with standard comparator o In case of ILC timing the CSA must be improved o Slow rise time could explained the minimum pulse detection o Next step o Digital part can be implemented in DIRACx/HARDROCx o. This link can be doubled to introduce redundancy (reduce risks of failure) CALICE electronics meeting LLR January 2010, Hervé MATHEZ 19

- Slides: 19