Topic Review FPGA vs ASIC Steve Poret RCS

![References [1] Measuring the Gap between FPGAs and ASICs � � � Ian Kuon References [1] Measuring the Gap between FPGAs and ASICs � � � Ian Kuon](https://slidetodoc.com/presentation_image_h/8d2567598ab441c93236cf612bcda0b6/image-2.jpg)

![References [5] Signal, Timing Integrity Assured with FPGAs - Technology Information � � � References [5] Signal, Timing Integrity Assured with FPGAs - Technology Information � � �](https://slidetodoc.com/presentation_image_h/8d2567598ab441c93236cf612bcda0b6/image-3.jpg)

- Slides: 41

Topic Review: FPGA vs. ASIC Steve Poret RCS – ENG 6530 June 10, 2008

![References 1 Measuring the Gap between FPGAs and ASICs Ian Kuon References [1] Measuring the Gap between FPGAs and ASICs � � � Ian Kuon](https://slidetodoc.com/presentation_image_h/8d2567598ab441c93236cf612bcda0b6/image-2.jpg)

References [1] Measuring the Gap between FPGAs and ASICs � � � Ian Kuon and Jonathan Rose The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto, 2006 [2] (When) Will FPGAs Kill ASICs? � � � Rajeev, Jayaraman Xilinx Inc. DAC-2001 [3] ASICs Verses FPGAs � � � Frank J. Bartos Control Engineering 6/1/2005 [4] Structured ASICs � Dan Lander, Haru Yamamoto, Shane Erickson � UCLA - EE 201 A � Spring 2004

![References 5 Signal Timing Integrity Assured with FPGAs Technology Information References [5] Signal, Timing Integrity Assured with FPGAs - Technology Information � � �](https://slidetodoc.com/presentation_image_h/8d2567598ab441c93236cf612bcda0b6/image-3.jpg)

References [5] Signal, Timing Integrity Assured with FPGAs - Technology Information � � � Rich Sevcik Electronic News July 24, 2000 [6] Navigating the Silicon Jungle: FPGA or ASIC? � � � Blyler, John Chip Design Magazine June/July 2005 [7] FPGA vs. ASIC � � � Xilinx Inc. Getting Started with Xilinx 2006 [8] Xilinx: Virtex-5 Family Overview � � Xilinx Inc. datasheet DS 100(v 4. 2) May 7, 2008

Overview � Introduction � Performance Perspective ◦ Measuring the Gap between FPGAs and ASICs, [1] � Cost/Risk/Lifecycle Perspective ◦ (When) Will FPGAs Kill ASICs? , [2] ◦ ASICs verses FPGAs, [3] � Summary � Future Technology ◦ Structured/Platform ASICs, [4] � Conclusion

Introduction ASIC (Application Specific Integrated Circuit) ◦ An IC designed for a particular use ◦ Standard cell, full-custom ASIC Applications ◦ Processors ◦ RAM ◦ ROM

Introduction Why are we interested? ◦ The size of transistors are shrinking to sub-micron levels Deep Sub-Micron (DSM) designs have problems � Two main fundamental issues: ◦ Signal Integrity ◦ Timing Closure � Is an ASIC still the best architecture?

Introduction FPGA (Field Programmable Gate Array) ◦ Logic blocks and programmable interconnects ◦ Synthesis tools are designed to counter DSM issues Applications ◦ ◦ ASIC Prototyping Massive parallelism (code breaking, cryptography) DSP, SDR, medical imaging FFT

Introduction � Implementation ◦ Based on: medium: FPGA or ASIC? �Area �Performance �Power consumption �Cost �Time-to-market �Design Cycle �Complexity of design � How do we measure the gap between FPGAs and ASICs?

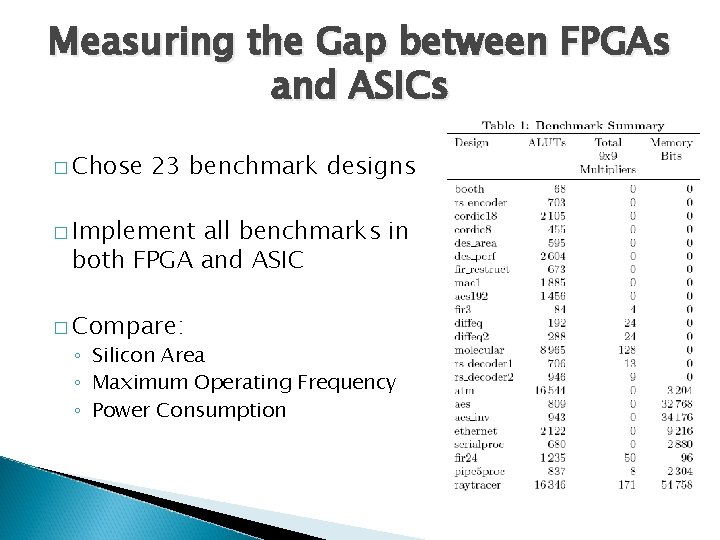

Measuring the Gap between FPGAs and ASICs � New FPGA vs. ASIC comparison, (Kuon, Rose) � System Architecture: ◦ Altera Stratix II (FPGA) ◦ STM CMOS 090 Design Platform standard cell (ASIC) � Look at previous comparisons: inadequate � Authors took many considerations to ensure most accurate possible comparison

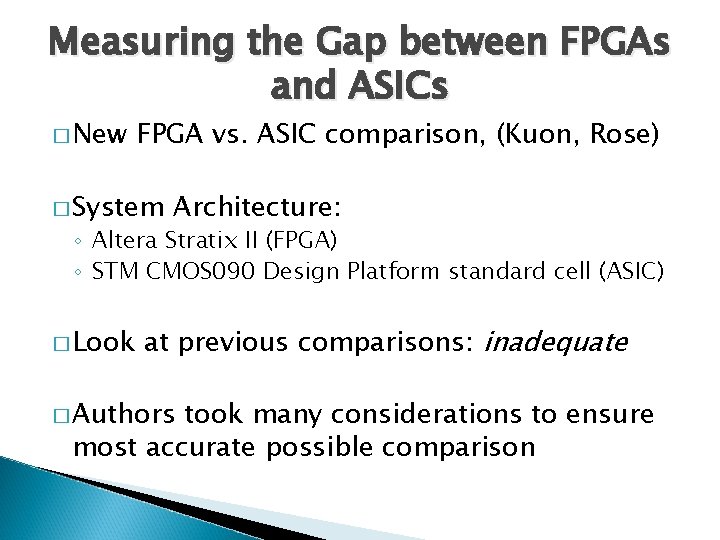

Measuring the Gap between FPGAs and ASICs � Chose 23 benchmark designs � Implement all benchmarks in both FPGA and ASIC � Compare: ◦ Silicon Area ◦ Maximum Operating Frequency ◦ Power Consumption

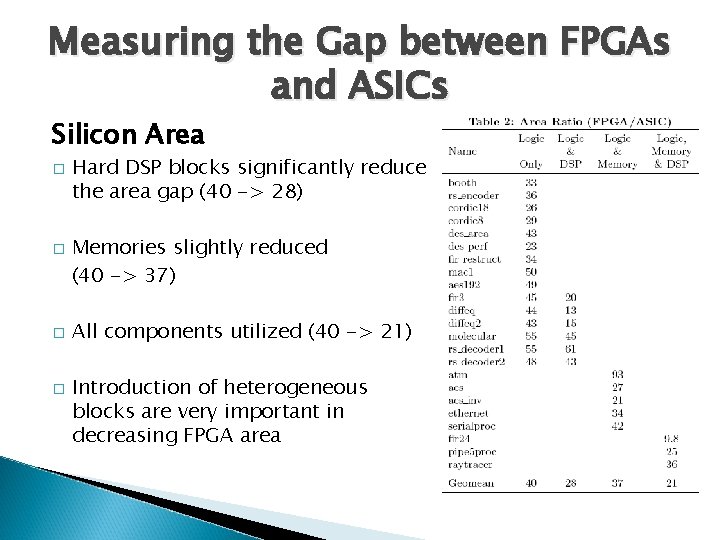

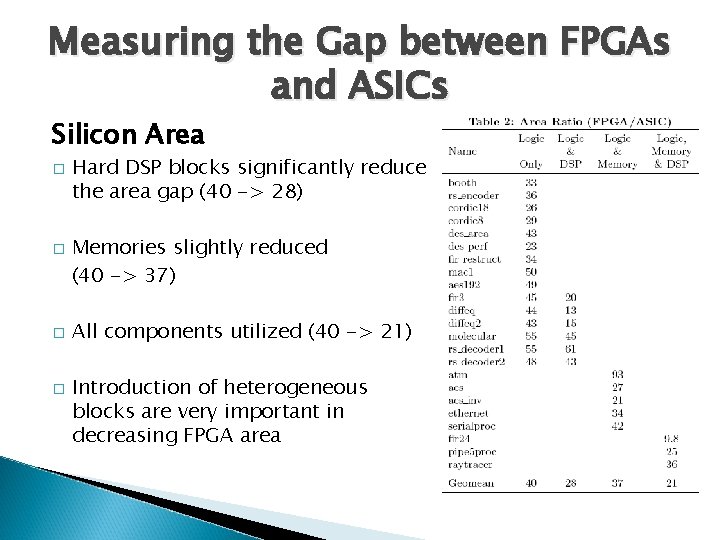

Measuring the Gap between FPGAs and ASICs Silicon Area � � Hard DSP blocks significantly reduce the area gap (40 -> 28) Memories slightly reduced (40 -> 37) All components utilized (40 -> 21) Introduction of heterogeneous blocks are very important in decreasing FPGA area

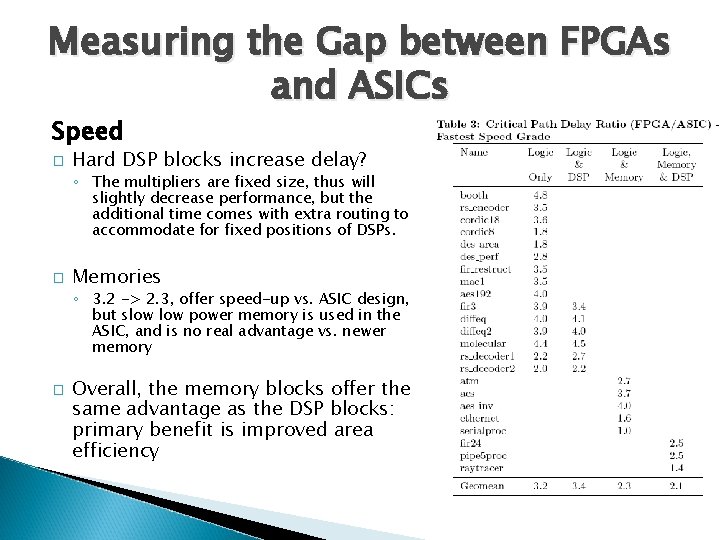

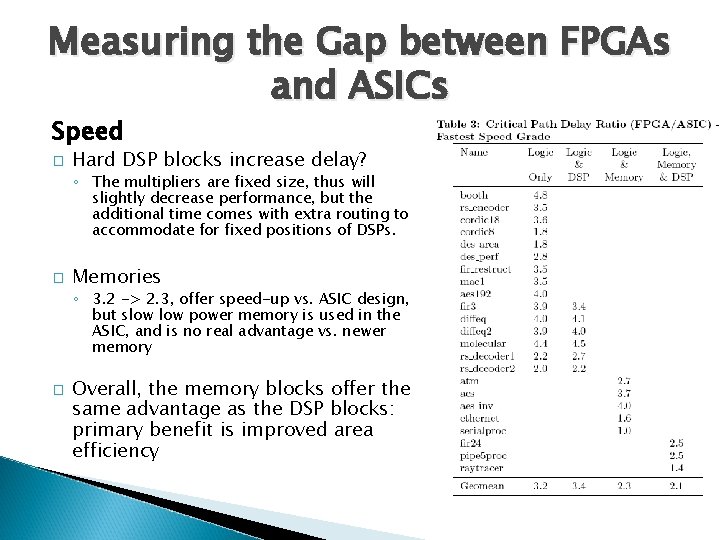

Measuring the Gap between FPGAs and ASICs Speed � Hard DSP blocks increase delay? ◦ The multipliers are fixed size, thus will slightly decrease performance, but the additional time comes with extra routing to accommodate for fixed positions of DSPs. � Memories ◦ 3. 2 -> 2. 3, offer speed-up vs. ASIC design, but slow power memory is used in the ASIC, and is no real advantage vs. newer memory � Overall, the memory blocks offer the same advantage as the DSP blocks: primary benefit is improved area efficiency

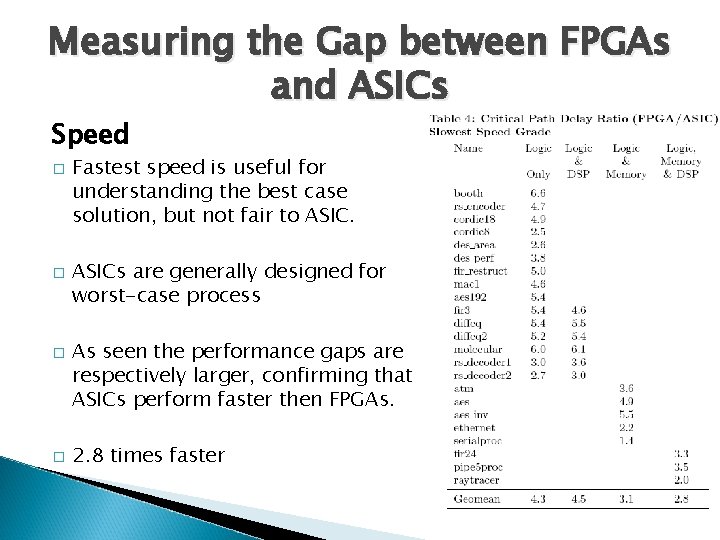

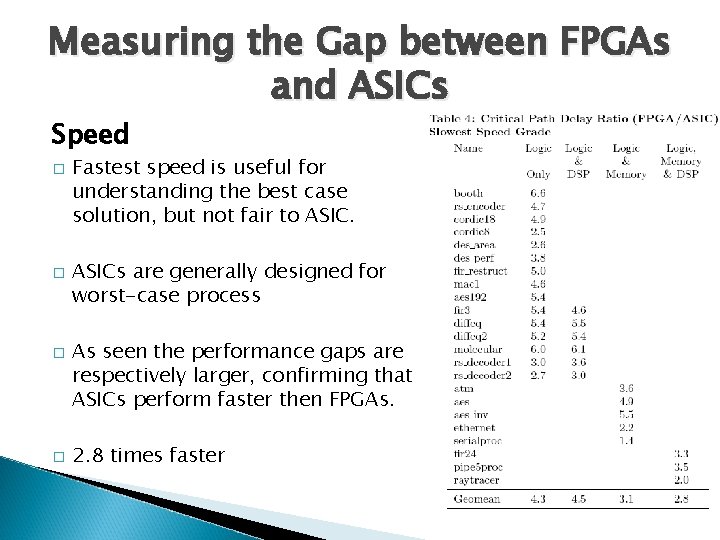

Measuring the Gap between FPGAs and ASICs Speed � � Fastest speed is useful for understanding the best case solution, but not fair to ASICs are generally designed for worst-case process As seen the performance gaps are respectively larger, confirming that ASICs perform faster then FPGAs. 2. 8 times faster

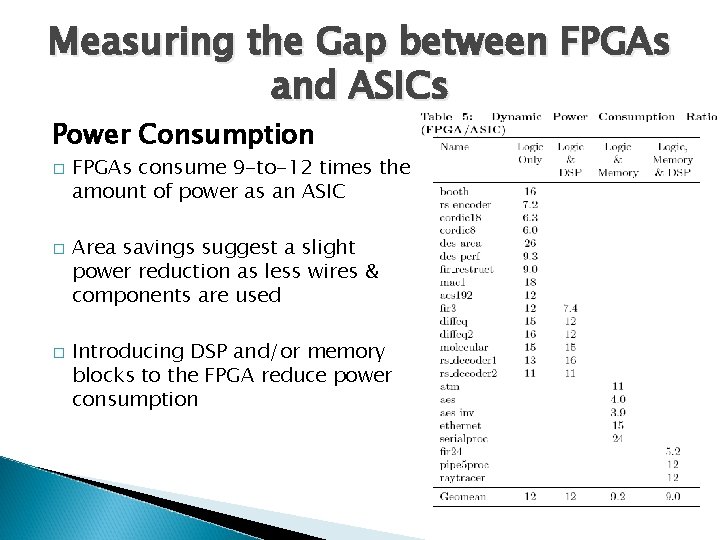

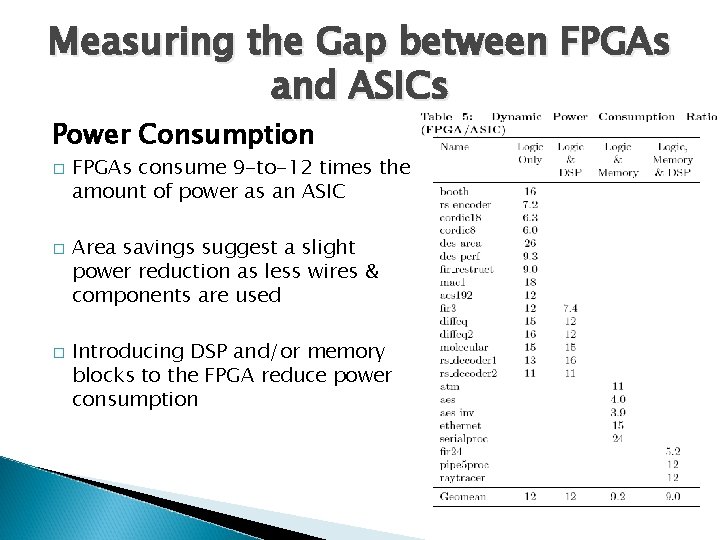

Measuring the Gap between FPGAs and ASICs Power Consumption � � � FPGAs consume 9 -to-12 times the amount of power as an ASIC Area savings suggest a slight power reduction as less wires & components are used Introducing DSP and/or memory blocks to the FPGA reduce power consumption

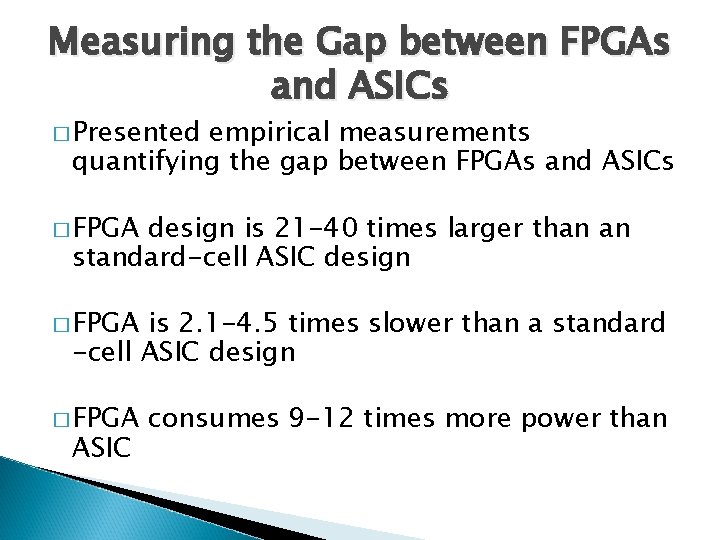

Measuring the Gap between FPGAs and ASICs � Presented empirical measurements quantifying the gap between FPGAs and ASICs � FPGA design is 21 -40 times larger than an standard-cell ASIC design � FPGA is 2. 1 -4. 5 times slower than a standard -cell ASIC design � FPGA ASIC consumes 9 -12 times more power than

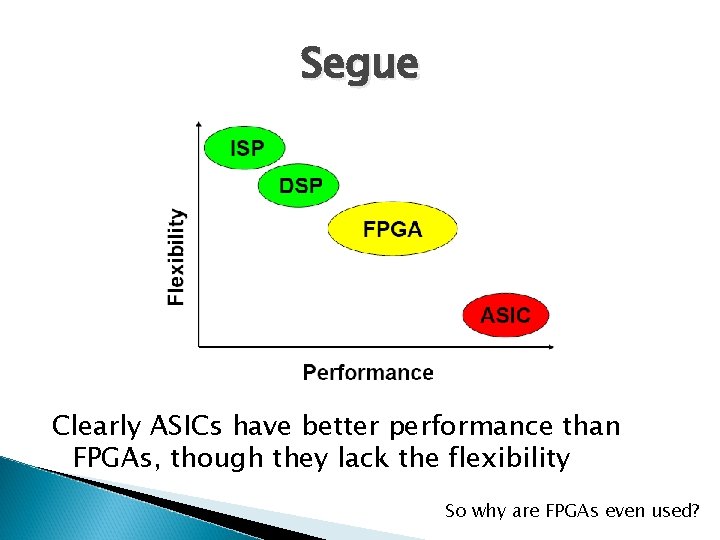

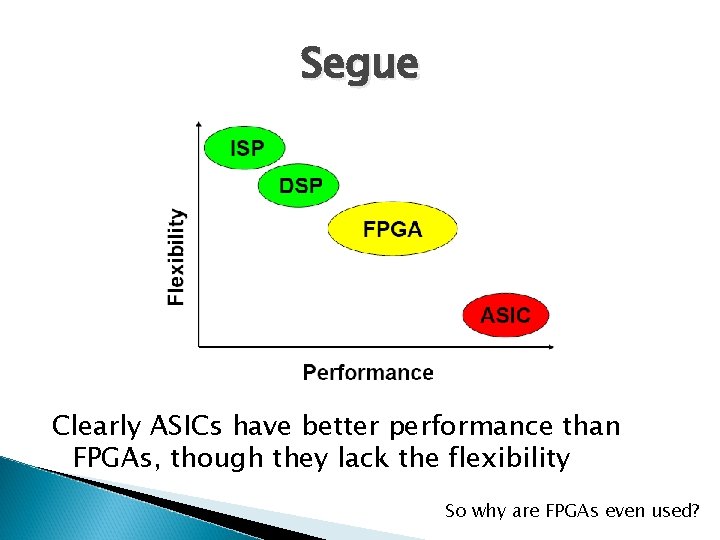

Segue Clearly ASICs have better performance than FPGAs, though they lack the flexibility So why are FPGAs even used?

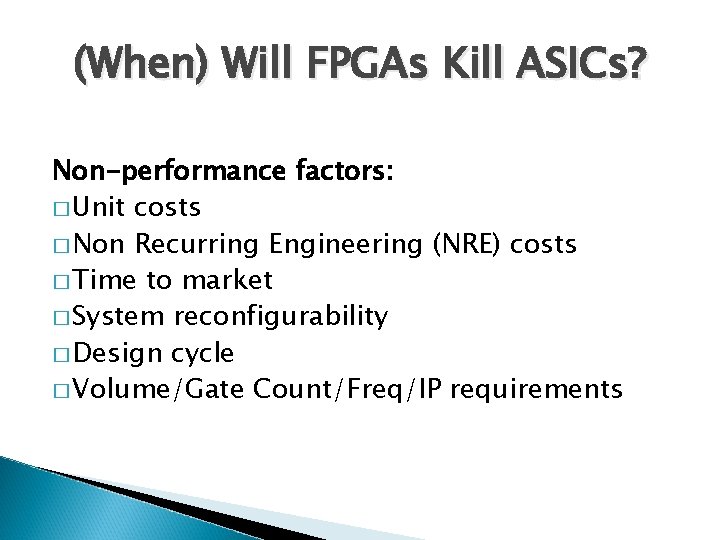

(When) Will FPGAs Kill ASICs? Non-performance factors: � Unit costs � Non Recurring Engineering (NRE) costs � Time to market � System reconfigurability � Design cycle � Volume/Gate Count/Freq/IP requirements

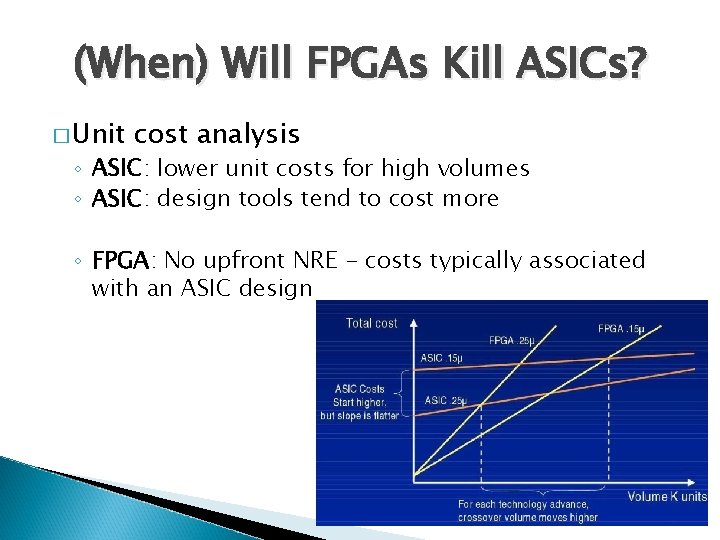

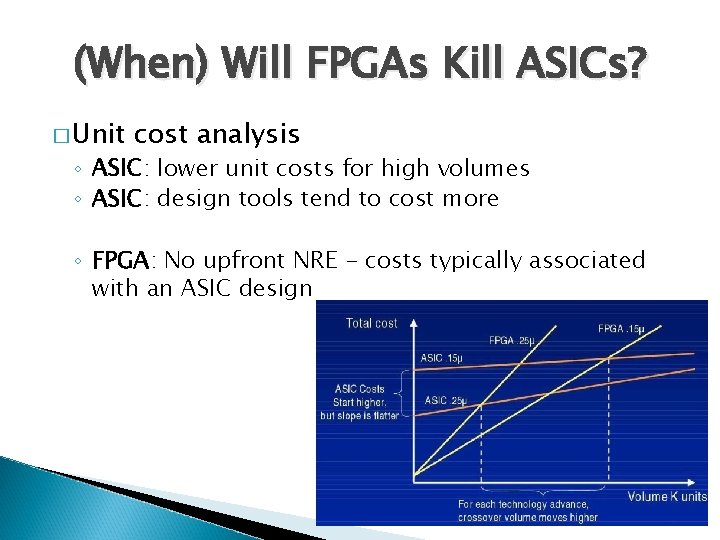

(When) Will FPGAs Kill ASICs? � Unit cost analysis ◦ ASIC: lower unit costs for high volumes ◦ ASIC: design tools tend to cost more ◦ FPGA: No upfront NRE - costs typically associated with an ASIC design

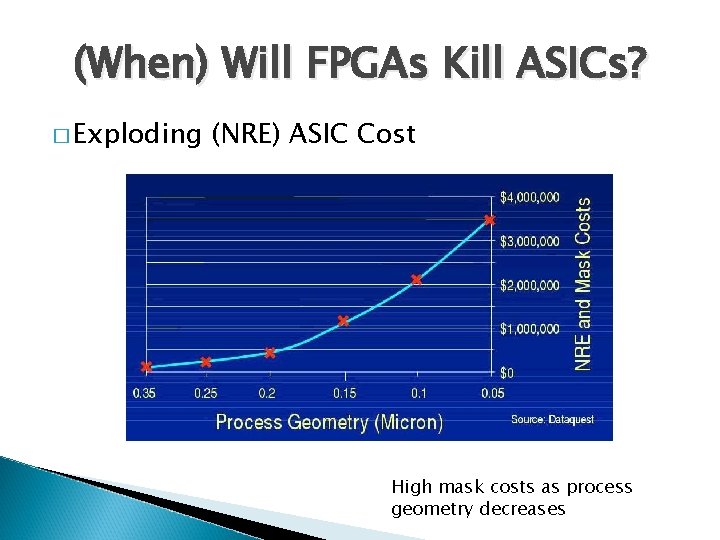

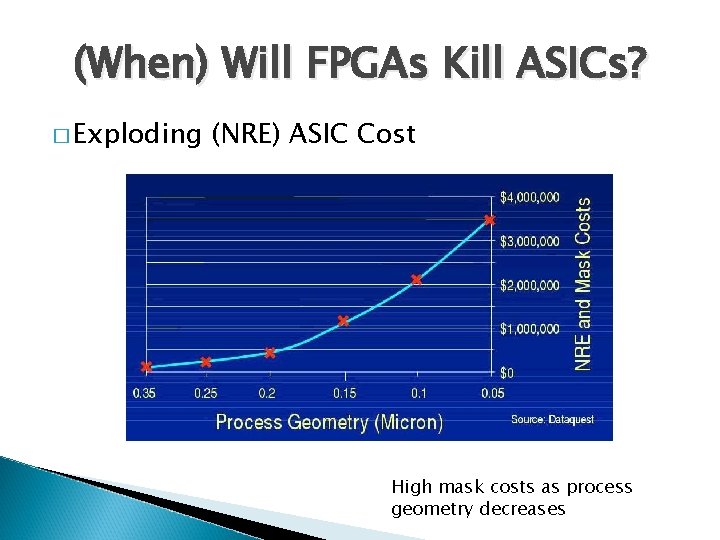

(When) Will FPGAs Kill ASICs? � Exploding (NRE) ASIC Cost High mask costs as process geometry decreases

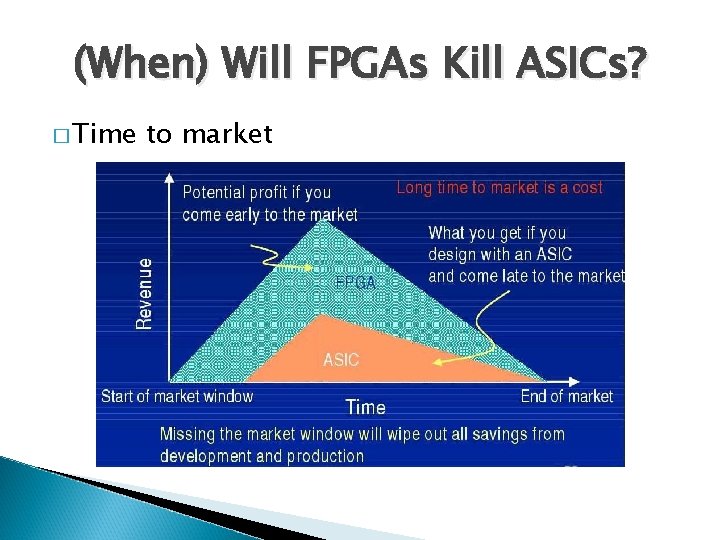

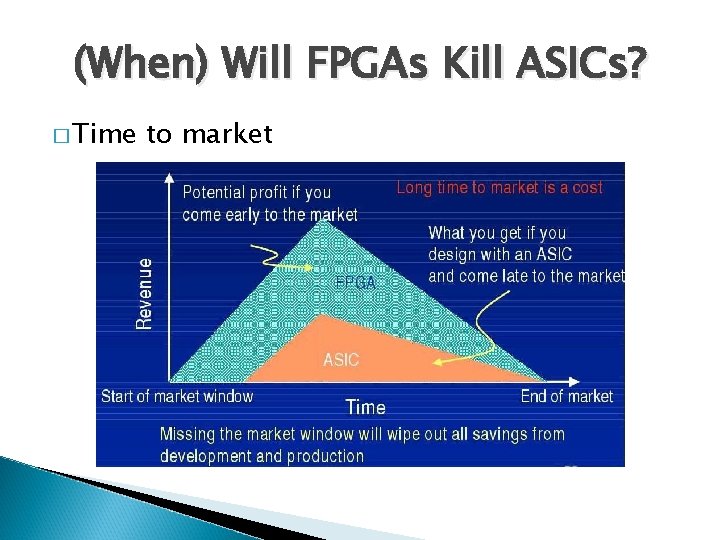

(When) Will FPGAs Kill ASICs? � Time to market

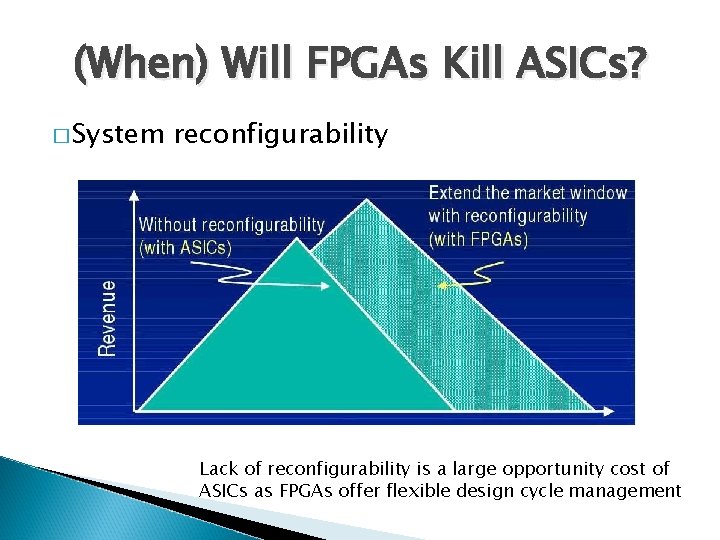

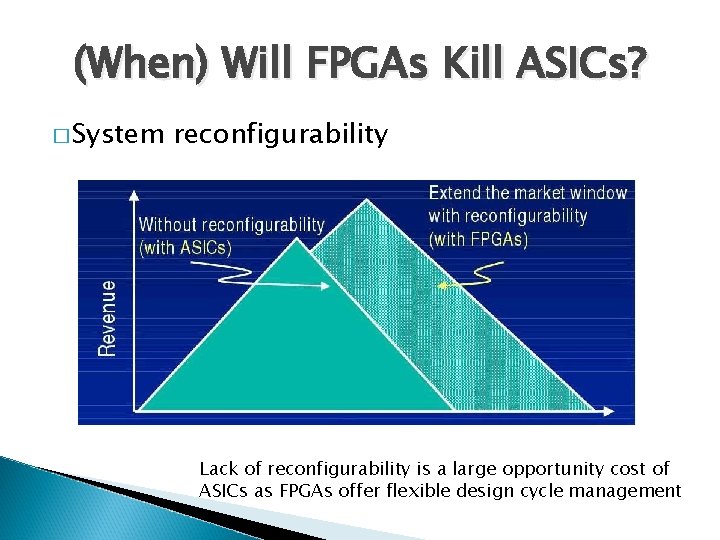

(When) Will FPGAs Kill ASICs? � System reconfigurability Lack of reconfigurability is a large opportunity cost of ASICs as FPGAs offer flexible design cycle management

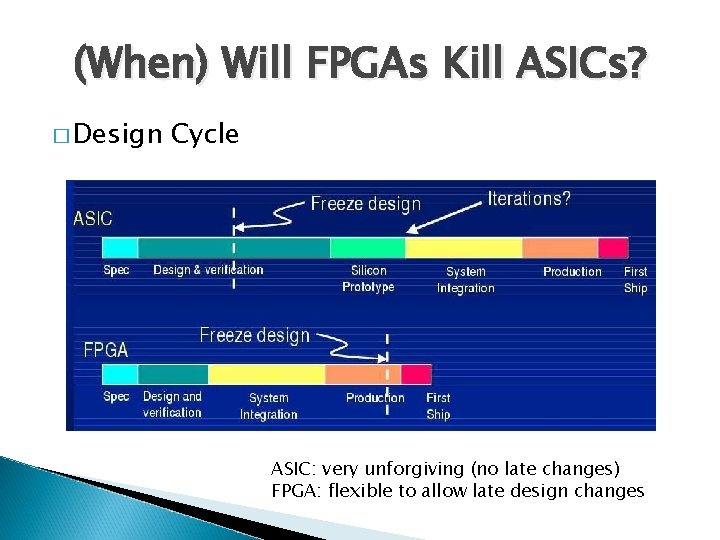

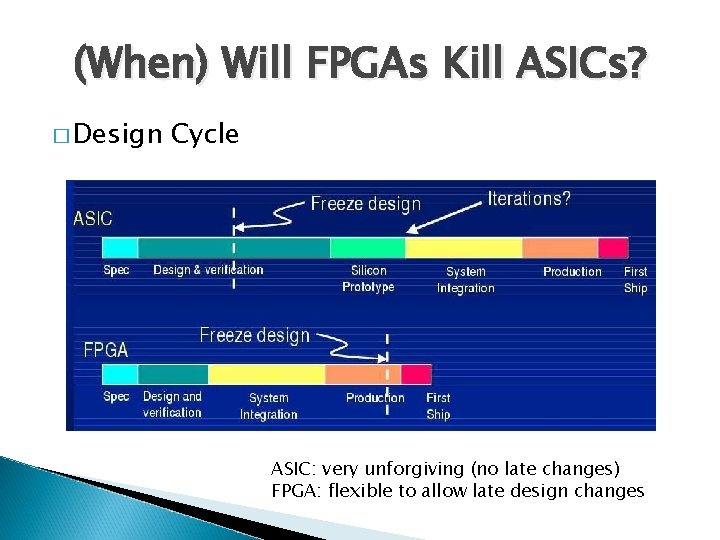

(When) Will FPGAs Kill ASICs? � Design Cycle ASIC: very unforgiving (no late changes) FPGA: flexible to allow late design changes

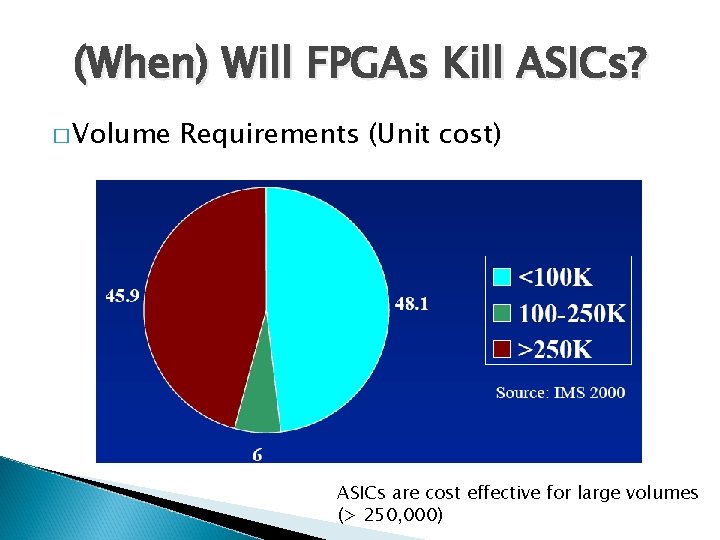

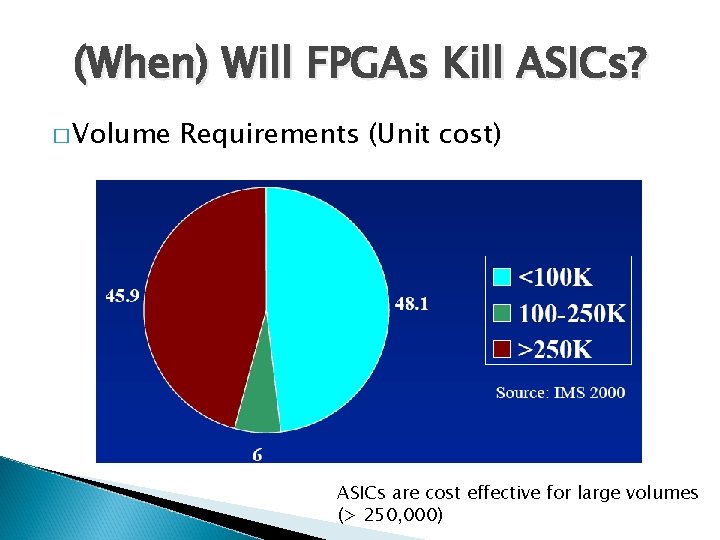

(When) Will FPGAs Kill ASICs? � Volume Requirements (Unit cost) ASICs are cost effective for large volumes (> 250, 000)

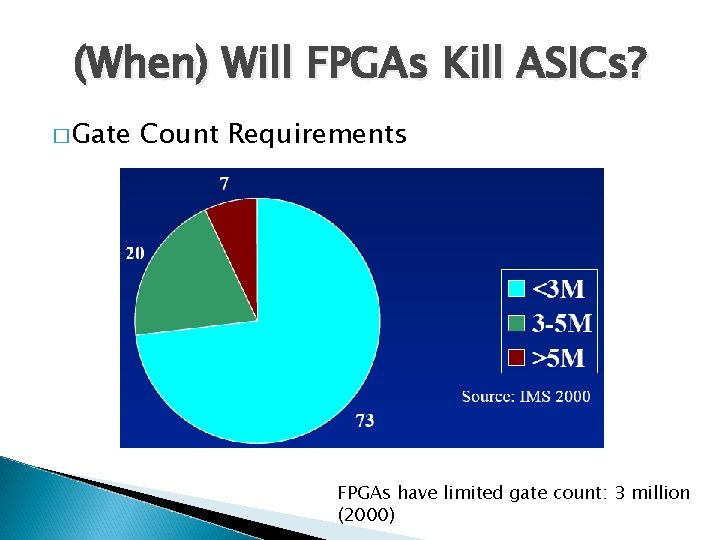

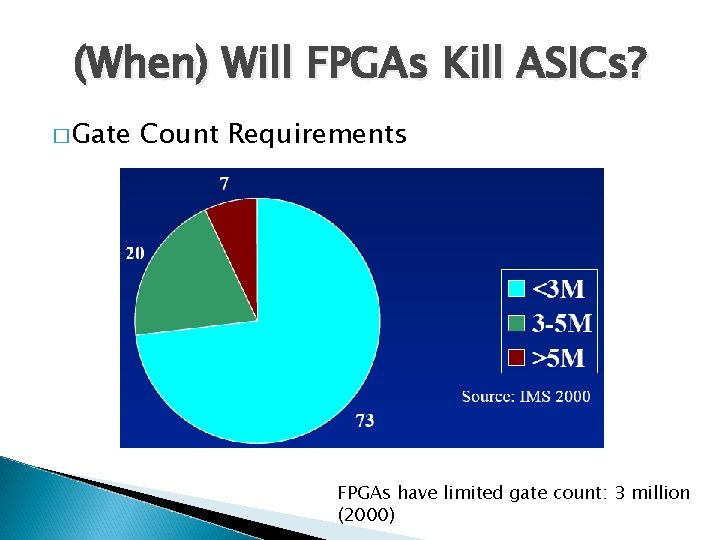

(When) Will FPGAs Kill ASICs? � Gate Count Requirements FPGAs have limited gate count: 3 million (2000)

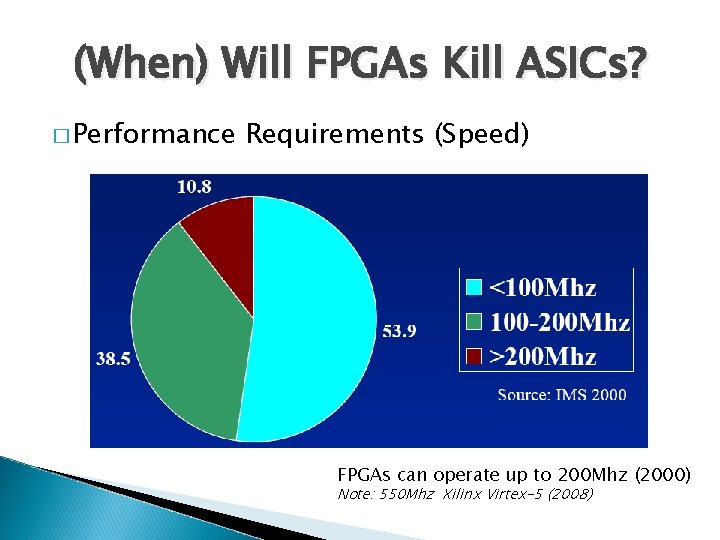

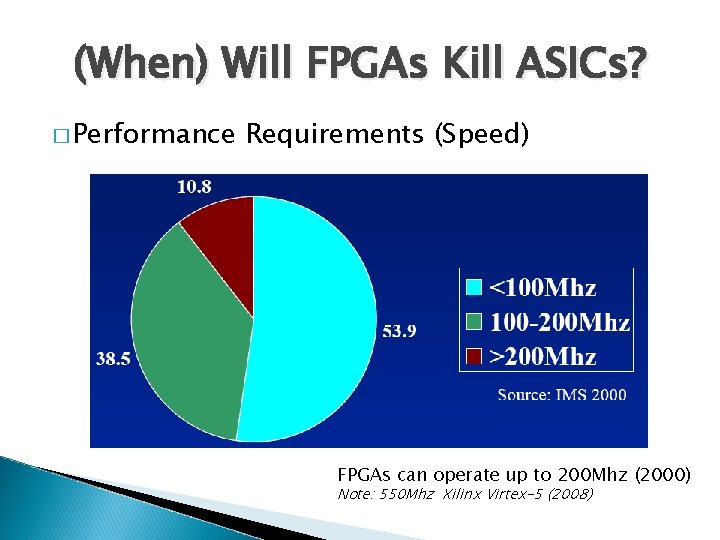

(When) Will FPGAs Kill ASICs? � Performance Requirements (Speed) FPGAs can operate up to 200 Mhz (2000) Note: 550 Mhz Xilinx Virtex-5 (2008)

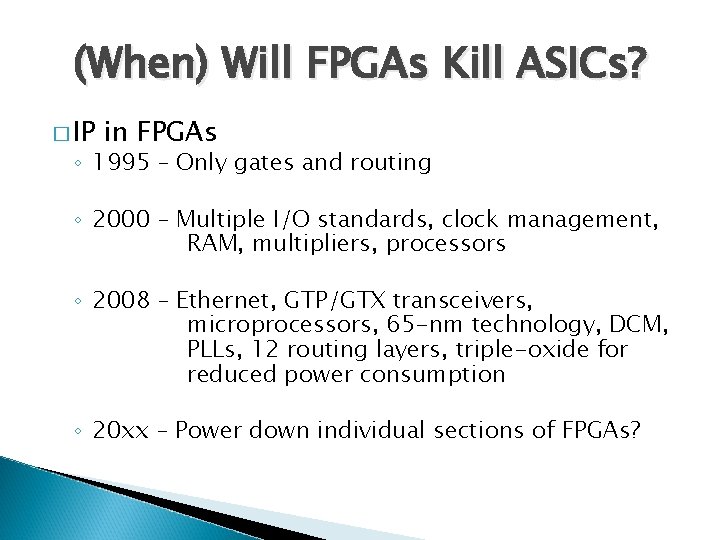

(When) Will FPGAs Kill ASICs? � IP in FPGAs ◦ 1995 – Only gates and routing ◦ 2000 – Multiple I/O standards, clock management, RAM, multipliers, processors ◦ 2008 – Ethernet, GTP/GTX transceivers, microprocessors, 65 -nm technology, DCM, PLLs, 12 routing layers, triple-oxide for reduced power consumption ◦ 20 xx – Power down individual sections of FPGAs?

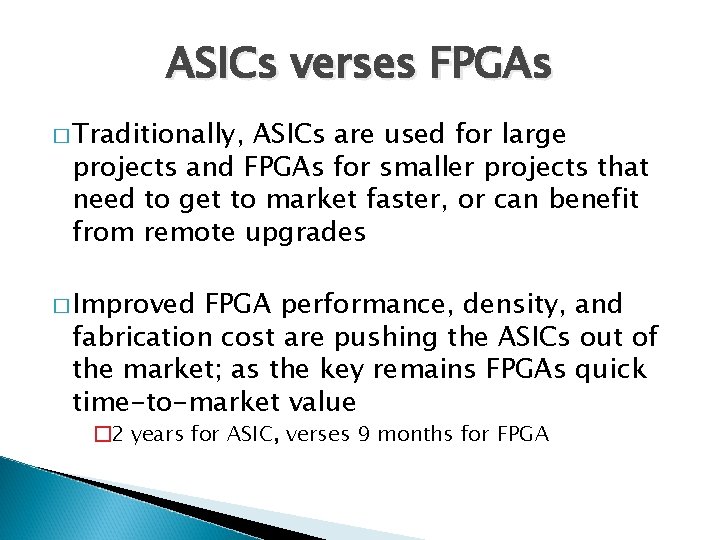

ASICs verses FPGAs � Traditionally, ASICs are used for large projects and FPGAs for smaller projects that need to get to market faster, or can benefit from remote upgrades � Improved FPGA performance, density, and fabrication cost are pushing the ASICs out of the market; as the key remains FPGAs quick time-to-market value � 2 years for ASIC, verses 9 months for FPGA

ASICs verses FPGAs (FGPA view) � Earlier FPGAs were only viable for prototyping or low-density applications; now they see very highvolume usage in consumer products and other moderate volume high-density applications � Highest-density FPGAs (90 nm) still have a definitive higher unit price than ASICs � However, cost trade-offs often favour FPGAs even with these highest density applications, when development and NRE charges are factored in David Greenfield, senior director of high-density FPGAs at Altera Corp

ASICs verses FPGAs (ASIC view) � Upfront development investment is higher with a cellbased ASIC approach � At high volumes, ROI is significantly better due to smaller die size and lower per unit costs. � FPGAs tend to be a better choice where unit price is less important, or time-to-market, or low initial development cost drives the solution � FPGAs and structured ASICs are suitable for low volume, short lifetime applications where customers can compromise on functionality and performance while still achieving their system objectives John Di. Filippo, silicon architect for TI's ASIC Communications Infrastructure Business Unit

Summary � FPGAs are closing in on ASICs for performance values, even though ASICs are smaller, faster and more efficient at the moment � FPGAs provide cost, time, reconfigurability and flexibility over ASIC designs which make them attractive � Gap is narrowing between the technologies

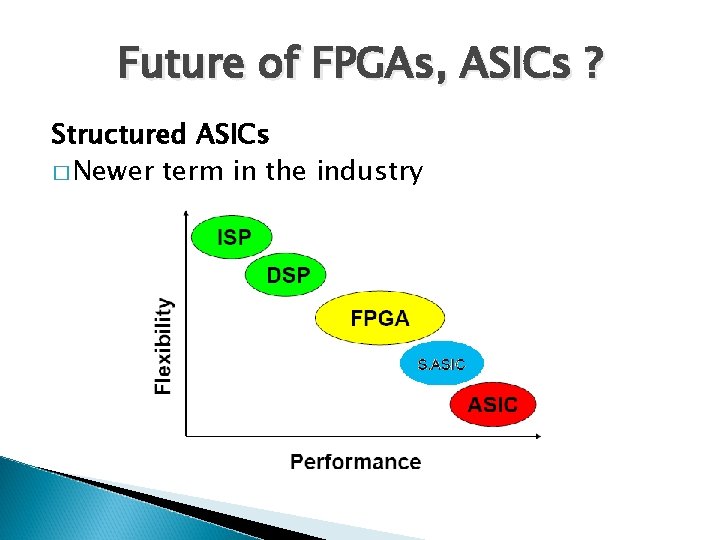

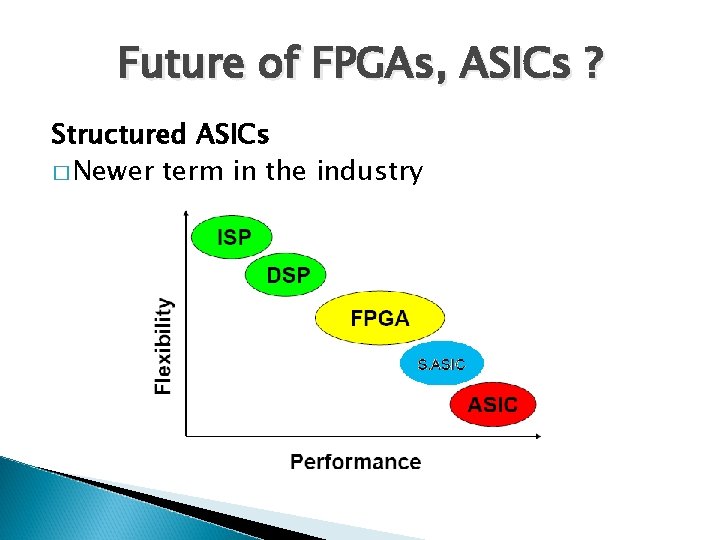

Future of FPGAs, ASICs ? Structured ASICs � Newer term in the industry

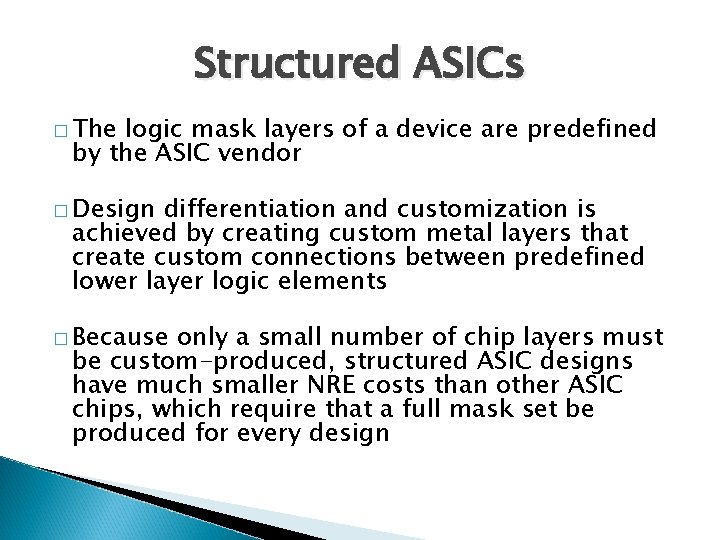

Structured ASICs � The logic mask layers of a device are predefined by the ASIC vendor � Design differentiation and customization is achieved by creating custom metal layers that create custom connections between predefined lower layer logic elements � Because only a small number of chip layers must be custom-produced, structured ASIC designs have much smaller NRE costs than other ASIC chips, which require that a full mask set be produced for every design

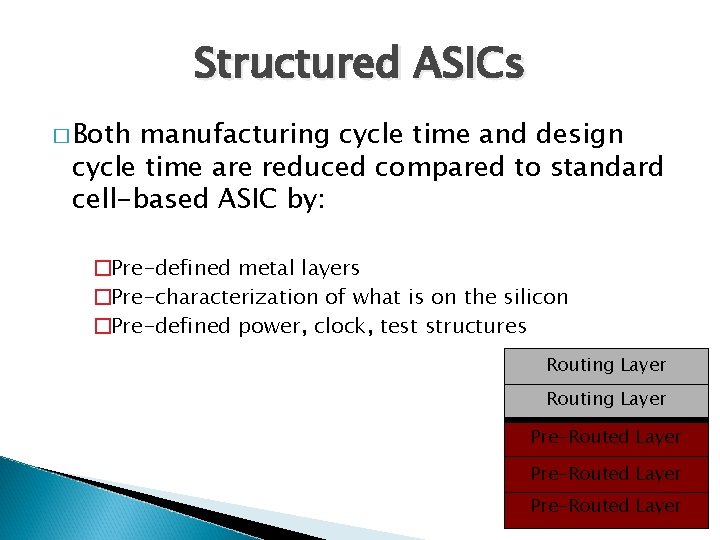

Structured ASICs � Both manufacturing cycle time and design cycle time are reduced compared to standard cell-based ASIC by: �Pre-defined metal layers �Pre-characterization of what is on the silicon �Pre-defined power, clock, test structures Routing Layer Pre-Routed Layer

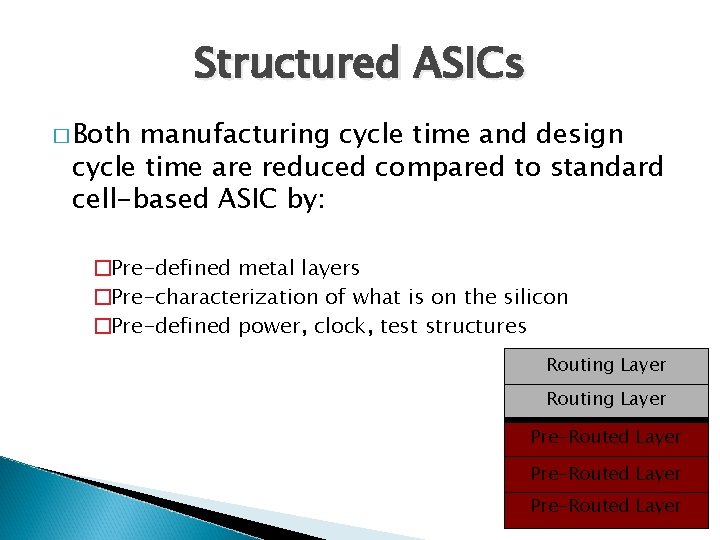

Structured ASICs � FPGA vendors have also designed their own version of the structured ASICs: � Altera (Hard. Copy) � Xilinx (Easy. Path) ◦ Same design cells as FPGA, but programmable routing replaced with fixed wire interconnects ◦ “customer specific FPGA”; 30 -70% cheaper than standard FPGA, same standard FPGA cells � Both designs have the programming capabilities removed

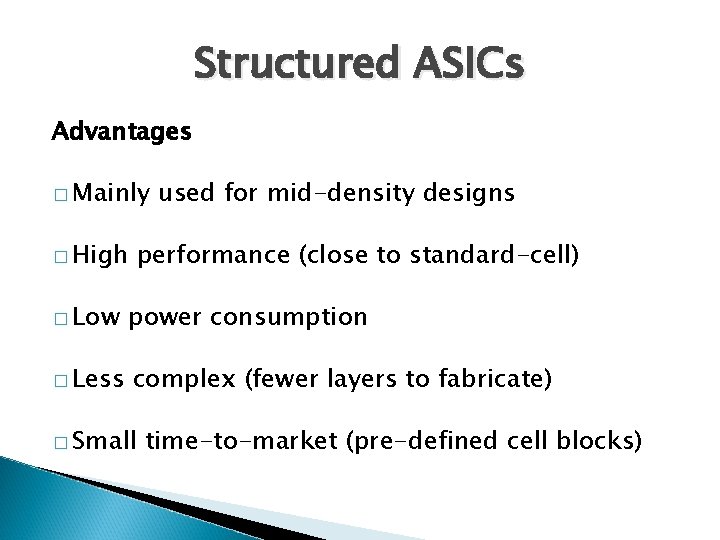

Structured ASICs Advantages � Mainly � High used for mid-density designs performance (close to standard-cell) � Low power consumption � Less complex (fewer layers to fabricate) � Small time-to-market (pre-defined cell blocks)

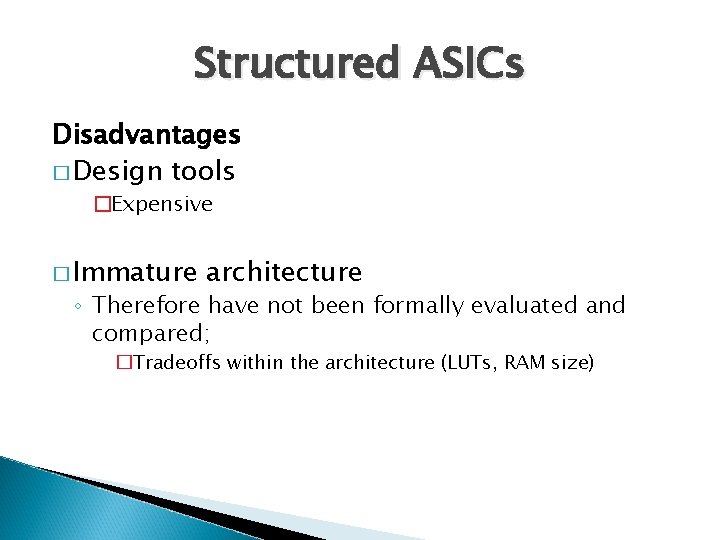

Structured ASICs Disadvantages � Design tools �Expensive � Immature architecture ◦ Therefore have not been formally evaluated and compared; �Tradeoffs within the architecture (LUTs, RAM size)

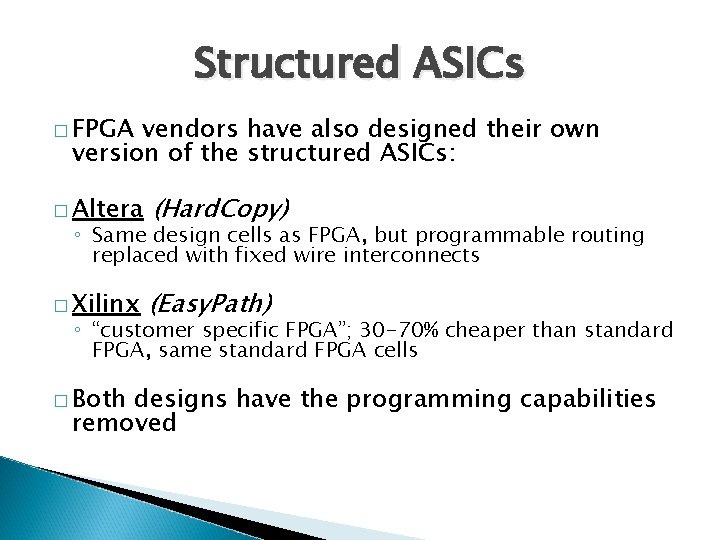

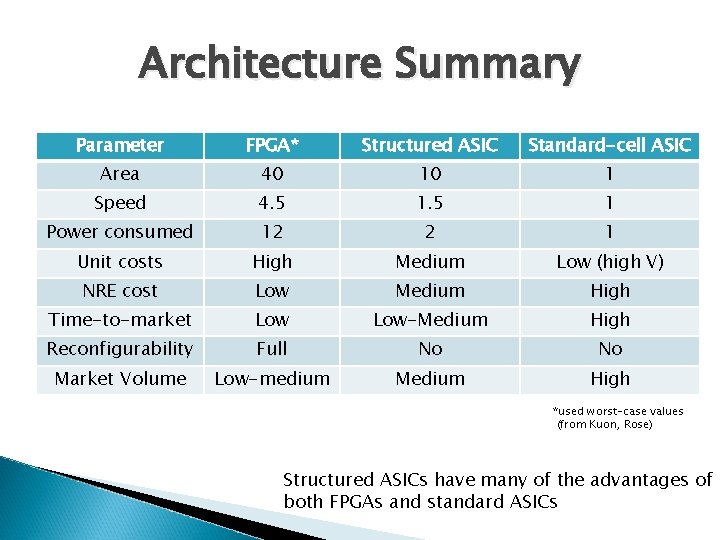

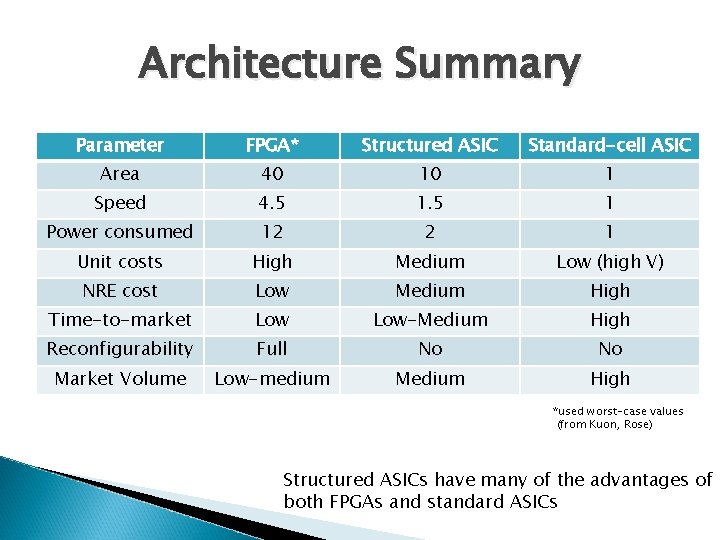

Architecture Summary Parameter FPGA* Structured ASIC Standard-cell ASIC Area 40 10 1 Speed 4. 5 1 Power consumed 12 2 1 Unit costs High Medium Low (high V) NRE cost Low Medium High Time-to-market Low-Medium High Reconfigurability Full No No Market Volume Low-medium Medium High *used worst-case values (from Kuon, Rose) Structured ASICs have many of the advantages of both FPGAs and standard ASICs

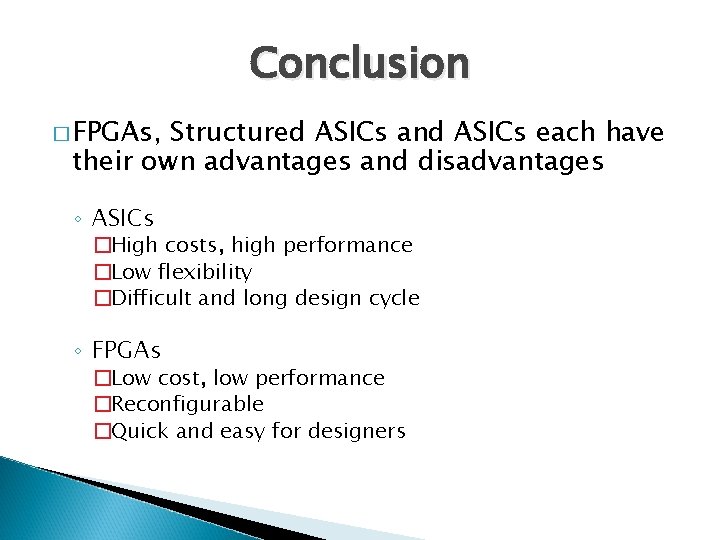

Conclusion � FPGAs, Structured ASICs and ASICs each have their own advantages and disadvantages ◦ ASICs �High costs, high performance �Low flexibility �Difficult and long design cycle ◦ FPGAs �Low cost, low performance �Reconfigurable �Quick and easy for designers

Questions � Do you have any questions? � Project …. .

Project Outline: Start with 1 -bit ALU design using VHDL (Xilinx) Modify an ALU from a 4 -bit to 16 -bits Add other capabilities to the ALU (Multiplication, Division) Duplicate the ALU to max capacity of the FPGA The ALUs are connected using different connections: ◦ Bus ◦ Point-to-point matrix connection Comparisons between the two implementations Solve Benchmarks TERM PROJECT

Project Outline: Start with 1 -bit ALU design Re-learn VHDL code Modify an ALU from a 4 -bit to 16 -bits Add other capabilities to the ALU (Multiplication, Division) Duplicate the ALU to max capacity of the FPGA The ALUs are connected using different connections: ◦ Bus ◦ Point-to-point matrix connection Comparisons between the two implementations Solve Benchmarks TERM PROJECT