Szchenyi Istvn Egyetem DSP implementcik 1 Szchenyi Istvn

- Slides: 60

Széchenyi István Egyetem DSP implementációk 1

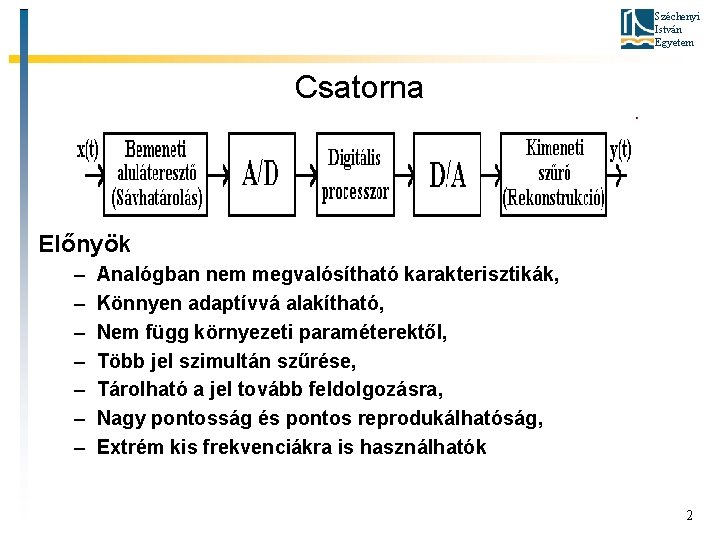

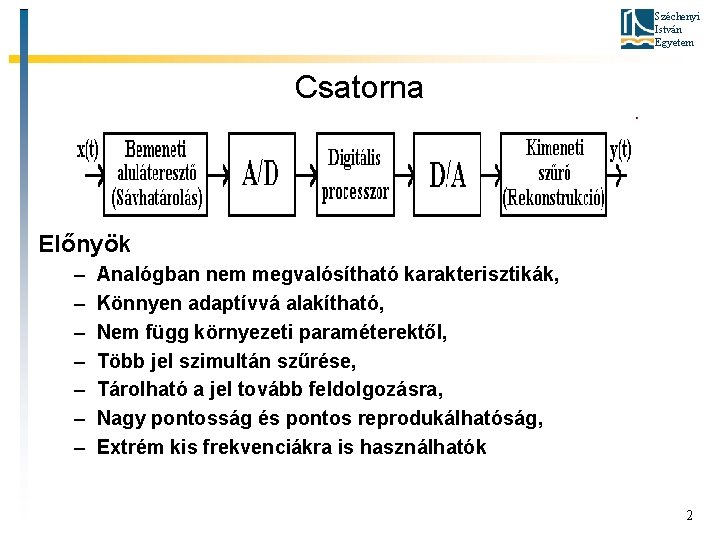

Széchenyi István Egyetem Csatorna Előnyök – – – – Analógban nem megvalósítható karakterisztikák, Könnyen adaptívvá alakítható, Nem függ környezeti paraméterektől, Több jel szimultán szűrése, Tárolható a jel tovább feldolgozásra, Nagy pontosság és pontos reprodukálhatóság, Extrém kis frekvenciákra is használhatók 2

Széchenyi István Egyetem DSP • Digital Signal Processing: jelfeldolgozó algoritmusok • Digital Signal Processor(s): Speciális mikroprocesszor osztály 3

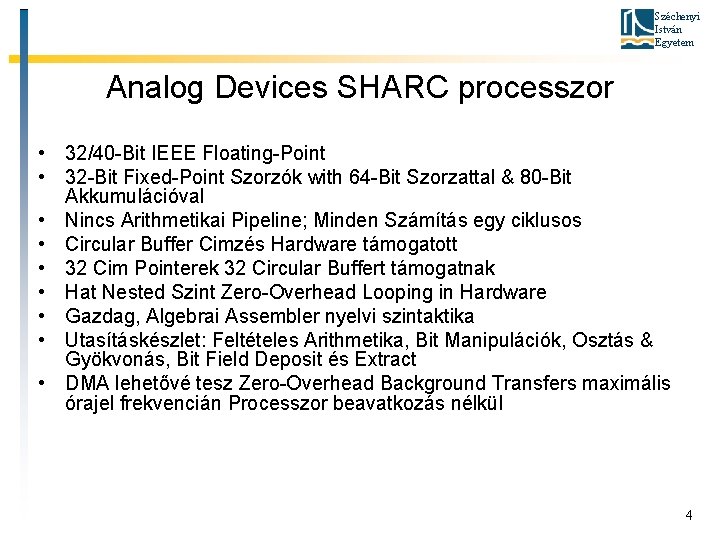

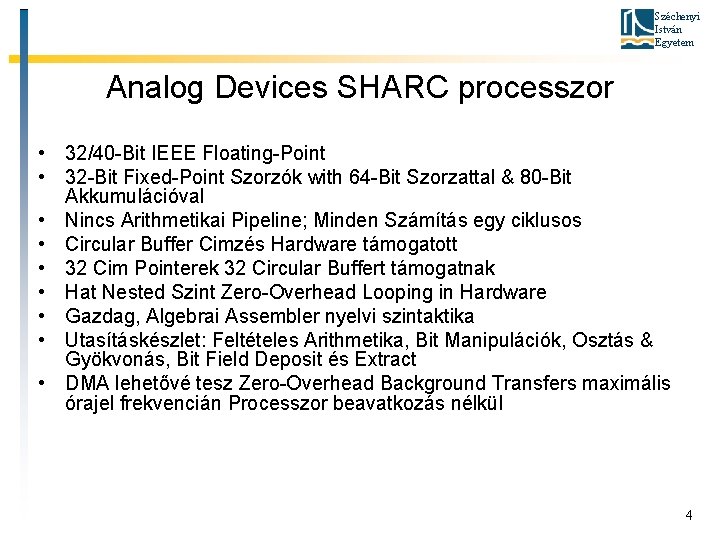

Széchenyi István Egyetem Analog Devices SHARC processzor • 32/40 -Bit IEEE Floating-Point • 32 -Bit Fixed-Point Szorzók with 64 -Bit Szorzattal & 80 -Bit Akkumulációval • Nincs Arithmetikai Pipeline; Minden Számítás egy ciklusos • Circular Buffer Cimzés Hardware támogatott • 32 Cim Pointerek 32 Circular Buffert támogatnak • Hat Nested Szint Zero-Overhead Looping in Hardware • Gazdag, Algebrai Assembler nyelvi szintaktika • Utasításkészlet: Feltételes Arithmetika, Bit Manipulációk, Osztás & Gyökvonás, Bit Field Deposit és Extract • DMA lehetővé tesz Zero-Overhead Background Transfers maximális órajel frekvencián Processzor beavatkozás nélkül 4

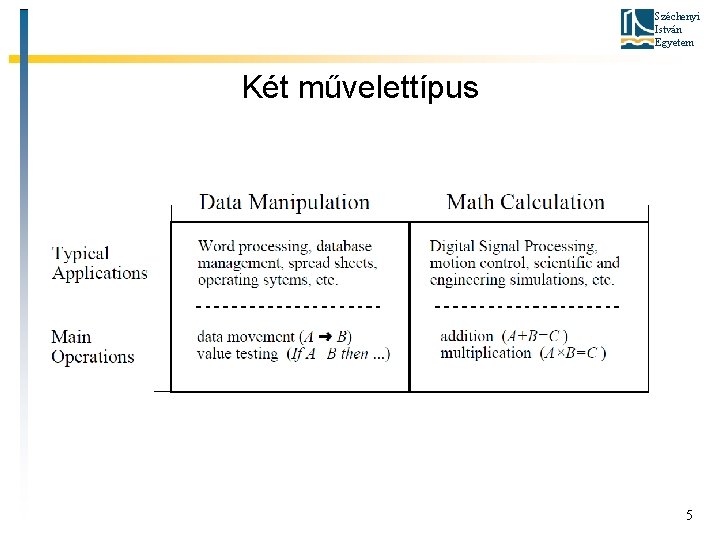

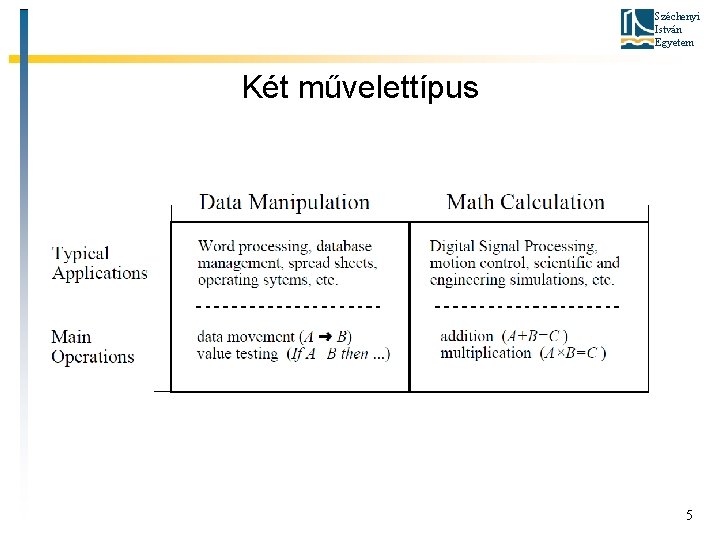

Széchenyi István Egyetem Két művelettípus 5

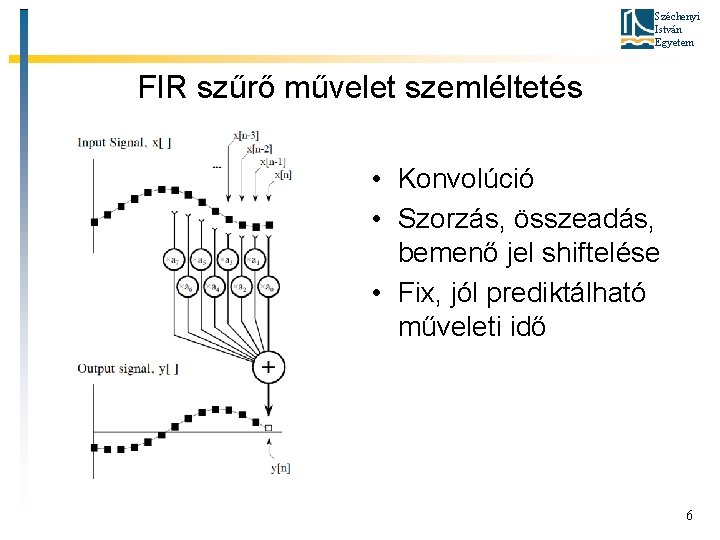

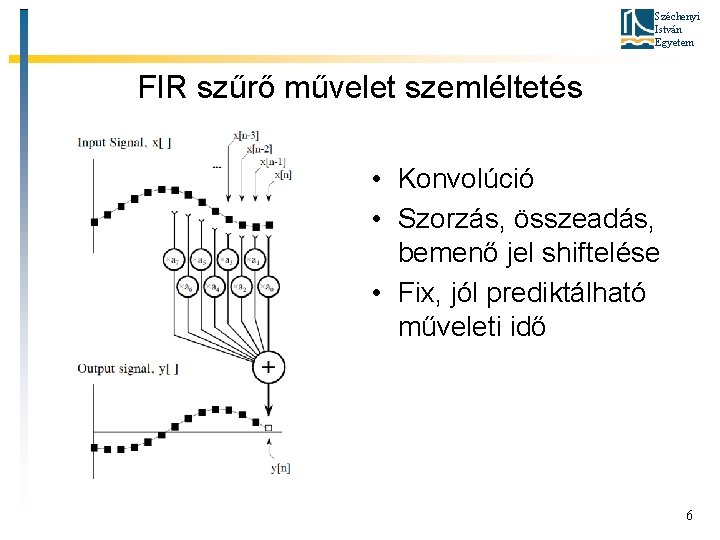

Széchenyi István Egyetem FIR szűrő művelet szemléltetés • Konvolúció • Szorzás, összeadás, bemenő jel shiftelése • Fix, jól prediktálható műveleti idő 6

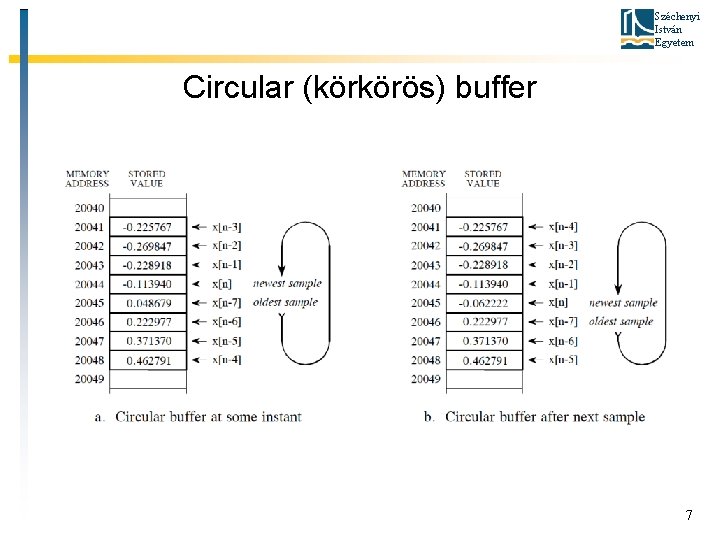

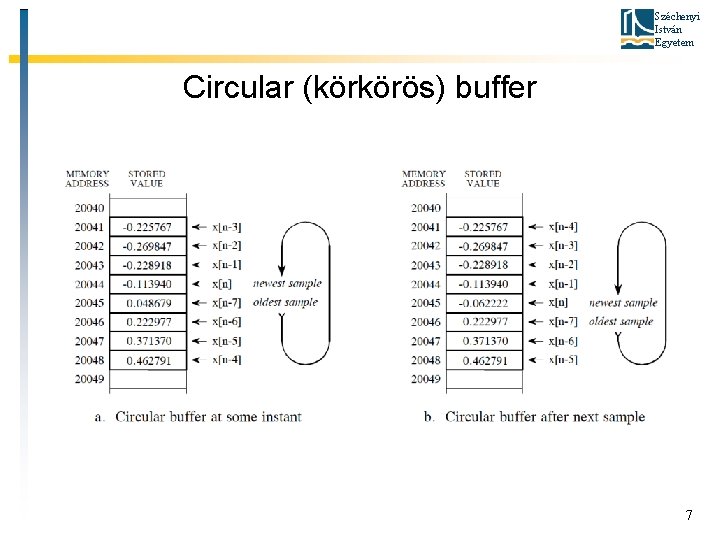

Széchenyi István Egyetem Circular (körkörös) buffer 7

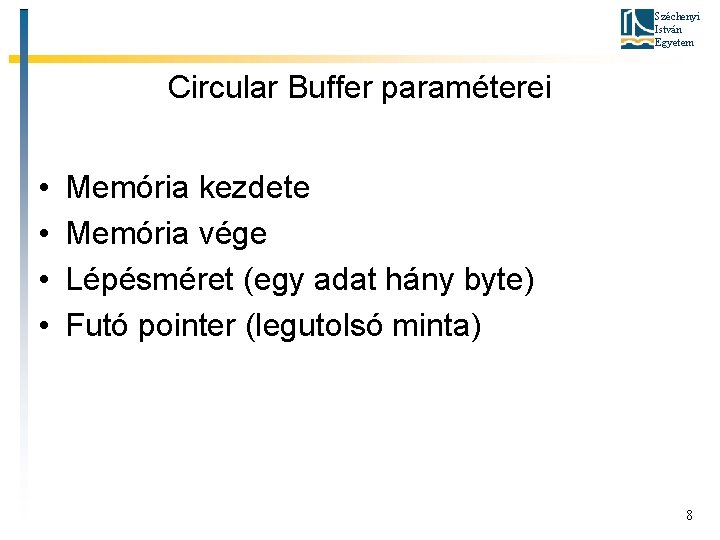

Széchenyi István Egyetem Circular Buffer paraméterei • • Memória kezdete Memória vége Lépésméret (egy adat hány byte) Futó pointer (legutolsó minta) 8

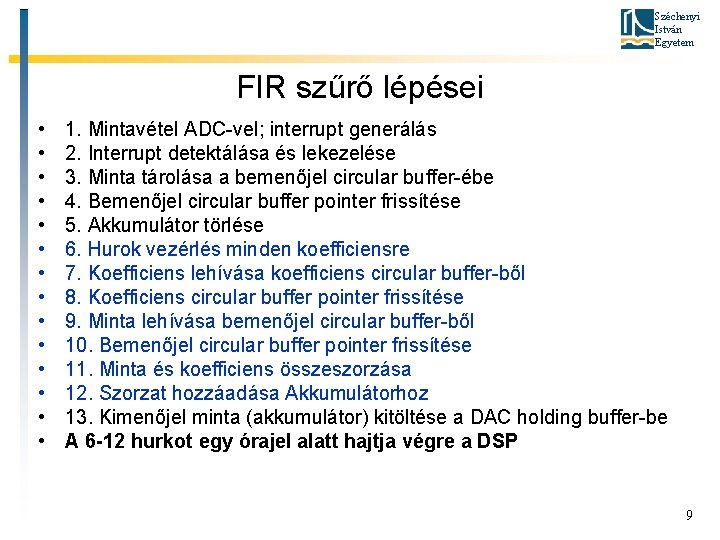

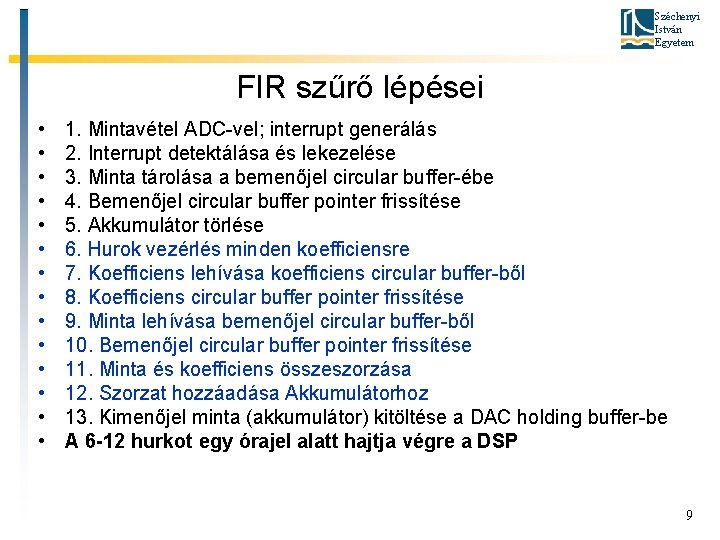

Széchenyi István Egyetem FIR szűrő lépései • • • • 1. Mintavétel ADC-vel; interrupt generálás 2. Interrupt detektálása és lekezelése 3. Minta tárolása a bemenőjel circular buffer-ébe 4. Bemenőjel circular buffer pointer frissítése 5. Akkumulátor törlése 6. Hurok vezérlés minden koefficiensre 7. Koefficiens lehívása koefficiens circular buffer-ből 8. Koefficiens circular buffer pointer frissítése 9. Minta lehívása bemenőjel circular buffer-ből 10. Bemenőjel circular buffer pointer frissítése 11. Minta és koefficiens összeszorzása 12. Szorzat hozzáadása Akkumulátorhoz 13. Kimenőjel minta (akkumulátor) kitöltése a DAC holding buffer-be A 6 -12 hurkot egy órajel alatt hajtja végre a DSP 9

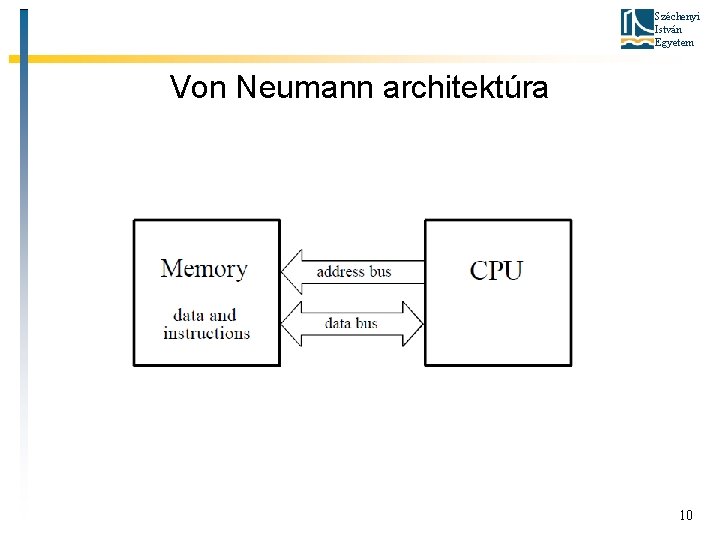

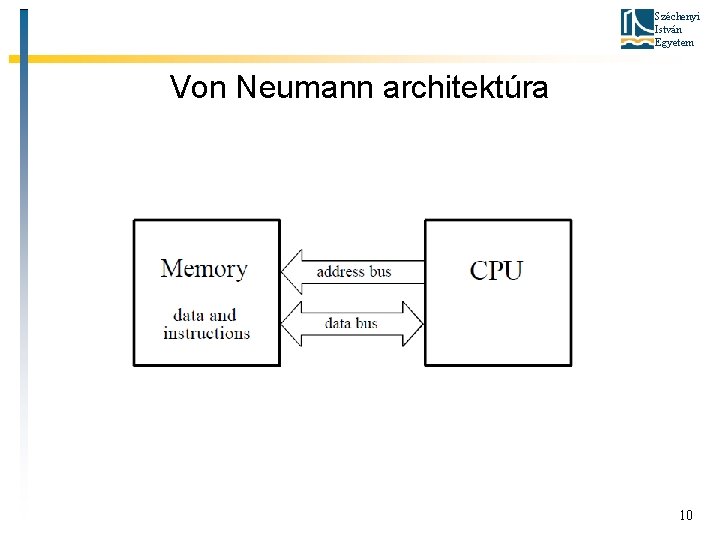

Széchenyi István Egyetem Von Neumann architektúra 10

Széchenyi István Egyetem RISC vs CISC RISC: Reduced Instruction Set • memóriaelérés csak load és store műveletek segítségével (aritmetika csak regisztereken végezhető) • egyszerűsített címzési módok • minden utasítás ugyanolyan hosszúságú • az utasításokat lehetőleg 1 órajelciklus alatt hajtsa végre • nagyszámú általános célú regiszter • nincs mikroprogramozás 11

Széchenyi István Egyetem RISC vs CISC: Complex Instruction Set • összetett memóriaelérési módok • összetett címzési módok • bonyolult utasításkészlet • változó utasítás hossz • változó utasítás végrehajtási idő • kevés de speciális regiszter • mikroprogramozás 12

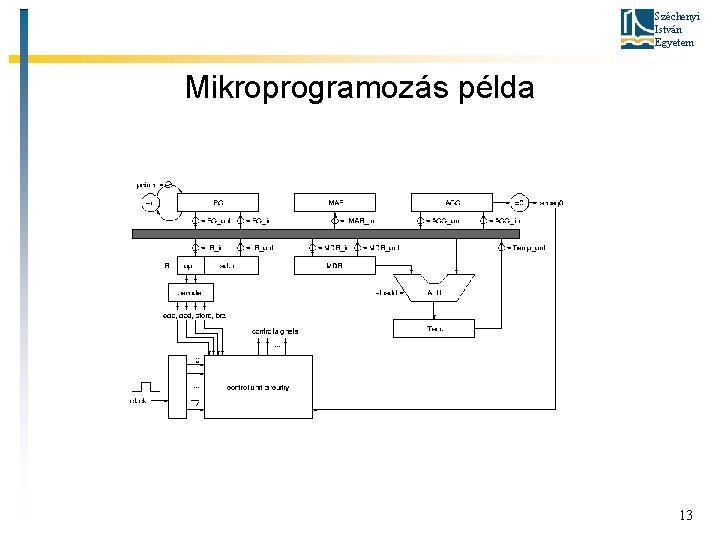

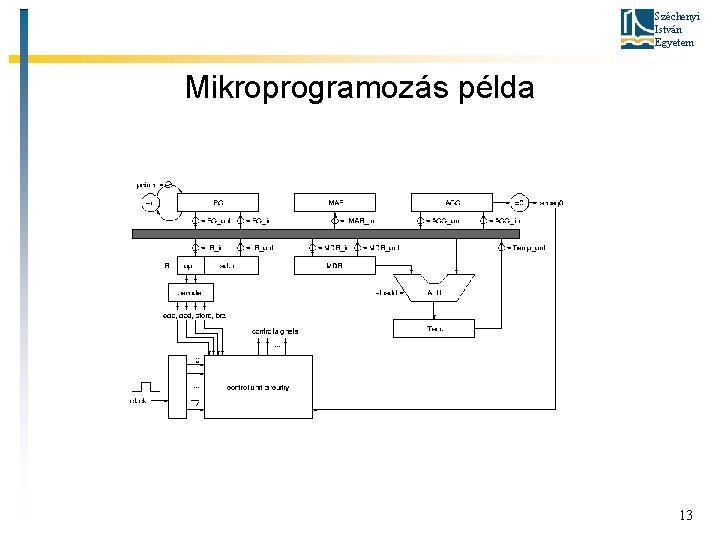

Széchenyi István Egyetem Mikroprogramozás példa 13

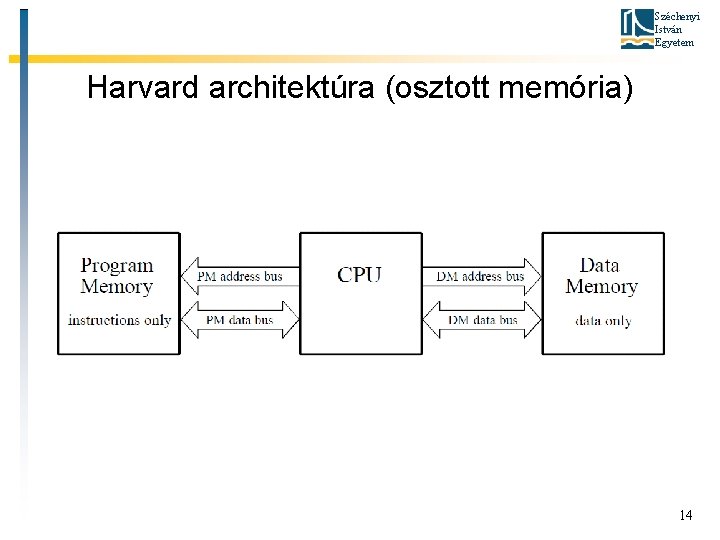

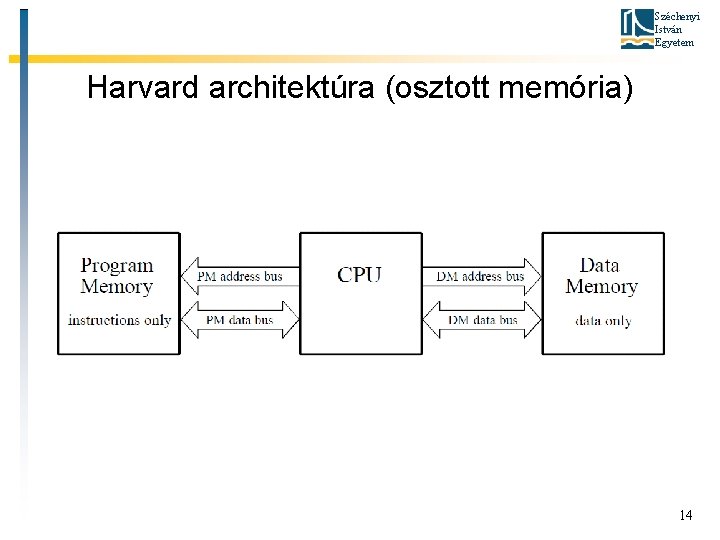

Széchenyi István Egyetem Harvard architektúra (osztott memória) 14

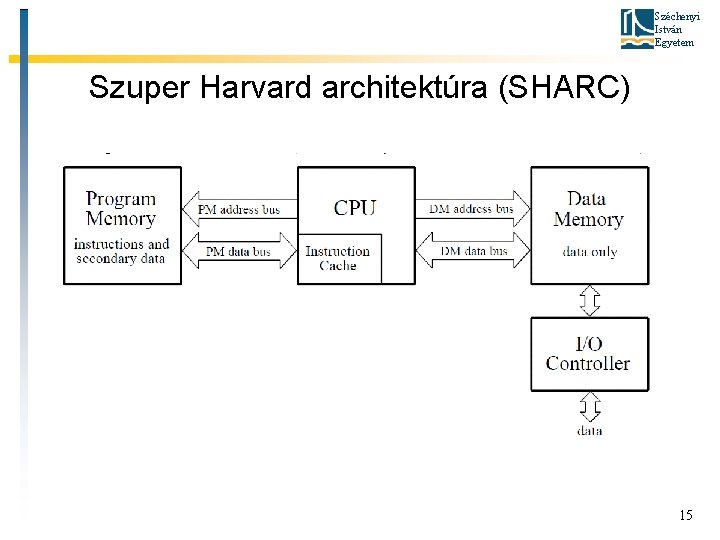

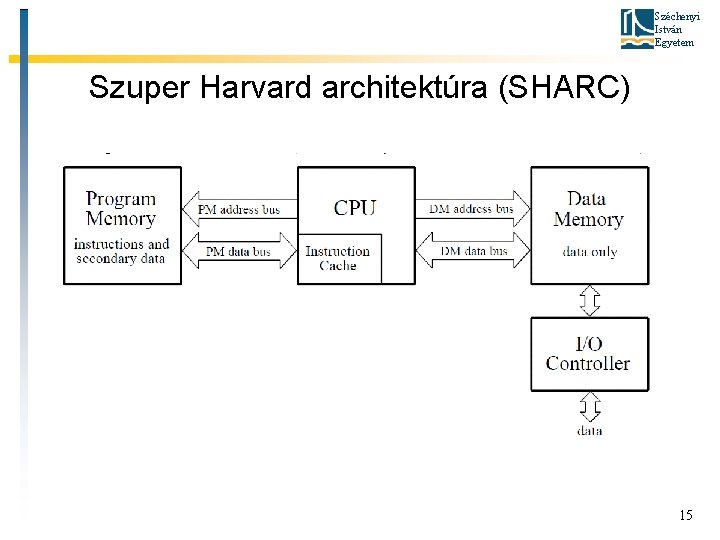

Széchenyi István Egyetem Szuper Harvard architektúra (SHARC) 15

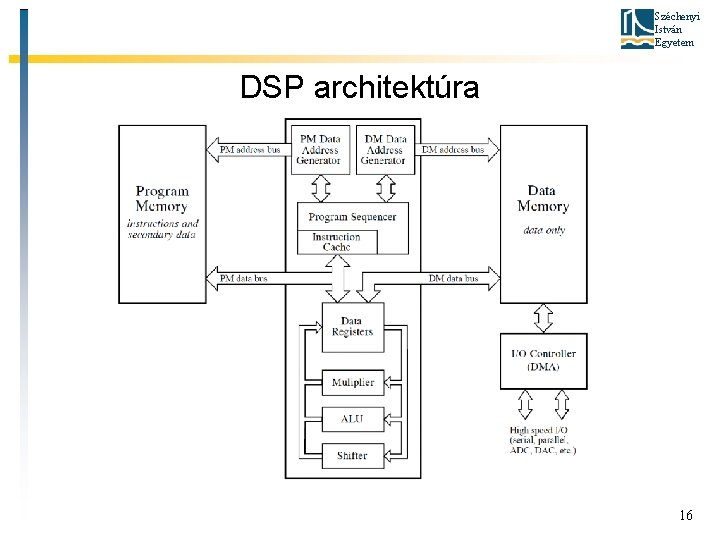

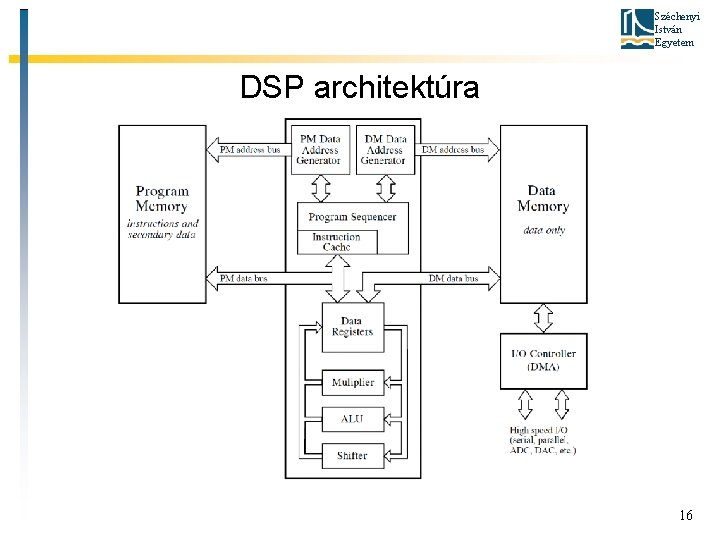

Széchenyi István Egyetem DSP architektúra 16

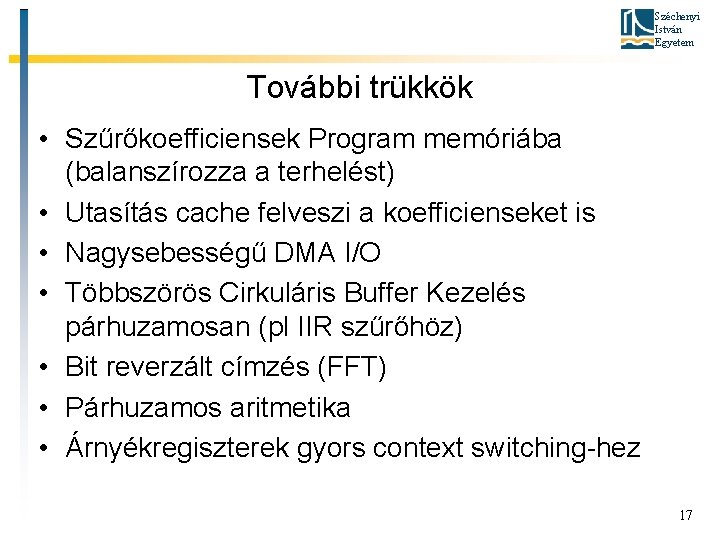

Széchenyi István Egyetem További trükkök • Szűrőkoefficiensek Program memóriába (balanszírozza a terhelést) • Utasítás cache felveszi a koefficienseket is • Nagysebességű DMA I/O • Többszörös Cirkuláris Buffer Kezelés párhuzamosan (pl IIR szűrőhöz) • Bit reverzált címzés (FFT) • Párhuzamos aritmetika • Árnyékregiszterek gyors context switching-hez 17

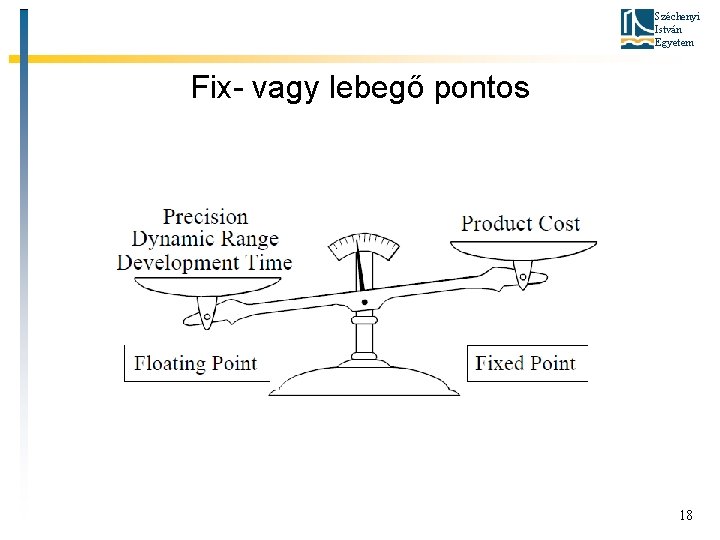

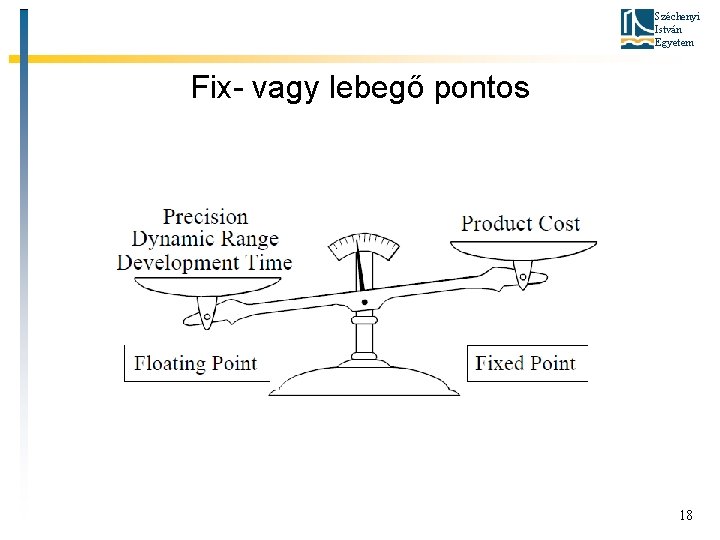

Széchenyi István Egyetem Fix- vagy lebegő pontos 18

Széchenyi István Egyetem DSP szoftver 19

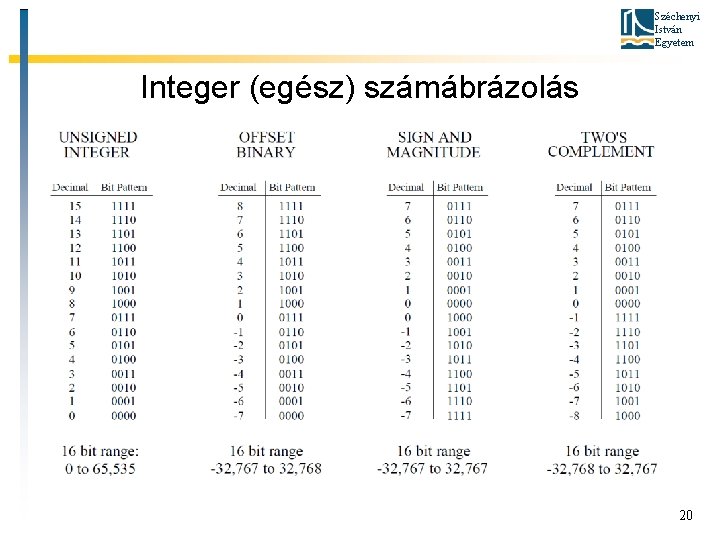

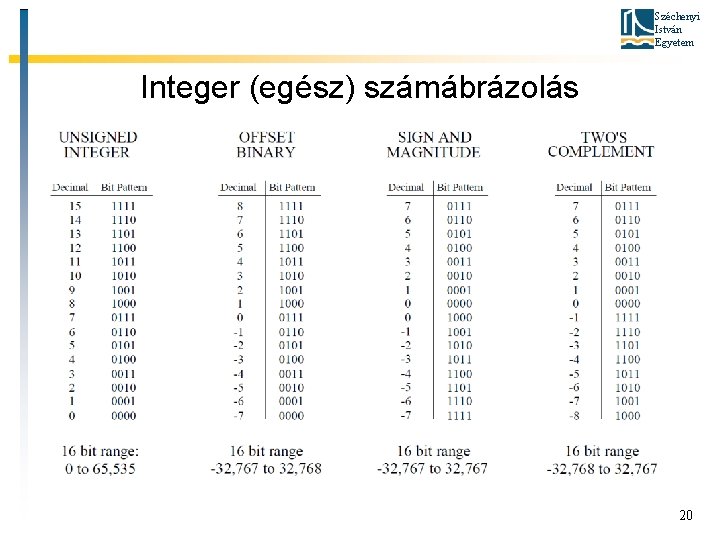

Széchenyi István Egyetem Integer (egész) számábrázolás 20

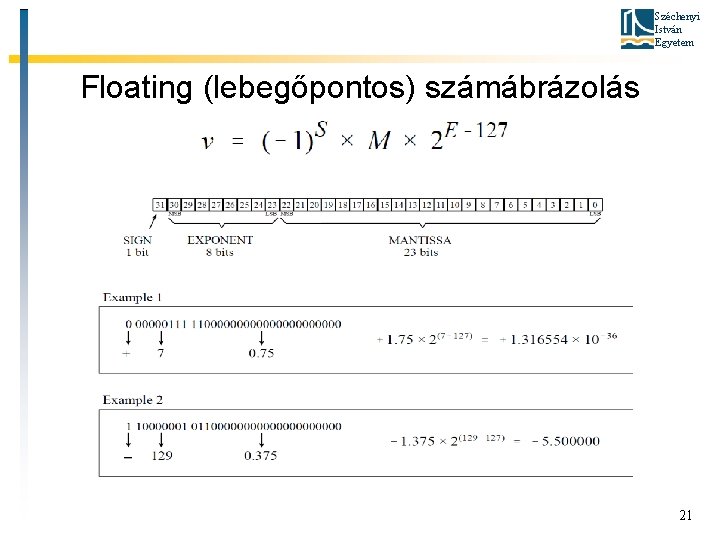

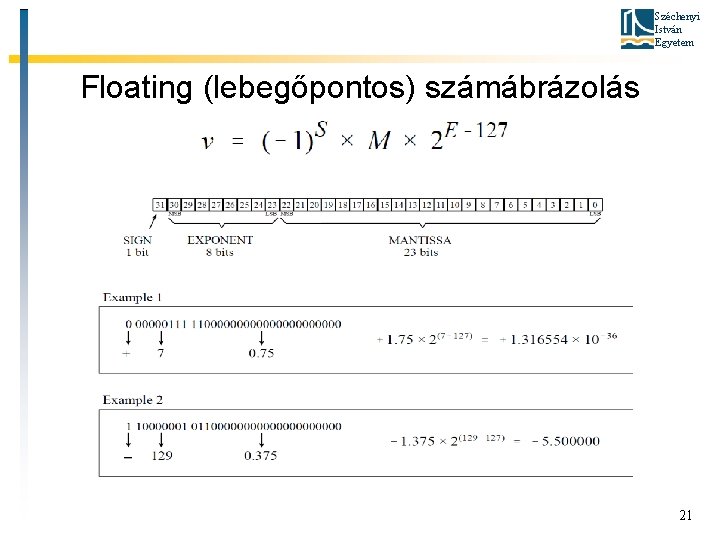

Széchenyi István Egyetem Floating (lebegőpontos) számábrázolás 21

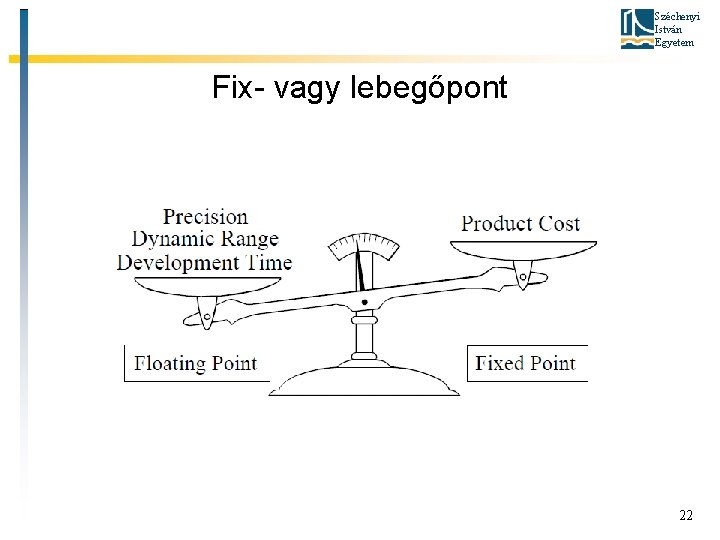

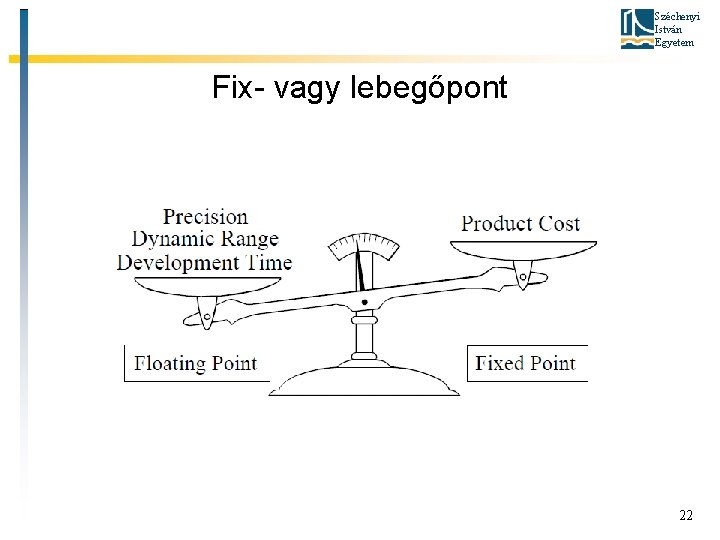

Széchenyi István Egyetem Fix- vagy lebegőpont 22

Széchenyi István Egyetem Megfontolások • • Lebegőpont kevesebb „zaj” Lebegőpont egyszerűbb programozás Fixpont olcsóbb Döntő a bemenő adat felbontás (12 -14 bitnél a határ) 23

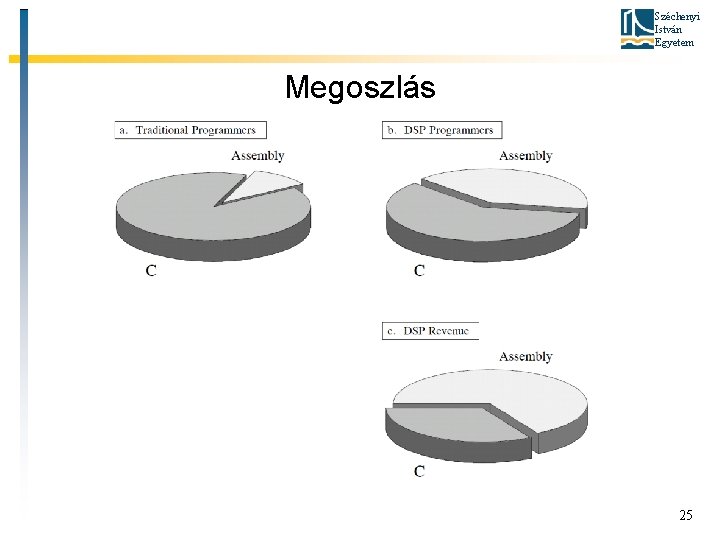

Széchenyi István Egyetem Programozás • Assembler: jobban kézbentartható, optimalizáltabb kód • C, C++ gyorsabb fejlesztési idő, újrafelhasználhatóság, team munka 24

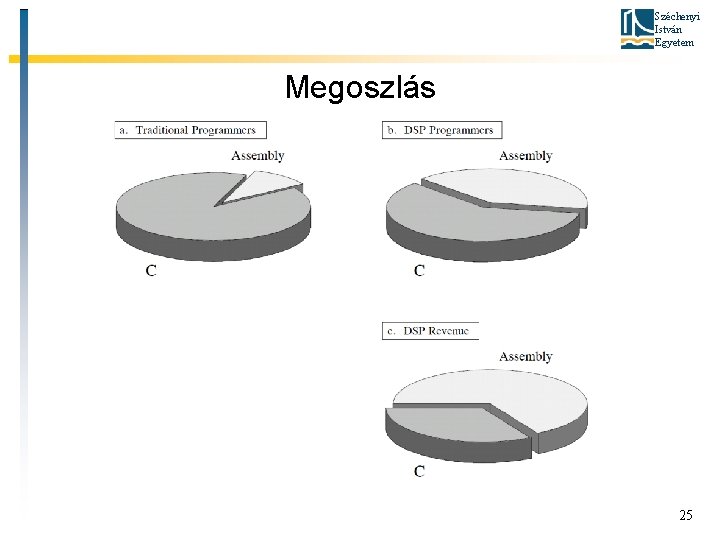

Széchenyi István Egyetem Megoszlás 25

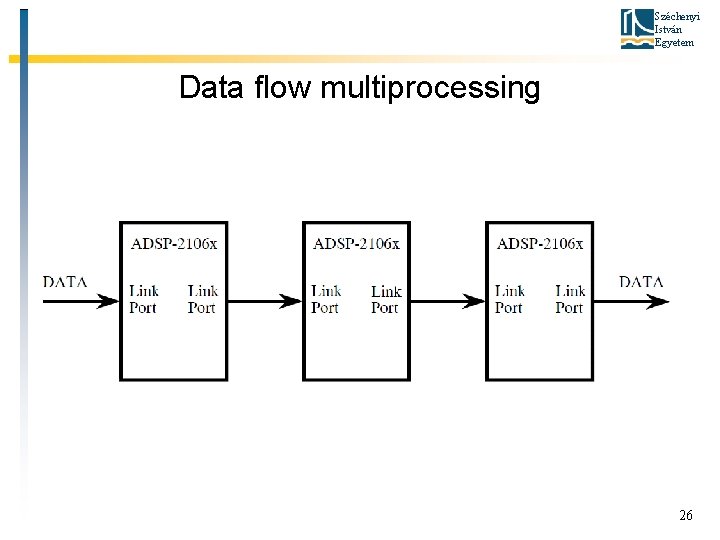

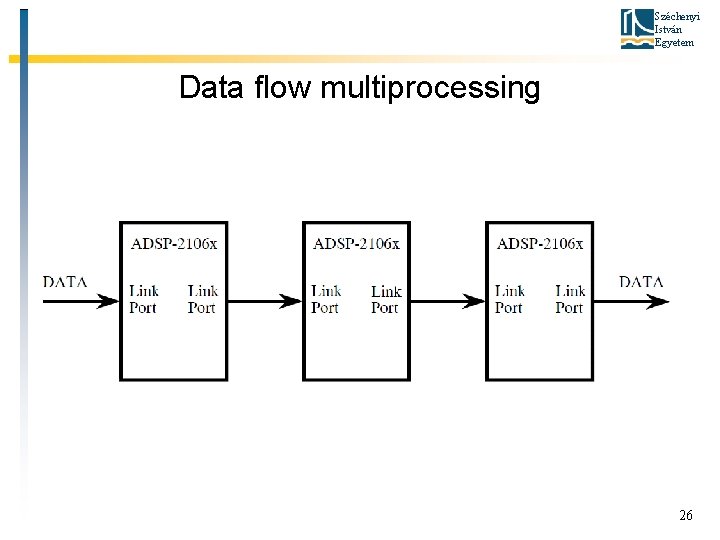

Széchenyi István Egyetem Data flow multiprocessing 26

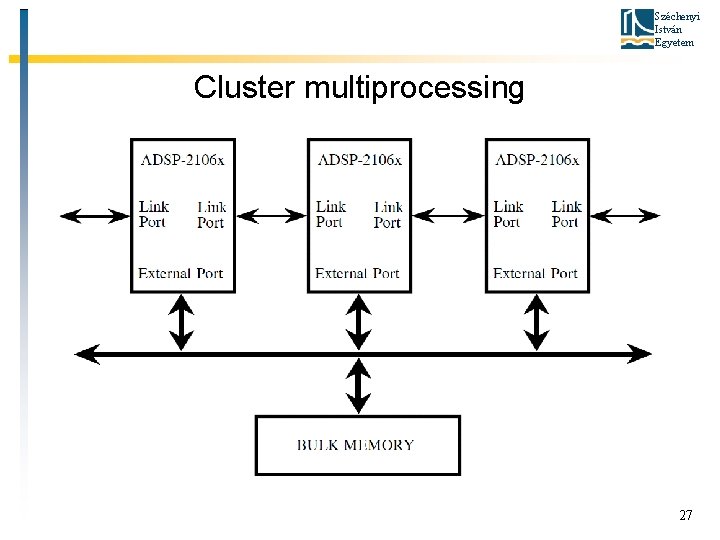

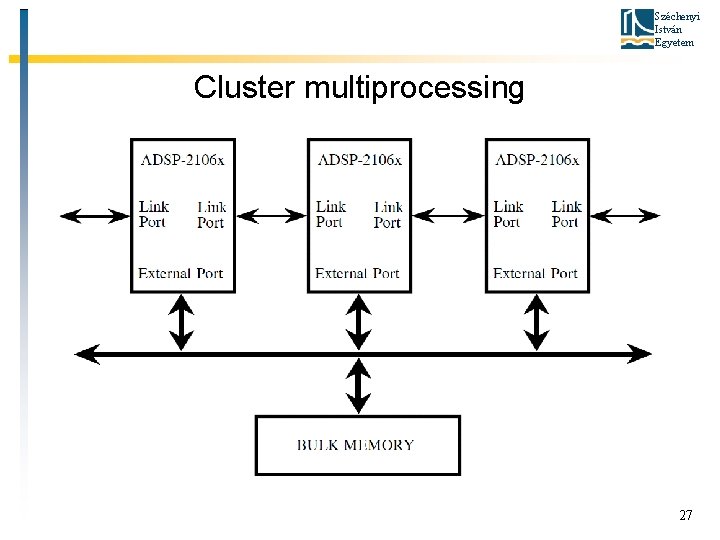

Széchenyi István Egyetem Cluster multiprocessing 27

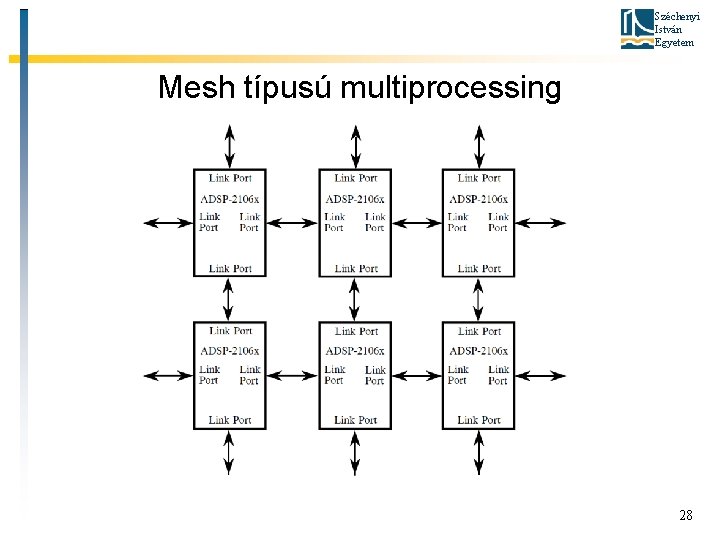

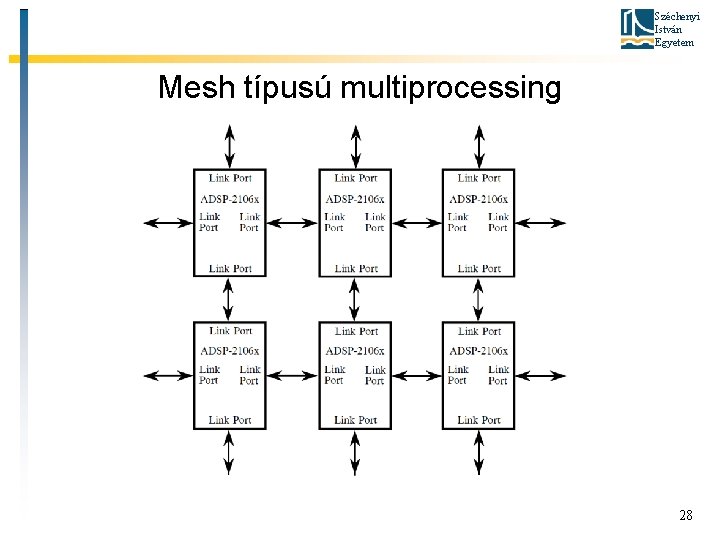

Széchenyi István Egyetem Mesh típusú multiprocessing 28

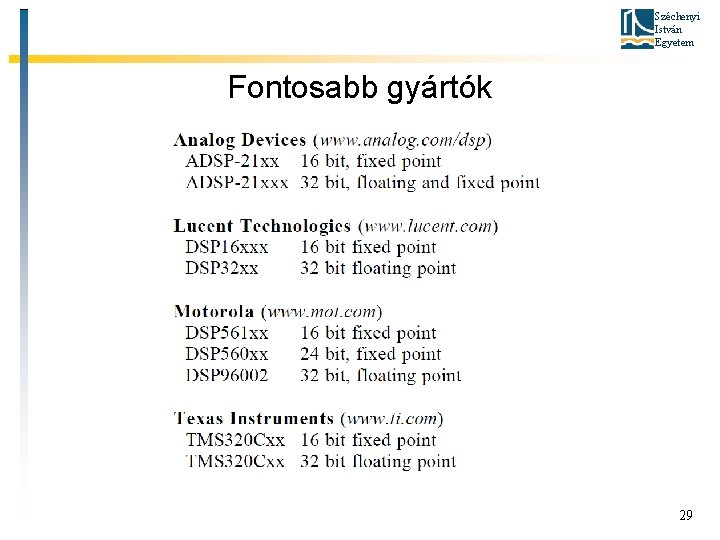

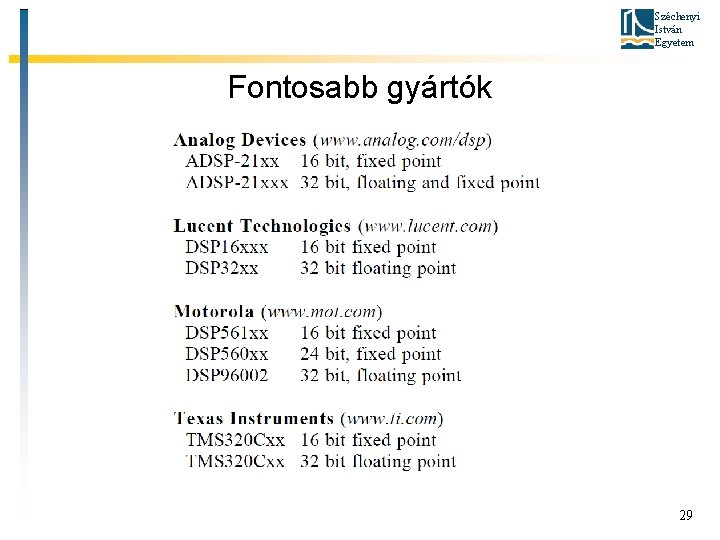

Széchenyi István Egyetem Fontosabb gyártók 29

Széchenyi István Egyetem Speciális DSP perifériák • Timerek • Esemény Manager – Input Capture – Output Compare • PWM 30

Széchenyi István Egyetem ARM = Advanced Risc Machine 31

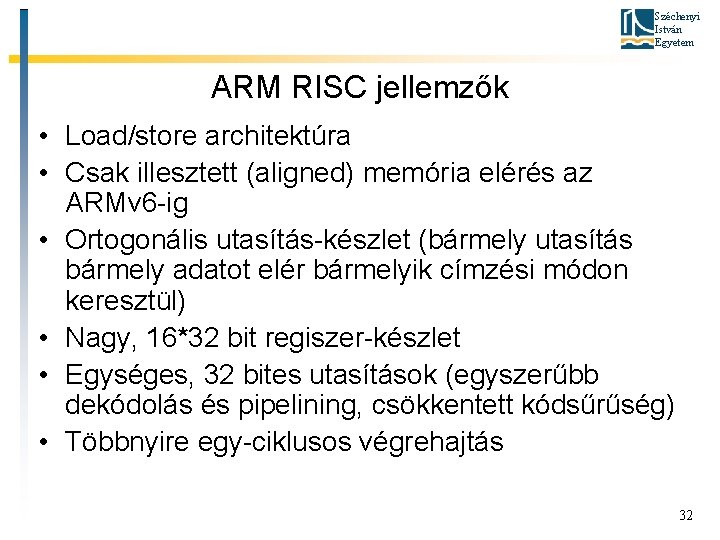

Széchenyi István Egyetem ARM RISC jellemzők • Load/store architektúra • Csak illesztett (aligned) memória elérés az ARMv 6 -ig • Ortogonális utasítás-készlet (bármely utasítás bármely adatot elér bármelyik címzési módon keresztül) • Nagy, 16*32 bit regiszer-készlet • Egységes, 32 bites utasítások (egyszerűbb dekódolás és pipelining, csökkentett kódsűrűség) • Többnyire egy-ciklusos végrehajtás 32

Széchenyi István Egyetem ARM egyedi jellemzők • A legtöbb utasításhoz feltételes végrehajtás, így csökkentve az elágazás idejét és kompenzálva az elágazás predikátor hiányát. • Az aritmetikai utasítások a feltételes kód regisztert csak kérésre módosítják • 32 -bites léptető, amellyel teljesítmény-veszteség nélkül lehet aritmetikai és cím-számolásokat végezni • Erőteljes indexelt címzési módok • Egyszerű, de gyors, két prioritási szintű megszakítás-alrendszer cserélt regiszerkészlettel 33

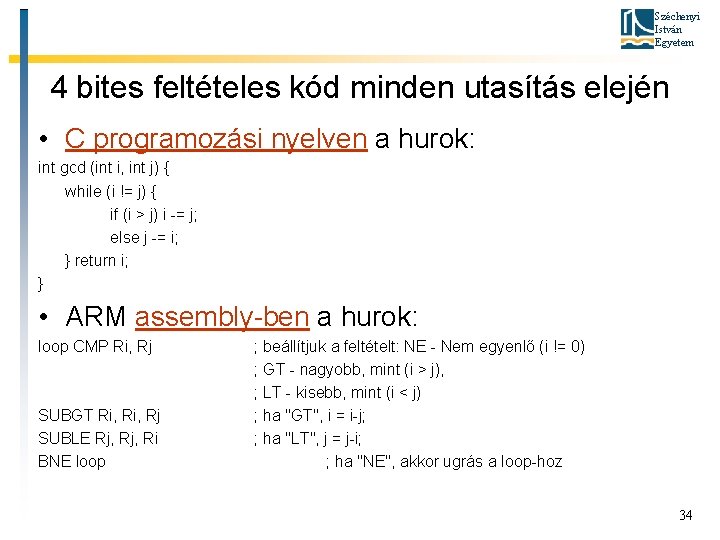

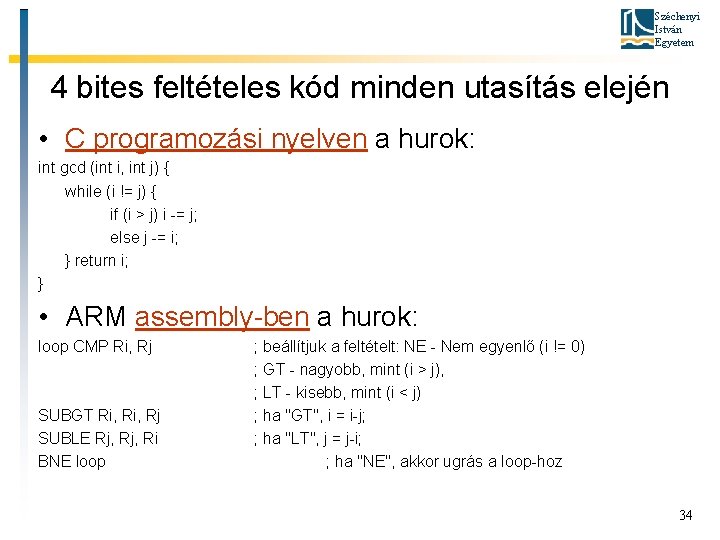

Széchenyi István Egyetem 4 bites feltételes kód minden utasítás elején • C programozási nyelven a hurok: int gcd (int i, int j) { while (i != j) { if (i > j) i -= j; else j -= i; } return i; } • ARM assembly-ben a hurok: loop CMP Ri, Rj SUBGT Ri, Rj SUBLE Rj, Ri BNE loop ; beállítjuk a feltételt: NE - Nem egyenlő (i != 0) ; GT - nagyobb, mint (i > j), ; LT - kisebb, mint (i < j) ; ha "GT", i = i-j; ; ha "LT", j = j-i; ; ha "NE", akkor ugrás a loop-hoz 34

Széchenyi István Egyetem Léptető és forgató utasítások beépíthetősége a += (j << 2); egy-ciklusú utasítás lehet az ARM-on. ADD Ra, Rj, LSL #2 35

Széchenyi István Egyetem ARM érdekességek • • Utasításszámláló relatív címzés Elő és utónövekményes címzési módok Bár már régi de utasításkészlete alig nőtt Az ARM 7 -ig három-szakaszú pipeline : begyűjtés, dekódolás és végrehajtás. • ARM 9, öt-szakaszú pipeline. • A nagyobb teljesítmény elérésének módjai között szerepel a gyorsabb összeadó és a kiterjedtebb predikációs rendszer. 36

Széchenyi István Egyetem Koprocesszorok • Szoftveresen címezhetőek az MCR, MRC, MRRC és MCRR utasításokkal. • A koprocesszor-tér 16 logikai koprocesszorra van felosztva (0 -tól 15 -ig számozva), a 15 -ös (cp 15) tipikus vezérlési funkcióknak (gyorsítótár és memória kezelés) van fenntartva. • Az ARM alapú gépekben a perifériák általában a fizikai regisztereik ARM memóriájába, a koprocesszor-térbe vagy egy, a processzorhoz kapcsolódó másik eszköz (sín) való leképezésével kapcsolódnak a processzorhoz. • A koprocesszor elérés kisebb késleltetésű, így néhány periféria (például az XScale megszakítás-vezérlő) mindkét módon elérhető (memórián és koprocesszoron keresztül). 37

Széchenyi István Egyetem Thumb • Tömörített utasítás-készlet • 16 bites utasításokat használ (de továbbra is 32 bites adatokkal dolgozik). • Kevesebb funkció érhető el. Például csak az elágazások köthetők feltételhez és sok opkód nem érheti el a CPU regisztereit. • Növekszik a kódsűrűség, annak ellenére, hogy néhány művelethez több utasítás szükséges. • A beágyazott hardware-eknek többnyire kevesebb a 32 bites adatútja, a többi 16 bites, vagy még vékonyabb • Ebben az esetben van értelme a Thumb code-ra fordításának, majd a CPU-t inkább igénybe vevő részeket kézzel átírni a 32 bites nem Thumb utasításkészlettel, és utóbbiakat a 32 -bites busz szélességű memóriába elhelyezni. • Az első Thumb utasítás dekóderrel készült processzor az ARM 7 TDMI volt. Az ARM 9 és a későbbiek (ideértve az XScale-t is) rendelkeznek ilyen értelmezővel. 38

Széchenyi István Egyetem DSP Enhancement utasítások • Az ARM digitális jelfeldolgozásra és multimédiás programokra fejlesztéseként néhány új utasítással egészítették ki. • Ezt az ARMv 5 TE és ARMv 5 TEJ nevekben az "E" jelöli. • Különböző variációk az előjeles szorzásra, telített összeadásra és kivonásra és a vezető nullák számolására. 39

Széchenyi István Egyetem Jazelle • A Jazelle DBX (közvetlen bytekód futtatás) technológia segítségével néhány ARM architektúra képes Java bytekódot futtatni az ARM és Thumb futtatási módok mellett. Néhány bytekódot gyorsítva futtat, a többit szoftverkérésekkel hajtja végre. • Az első Jazelle-t támogató processzor az ARM 926 EJ- volt: a névben szereplő J jelöli a Jazelle-képességet. • Főként mobiltelefonokban használják, így gyorsítva a Java ME játékok és programok futását. 40

Széchenyi István Egyetem Thumb-2 • A Thumb-2, az ARM 1156 core-ban, 2003 -ban debütáló technológia • Thumb 16 bites utasításkészletét egészíti ki 32 bites utasításokkal, hogy az utasítás-készlet átfogóbb legyen. • A Thumb-2 a Thumb kódsűrűségével és 32 -bites memóriával rendelkező ARM utasítás-készlet sebességével bír. • A Thumb-2 mind az ARM mind a Thumb utasítás-készletet kiegészíti új utasításokkal, így például bit-mező módosításokkal, ugrótáblákkal (elágazási tábla) és feltételes futtatással. • Minden ARMv 7 chip támogatja a Thumb-2 utasítás-készletet. Néhány chip, mint például a Cortex-M 3 csak a Thumb-2 -t támogatja. • Más Cortex és ARM 11 sorozatú chipek támogatják az "ARM utasítás-készlet módot" és a "Thumb-2 utasítás-készlet módot". 41

Széchenyi István Egyetem Thumb Futtatási környezet (Thumb. EE) • A Thumb. EE (esetleg Thumb-2 EE), a 2005 -ben bejelentett, majd a Cortex-A 8 processzorban debütáló, Jazelle RCT néven ismert technológia. • A Thumb. EE a Thumb-2 utasításkészletét egészíti ki úgy, hogy az alkalmas legyen futási időben létrehozott kód futtatására (pl. : Just-intime compilation ("Pont időben fordítás")) megfelelően kezelt futtatási környezetekben. • A Thumb. EE cél-nyelvei között megtalálható a Limbo, a [Java], a C#, a Perl és a Python, továbbá a segítségével a JIT fordítók teljesítmény-veszteség nélkül képesek rövidebb kódot előállítani. • A Thumb. EE nyújtotta új szolgáltatások között megtalálható a minden írás/olvasás műveletkor lefutó automatikus null pointer ellenőrzés (tömb határ-ellenőrzésnél hasznos), az r 8 -r 15 regiszterek (ezekben tárolódik a Jazelle/DBX Java virtuális gép állapota) elérhetősége, és az ún. handler-ek ("kezelők": gyakran meghívott kódok) feltételhez kötése (így a magas szintű programozási nyelvek szolgáltatásai (mint például a memória-allokáció) egyszerűen megvalósíthatók). 42

Széchenyi István Egyetem Advanced SIMD • Az Advanced SIMD (Továbbfejlesztett Egy utasítás több adat), a NEON néven ismert technológia a média és jelfeldolgozás gyorsítására kínál utasításokat. • Egy 10 MHz-en futó NEON proceszor képes MP 3 hang dekódolására, egy 13 MHz-es pedig a GSM-eknél használt AMR (Adaptive Multi-Rate) kodek használatára. • Az ASIMD új utasításokból, új regiszter-készletből és külön futtató hardware-ből áll. Támogatja a 8, 16, 32 ill. 64 bites egészeket és az egyszeres pontosságú lebegőpontos értékeket, amelyeket SIMD módon kezel így audió/videó/grafika- és játékszámításokra alkalmas. • A NEON-ban a SIMD párhuzamosan akár 16 művelet elvégzésére is képes. 43

Széchenyi István Egyetem VFP • A VFP egy az ARM-hoz készült segédprocesszor, az IEEE 754 szabványnak megfelelő lebegőpontos aritmetikát támogató, alacsony költségű megoldás. • A VFP széles körben felhasználhatóan támogatja a lebegőpontos számításokat, így például használható PDA-kban, nyomtatókban, set -top boxokban, autókban, okos telefonokban, hangtömörítésre és kitömörítésre, 3 -dimenziós grafikára valamint digitális audió feldolgozásra. • Alkalmas továbbá egyszerűbb vektor-műveletekre, így SIMD párhuzamosságra. Ez jól kihasználható grafikai és jelfeldolgozó programoknál, a kód rövidítése és így az átviteli képesség növelése révén. • Az ARM-hoz készültek további lebegőpontos és/vagy SIMD segédprocesszorok (pl. : FPA, FPE, iw. MMXt). Ezek az VFP funkcionalitását biztosít(hat)ják, de azzal nem opkód-kompatibilisek. 44

Széchenyi István Egyetem Trust Zone • ARMv 6 KZ-től kezdődően találhatók meg az architektúrákban. • Olcsó alternatívát jelent a dedikált biztonsági mag beépítése mellett. • Két virtuális processzort szolgáltat, hardware-alapú biztonsági rendszerrel. Így egy program két állapot (ún. világ) között váltogathat, így a megbízható világból a kevésbé megbízhatóbb világba nem kerülhetnek információk. • Ez a világ-váltás általában ortogonális a processzor további képességeivel, így mindkét világ függetlenül működhet egy rendszermagot használva. • A memória és a perifériák is észlelik ezt a váltást, így engedhetik jelszavak és egyéb titkosított adatok elérését az eszközön. • Egy tipikus felhasználási módja, hogy egy teljes értékű operációsrendszer fut a kevésbé megbízható világban, míg egy biztonságra specializált kód fut a megbízható világban. 45

Széchenyi István Egyetem Licencezés • Az ARM Ltd. nem gyárt a terveik alapján CPU-kat, hanem az architektúrákat az érdeklődő cégeknek licencezi. • Többféle licencezési módot is ajánl, az ár és az eladható daraboktól függően. • Minden ARM licenccel az ARM mag egy elkészíthető hardware leírását, teljes szoftverfejlesztői készletet (fordító, debugger, SDK) és a legyártott ARM CPU-t tartalmazó szilícium eladásának jogát adja • ARM licensszel rendelkező cégek: Analog Devices, Atmel, Broadcom, Cirrus Logic, Faraday technology, Freescale (a Motorola-ból 2004 -ben kivált cég), Fujitsu, Intel , IBM, Infineon Technologies, Nintendo, NXP Semiconductors (a Philips-ből 2006 -ban kivált cég), OKI, Samsung, Sharp, STMicroelectronics, Texas Instruments, Xilinx. 46

Széchenyi István Egyetem DFT, FFT 47

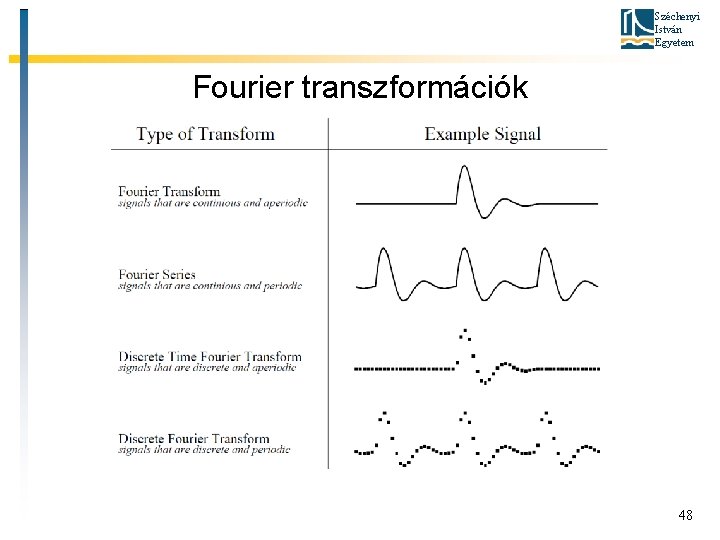

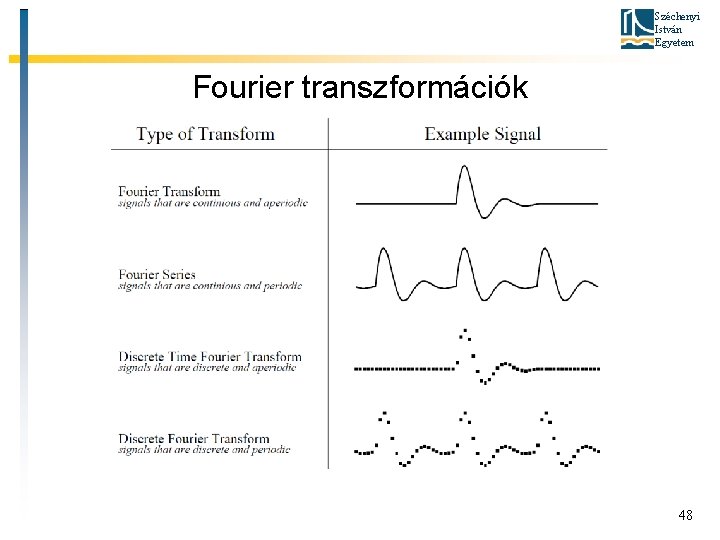

Széchenyi István Egyetem Fourier transzformációk 48

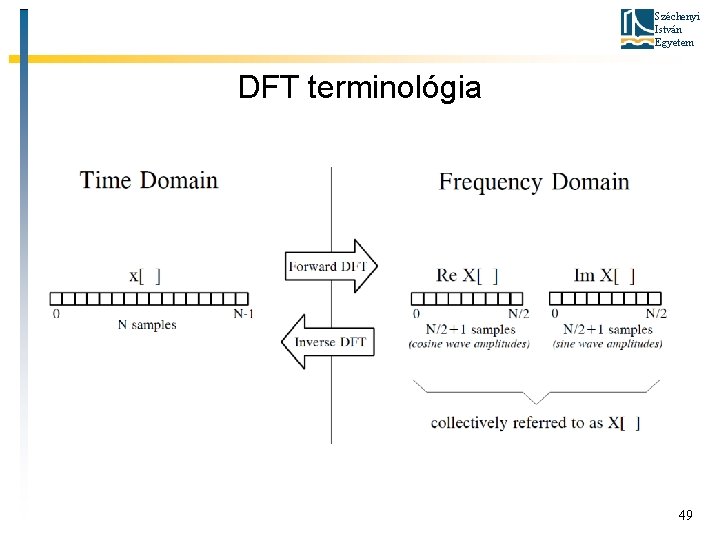

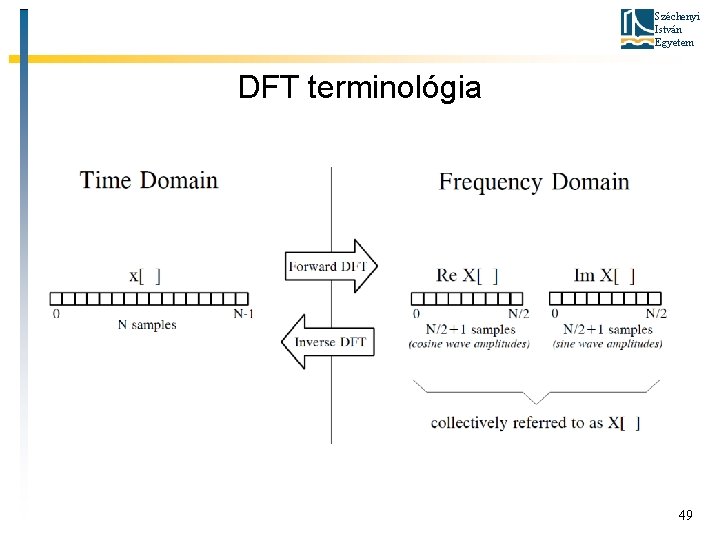

Széchenyi István Egyetem DFT terminológia 49

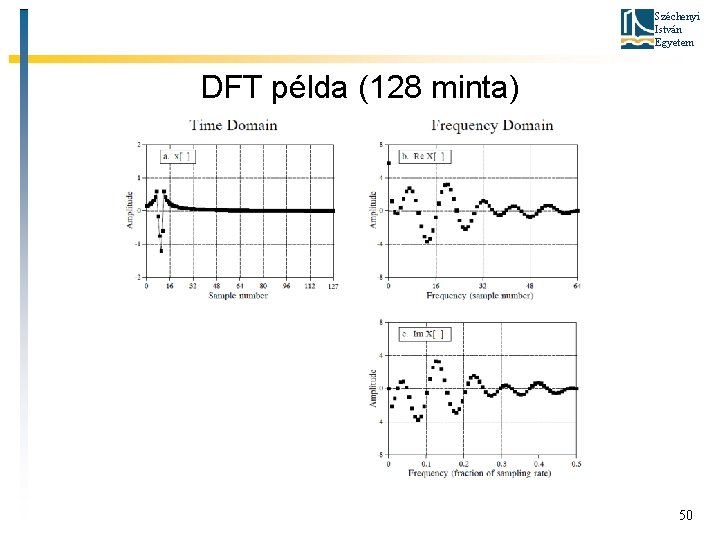

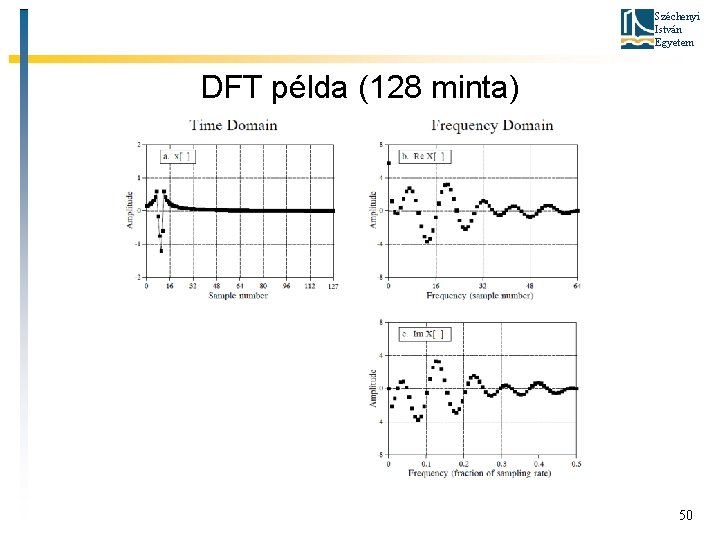

Széchenyi István Egyetem DFT példa (128 minta) 50

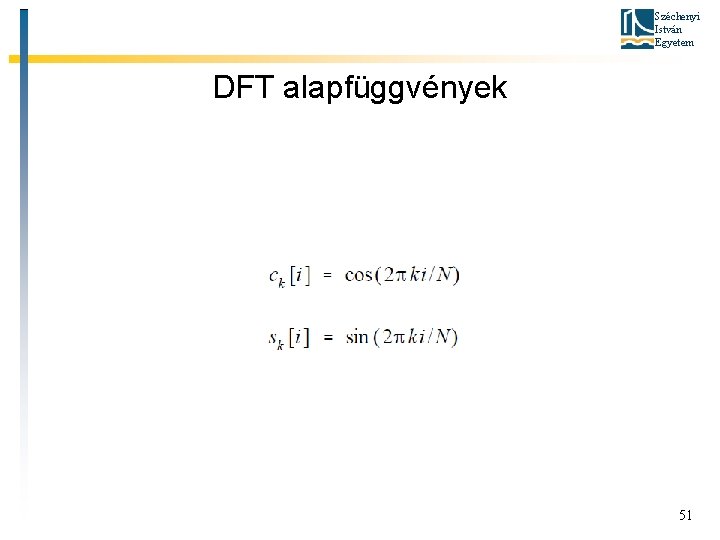

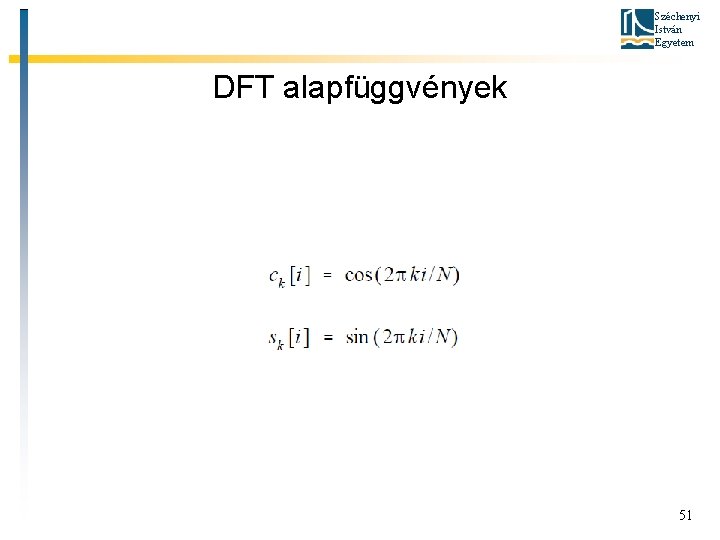

Széchenyi István Egyetem DFT alapfüggvények 51

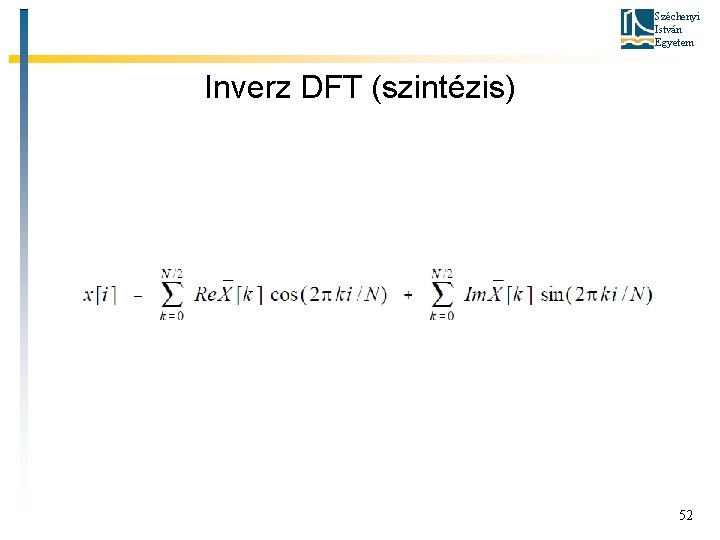

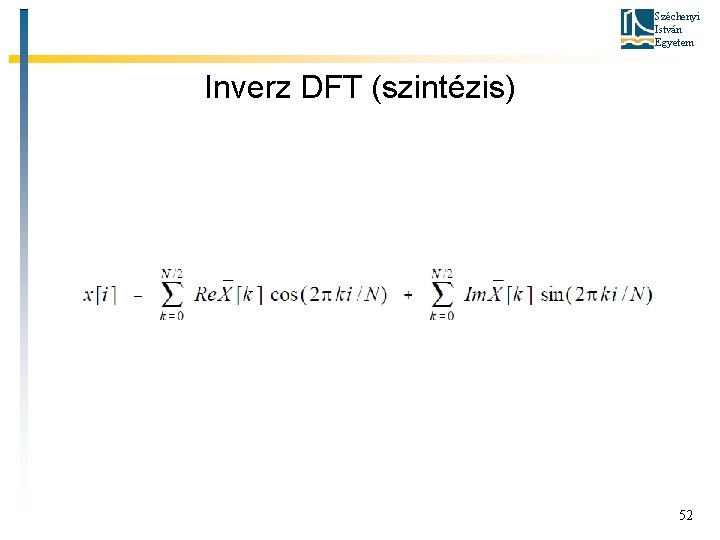

Széchenyi István Egyetem Inverz DFT (szintézis) 52

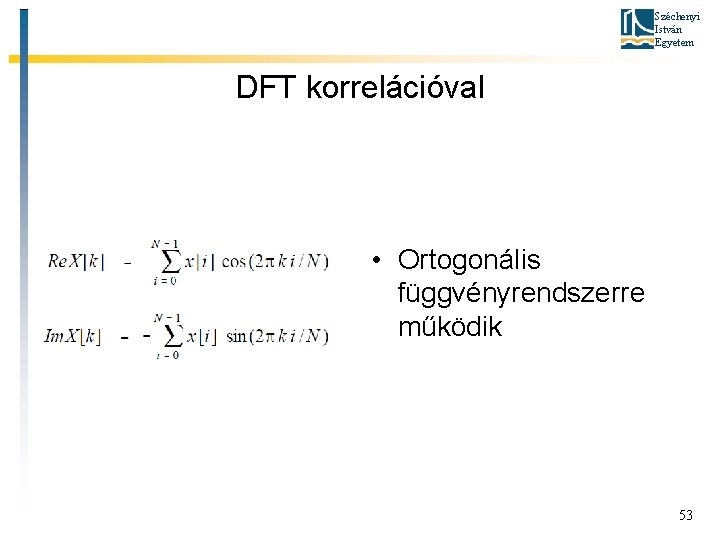

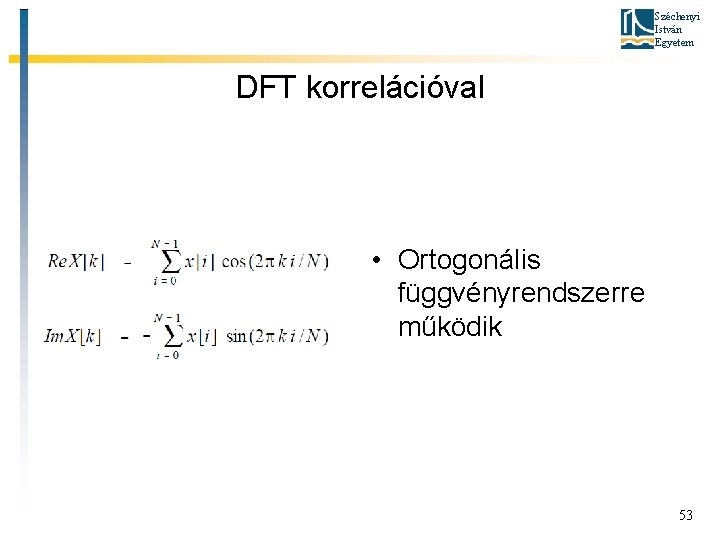

Széchenyi István Egyetem DFT korrelációval • Ortogonális függvényrendszerre működik 53

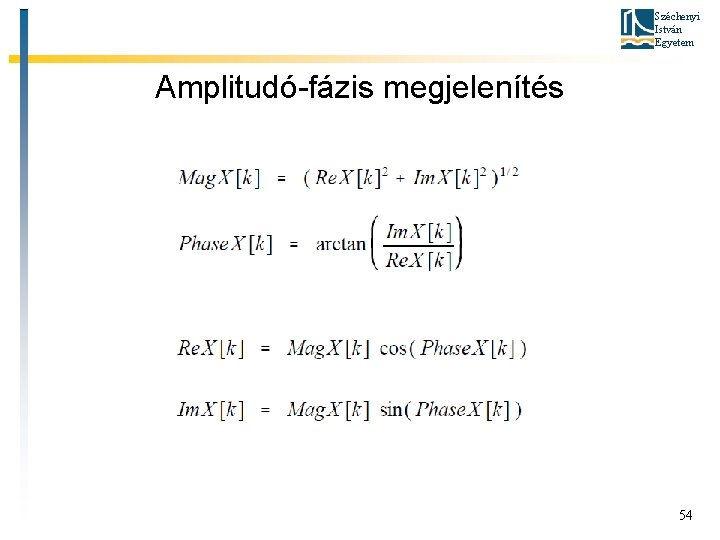

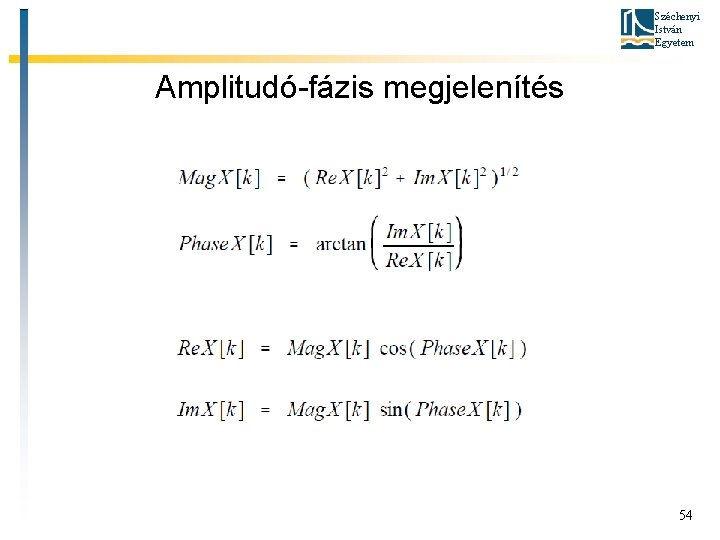

Széchenyi István Egyetem Amplitudó-fázis megjelenítés 54

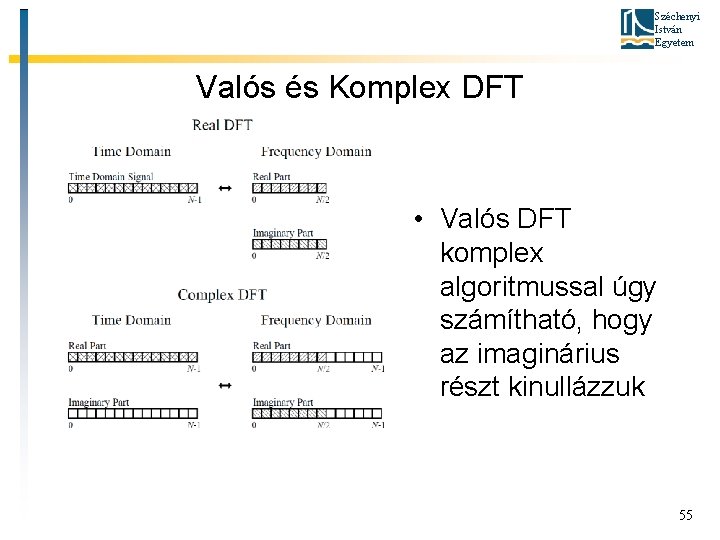

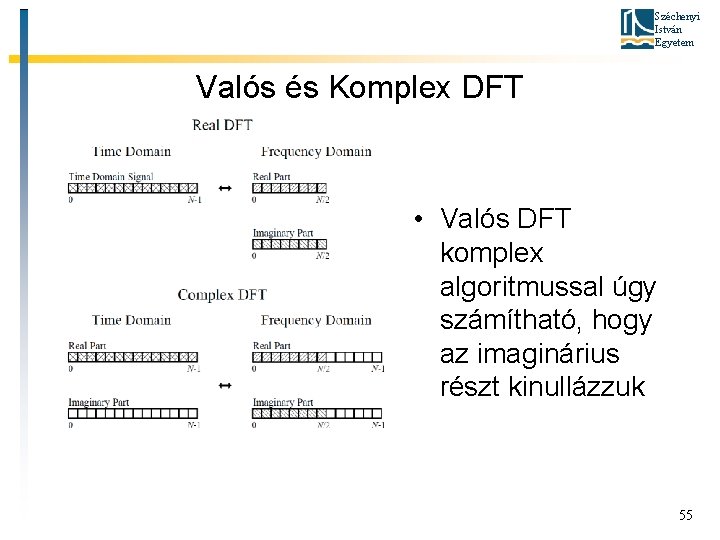

Széchenyi István Egyetem Valós és Komplex DFT • Valós DFT komplex algoritmussal úgy számítható, hogy az imaginárius részt kinullázzuk 55

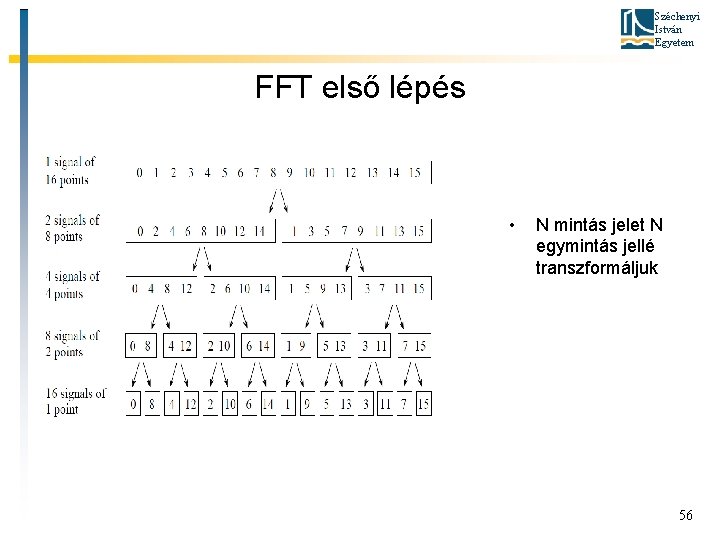

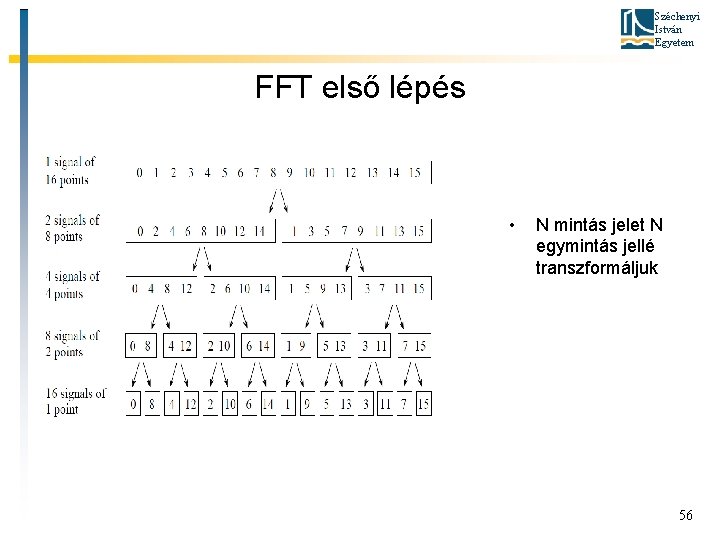

Széchenyi István Egyetem FFT első lépés • N mintás jelet N egymintás jellé transzformáljuk 56

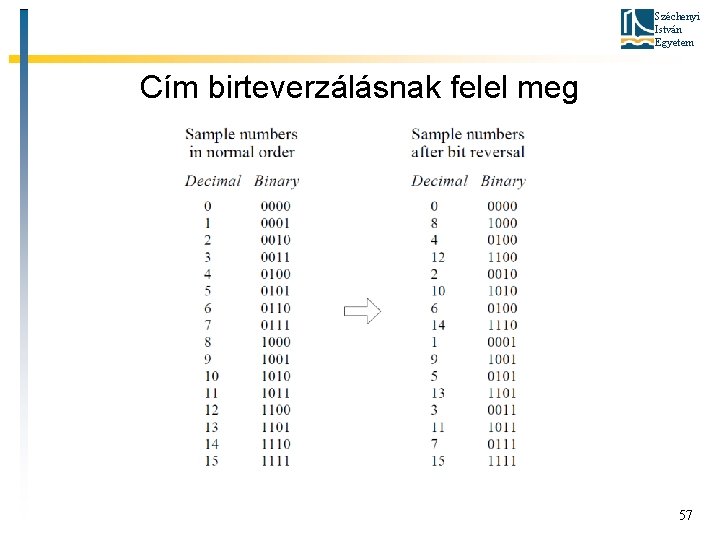

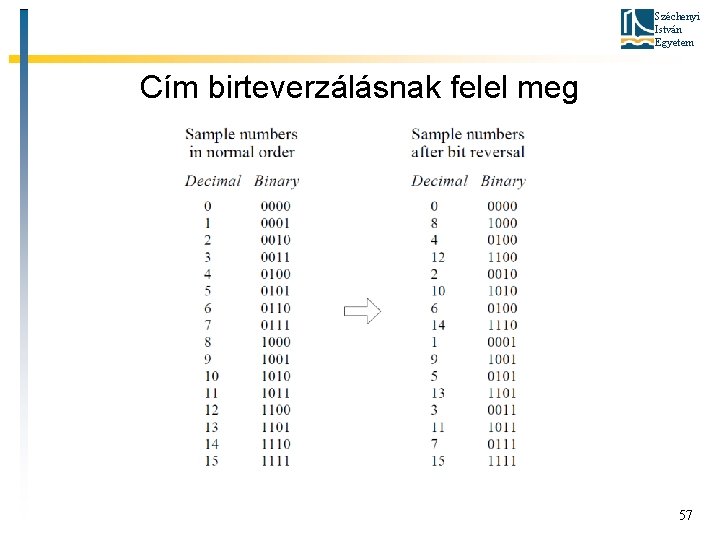

Széchenyi István Egyetem Cím birteverzálásnak felel meg 57

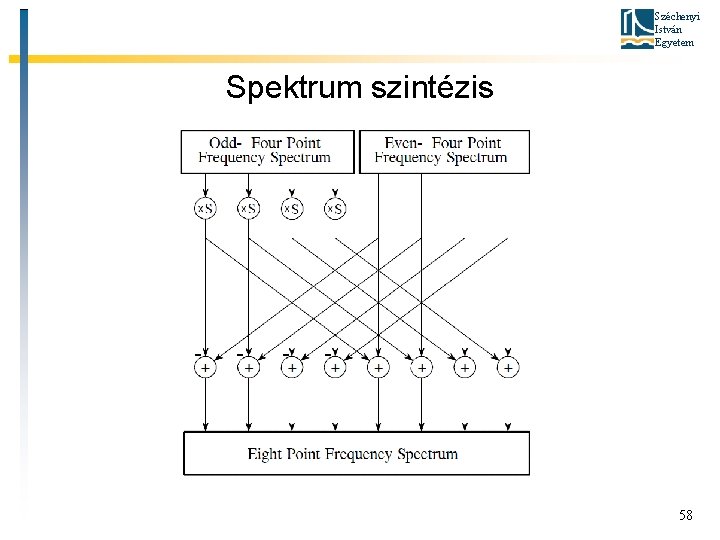

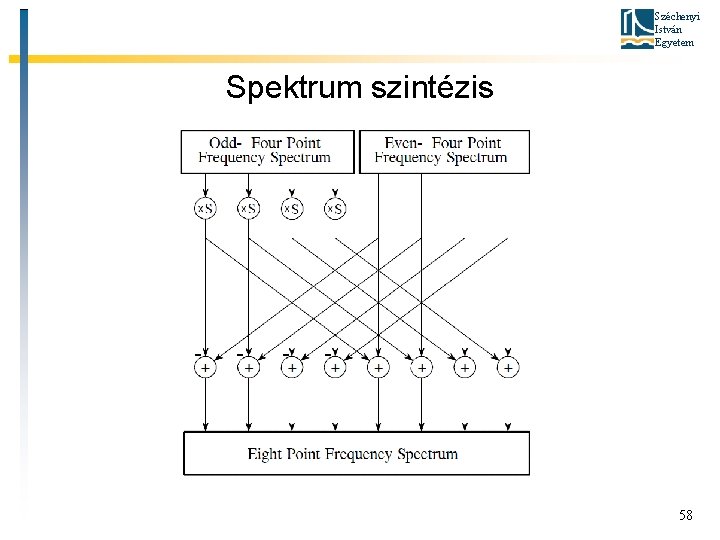

Széchenyi István Egyetem Spektrum szintézis 58

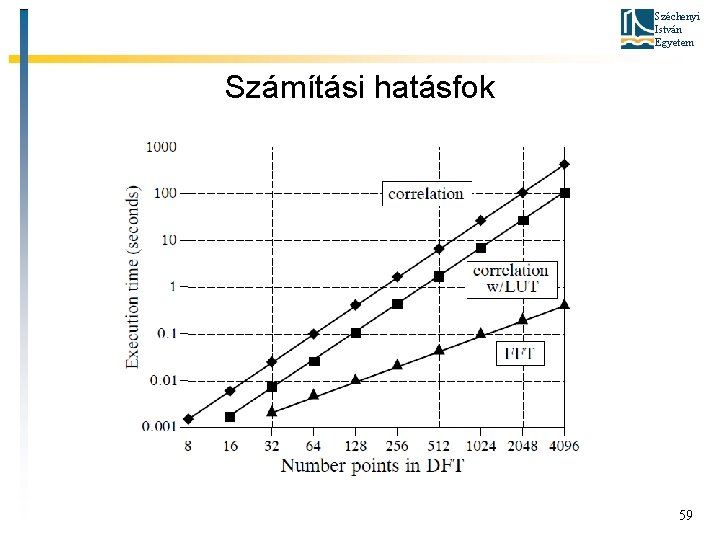

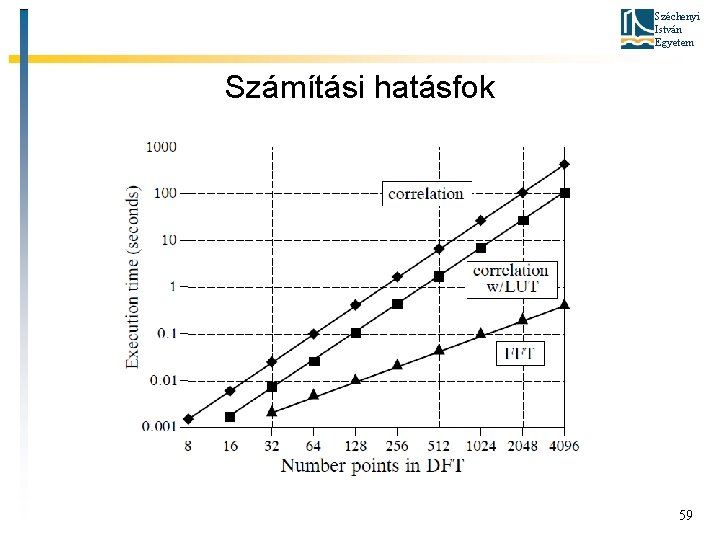

Széchenyi István Egyetem Számítási hatásfok 59

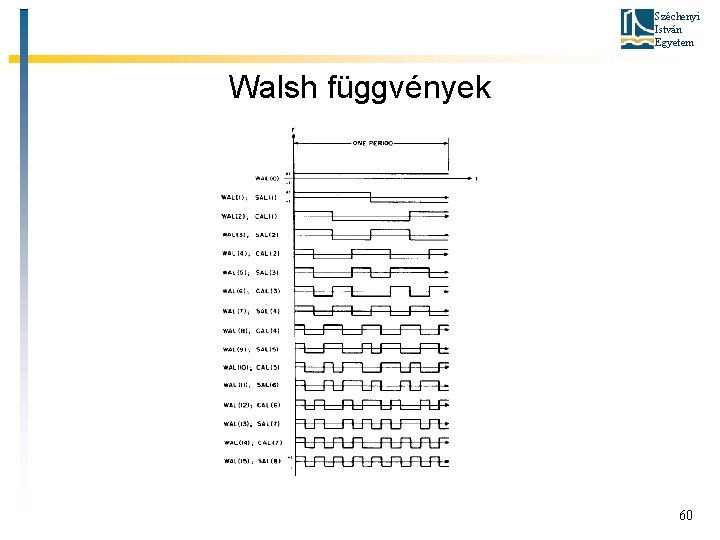

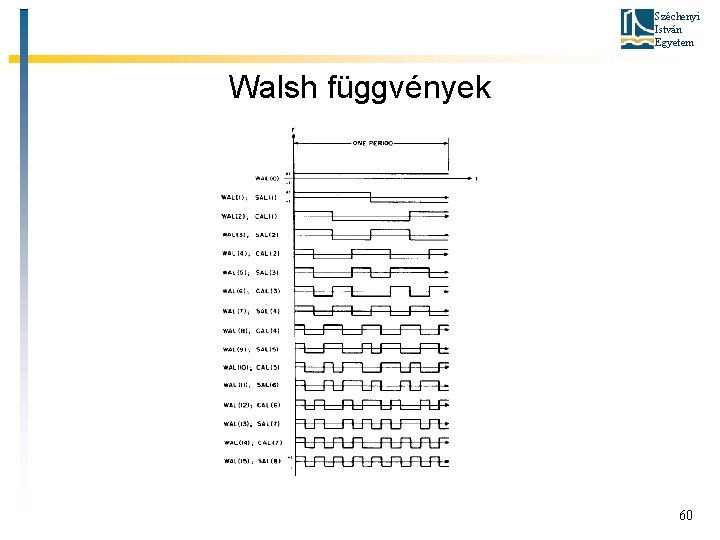

Széchenyi István Egyetem Walsh függvények 60