Szchenyi Istvn Egyetem FPGA implementcik 1 Szchenyi Istvn

- Slides: 31

Széchenyi István Egyetem FPGA implementációk 1

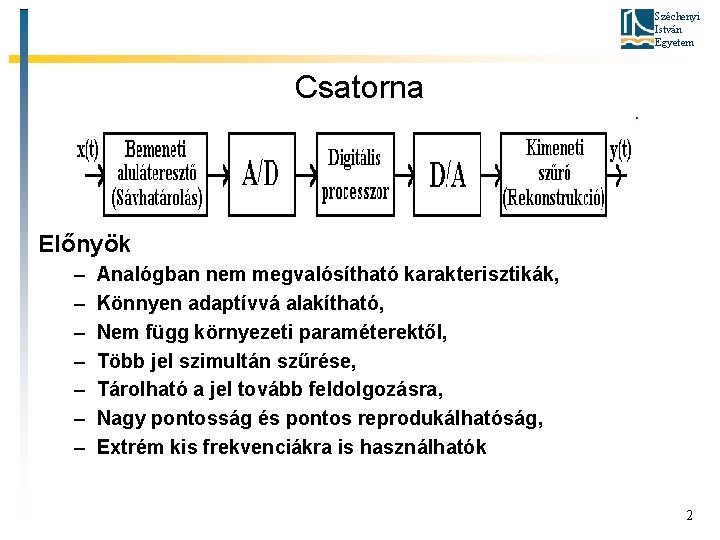

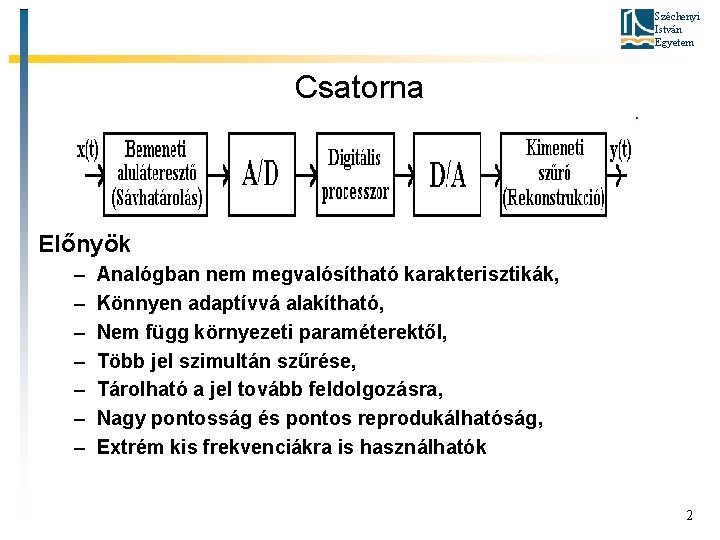

Széchenyi István Egyetem Csatorna Előnyök – – – – Analógban nem megvalósítható karakterisztikák, Könnyen adaptívvá alakítható, Nem függ környezeti paraméterektől, Több jel szimultán szűrése, Tárolható a jel tovább feldolgozásra, Nagy pontosság és pontos reprodukálhatóság, Extrém kis frekvenciákra is használhatók 2

Széchenyi István Egyetem Programozható logikák granualitása • Finom (Pilkington, vagy „kapuk tengere”) • Közepes (FPGA) • Nagy (CPLD) 3

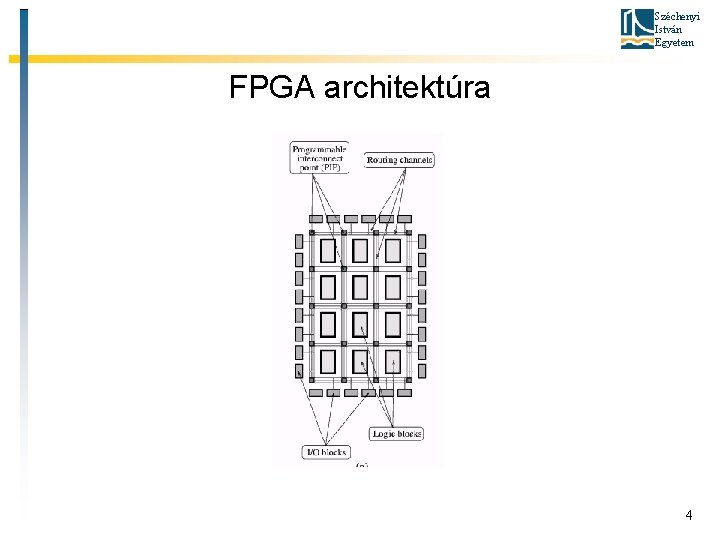

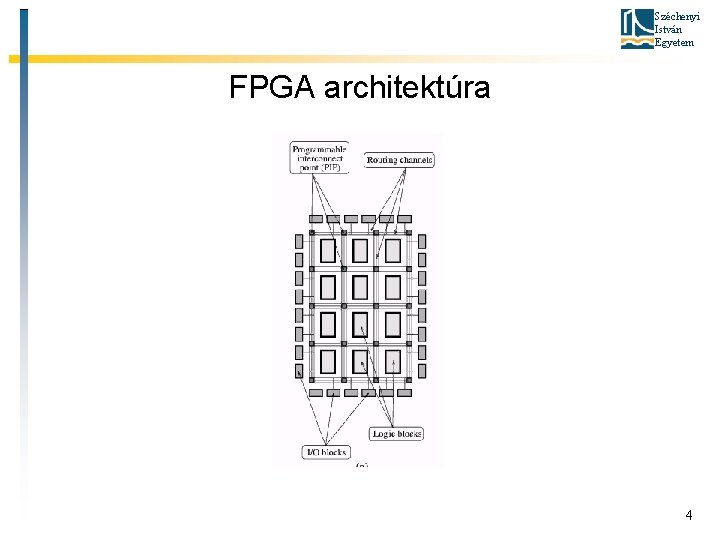

Széchenyi István Egyetem FPGA architektúra 4

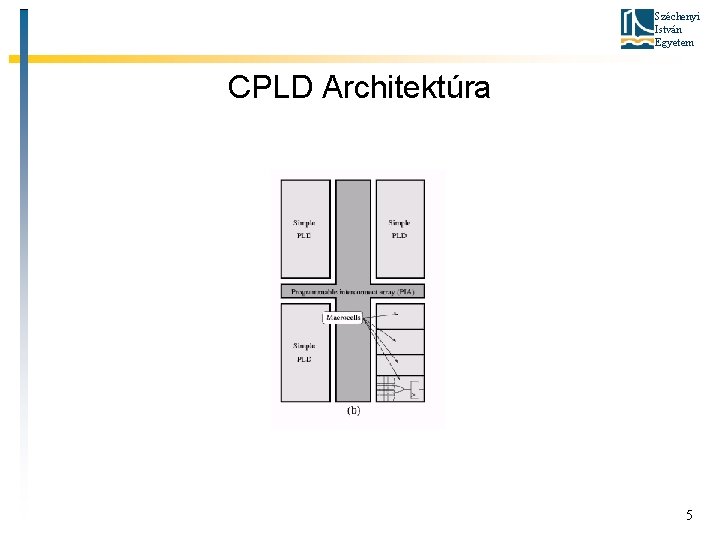

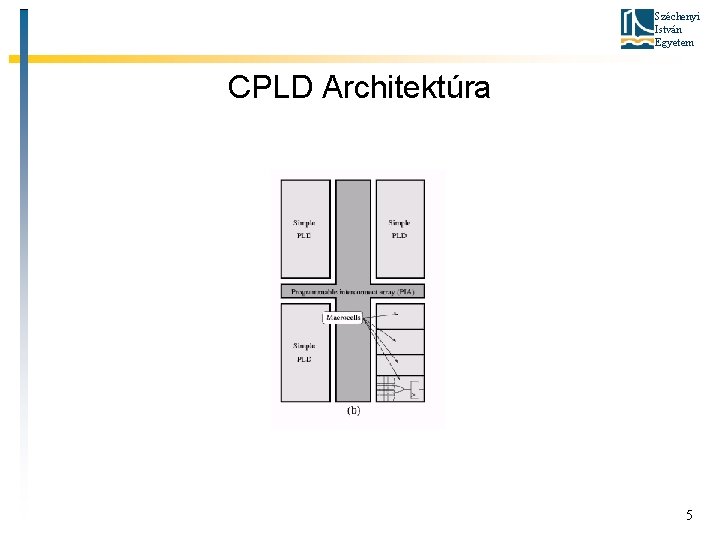

Széchenyi István Egyetem CPLD Architektúra 5

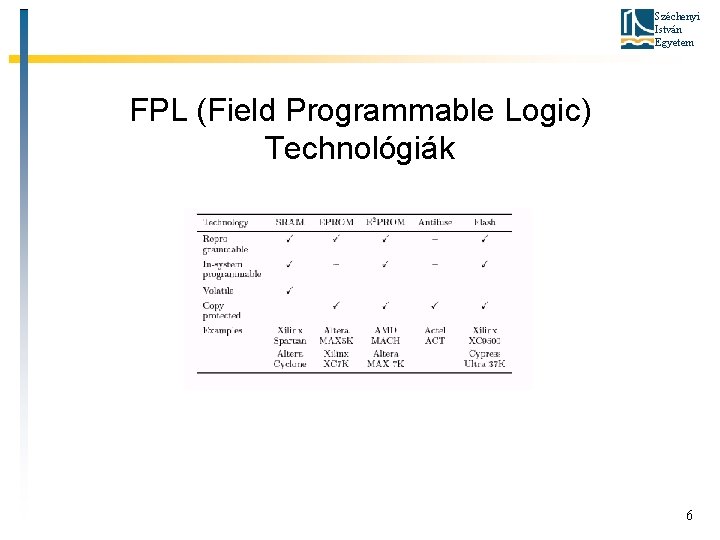

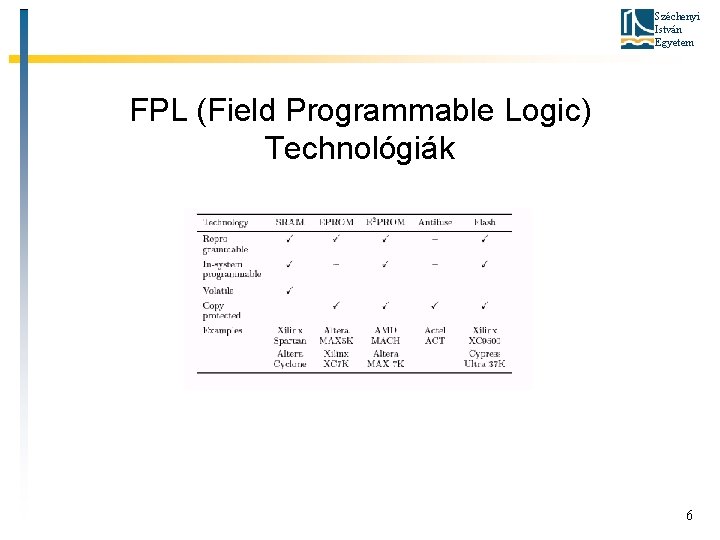

Széchenyi István Egyetem FPL (Field Programmable Logic) Technológiák 6

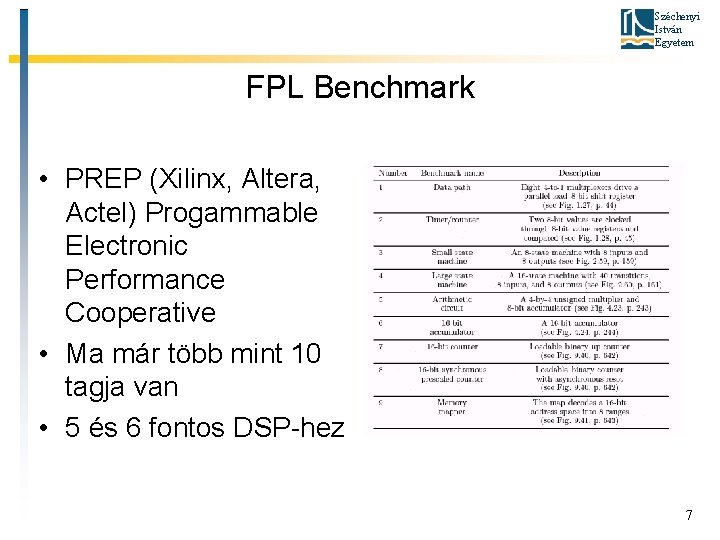

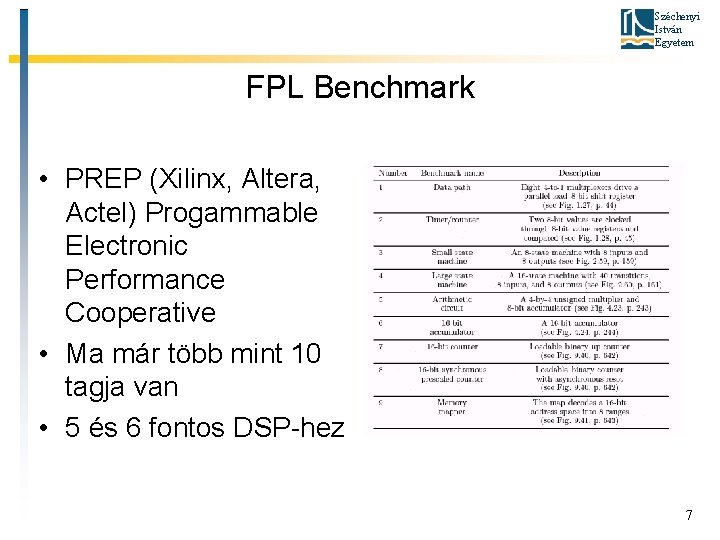

Széchenyi István Egyetem FPL Benchmark • PREP (Xilinx, Altera, Actel) Progammable Electronic Performance Cooperative • Ma már több mint 10 tagja van • 5 és 6 fontos DSP-hez 7

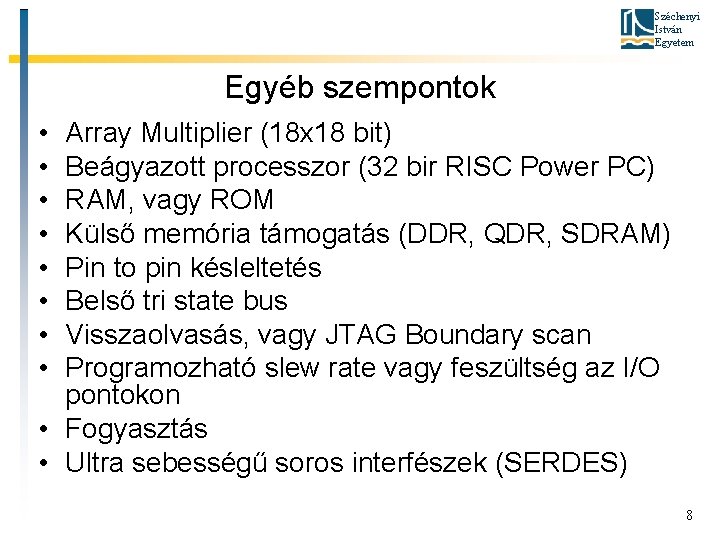

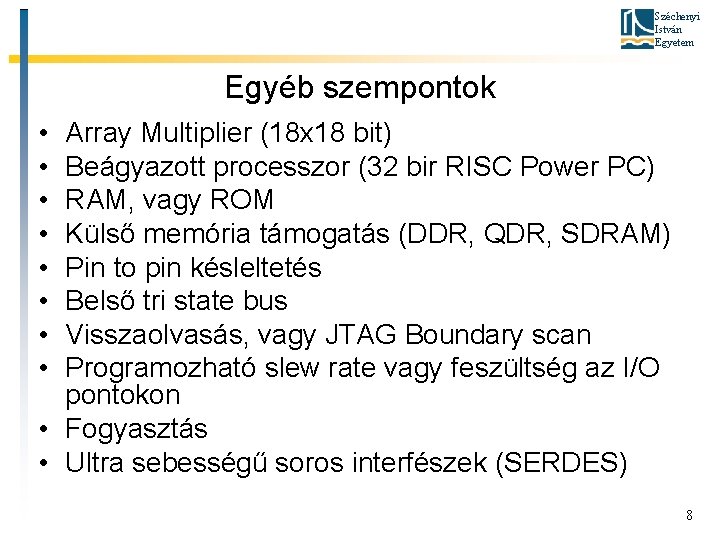

Széchenyi István Egyetem Egyéb szempontok • • Array Multiplier (18 x 18 bit) Beágyazott processzor (32 bir RISC Power PC) RAM, vagy ROM Külső memória támogatás (DDR, QDR, SDRAM) Pin to pin késleltetés Belső tri state bus Visszaolvasás, vagy JTAG Boundary scan Programozható slew rate vagy feszültség az I/O pontokon • Fogyasztás • Ultra sebességű soros interfészek (SERDES) 8

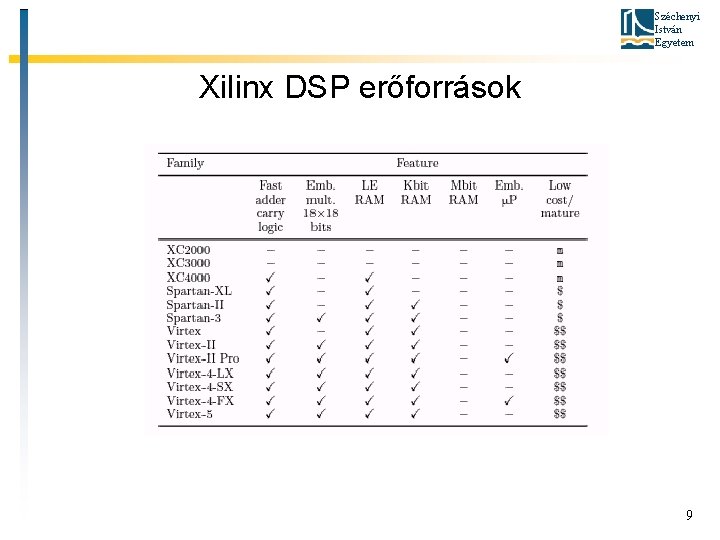

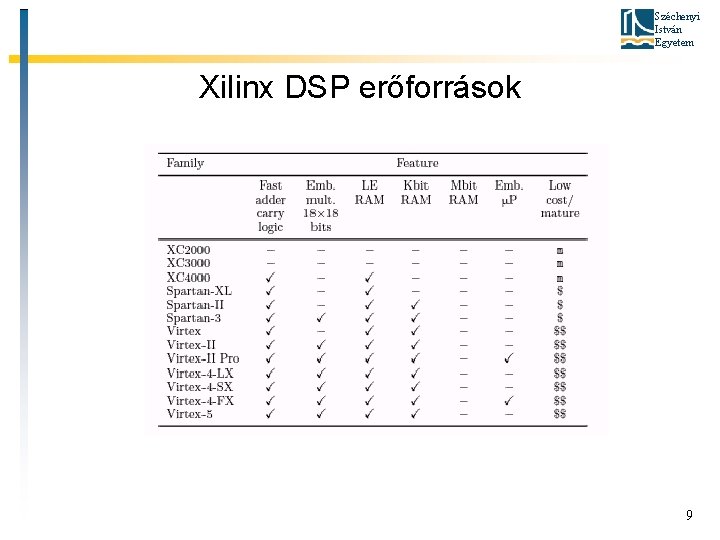

Széchenyi István Egyetem Xilinx DSP erőforrások 9

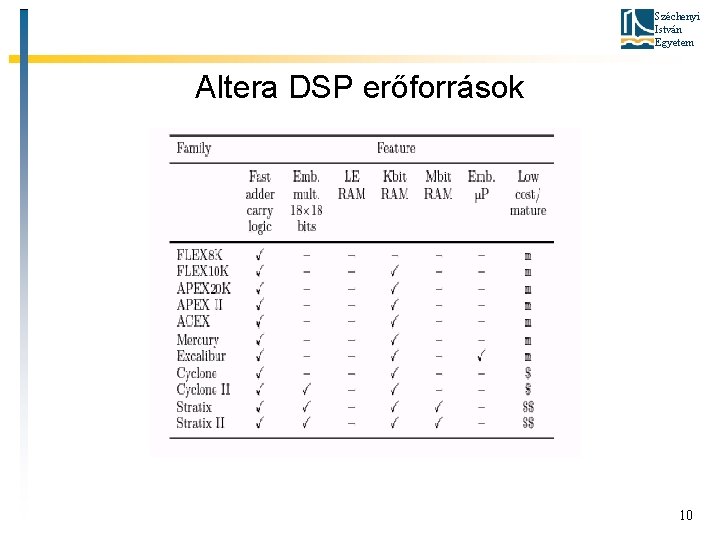

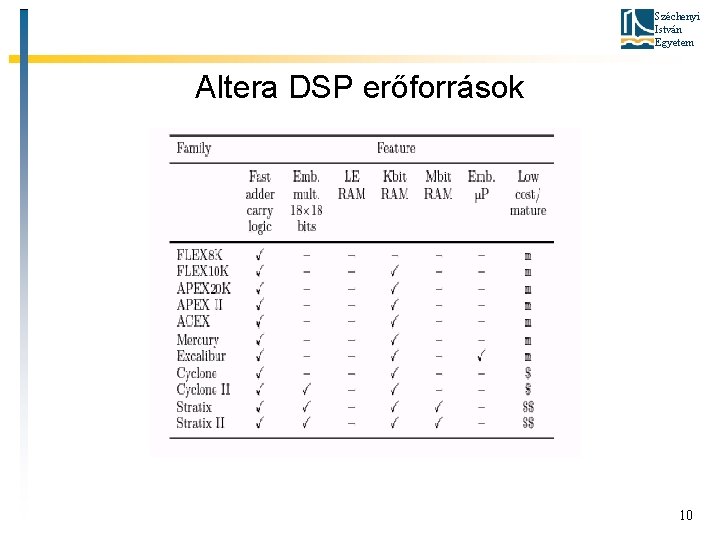

Széchenyi István Egyetem Altera DSP erőforrások 10

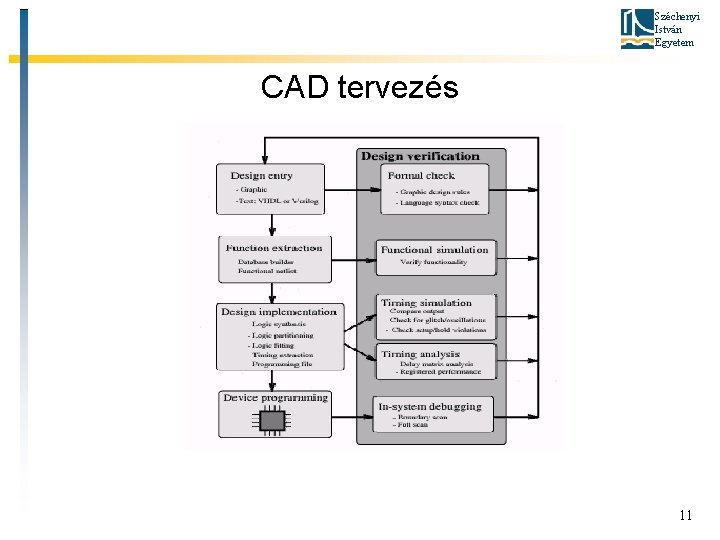

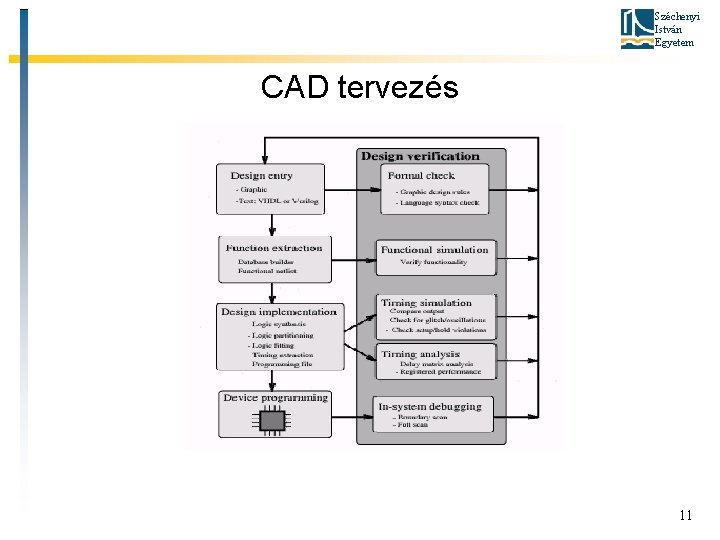

Széchenyi István Egyetem CAD tervezés 11

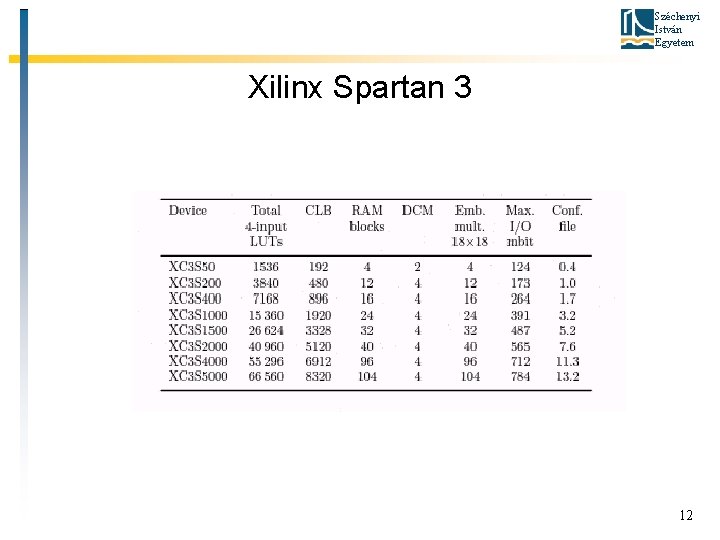

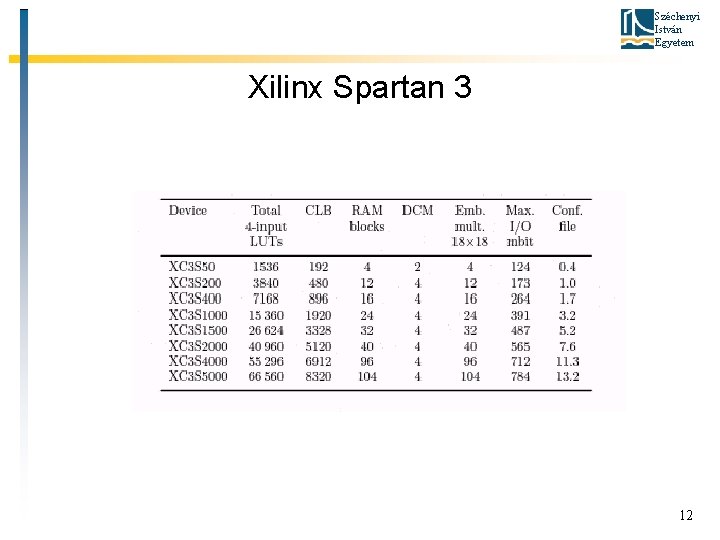

Széchenyi István Egyetem Xilinx Spartan 3 12

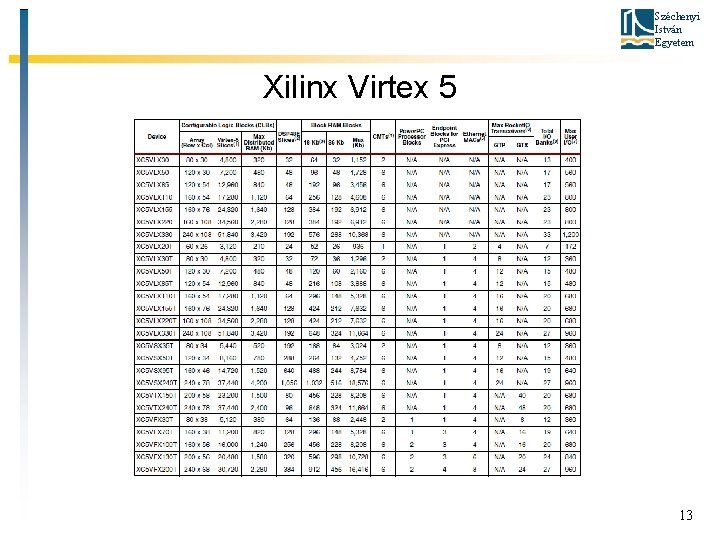

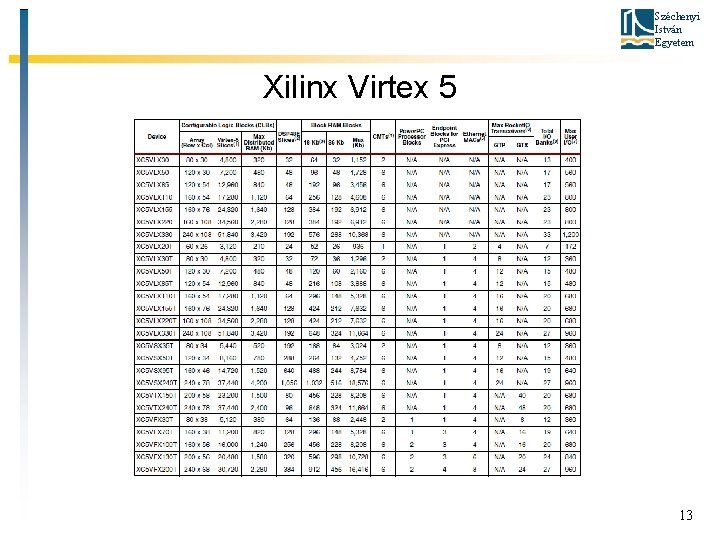

Széchenyi István Egyetem Xilinx Virtex 5 13

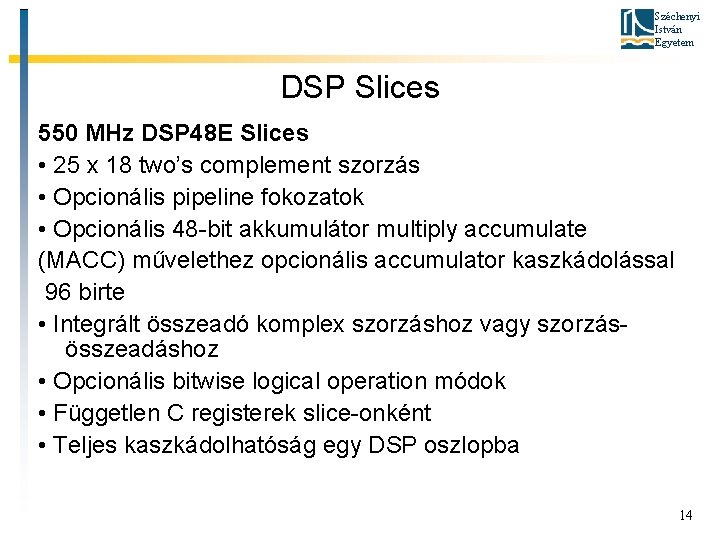

Széchenyi István Egyetem DSP Slices 550 MHz DSP 48 E Slices • 25 x 18 two’s complement szorzás • Opcionális pipeline fokozatok • Opcionális 48 -bit akkumulátor multiply accumulate (MACC) művelethez opcionális accumulator kaszkádolással 96 birte • Integrált összeadó komplex szorzáshoz vagy szorzásösszeadáshoz • Opcionális bitwise logical operation módok • Független C registerek slice-onként • Teljes kaszkádolhatóság egy DSP oszlopba 14

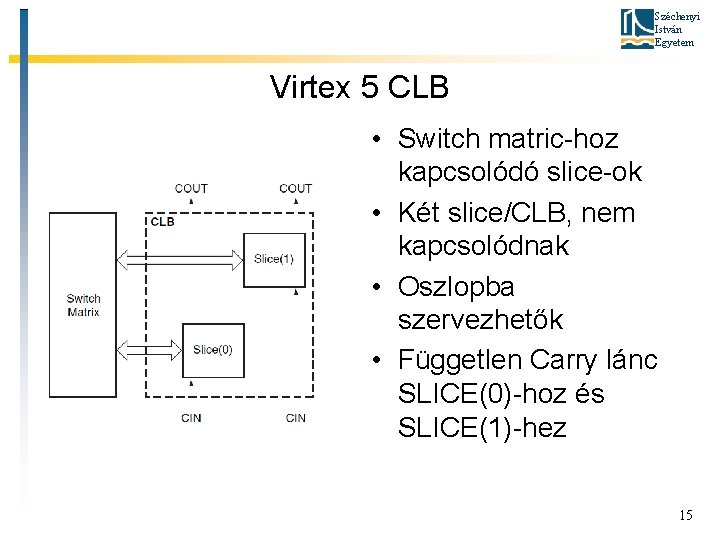

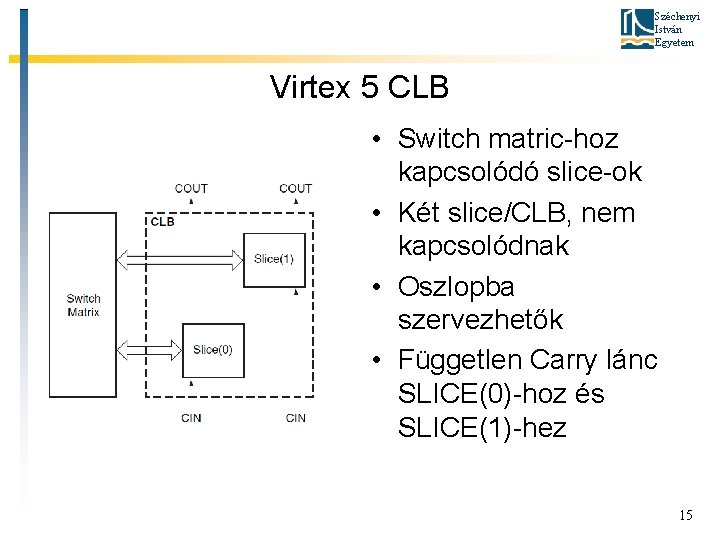

Széchenyi István Egyetem Virtex 5 CLB • Switch matric-hoz kapcsolódó slice-ok • Két slice/CLB, nem kapcsolódnak • Oszlopba szervezhetők • Független Carry lánc SLICE(0)-hoz és SLICE(1)-hez 15

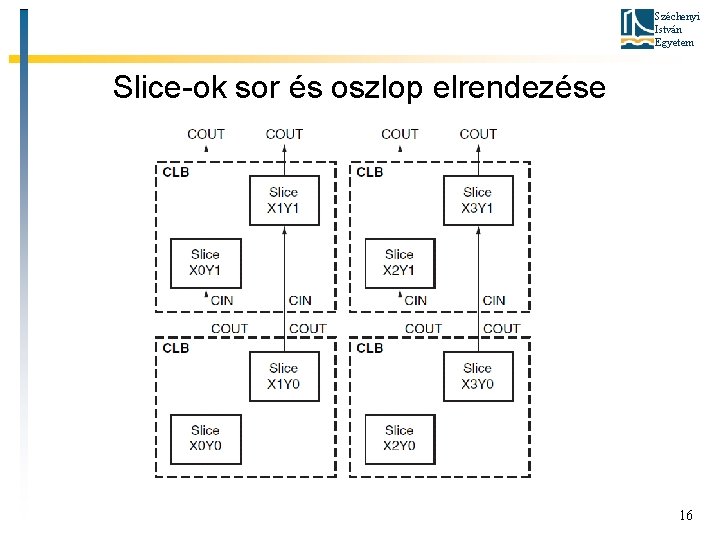

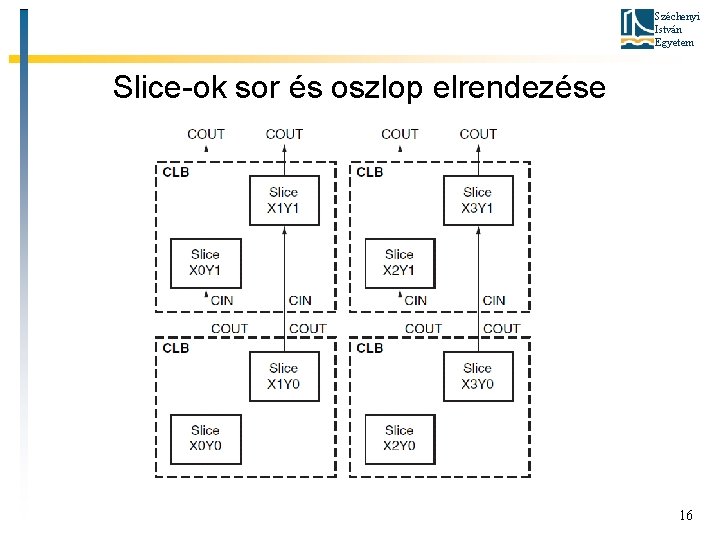

Széchenyi István Egyetem Slice-ok sor és oszlop elrendezése 16

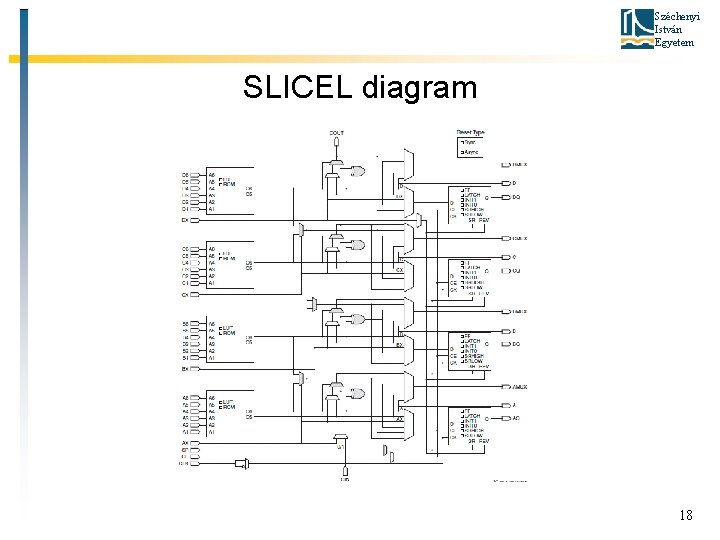

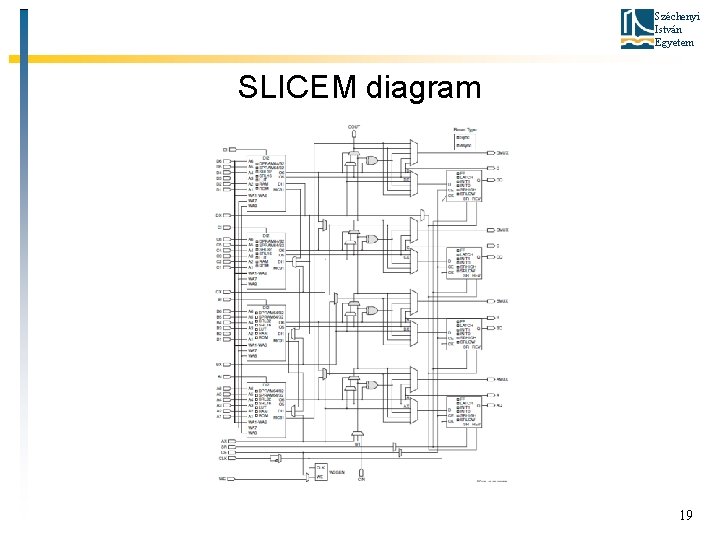

Széchenyi István Egyetem Slice-ok felépítése SLICEL • Négy logikai függvény generátor (LUT) • Négy tároló elem • Multiplexerek • Carry logika SLICEM fentieken kívül • Adattárolás elosztott RAM-ban • Adatshiftelés 32 bites regiszterekkel 17

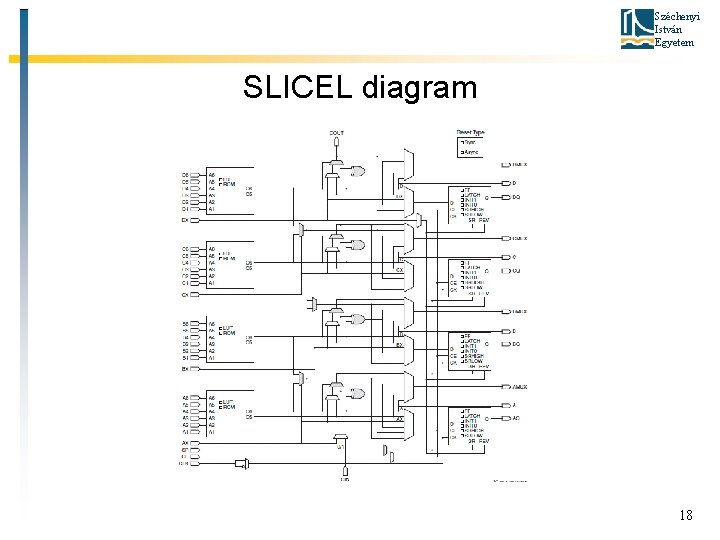

Széchenyi István Egyetem SLICEL diagram 18

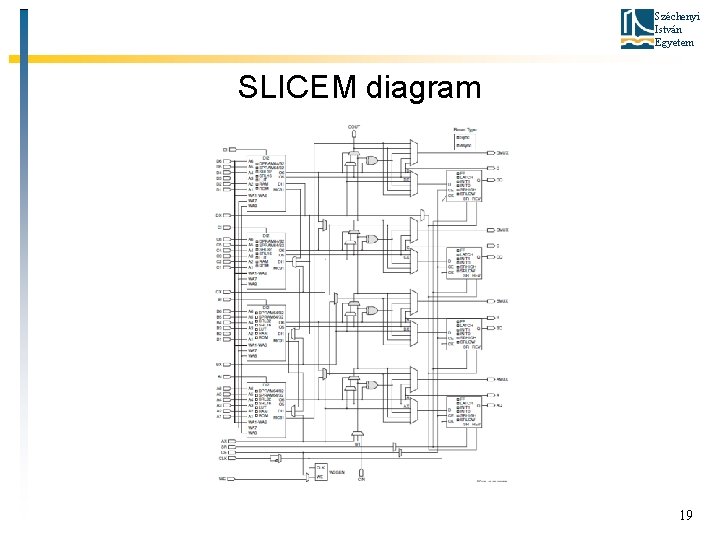

Széchenyi István Egyetem SLICEM diagram 19

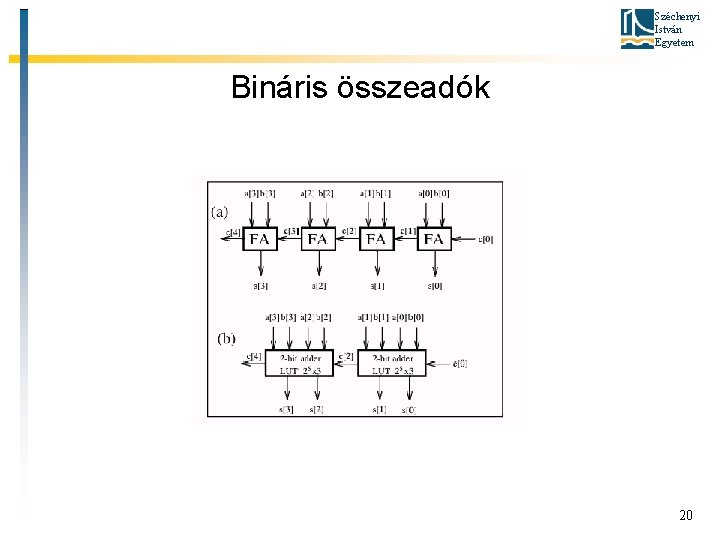

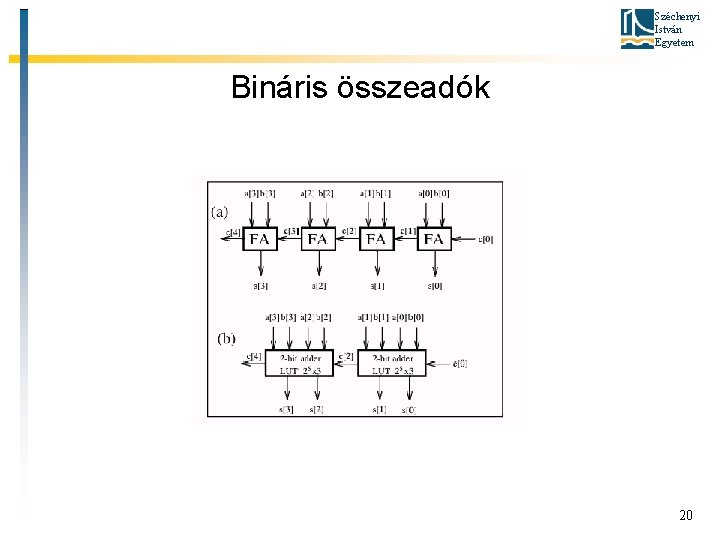

Széchenyi István Egyetem Bináris összeadók 20

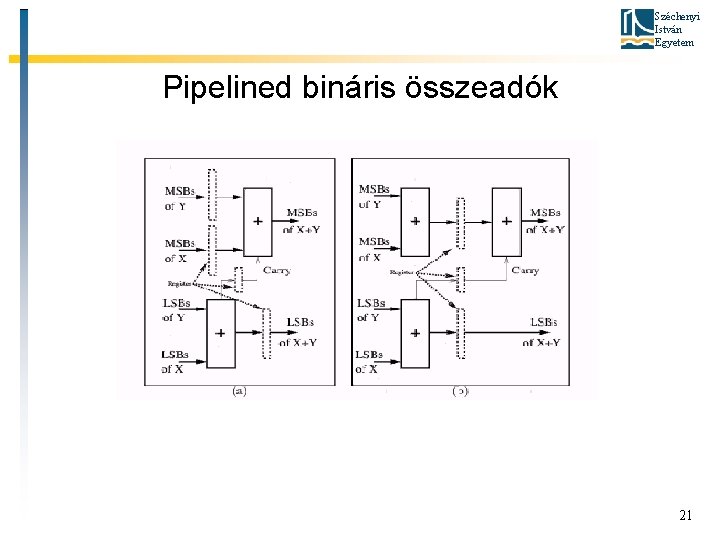

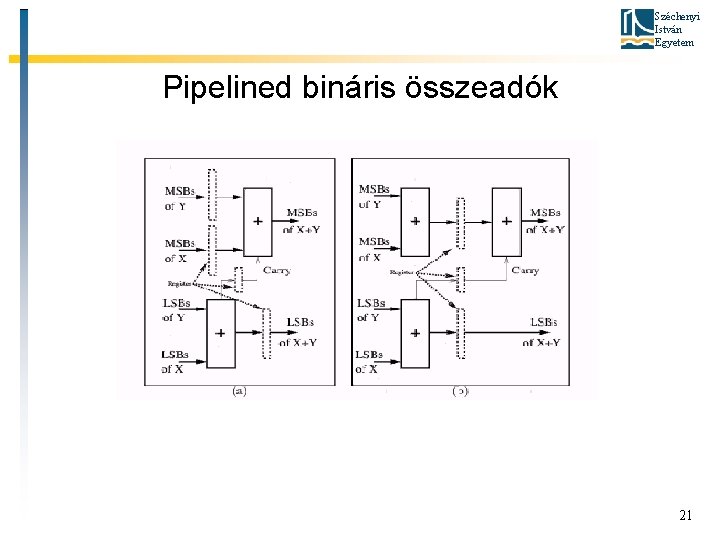

Széchenyi István Egyetem Pipelined bináris összeadók 21

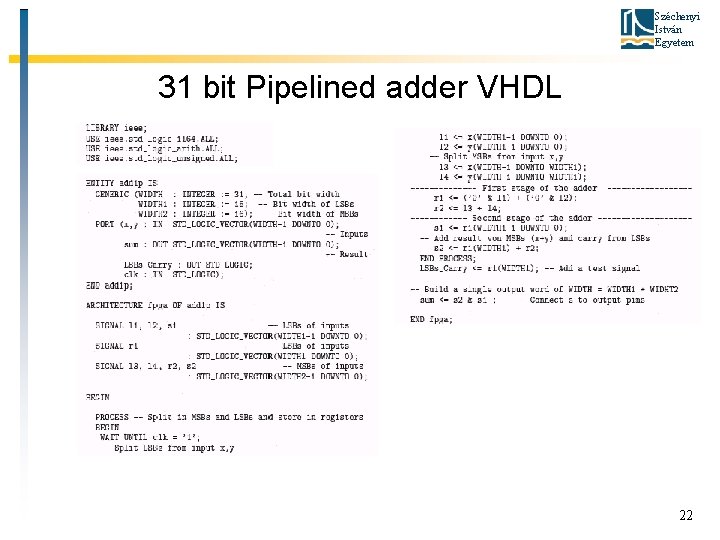

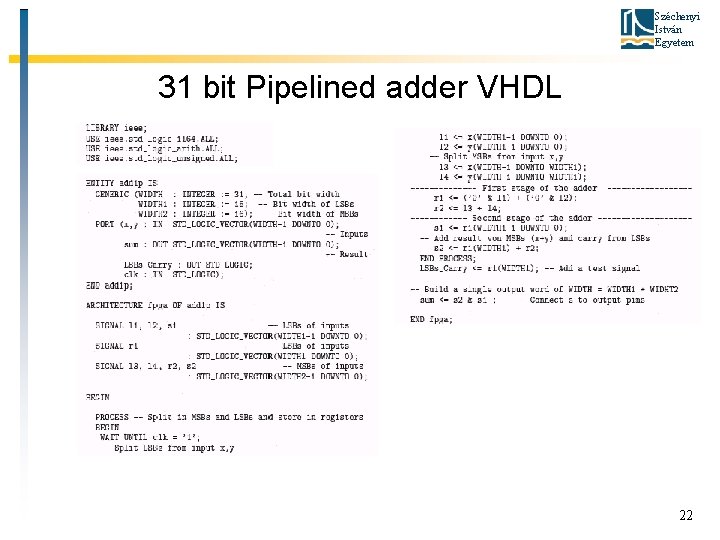

Széchenyi István Egyetem 31 bit Pipelined adder VHDL 22

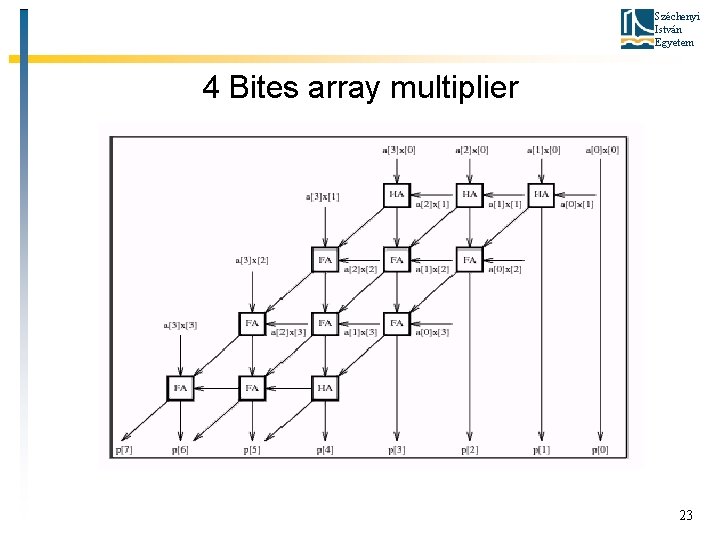

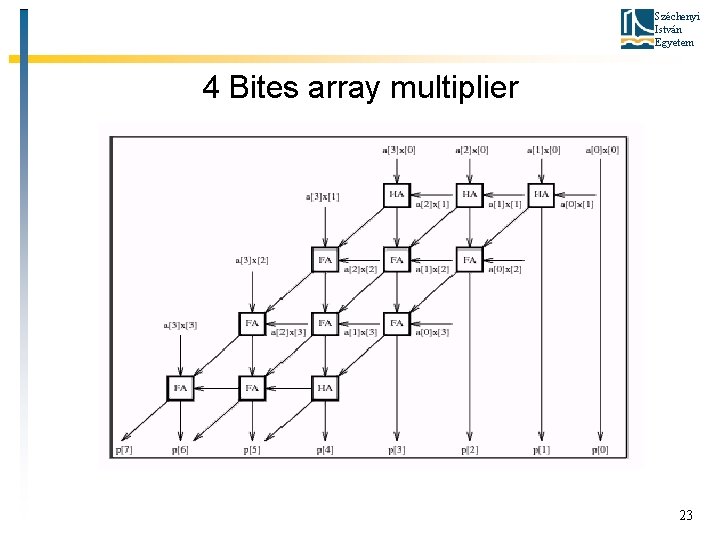

Széchenyi István Egyetem 4 Bites array multiplier 23

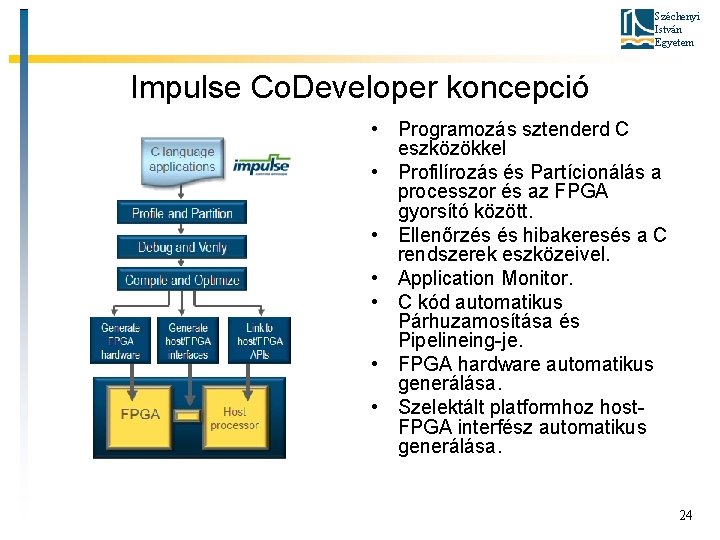

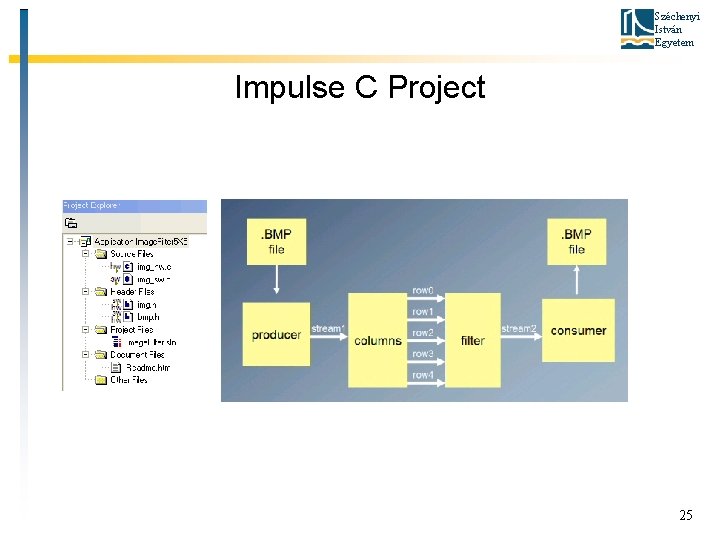

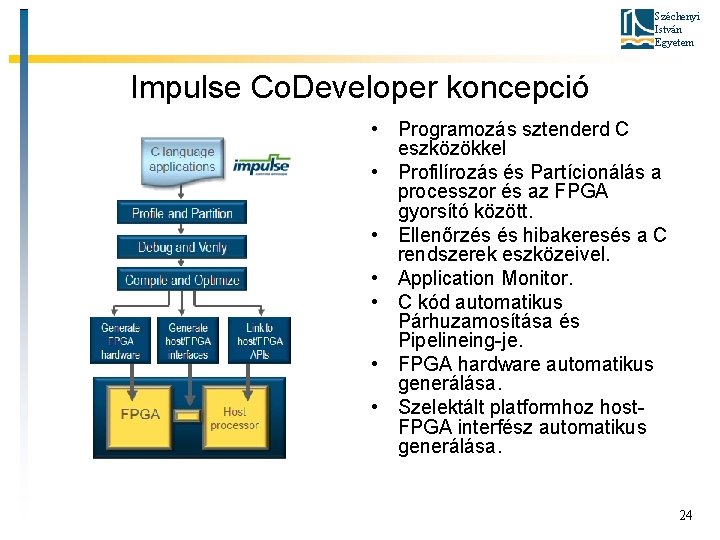

Széchenyi István Egyetem Impulse Co. Developer koncepció • Programozás sztenderd C eszközökkel • Profilírozás és Partícionálás a processzor és az FPGA gyorsító között. • Ellenőrzés és hibakeresés a C rendszerek eszközeivel. • Application Monitor. • C kód automatikus Párhuzamosítása és Pipelineing-je. • FPGA hardware automatikus generálása. • Szelektált platformhoz host. FPGA interfész automatikus generálása. 24

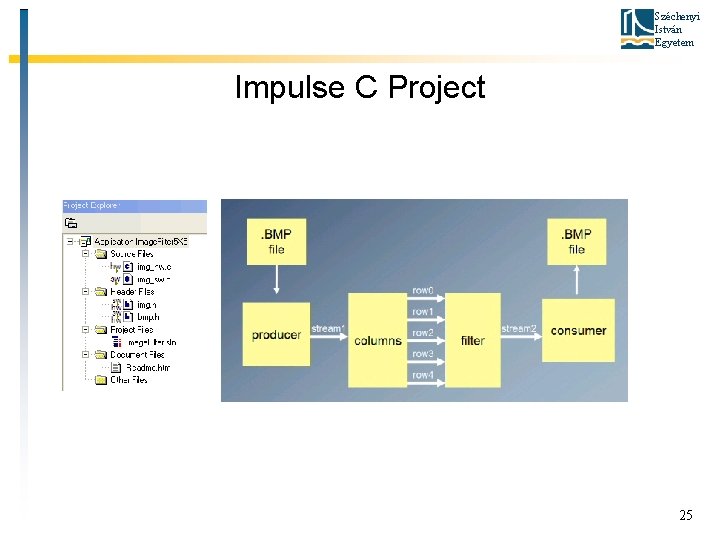

Széchenyi István Egyetem Impulse C Project 25

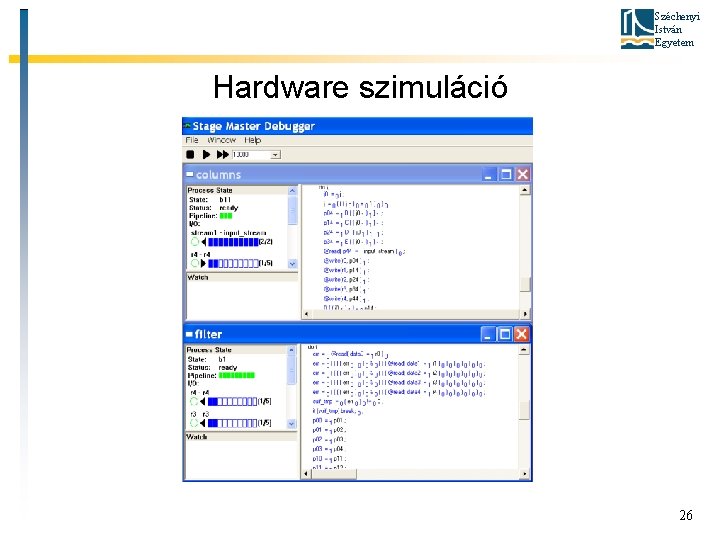

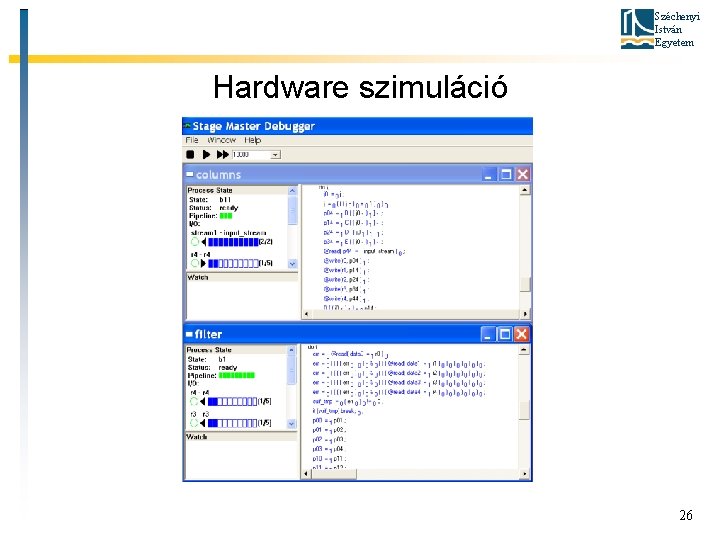

Széchenyi István Egyetem Hardware szimuláció 26

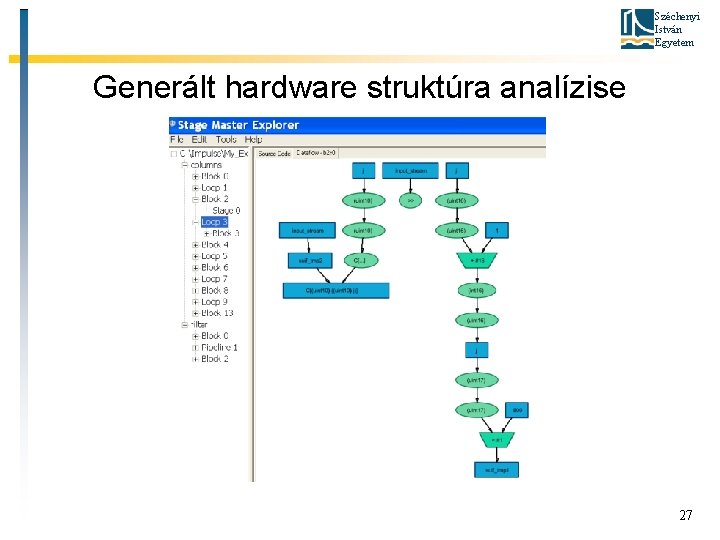

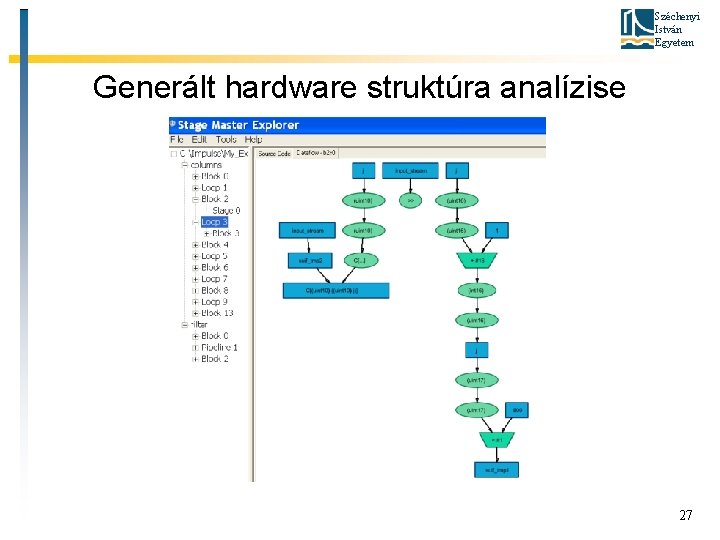

Széchenyi István Egyetem Generált hardware struktúra analízise 27

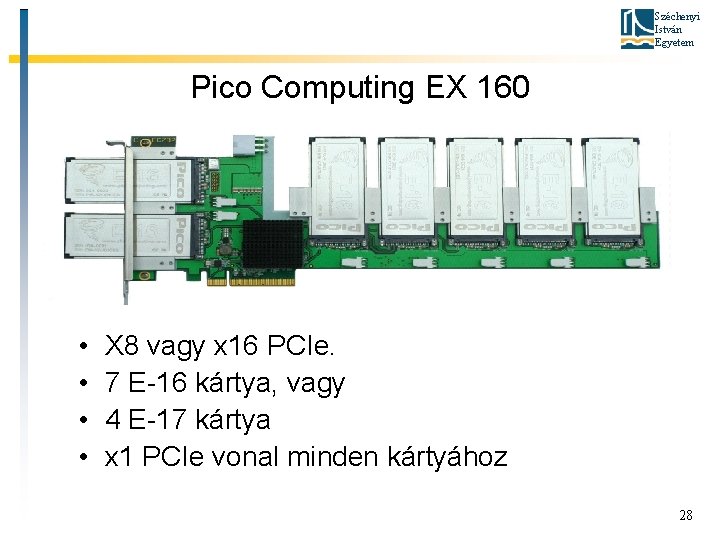

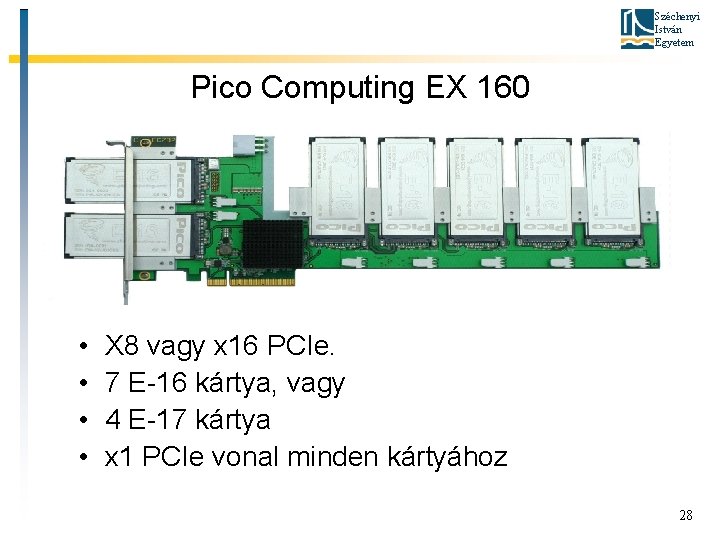

Széchenyi István Egyetem Pico Computing EX 160 • • X 8 vagy x 16 PCIe. 7 E-16 kártya, vagy 4 E-17 kártya x 1 PCIe vonal minden kártyához 28

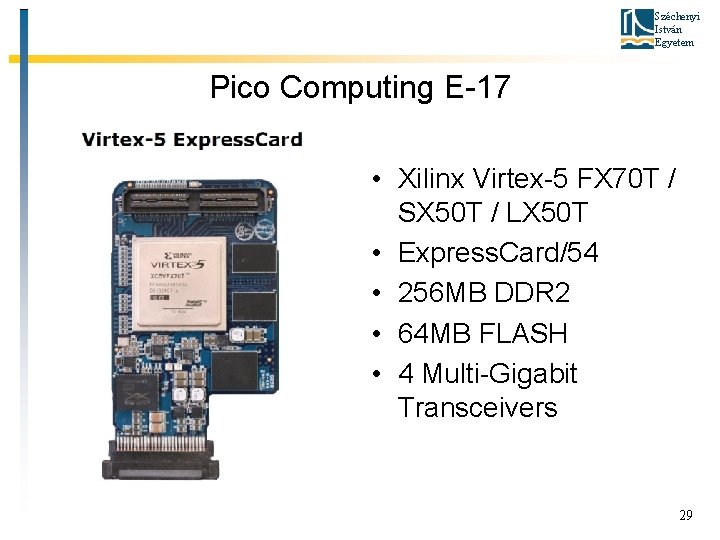

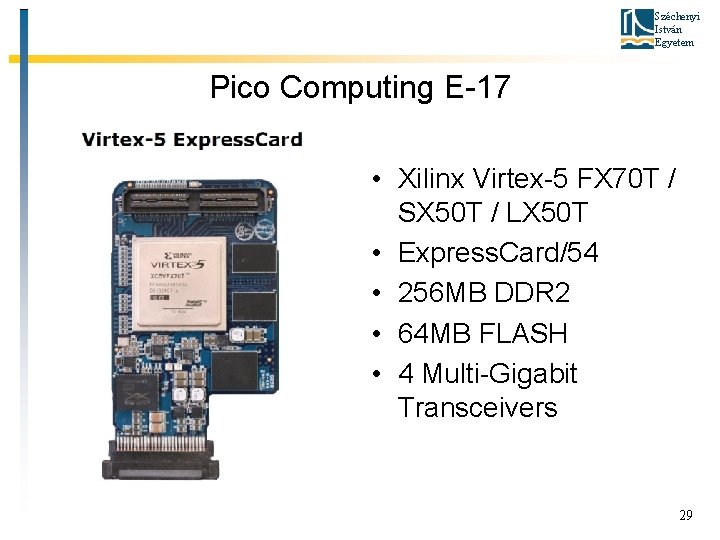

Széchenyi István Egyetem Pico Computing E-17 • Xilinx Virtex-5 FX 70 T / SX 50 T / LX 50 T • Express. Card/54 • 256 MB DDR 2 • 64 MB FLASH • 4 Multi-Gigabit Transceivers 29

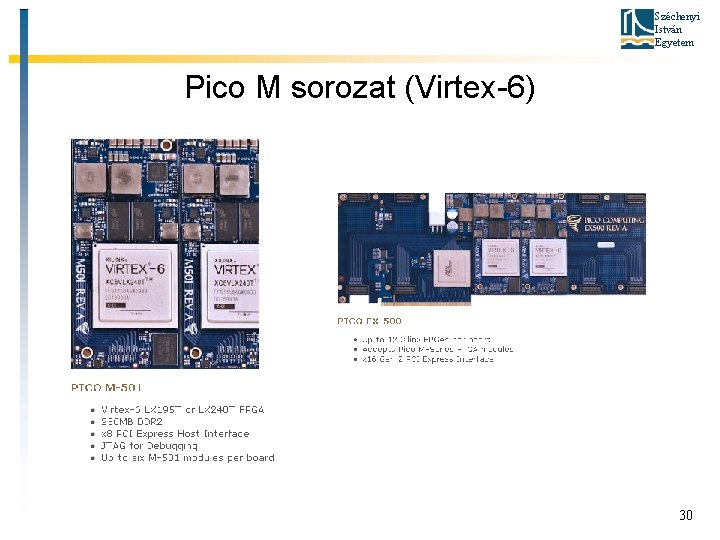

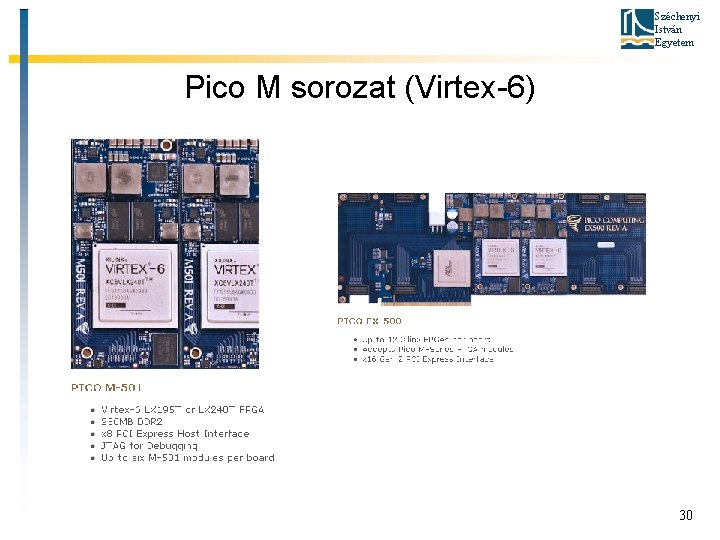

Széchenyi István Egyetem Pico M sorozat (Virtex-6) 30

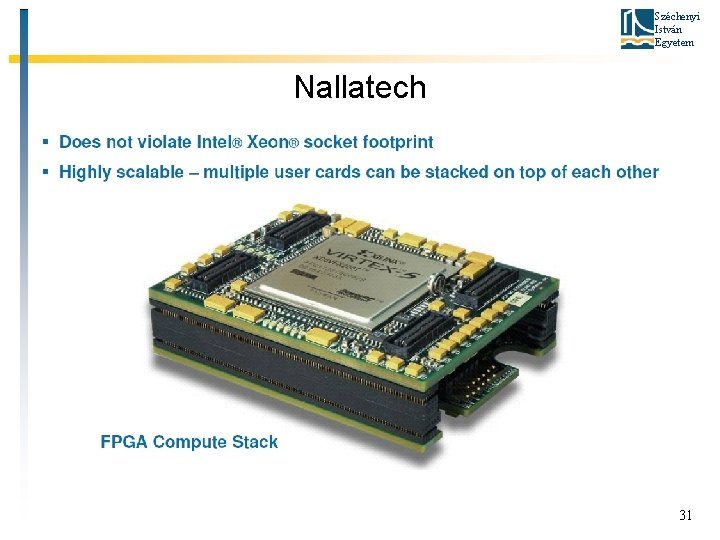

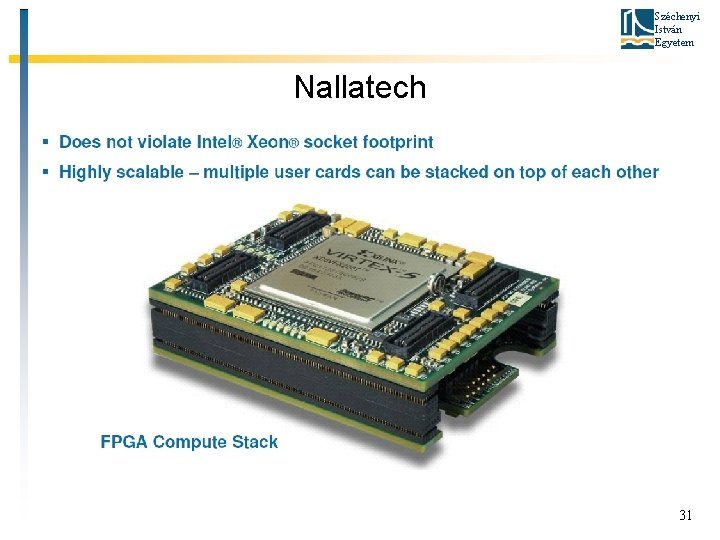

Széchenyi István Egyetem Nallatech 31