FPGA for Dummies Design flow ESS FPGA for

- Slides: 38

FPGA for Dummies Design flow ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

FPGA for Dummies • FPGA Architecture: Ø basic blocks (Logic, FFs, wires and IOs); Ø additional modern elements; • FPGA Programming: ØHDL languages; ØDesign flow; • FPGA DSP: ØArithmetic, FFT and filters; ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

FPGA for Dummies • FPGA Architecture: Ø basic blocks (Logic, FFs, wires and IOs); Ø additional modern elements; • FPGA Programming: ØHDL languages; ØDesign flow; • FPGA DSP: ØArithmetic, FFT and filters; ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

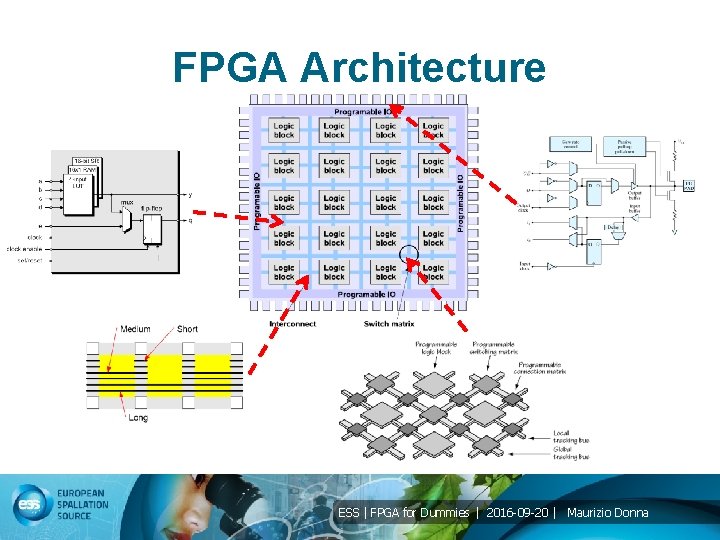

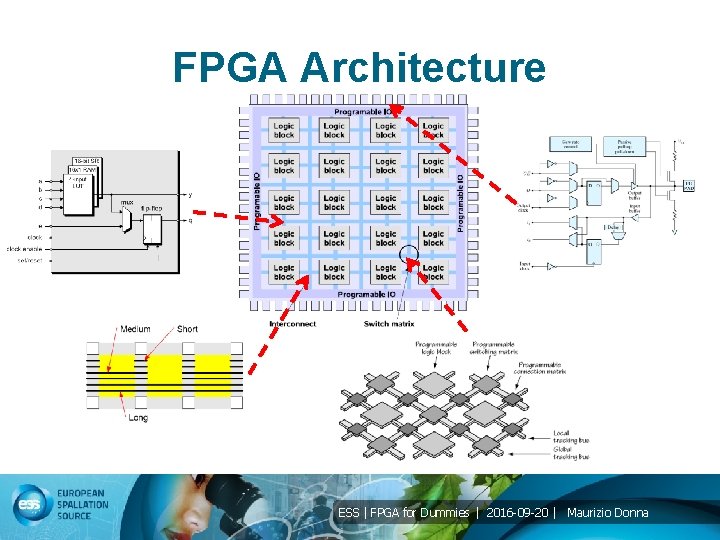

FPGA Architecture ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

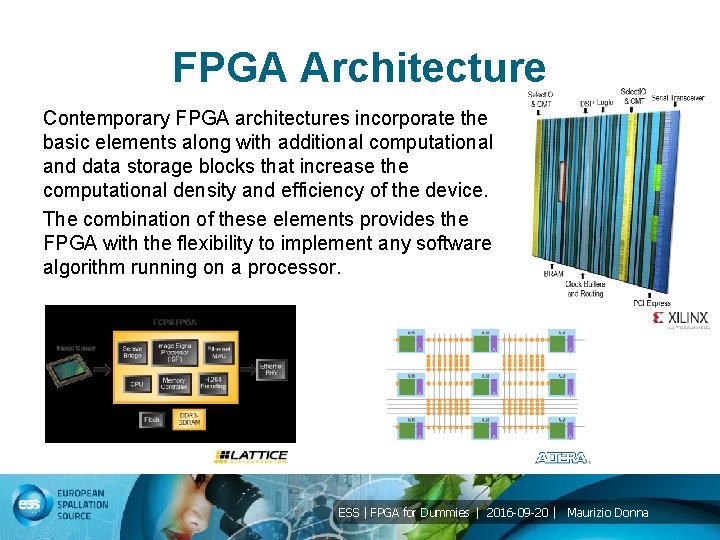

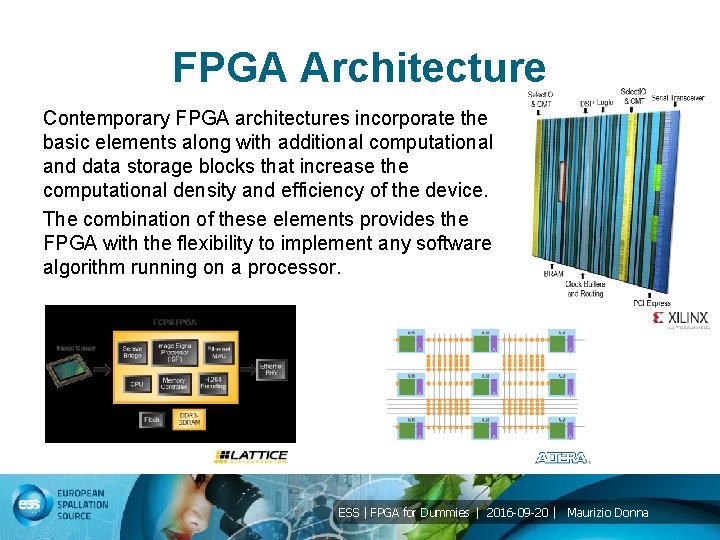

FPGA Architecture Contemporary FPGA architectures incorporate the basic elements along with additional computational and data storage blocks that increase the computational density and efficiency of the device. The combination of these elements provides the FPGA with the flexibility to implement any software algorithm running on a processor. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

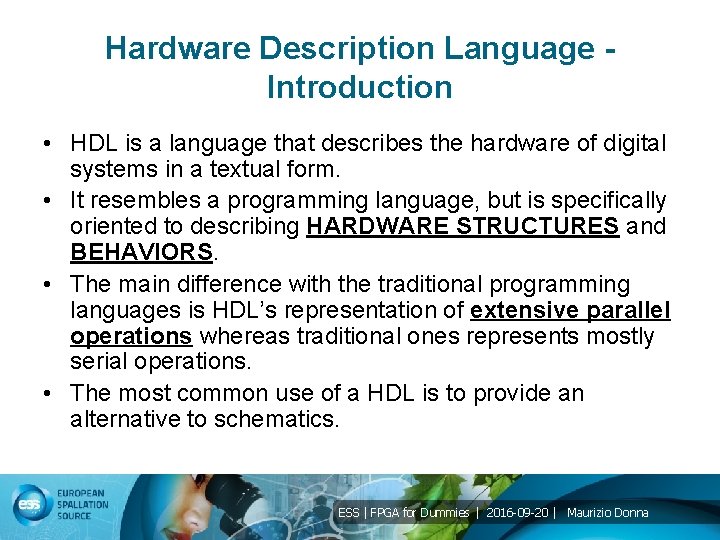

Hardware Description Language Introduction • HDL is a language that describes the hardware of digital systems in a textual form. • It resembles a programming language, but is specifically oriented to describing HARDWARE STRUCTURES and BEHAVIORS. • The main difference with the traditional programming languages is HDL’s representation of extensive parallel operations whereas traditional ones represents mostly serial operations. • The most common use of a HDL is to provide an alternative to schematics. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

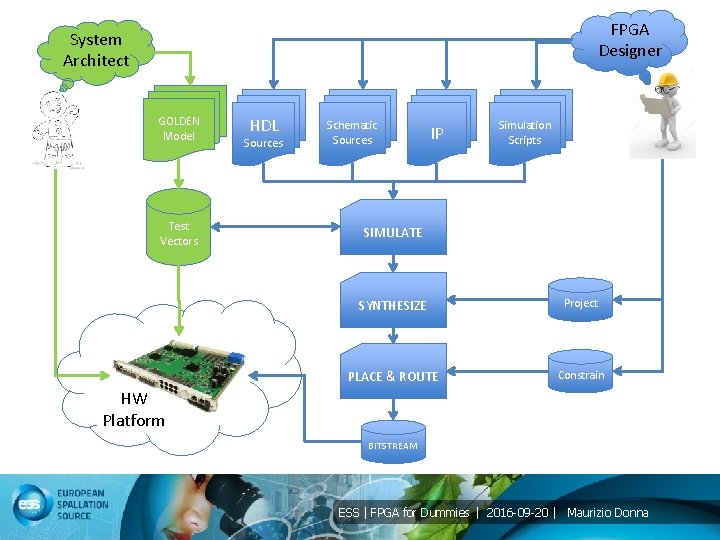

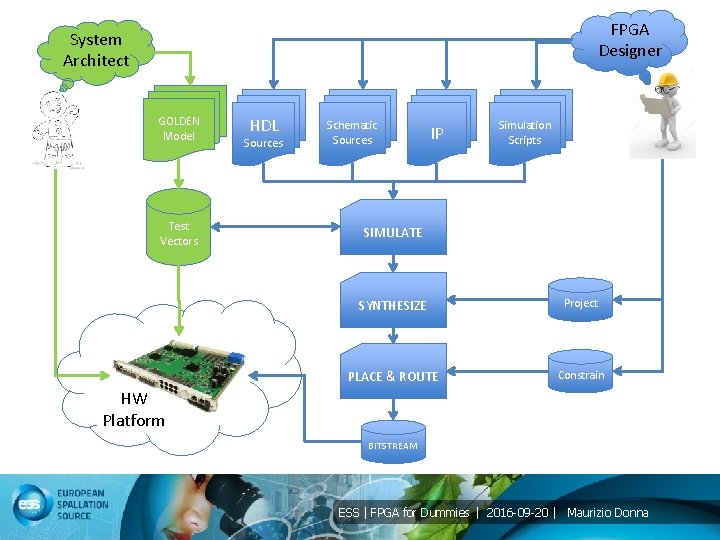

FPGA Designer System Architect GOLDEN Model Test Vectors HDL Sources Schematic Sources IP Simulation Scripts SIMULATE SYNTHESIZE Project PLACE & ROUTE Constrain HW Platform BITSTREAM ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

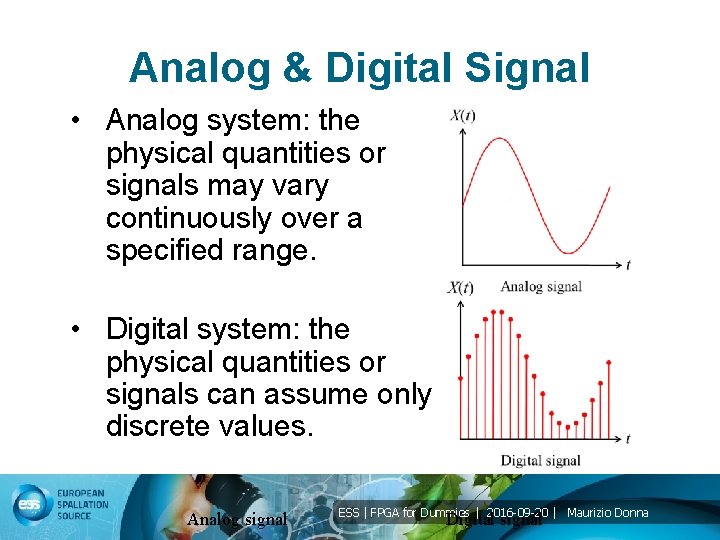

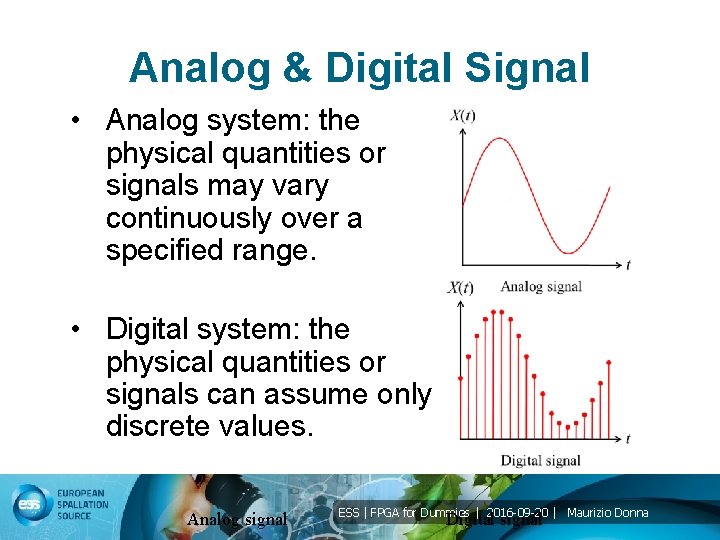

Analog & Digital Signal • Analog system: the physical quantities or signals may vary continuously over a specified range. • Digital system: the physical quantities or signals can assume only discrete values. Analog signal ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna Digital signal

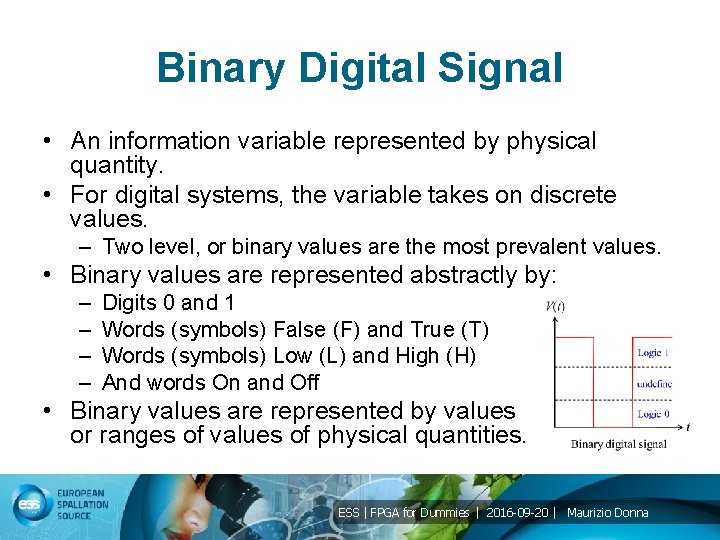

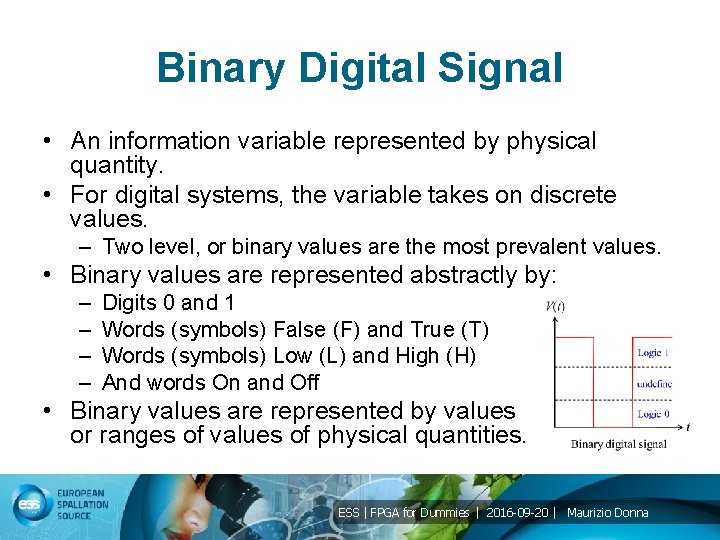

Binary Digital Signal • An information variable represented by physical quantity. • For digital systems, the variable takes on discrete values. – Two level, or binary values are the most prevalent values. • Binary values are represented abstractly by: – – Digits 0 and 1 Words (symbols) False (F) and True (T) Words (symbols) Low (L) and High (H) And words On and Off • Binary values are represented by values or ranges of values of physical quantities. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

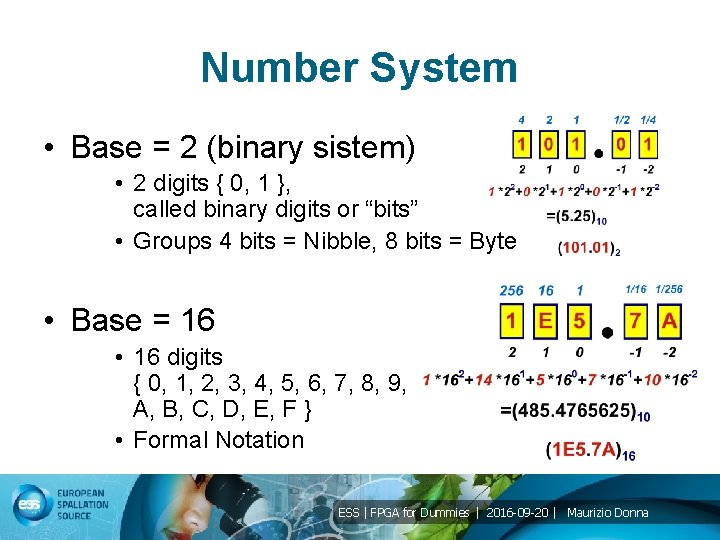

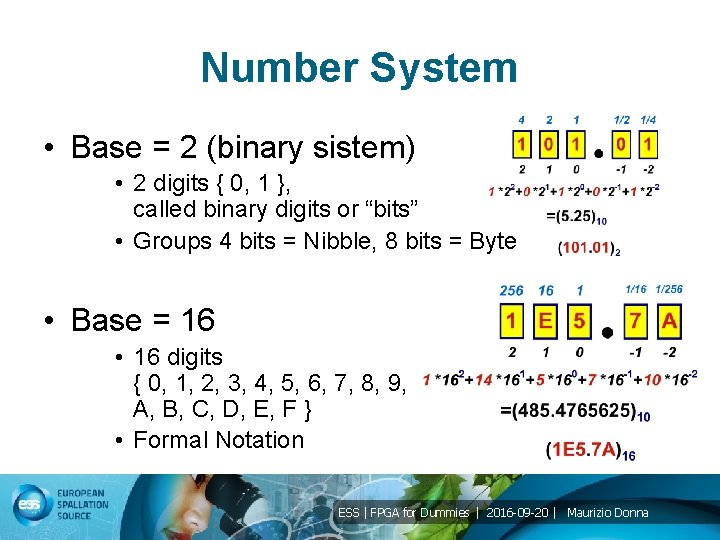

Number System • Base = 2 (binary sistem) • 2 digits { 0, 1 }, called binary digits or “bits” • Groups 4 bits = Nibble, 8 bits = Byte • Base = 16 • 16 digits { 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F } • Formal Notation ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

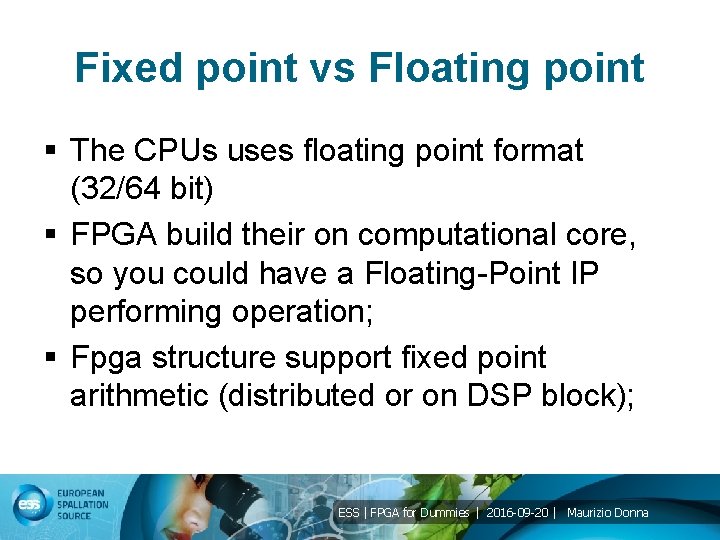

Fixed point vs Floating point § The CPUs uses floating point format (32/64 bit) § FPGA build their on computational core, so you could have a Floating-Point IP performing operation; § Fpga structure support fixed point arithmetic (distributed or on DSP block); ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

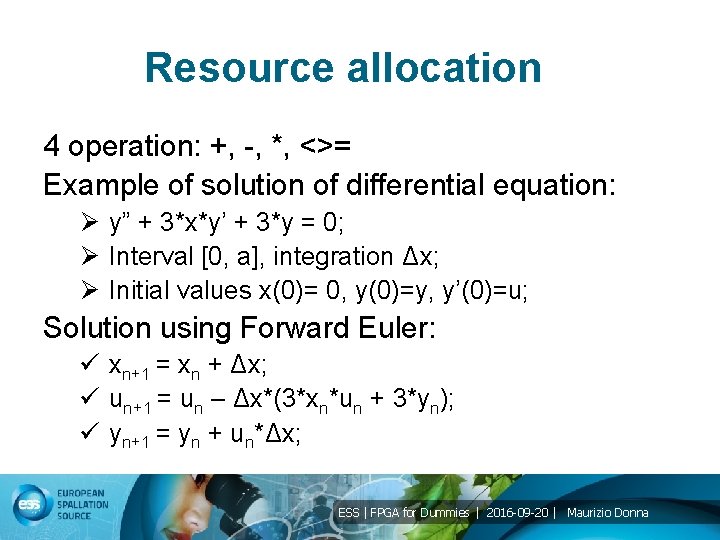

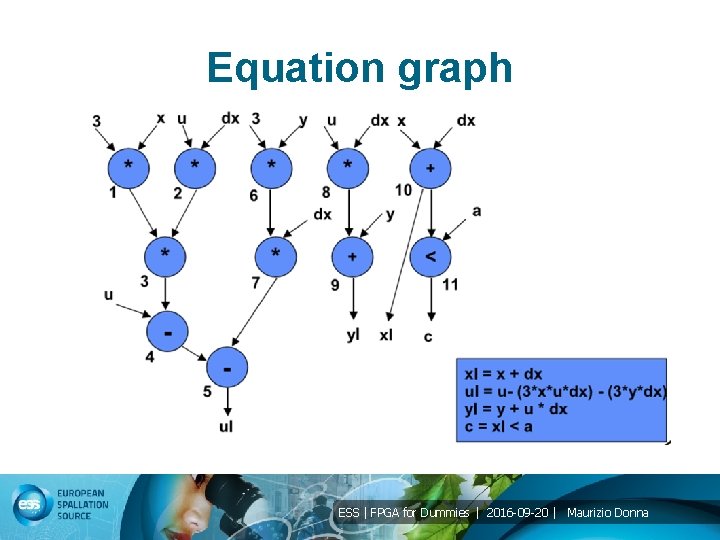

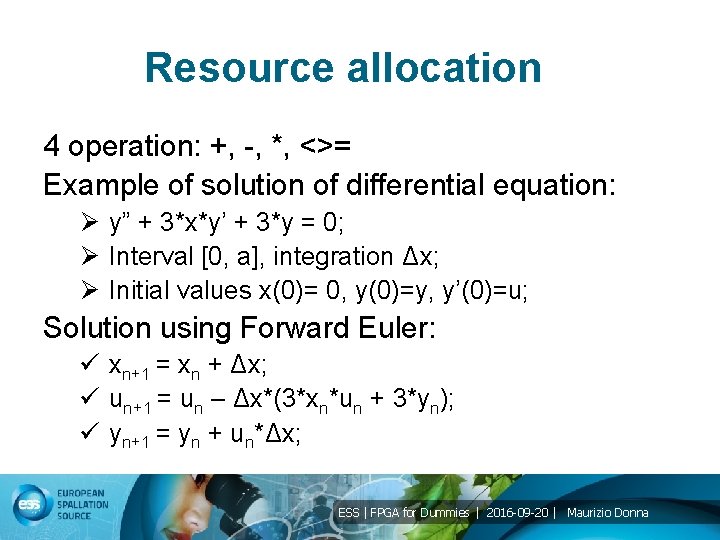

Resource allocation 4 operation: +, -, *, <>= Example of solution of differential equation: Ø y” + 3*x*y’ + 3*y = 0; Ø Interval [0, a], integration Δx; Ø Initial values x(0)= 0, y(0)=y, y’(0)=u; Solution using Forward Euler: ü xn+1 = xn + Δx; ü un+1 = un – Δx*(3*xn*un + 3*yn); ü yn+1 = yn + un*Δx; ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

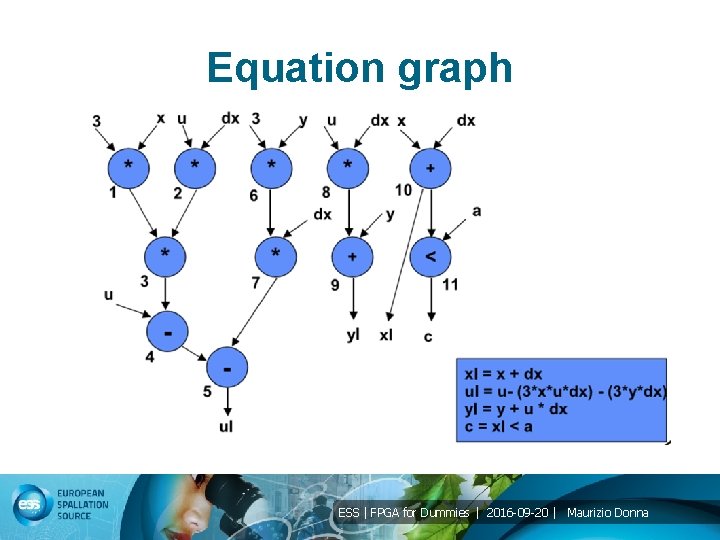

Equation graph ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

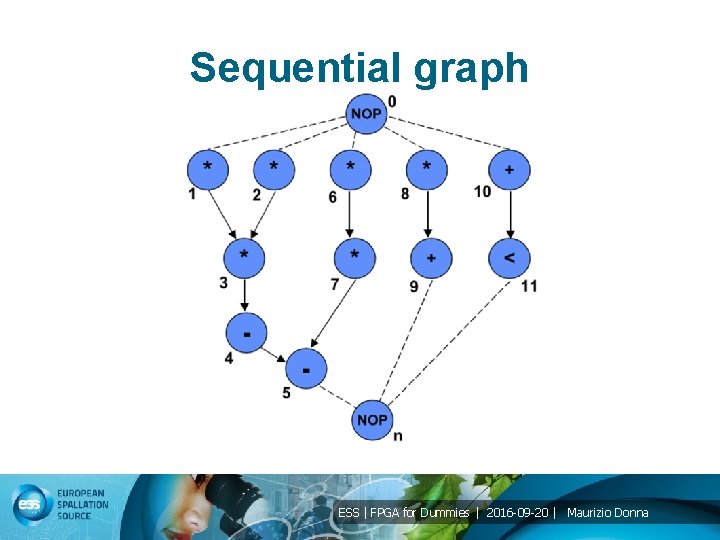

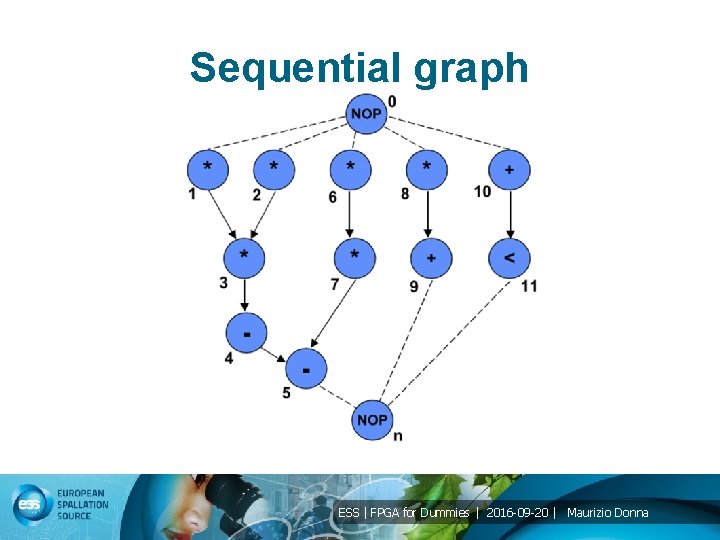

Sequential graph ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

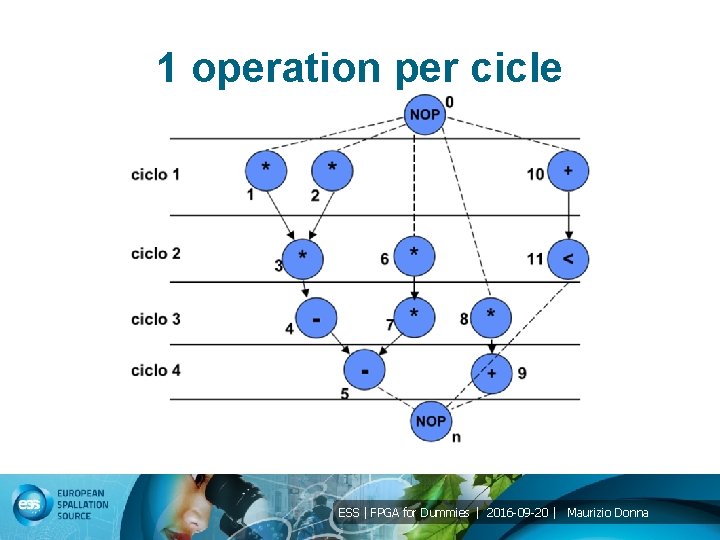

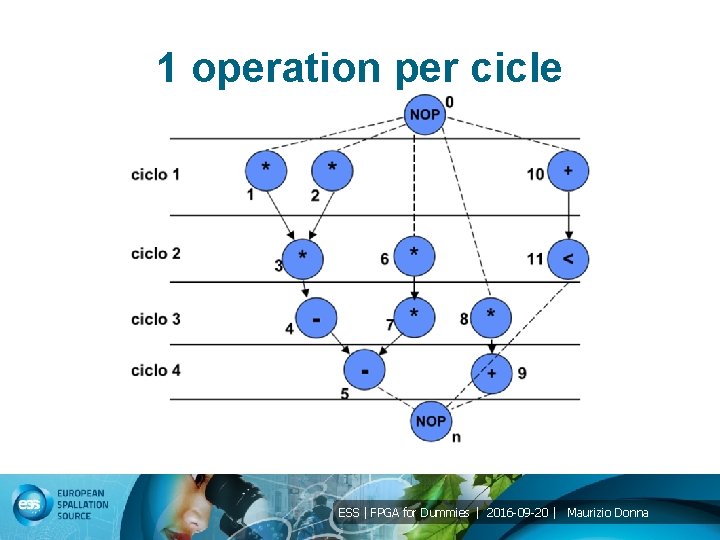

1 operation per cicle ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

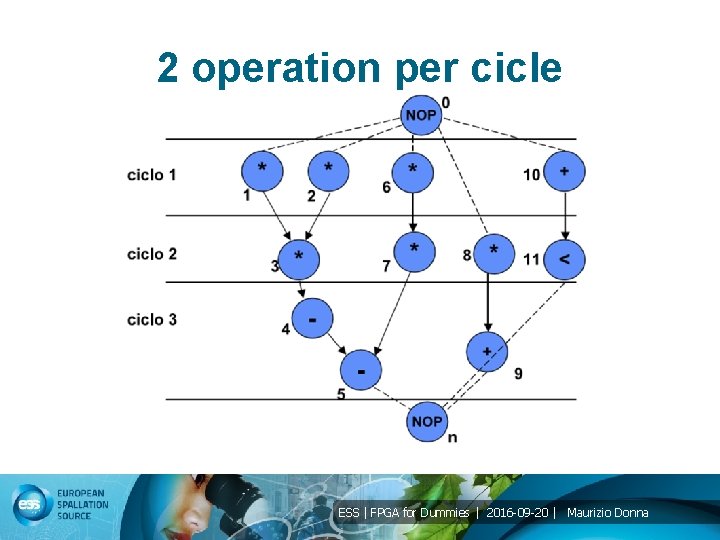

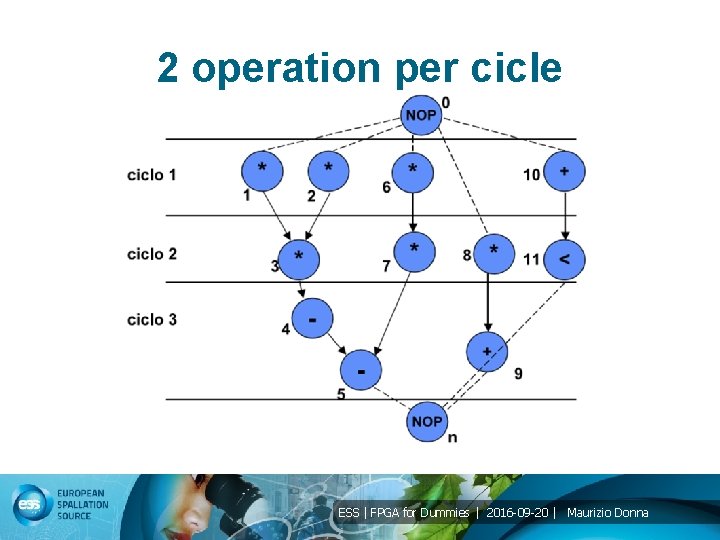

2 operation per cicle ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

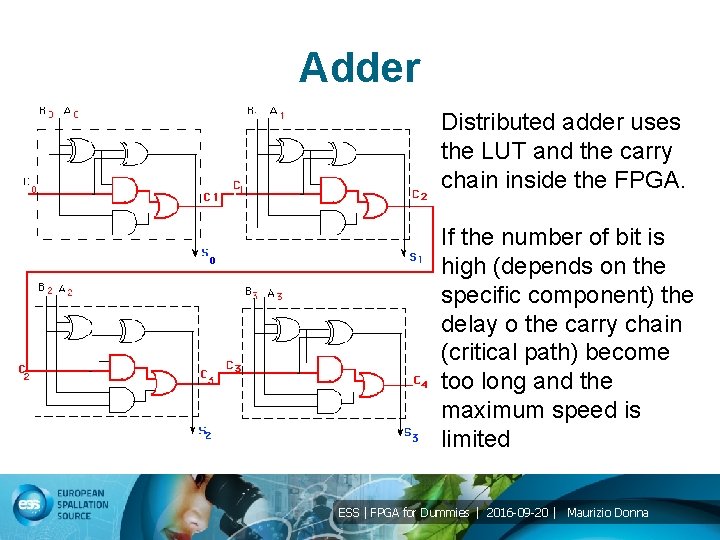

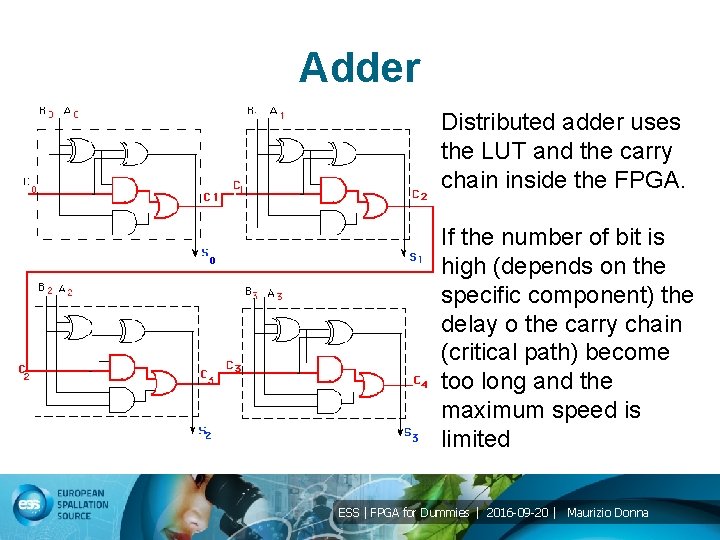

Adder Distributed adder uses the LUT and the carry chain inside the FPGA. If the number of bit is high (depends on the specific component) the delay o the carry chain (critical path) become too long and the maximum speed is limited ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

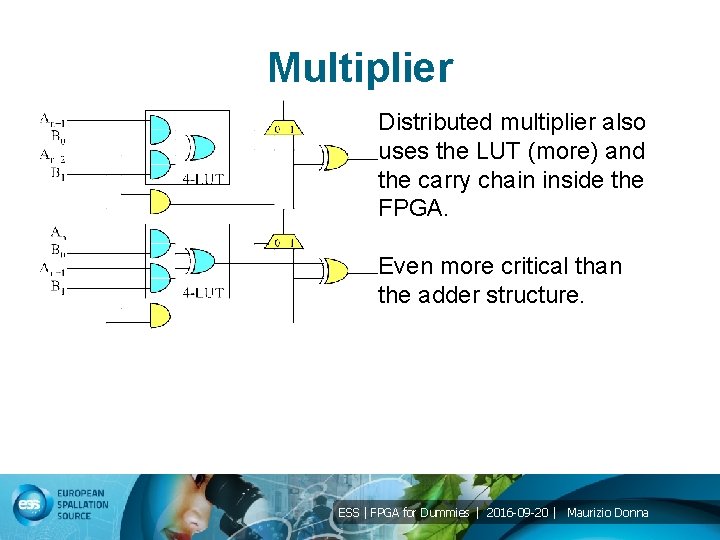

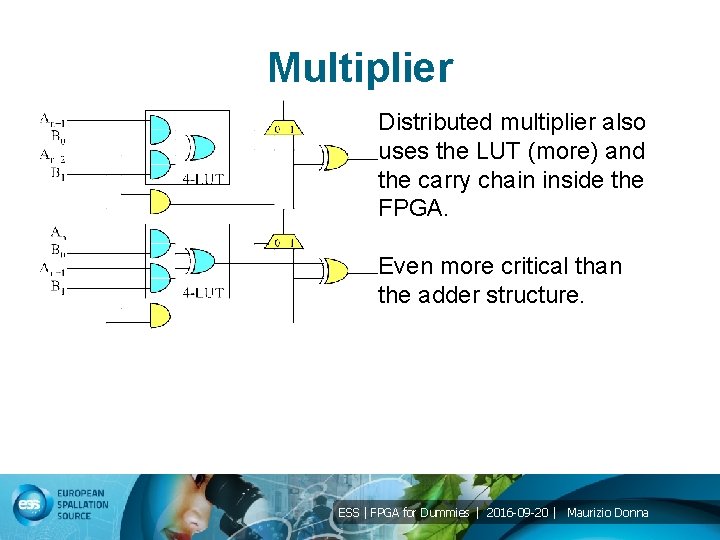

Multiplier Distributed multiplier also uses the LUT (more) and the carry chain inside the FPGA. Even more critical than the adder structure. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

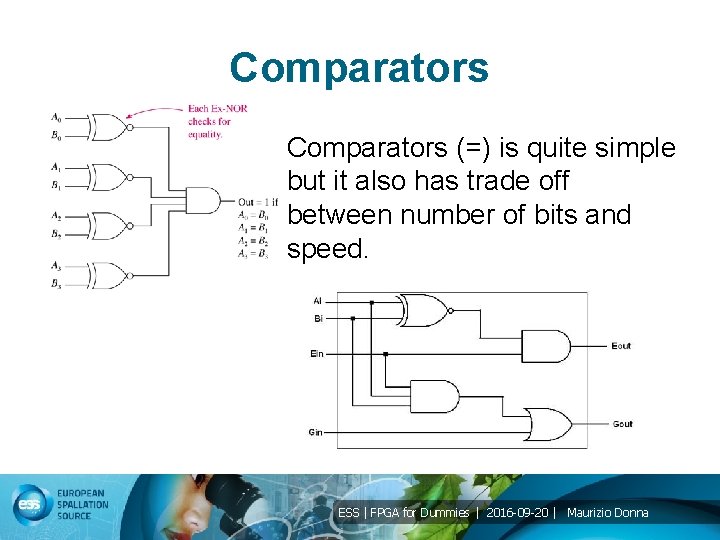

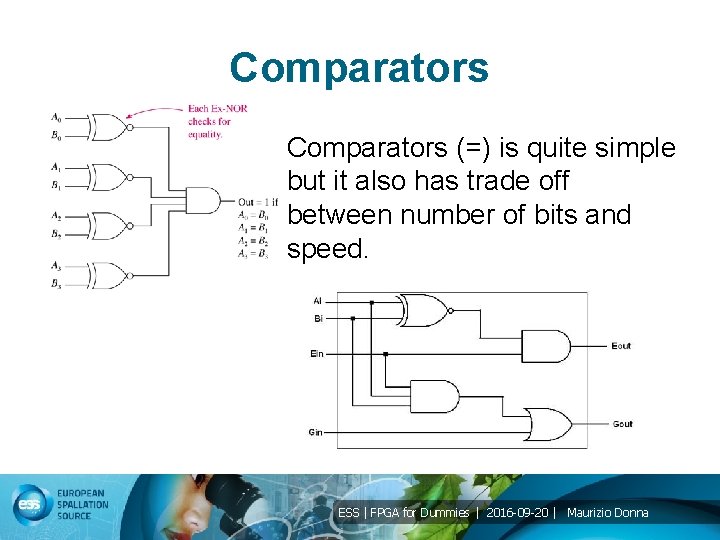

Comparators (=) is quite simple but it also has trade off between number of bits and speed. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

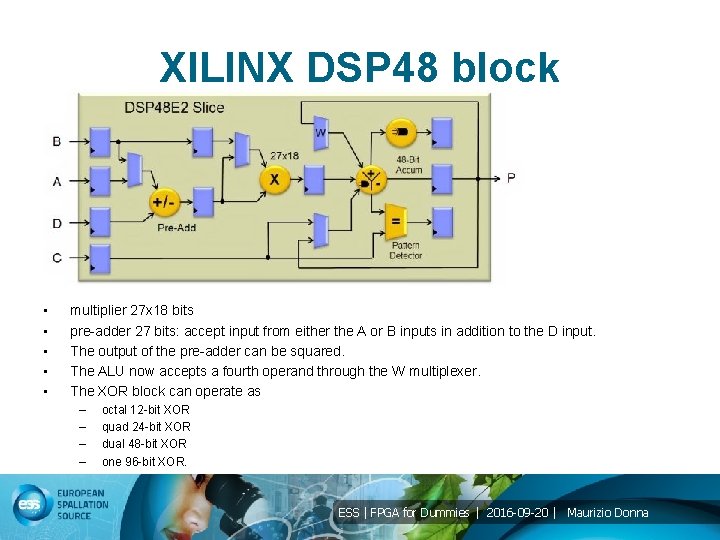

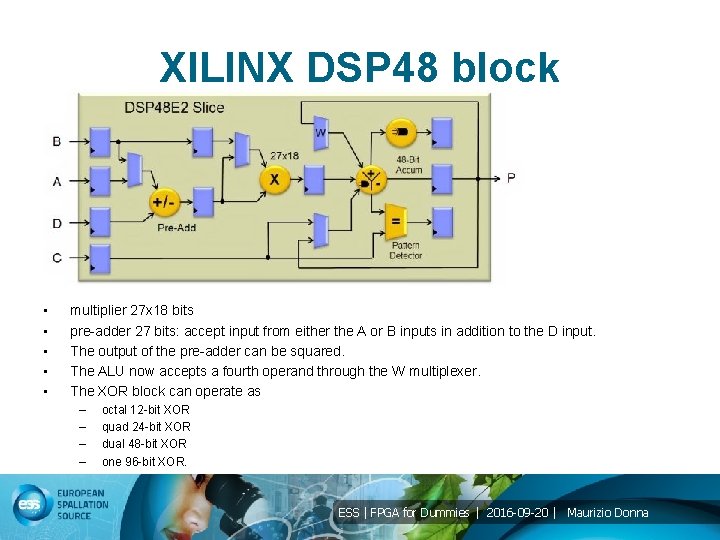

XILINX DSP 48 block • • • multiplier 27 x 18 bits pre-adder 27 bits: accept input from either the A or B inputs in addition to the D input. The output of the pre-adder can be squared. The ALU now accepts a fourth operand through the W multiplexer. The XOR block can operate as – – octal 12 -bit XOR quad 24 -bit XOR dual 48 -bit XOR one 96 -bit XOR. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

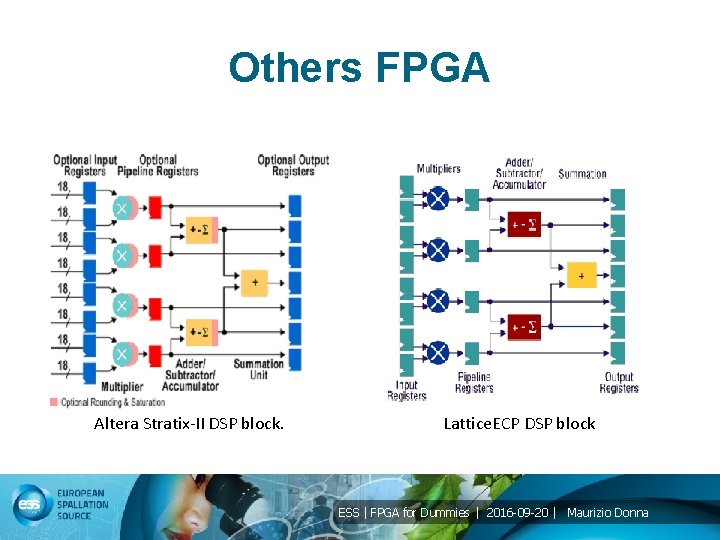

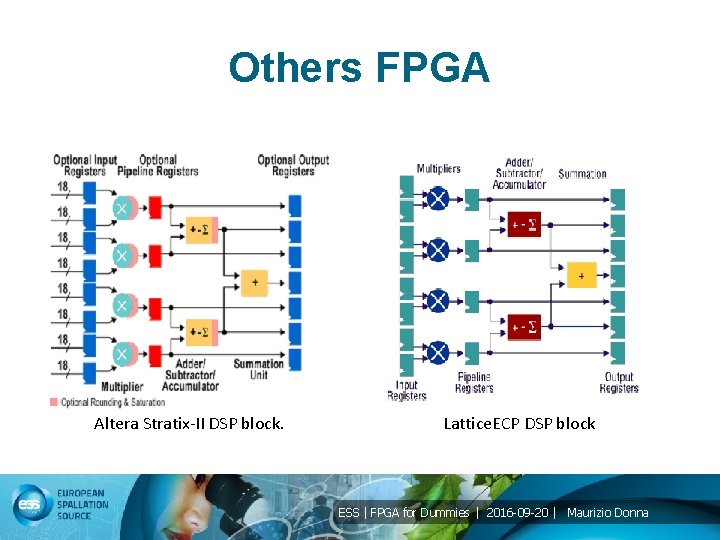

Others FPGA Altera Stratix-II DSP block. Lattice. ECP DSP block ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

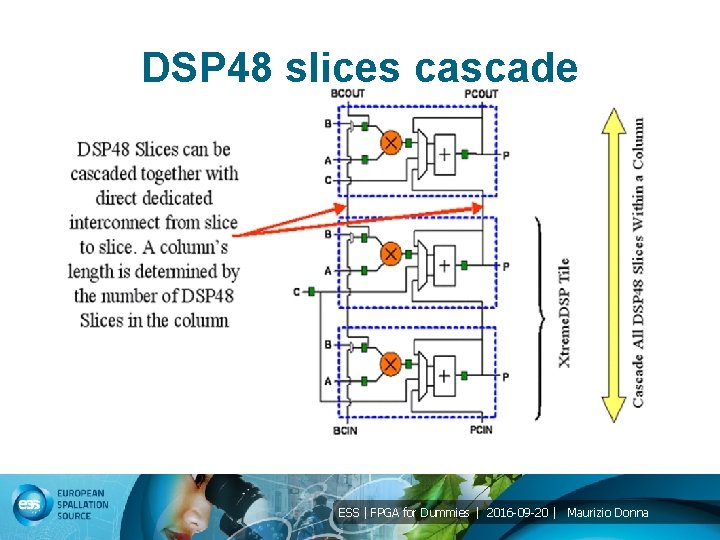

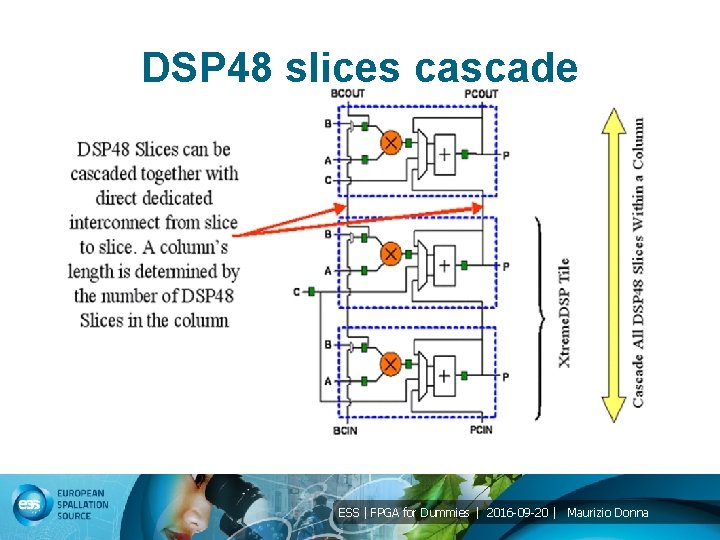

DSP 48 slices cascade ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

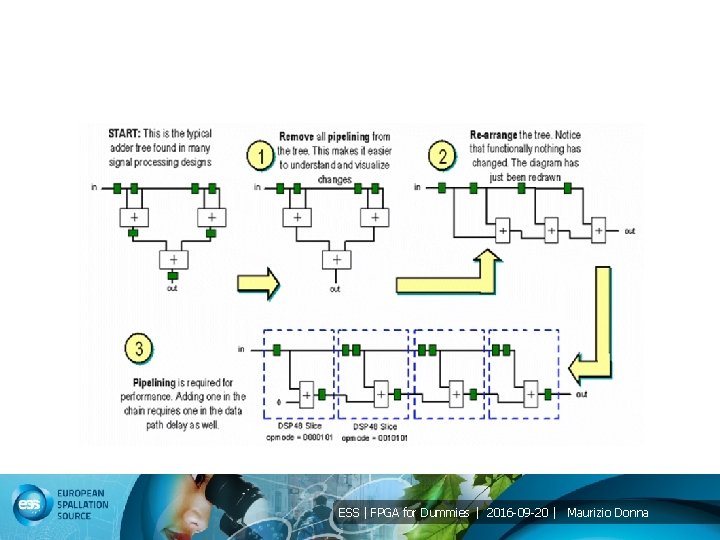

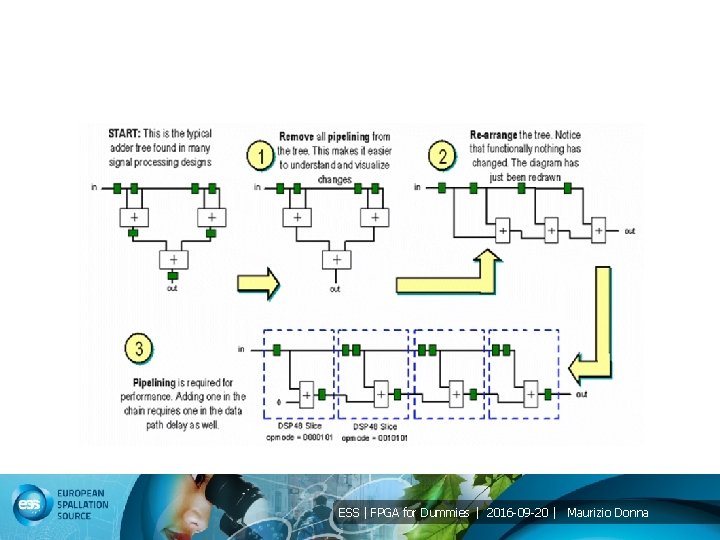

ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

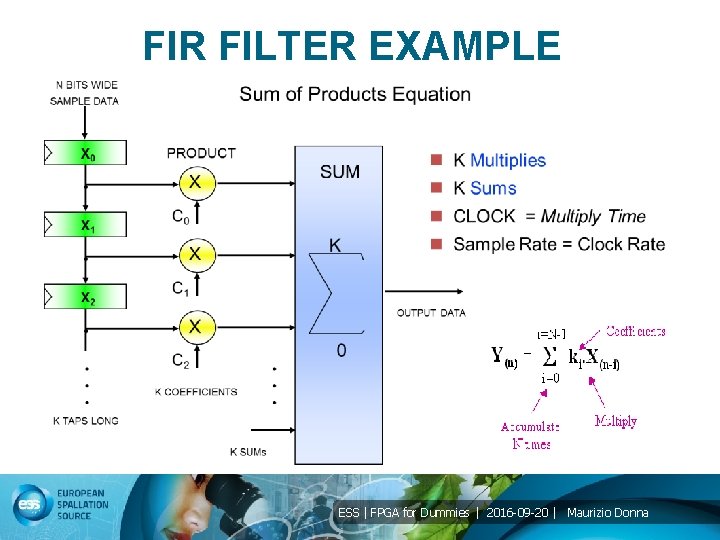

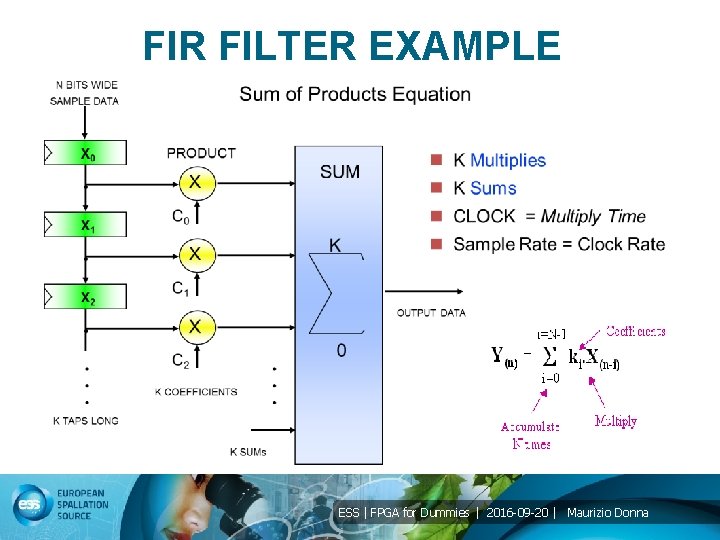

FIR FILTER EXAMPLE ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

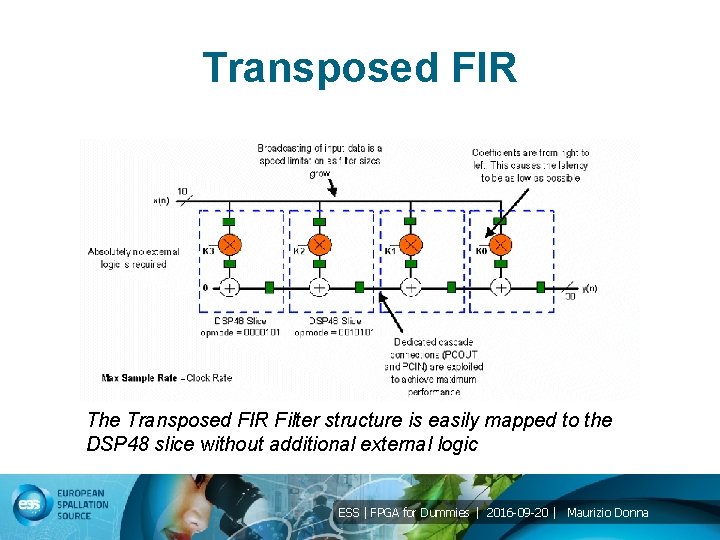

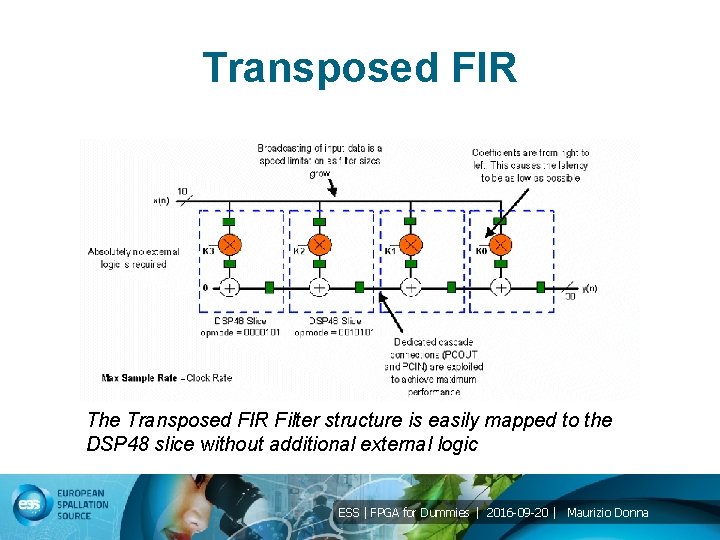

Transposed FIR The Transposed FIR Filter structure is easily mapped to the DSP 48 slice without additional external logic ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

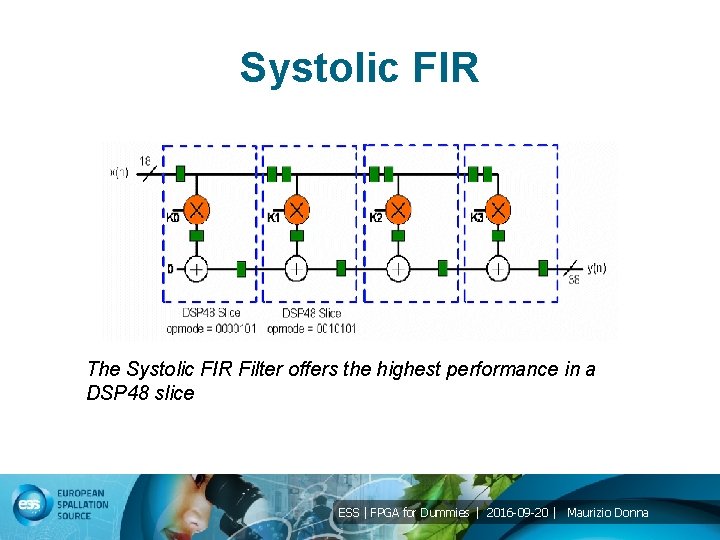

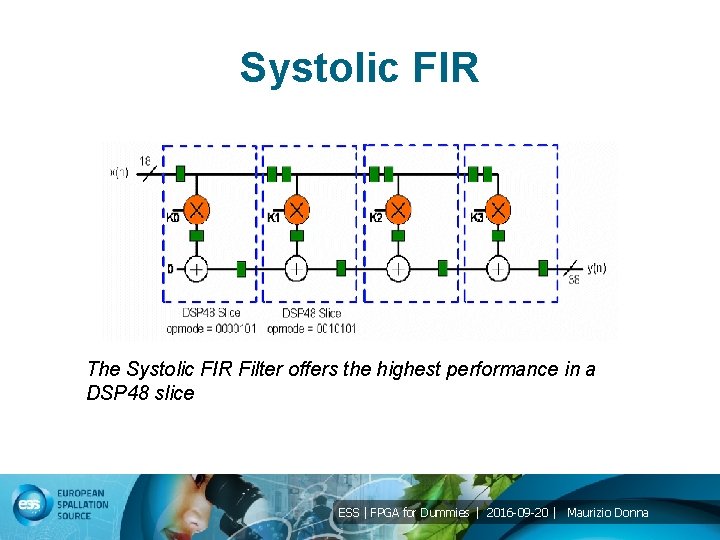

Systolic FIR The Systolic FIR Filter offers the highest performance in a DSP 48 slice ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

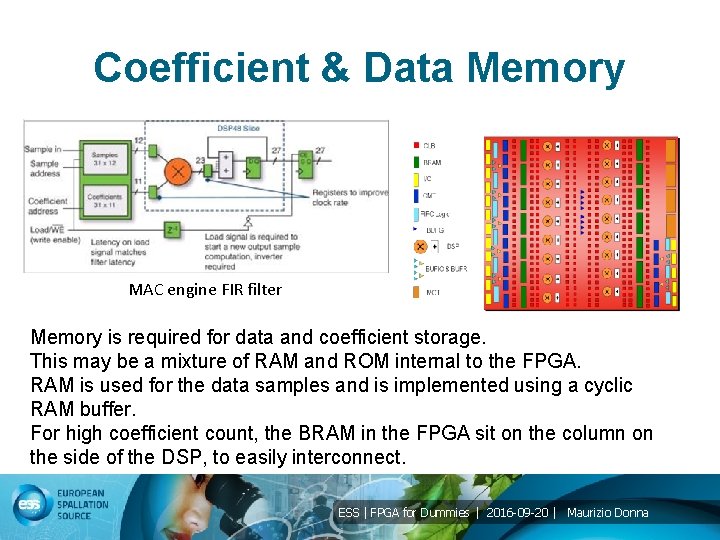

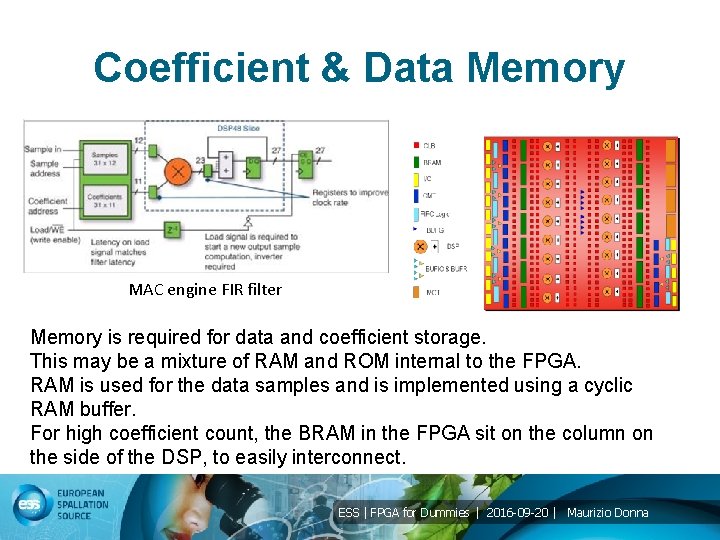

Coefficient & Data Memory MAC engine FIR filter Memory is required for data and coefficient storage. This may be a mixture of RAM and ROM internal to the FPGA. RAM is used for the data samples and is implemented using a cyclic RAM buffer. For high coefficient count, the BRAM in the FPGA sit on the column on the side of the DSP, to easily interconnect. ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

The Fourier Transform • FFT is a mathematical procedure used to determine the harmonic, or frequency, content of a discrete signal sequence; • DFT is the discrete equivalent of the continuous Fourier Transform; ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

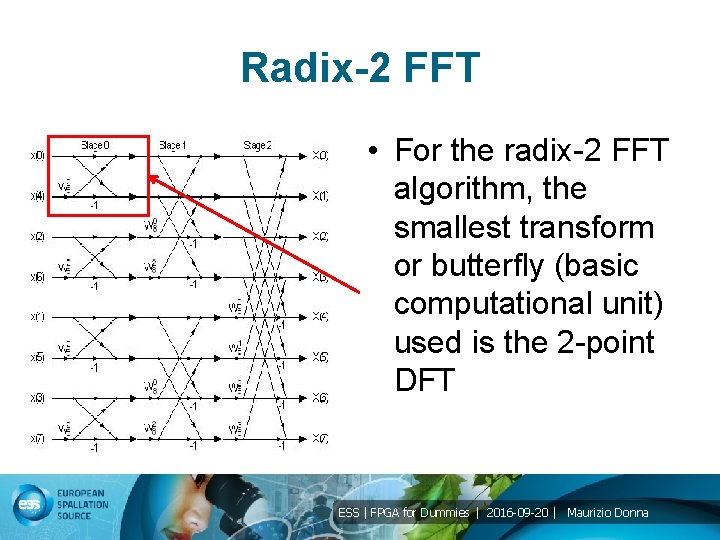

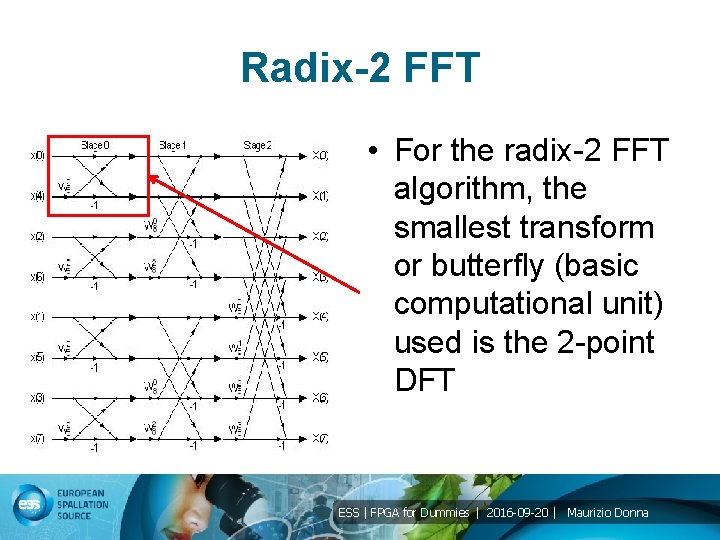

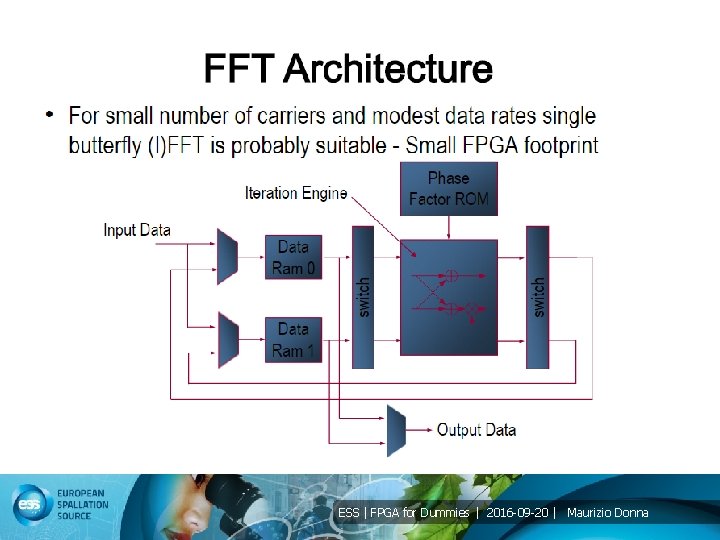

Radix-2 FFT • For the radix-2 FFT algorithm, the smallest transform or butterfly (basic computational unit) used is the 2 -point DFT ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

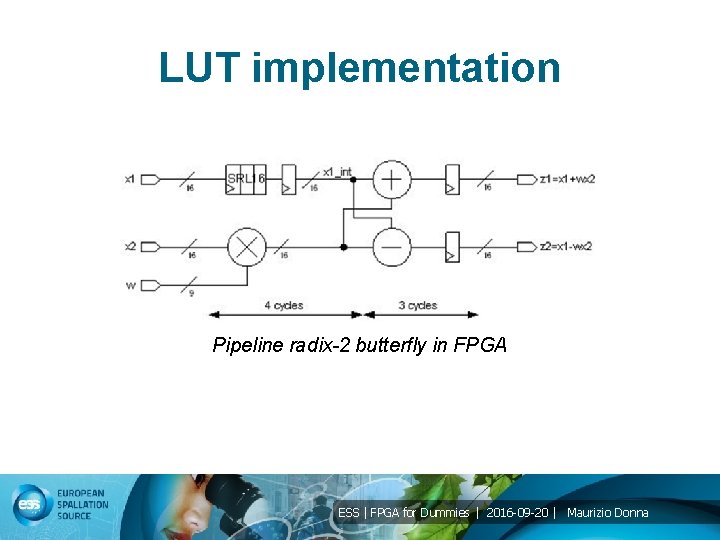

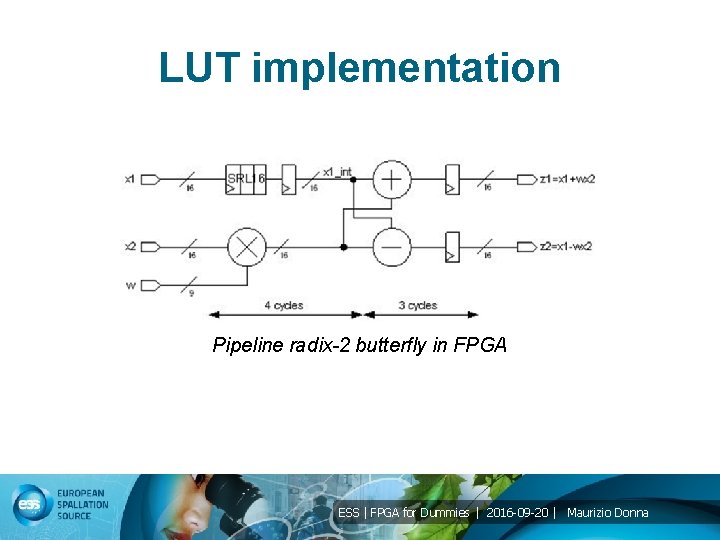

LUT implementation Pipeline radix-2 butterfly in FPGA ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

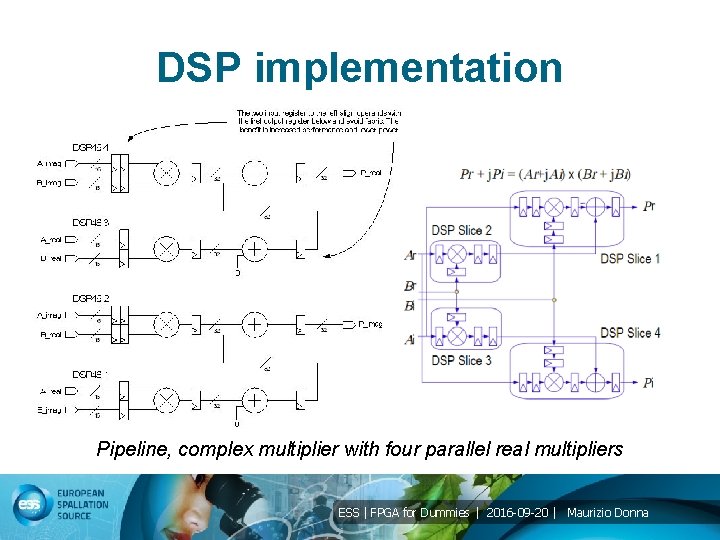

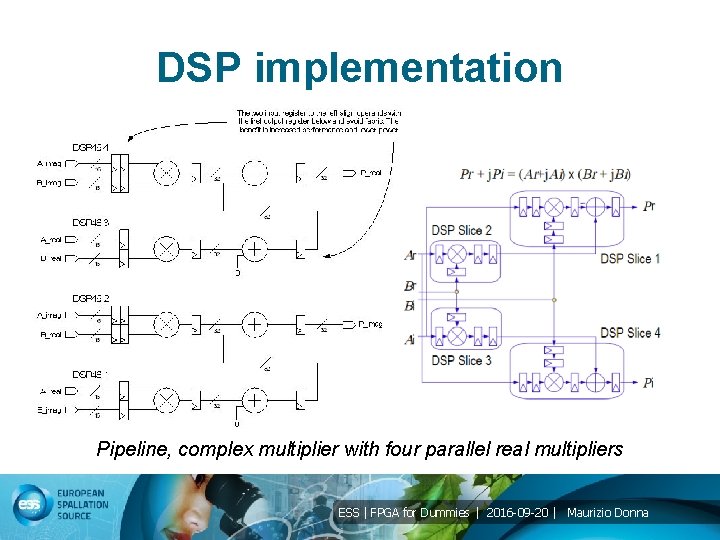

DSP implementation Pipeline, complex multiplier with four parallel real multipliers ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

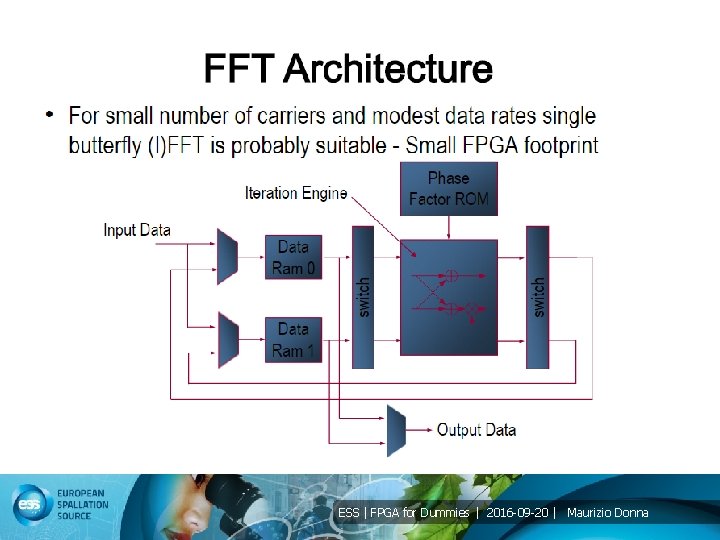

ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

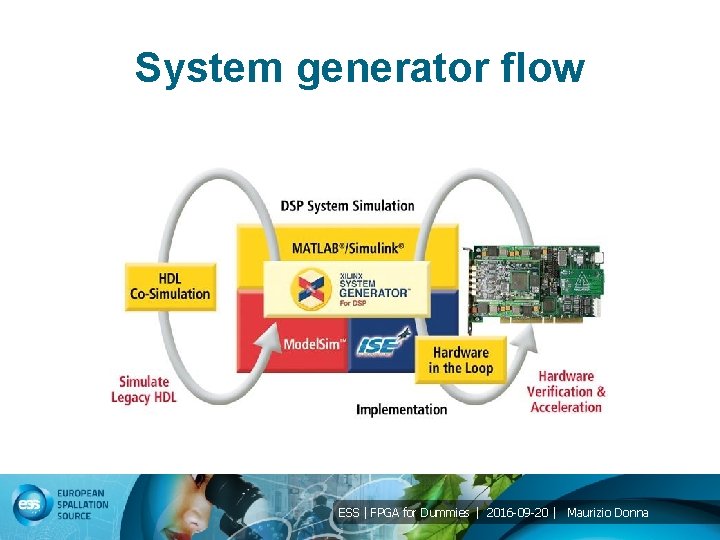

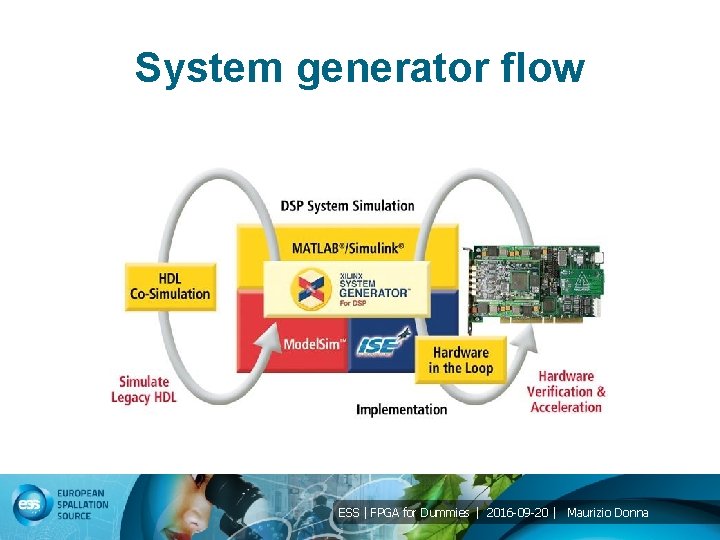

System generator flow ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

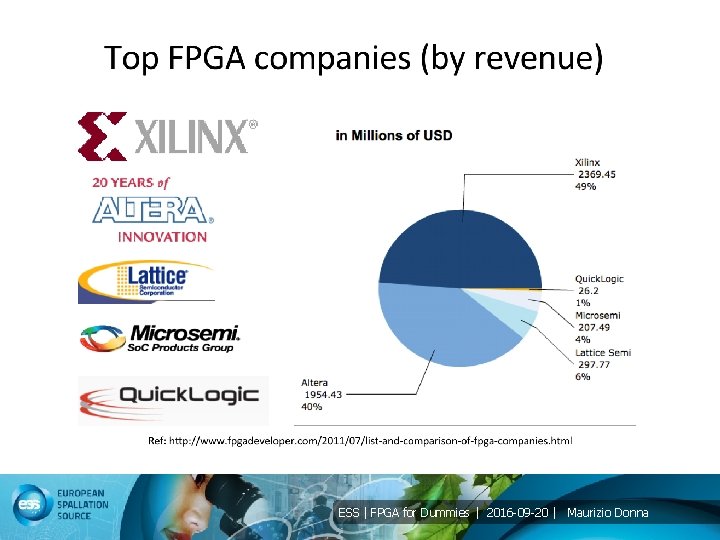

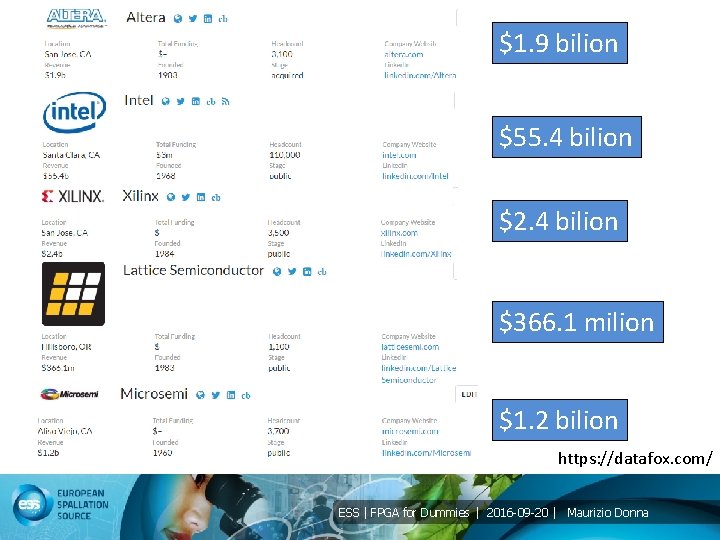

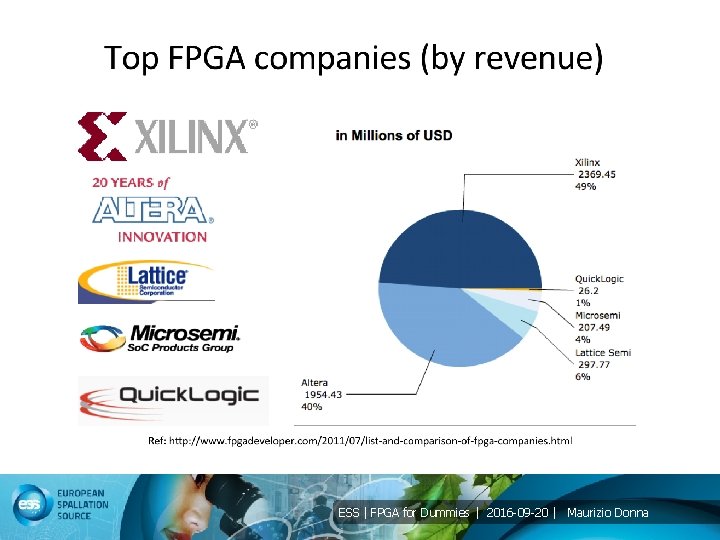

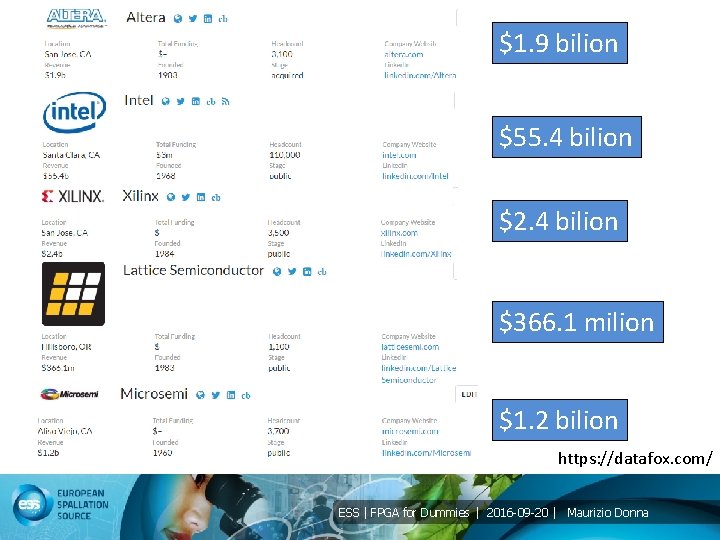

$1. 9 bilion $55. 4 bilion $2. 4 bilion $366. 1 milion $1. 2 bilion https: //datafox. com/ ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

Questions ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna

ESS | FPGA for Dummies | 2016 -09 -20 | Maurizio Donna