Ehsan Shams Saeed Sharifi Tehrani What is DSP

- Slides: 22

Ehsan Shams Saeed Sharifi Tehrani

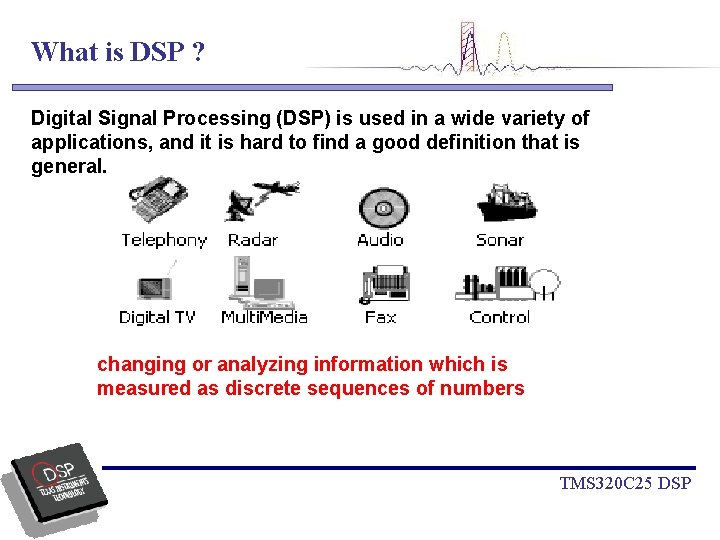

What is DSP ? Digital Signal Processing (DSP) is used in a wide variety of applications, and it is hard to find a good definition that is general. changing or analyzing information which is measured as discrete sequences of numbers TMS 320 C 25 DSP

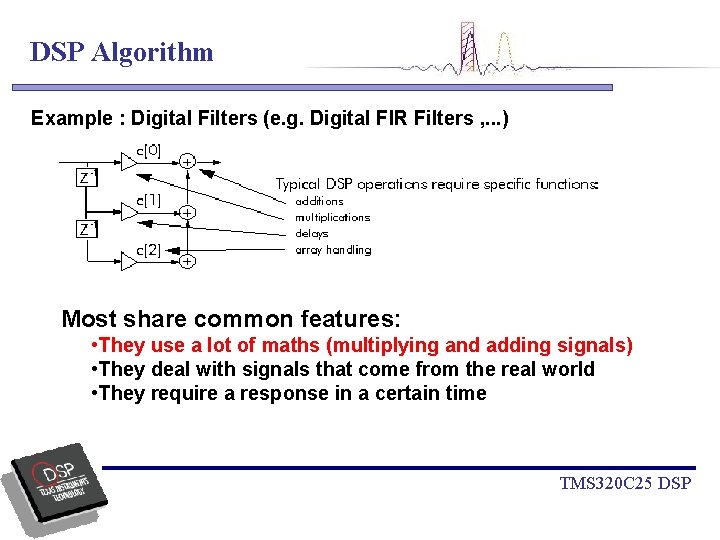

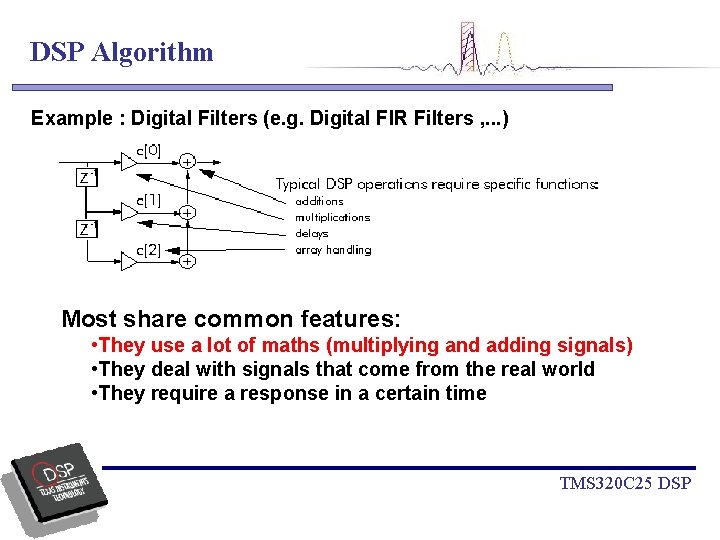

DSP Algorithm Example : Digital Filters (e. g. Digital FIR Filters , . . . ) Most share common features: • They use a lot of maths (multiplying and adding signals) • They deal with signals that come from the real world • They require a response in a certain time TMS 320 C 25 DSP

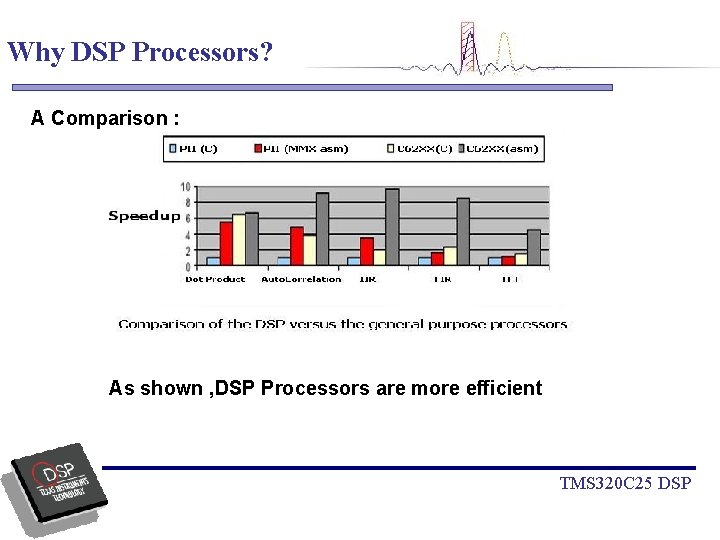

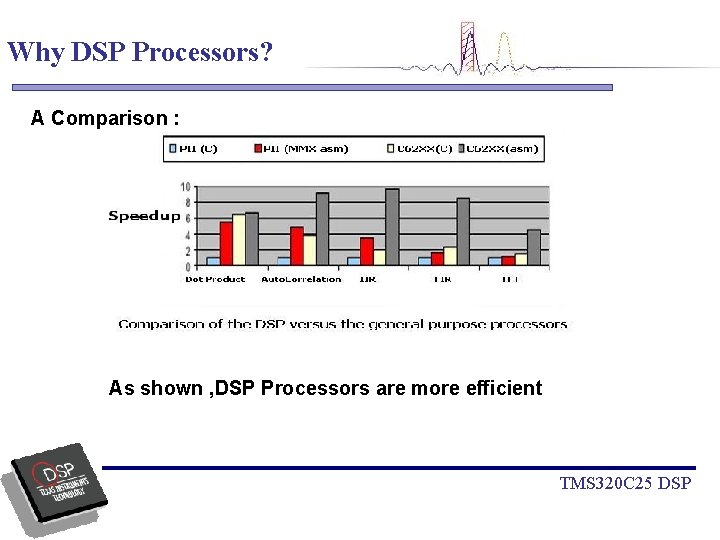

Why DSP Processors? A Comparison : As shown , DSP Processors are more efficient TMS 320 C 25 DSP

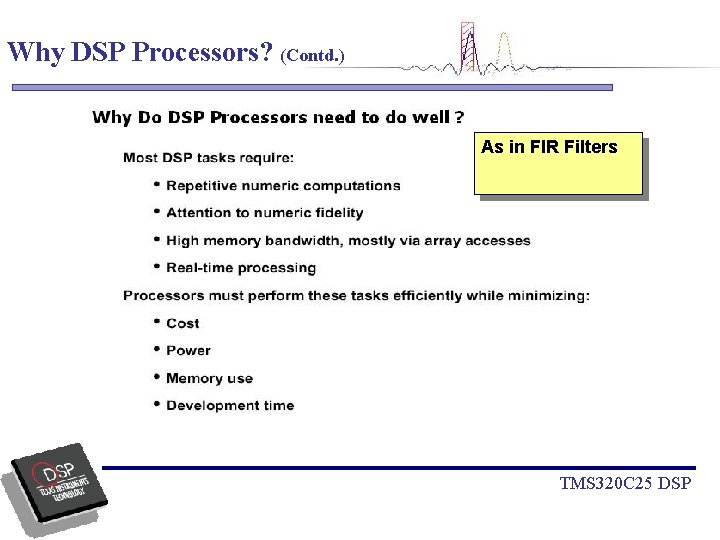

Why DSP Processors? (Contd. ) As in FIR Filters TMS 320 C 25 DSP

Texas Instruments, the company designer and supplier of digital signal processing and analog technologies Six decades of history TI envisions a world where every wireless call, every phone call and every Internet connection is touched by a Digital Signal Processor (DSP). TMS 320 C 25 DSP

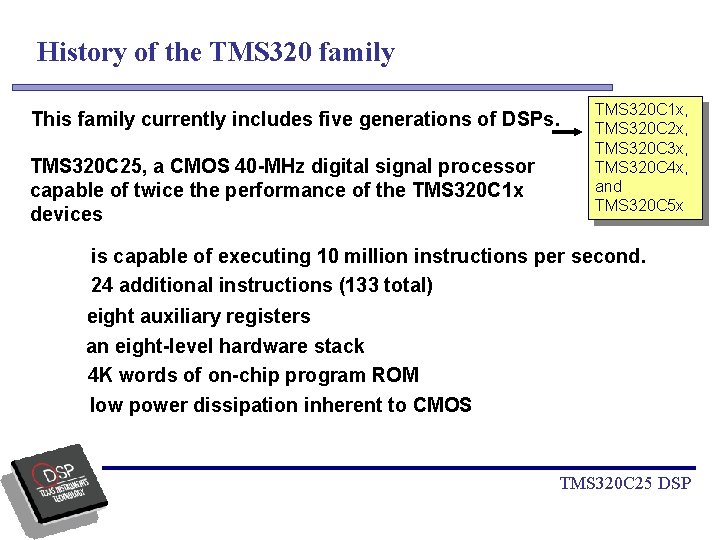

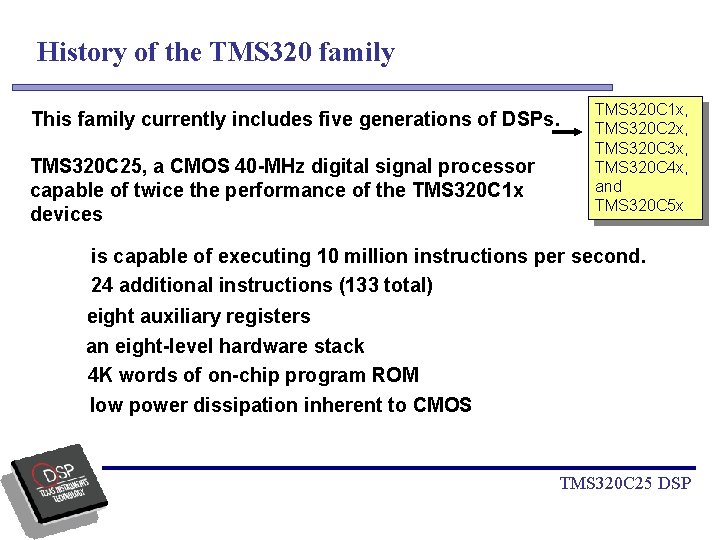

History of the TMS 320 family This family currently includes five generations of DSPs. TMS 320 C 25, a CMOS 40 -MHz digital signal processor capable of twice the performance of the TMS 320 C 1 x devices TMS 320 C 1 x, TMS 320 C 2 x, TMS 320 C 3 x, TMS 320 C 4 x, and TMS 320 C 5 x is capable of executing 10 million instructions per second. 24 additional instructions (133 total) eight auxiliary registers an eight-level hardware stack 4 K words of on-chip program ROM low power dissipation inherent to CMOS TMS 320 C 25 DSP

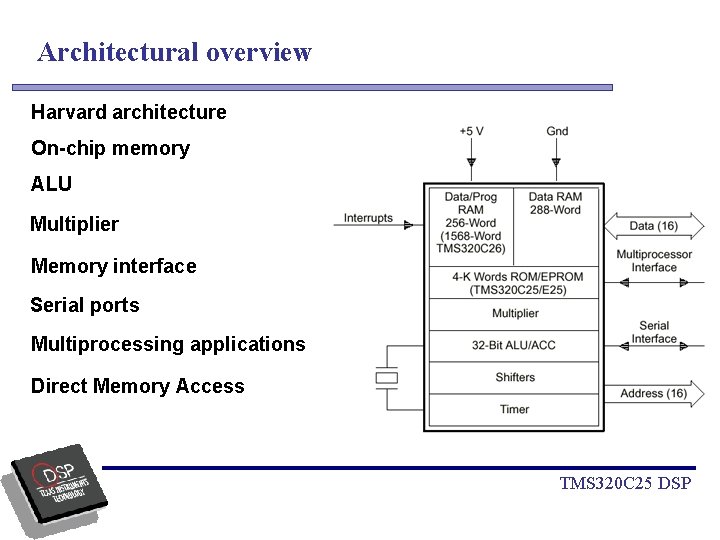

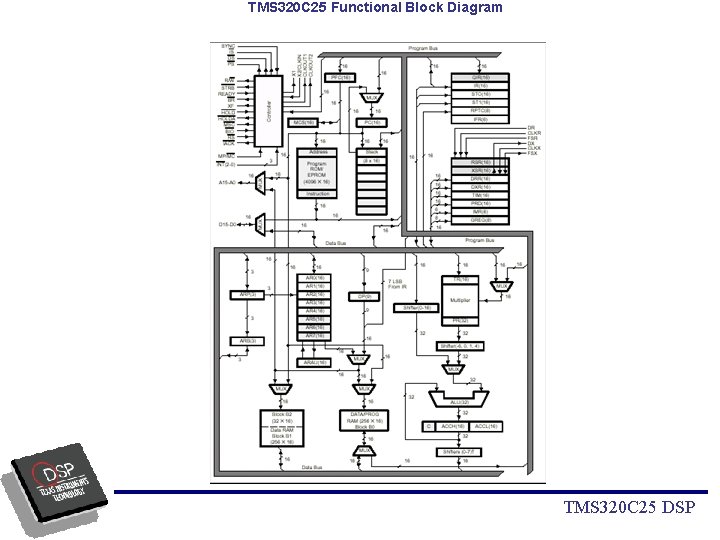

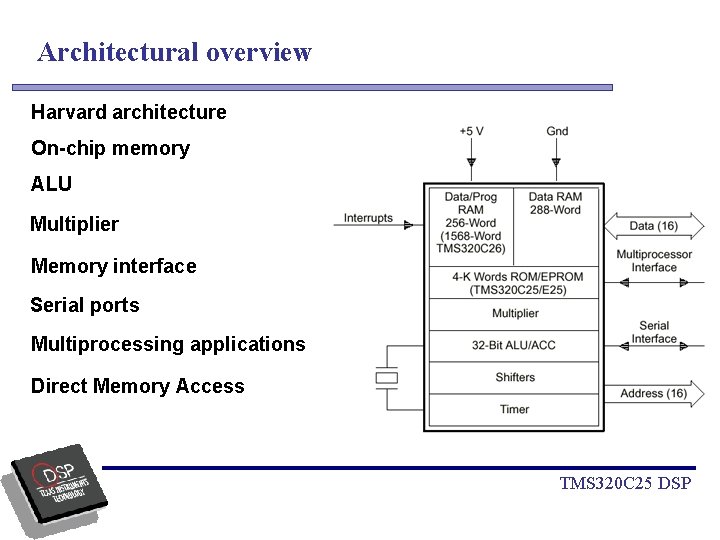

Architectural overview Harvard architecture On-chip memory ALU Multiplier Memory interface Serial ports Multiprocessing applications Direct Memory Access TMS 320 C 25 DSP

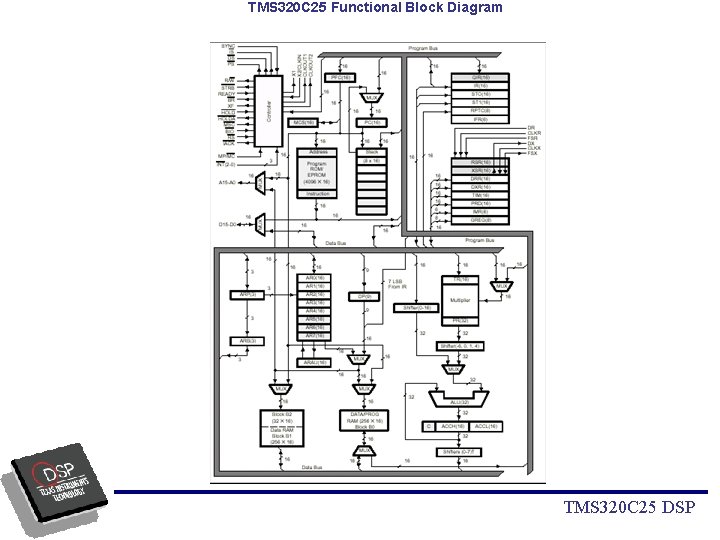

TMS 320 C 25 Functional Block Diagram TMS 320 C 25 DSP

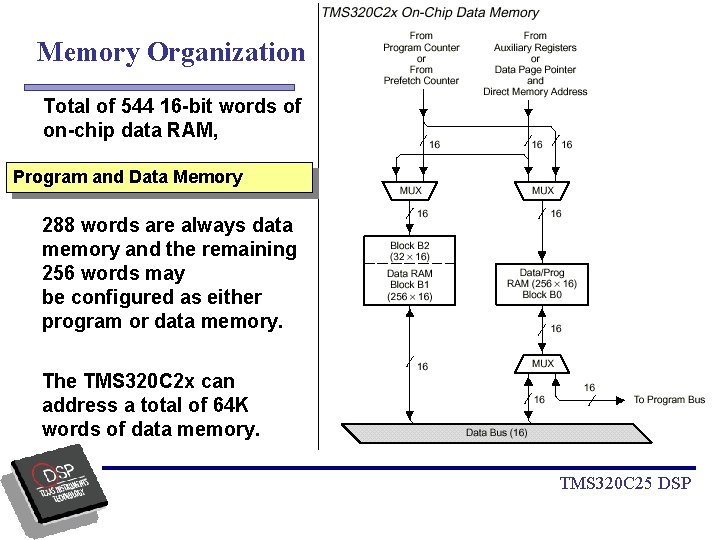

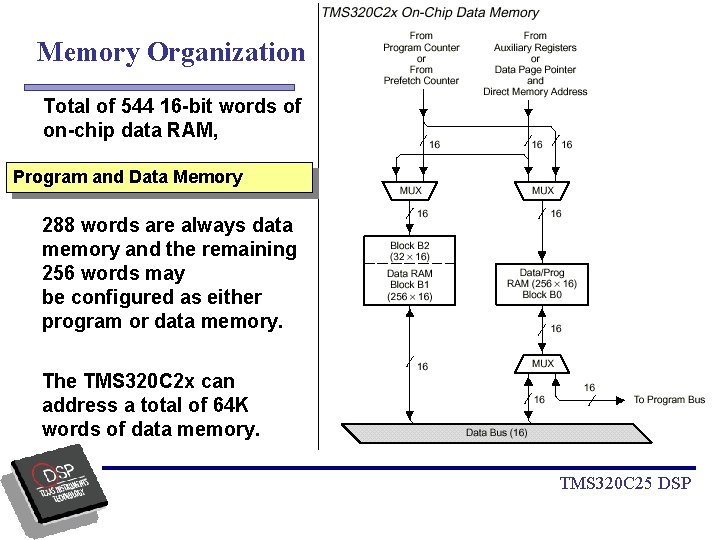

Memory Organization Total of 544 16 -bit words of on-chip data RAM, Program and Data Memory 288 words are always data memory and the remaining 256 words may be configured as either program or data memory. The TMS 320 C 2 x can address a total of 64 K words of data memory. TMS 320 C 25 DSP

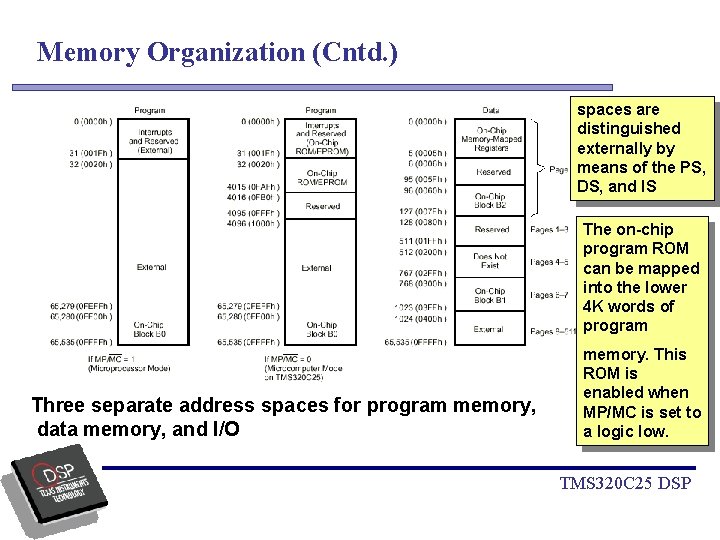

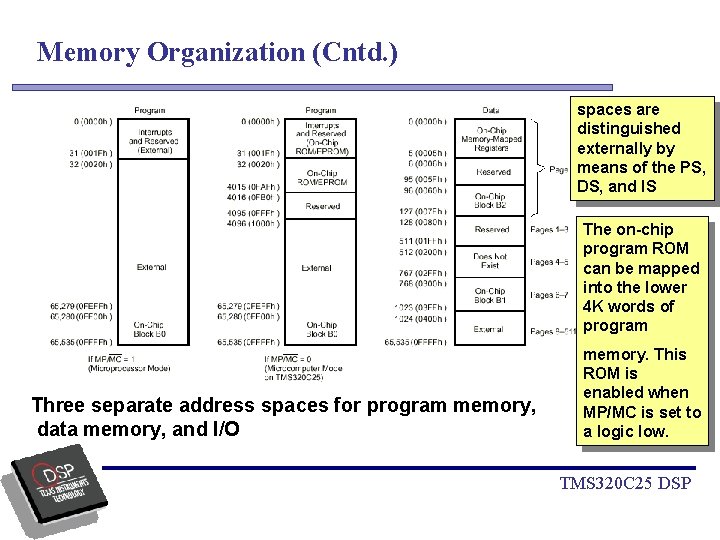

Memory Organization (Cntd. ) spaces are distinguished externally by means of the PS, DS, and IS The on-chip program ROM can be mapped into the lower 4 K words of program Three separate address spaces for program memory, data memory, and I/O memory. This ROM is enabled when MP/MC is set to a logic low. TMS 320 C 25 DSP

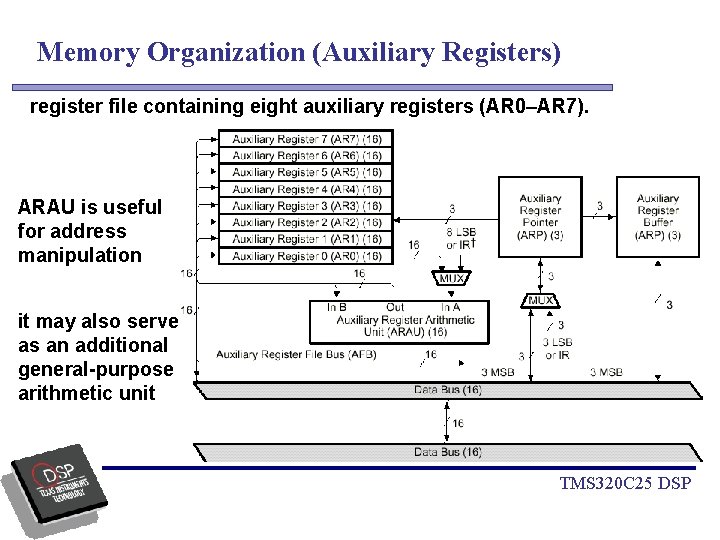

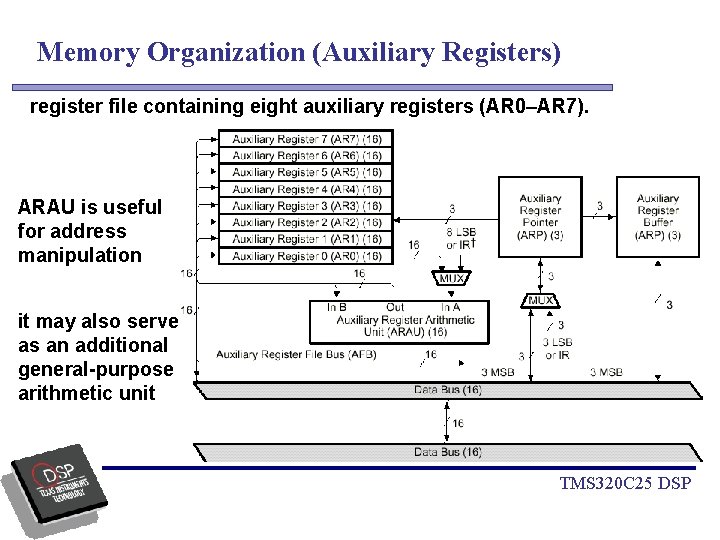

Memory Organization (Auxiliary Registers) register file containing eight auxiliary registers (AR 0–AR 7). ARAU is useful for address manipulation it may also serve as an additional general-purpose arithmetic unit TMS 320 C 25 DSP

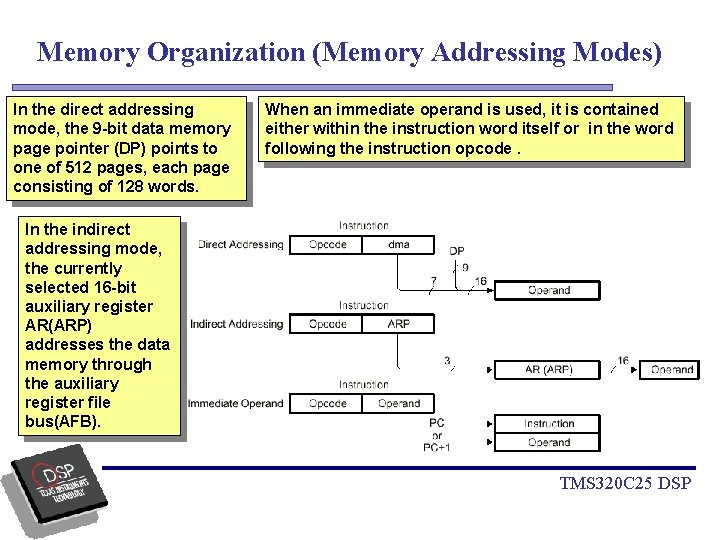

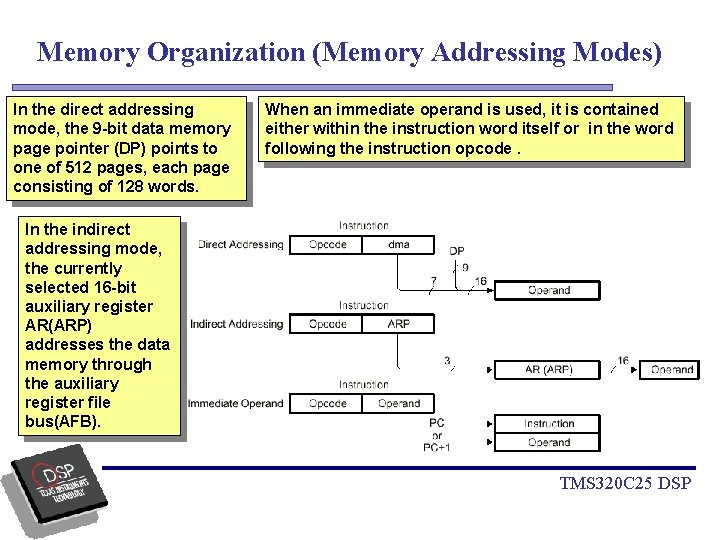

Memory Organization (Memory Addressing Modes) In the direct addressing mode, the 9 -bit data memory page pointer (DP) points to one of 512 pages, each page consisting of 128 words. When an immediate operand is used, it is contained either within the instruction word itself or in the word following the instruction opcode. In the indirect addressing mode, the currently selected 16 -bit auxiliary register AR(ARP) addresses the data memory through the auxiliary register file bus(AFB). TMS 320 C 25 DSP

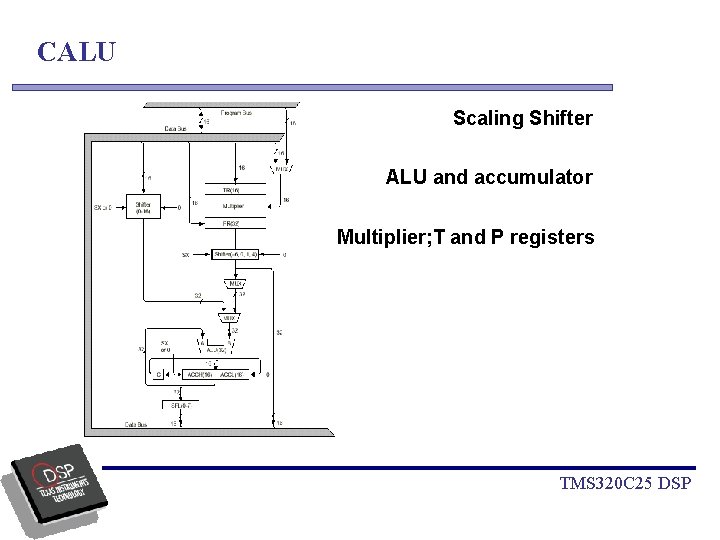

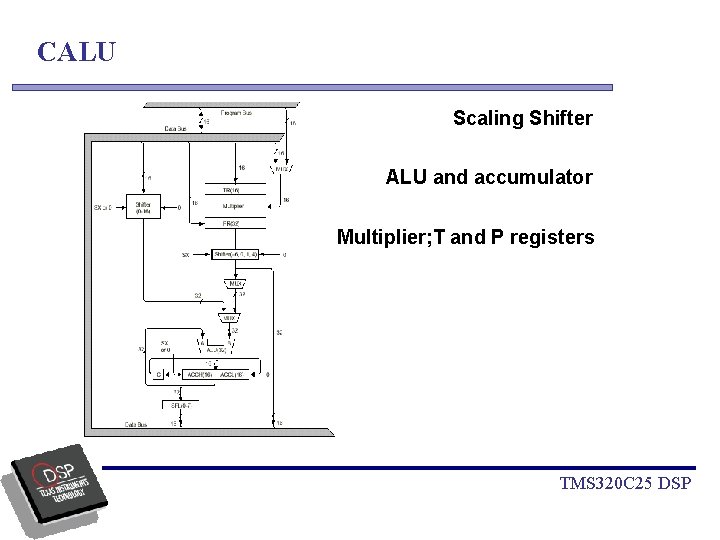

CALU A typical ALU instruction: Scaling Shifter 1) Data is fetched from the RAM on the data bus, 2) Data is passed through the scaling shifter and the ALU and accumulator 3) The result is moved into the accumulator. Multiplier; T and P registers TMS 320 C 25 DSP

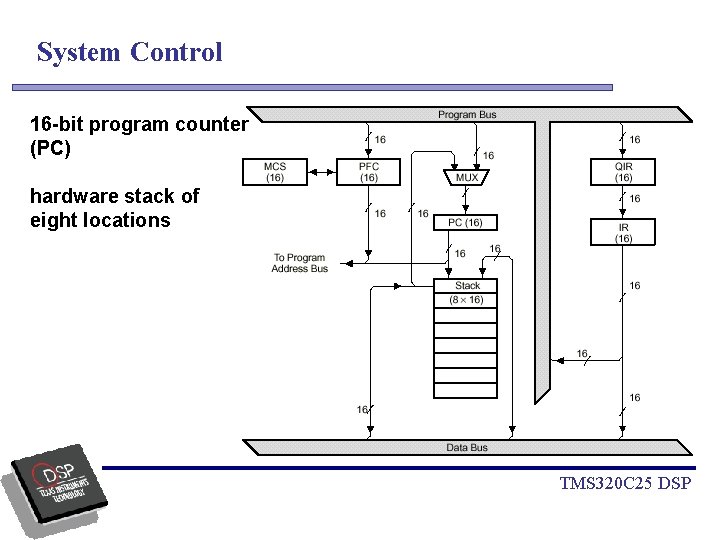

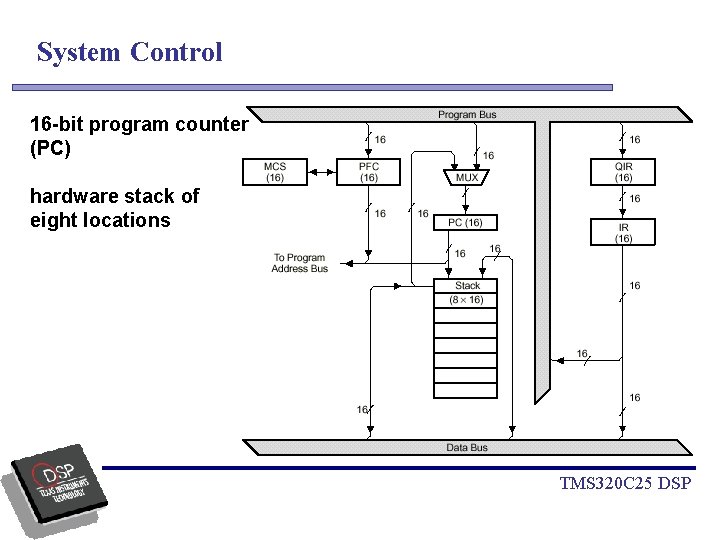

System Control 16 -bit program counter (PC) hardware stack of eight locations TMS 320 C 25 DSP

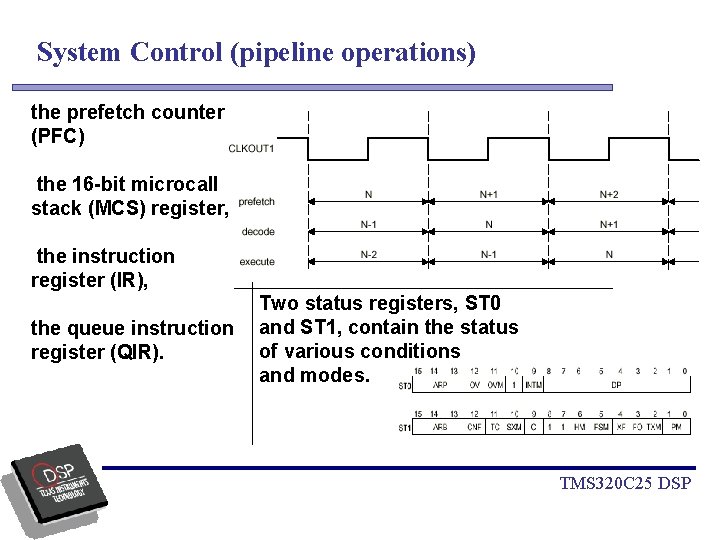

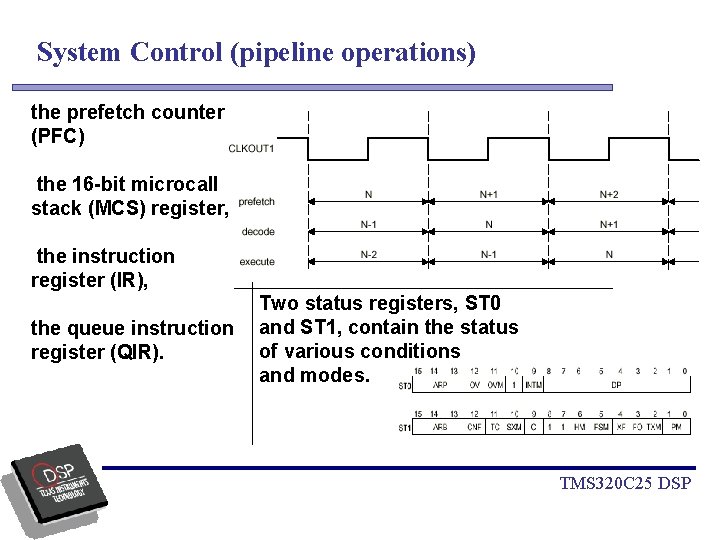

System Control (pipeline operations) the prefetch counter (PFC) the 16 -bit microcall stack (MCS) register, the instruction register (IR), the queue instruction register (QIR). Two status registers, ST 0 and ST 1, contain the status of various conditions and modes. TMS 320 C 25 DSP

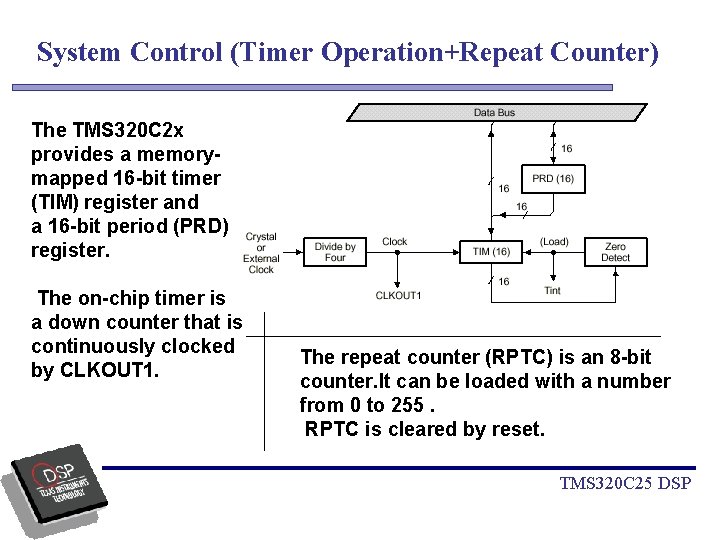

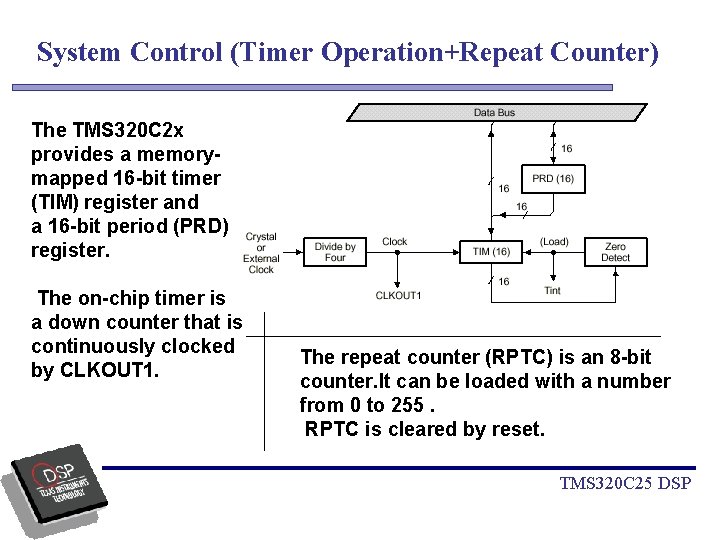

System Control (Timer Operation+Repeat Counter) The TMS 320 C 2 x provides a memorymapped 16 -bit timer (TIM) register and a 16 -bit period (PRD) register. The on-chip timer is a down counter that is continuously clocked by CLKOUT 1. The repeat counter (RPTC) is an 8 -bit counter. It can be loaded with a number from 0 to 255. RPTC is cleared by reset. TMS 320 C 25 DSP

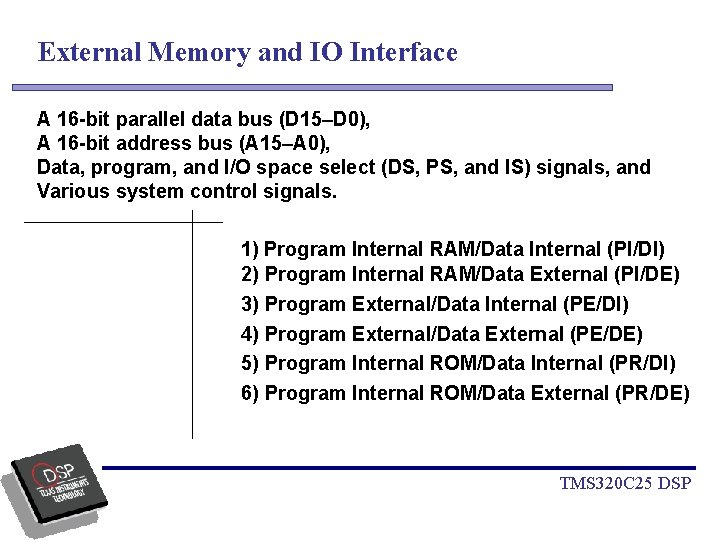

External Memory and IO Interface A 16 -bit parallel data bus (D 15–D 0), A 16 -bit address bus (A 15–A 0), Data, program, and I/O space select (DS, PS, and IS) signals, and Various system control signals. 1) Program Internal RAM/Data Internal (PI/DI) 2) Program Internal RAM/Data External (PI/DE) 3) Program External/Data Internal (PE/DI) 4) Program External/Data External (PE/DE) 5) Program Internal ROM/Data Internal (PR/DI) 6) Program Internal ROM/Data External (PR/DE) TMS 320 C 25 DSP

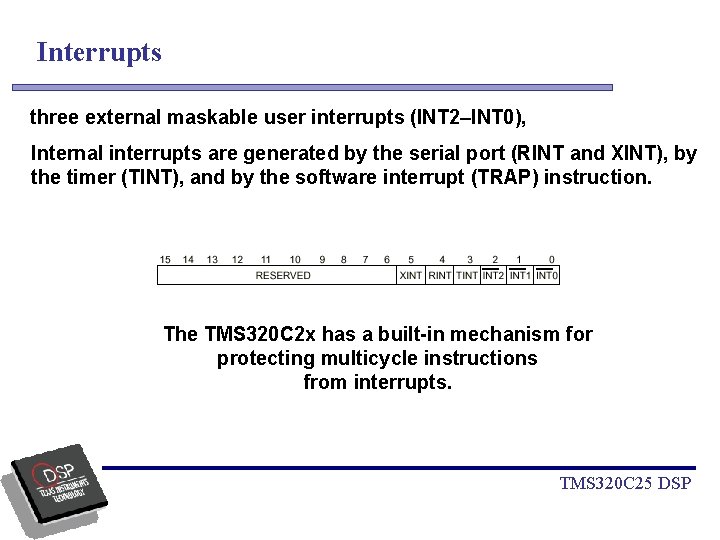

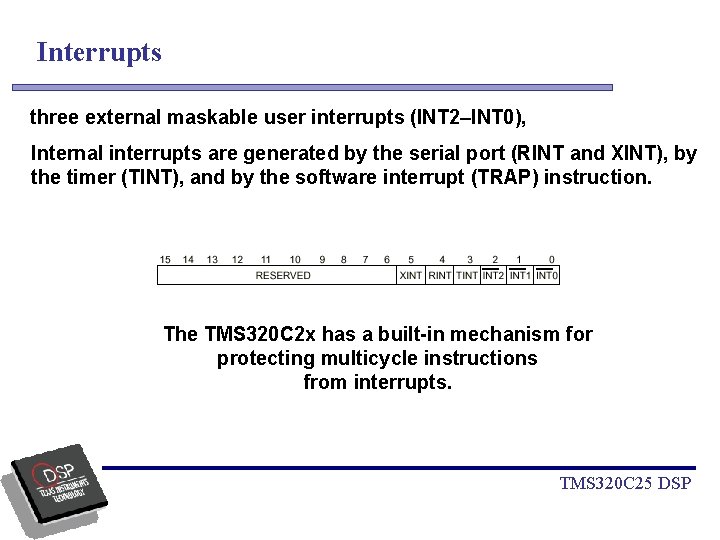

Interrupts three external maskable user interrupts (INT 2–INT 0), Internal interrupts are generated by the serial port (RINT and XINT), by the timer (TINT), and by the software interrupt (TRAP) instruction. The TMS 320 C 2 x has a built-in mechanism for protecting multicycle instructions from interrupts. TMS 320 C 25 DSP

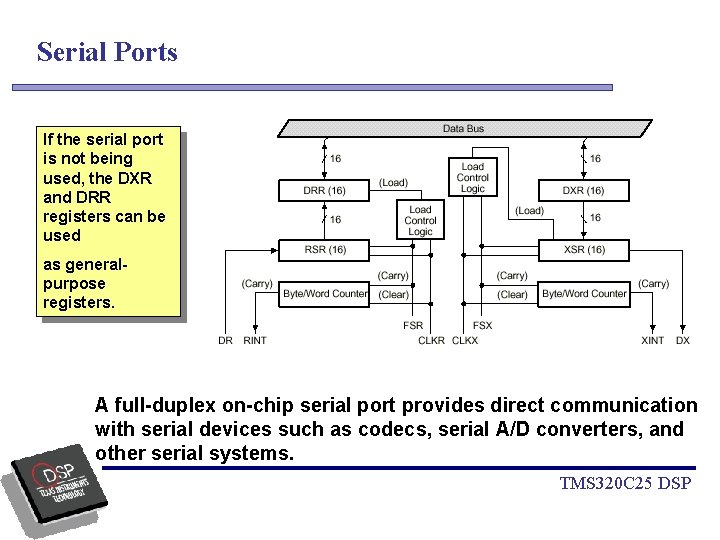

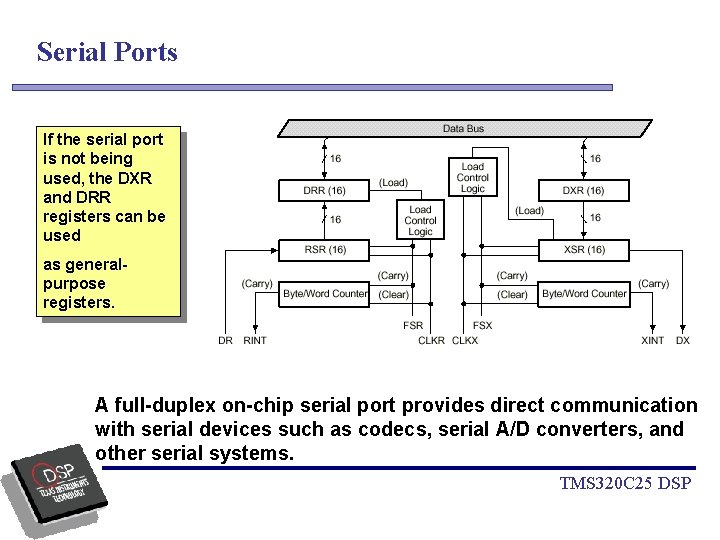

Serial Ports If the serial port is not being used, the DXR and DRR registers can be used as generalpurpose registers. A full-duplex on-chip serial port provides direct communication with serial devices such as codecs, serial A/D converters, and other serial systems. TMS 320 C 25 DSP

Direct Memory Access The flexibility of theenvironment, TMS 320 C 2 x allows configurations satisfy In a multiprocessor the SYNC input can betoused a wide range system requirements: to greatly easeofinterface between processors. A standalone systemapplications, (single processor), For multiprocessing the TMS 320 C 2 xs allocates global data memory space and communicates with that space A with devices in parallel, viamultiprocessor the BR (bus request) and READY control signals. A host/slave multiprocessor with shared global data memory space A peripheral processor TMS 320 C 25 DSP