Diseo Microelectrnico II Captulo 3 MEMORIAS SEMICONDUCTORAS Circuitos

![7. Memoria Flash de 1 Gbit From [Nakamura 02] Sense Latches (1024 + 32) 7. Memoria Flash de 1 Gbit From [Nakamura 02] Sense Latches (1024 + 32)](https://slidetodoc.com/presentation_image_h2/5afa606ded20c1008c7eea1356251835/image-72.jpg)

![Memoria NAND - Flash de 1 Gbit y From [Nakamura 02] 125 mm 2 Memoria NAND - Flash de 1 Gbit y From [Nakamura 02] 125 mm 2](https://slidetodoc.com/presentation_image_h2/5afa606ded20c1008c7eea1356251835/image-76.jpg)

![Evolución de las Memorias Semiconductoras (hasta la fecha) From [Itoh 01] 1 K 1 Evolución de las Memorias Semiconductoras (hasta la fecha) From [Itoh 01] 1 K 1](https://slidetodoc.com/presentation_image_h2/5afa606ded20c1008c7eea1356251835/image-78.jpg)

- Slides: 80

Diseño Microelectrónico II Capítulo 3: MEMORIAS SEMICONDUCTORAS Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

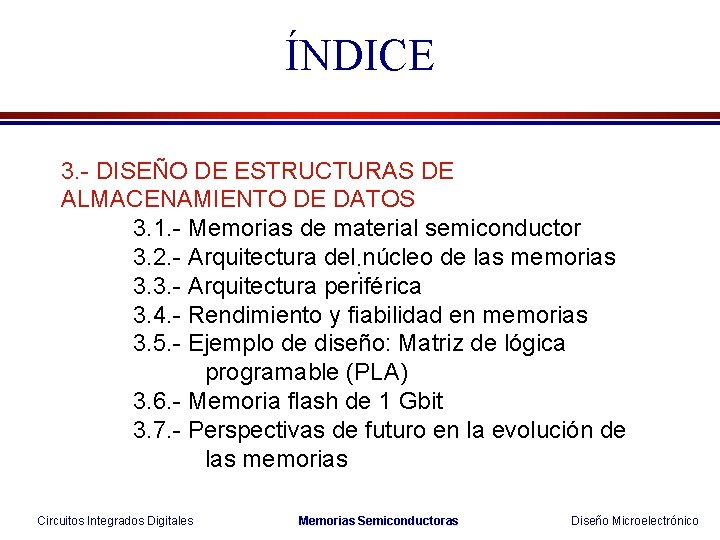

ÍNDICE 3. - DISEÑO DE ESTRUCTURAS DE ALMACENAMIENTO DE DATOS 3. 1. - Memorias de material semiconductor 3. 2. - Arquitectura del: núcleo de las memorias 3. 3. - Arquitectura periférica 3. 4. - Rendimiento y fiabilidad en memorias 3. 5. - Ejemplo de diseño: Matriz de lógica programable (PLA) 3. 6. - Memoria flash de 1 Gbit 3. 7. - Perspectivas de futuro en la evolución de las memorias Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

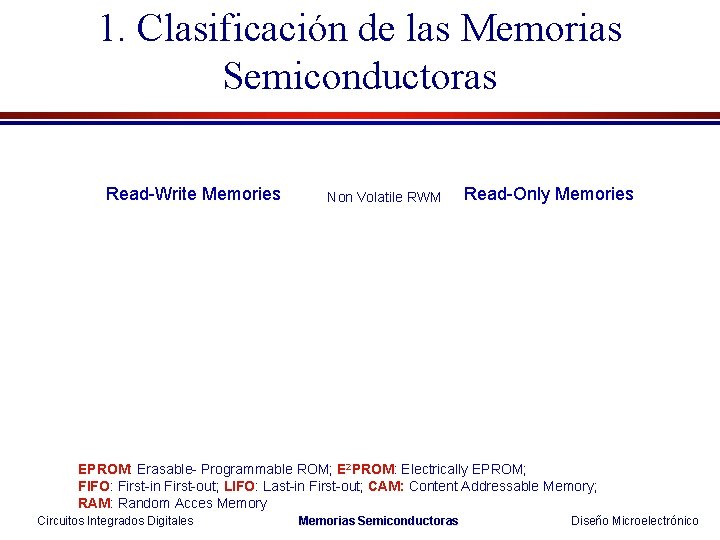

1. Clasificación de las Memorias Semiconductoras Read-Write Memories Non Volatile RWM Read-Only Memories EPROM: Erasable- Programmable ROM; E 2 PROM: Electrically EPROM; FIFO: First-in First-out; LIFO: Last-in First-out; CAM: Content Addressable Memory; RAM: Random Acces Memory Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

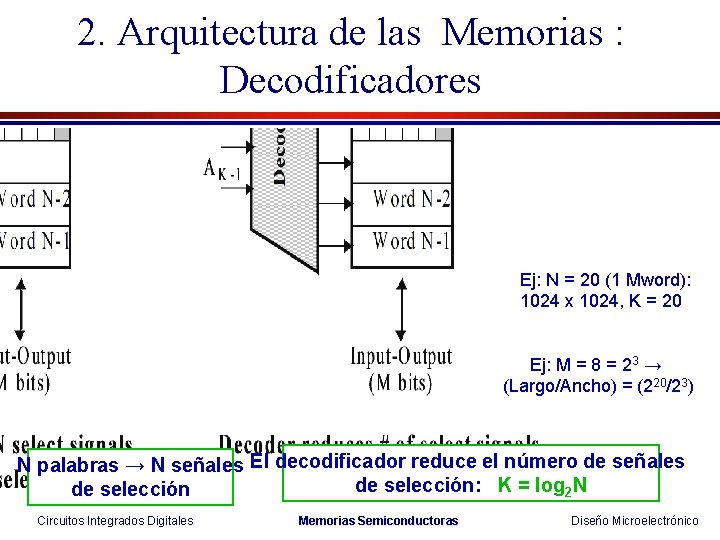

2. Arquitectura de las Memorias : Decodificadores Ej: N = 20 (1 Mword): 1024 x 1024, K = 20 Ej: M = 8 = 23 → (Largo/Ancho) = (220/23) N palabras → N señales El decodificador reduce el número de señales de selección: K = log 2 N de selección Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

Arquitectura matricial Problema: “Aspect Ratio”: altura >> anchura Aceptable entre 64 y 256 Kbits Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

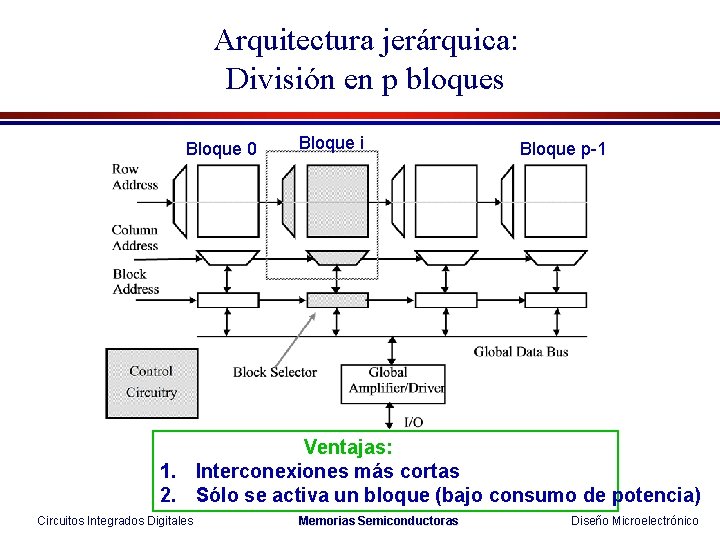

Arquitectura jerárquica: División en p bloques Bloque 0 Bloque i Bloque p-1 Ventajas: 1. Interconexiones más cortas 2. Sólo se activa un bloque (bajo consumo de potencia) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

Definiciones temporales Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

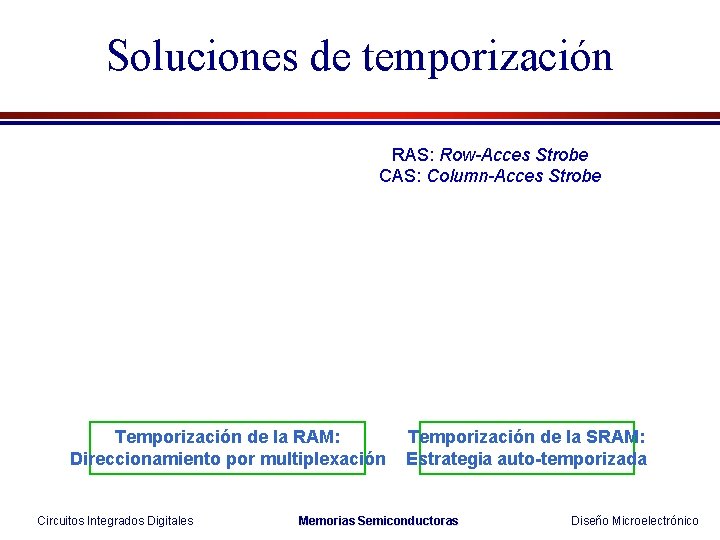

Soluciones de temporización RAS: Row-Acces Strobe CAS: Column-Acces Strobe Temporización de la RAM: Direccionamiento por multiplexación Circuitos Integrados Digitales Temporización de la SRAM: Estrategia auto-temporizada Memorias Semiconductoras Diseño Microelectrónico

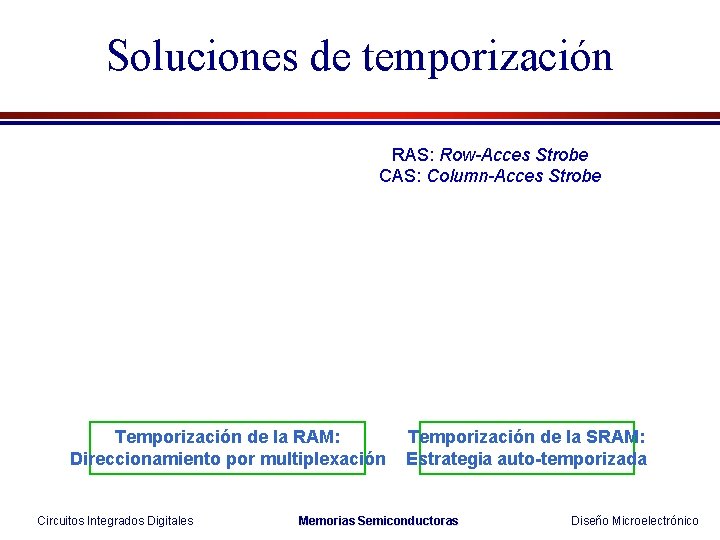

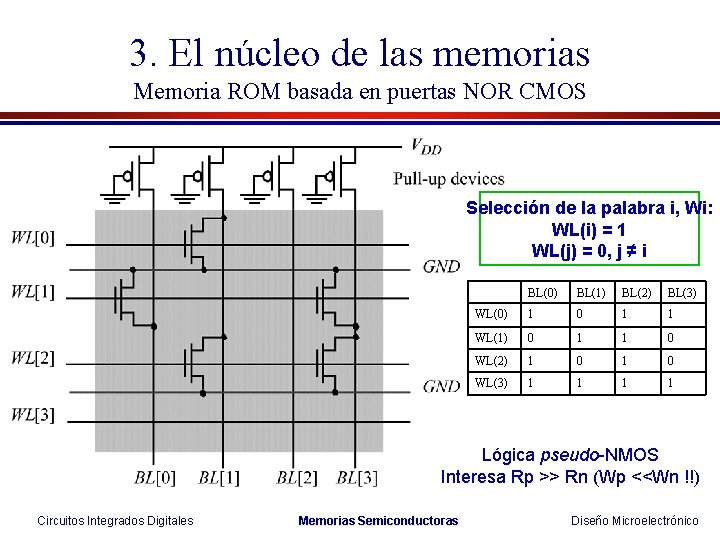

3. El núcleo de las memorias Memoria ROM basada en puertas NOR CMOS Selección de la palabra i, Wi: WL(i) = 1 WL(j) = 0, j ≠ i BL(0) BL(1) BL(2) BL(3) WL(0) 1 0 1 1 WL(1) 0 1 1 0 WL(2) 1 0 WL(3) 1 1 Lógica pseudo-NMOS Interesa Rp >> Rn (Wp <<Wn !!) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

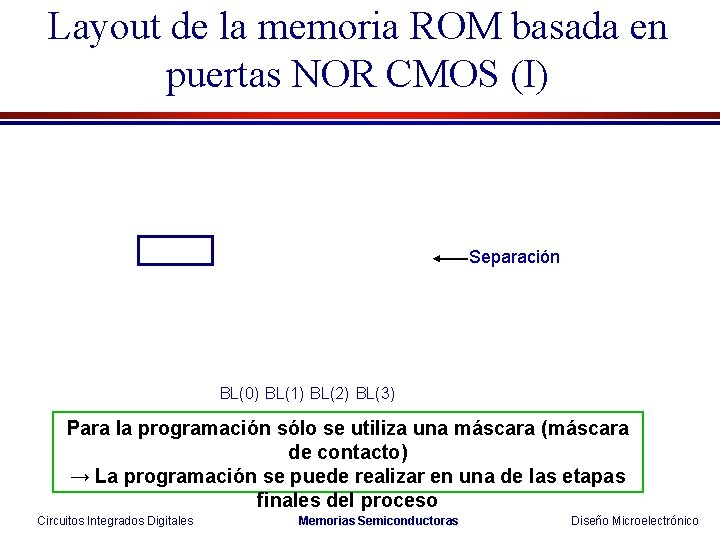

Layout de la memoria ROM basada en puertas NOR CMOS (I) Separación BL(0) BL(1) BL(2) BL(3) Para la programación sólo se utiliza una máscara (máscara de contacto) → La programación se puede realizar en una de las etapas finales del proceso Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

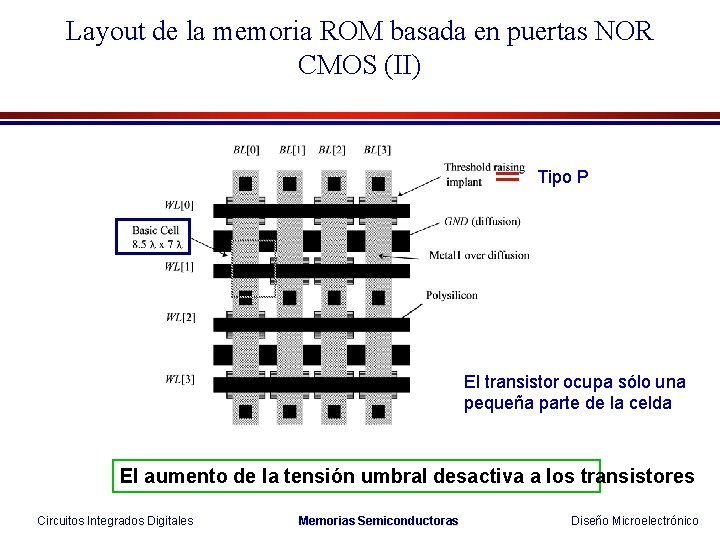

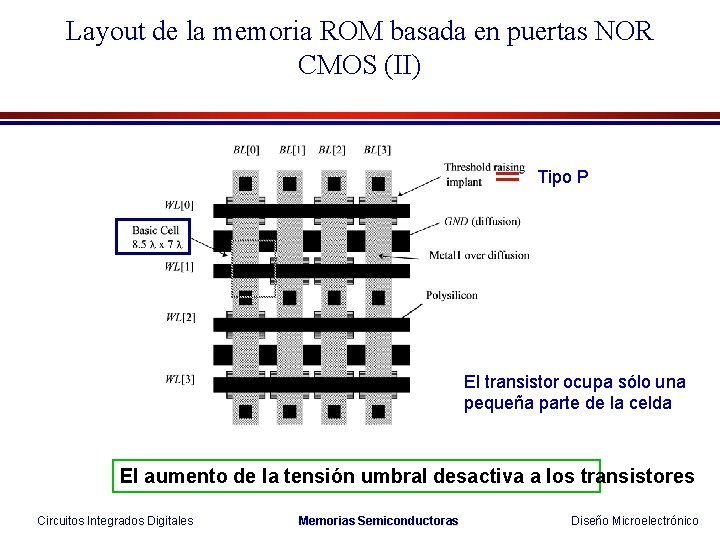

Layout de la memoria ROM basada en puertas NOR CMOS (II) Tipo P El transistor ocupa sólo una pequeña parte de la celda El aumento de la tensión umbral desactiva a los transistores Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

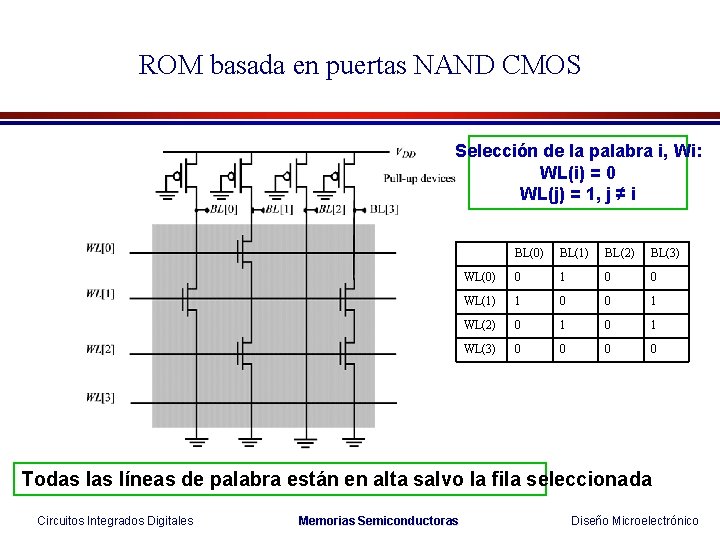

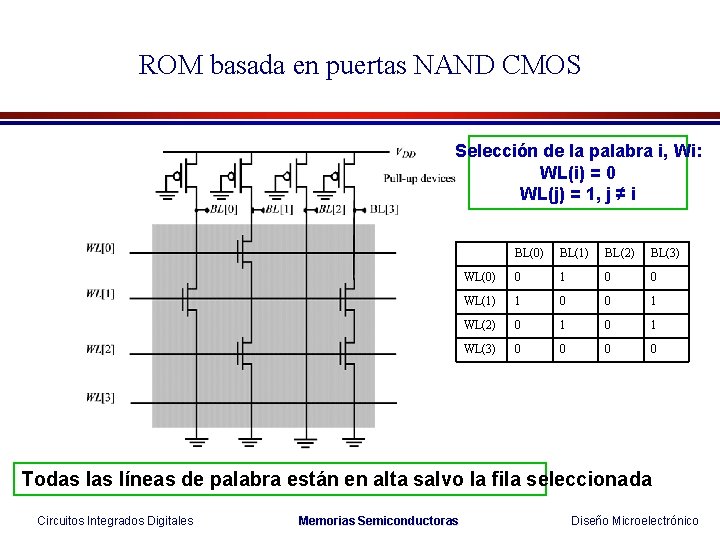

ROM basada en puertas NAND CMOS Selección de la palabra i, Wi: WL(i) = 0 WL(j) = 1, j ≠ i BL(0) BL(1) BL(2) BL(3) WL(0) 0 1 0 0 WL(1) 1 0 0 1 WL(2) 0 1 WL(3) 0 0 Todas líneas de palabra están en alta salvo la fila seleccionada Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

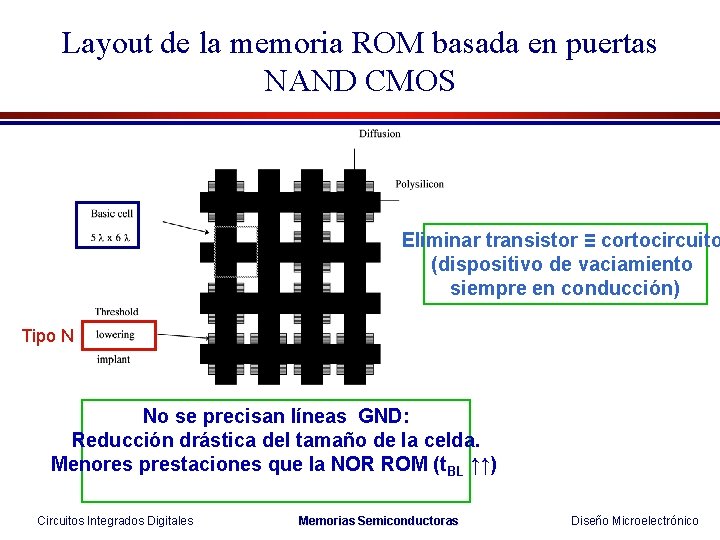

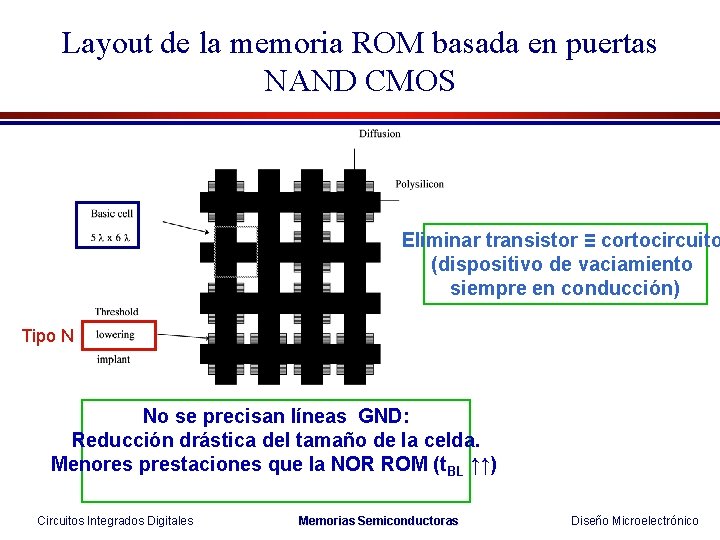

Layout de la memoria ROM basada en puertas NAND CMOS Eliminar transistor ≡ cortocircuito (dispositivo de vaciamiento siempre en conducción) Tipo N No se precisan líneas GND: Reducción drástica del tamaño de la celda. Menores prestaciones que la NOR ROM (t. BL ↑↑) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

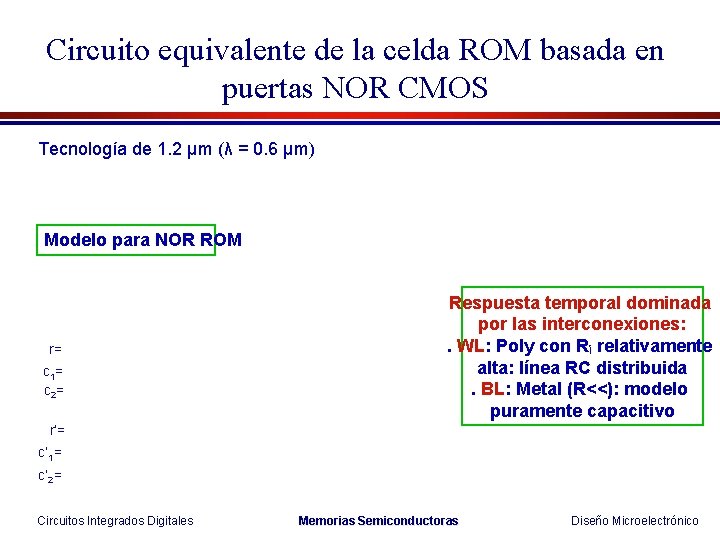

Circuito equivalente de la celda ROM basada en puertas NOR CMOS Tecnología de 1. 2 μm (λ = 0. 6 μm) Modelo para NOR ROM r= c 1= c 2= Respuesta temporal dominada por las interconexiones: . WL: Poly con R ٱ relativamente alta: línea RC distribuida. BL: Metal (R<<): modelo puramente capacitivo r’= c’ 1= c’ 2= Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

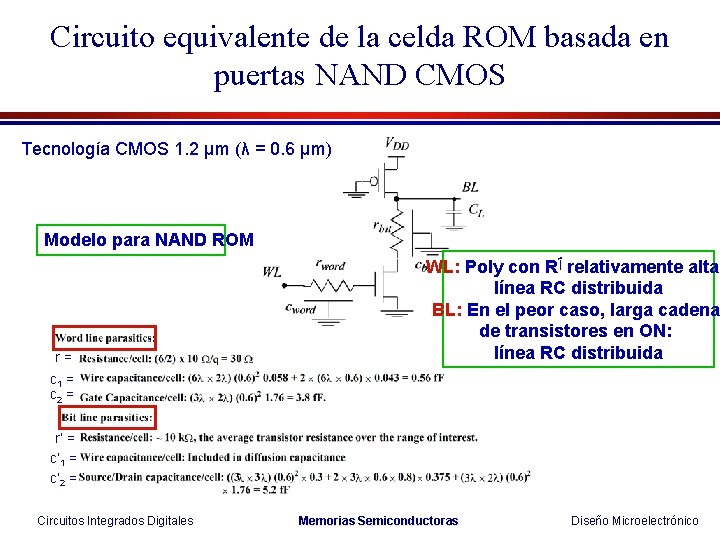

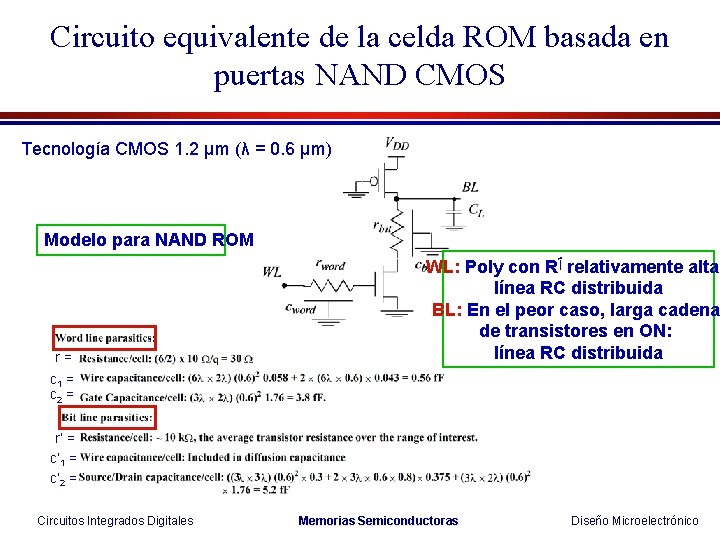

Circuito equivalente de la celda ROM basada en puertas NAND CMOS Tecnología CMOS 1. 2 μm (λ = 0. 6 μm) Modelo para NAND ROM r= WL: Poly con R ٱ relativamente alta: línea RC distribuida BL: En el peor caso, larga cadena de transistores en ON: línea RC distribuida c 1 = c 2 = r’ = c’ 1 = c’ 2 = Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

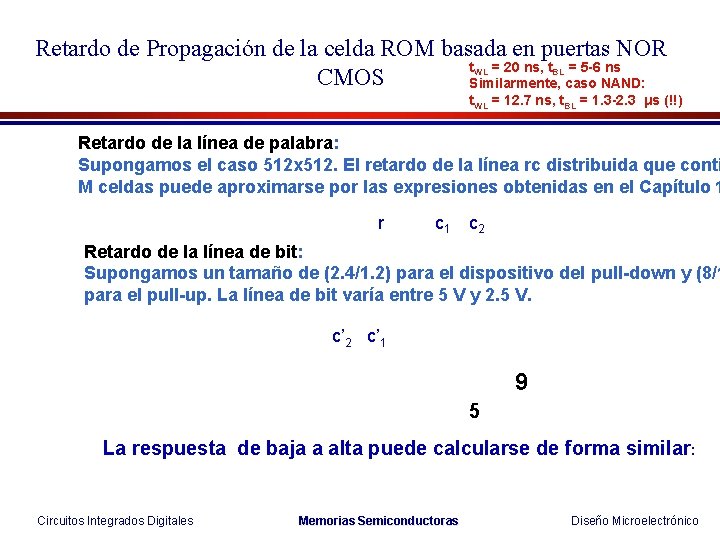

Retardo de Propagación de la celda ROM basada en puertas NOR t = 20 ns, t = 5 -6 ns CMOS Similarmente, caso NAND: WL BL t. WL = 12. 7 ns, t. BL = 1. 3 -2. 3 μs (!!) Retardo de la línea de palabra: Supongamos el caso 512 x 512. El retardo de la línea 1 rc distribuida que conti M celdas puede aproximarse por las expresiones obtenidas en el Capítulo 1 r c 1 c 2 Retardo de la línea de bit: Supongamos un tamaño de (2. 4/1. 2) para el dispositivo del pull-down y (8/1 para el pull-up. La línea de bit varía entre 5 V y 2. 5 V. c’ 2 c’ 1 9 5 La respuesta de baja a alta puede calcularse de forma similar: Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

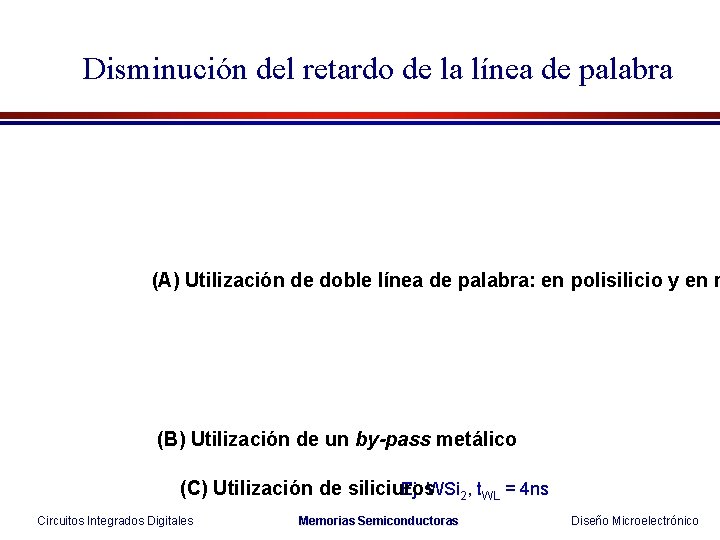

Disminución del retardo de la línea de palabra (A) Utilización de doble línea de palabra: en polisilicio y en m (B) Utilización de un by-pass metálico (C) Utilización de siliciuros Ej: WSi 2, t. WL = 4 ns Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

Memoria ROM precargada basada en puertas NOR CMOS Para soslayar los inconvenientes de la lógica pseudo-NMOS Durante la precarga todos los transistore NMOS deben estar en OFF Los transistores PMOS de precarga pueden hacerse tan grandes como sea necesario, pero ello da lugar a una línea de reloj muy cargada Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

3. 2. Memorias de lectura-escritura no volátiles (NVRWM) Floating-gate avalanche-injection transistor (FAMOS) (a) Sección transversal (b) Símbolo esquemátic MOS → FAMOS: tox → 2 tox VTH programable Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

Programación del transistor FAMOS Al retirar el voltaje de programación. La programación aumenta Inyección por avalancha queda carga atrapada la tensión umbral, VT (~ 7 Borrado de la EPROM: Iluminación U. V. (generación de pares e-h en el Si. O → off system Limitación: # ciclos programación/borrado ≤ 1000 Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

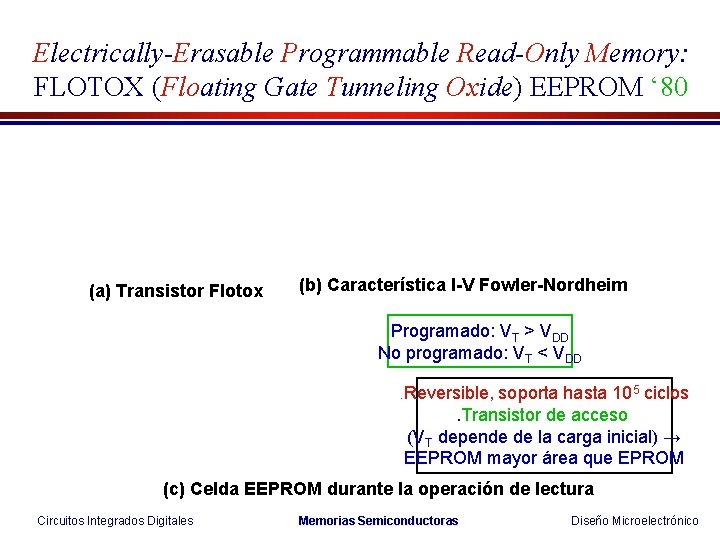

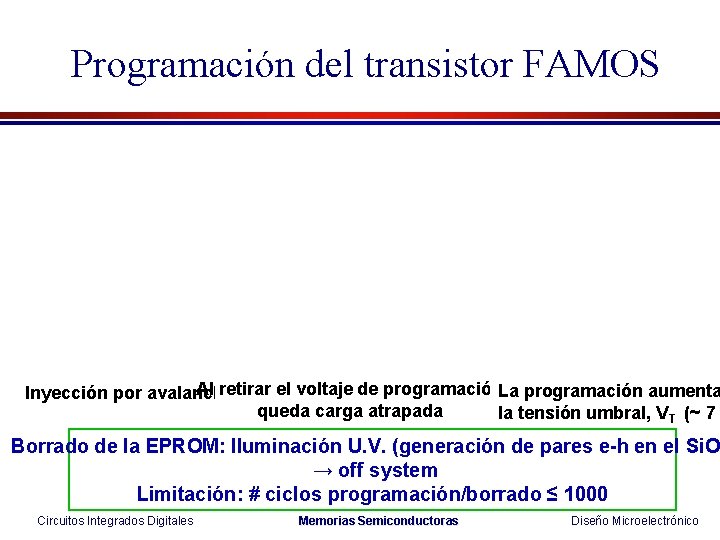

Electrically-Erasable Programmable Read-Only Memory: FLOTOX (Floating Gate Tunneling Oxide) EEPROM ‘ 80 (a) Transistor Flotox (b) Característica I-V Fowler-Nordheim Programado: VT > VDD No programado: VT < VDD. Reversible, soporta hasta 105 ciclos . Transistor de acceso (VT depende de la carga inicial) → EEPROM mayor área que EPROM (c) Celda EEPROM durante la operación de lectura Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

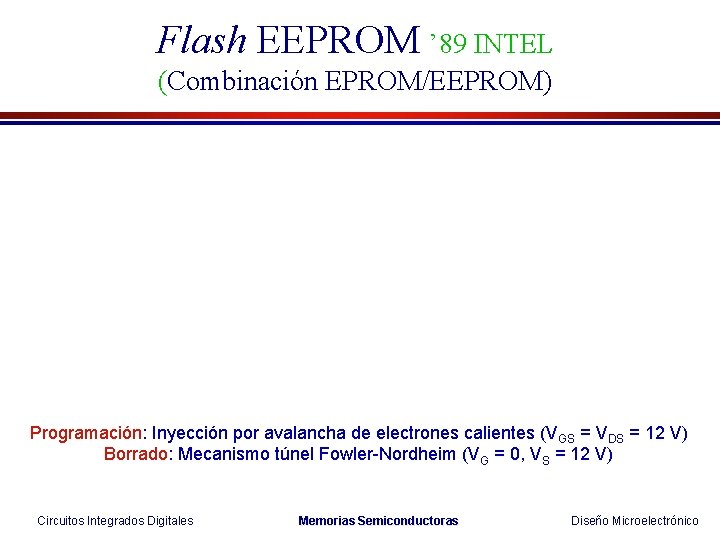

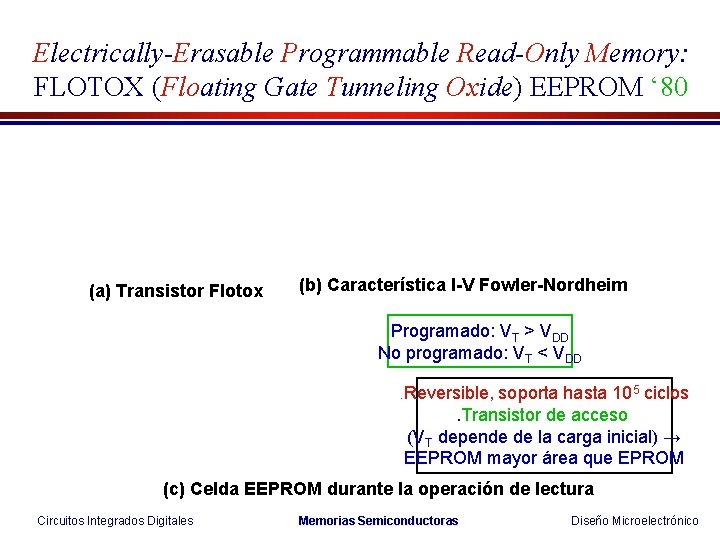

Flash EEPROM ’ 89 INTEL (Combinación EPROM/EEPROM) Programación: Inyección por avalancha de electrones calientes (VGS = VDS = 12 V) Borrado: Mecanismo túnel Fowler-Nordheim (VG = 0, VS = 12 V) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

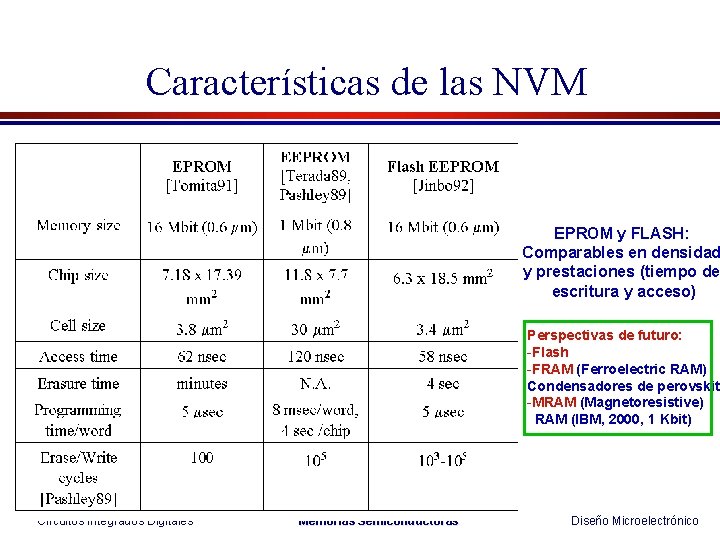

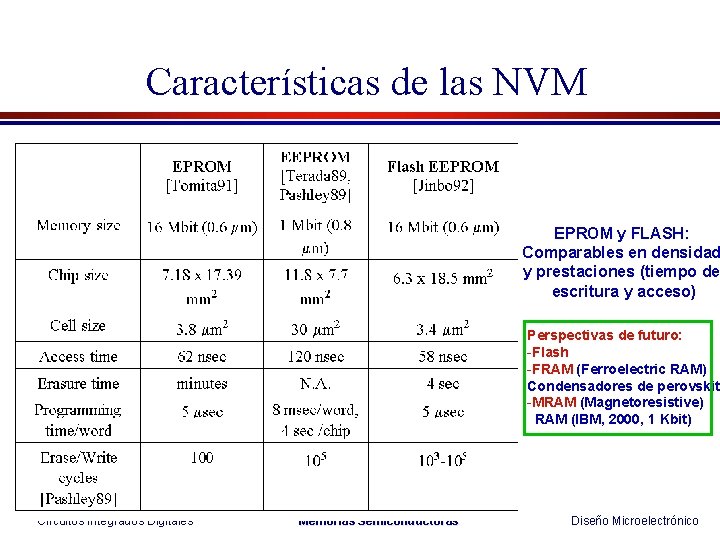

Características de las NVM EPROM y FLASH: Comparables en densidad y prestaciones (tiempo de escritura y acceso) Perspectivas de futuro: -Flash -FRAM (Ferroelectric RAM) Condensadores de perovskita -MRAM (Magnetoresistive) RAM (IBM, 2000, 1 Kbit) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

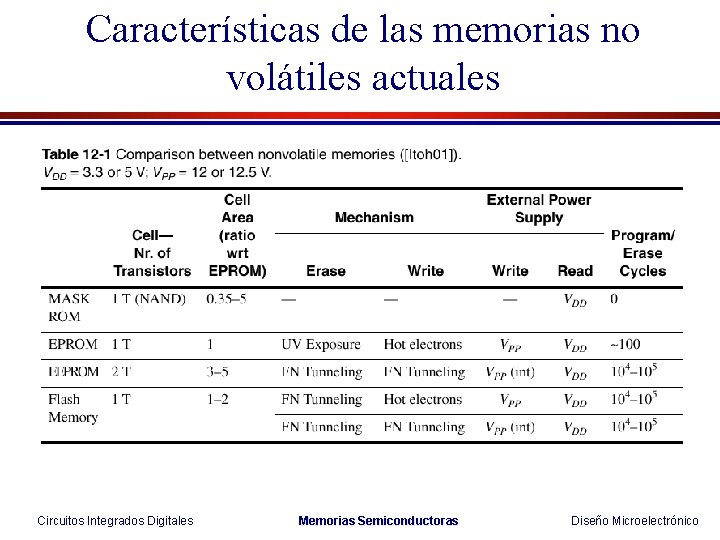

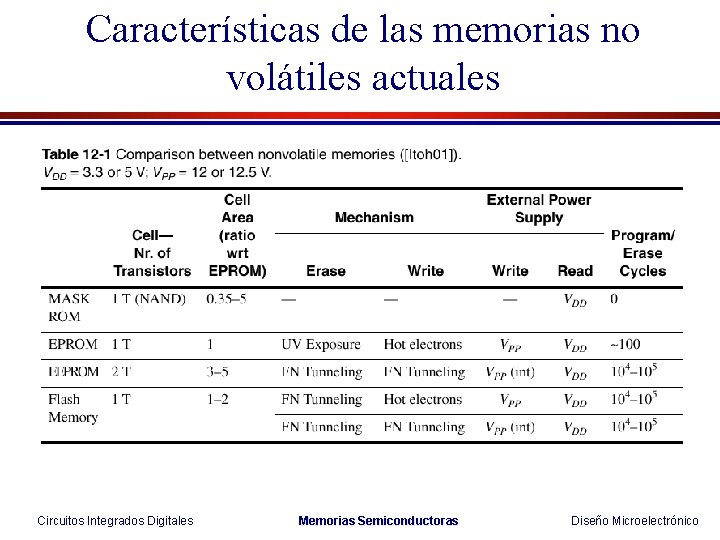

Características de las memorias no volátiles actuales Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

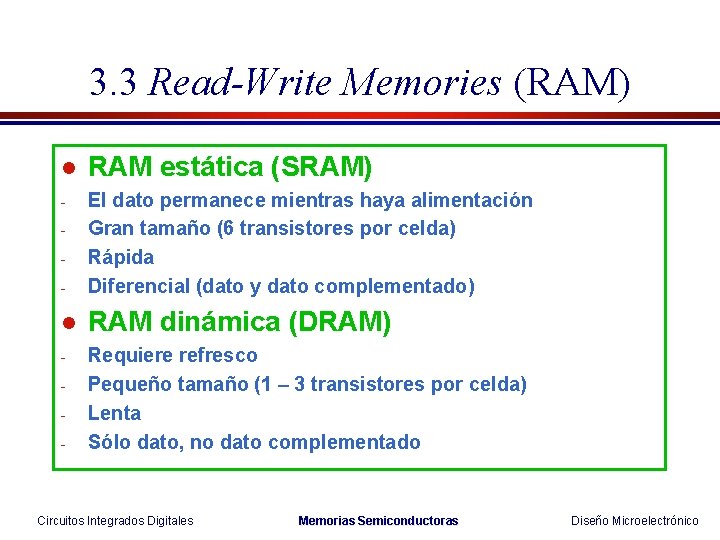

3. 3 Read-Write Memories (RAM) l RAM estática (SRAM) - - El dato permanece mientras haya alimentación Gran tamaño (6 transistores por celda) Rápida Diferencial (dato y dato complementado) l RAM dinámica (DRAM) - Requiere refresco Pequeño tamaño (1 – 3 transistores por celda) Lenta Sólo dato, no dato complementado - - Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

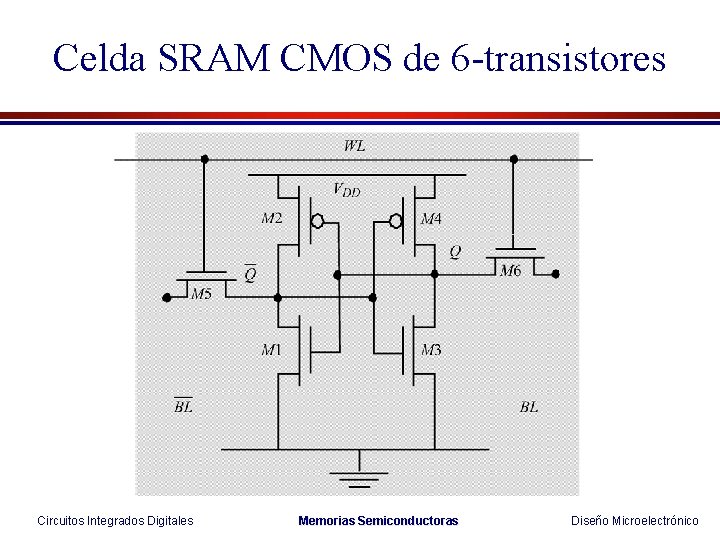

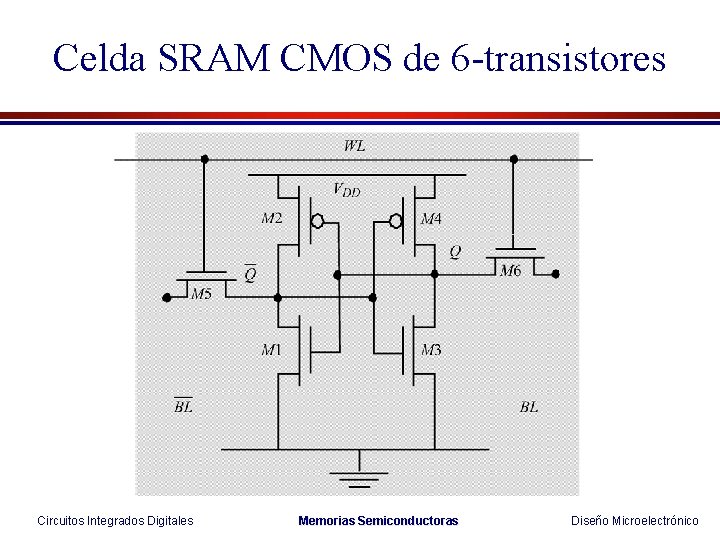

Celda SRAM CMOS de 6 -transistores Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

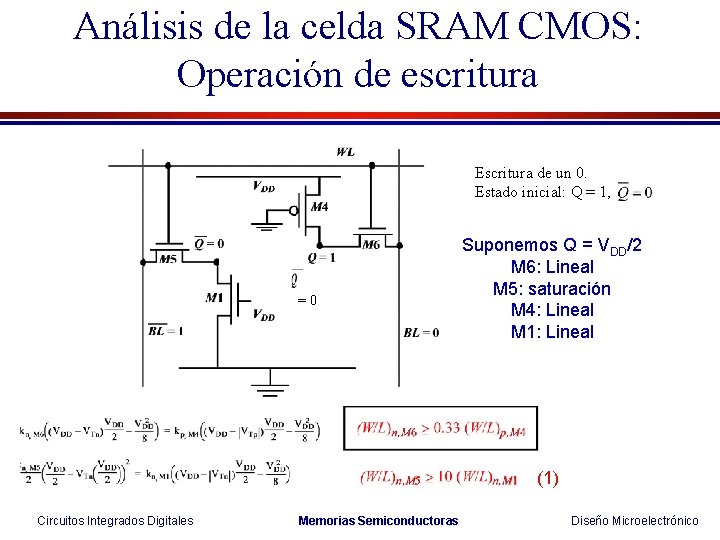

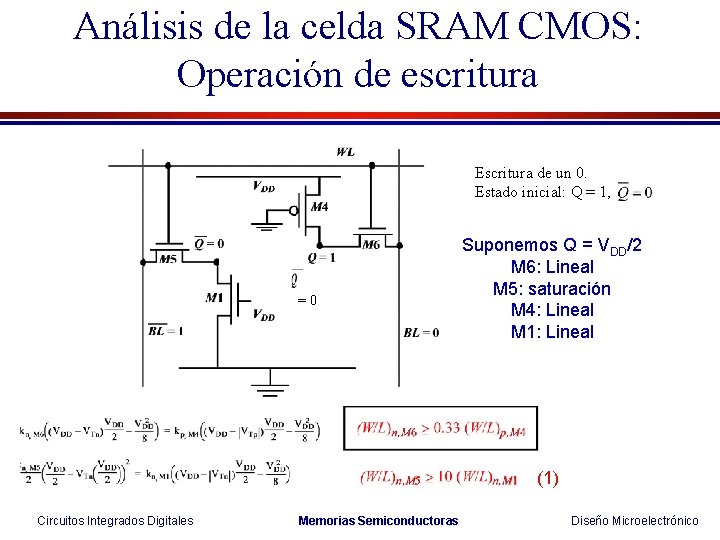

Análisis de la celda SRAM CMOS: Operación de escritura Escritura de un 0. Estado inicial: Q = 1, =0 Suponemos Q = VDD/2 M 6: Lineal M 5: saturación M 4: Lineal M 1: Lineal (1) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

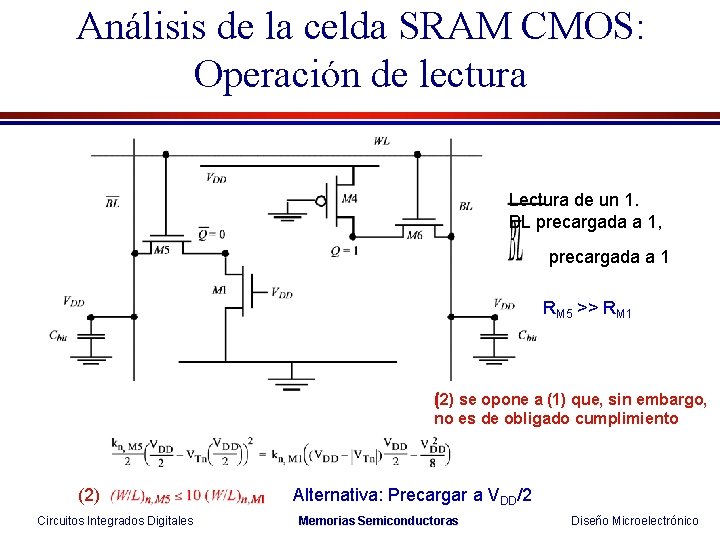

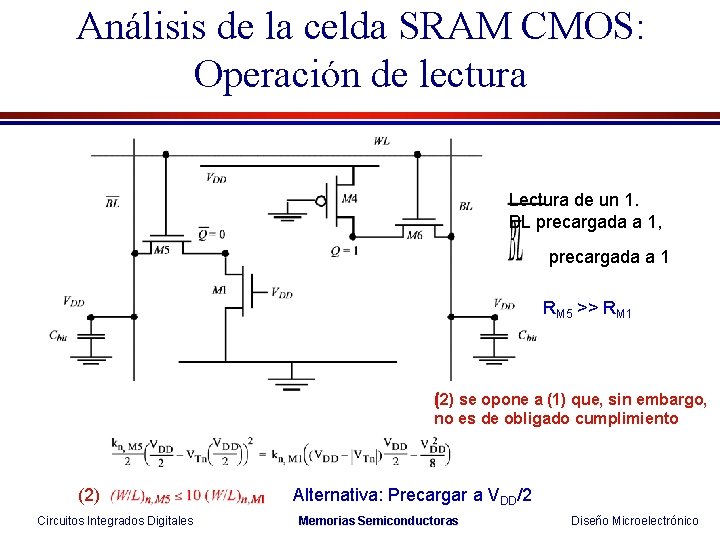

Análisis de la celda SRAM CMOS: Operación de lectura Lectura de un 1. BL precargada a 1, precargada a 1 RM 5 >> RM 1 (2) se opone a (1) que, sin embargo, no es de obligado cumplimiento (2) Circuitos Integrados Digitales Alternativa: Precargar a VDD/2 Memorias Semiconductoras Diseño Microelectrónico

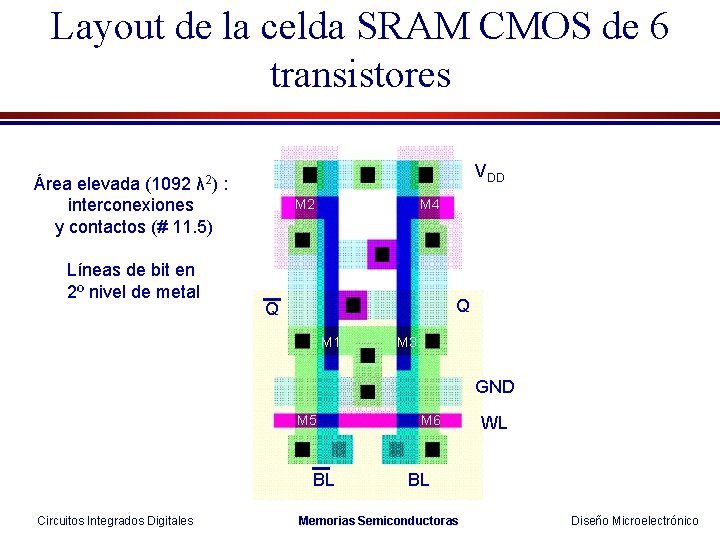

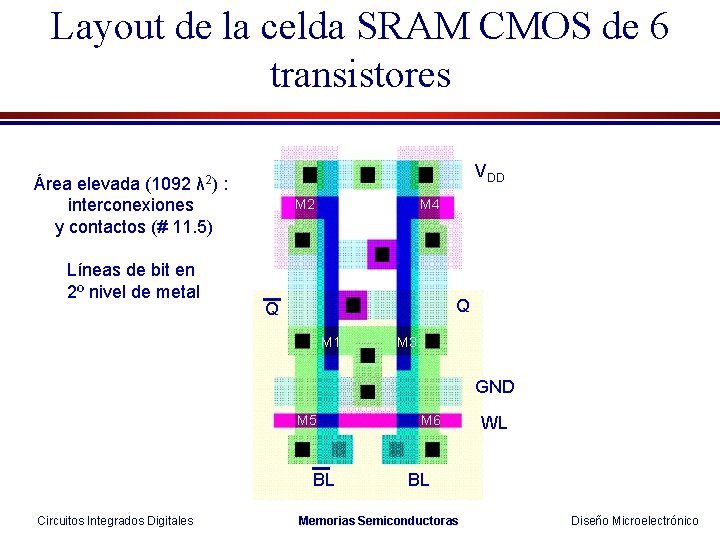

Layout de la celda SRAM CMOS de 6 transistores VDD Área elevada (1092 λ 2) : interconexiones y contactos (# 11. 5) Líneas de bit en 2º nivel de metal M 2 M 4 Q Q M 1 M 3 GND M 5 BL Circuitos Integrados Digitales M 6 WL BL Memorias Semiconductoras Diseño Microelectrónico

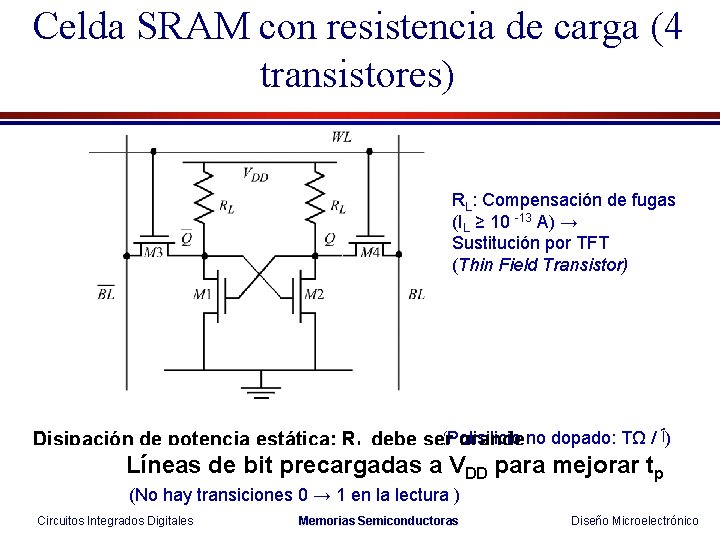

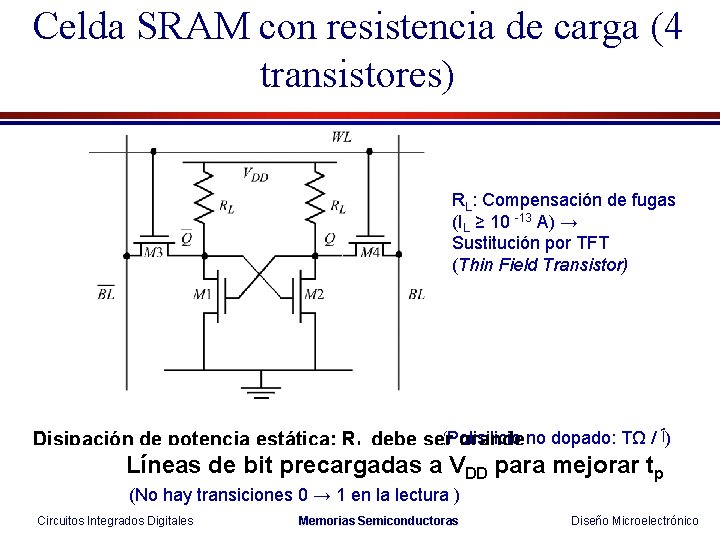

Celda SRAM con resistencia de carga (4 transistores) RL: Compensación de fugas (IL ≥ 10 -13 A) → Sustitución por TFT (Thin Field Transistor) (Polisilicio Disipación de potencia estática: RL debe ser grande no dopado: TΩ / )ٱ Líneas de bit precargadas a VDD para mejorar tp (No hay transiciones 0 → 1 en la lectura ) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

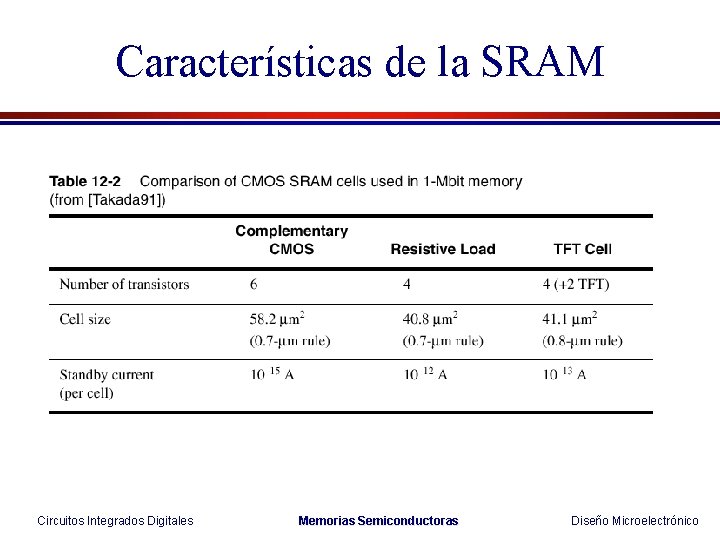

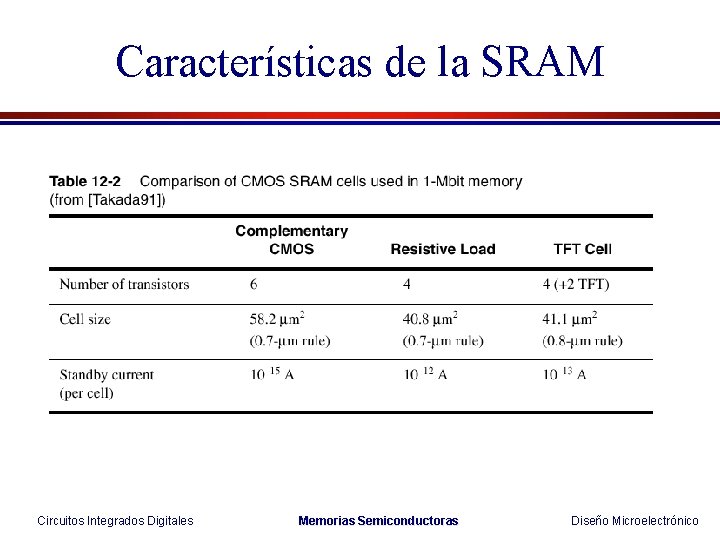

Características de la SRAM Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

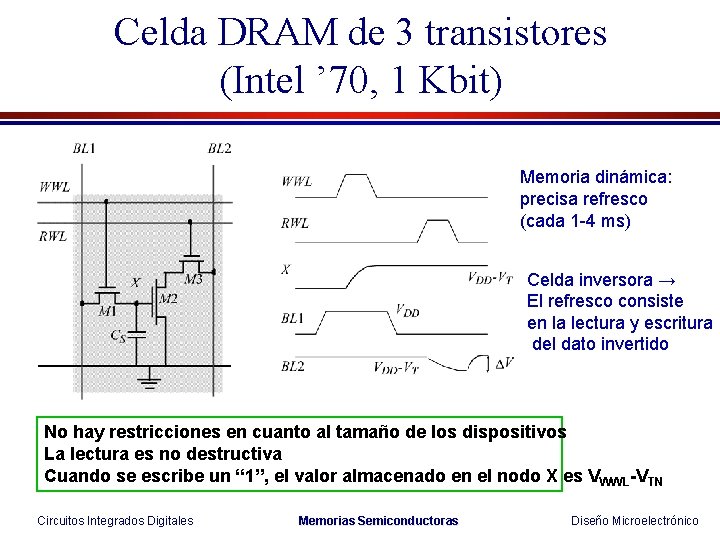

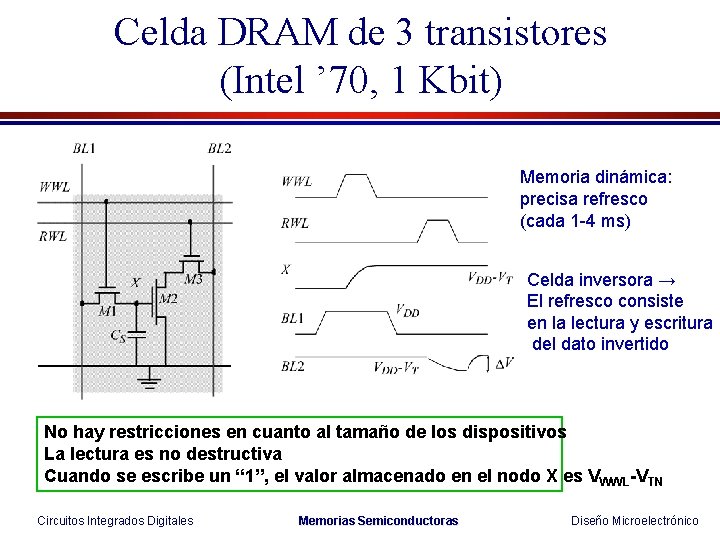

Celda DRAM de 3 transistores (Intel ’ 70, 1 Kbit) Memoria dinámica: precisa refresco (cada 1 -4 ms) Celda inversora → El refresco consiste en la lectura y escritura del dato invertido No hay restricciones en cuanto al tamaño de los dispositivos La lectura es no destructiva Cuando se escribe un “ 1”, el valor almacenado en el nodo X es V WWL-VTN Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

Layout de la celda DRAM de 3 transistores BL 2 BL 1 GND Vía A = 576 λ 2 vs. 1092 λ 2 (SRAM) RWL M 3 M 2 WWL M 1 Vía Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

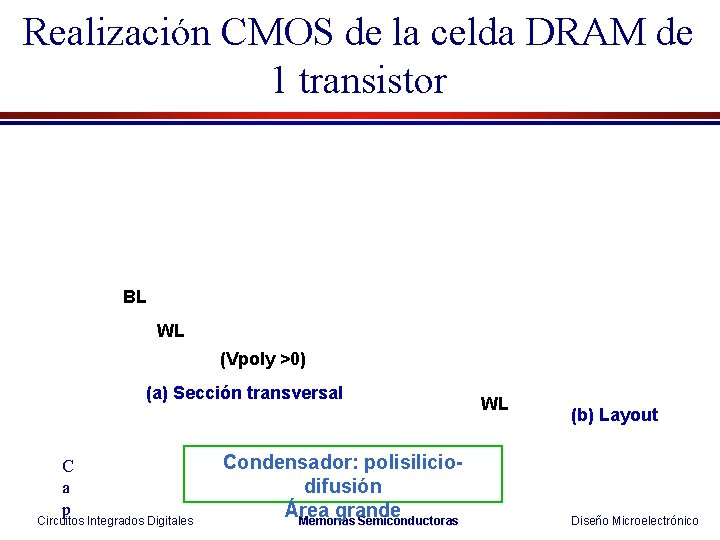

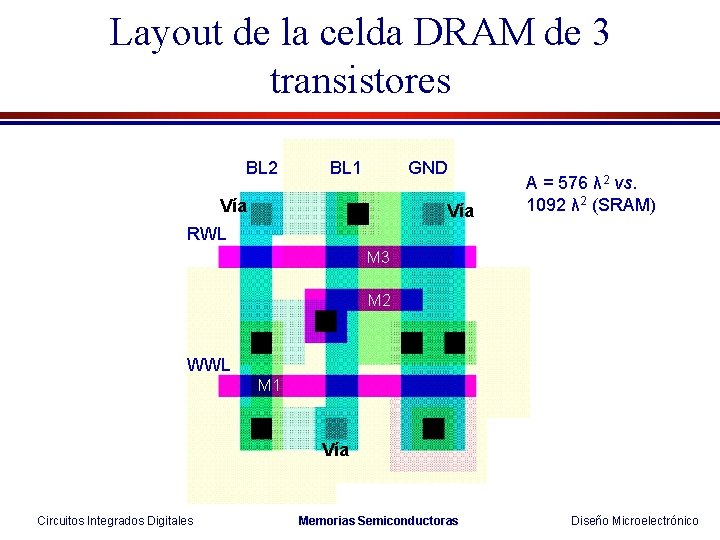

Celda DRAM de 1 transistor Vpre CBL + VBIT CS = VBL (CBL + CS) X CBL = 10 -100 CS VBIT : Valor almacenado en X Vpre = Ej: Cs = 50 f. F, CBL = 1 p. F → (Cs)/(Cs + CBL) = 0. 05 Escritura: Activando WL y BL Cs se carga o se descarga Lectura: Redistribución de carga entre la línea de(1 bit-10) y Cs % │ΔV│~ 250 m. V Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

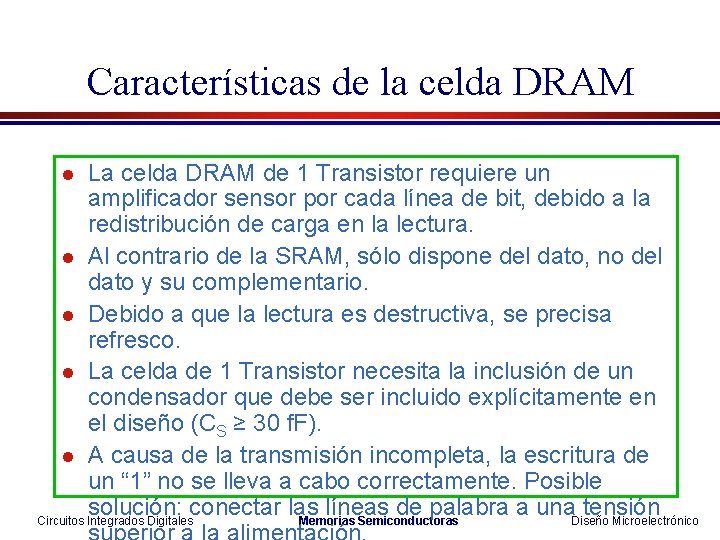

Características de la celda DRAM La celda DRAM de 1 Transistor requiere un amplificador sensor por cada línea de bit, debido a la redistribución de carga en la lectura. l Al contrario de la SRAM, sólo dispone del dato, no del dato y su complementario. l Debido a que la lectura es destructiva, se precisa refresco. l La celda de 1 Transistor necesita la inclusión de un condensador que debe ser incluido explícitamente en el diseño (CS ≥ 30 f. F). l A causa de la transmisión incompleta, la escritura de un “ 1” no se lleva a cabo correctamente. Posible solución: conectar las líneas de palabra a una. Diseño tensión Circuitos Integrados Digitales Microelectrónico Memorias Semiconductoras l

Realización CMOS de la celda DRAM de 1 transistor BL WL (Vpoly >0) (a) Sección transversal C a p Circuitos Integrados Digitales Condensador: polisiliciodifusión Área grande Memorias Semiconductoras WL (b) Layout Diseño Microelectrónico

SEM del condensador de la celda DRAM Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

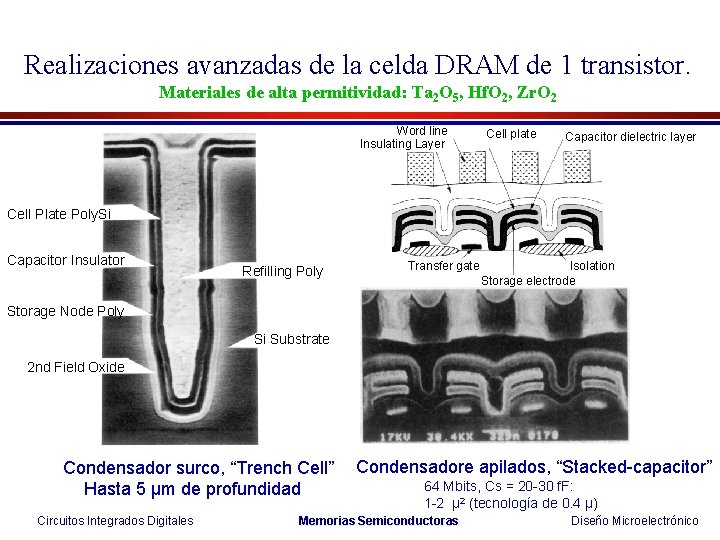

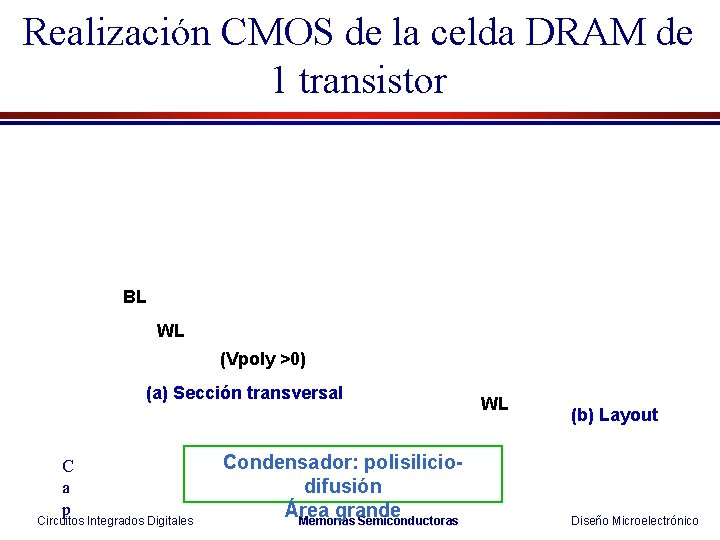

Realizaciones avanzadas de la celda DRAM de 1 transistor. Materiales de alta permitividad: Ta 2 O 5, Hf. O 2, Zr. O 2 Word line Insulating Layer Cell plate Capacitor dielectric layer Cell Plate Poly. Si Capacitor Insulator Refilling Poly Transfer gate Isolation Storage electrode Storage Node Poly Si Substrate 2 nd Field Oxide Condensador surco, “Trench Cell” Hasta 5 μm de profundidad Circuitos Integrados Digitales Condensadore apilados, “Stacked-capacitor” 64 Mbits, Cs = 20 -30 f. F: 1 -2 μ 2 (tecnología de 0. 4 μ) Memorias Semiconductoras Diseño Microelectrónico

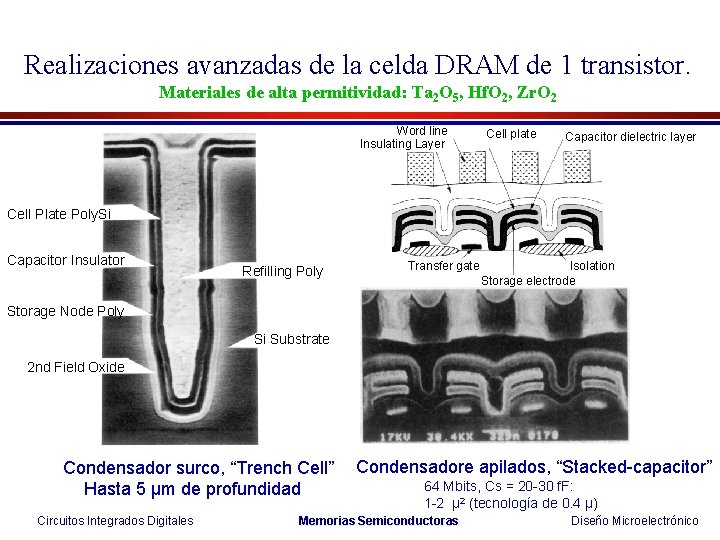

Arquitectura periférica. Decodificadores. Amplificadores sensores. Buffers de entrada/salida. Circuitería de control temporal Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

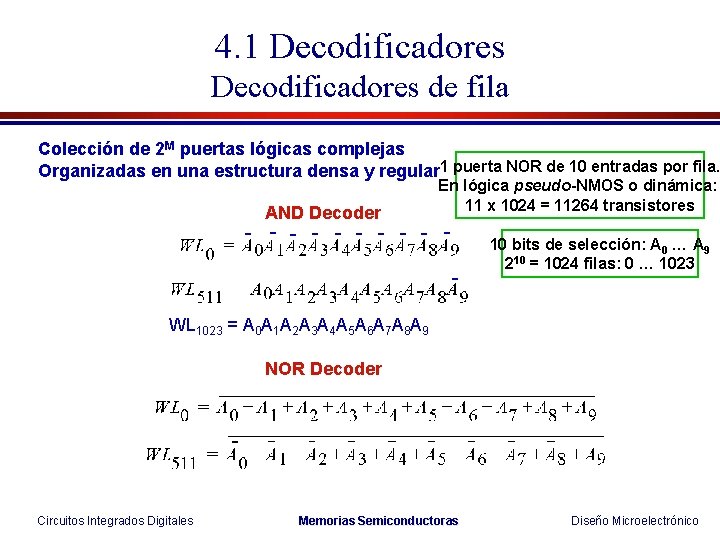

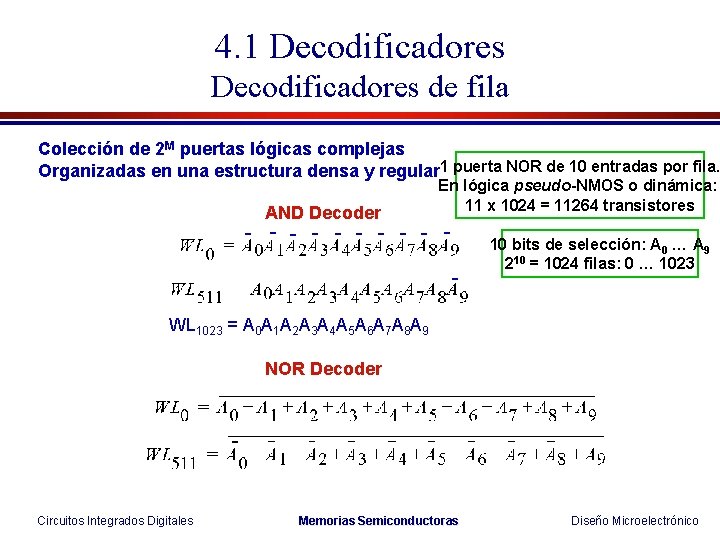

4. 1 Decodificadores de fila Colección de 2 M puertas lógicas complejas Organizadas en una estructura densa y regular 1 puerta NOR de 10 entradas por fila. En lógica pseudo-NMOS o dinámica: 11 x 1024 = 11264 transistores AND Decoder ‾ ‾ ‾ ‾ ‾ 10 bits de selección: A 0 … A 9 210 = 1024 filas: 0 … 1023 ‾ WL 1023 = A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 A 8 A 9 NOR Decoder ‾ Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

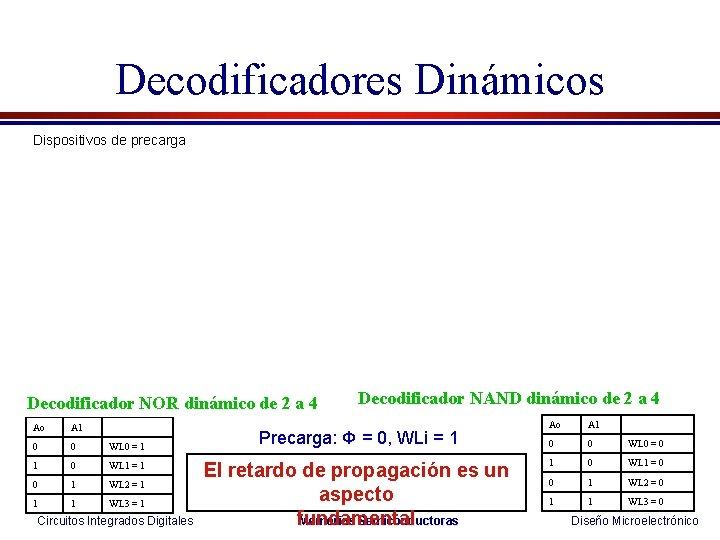

Decodificadores Dinámicos Dispositivos de precarga Decodificador NOR dinámico de 2 a 4 Ao A 1 0 0 WL 0 = 1 1 0 WL 1 = 1 0 1 WL 2 = 1 1 1 WL 3 = 1 Circuitos Integrados Digitales Decodificador NAND dinámico de 2 a 4 Precarga: Φ = 0, WLi = 1 El retardo de propagación es un aspecto Memorias Semiconductoras fundamental Ao A 1 0 0 WL 0 = 0 1 0 WL 1 = 0 0 1 WL 2 = 0 1 1 WL 3 = 0 Diseño Microelectrónico

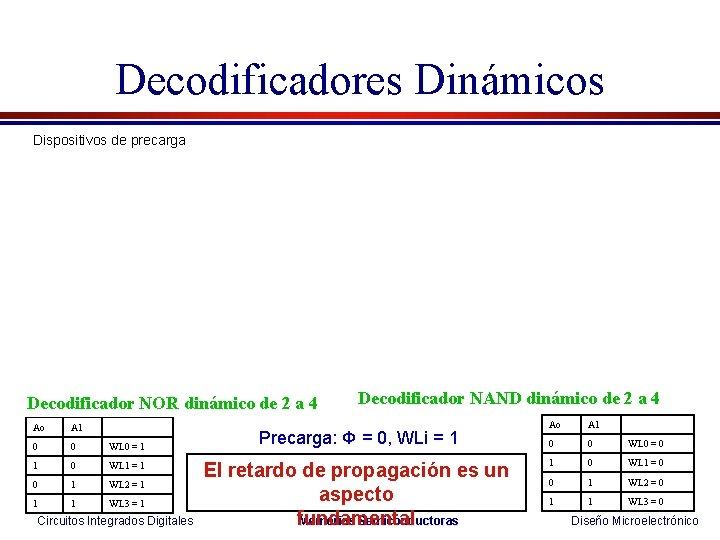

Pre-decodificadores # Transistores: 6224 (55 % del original) Retardo: 25 % El desdoblamiento del decodificador en varios niveles da lugar a una realización más rápida y económica Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

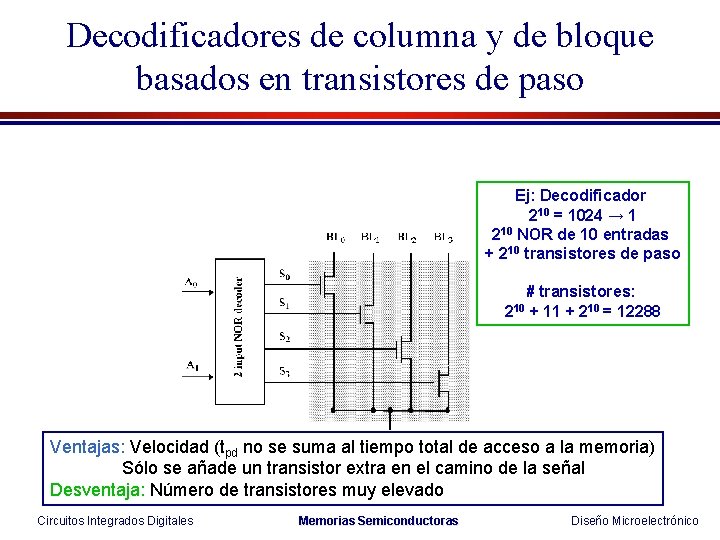

Decodificadores de columna y de bloque basados en transistores de paso Ej: Decodificador 210 = 1024 → 1 210 NOR de 10 entradas + 210 transistores de paso 210 # transistores: + 11 + 210 = 12288 Ventajas: Velocidad (tpd no se suma al tiempo total de acceso a la memoria) Sólo se añade un transistor extra en el camino de la señal Desventaja: Número de transistores muy elevado Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

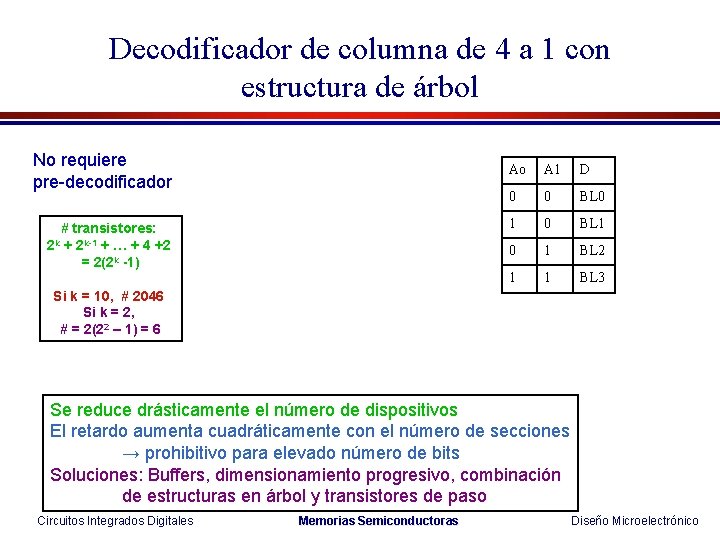

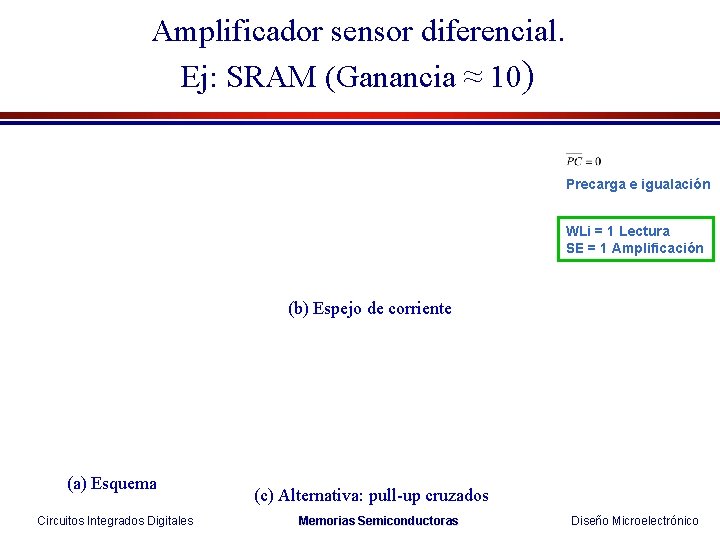

Decodificador de columna de 4 a 1 con estructura de árbol No requiere pre-decodificador # transistores: k 2 + 2 k-1 + … + 4 +2 = 2(2 k -1) Ao A 1 D 0 0 BL 0 1 0 BL 1 0 1 BL 2 1 1 BL 3 Si k = 10, # 2046 Si k = 2, # = 2(22 – 1) = 6 Se reduce drásticamente el número de dispositivos El retardo aumenta cuadráticamente con el número de secciones → prohibitivo para elevado número de bits Soluciones: Buffers, dimensionamiento progresivo, combinación de estructuras en árbol y transistores de paso Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

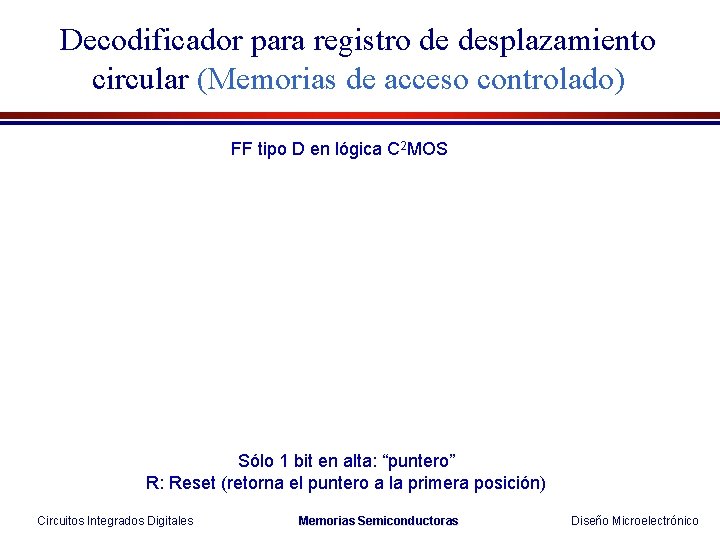

Decodificador para registro de desplazamiento circular (Memorias de acceso controlado) FF tipo D en lógica C 2 MOS Sólo 1 bit en alta: “puntero” R: Reset (retorna el puntero a la primera posición) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

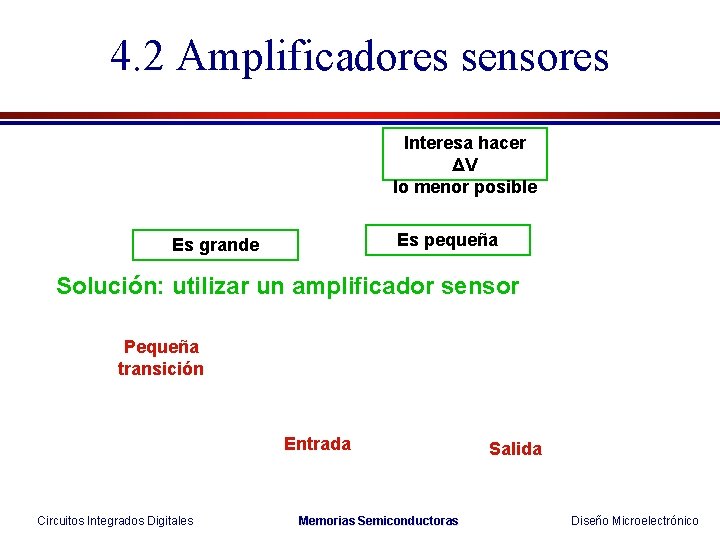

4. 2 Amplificadores sensores Interesa hacer ΔV lo menor posible Es pequeña Es grande Solución: utilizar un amplificador sensor Pequeña transición Entrada Circuitos Integrados Digitales Memorias Semiconductoras Salida Diseño Microelectrónico

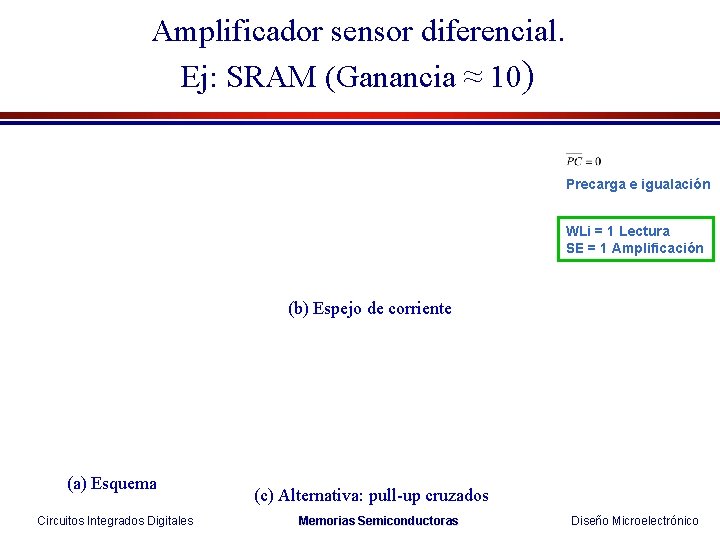

Amplificador sensor diferencial. Ej: SRAM (Ganancia ≈ 10) Precarga e igualación WLi = 1 Lectura SE = 1 Amplificación (b) Espejo de corriente (a) Esquema Circuitos Integrados Digitales (c) Alternativa: pull-up cruzados Memorias Semiconductoras Diseño Microelectrónico

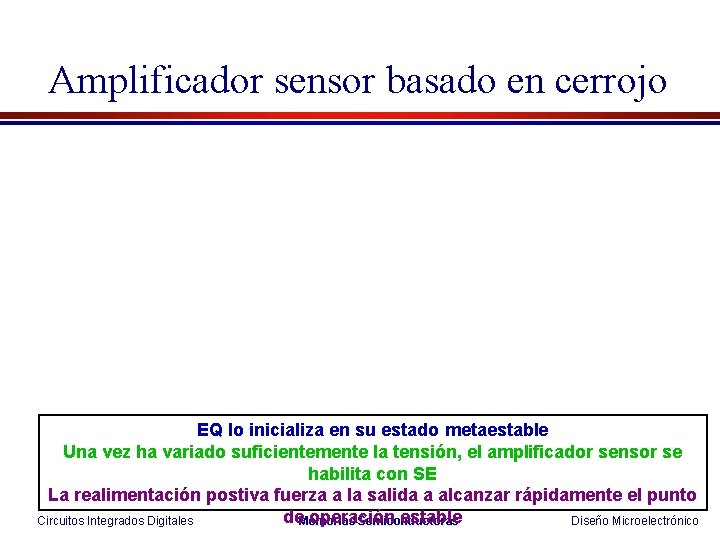

Amplificador sensor basado en cerrojo EQ lo inicializa en su estado metaestable Una vez ha variado suficientemente la tensión, el amplificador sensor se habilita con SE La realimentación postiva fuerza a la salida a alcanzar rápidamente el punto de. Memorias operación estable Circuitos Integrados Digitales Diseño Microelectrónico Semiconductoras

Utilización de amplificador diferencial Problema: Establecer una referencia Vref adecuada Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

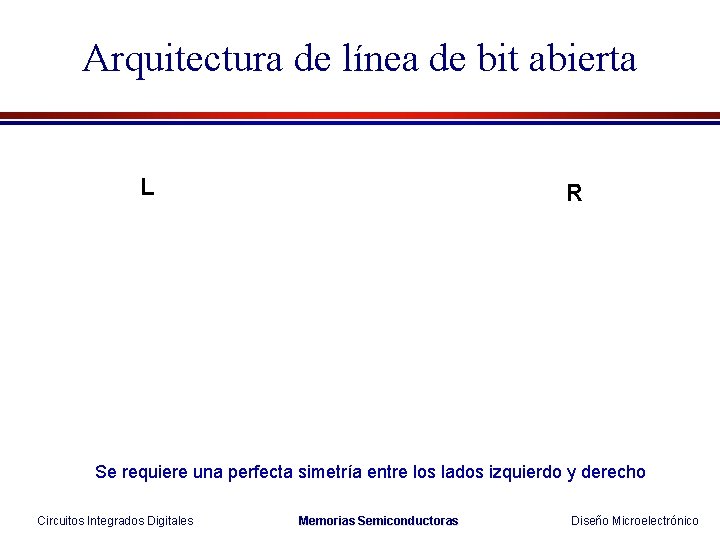

Arquitectura de línea de bit abierta L X R X Se requiere una perfecta simetría entre los lados izquierdo y derecho Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

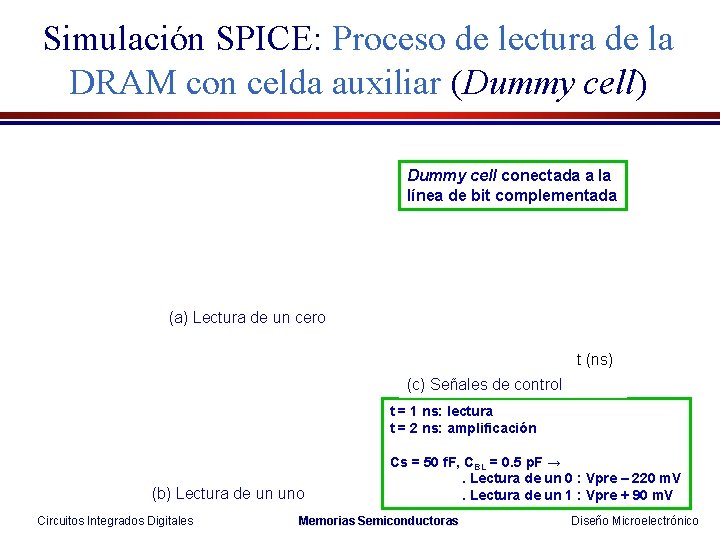

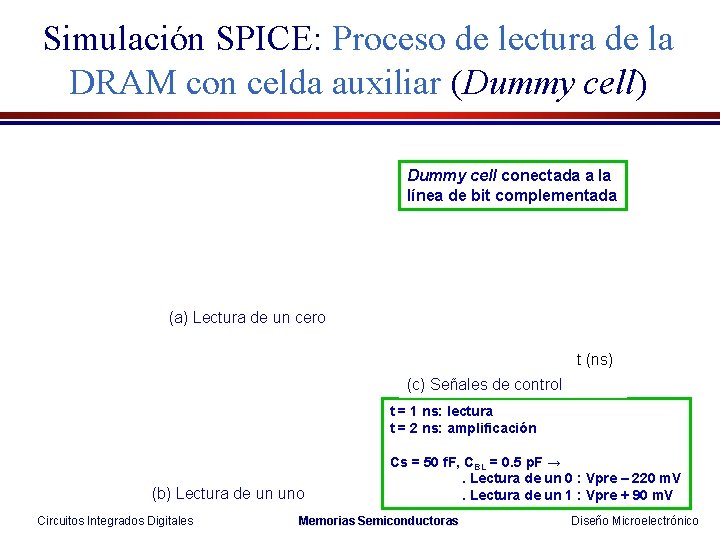

Simulación SPICE: Proceso de lectura de la DRAM con celda auxiliar (Dummy cell) Dummy cell conectada a la línea de bit complementada (a) Lectura de un cero t (ns) (c) Señales de control t = 1 ns: lectura t = 2 ns: amplificación (b) Lectura de un uno Circuitos Integrados Digitales Cs = 50 f. F, CBL = 0. 5 p. F →. Lectura de un 0 : Vpre – 220 m. V. Lectura de un 1 : Vpre + 90 m. V Memorias Semiconductoras Diseño Microelectrónico

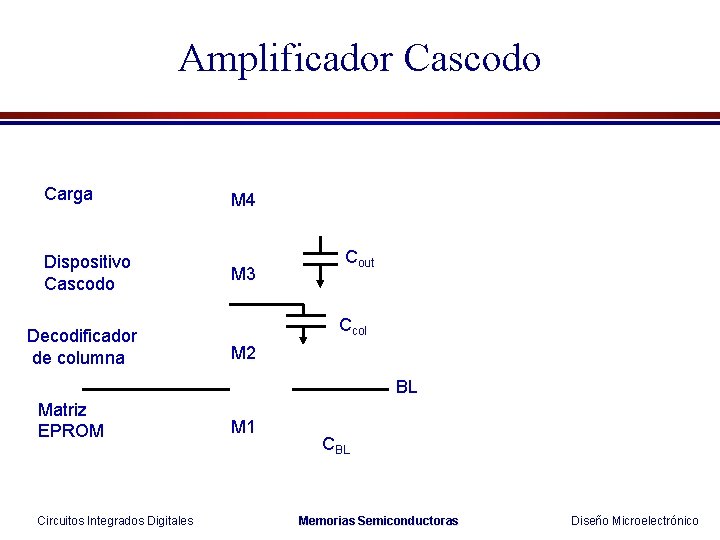

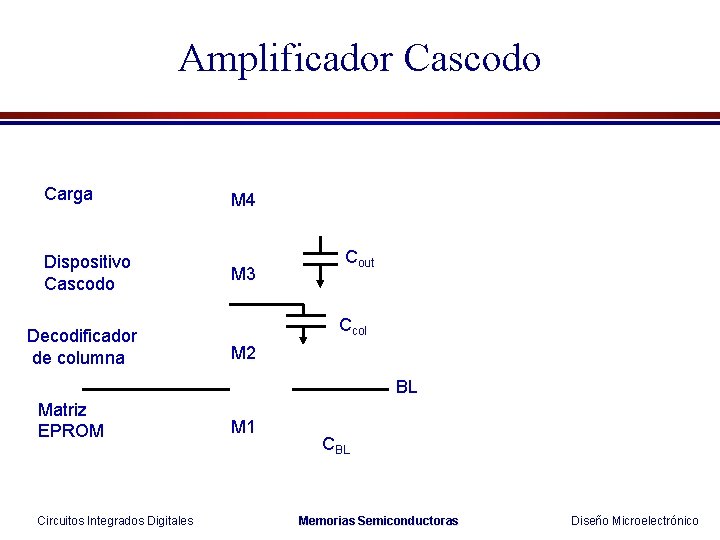

Amplificador Cascodo Carga Dispositivo Cascodo Decodificador de columna M 4 M 3 Cout Ccol M 2 BL Matriz EPROM Circuitos Integrados Digitales M 1 CBL Memorias Semiconductoras Diseño Microelectrónico

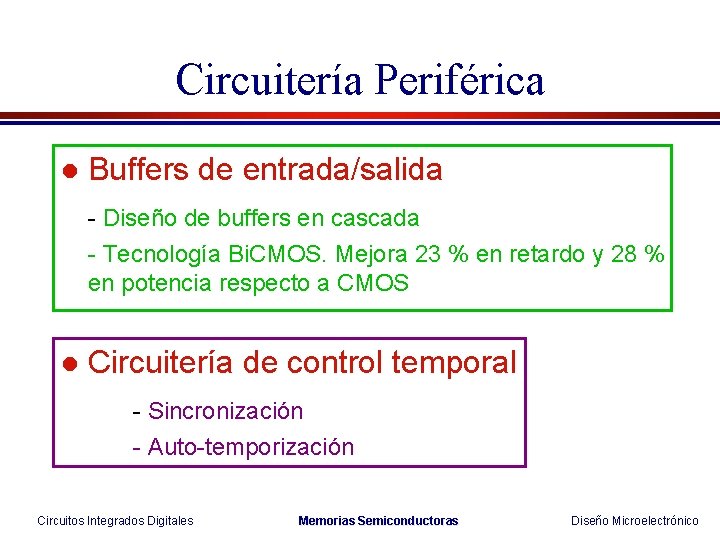

Circuitería Periférica l Buffers de entrada/salida - Diseño de buffers en cascada - Tecnología Bi. CMOS. Mejora 23 % en retardo y 28 % en potencia respecto a CMOS l Circuitería de control temporal - Sincronización - Auto-temporización Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

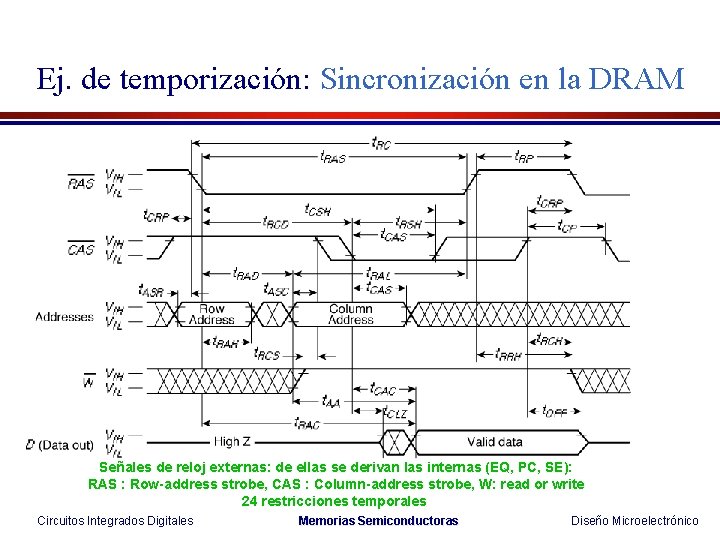

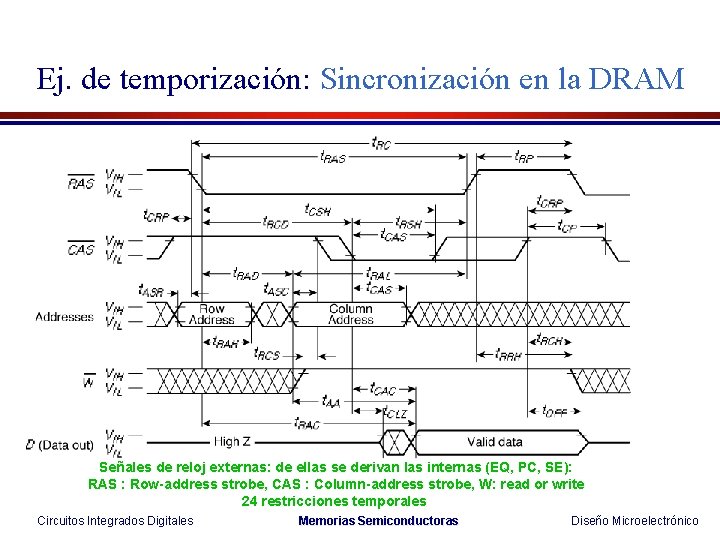

Ej. de temporización: Sincronización en la DRAM Señales de reloj externas: de ellas se derivan las internas (EQ, PC, SE): RAS : Row-address strobe, CAS : Column-address strobe, W: read or write 24 restricciones temporales Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

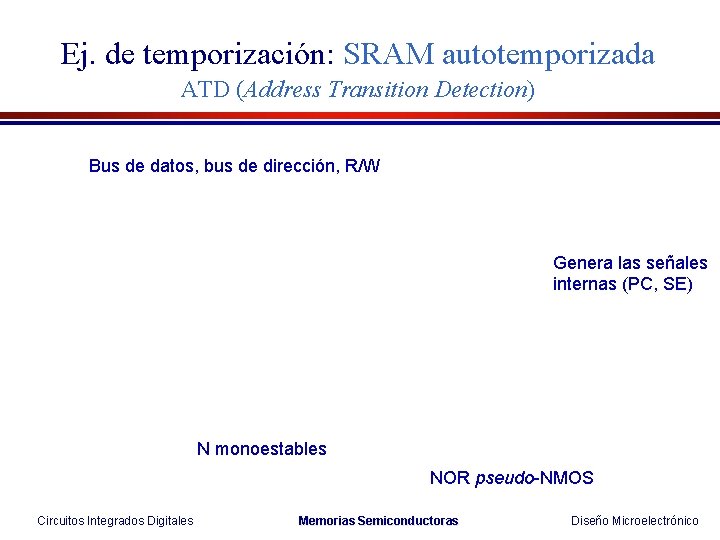

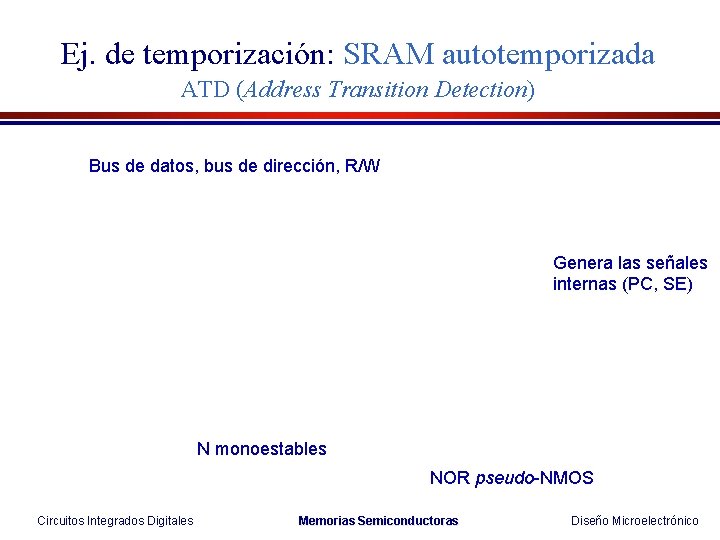

Ej. de temporización: SRAM autotemporizada ATD (Address Transition Detection) Bus de datos, bus de dirección, R/W Genera las señales internas (PC, SE) N monoestables NOR pseudo-NMOS Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

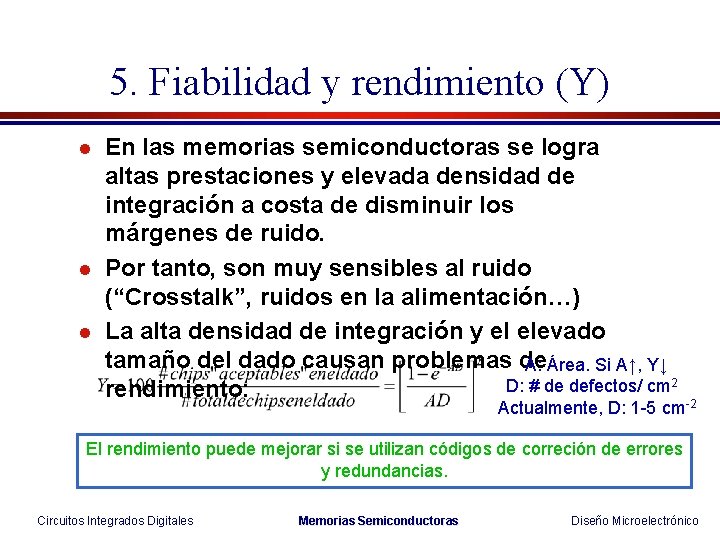

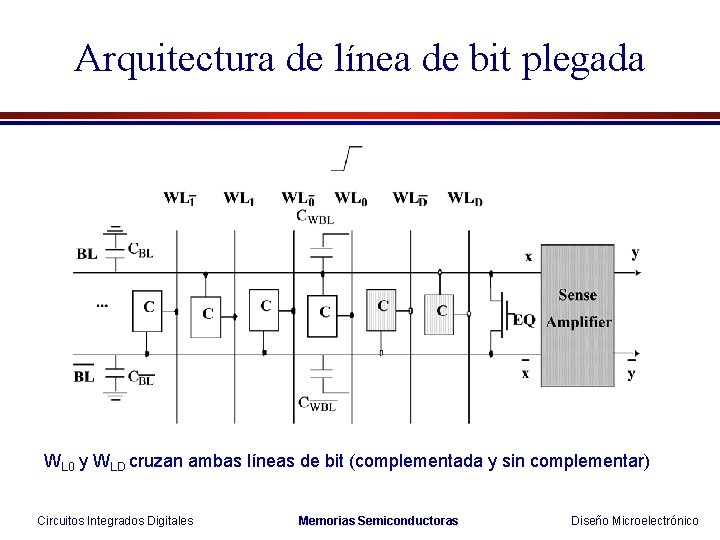

5. Fiabilidad y rendimiento (Y) l l l En las memorias semiconductoras se logra altas prestaciones y elevada densidad de integración a costa de disminuir los márgenes de ruido. Por tanto, son muy sensibles al ruido (“Crosstalk”, ruidos en la alimentación…) La alta densidad de integración y el elevado tamaño del dado causan problemas de A: Área. Si A↑, Y↓ D: # de defectos/ cm 2 rendimiento: Actualmente, D: 1 -5 cm-2 El rendimiento puede mejorar si se utilizan códigos de correción de errores y redundancias. Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

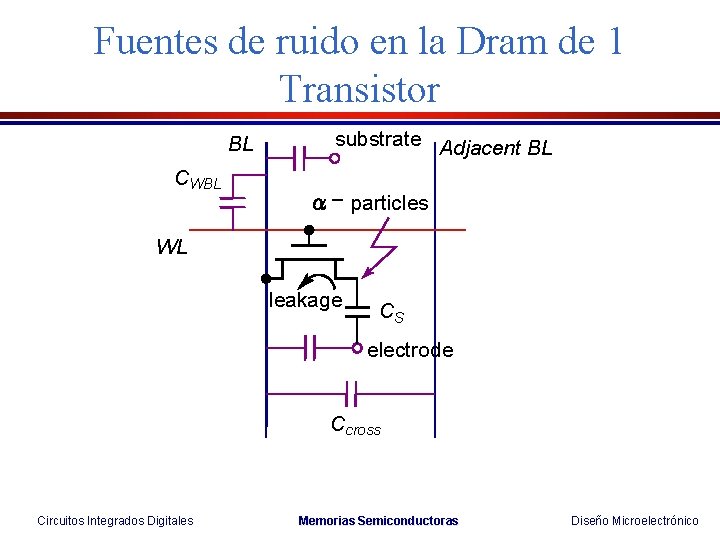

Fuentes de ruido en la Dram de 1 Transistor BL CWBL substrate Adjacent BL a -particles α- WL leakage CS electrode Ccross Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

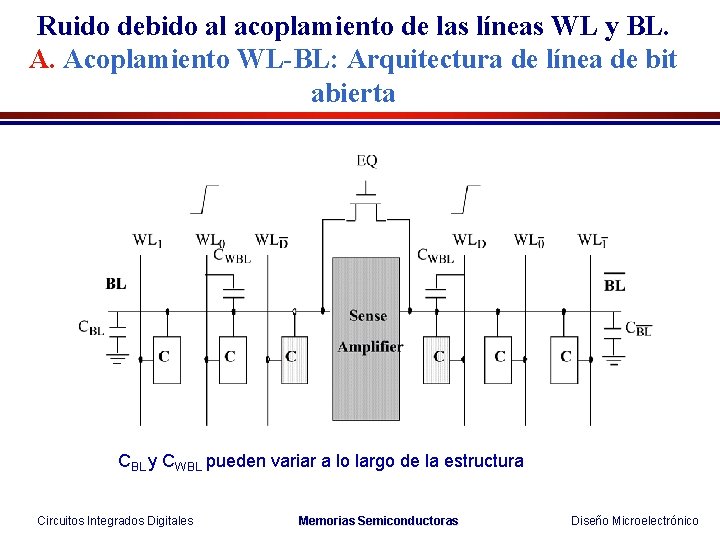

Ruido debido al acoplamiento de las líneas WL y BL. A. Acoplamiento WL-BL: Arquitectura de línea de bit abierta CBL y CWBL pueden variar a lo largo de la estructura Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

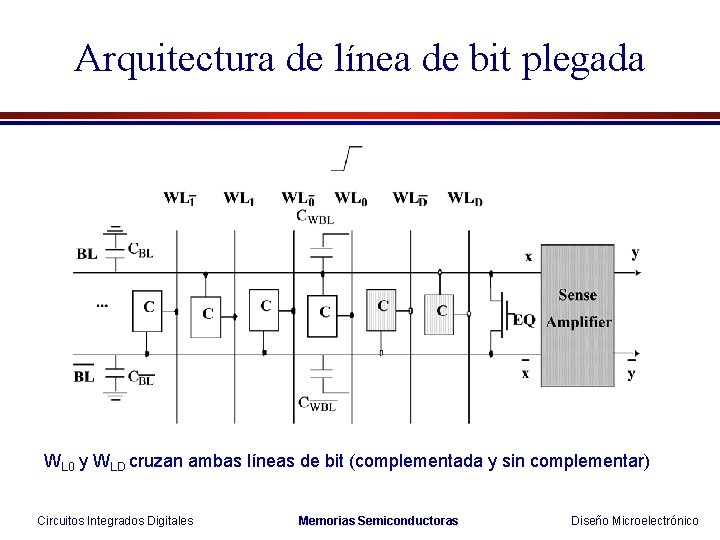

Arquitectura de línea de bit plegada WL 0 y WLD cruzan ambas líneas de bit (complementada y sin complementar) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

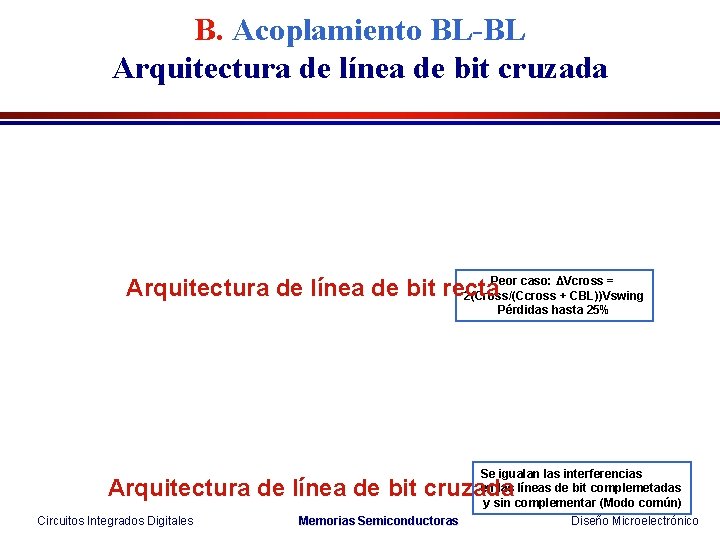

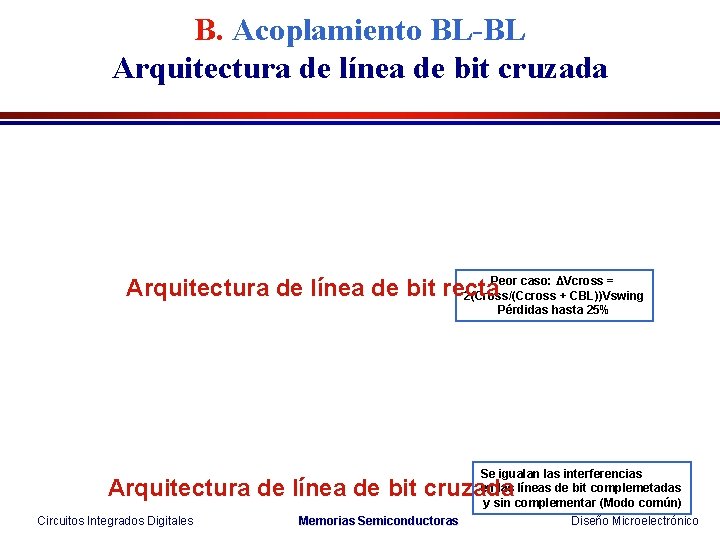

B. Acoplamiento BL-BL Arquitectura de línea de bit cruzada Peor caso: ΔVcross = Arquitectura de línea de bit recta 2(Cross/(Ccross + CBL))Vswing Pérdidas hasta 25% Se igualan las interferencias en las líneas de bit complemetadas y sin complementar (Modo común) Arquitectura de línea de bit cruzada Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

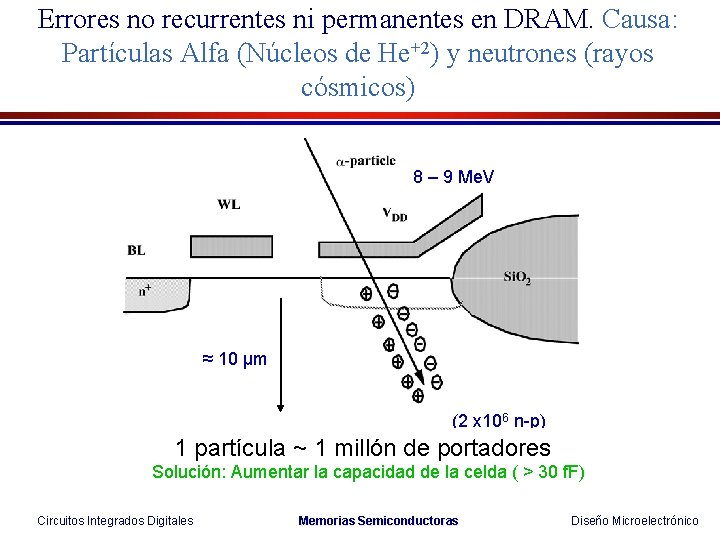

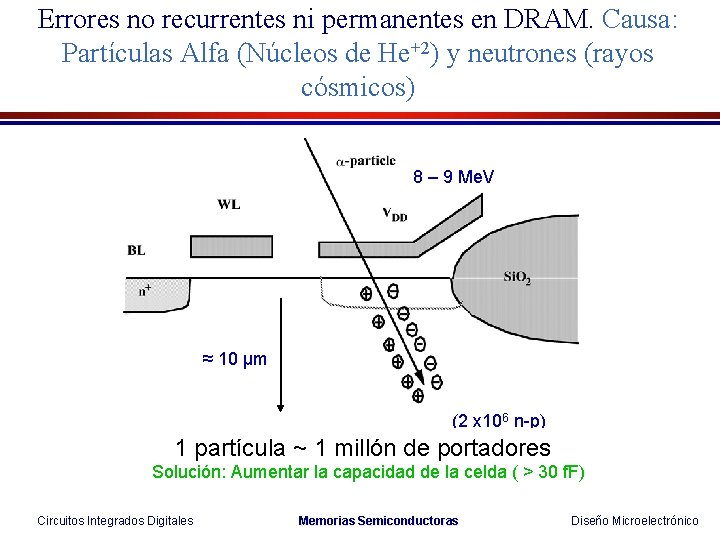

Errores no recurrentes ni permanentes en DRAM. Causa: Partículas Alfa (Núcleos de He+2) y neutrones (rayos cósmicos) 8 – 9 Me. V ≈ 10 μm (2 x 106 n-p) 1 partícula ~ 1 millón de portadores Solución: Aumentar la capacidad de la celda ( > 30 f. F) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

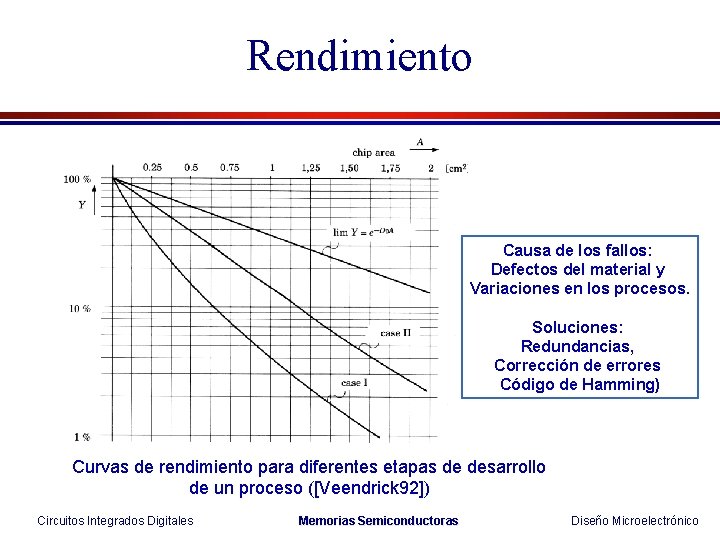

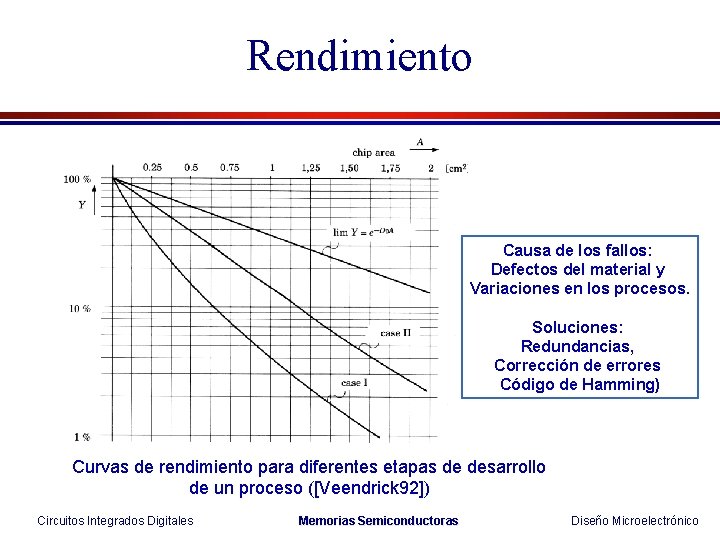

Rendimiento Causa de los fallos: Defectos del material y Variaciones en los procesos. Soluciones: Redundancias, Corrección de errores Código de Hamming) Curvas de rendimiento para diferentes etapas de desarrollo de un proceso ([Veendrick 92]) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

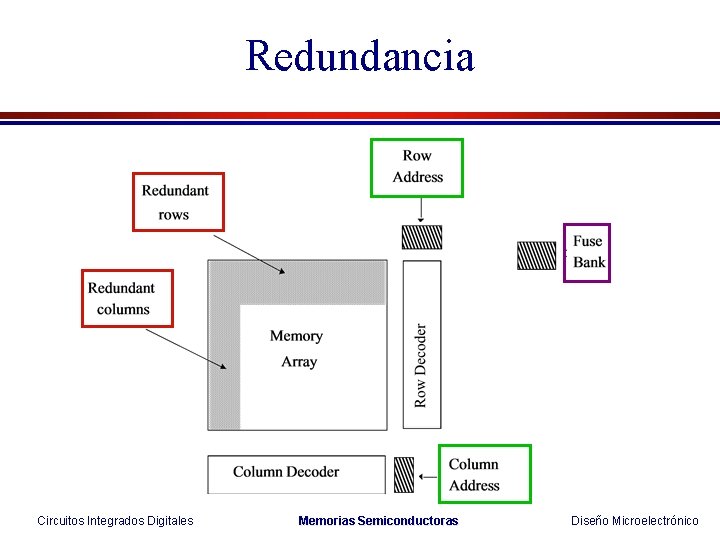

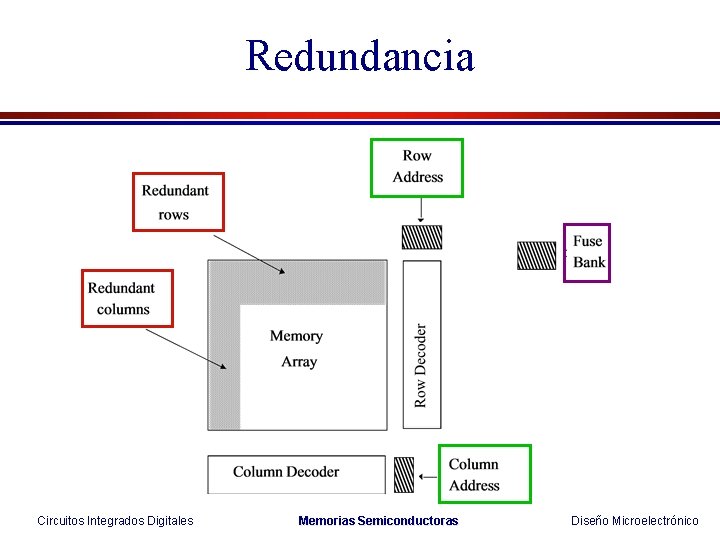

Redundancia Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

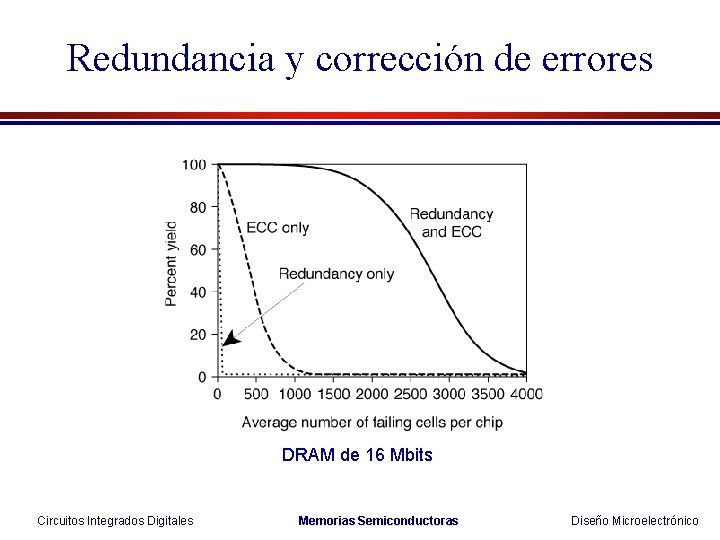

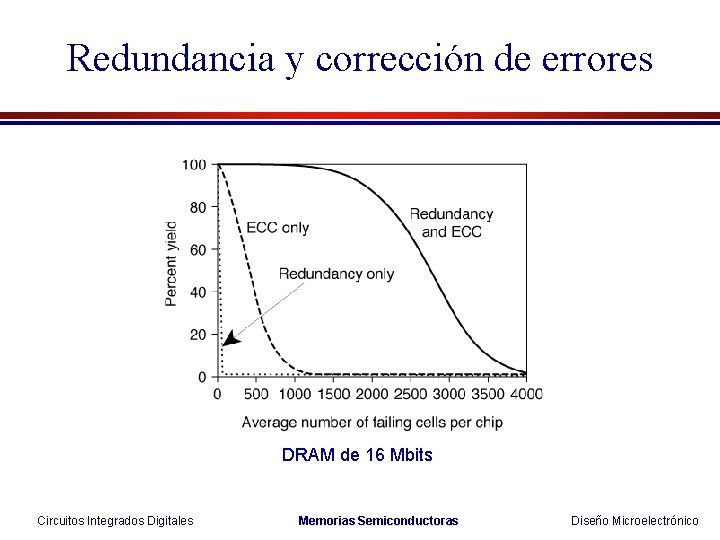

Redundancia y corrección de errores DRAM de 16 Mbits Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

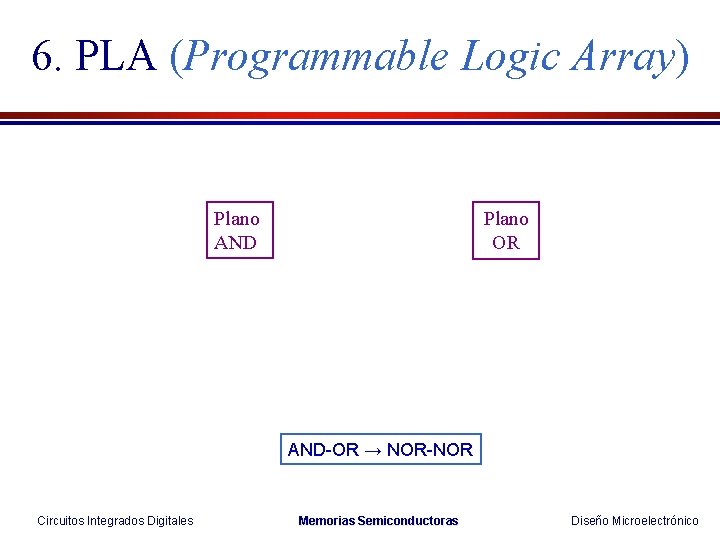

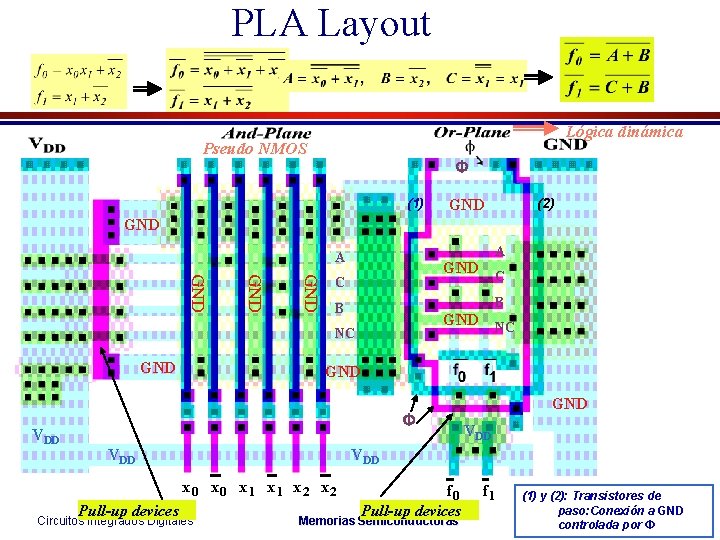

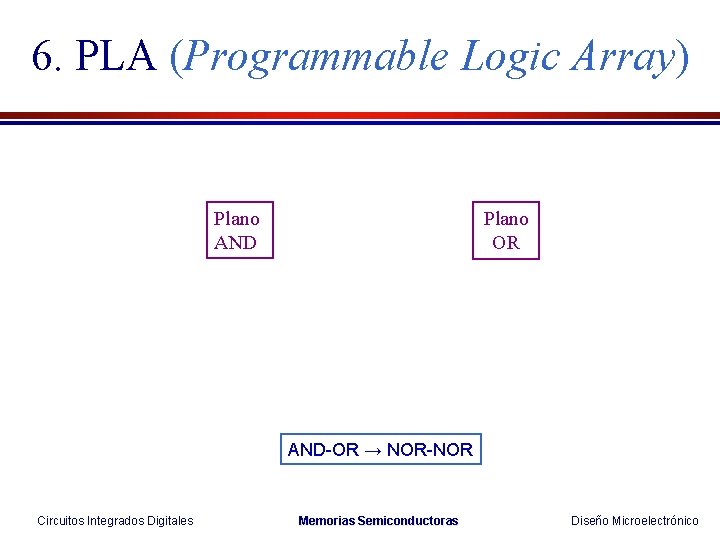

6. PLA (Programmable Logic Array) Plano AND Plano OR AND-OR → NOR-NOR Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

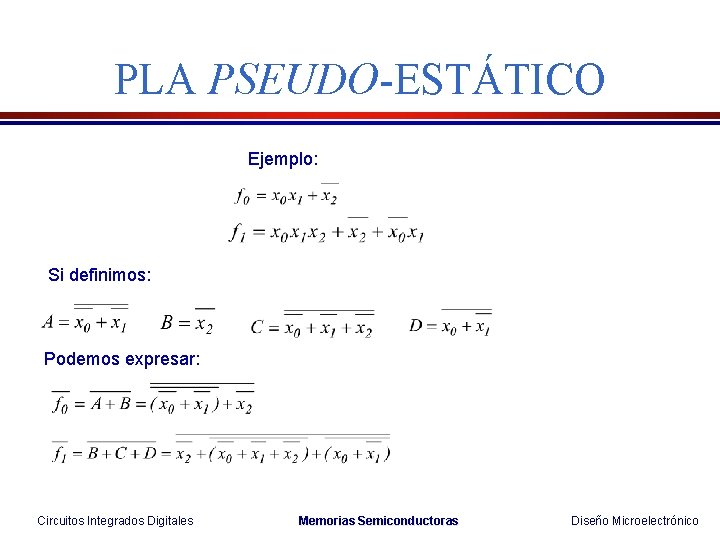

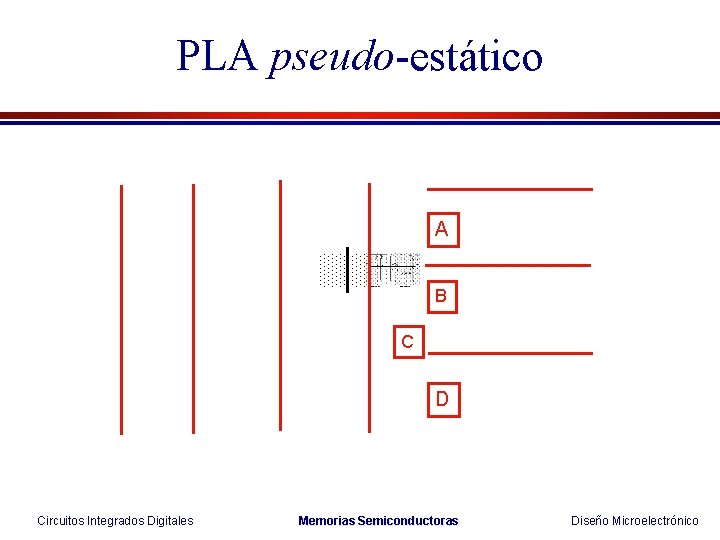

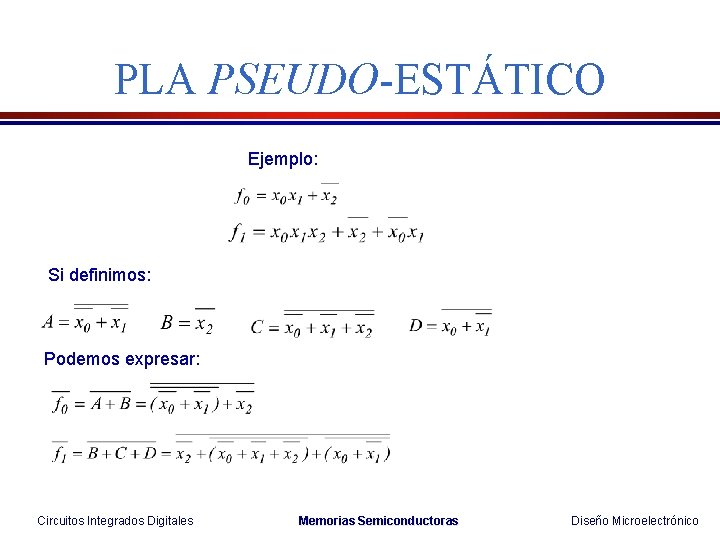

PLA PSEUDO-ESTÁTICO Ejemplo: Si definimos: Podemos expresar: Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

PLA pseudo-estático A B C D Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

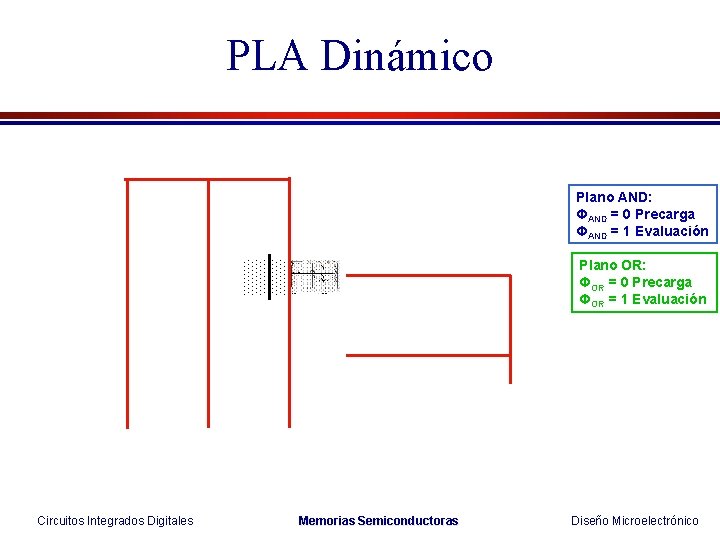

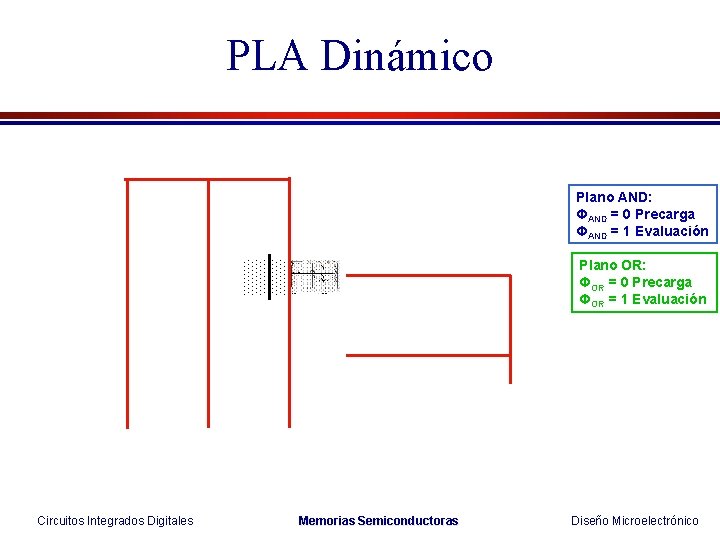

PLA Dinámico Plano AND: ΦAND = 0 Precarga ΦAND = 1 Evaluación Plano OR: ΦOR = 0 Precarga ΦOR = 1 Evaluación Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

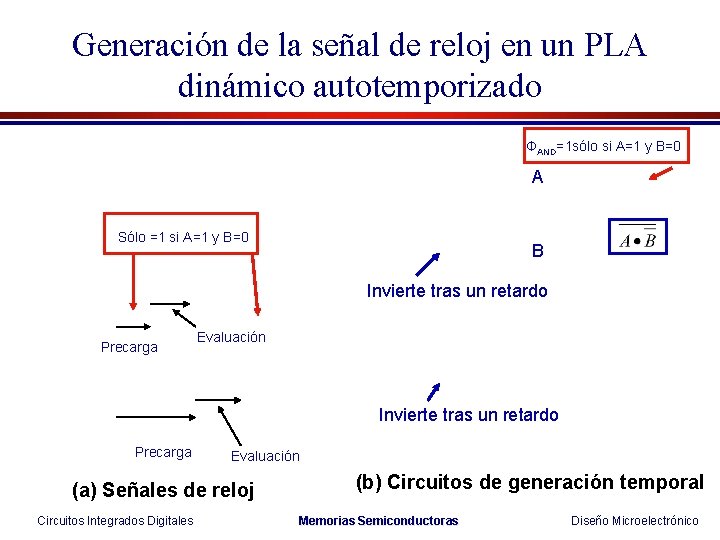

Generación de la señal de reloj en un PLA dinámico autotemporizado ΦAND=1 sólo si A=1 y B=0 A Sólo =1 si A=1 y B=0 B Invierte tras un retardo Precarga Evaluación (a) Señales de reloj Circuitos Integrados Digitales (b) Circuitos de generación temporal Memorias Semiconductoras Diseño Microelectrónico

Generación de ΦOR Wp ↑↑ Carga instantánea ΦOR • • • ΦAND Dummy AND row Descarga retardada ΦAND ΦOR Circuitos Integrados Digitales Memorias Semiconductoras Δt Δt Diseño Microelectrónico

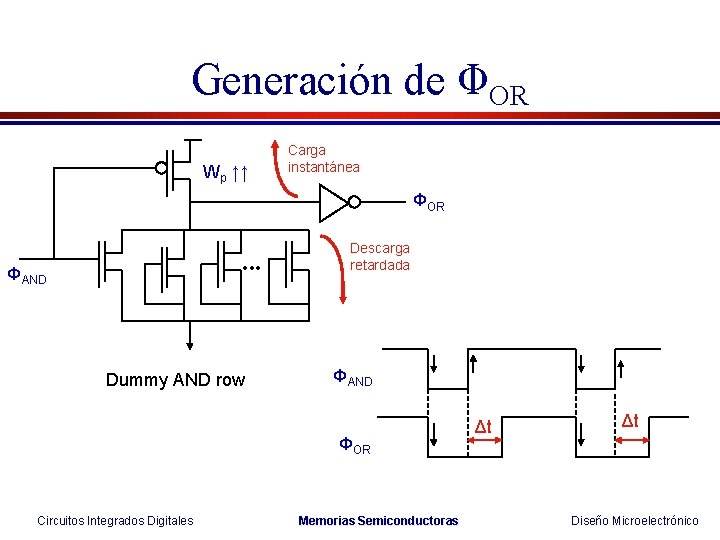

PLA Layout Lógica dinámica Pseudo NMOS Φ (1) (2) GND A GND GND C VDD GND NC GND Φ VDD GND VDD x 0 x 1 x 2 Pull-up devices C B B NC GND A Circuitos Integrados Digitales f 0 Pull-up devices Memorias Semiconductoras f 1 (1) y (2): Transistores de paso: Conexión a GND Diseño Microelectrónico controlada por Φ

![7 Memoria Flash de 1 Gbit From Nakamura 02 Sense Latches 1024 32 7. Memoria Flash de 1 Gbit From [Nakamura 02] Sense Latches (1024 + 32)](https://slidetodoc.com/presentation_image_h2/5afa606ded20c1008c7eea1356251835/image-72.jpg)

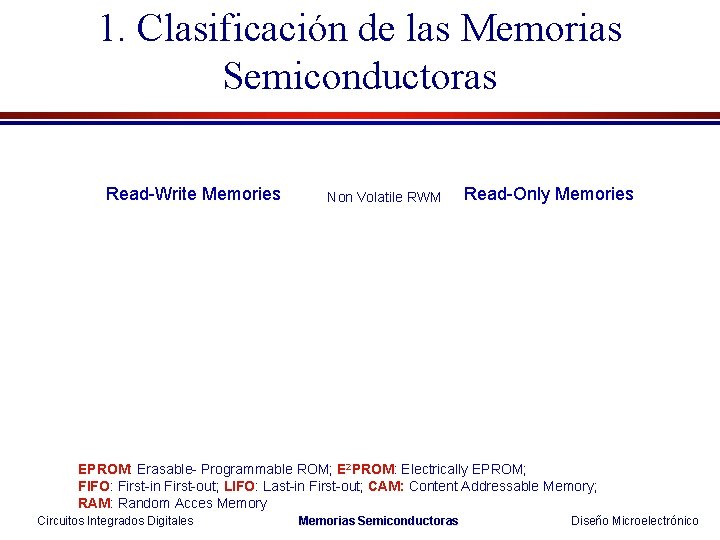

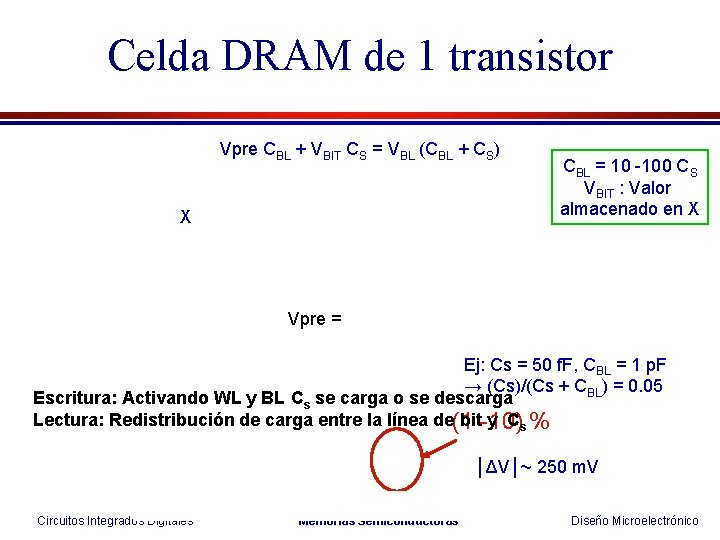

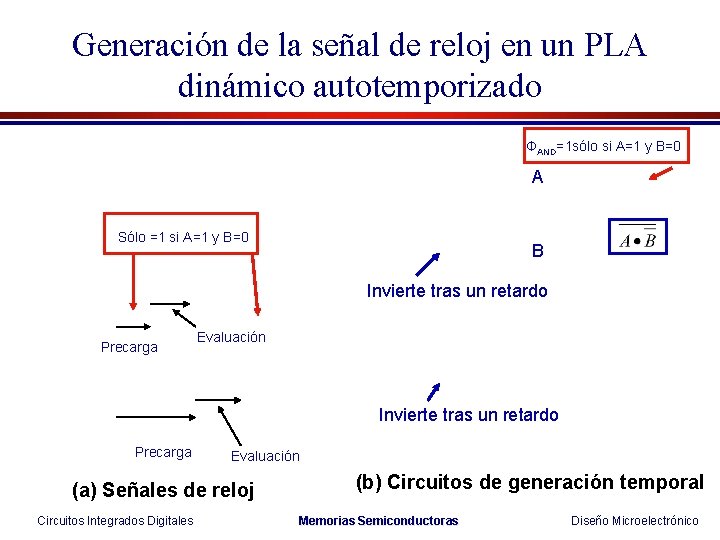

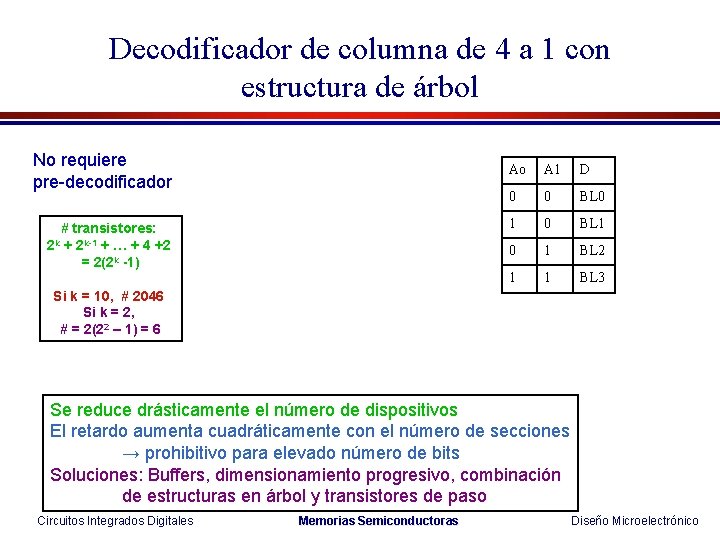

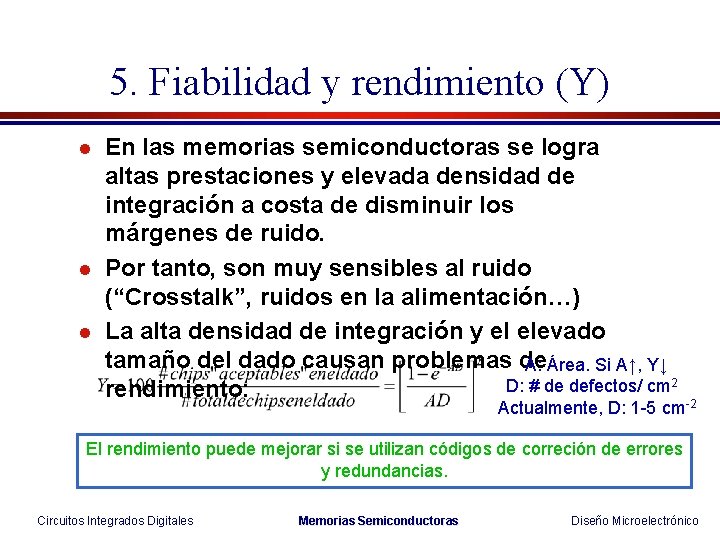

7. Memoria Flash de 1 Gbit From [Nakamura 02] Sense Latches (1024 + 32) x 8 Data Caches (1024 + 32) x 8 Circuitos Integrados Digitales Sense Latches (1024 + 32) x 8 Data Caches (1024 + 32) x 8 Memorias Semiconductoras Diseño Microelectrónico

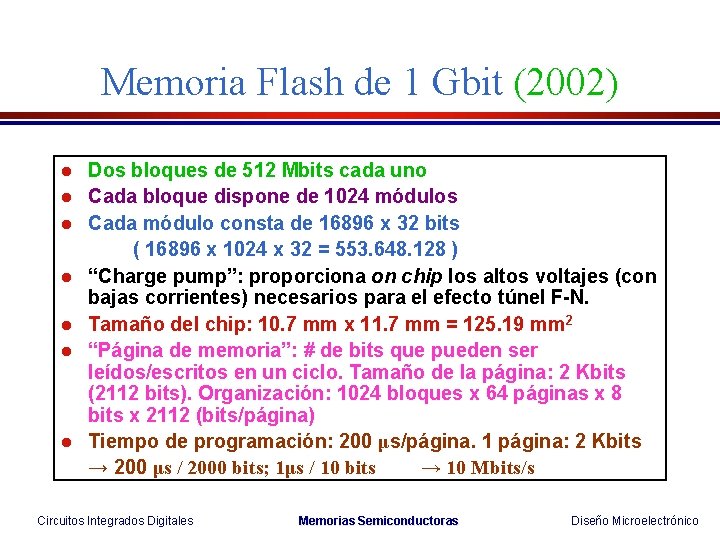

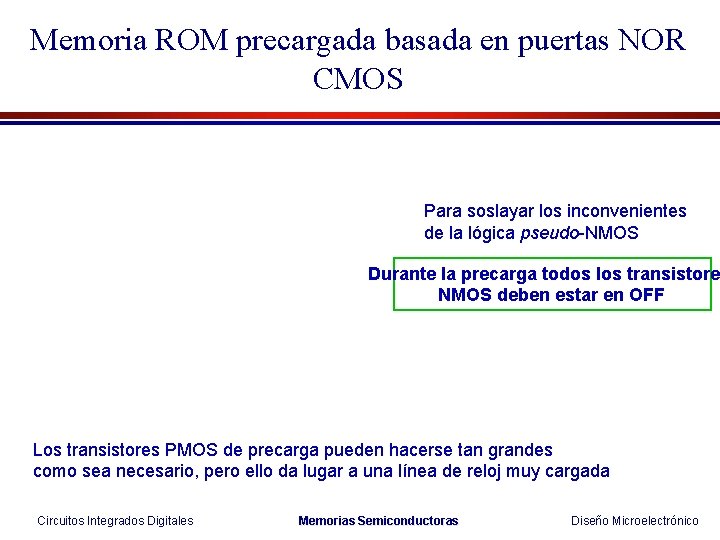

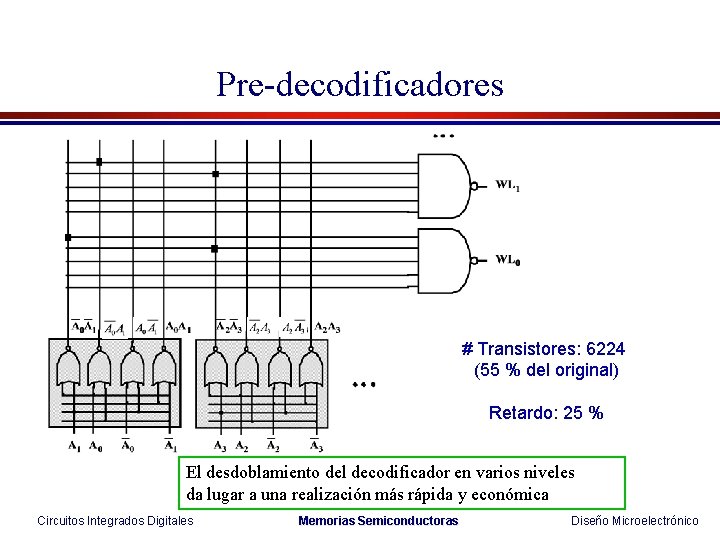

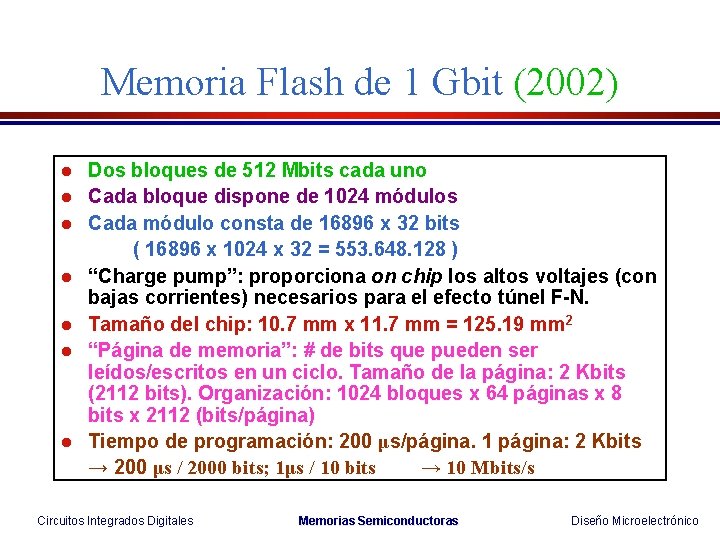

Memoria Flash de 1 Gbit (2002) l l l l Dos bloques de 512 Mbits cada uno Cada bloque dispone de 1024 módulos Cada módulo consta de 16896 x 32 bits ( 16896 x 1024 x 32 = 553. 648. 128 ) “Charge pump”: proporciona on chip los altos voltajes (con bajas corrientes) necesarios para el efecto túnel F-N. Tamaño del chip: 10. 7 mm x 11. 7 mm = 125. 19 mm 2 “Página de memoria”: # de bits que pueden ser leídos/escritos en un ciclo. Tamaño de la página: 2 Kbits (2112 bits). Organización: 1024 bloques x 64 páginas x 8 bits x 2112 (bits/página) Tiempo de programación: 200 μs/página. 1 página: 2 Kbits → 200 μs / 2000 bits; 1μs / 10 bits → 10 Mbits/s Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

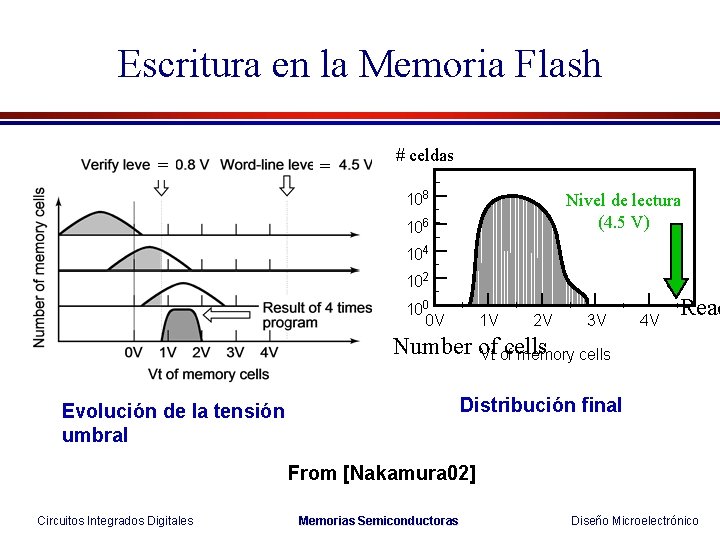

Escritura en la Memoria Flash = = # celdas 108 Nivel de lectura (4. 5 V) 106 104 102 100 0 V 1 V 2 V 3 V 4 V Read Number of cells Vt of memory cells Evolución de tensión Evolution oflathresholds Distribución final Final Distribution umbral From [Nakamura 02] Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

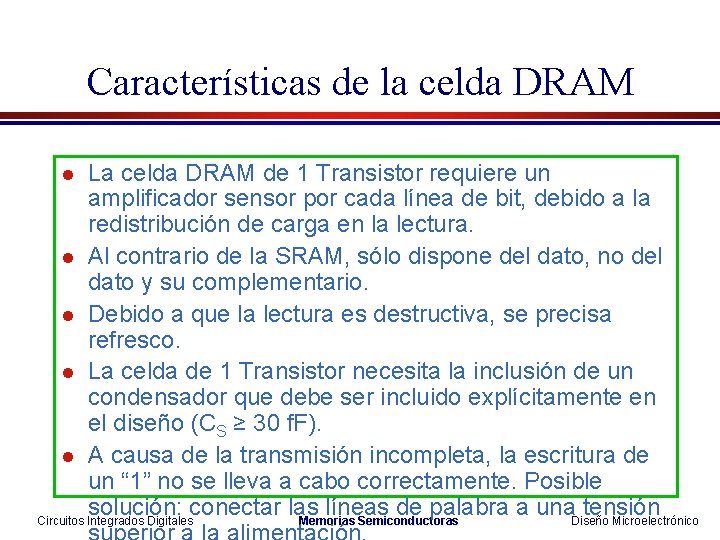

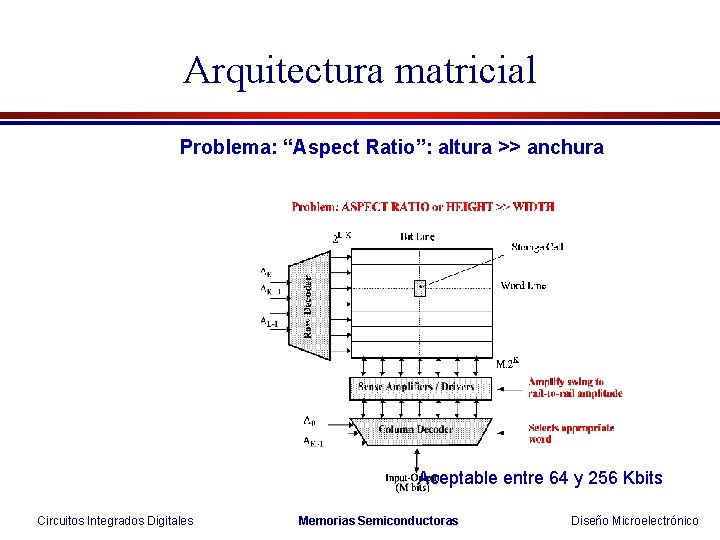

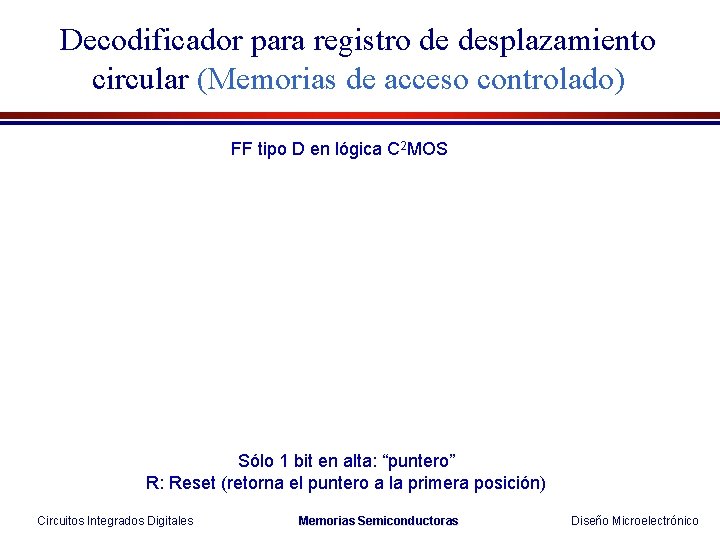

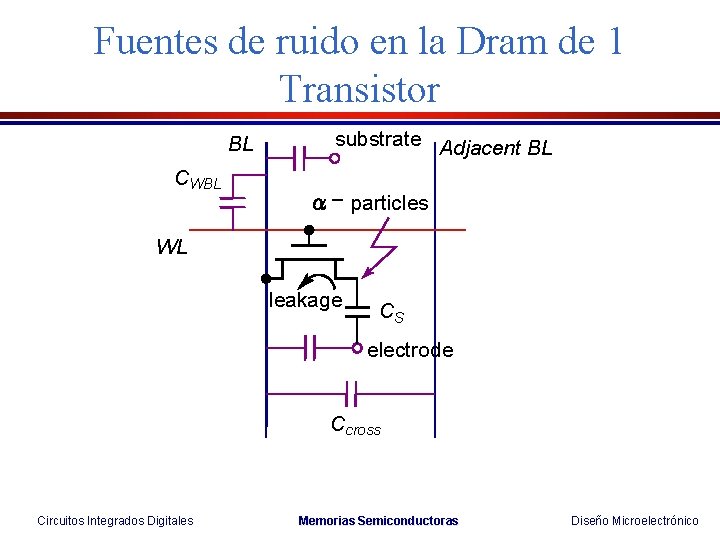

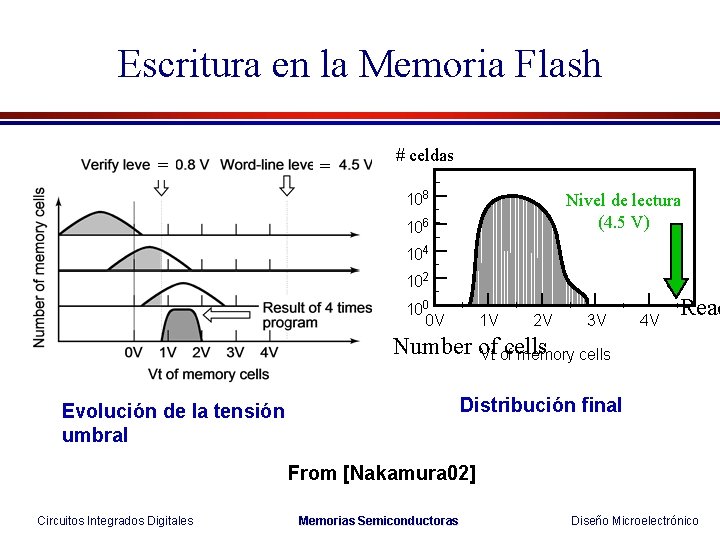

2 k. B Page buffer & cache Charge pump 10. 7 mm Memoria NAND - Flash de 1 Gbit y 125 mm 2 32 word lines x 1024 blocks 16896 bit lines From [Nakamura 02] 11. 7 mm Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

![Memoria NAND Flash de 1 Gbit y From Nakamura 02 125 mm 2 Memoria NAND - Flash de 1 Gbit y From [Nakamura 02] 125 mm 2](https://slidetodoc.com/presentation_image_h2/5afa606ded20c1008c7eea1356251835/image-76.jpg)

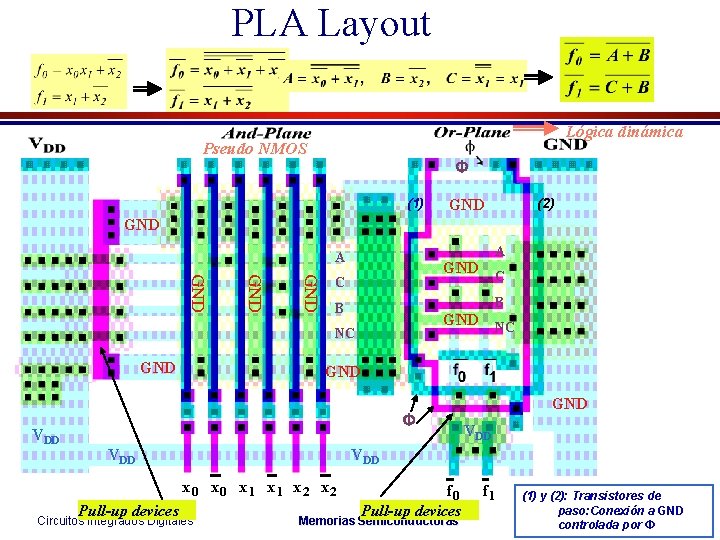

Memoria NAND - Flash de 1 Gbit y From [Nakamura 02] 125 mm 2 l l l l l Tecnología 0. 13 m p-sub CMOS triple-well 1 poly, 1 polycide, 1 W, 2 Al Tamaño de la Celda 0. 077 m 2 Tamaño del Chip 125. 2 mm 2 Organización 2112 x 8 b x 64 page x 1 k block 1 página: 2 Kbits Alimentación 2. 7 V-3. 6 V Duración del Ciclo 50 ns Tiempo de lectura 25 s Tiempo de programación 200 s / page (10 Mbits/s) Tiempo de borrado 2 ms / block Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

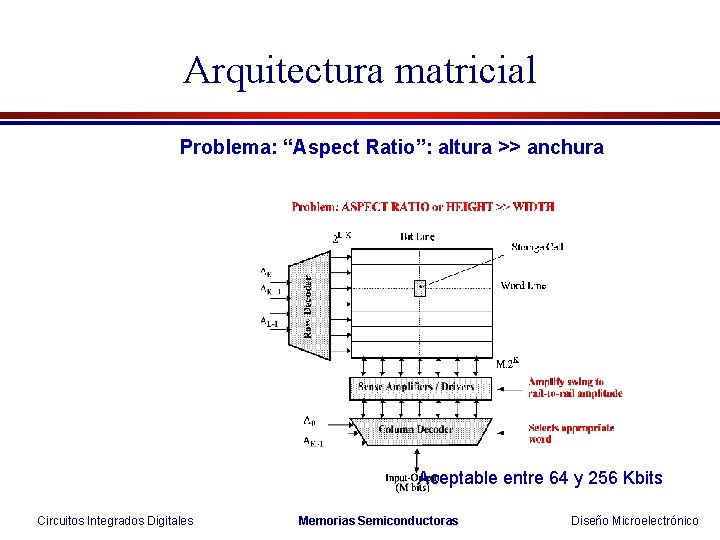

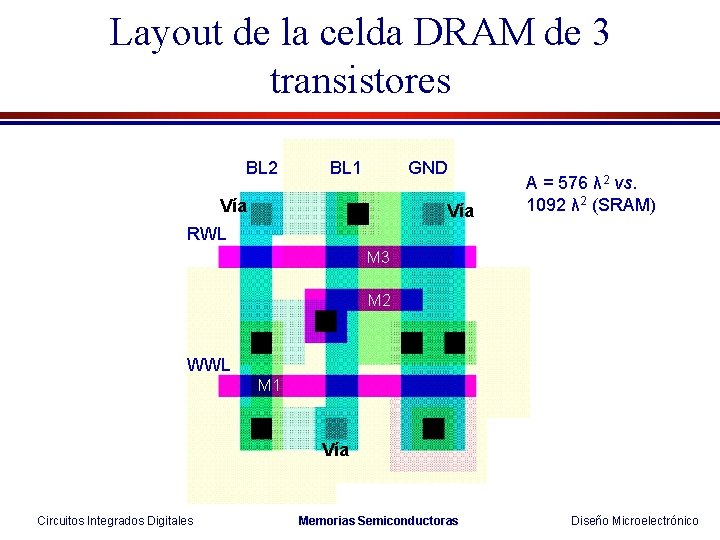

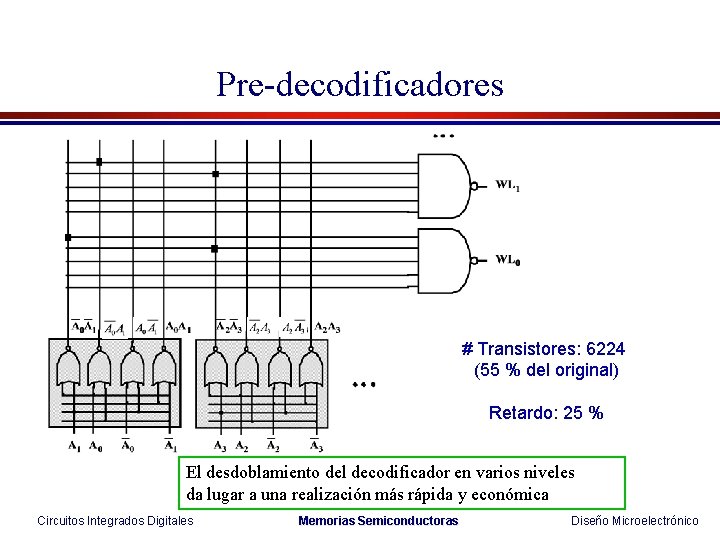

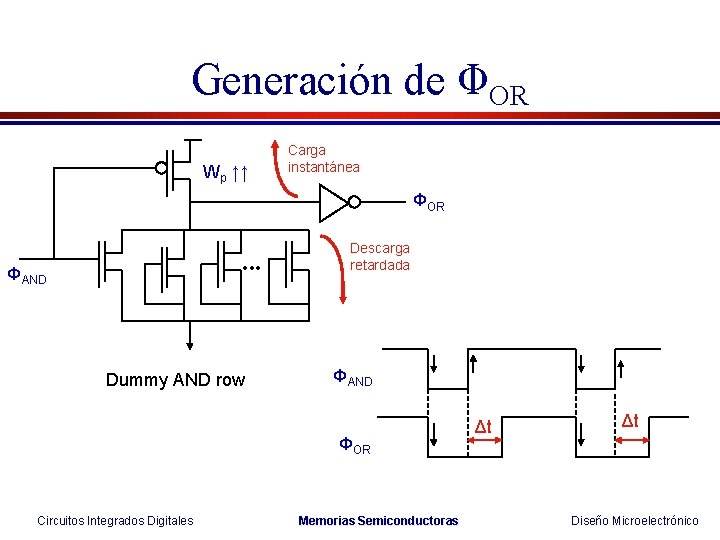

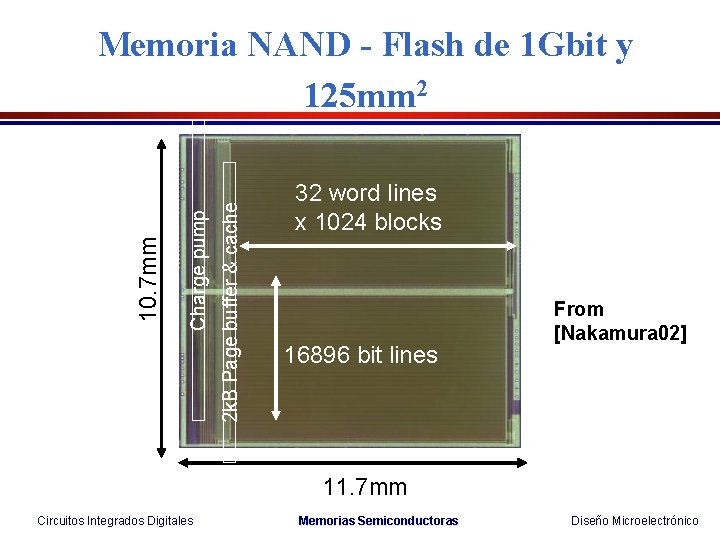

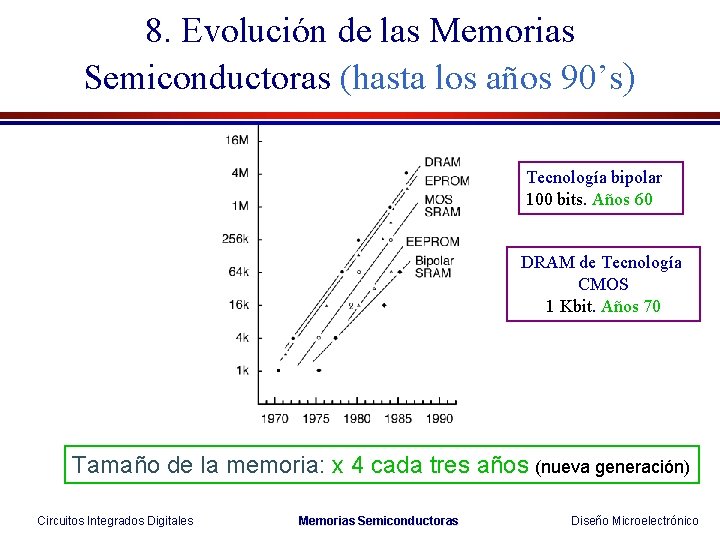

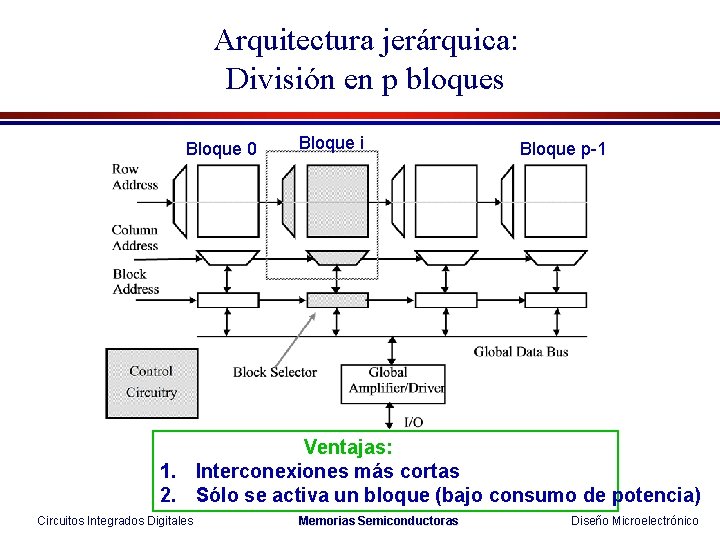

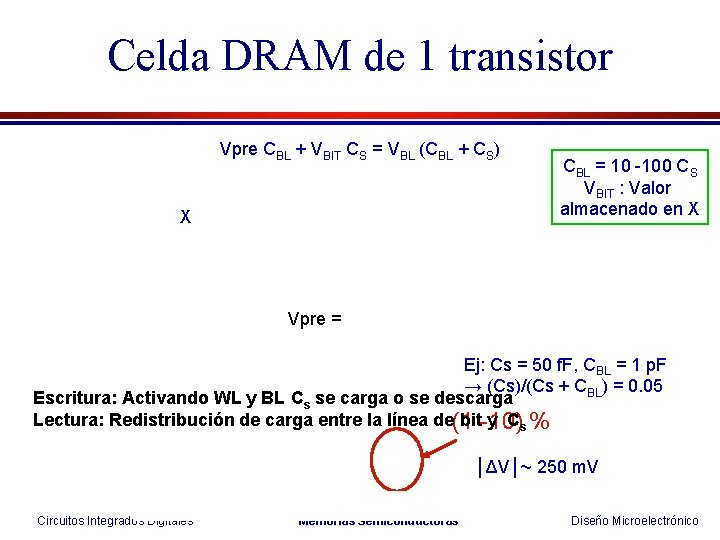

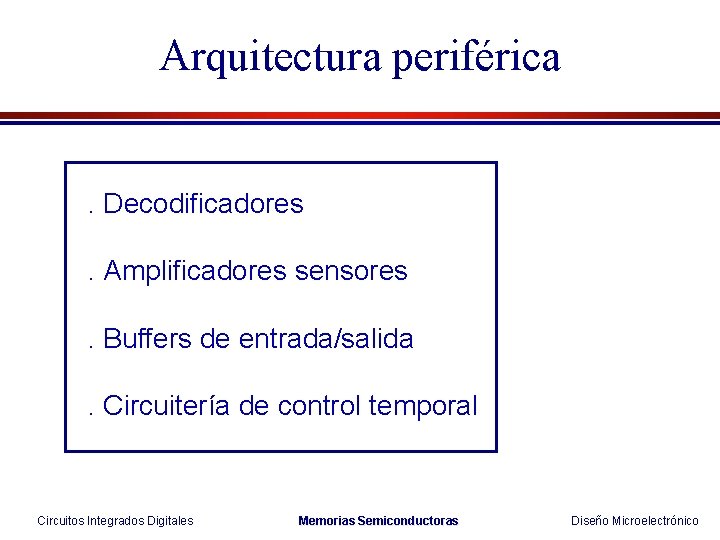

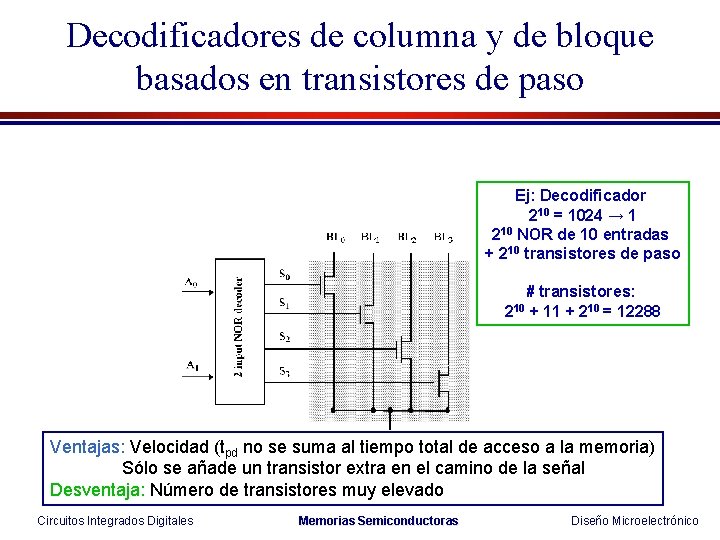

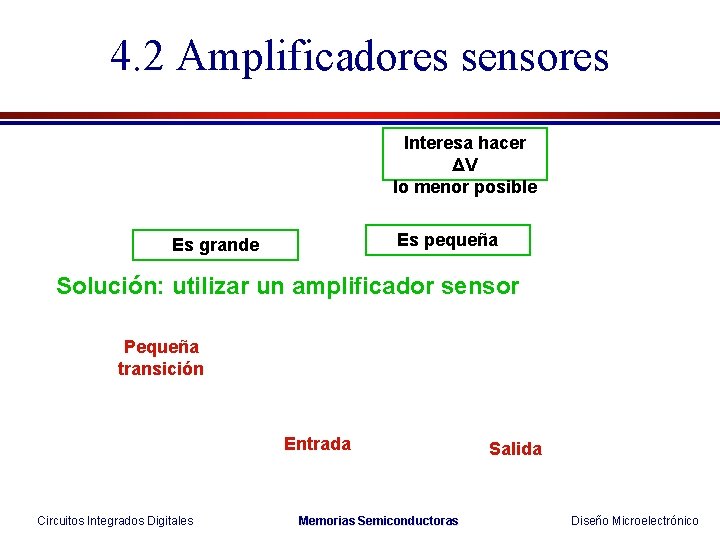

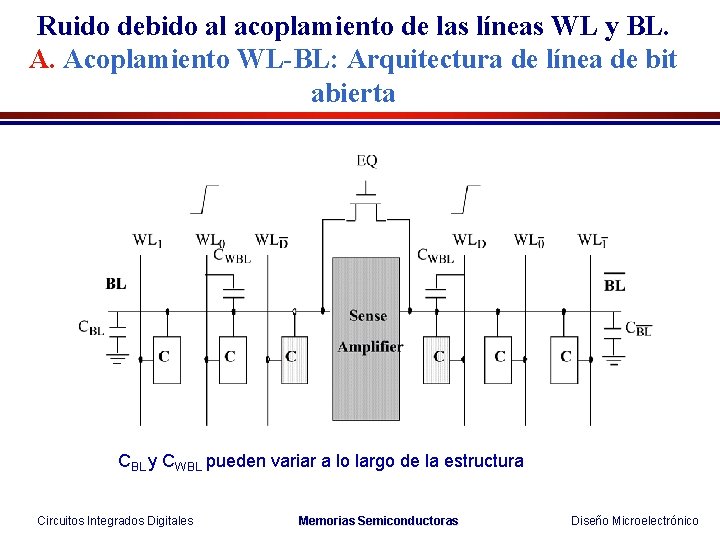

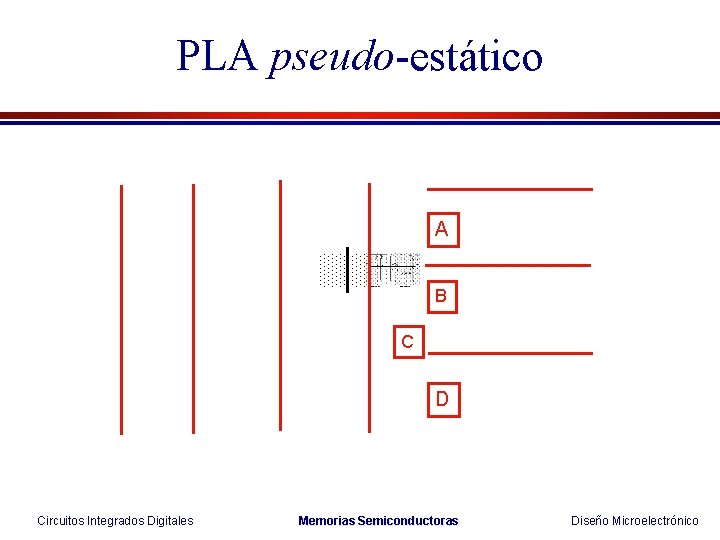

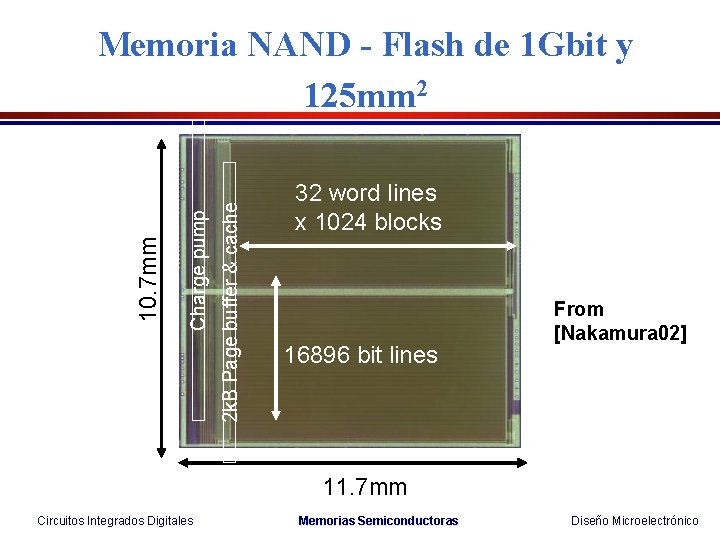

8. Evolución de las Memorias Semiconductoras (hasta los años 90’s) Tecnología bipolar 100 bits. Años 60 DRAM de Tecnología CMOS 1 Kbit. Años 70 Tamaño de la memoria: x 4 cada tres años (nueva generación) Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

![Evolución de las Memorias Semiconductoras hasta la fecha From Itoh 01 1 K 1 Evolución de las Memorias Semiconductoras (hasta la fecha) From [Itoh 01] 1 K 1](https://slidetodoc.com/presentation_image_h2/5afa606ded20c1008c7eea1356251835/image-78.jpg)

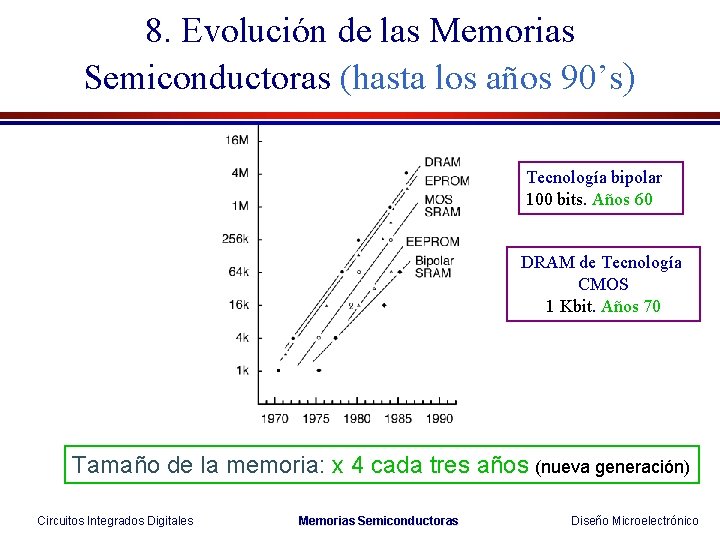

Evolución de las Memorias Semiconductoras (hasta la fecha) From [Itoh 01] 1 K 1 G 1970 2000 6 órdenes de magnitud en 30 años A partir de 1995: Saturación Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

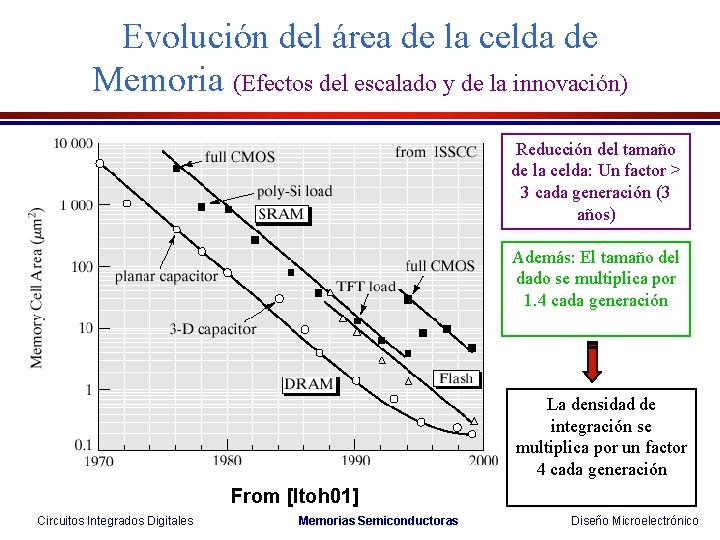

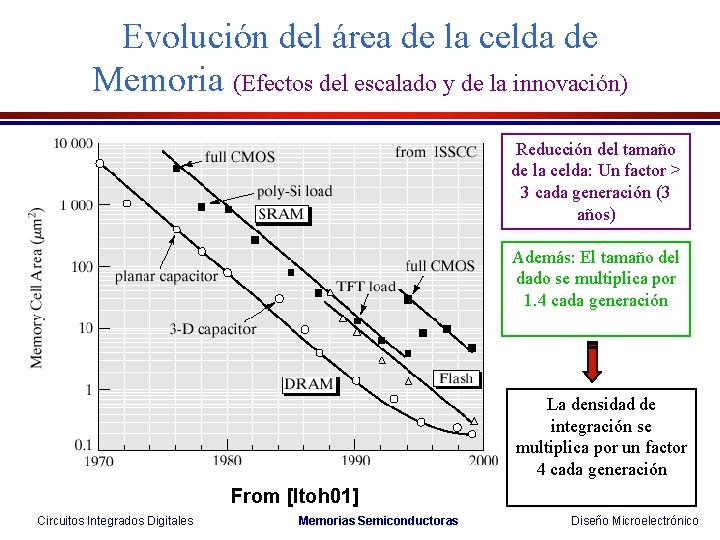

Evolución del área de la celda de Memoria (Efectos del escalado y de la innovación) Reducción del tamaño de la celda: Un factor > 3 cada generación (3 años) Además: El tamaño del dado se multiplica por 1. 4 cada generación La densidad de integración se multiplica por un factor 4 cada generación From [Itoh 01] Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico

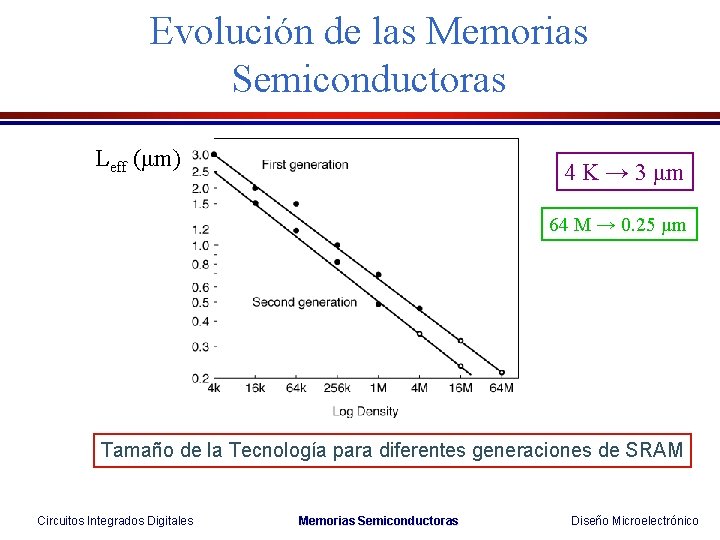

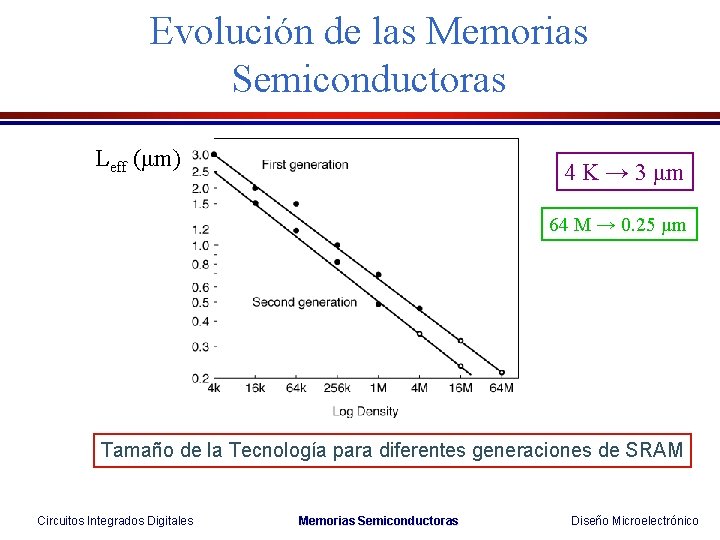

Evolución de las Memorias Semiconductoras Leff (μm) 4 K → 3 μm 64 M → 0. 25 μm Tamaño de la Tecnología para diferentes generaciones de SRAM Circuitos Integrados Digitales Memorias Semiconductoras Diseño Microelectrónico