Diseo de Lgica Combinacional SISTEMAS DIGITALES I Circuito

Diseño de Lógica Combinacional SISTEMAS DIGITALES I

Circuito Lógico Combinacional Un circuito lógico cuya salida solo depende del valor de sus entradas es llamado un circuito combinacional Su operación es totalmente descrita por la tabla de verdad, que lista todas las combinaciones posibles de las entradas y el respectivo valor de salida X Y Z F

Minimización de Lógica Combinacional Implementar el circuito directamente de la tabla de verdad tiene varias desventajas: • Es antieconómico, por la cantidad de compuertas lógicas necesarias • Es propenso a errores, por la cantidad de ‘cableado’ necesario Minimización consiste en reducir la cantidad y el tamaño de las compuertas lógicas necesarias para implementar el circuito combinacional

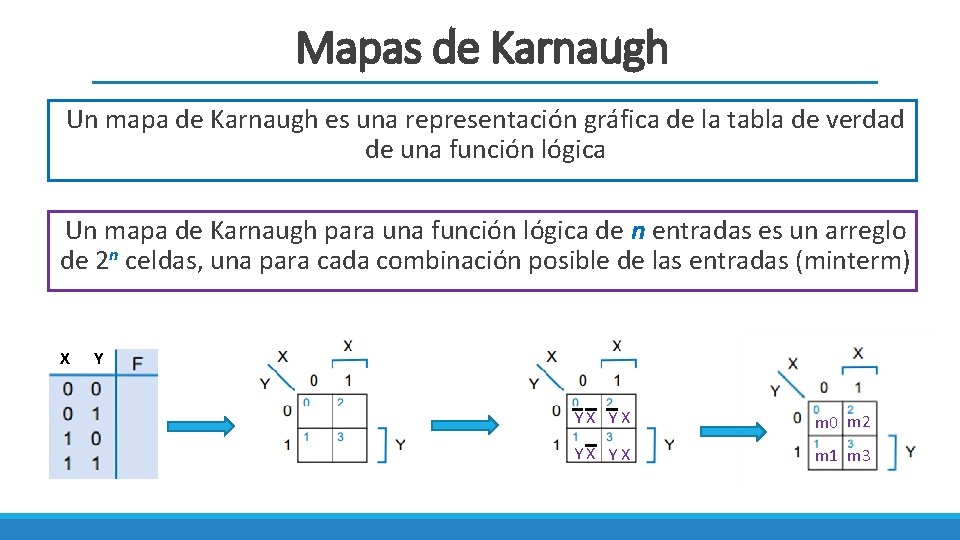

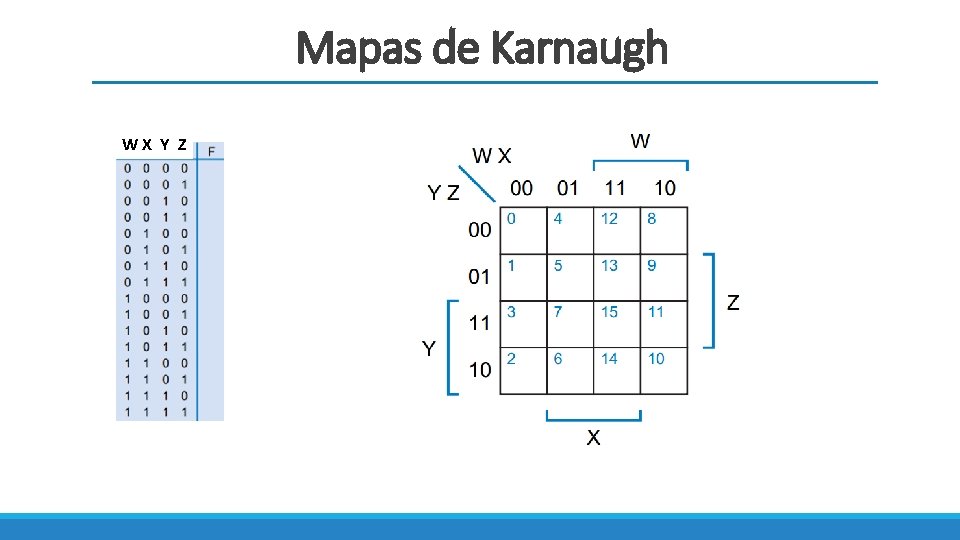

Mapas de Karnaugh Un mapa de Karnaugh es una representación gráfica de la tabla de verdad de una función lógica Un mapa de Karnaugh para una función lógica de n entradas es un arreglo de 2 n celdas, una para cada combinación posible de las entradas (minterm) X Y YX YX m 0 m 2 YX YX m 1 m 3

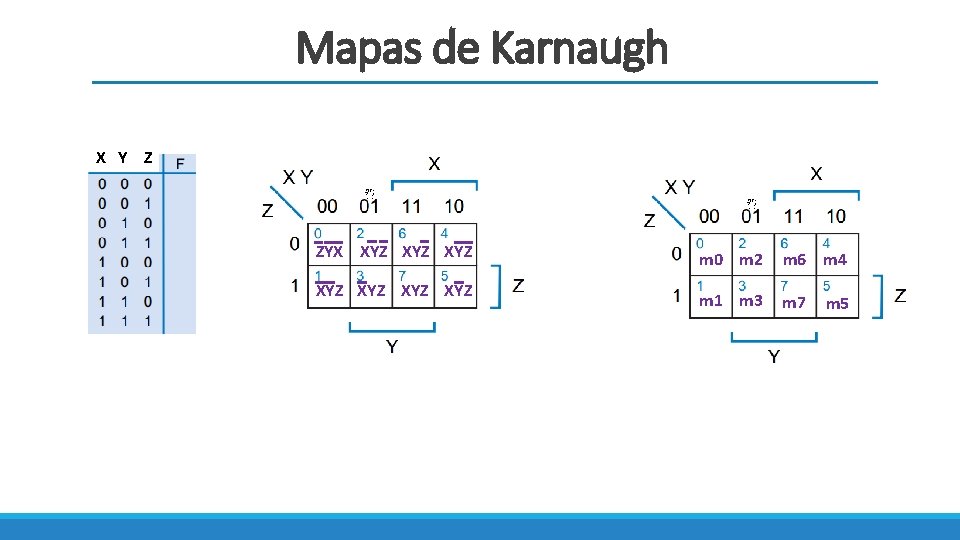

Mapas de Karnaugh X Y Z ZYX XYZ XYZ m 0 m 2 m 6 m 4 m 1 m 3 m 7 m 5

Mapas de Karnaugh WX Y Z

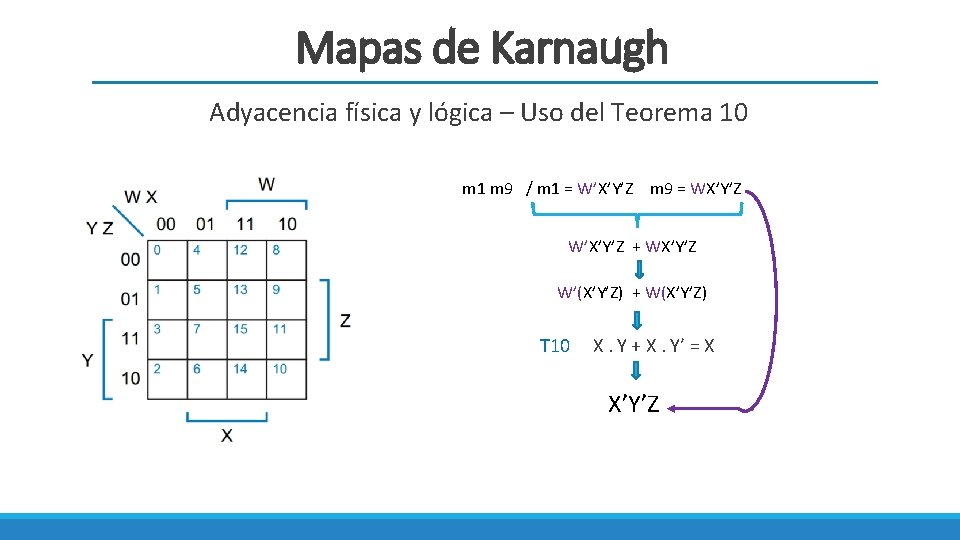

Mapas de Karnaugh Adyacencia física y lógica – Uso del Teorema 10 m 1 m 9 / m 1 = W’X’Y’Z m 9 = WX’Y’Z W’X’Y’Z + WX’Y’Z W’(X’Y’Z) + W(X’Y’Z) T 10 X. Y + X. Y’ = X X’Y’Z

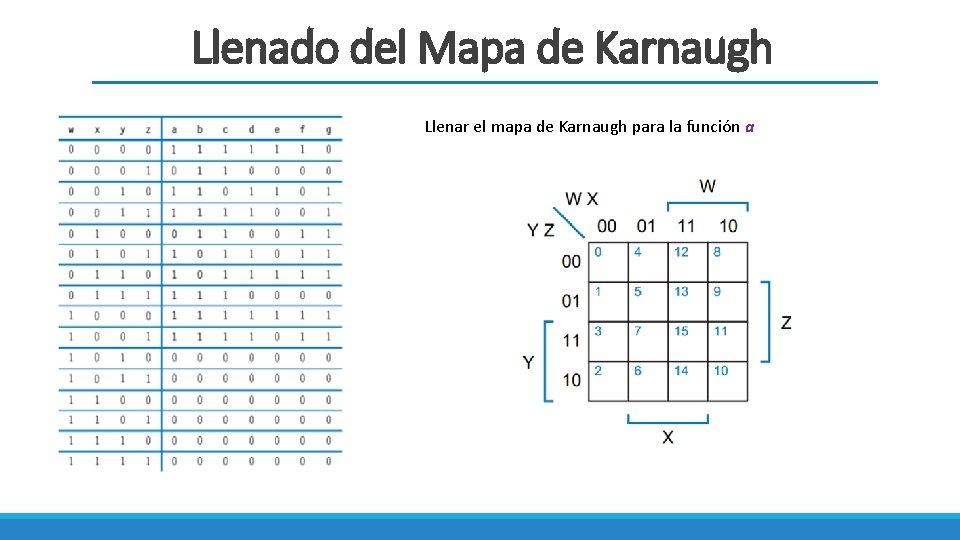

Llenado del Mapa de Karnaugh Llenar el mapa de Karnaugh para la función a

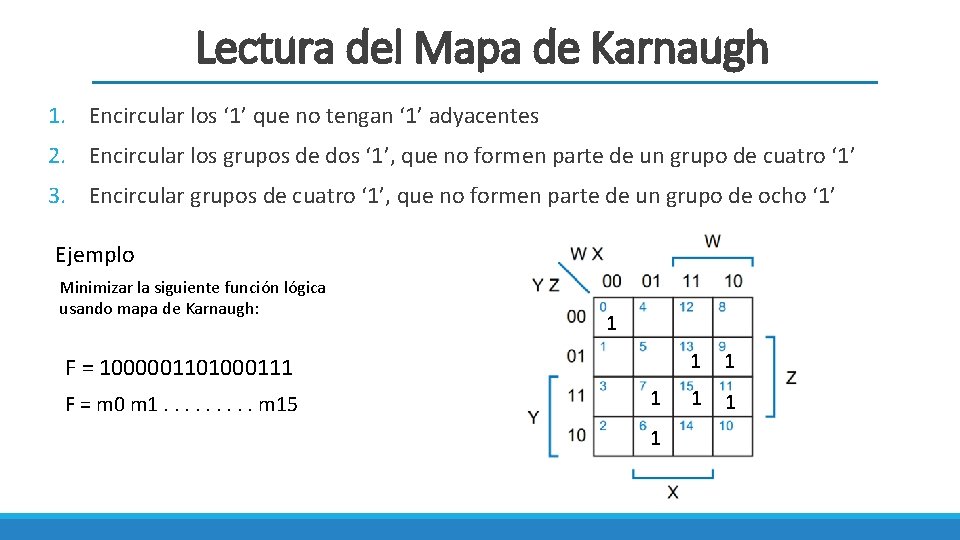

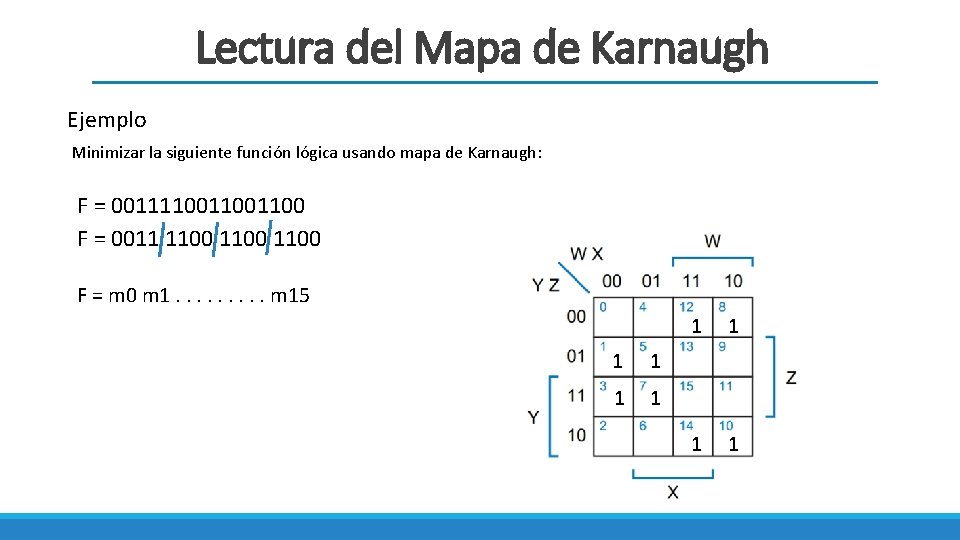

Lectura del Mapa de Karnaugh 1. Encircular los ‘ 1’ que no tengan ‘ 1’ adyacentes 2. Encircular los grupos de dos ‘ 1’, que no formen parte de un grupo de cuatro ‘ 1’ 3. Encircular grupos de cuatro ‘ 1’, que no formen parte de un grupo de ocho ‘ 1’ Ejemplo Minimizar la siguiente función lógica usando mapa de Karnaugh: 1 F = 1000001101000111 F = m 0 m 1. . m 15 1 1 1

Lectura del Mapa de Karnaugh Ejemplo Minimizar la siguiente función lógica usando mapa de Karnaugh: F = 001111001100 F = 0011 1100 F = m 0 m 1. . m 15 1 1 1 1

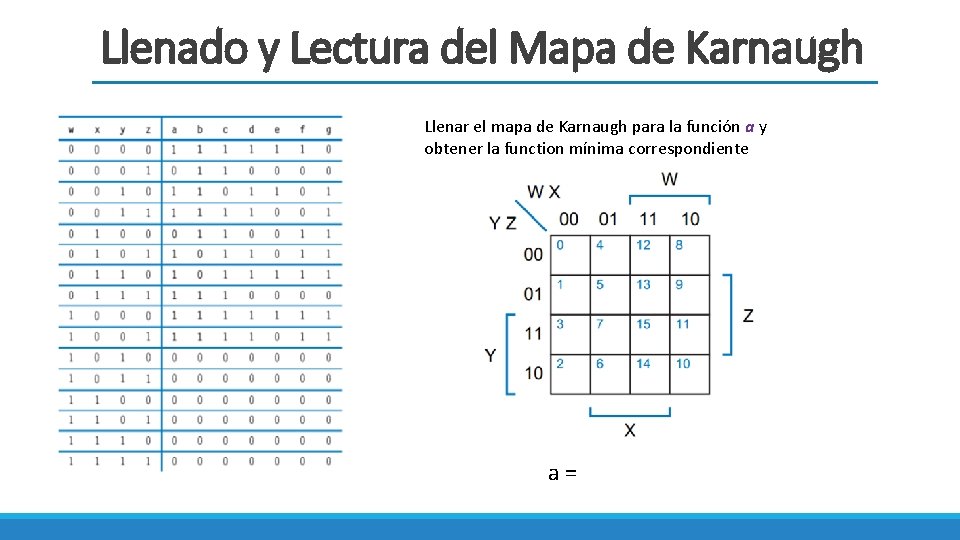

Llenado y Lectura del Mapa de Karnaugh Llenar el mapa de Karnaugh para la función a y obtener la function mínima correspondiente a=

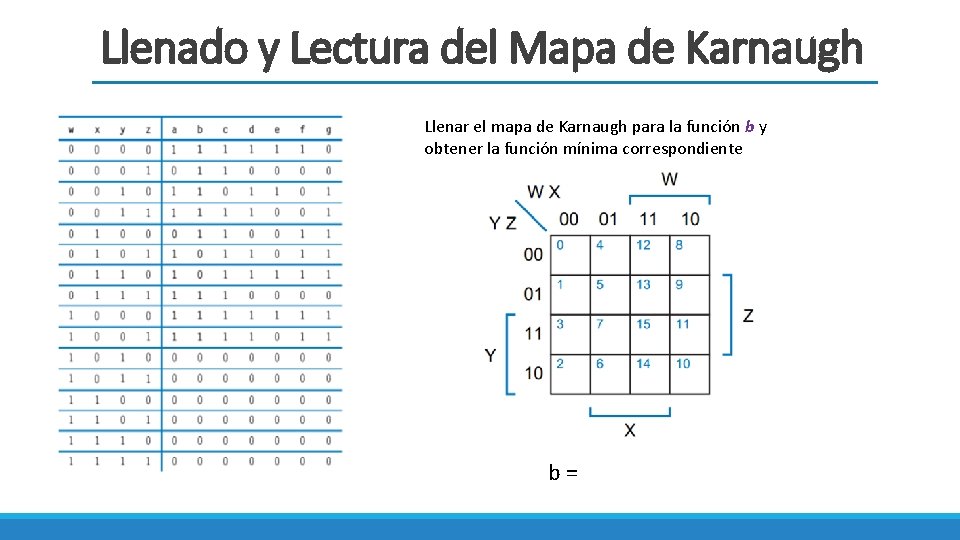

Llenado y Lectura del Mapa de Karnaugh Llenar el mapa de Karnaugh para la función b y obtener la función mínima correspondiente b=

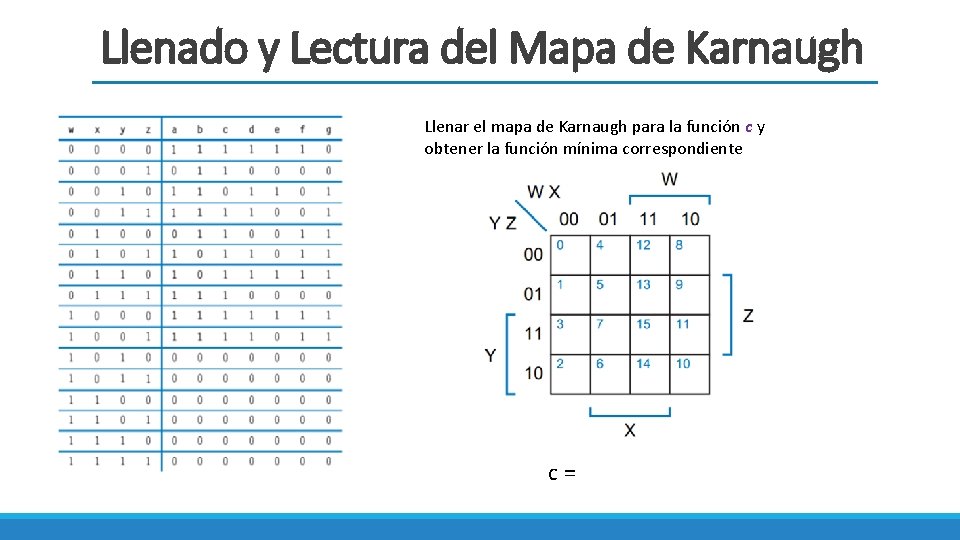

Llenado y Lectura del Mapa de Karnaugh Llenar el mapa de Karnaugh para la función c y obtener la función mínima correspondiente c=

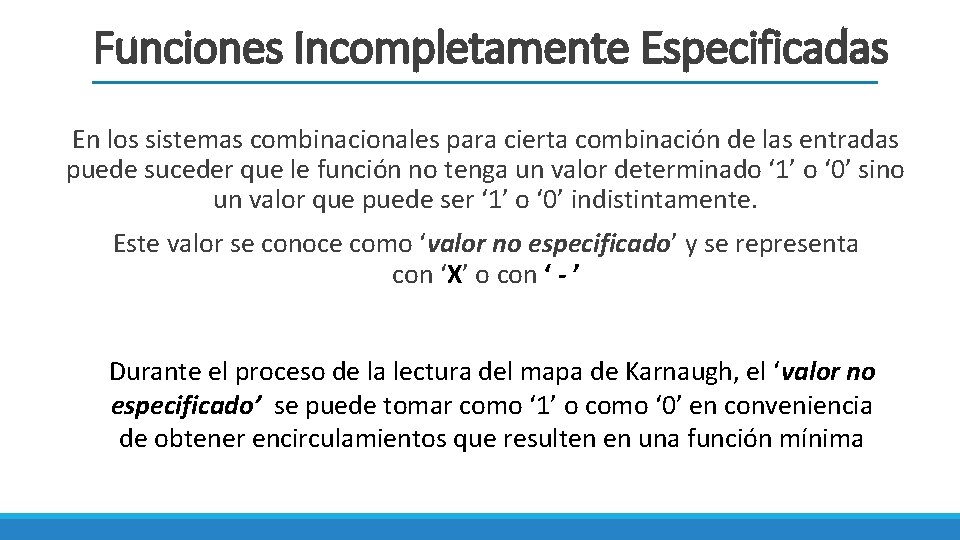

Funciones Incompletamente Especificadas En los sistemas combinacionales para cierta combinación de las entradas puede suceder que le función no tenga un valor determinado ‘ 1’ o ‘ 0’ sino un valor que puede ser ‘ 1’ o ‘ 0’ indistintamente. Este valor se conoce como ‘valor no especificado’ y se representa con ‘X’ o con ‘ - ’ Durante el proceso de la lectura del mapa de Karnaugh, el ‘valor no especificado’ se puede tomar como ‘ 1’ o como ‘ 0’ en conveniencia de obtener encirculamientos que resulten en una función mínima

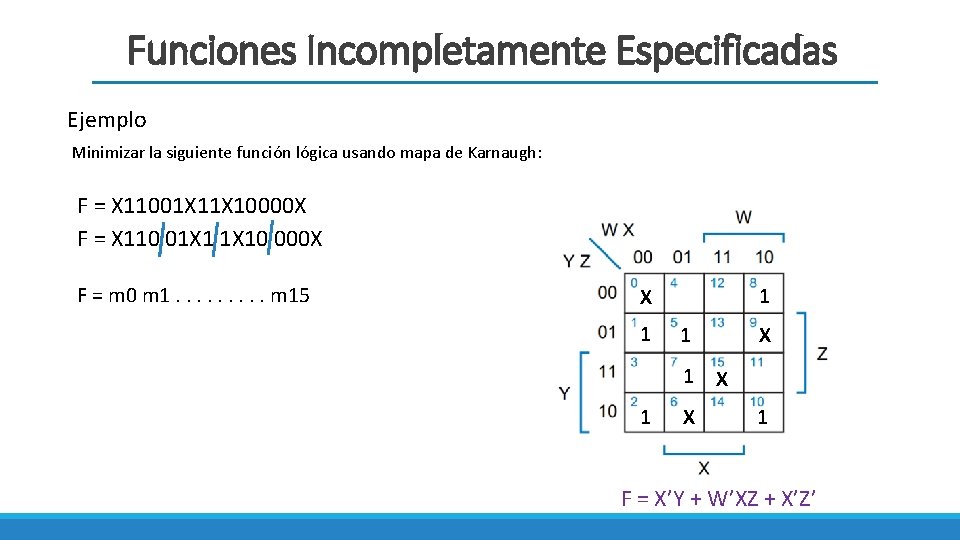

Funciones Incompletamente Especificadas Ejemplo Minimizar la siguiente función lógica usando mapa de Karnaugh: F = X 11001 X 10000 X F = X 110 01 X 10 000 X F = m 0 m 1. . m 15 1 X 1 1 X X X 1 F = X’Y + W’XZ + X’Z’

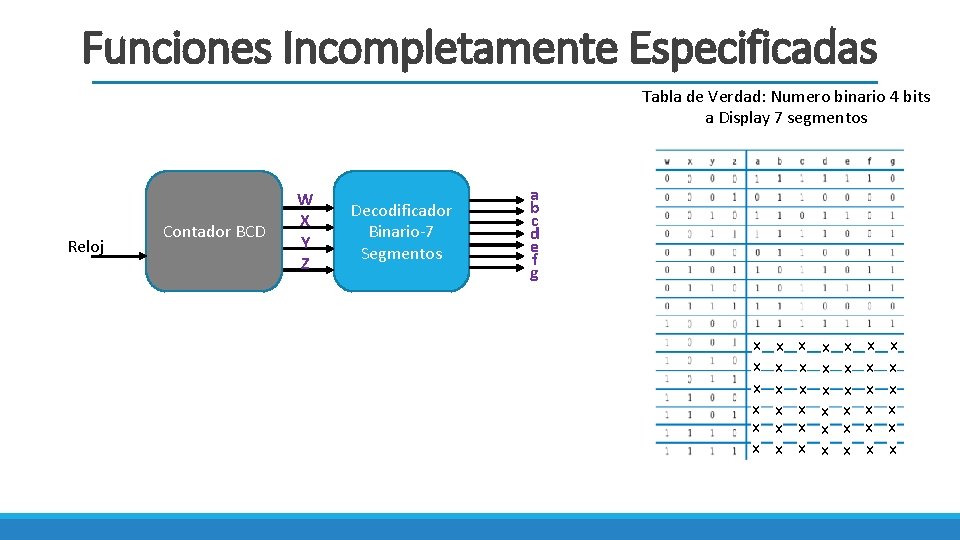

Funciones Incompletamente Especificadas Tabla de Verdad: Numero binario 4 bits a Display 7 segmentos a b c d e f g x x x x x x x x x Contador BCD Decodificador Binario-7 Segmentos x x x Reloj W X Y Z

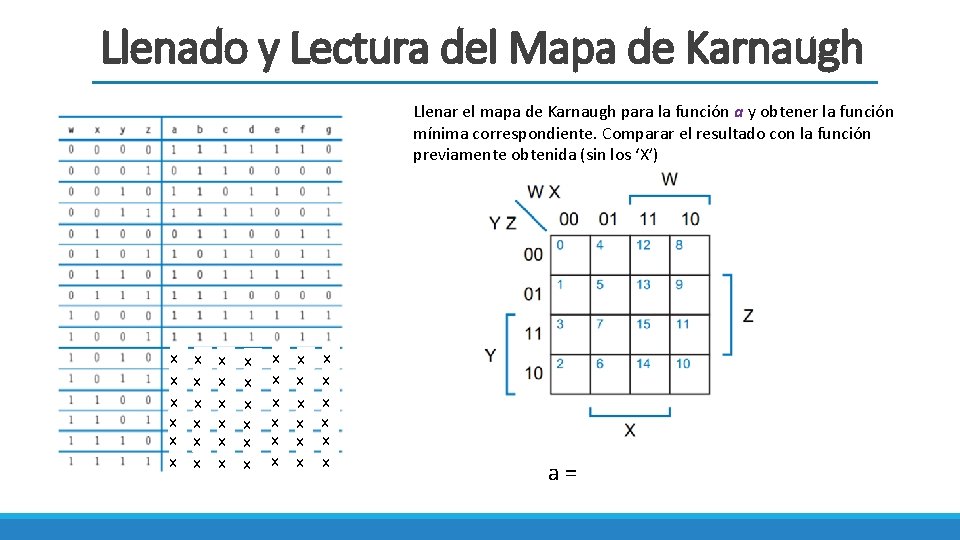

Llenado y Lectura del Mapa de Karnaugh Llenar el mapa de Karnaugh para la función a y obtener la función mínima correspondiente. Comparar el resultado con la función previamente obtenida (sin los ‘X’) x x x x x x x x x x x a=

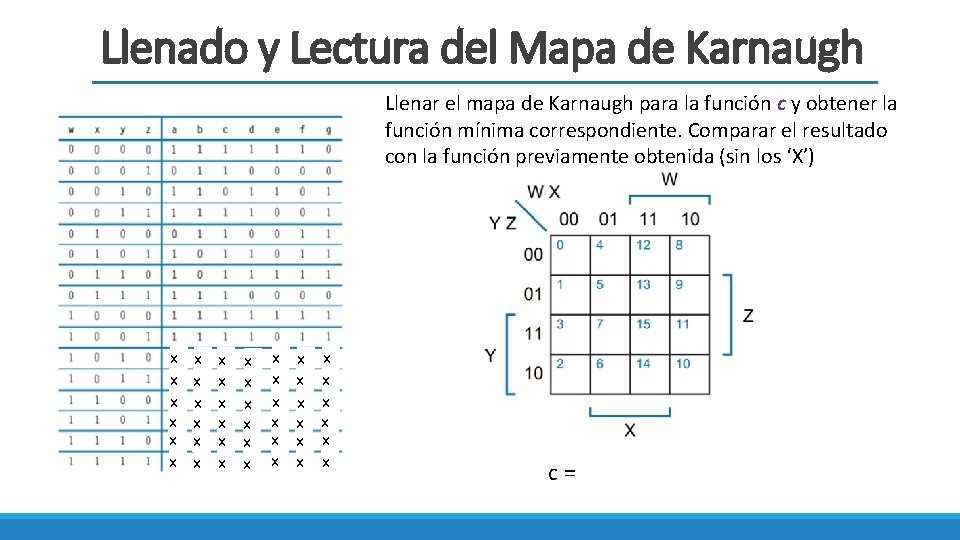

Llenado y Lectura del Mapa de Karnaugh Llenar el mapa de Karnaugh para la función c y obtener la función mínima correspondiente. Comparar el resultado con la función previamente obtenida (sin los ‘X’) x x x x x x x x x x x c=

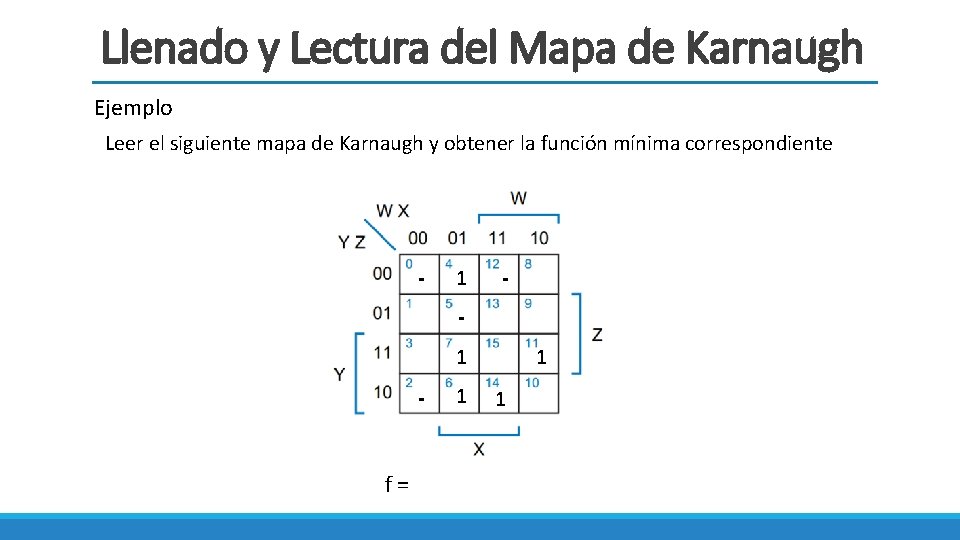

Llenado y Lectura del Mapa de Karnaugh Ejemplo Leer el siguiente mapa de Karnaugh y obtener la función mínima correspondiente - 1 - f= 1 1 1

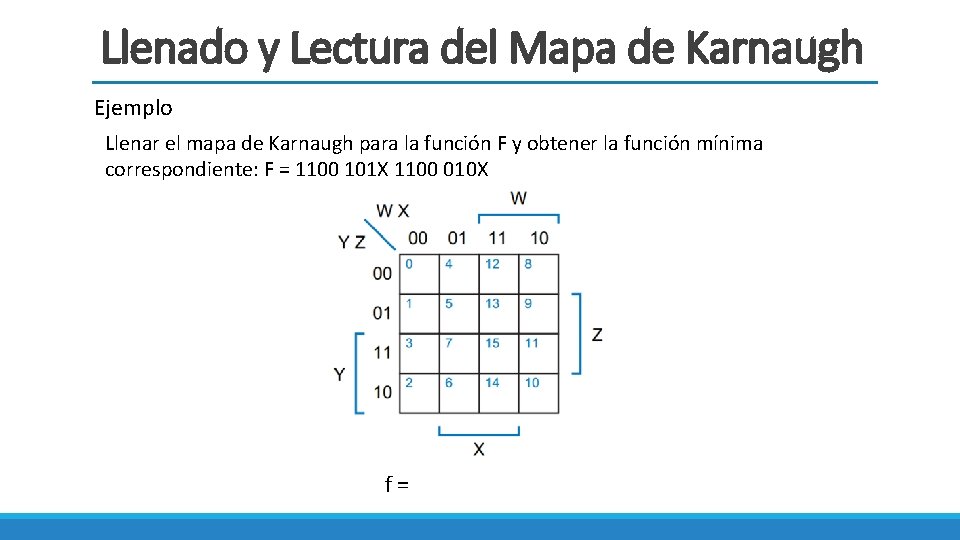

Llenado y Lectura del Mapa de Karnaugh Ejemplo Llenar el mapa de Karnaugh para la función F y obtener la función mínima correspondiente: F = 1100 101 X 1100 010 X f=

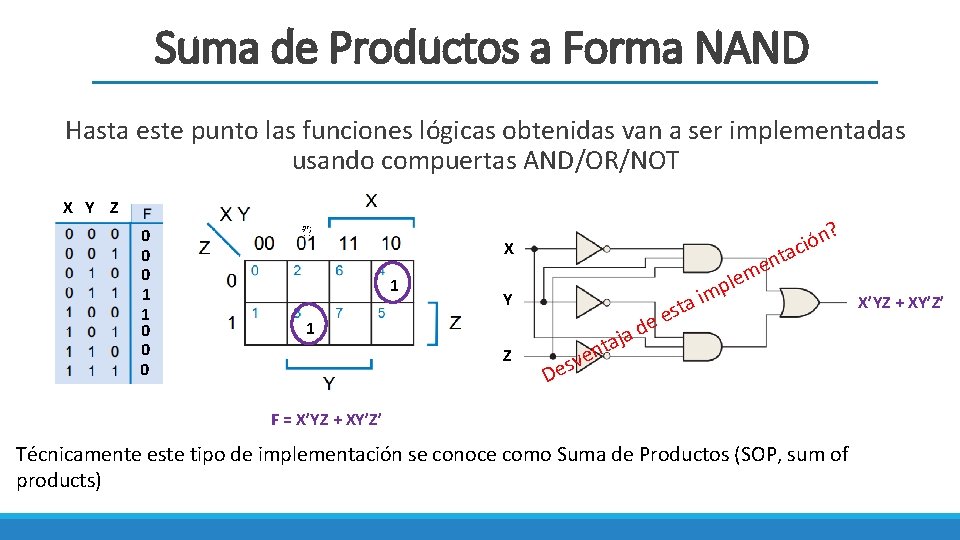

Suma de Productos a Forma NAND Hasta este punto las funciones lógicas obtenidas van a ser implementadas usando compuertas AND/OR/NOT X Y Z 0 0 0 1 1 0 0 0 X 1 nt e m Y 1 Z n? ó i ac e d a j ta a est le p im en v s De F = X’YZ + XY’Z’ Técnicamente este tipo de implementación se conoce como Suma de Productos (SOP, sum of products) X’YZ + XY’Z’

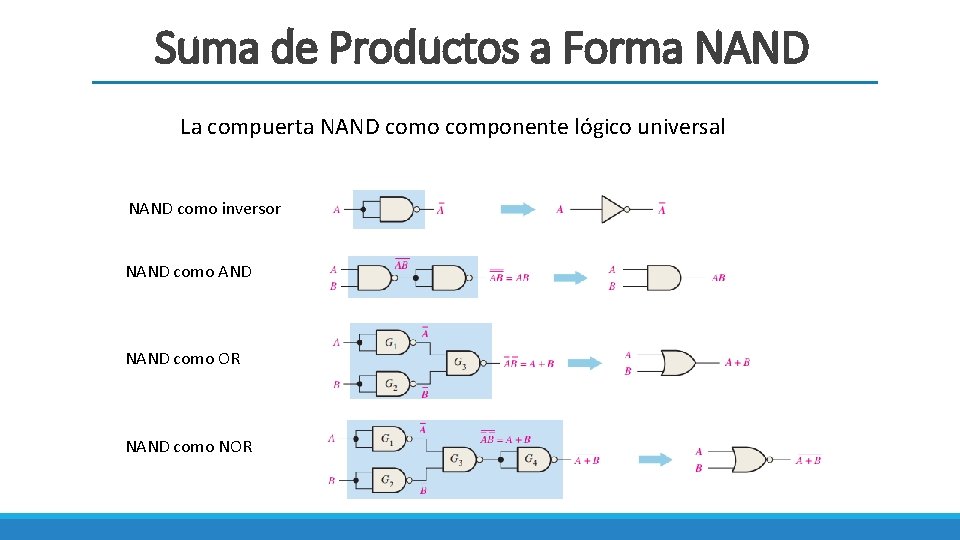

Suma de Productos a Forma NAND La compuerta NAND como componente lógico universal NAND como inversor NAND como AND NAND como OR NAND como NOR

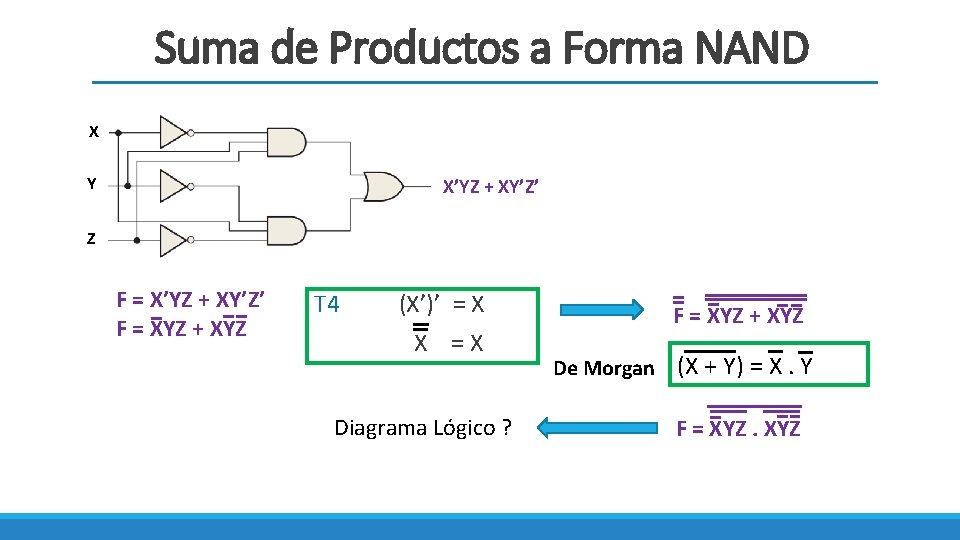

Suma de Productos a Forma NAND X Y X’YZ + XY’Z’ Z F = X’YZ + XY’Z’ F = XYZ + XYZ T 4 (X’)’ = X X =X Diagrama Lógico ? F = XYZ + XYZ De Morgan (X + Y) = X. Y F = XYZ

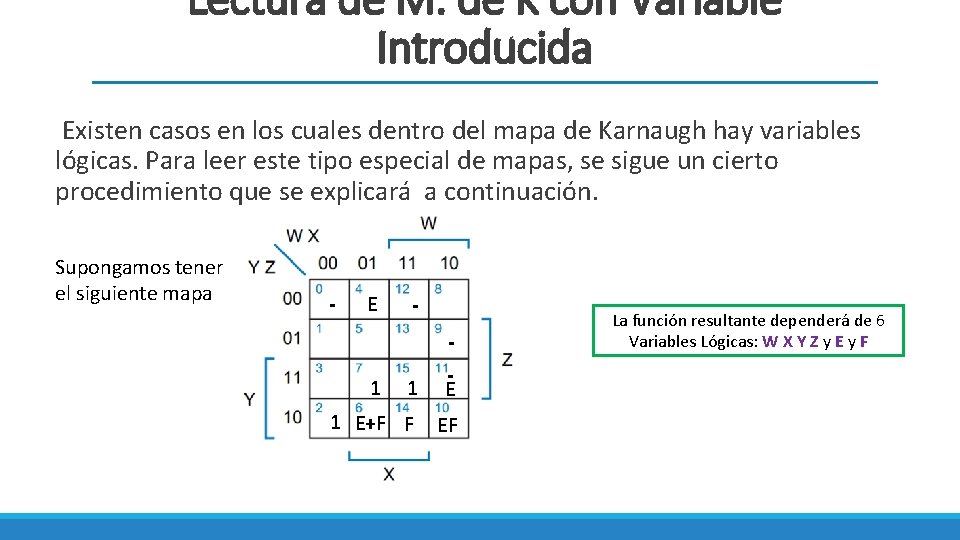

Lectura de M. de K con Variable Introducida Existen casos en los cuales dentro del mapa de Karnaugh hay variables lógicas. Para leer este tipo especial de mapas, se sigue un cierto procedimiento que se explicará a continuación. Supongamos tener el siguiente mapa - E 1 E+F F EF 1 La función resultante dependerá de 6 Variables Lógicas: W X Y Z y E y F

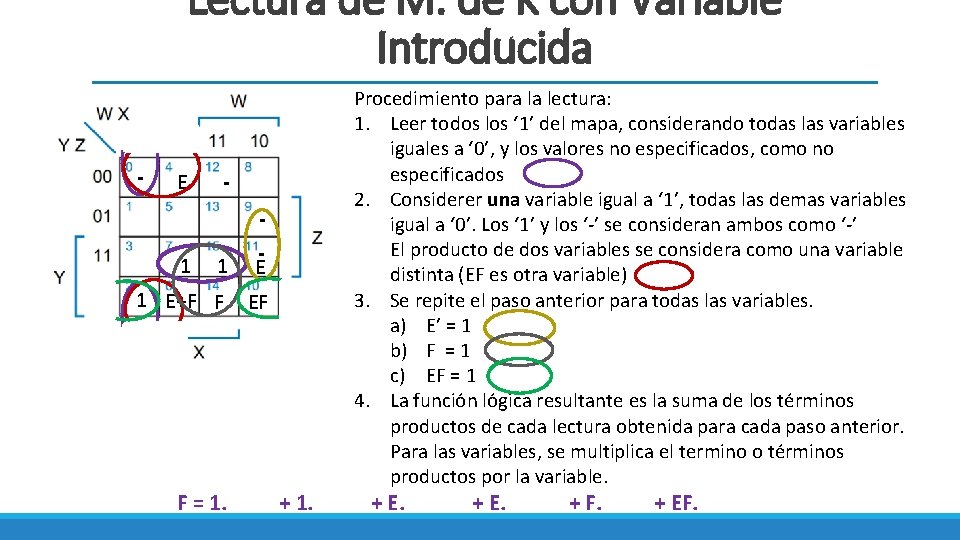

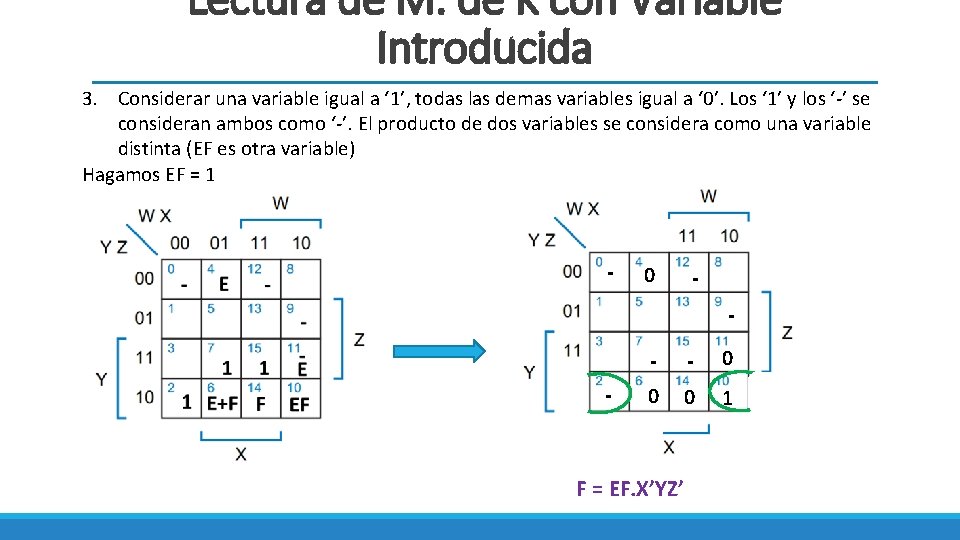

Lectura de M. de K con Variable Introducida - E 1 E+F F EF 1 F = 1. + 1. Procedimiento para la lectura: 1. Leer todos los ‘ 1’ del mapa, considerando todas las variables iguales a ‘ 0’, y los valores no especificados, como no especificados 2. Considerer una variable igual a ‘ 1’, todas las demas variables igual a ‘ 0’. Los ‘ 1’ y los ‘-’ se consideran ambos como ‘-’ El producto de dos variables se considera como una variable distinta (EF es otra variable) 3. Se repite el paso anterior para todas las variables. a) E’ = 1 b) F = 1 c) EF = 1 4. La función lógica resultante es la suma de los términos productos de cada lectura obtenida para cada paso anterior. Para las variables, se multiplica el termino o términos productos por la variable. + E. + F. + EF.

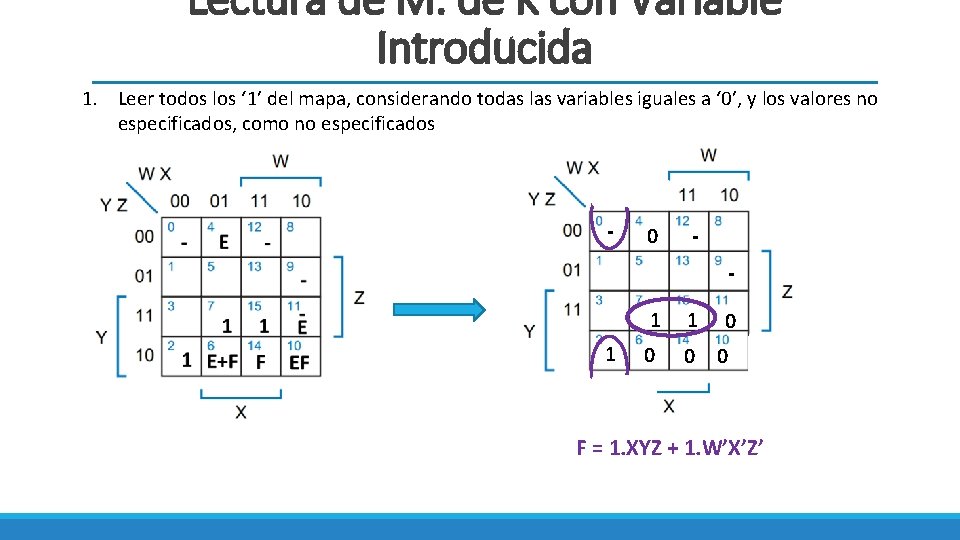

Lectura de M. de K con Variable Introducida 1. Leer todos los ‘ 1’ del mapa, considerando todas las variables iguales a ‘ 0’, y los valores no especificados, como no especificados - 0 - 1 1 1 0 0 F = 1. XYZ + 1. W’X’Z’

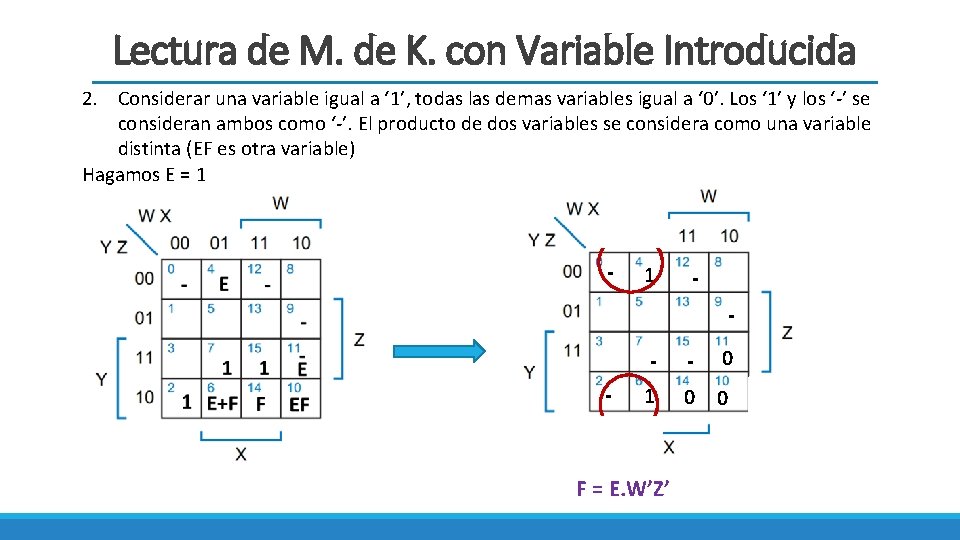

Lectura de M. de K. con Variable Introducida 2. Considerar una variable igual a ‘ 1’, todas las demas variables igual a ‘ 0’. Los ‘ 1’ y los ‘-’ se consideran ambos como ‘-’. El producto de dos variables se considera como una variable distinta (EF es otra variable) Hagamos E = 1 - - - - 0 1 0 0 F = E. W’Z’

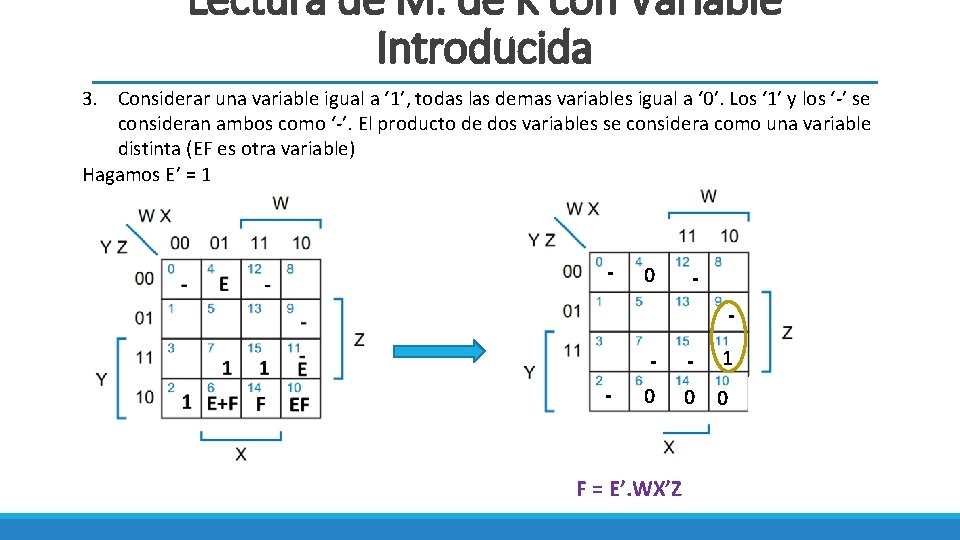

Lectura de M. de K con Variable Introducida 3. Considerar una variable igual a ‘ 1’, todas las demas variables igual a ‘ 0’. Los ‘ 1’ y los ‘-’ se consideran ambos como ‘-’. El producto de dos variables se considera como una variable distinta (EF es otra variable) Hagamos E’ = 1 - 0 - - 1 0 0 0 F = E’. WX’Z

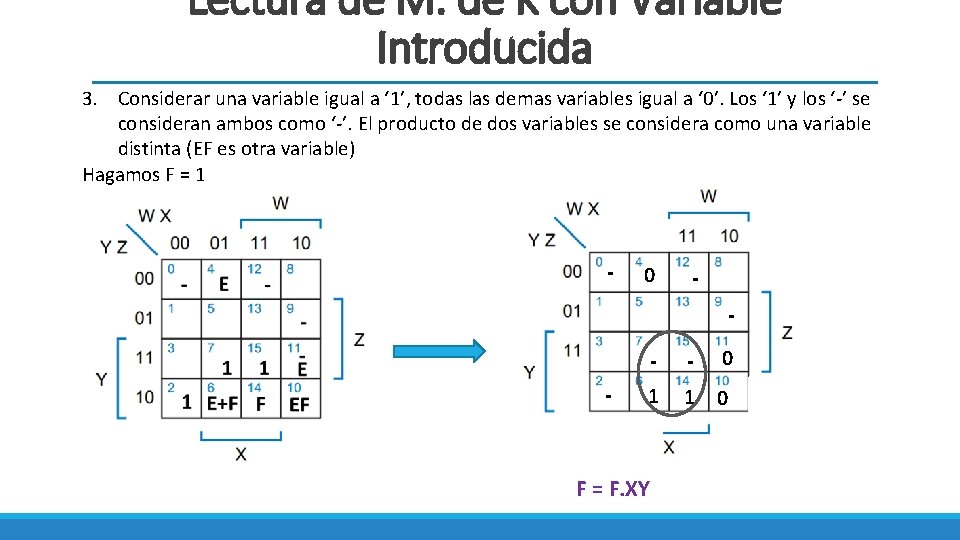

Lectura de M. de K con Variable Introducida 3. Considerar una variable igual a ‘ 1’, todas las demas variables igual a ‘ 0’. Los ‘ 1’ y los ‘-’ se consideran ambos como ‘-’. El producto de dos variables se considera como una variable distinta (EF es otra variable) Hagamos F = 1 - 0 - - 0 1 1 0 F = F. XY

Lectura de M. de K con Variable Introducida 3. Considerar una variable igual a ‘ 1’, todas las demas variables igual a ‘ 0’. Los ‘ 1’ y los ‘-’ se consideran ambos como ‘-’. El producto de dos variables se considera como una variable distinta (EF es otra variable) Hagamos EF = 1 - 0 - - 0 0 0 1 F = EF. X’YZ’

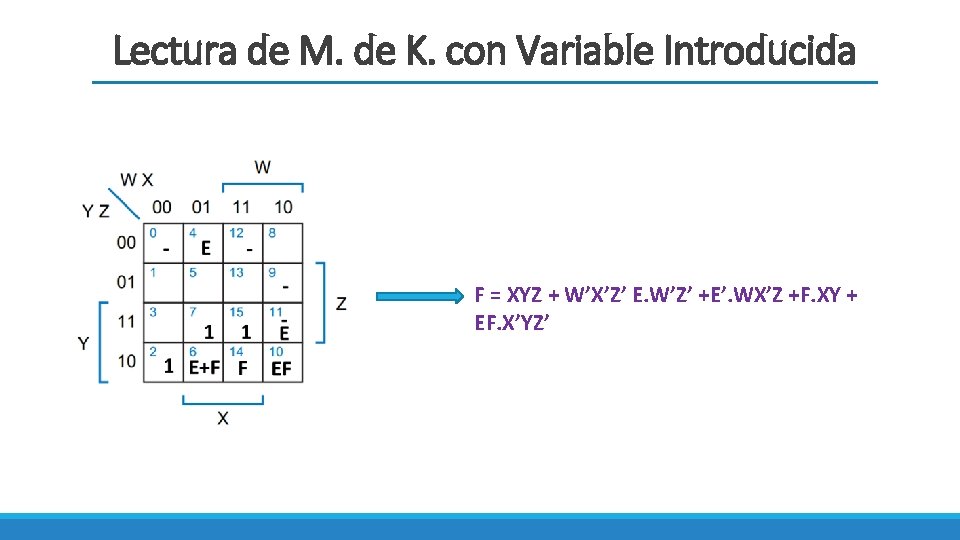

Lectura de M. de K. con Variable Introducida F = XYZ + W’X’Z’ E. W’Z’ +E’. WX’Z +F. XY + EF. X’YZ’

Lógica Combinacional - Ejercicios 1. Obtener la expresión mínima de una función, que detecte cuando el números de las variables de entrada (cuatro variables de entrada) que tengan un valor lógico ‘ 1’ es menor que el número de variables con valor lógico ‘ 0’. La función esta únicamente definida cuando al menos una variable se encuentra en ‘ 1’.

Lógica Combinacional - Ejercicios 2. Diseñar un sistema que detecte cuando un número codificado en ‘Exceso de 3’ tenga igual cantidad de ‘ 1’ y de ‘ 0’.

Lógica Combinacional - Ejercicios 3. Diseñar un circuito combinacional que teniendo como entrada un data de cuatro bits, detecte cuando el número de unos de las entradas es par si el número es mayor que Siete, y si es impar cuando el número es menor que siete.

Lógica Combinacional - Ejercicios 4. Diseñar un circuito combinacional comparador que detecte cuando un número representado por dos bits de los cuatro bits de entrada sea mayor, igual o menor que los otros dos números de dos bits. WX ><= YZ

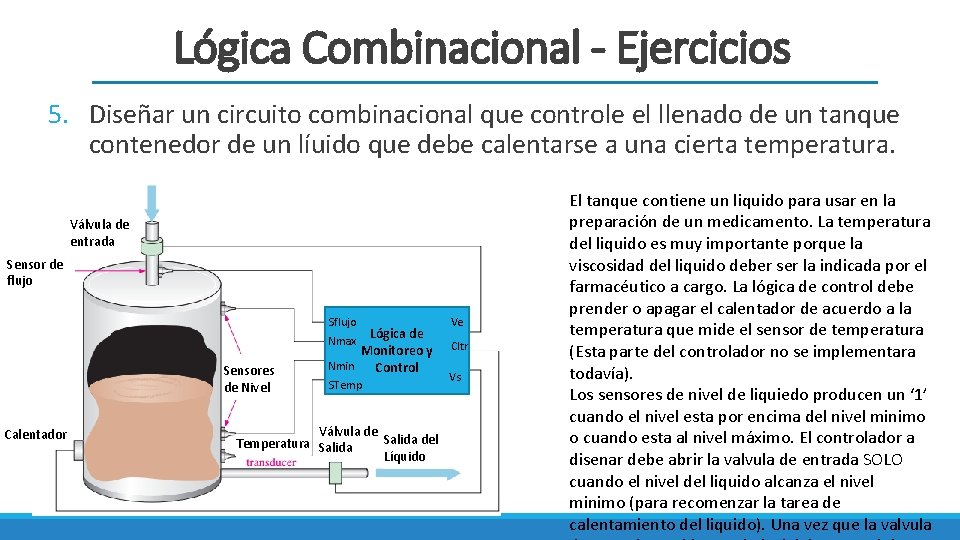

Lógica Combinacional - Ejercicios 5. Diseñar un circuito combinacional que controle el llenado de un tanque contenedor de un líuido que debe calentarse a una cierta temperatura. Válvula de entrada Sensor de flujo Sensores de Nivel Calentador Lógica de Nmax Monitoreo y Nmin Control STemp Válvula de Salida del Temperatura Salida Líquido Ve Cltr Vs El tanque contiene un liquido para usar en la preparación de un medicamento. La temperatura del liquido es muy importante porque la viscosidad del liquido deber ser la indicada por el farmacéutico a cargo. La lógica de control debe prender o apagar el calentador de acuerdo a la temperatura que mide el sensor de temperatura (Esta parte del controlador no se implementara todavía). Los sensores de nivel de liquiedo producen un ‘ 1’ cuando el nivel esta por encima del nivel minimo o cuando esta al nivel máximo. El controlador a disenar debe abrir la valvula de entrada SOLO cuando el nivel del liquido alcanza el nivel minimo (para recomenzar la tarea de calentamiento del liquido). Una vez que la valvula

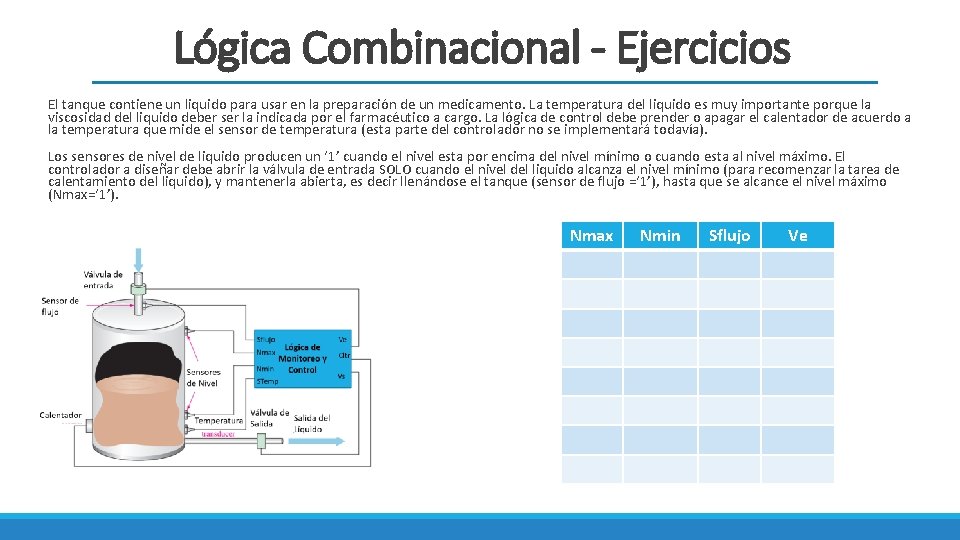

Lógica Combinacional - Ejercicios El tanque contiene un liquido para usar en la preparación de un medicamento. La temperatura del liquido es muy importante porque la viscosidad del liquido deber ser la indicada por el farmacéutico a cargo. La lógica de control debe prender o apagar el calentador de acuerdo a la temperatura que mide el sensor de temperatura (esta parte del controlador no se implementará todavía). Los sensores de nivel de liquido producen un ‘ 1’ cuando el nivel esta por encima del nivel mínimo o cuando esta al nivel máximo. El controlador a diseñar debe abrir la válvula de entrada SOLO cuando el nivel del liquido alcanza el nivel mínimo (para recomenzar la tarea de calentamiento del liquido), y mantenerla abierta, es decir llenándose el tanque (sensor de flujo =‘ 1’), hasta que se alcance el nivel máximo (Nmax=‘ 1’). Nmax Nmin Sflujo Ve

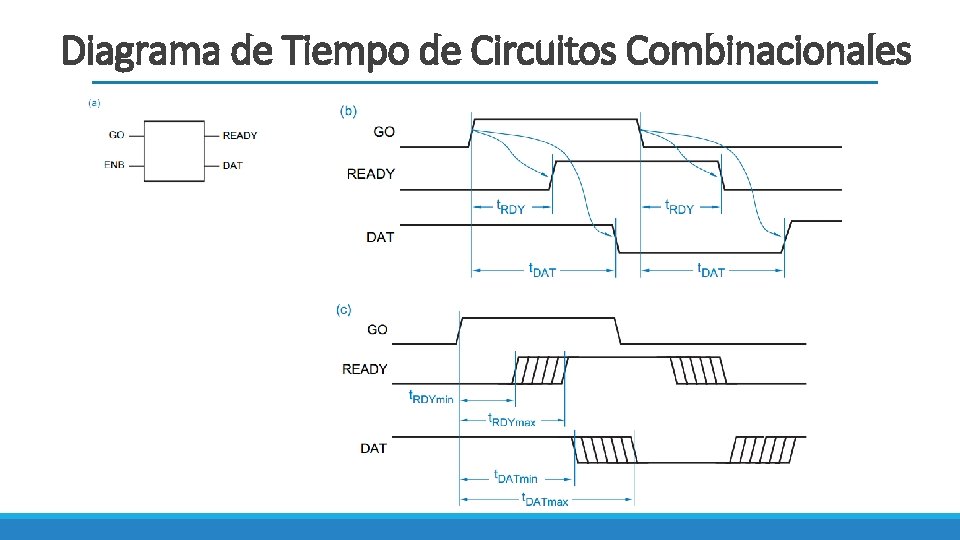

Diagrama de Tiempo de Circuitos Combinacionales Un diagrama de tiempo detalla gráficamente el comportamiento de las señales de un circuito digital en función del tiempo Diagramas de tiempo constituyen una importante parte de la documentación de cualquier sistema digital Son usados para: • Detallar la relación temporal entra las señales de un sistema • Para definir los requerimientos de las señales de entrada y de las señales de salida del sistema a diseñar

Diagrama de Tiempo de Circuitos Combinacionales

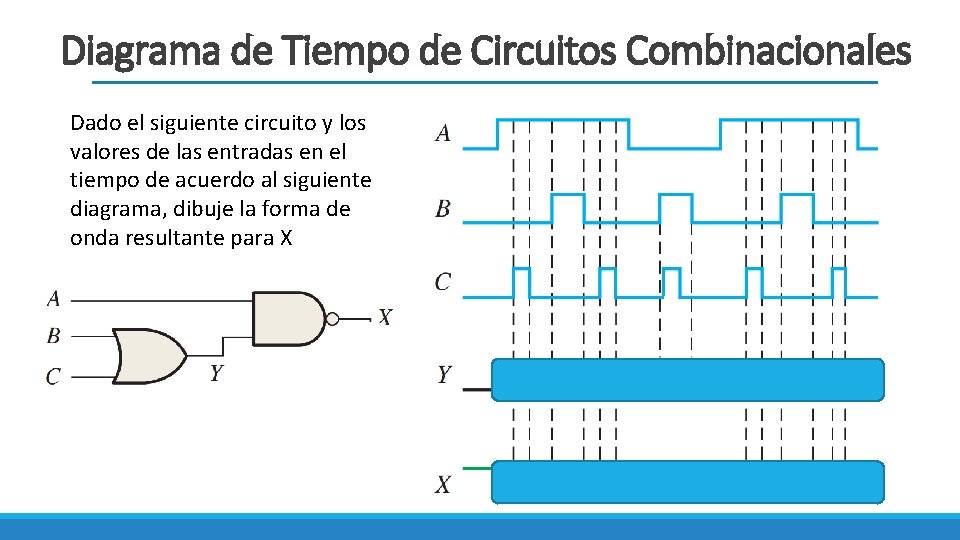

Diagrama de Tiempo de Circuitos Combinacionales Dado el siguiente circuito y los valores de las entradas en el tiempo de acuerdo al siguiente diagrama, dibuje la forma de onda resultante para X

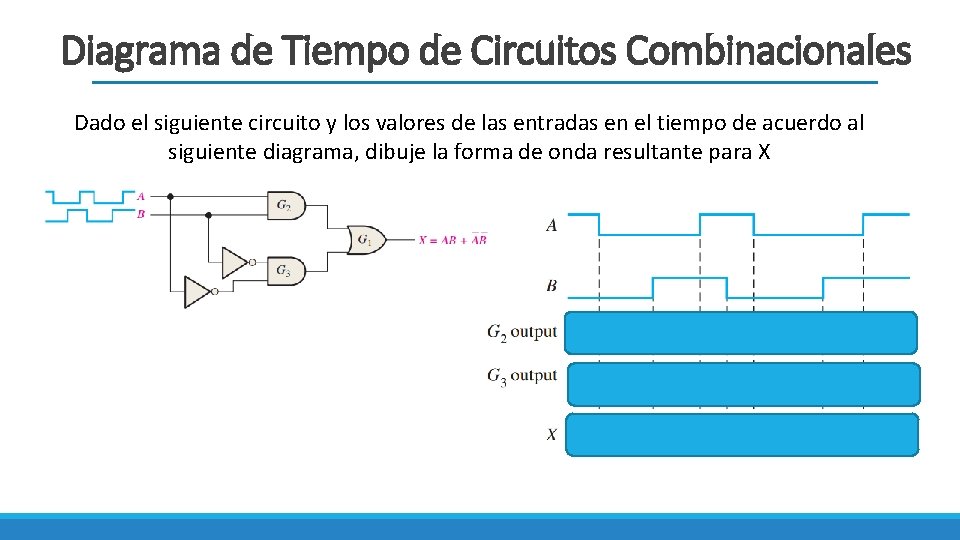

Diagrama de Tiempo de Circuitos Combinacionales Dado el siguiente circuito y los valores de las entradas en el tiempo de acuerdo al siguiente diagrama, dibuje la forma de onda resultante para X

Diagrama de Tiempo de Circuitos Combinacionales Ejercicio Un pulso de 50 us es aplicado a la entrada una OR-Exclusiva. Un segundo pulso de 10 us es aplicado a la otra entrada. Este pulso comienza 15 us después del comienzo del primer pulso. Dibujar el diagrama de tiempo de la salida en relación a los cambios de las entradas.

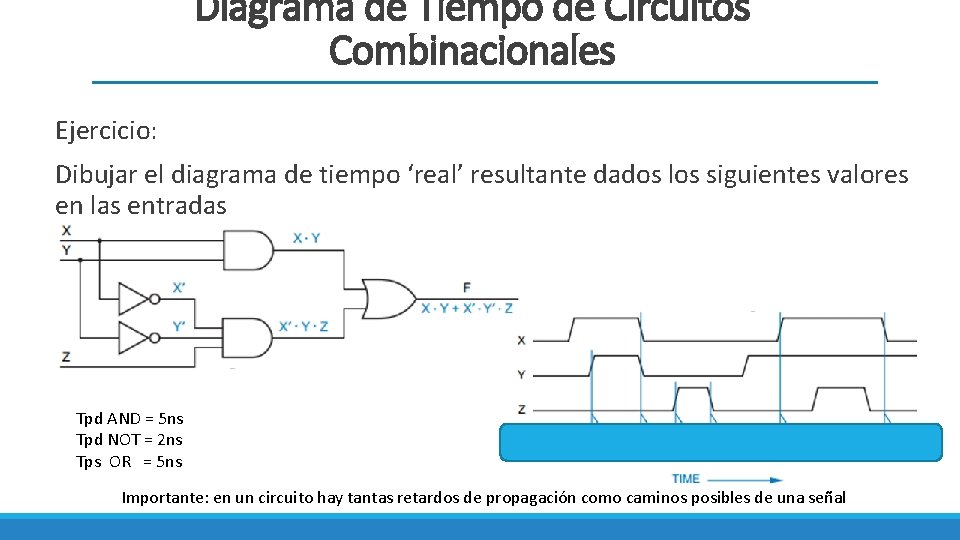

Diagrama de Tiempo de Circuitos Combinacionales Ejercicio: Dibujar el diagrama de tiempo ‘real’ resultante dados los siguientes valores en las entradas Tpd AND = 5 ns Tpd NOT = 2 ns Tps OR = 5 ns Importante: en un circuito hay tantas retardos de propagación como caminos posibles de una señal

- Slides: 43