Memorias Memorias en General o Un simple flipflop

- Slides: 52

Memorias

Memorias en General o Un simple flip-flop es un elemento básico de memoria o En general el termino memoria se usa para un arreglo bidimensional, en el cual se puede acceder a una fila de bits en un cierto tiempo o Memorias son CI usados con otros CI (microprocesadores, MEF, contadores, etc) o En un sistema basado en microprocesador una memoria se usa para almacenar las instrucciones a ser ejecutadas por el microprocesador, y también para almacenar los datos a procesar o procesados o Otros usos incluye almacenamiento de audio en un DVD player por ejemplo, voces digitales, mensajes de LEDs, etc, ICTP FPGA-VHDL 2

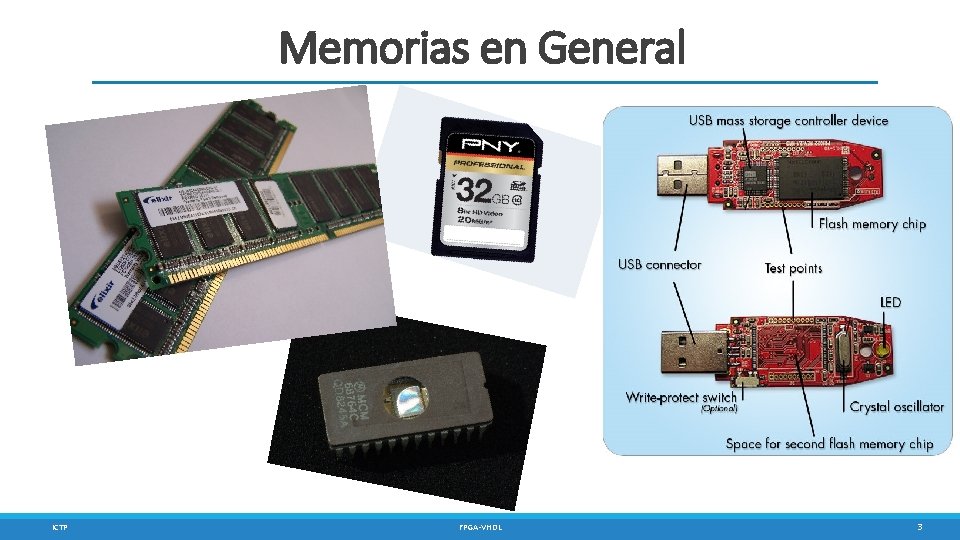

Memorias en General ICTP FPGA-VHDL 3

Memoria de Solo Lectura (ROM) Las memorias de solo lectura son conocidas por la siglas ROM, que en inglés significa Read Only Memory Las memorias ROM almacenan cierta información, que se graba originalmente por algún medio, y esa información, al ser la memoria de solo lectura, no se puede modificar ICTP FPGA-VHDL 4

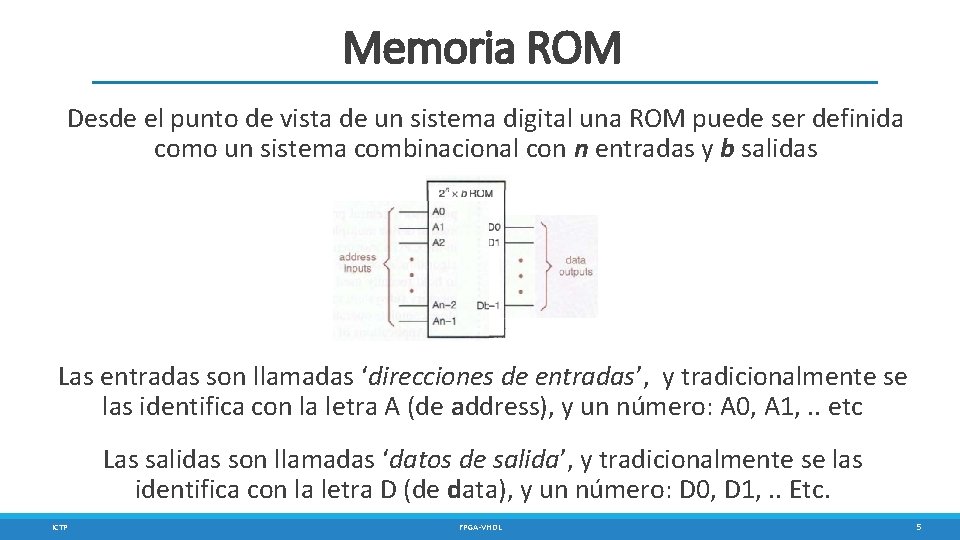

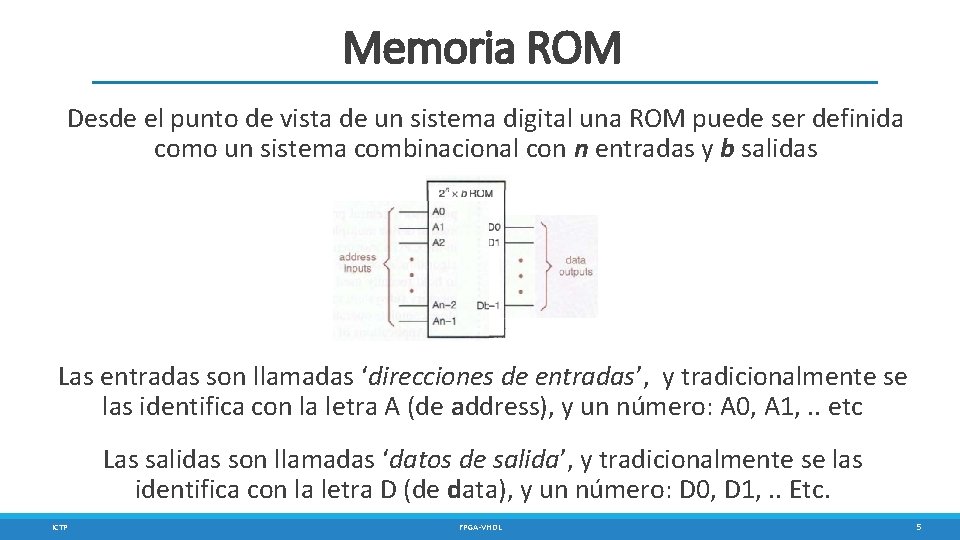

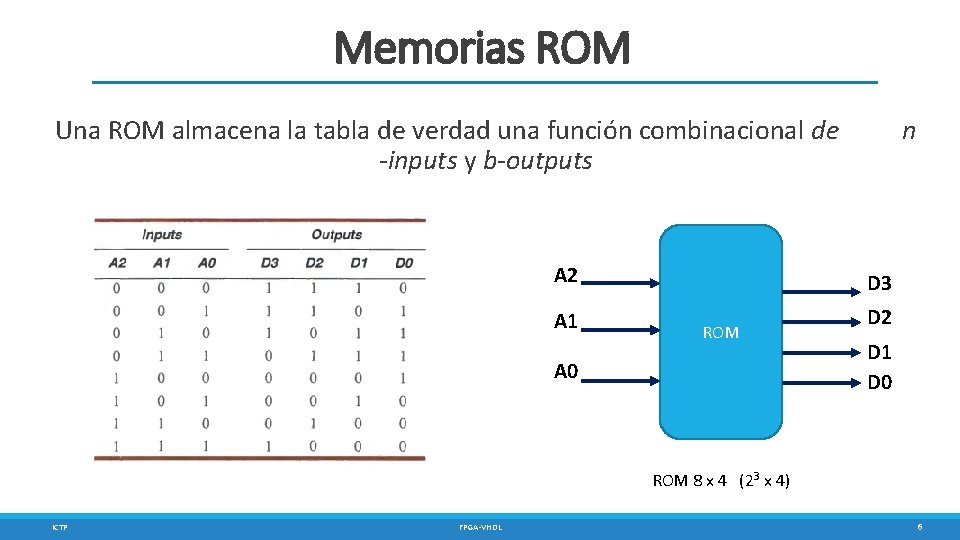

Memoria ROM Desde el punto de vista de un sistema digital una ROM puede ser definida como un sistema combinacional con n entradas y b salidas Las entradas son llamadas ‘direcciones de entradas’, y tradicionalmente se las identifica con la letra A (de address), y un número: A 0, A 1, . . etc Las salidas son llamadas ‘datos de salida’, y tradicionalmente se las identifica con la letra D (de data), y un número: D 0, D 1, . . Etc. ICTP FPGA-VHDL 5

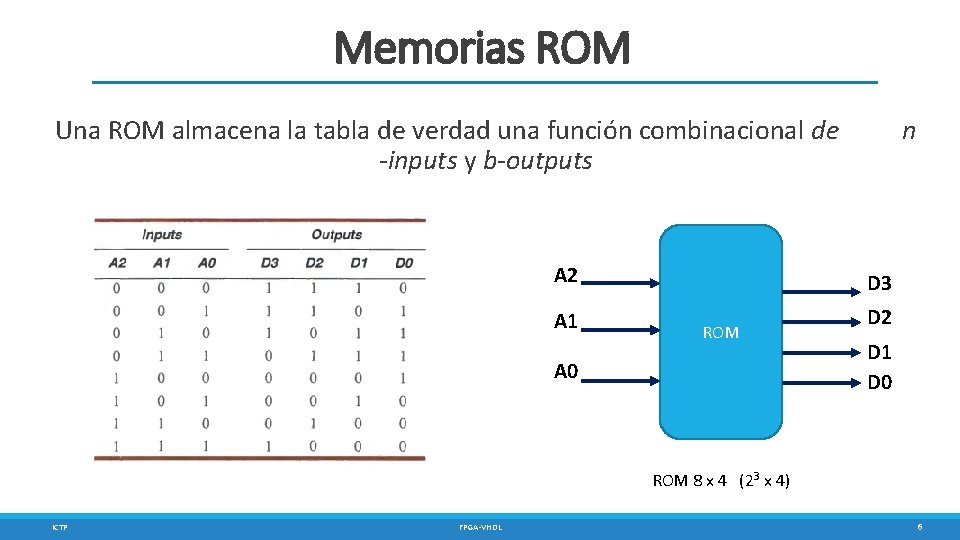

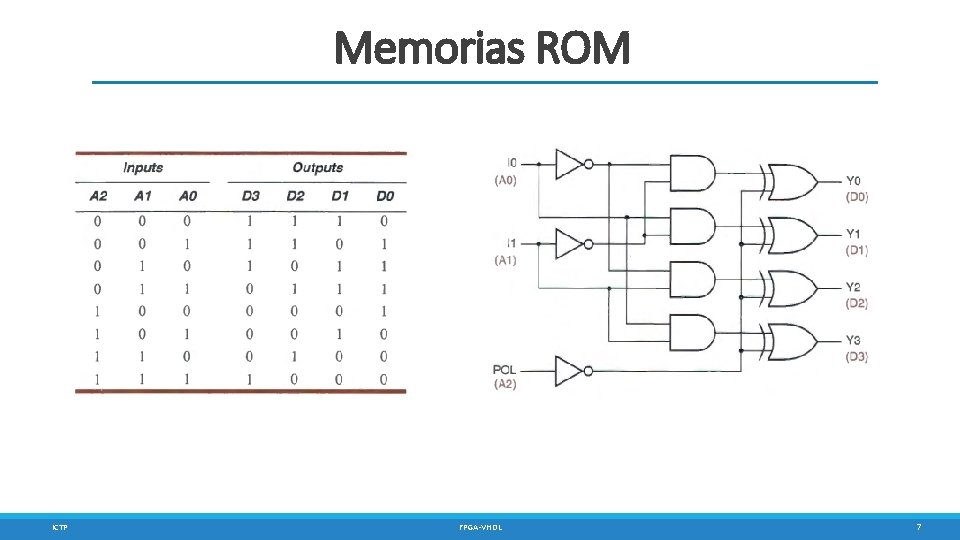

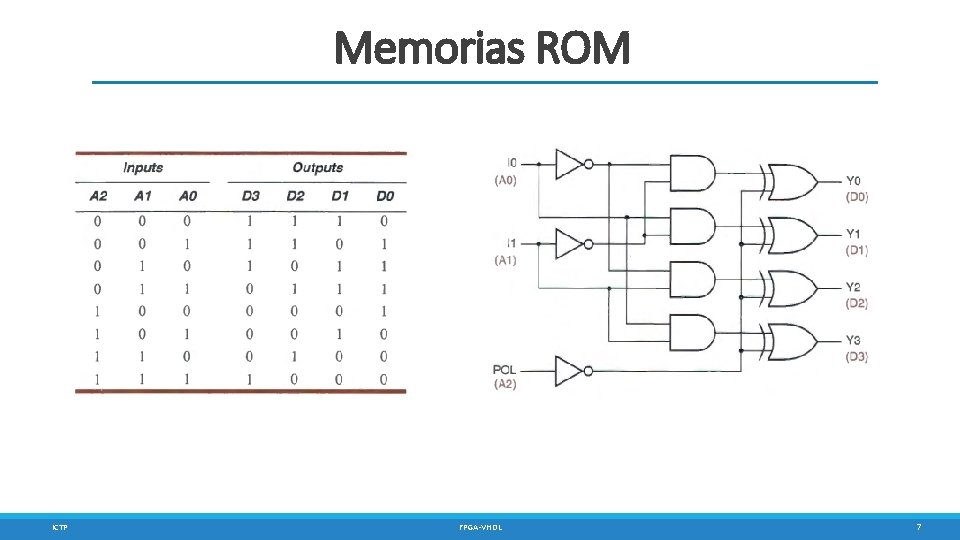

Memorias ROM Una ROM almacena la tabla de verdad una función combinacional de -inputs y b-outputs A 2 A 1 n D 3 ROM A 0 D 2 D 1 D 0 ROM 8 x 4 (23 x 4) ICTP FPGA-VHDL 6

Memorias ROM ICTP FPGA-VHDL 7

Memoria ROM Las memorias ROM tienen una particularidad que las hacen muy útiles: son memorias NO VOLÁTILES ICTP FPGA-VHDL 8

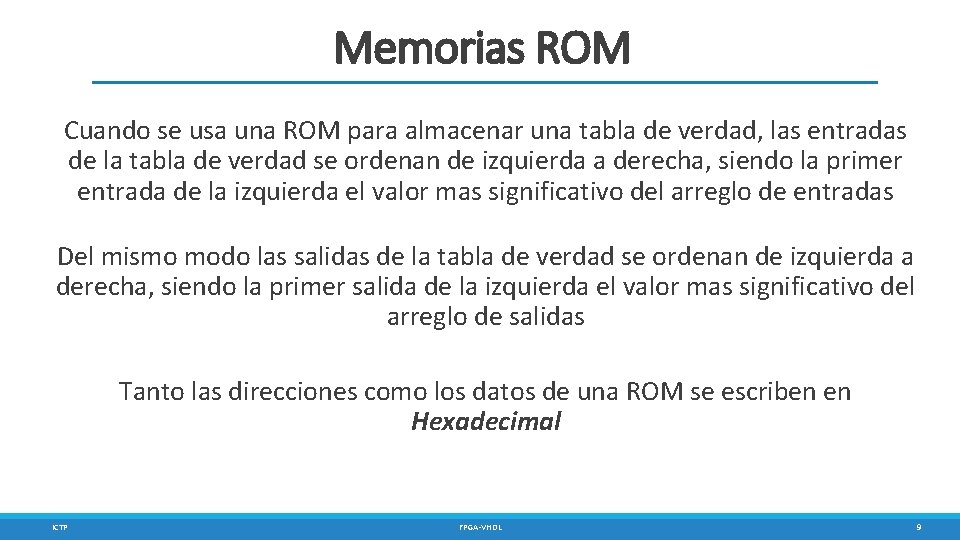

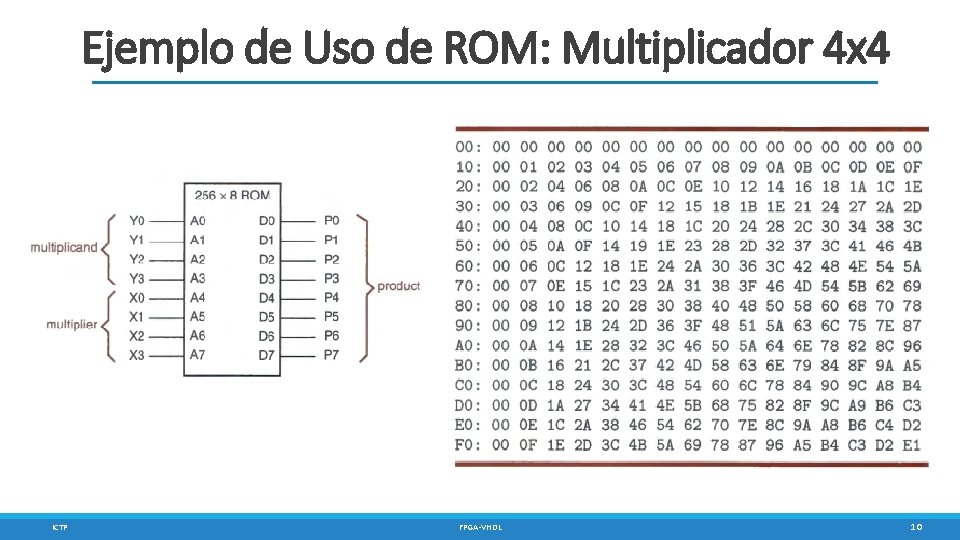

Memorias ROM Cuando se usa una ROM para almacenar una tabla de verdad, las entradas de la tabla de verdad se ordenan de izquierda a derecha, siendo la primer entrada de la izquierda el valor mas significativo del arreglo de entradas Del mismo modo las salidas de la tabla de verdad se ordenan de izquierda a derecha, siendo la primer salida de la izquierda el valor mas significativo del arreglo de salidas Tanto las direcciones como los datos de una ROM se escriben en Hexadecimal ICTP FPGA-VHDL 9

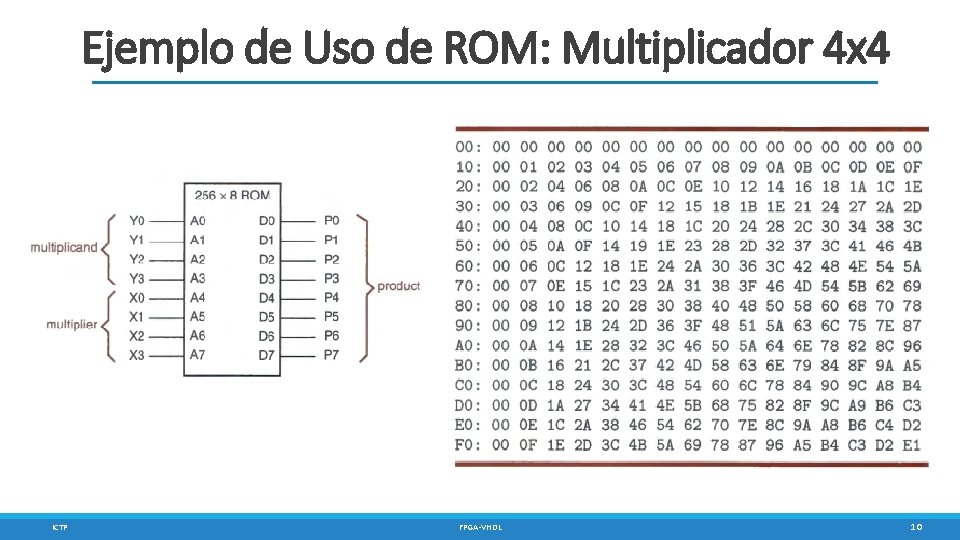

Ejemplo de Uso de ROM: Multiplicador 4 x 4 ICTP FPGA-VHDL 10

Tecnología usada en las ROM Programada por Máscara La memoria ROM es fabricada por el fabricante de CI usando un patrón de conexiones y no conexiones, llamado mascara, generado por el diseñador (cliente) El fabricante de CI usa esta información para crear una ROM dedicada, siguiendo el patrón provisto por el diseñador Debido a que la ROM fabricada, es una memoria de uso especifico, basada en el patrón de conexiones provisto por el diseñador, el costo de la mascara es muy alto. Por lo que únicamente se justifica usar esta tecnología para muy altos volúmenes de producción ICTP FPGA-VHDL 11

Tecnología usada en las ROMs (2) ROM Programable - PROM En esta tecnología se usa un programador de ROM para ‘programar’ la ROM La memoria tipo PROM se fabrica con todos sus transistores o diodos conectados. Así, todos los bits de la memoria tienen un valor lógico definido, típicamente ‘ 1’ El programador PROM es utilizado para cambiar el valor de fabrica por el valor opuesto. En tecnología bipolar (TTL) este proceso se realizaba al vaporizar un pequeño fusible de unión existente en cada cruce de la línea de palabra y la columna de bit Con este tipo de tecnología, una vez programada la ROM no se puede modificar, ya que el fusible quedo abierto o cerrado. Este tipo de memorias se les llama OTPROM (One Time Programmable ROM) ICTP FPGA-VHDL 12

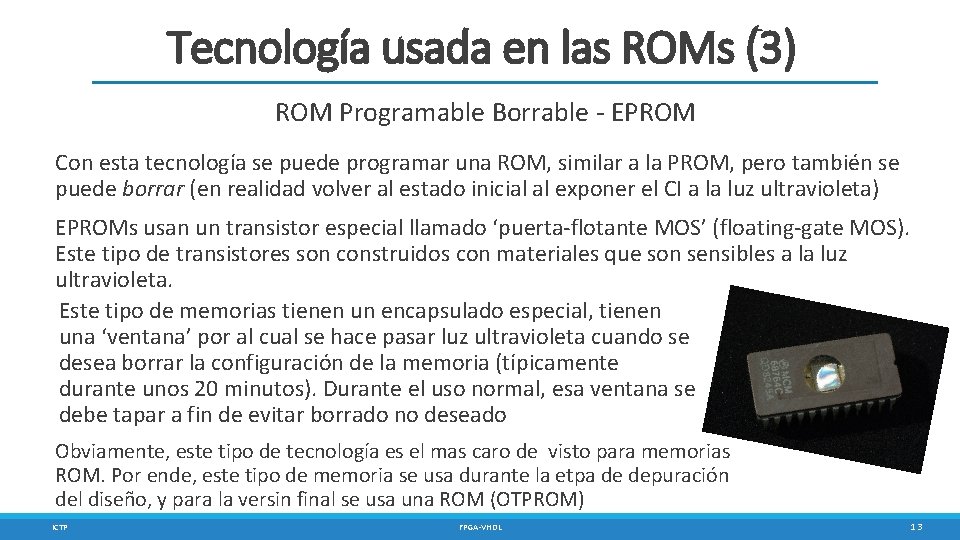

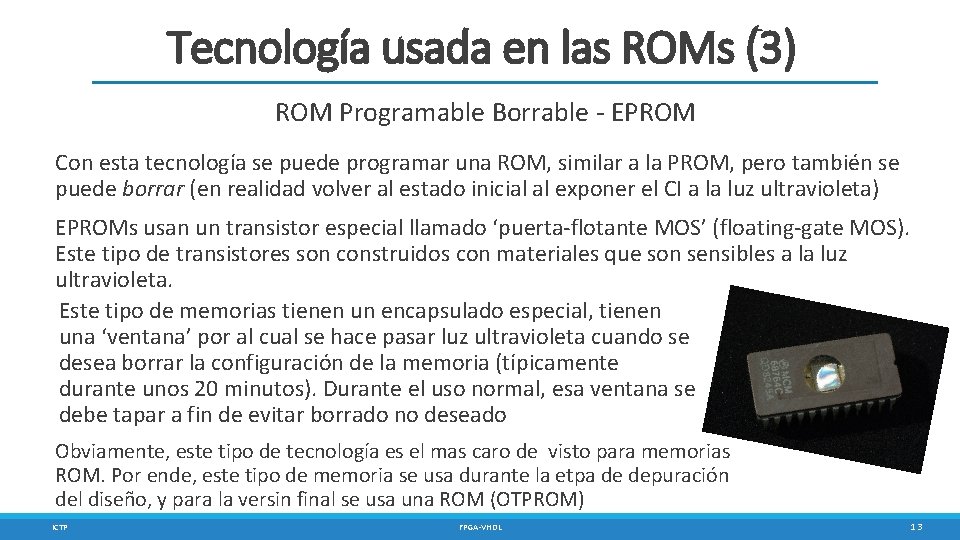

Tecnología usada en las ROMs (3) ROM Programable Borrable - EPROM Con esta tecnología se puede programar una ROM, similar a la PROM, pero también se puede borrar (en realidad volver al estado inicial al exponer el CI a la luz ultravioleta) EPROMs usan un transistor especial llamado ‘puerta-flotante MOS’ (floating-gate MOS). Este tipo de transistores son construidos con materiales que son sensibles a la luz ultravioleta. Este tipo de memorias tienen un encapsulado especial, tienen una ‘ventana’ por al cual se hace pasar luz ultravioleta cuando se desea borrar la configuración de la memoria (típicamente durante unos 20 minutos). Durante el uso normal, esa ventana se debe tapar a fin de evitar borrado no deseado Obviamente, este tipo de tecnología es el mas caro de visto para memorias ROM. Por ende, este tipo de memoria se usa durante la etpa de depuración del diseño, y para la versin final se usa una ROM (OTPROM) ICTP FPGA-VHDL 13

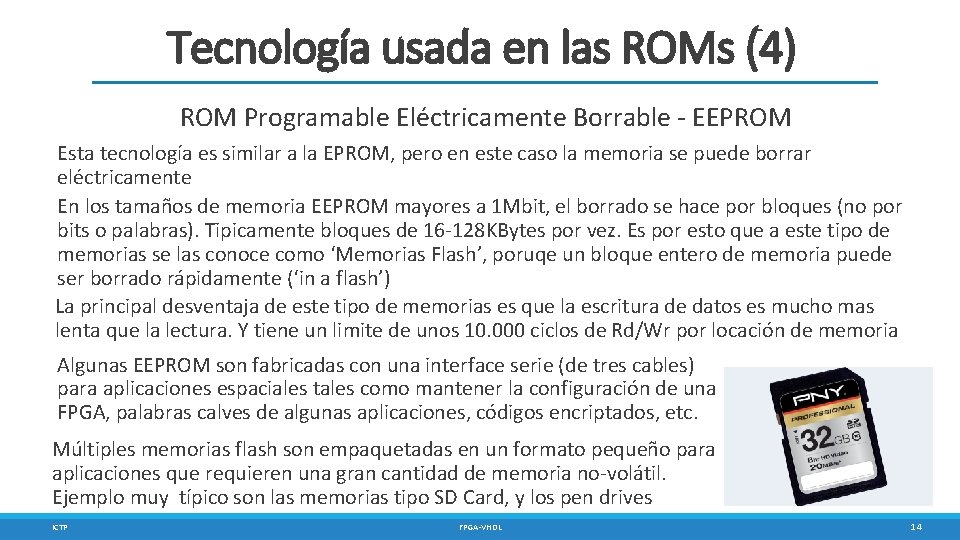

Tecnología usada en las ROMs (4) ROM Programable Eléctricamente Borrable - EEPROM Esta tecnología es similar a la EPROM, pero en este caso la memoria se puede borrar eléctricamente En los tamaños de memoria EEPROM mayores a 1 Mbit, el borrado se hace por bloques (no por bits o palabras). Tipicamente bloques de 16 -128 KBytes por vez. Es por esto que a este tipo de memorias se las conoce como ‘Memorias Flash’, poruqe un bloque entero de memoria puede ser borrado rápidamente (‘in a flash’) La principal desventaja de este tipo de memorias es que la escritura de datos es mucho mas lenta que la lectura. Y tiene un limite de unos 10. 000 ciclos de Rd/Wr por locación de memoria Algunas EEPROM son fabricadas con una interface serie (de tres cables) para aplicaciones espaciales tales como mantener la configuración de una FPGA, palabras calves de algunas aplicaciones, códigos encriptados, etc. Múltiples memorias flash son empaquetadas en un formato pequeño para aplicaciones que requieren una gran cantidad de memoria no-volátil. Ejemplo muy típico son las memorias tipo SD Card, y los pen drives ICTP FPGA-VHDL 14

ROM – Entradas de Control Las memorias ROM normalmente se usan en sistemas donde existe un bus al cual están conectados otros CI, por lo tanto la mayoría de las ROMs tienen disponibles entrada de control para salidas tres-estados Esta entrada se comúnmente se denomina habilitación de salida, output-enable, y se simboliza con las letras OE debe ser asertiva para habilitar las salidas Otra entrada de control que se usa en las ROM es una entrada que habilita la ROM en si. Esta señal de control se denomina selector de integrado, chip-select, y se simboliza con las letras CS Tanto CS como OE deben ser asertivas para habilitar las salidas ICTP FPGA-VHDL 15

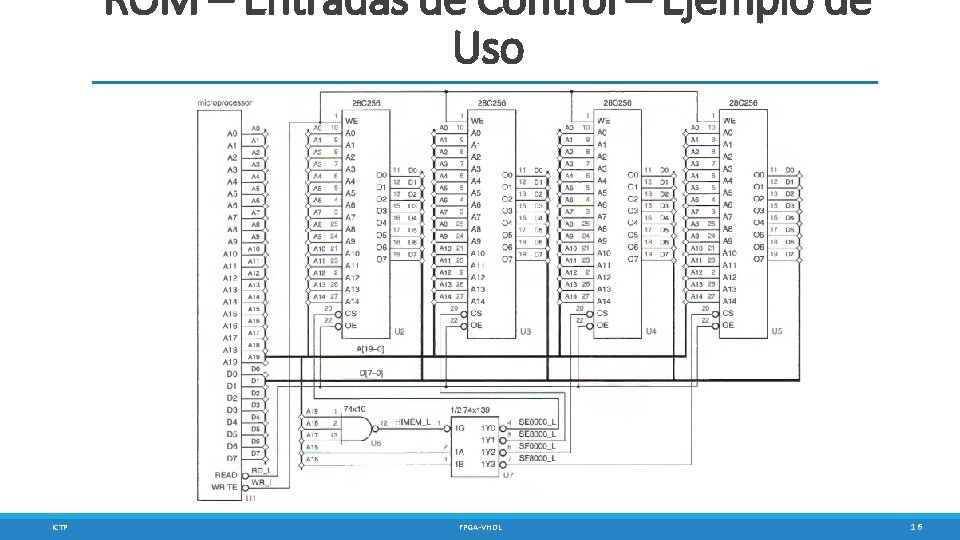

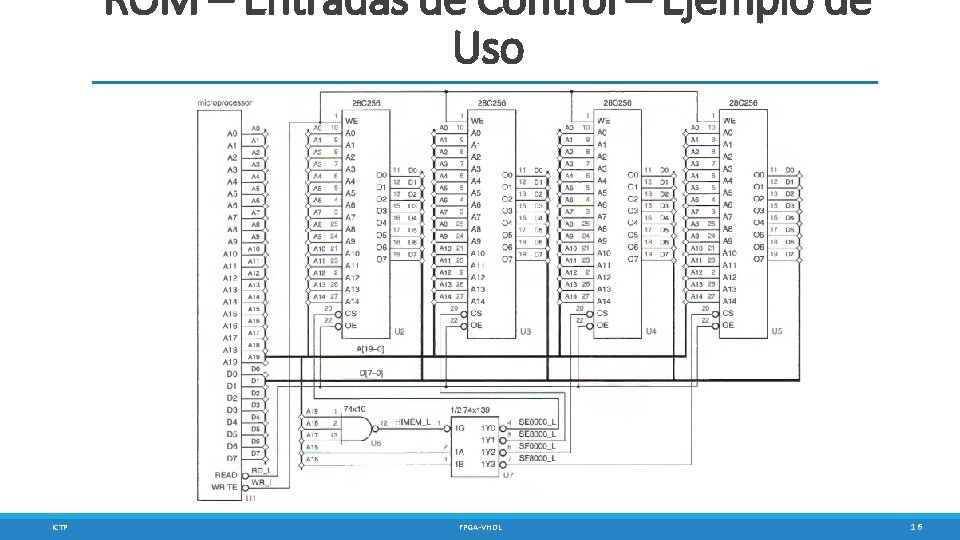

ROM – Entradas de Control – Ejemplo de Uso ICTP FPGA-VHDL 16

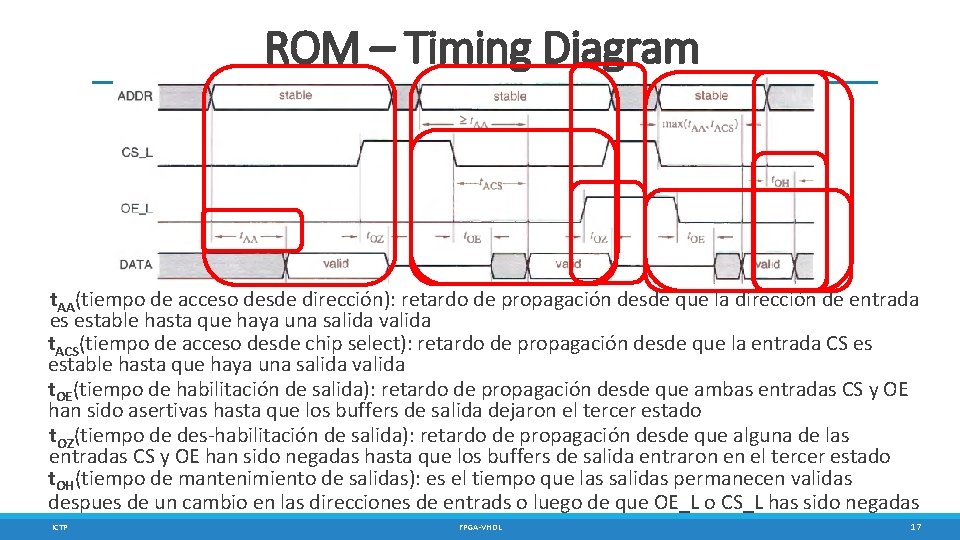

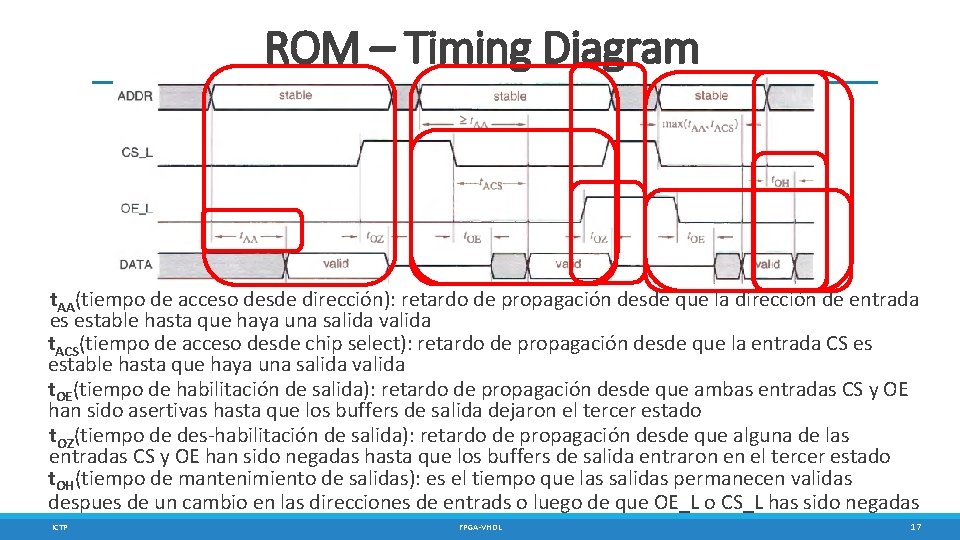

ROM – Timing Diagram t. AA(tiempo de acceso desde dirección): retardo de propagación desde que la dirección de entrada es estable hasta que haya una salida valida t. ACS(tiempo de acceso desde chip select): retardo de propagación desde que la entrada CS es estable hasta que haya una salida valida t. OE(tiempo de habilitación de salida): retardo de propagación desde que ambas entradas CS y OE han sido asertivas hasta que los buffers de salida dejaron el tercer estado t. OZ(tiempo de des-habilitación de salida): retardo de propagación desde que alguna de las entradas CS y OE han sido negadas hasta que los buffers de salida entraron en el tercer estado t. OH(tiempo de mantenimiento de salidas): es el tiempo que las salidas permanecen validas despues de un cambio en las direcciones de entrads o luego de que OE_L o CS_L has sido negadas ICTP FPGA-VHDL 17

ROM – Ventajas/Desventajas de Uso Pros ◦ Para funciones lógicas de complejidad moderada, un circuito basado en ROM es normalmente mas rápido que uno usando compuertas lógicas, o FPGAs ◦ La función lógica almacenada en la ROM es fácilmente modificable, sin tener que cambiar el hardware (en la mayoia de los casos, no siempre… ) ◦ El precio de las ROMs continua bajando, al mismo tiempo que el tamaño de las mismas se va incrementando ◦ Máquinas de estados basadas en ROM (microprogramación) son muy eficientes, alto rendimiento y bajo consumo Cons ◦ Para funciones lógicas pequeñas, un circuito basado en ROM puede ser mas caro, consumir mas potencia o ser mas lento que uno construido con lógica discreta o FPGA ICTP FPGA-VHDL 18

Memorias de Lectura/Escritura Una memoria de lectura y escritura permite escribir y leer los datos en cualquier momento Este tipo de memoria se las conoce como memoria de acceso aleatorio (Random Access Memory, RAM), lo que significa que toma el mismo tiempo la lectura o escritura de un bit de la memoria, independientemente de la locación del bit en la memoria Basado en el funcionamiento de una ROM, también puede decirse que una ROM es una RAM, pero el nombre RAM se usa generalmente para las memorias de escritura/lectura ICTP FPGA-VHDL 19

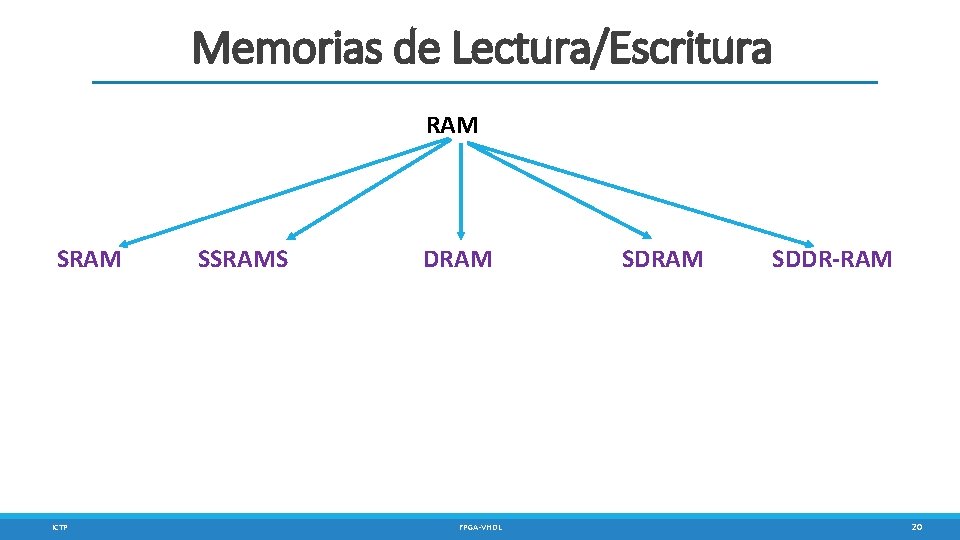

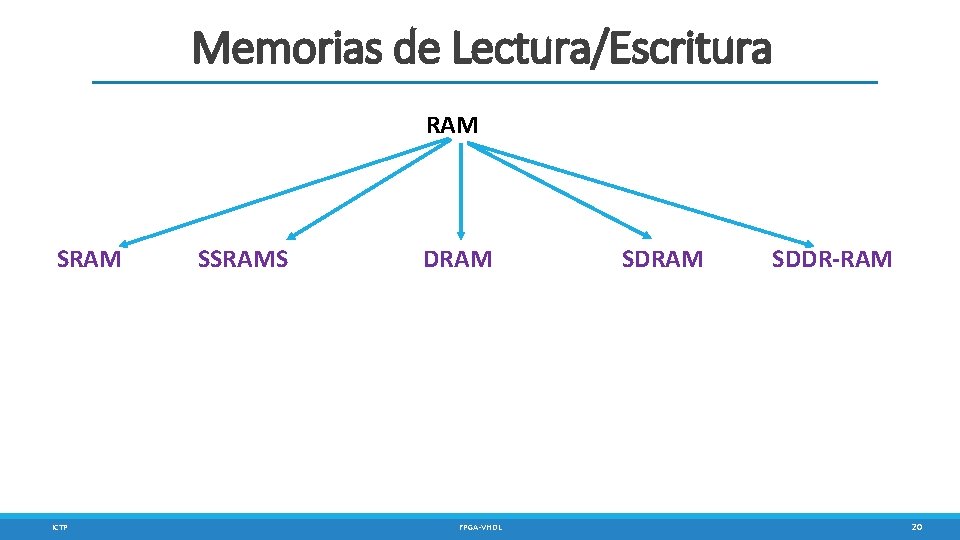

Memorias de Lectura/Escritura RAM SRAM ICTP SSRAMS DRAM FPGA-VHDL SDRAM SDDR-RAM 20

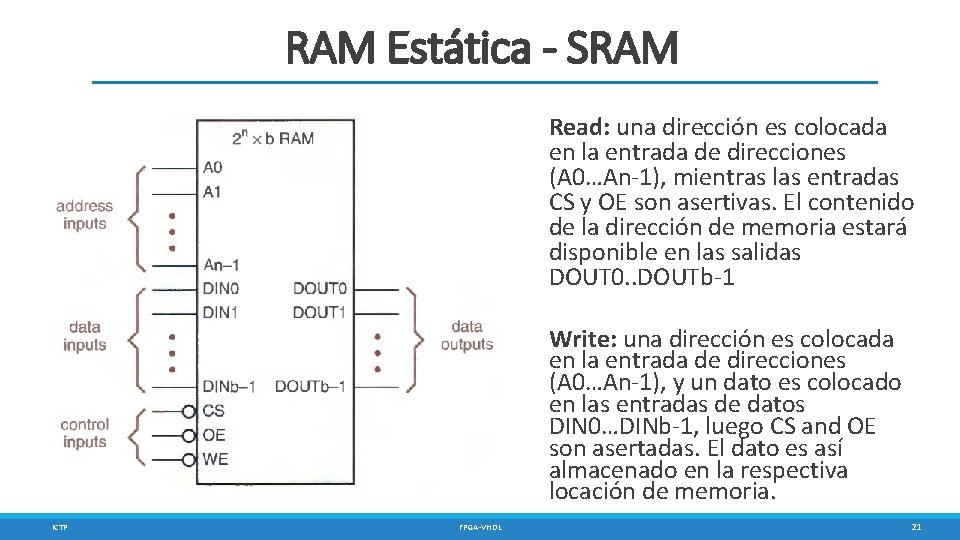

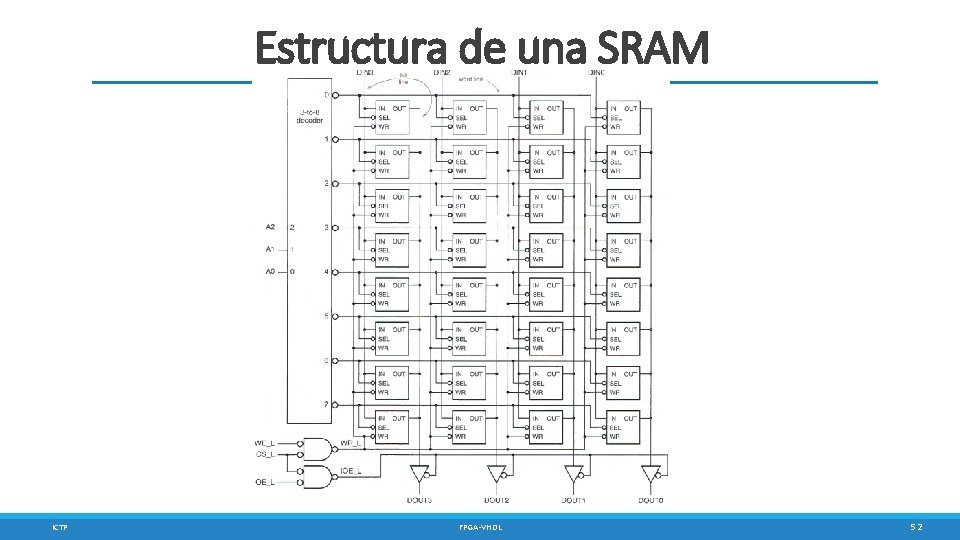

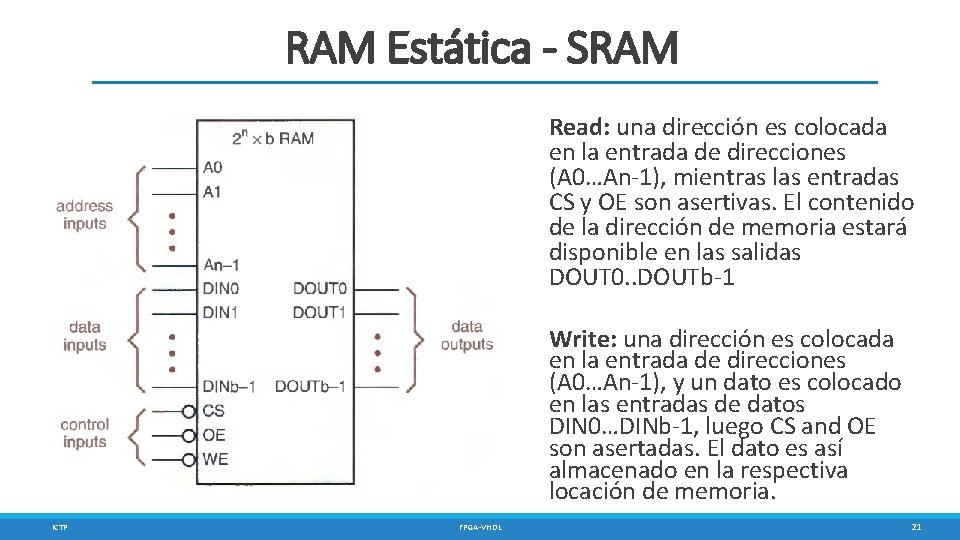

RAM Estática - SRAM Read: una dirección es colocada en la entrada de direcciones (A 0…An-1), mientras las entradas CS y OE son asertivas. El contenido de la dirección de memoria estará disponible en las salidas DOUT 0. . DOUTb-1 Write: una dirección es colocada en la entrada de direcciones (A 0…An-1), y un dato es colocado en las entradas de datos DIN 0…DINb-1, luego CS and OE son asertadas. El dato es así almacenado en la respectiva locación de memoria. ICTP FPGA-VHDL 21

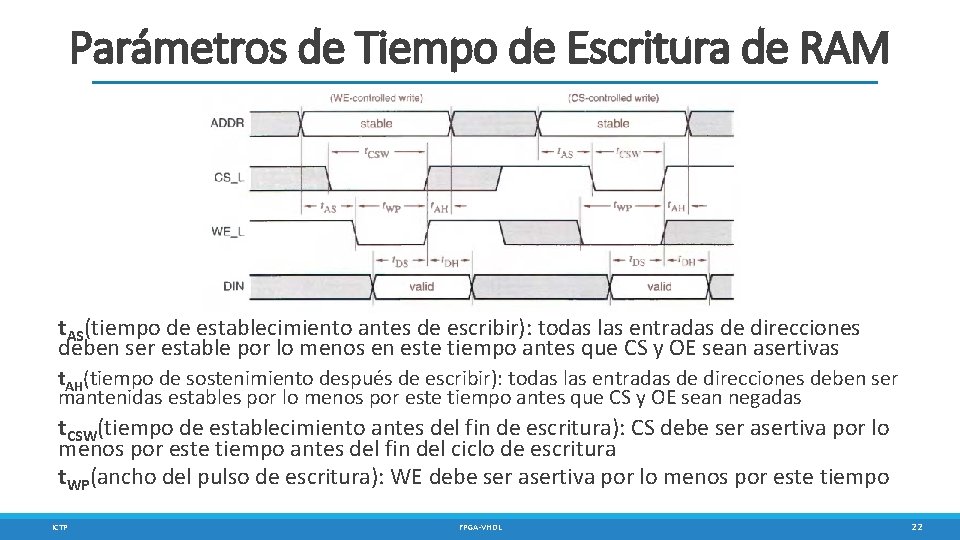

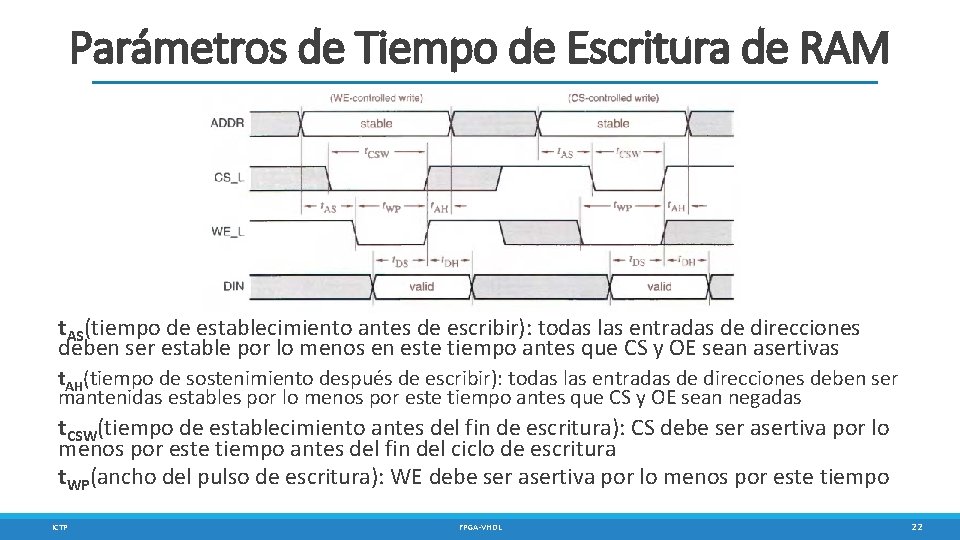

Parámetros de Tiempo de Escritura de RAM t. AS(tiempo de establecimiento antes de escribir): todas las entradas de direcciones deben ser estable por lo menos en este tiempo antes que CS y OE sean asertivas t. AH(tiempo de sostenimiento después de escribir): todas las entradas de direcciones deben ser mantenidas estables por lo menos por este tiempo antes que CS y OE sean negadas t. CSW(tiempo de establecimiento antes del fin de escritura): CS debe ser asertiva por lo menos por este tiempo antes del fin del ciclo de escritura t. WP(ancho del pulso de escritura): WE debe ser asertiva por lo menos por este tiempo ICTP FPGA-VHDL 22

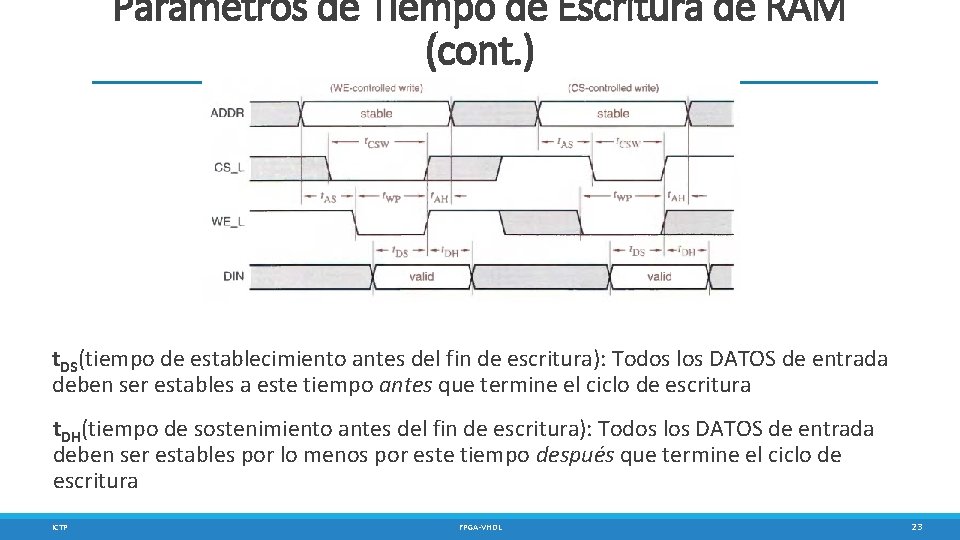

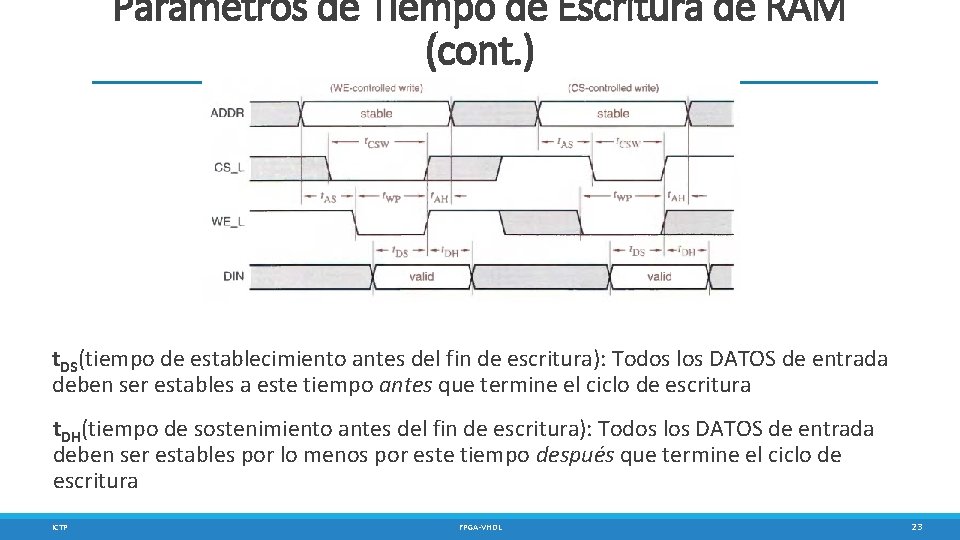

Parámetros de Tiempo de Escritura de RAM (cont. ) t. DS(tiempo de establecimiento antes del fin de escritura): Todos los DATOS de entrada deben ser estables a este tiempo antes que termine el ciclo de escritura t. DH(tiempo de sostenimiento antes del fin de escritura): Todos los DATOS de entrada deben ser estables por lo menos por este tiempo después que termine el ciclo de escritura ICTP FPGA-VHDL 23

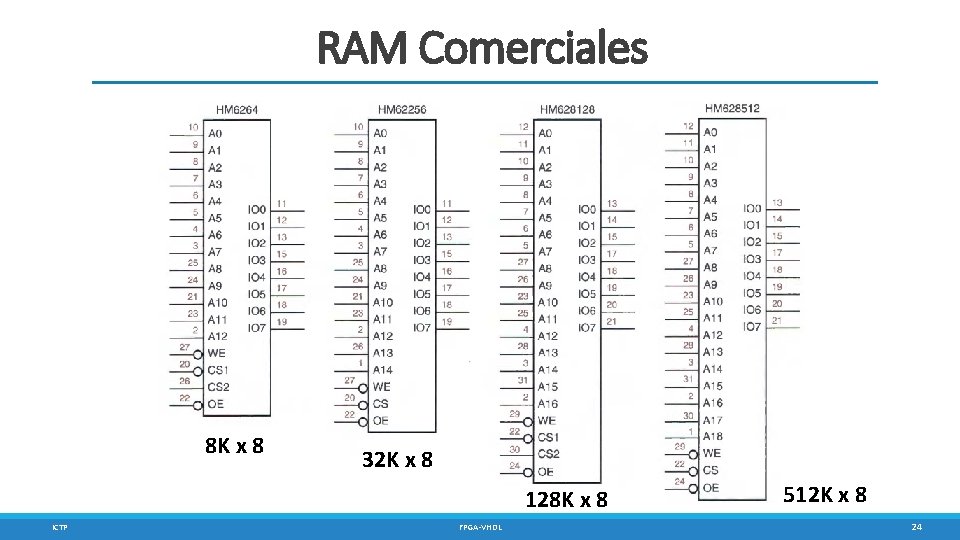

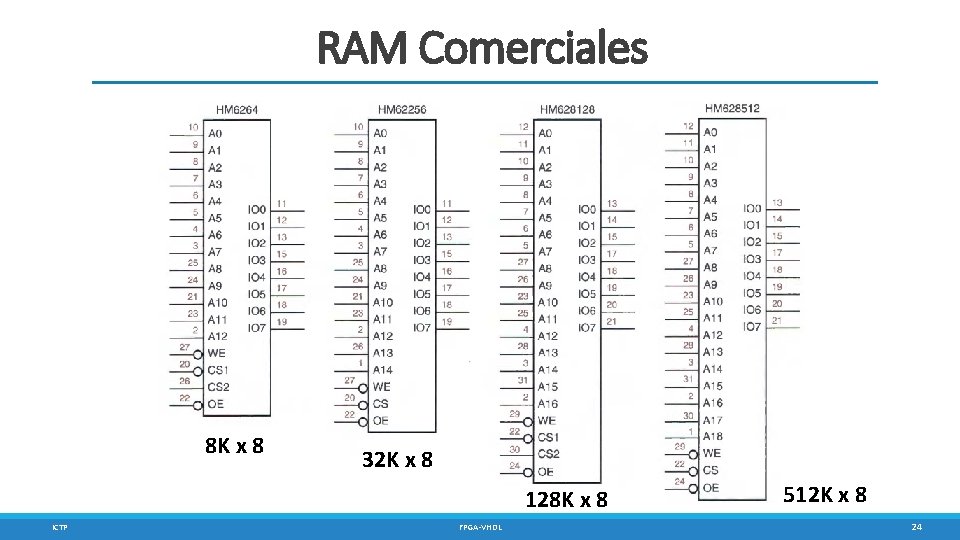

RAM Comerciales 8 K x 8 32 K x 8 128 K x 8 ICTP FPGA-VHDL 512 K x 8 24

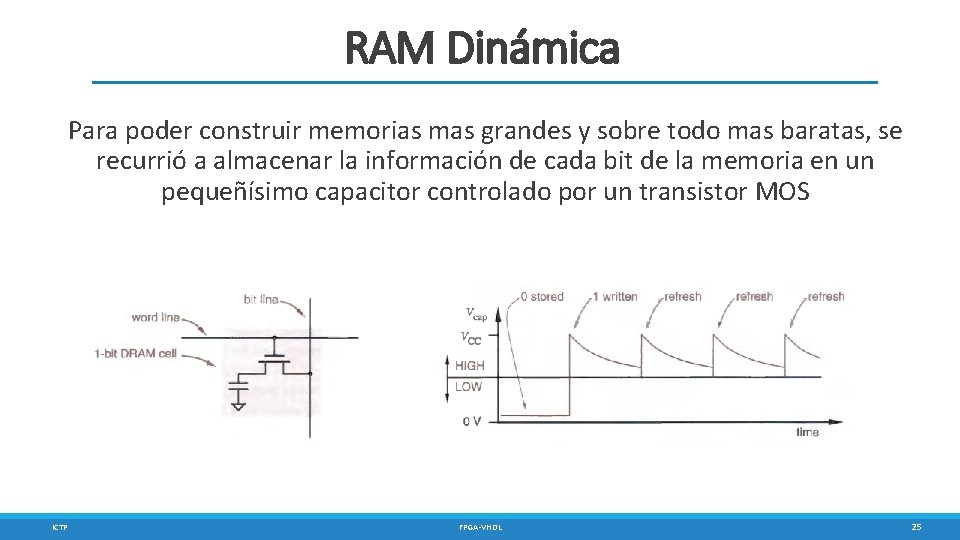

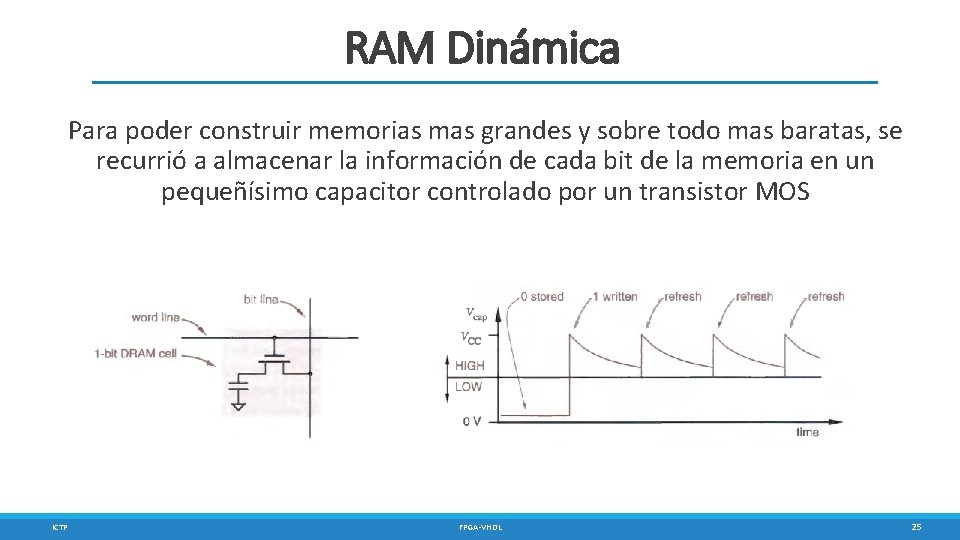

RAM Dinámica Para poder construir memorias mas grandes y sobre todo mas baratas, se recurrió a almacenar la información de cada bit de la memoria en un pequeñísimo capacitor controlado por un transistor MOS ICTP FPGA-VHDL 25

Ciclo de Refresco El capacitor de la DRAM tarda unos 100 milisegundos para descargarse a través del transistor MOS, mientras tanto el capacitor almacena un ‘ 1’ Las memorias DRAM tienen un ‘ciclo de refresco’, durante el cual, cada 64 milisegundos se ‘refresca’ la carga del capacitor La operación de refresco toma menos de 100 ns, por lo que las memorias DRAM están disponibles para operaciones de escritura o lectura el 99% del tiempo ICTP FPGA-VHDL 26

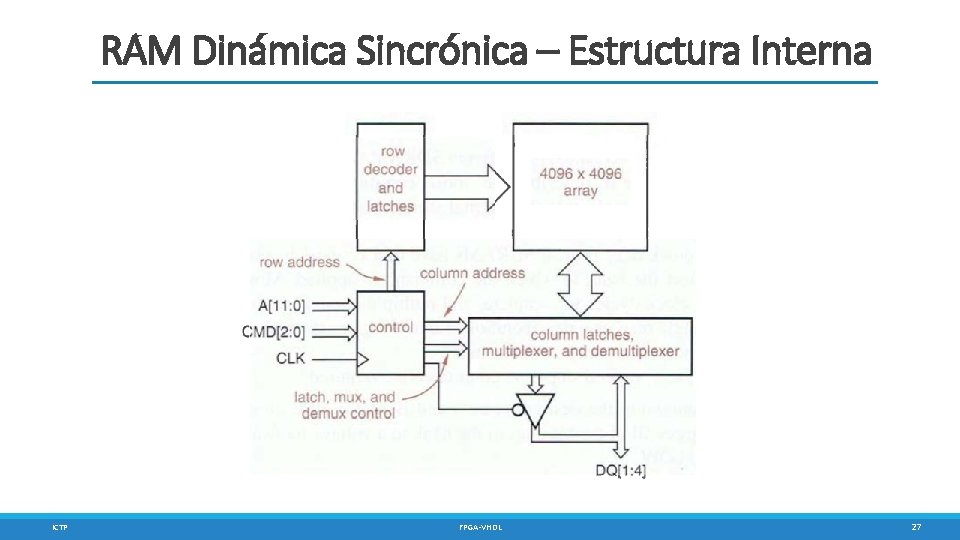

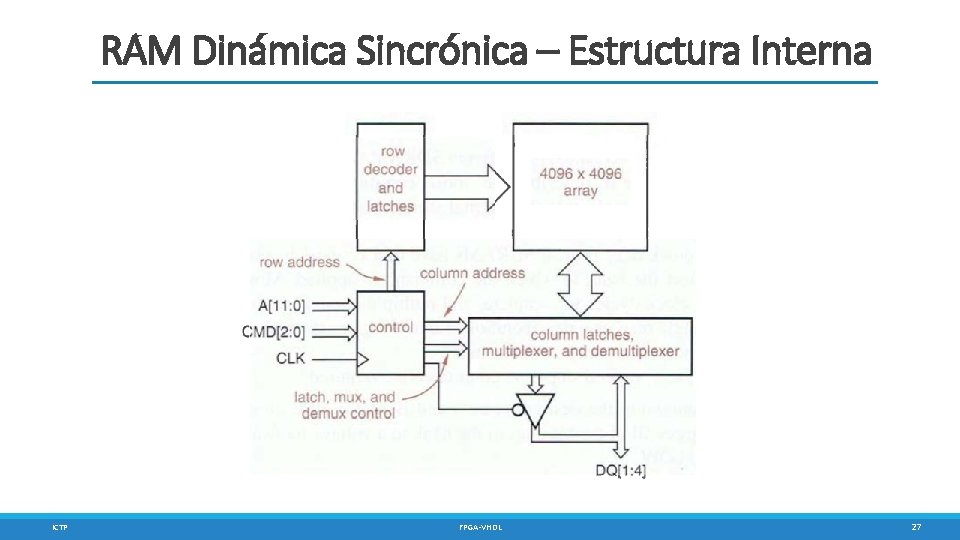

RAM Dinámica Sincrónica – Estructura Interna ICTP FPGA-VHDL 27

Memorias Tipo Dual Data Rate (DDR) ICTP FPGA-VHDL 28

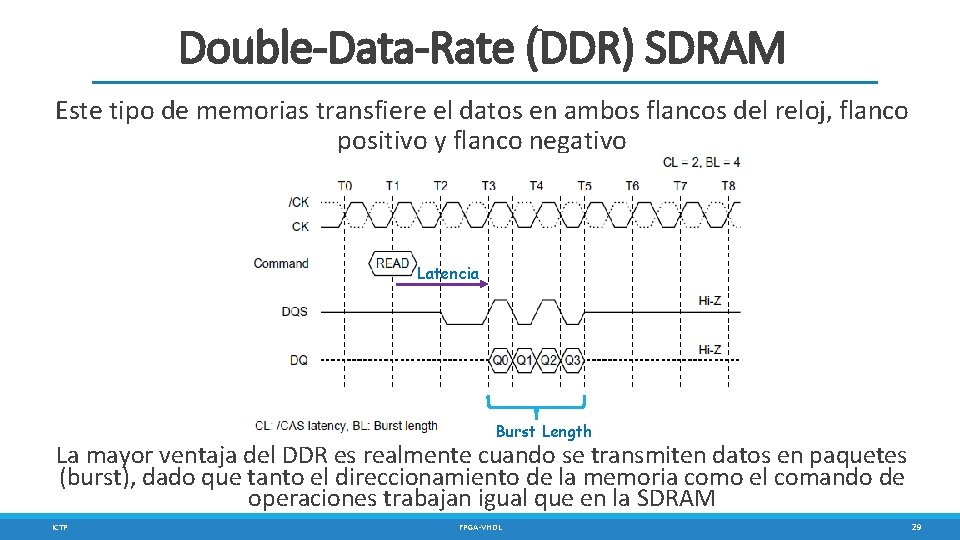

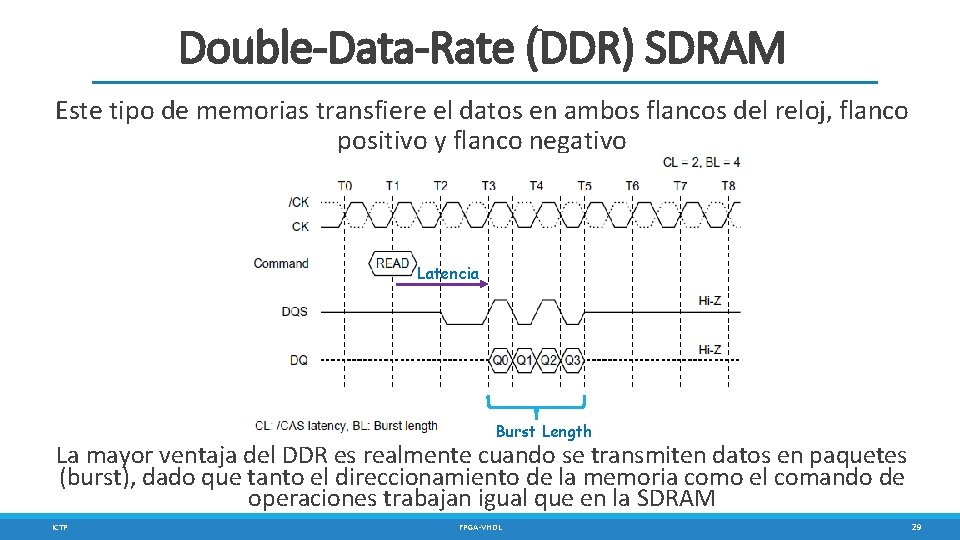

Double-Data-Rate (DDR) SDRAM Este tipo de memorias transfiere el datos en ambos flancos del reloj, flanco positivo y flanco negativo Latencia Burst Length La mayor ventaja del DDR es realmente cuando se transmiten datos en paquetes (burst), dado que tanto el direccionamiento de la memoria como el comando de operaciones trabajan igual que en la SDRAM ICTP FPGA-VHDL 29

Senal de Reloj de Alta Frecuencia La integridad de la señal de los relojes de alta frecuencia son afectados por factores eléctricos, electromagnéticos, mecánicos, etc. ◦ Afectan el ciclo de trabajo del reloj (50% ‘ 1’, 50% ‘ 0’) ◦ Para memorias tipo SDR (single data rate) no es problema. Para DDR gran problema ICTP FPGA-VHDL 30

Señal Real de Reloj ICTP FPGA-VHDL 31

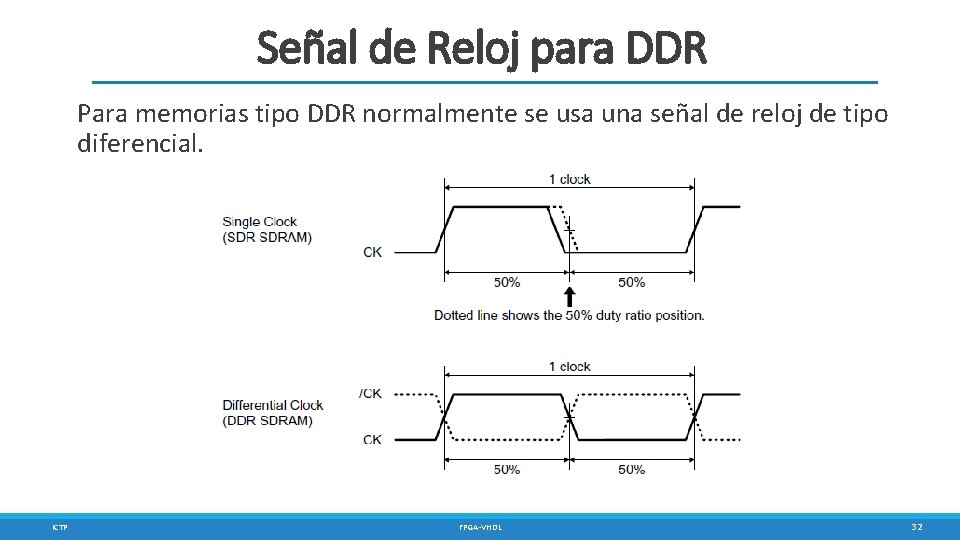

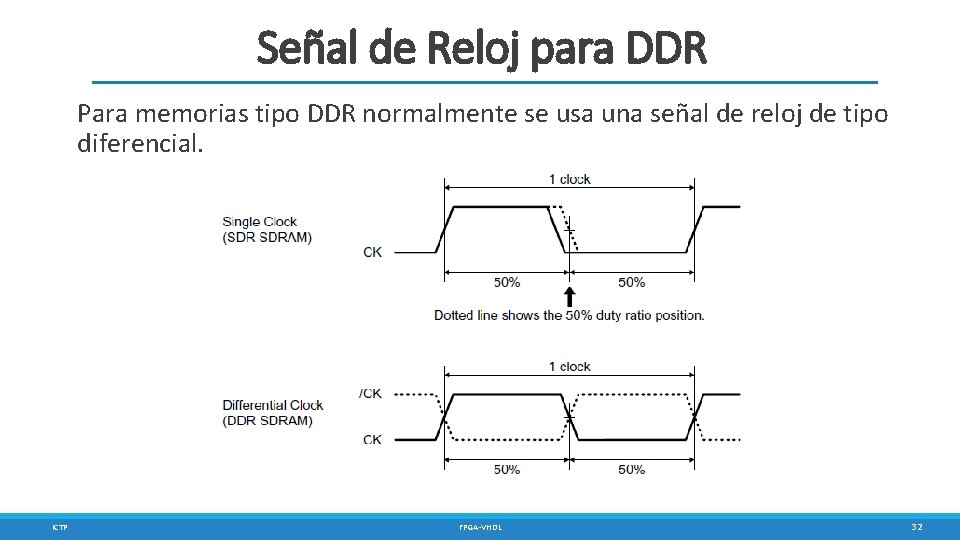

Señal de Reloj para DDR Para memorias tipo DDR normalmente se usa una señal de reloj de tipo diferencial. ICTP FPGA-VHDL 32

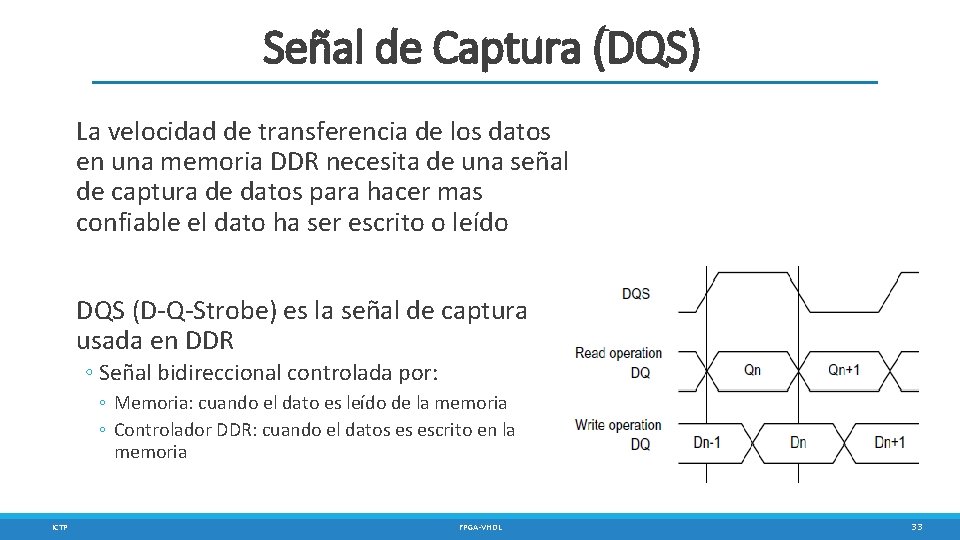

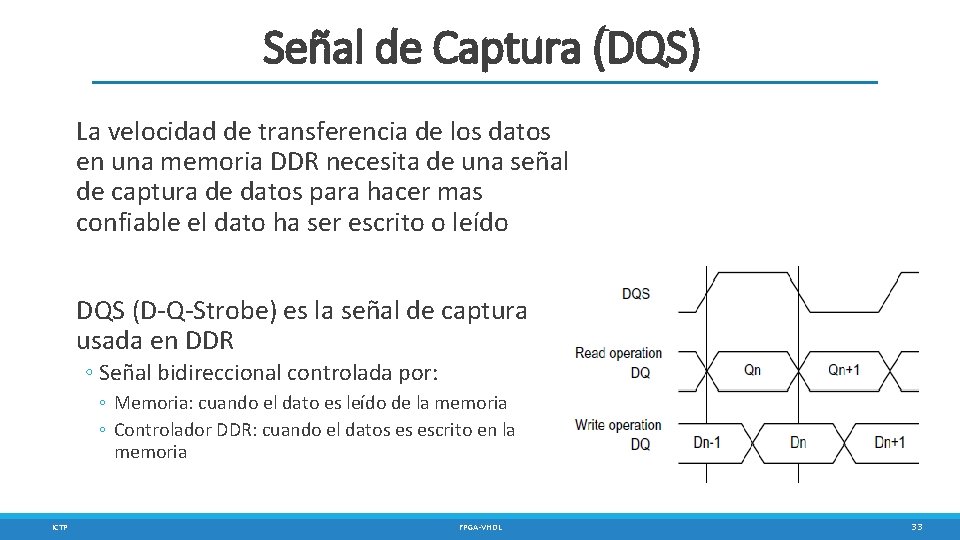

Señal de Captura (DQS) La velocidad de transferencia de los datos en una memoria DDR necesita de una señal de captura de datos para hacer mas confiable el dato ha ser escrito o leído DQS (D-Q-Strobe) es la señal de captura usada en DDR ◦ Señal bidireccional controlada por: ◦ Memoria: cuando el dato es leído de la memoria ◦ Controlador DDR: cuando el datos es escrito en la memoria ICTP FPGA-VHDL 33

Inferring Memory Cristian Sisterna DSDA 34

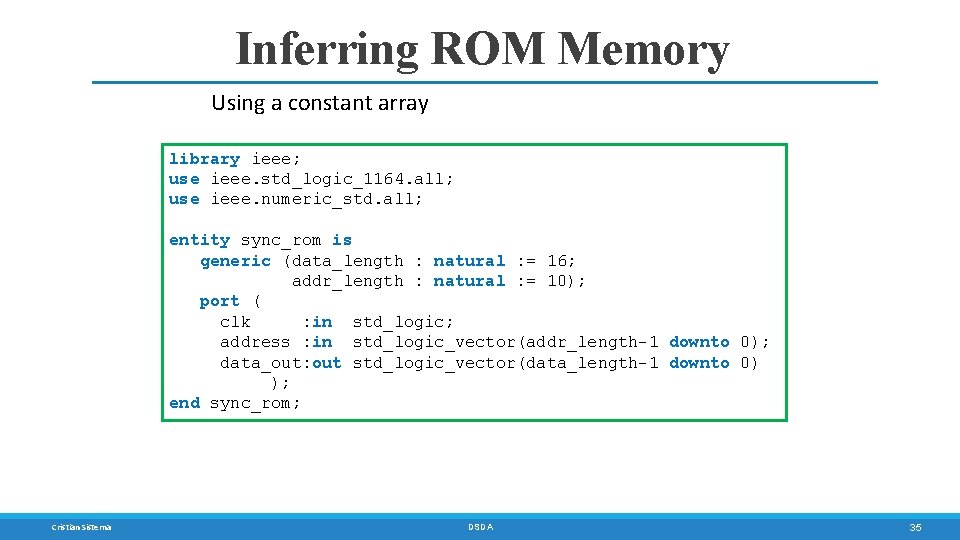

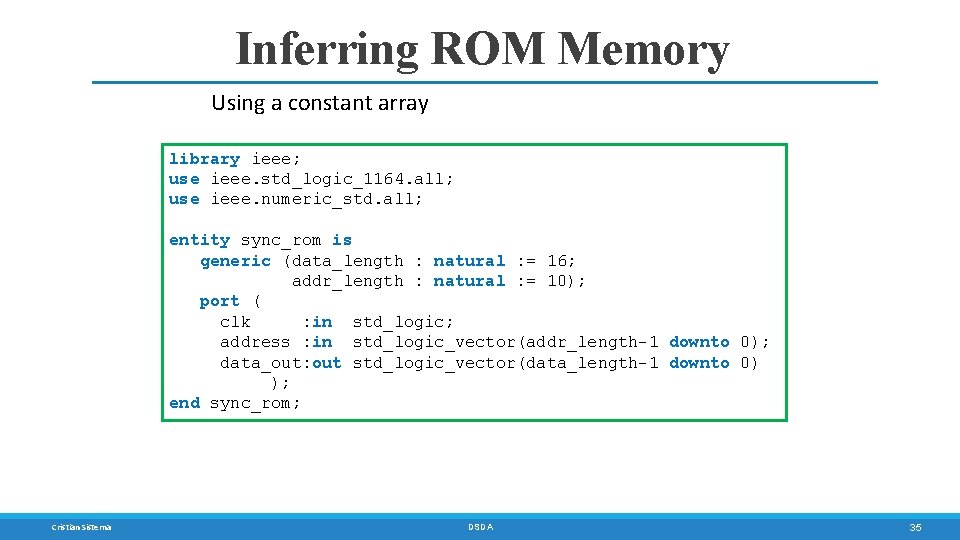

Inferring ROM Memory Using a constant array library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity sync_rom is generic (data_length : natural : = 16; addr_length : natural : = 10); port ( clk : in std_logic; address : in std_logic_vector(addr_length-1 downto 0); data_out: out std_logic_vector(data_length-1 downto 0) ); end sync_rom; Cristian Sisterna DSDA 35

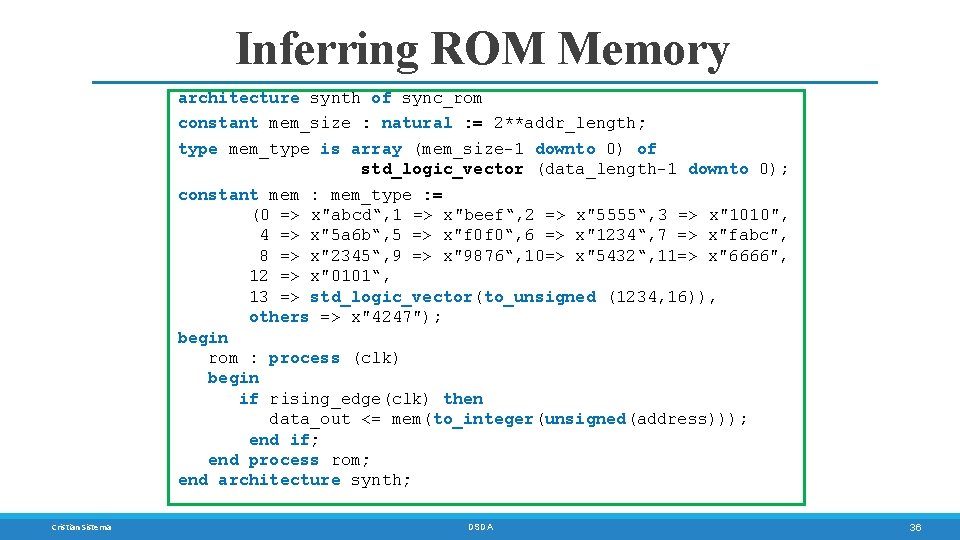

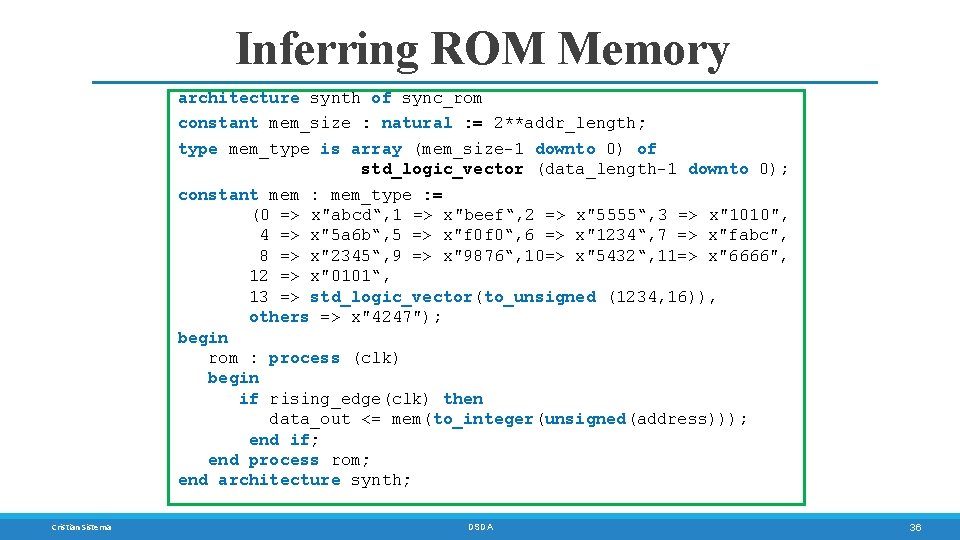

Inferring ROM Memory architecture synth of sync_rom constant mem_size : natural : = 2**addr_length; type mem_type is array (mem_size-1 downto 0) of std_logic_vector (data_length-1 downto 0); constant mem : mem_type : = (0 => x"abcd“, 1 => x"beef“, 2 => x"5555“, 3 => x"1010", 4 => x"5 a 6 b“, 5 => x"f 0 f 0“, 6 => x"1234“, 7 => x"fabc", 8 => x"2345“, 9 => x"9876“, 10=> x"5432“, 11=> x"6666", 12 => x"0101“, 13 => std_logic_vector(to_unsigned (1234, 16)), others => x"4247"); begin rom : process (clk) begin if rising_edge(clk) then data_out <= mem(to_integer(unsigned(address))); end if; end process rom; end architecture synth; Cristian Sisterna DSDA 36

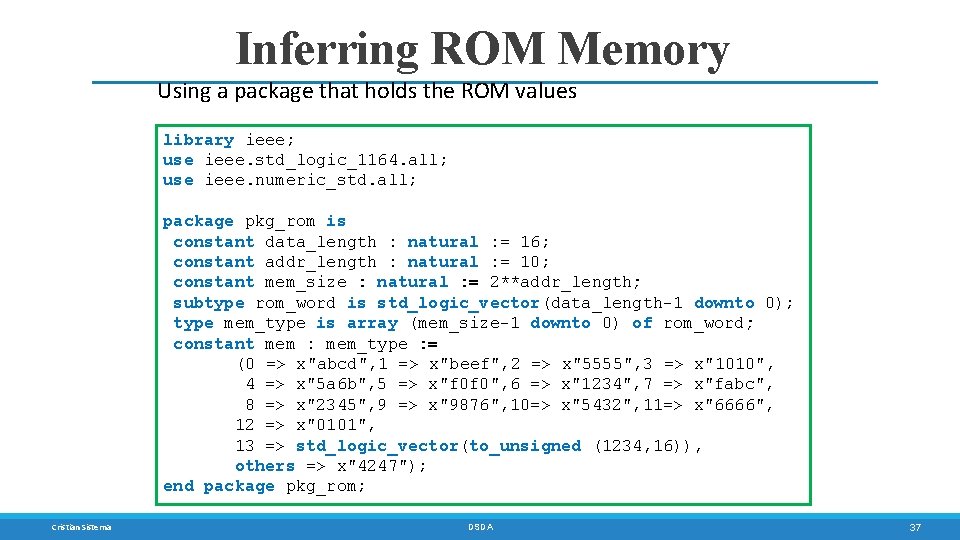

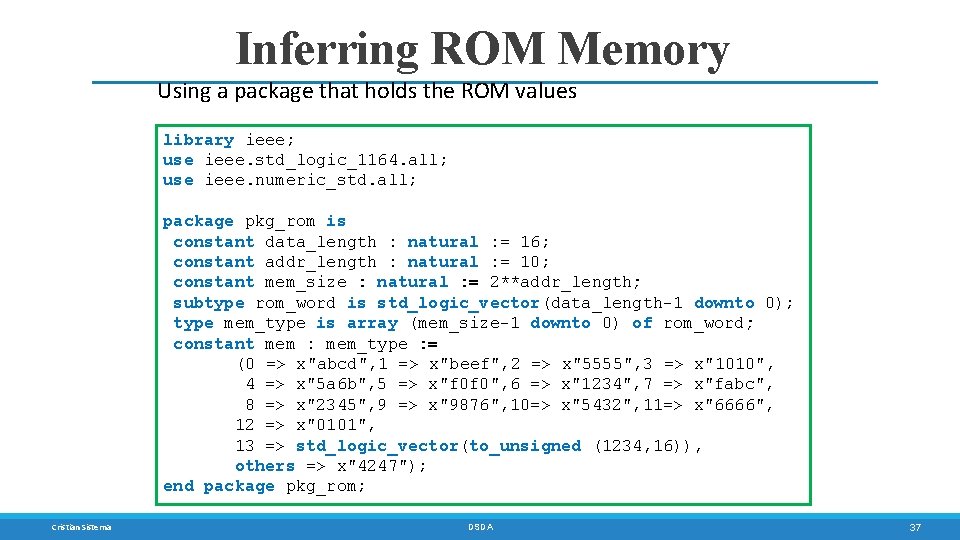

Inferring ROM Memory Using a package that holds the ROM values library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; package pkg_rom is constant data_length : natural : = 16; constant addr_length : natural : = 10; constant mem_size : natural : = 2**addr_length; subtype rom_word is std_logic_vector(data_length-1 downto 0); type mem_type is array (mem_size-1 downto 0) of rom_word; constant mem : mem_type : = (0 => x"abcd", 1 => x"beef", 2 => x"5555", 3 => x"1010", 4 => x"5 a 6 b", 5 => x"f 0 f 0", 6 => x"1234", 7 => x"fabc", 8 => x"2345", 9 => x"9876", 10=> x"5432", 11=> x"6666", 12 => x"0101", 13 => std_logic_vector(to_unsigned (1234, 16)), others => x"4247"); end package pkg_rom; Cristian Sisterna DSDA 37

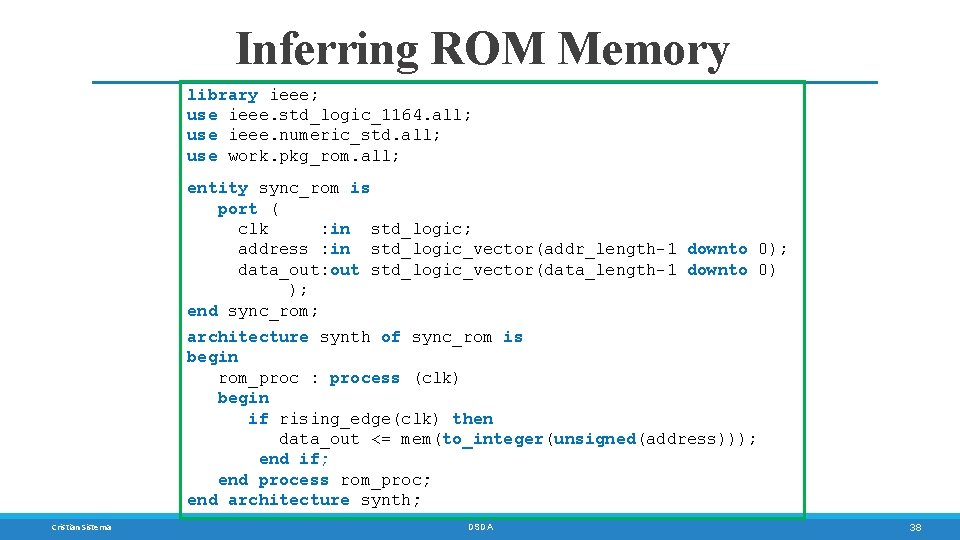

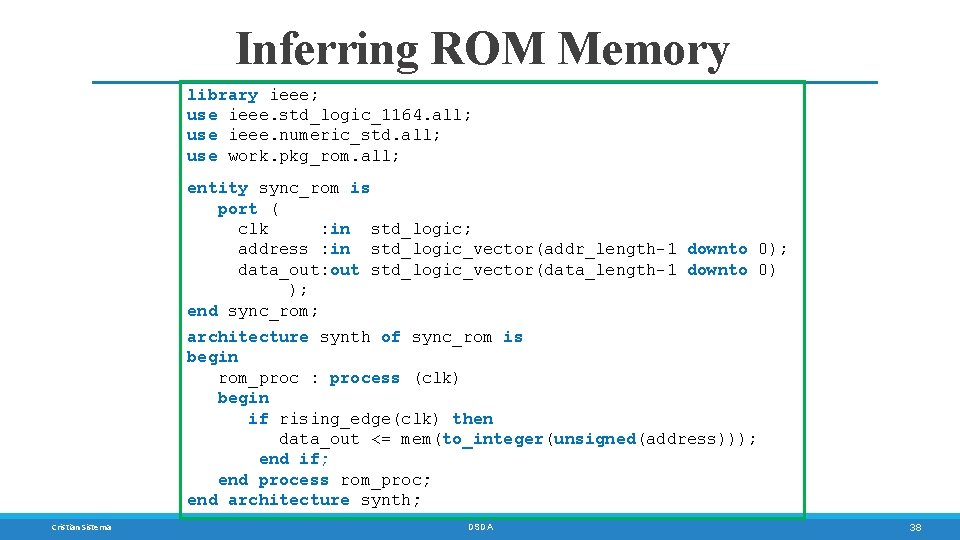

Inferring ROM Memory library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; use work. pkg_rom. all; entity sync_rom is port ( clk : in std_logic; address : in std_logic_vector(addr_length-1 downto 0); data_out: out std_logic_vector(data_length-1 downto 0) ); end sync_rom; architecture synth of sync_rom is begin rom_proc : process (clk) begin if rising_edge(clk) then data_out <= mem(to_integer(unsigned(address))); end if; end process rom_proc; end architecture synth; Cristian Sisterna DSDA 38

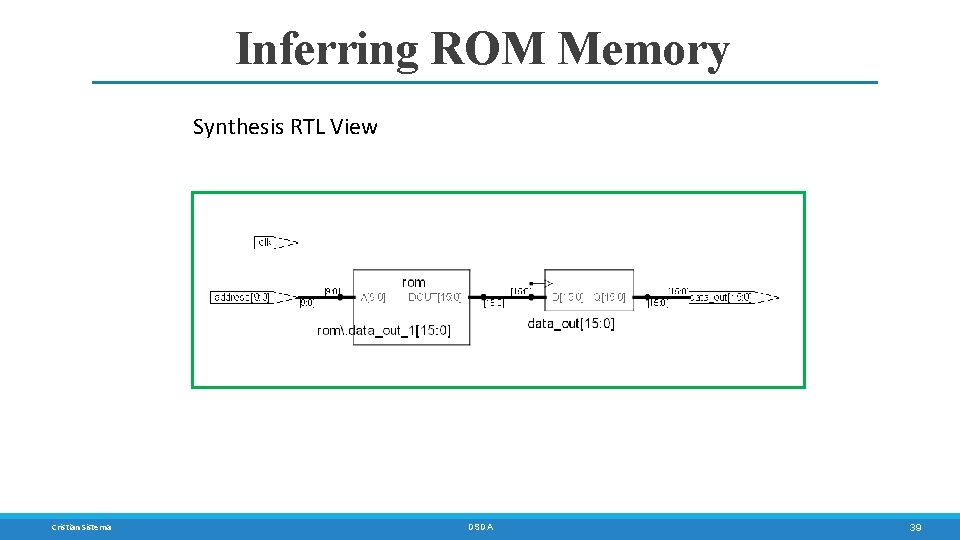

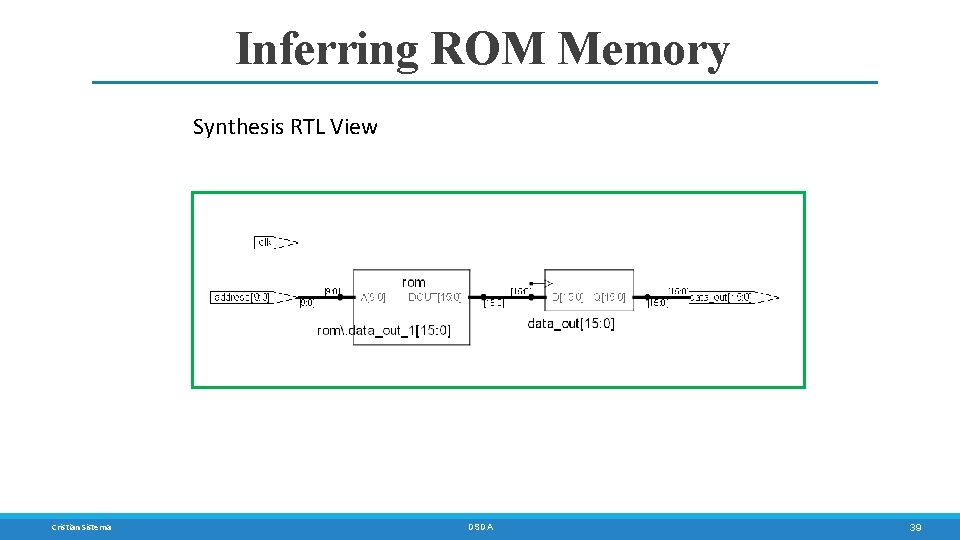

Inferring ROM Memory Synthesis RTL View Cristian Sisterna DSDA 39

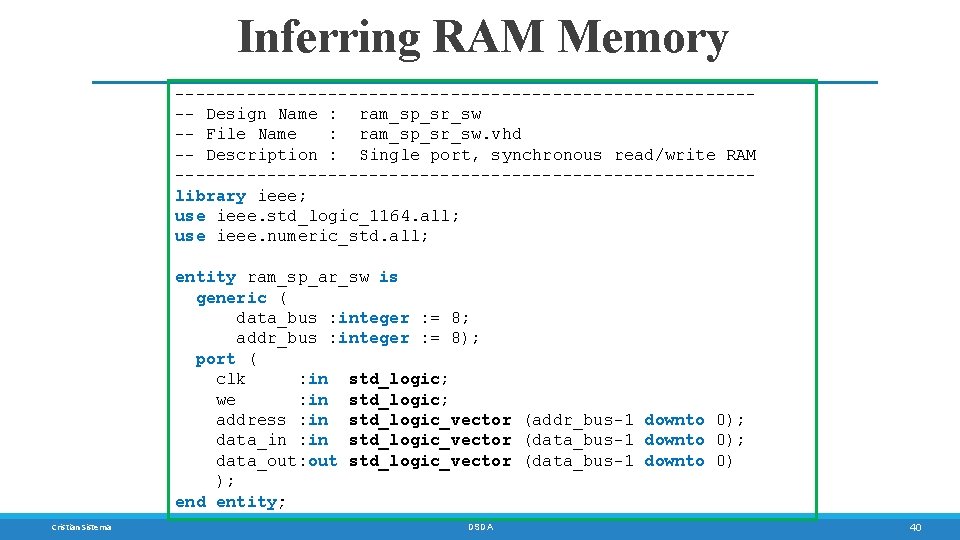

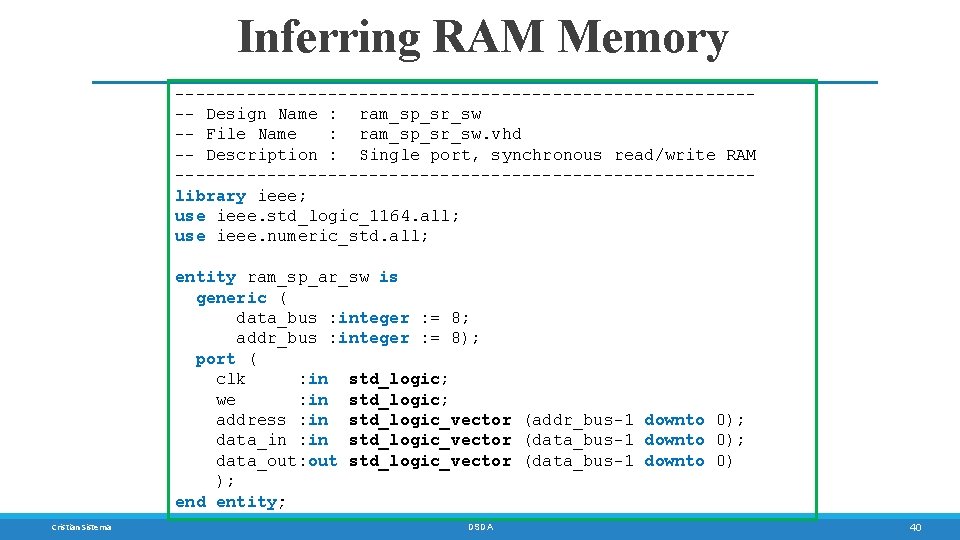

Inferring RAM Memory ----------------------------- -- Design Name : ram_sp_sr_sw -- File Name : ram_sp_sr_sw. vhd -- Description : Single port, synchronous read/write RAM ----------------------------- library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity ram_sp_ar_sw is generic ( data_bus : integer : = 8; addr_bus : integer : = 8); port ( clk : in std_logic; we : in std_logic; address : in std_logic_vector (addr_bus-1 downto 0); data_in : in std_logic_vector (data_bus-1 downto 0); data_out: out std_logic_vector (data_bus-1 downto 0) ); end entity; Cristian Sisterna DSDA 40

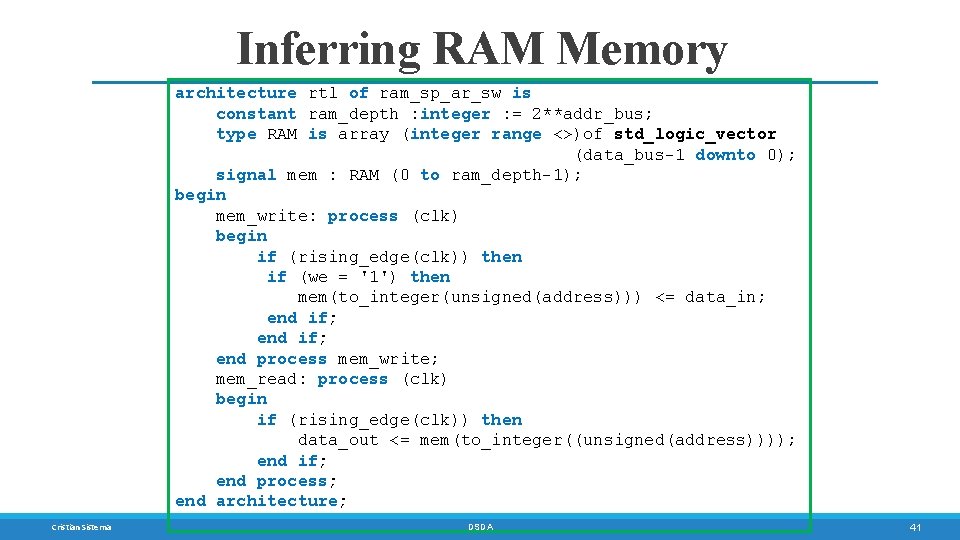

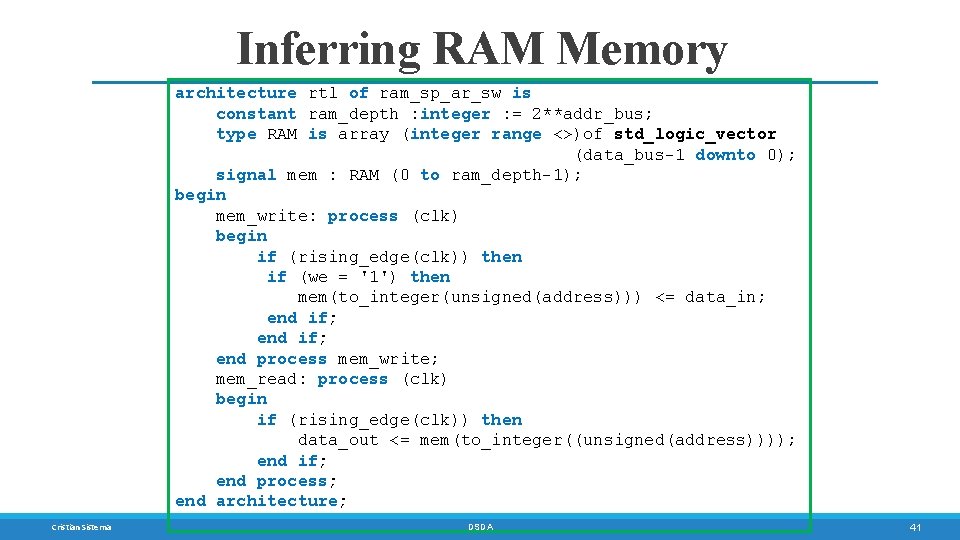

Inferring RAM Memory architecture rtl of ram_sp_ar_sw is constant ram_depth : integer : = 2**addr_bus; type RAM is array (integer range <>)of std_logic_vector (data_bus-1 downto 0); signal mem : RAM (0 to ram_depth-1); begin mem_write: process (clk) begin if (rising_edge(clk)) then if (we = '1') then mem(to_integer(unsigned(address))) <= data_in; end if; end process mem_write; mem_read: process (clk) begin if (rising_edge(clk)) then data_out <= mem(to_integer((unsigned(address)))); end if; end process; end architecture; Cristian Sisterna DSDA 41

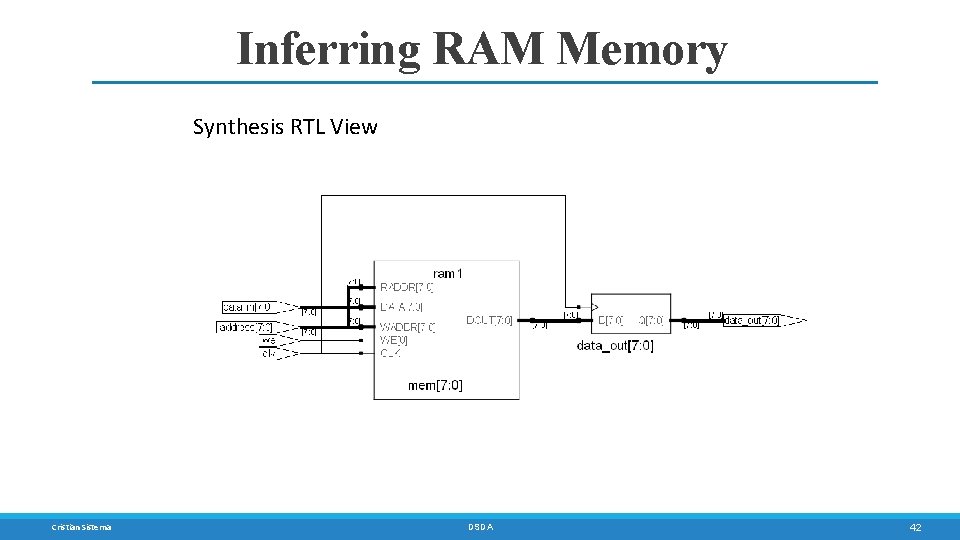

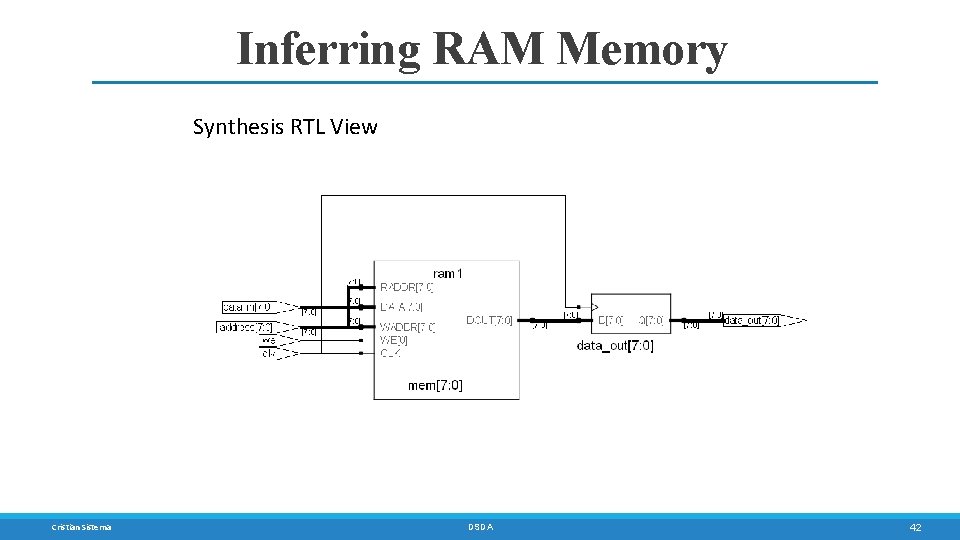

Inferring RAM Memory Synthesis RTL View Cristian Sisterna DSDA 42

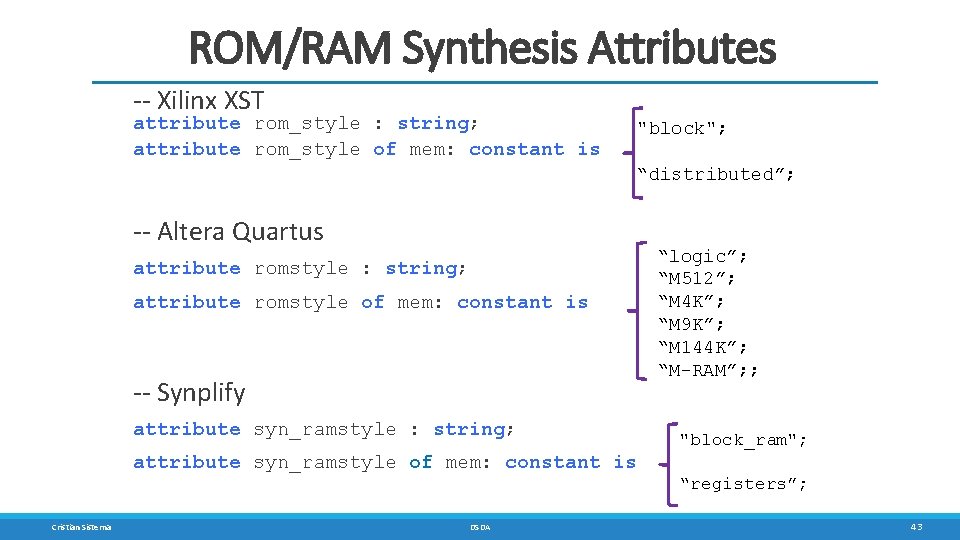

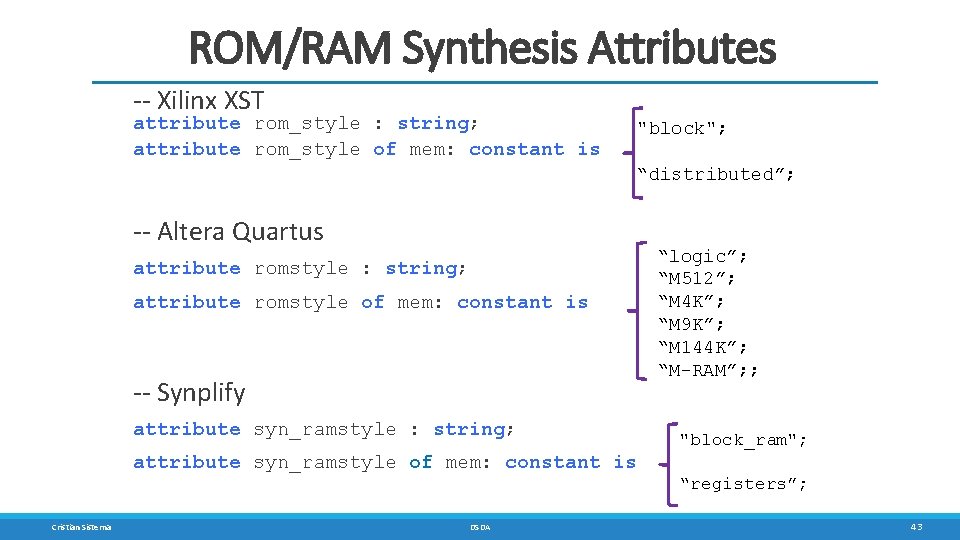

ROM/RAM Synthesis Attributes -- Xilinx XST attribute rom_style : string; attribute rom_style of mem: constant is "block"; “distributed”; -- Altera Quartus attribute romstyle : string; attribute romstyle of mem: constant is -- Synplify attribute syn_ramstyle : string; attribute syn_ramstyle of mem: constant is Cristian Sisterna DSDA “logic”; “M 512”; “M 4 K”; “M 9 K”; “M 144 K”; “M-RAM”; ; "block_ram"; “registers”; 43

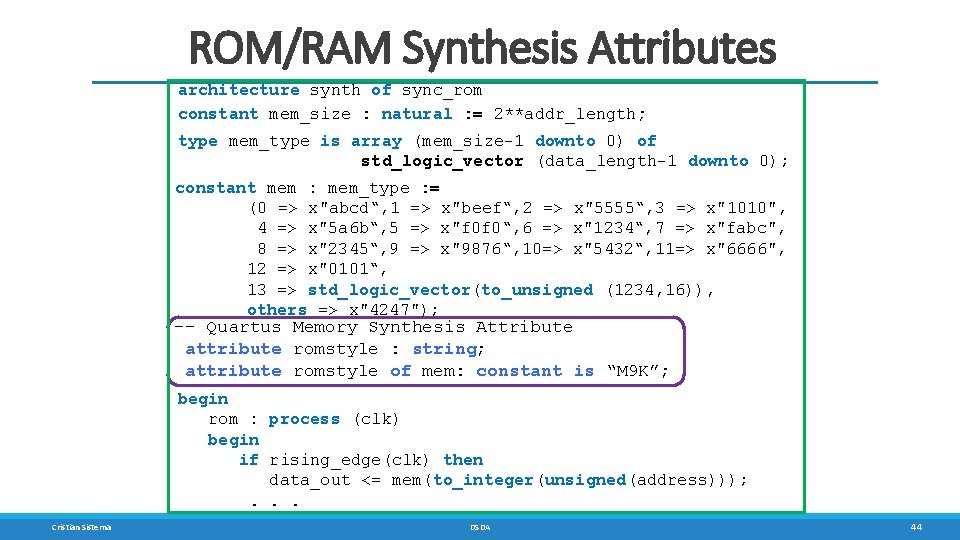

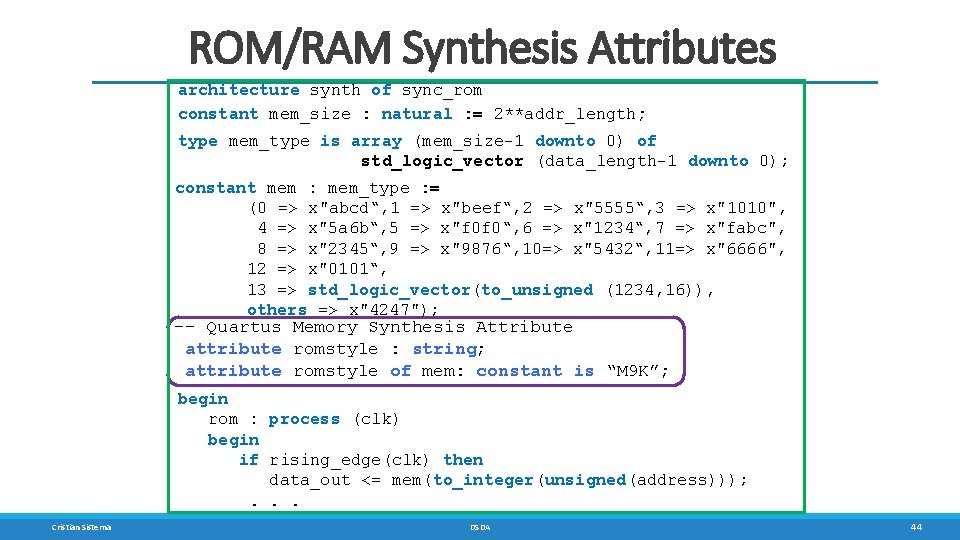

ROM/RAM Synthesis Attributes architecture synth of sync_rom constant mem_size : natural : = 2**addr_length; type mem_type is array (mem_size-1 downto 0) of std_logic_vector (data_length-1 downto 0); constant mem : mem_type : = (0 => x"abcd“, 1 => x"beef“, 2 => x"5555“, 3 => x"1010", 4 => x"5 a 6 b“, 5 => x"f 0 f 0“, 6 => x"1234“, 7 => x"fabc", 8 => x"2345“, 9 => x"9876“, 10=> x"5432“, 11=> x"6666", 12 => x"0101“, 13 => std_logic_vector(to_unsigned (1234, 16)), others => x"4247"); -- Quartus Memory Synthesis Attribute attribute romstyle : string; attribute romstyle of mem: constant is “M 9 K”; begin rom : process (clk) begin if rising_edge(clk) then data_out <= mem(to_integer(unsigned(address))); . . . Cristian Sisterna DSDA 44

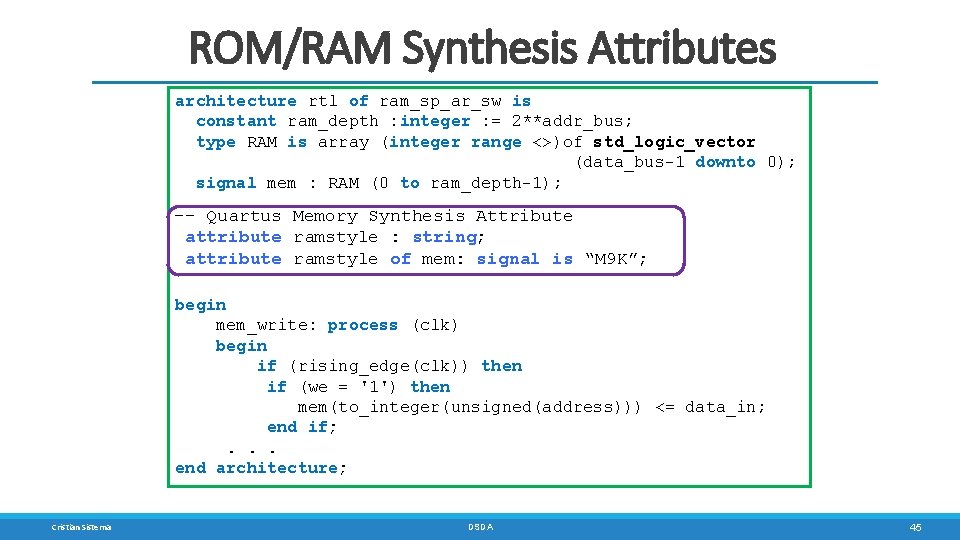

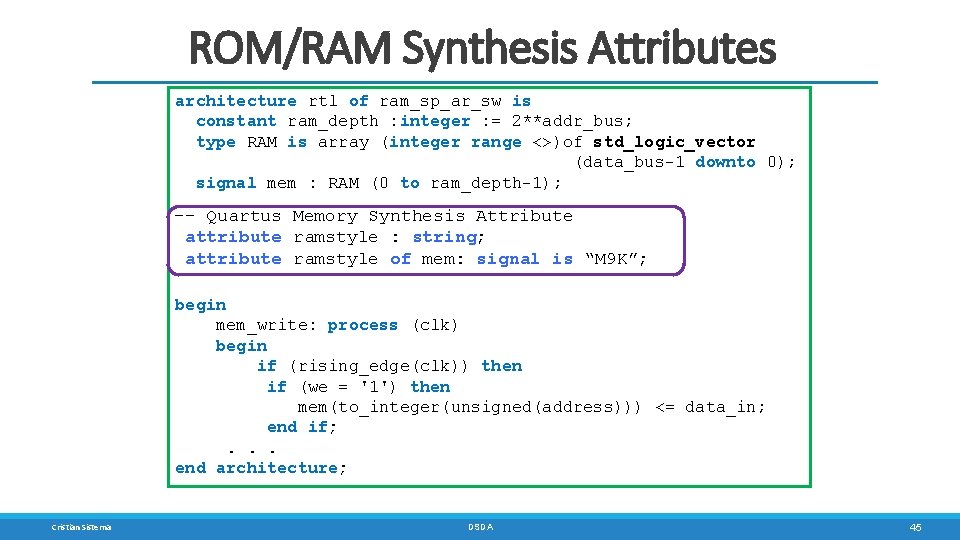

ROM/RAM Synthesis Attributes architecture rtl of ram_sp_ar_sw is constant ram_depth : integer : = 2**addr_bus; type RAM is array (integer range <>)of std_logic_vector (data_bus-1 downto 0); signal mem : RAM (0 to ram_depth-1); -- Quartus Memory Synthesis Attribute attribute ramstyle : string; attribute ramstyle of mem: signal is “M 9 K”; begin mem_write: process (clk) begin if (rising_edge(clk)) then if (we = '1') then mem(to_integer(unsigned(address))) <= data_in; end if; . . . end architecture; Cristian Sisterna DSDA 45

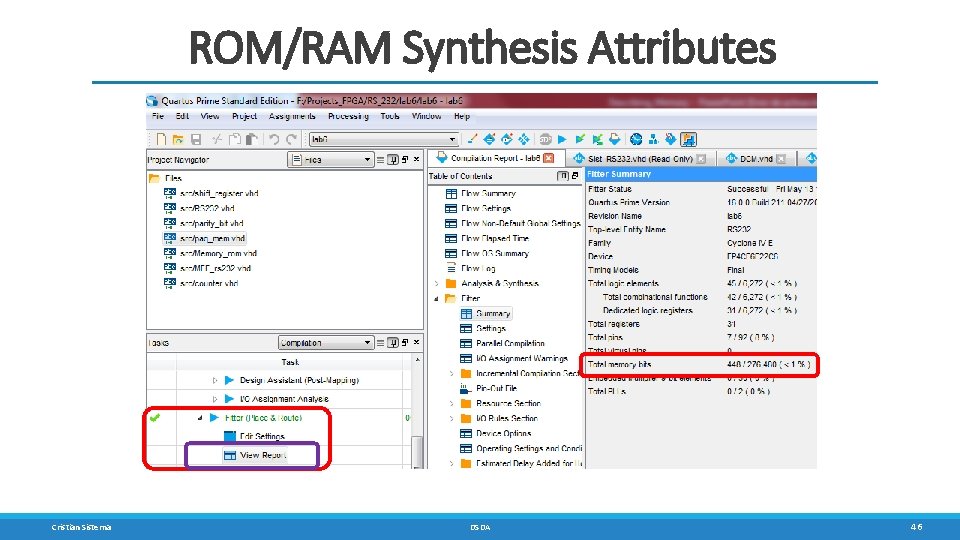

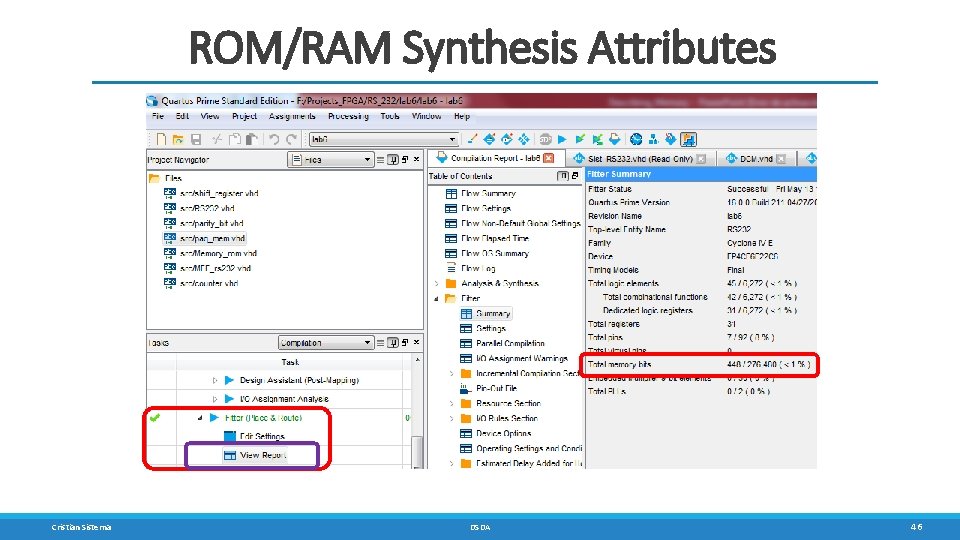

ROM/RAM Synthesis Attributes Cristian Sisterna DSDA 46

Apendix ICTP FPGA-VHDL 47

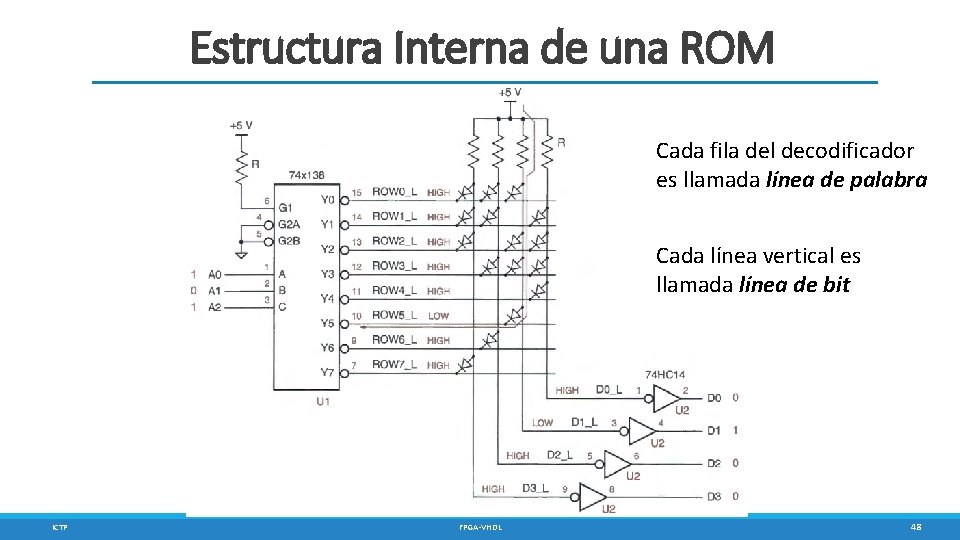

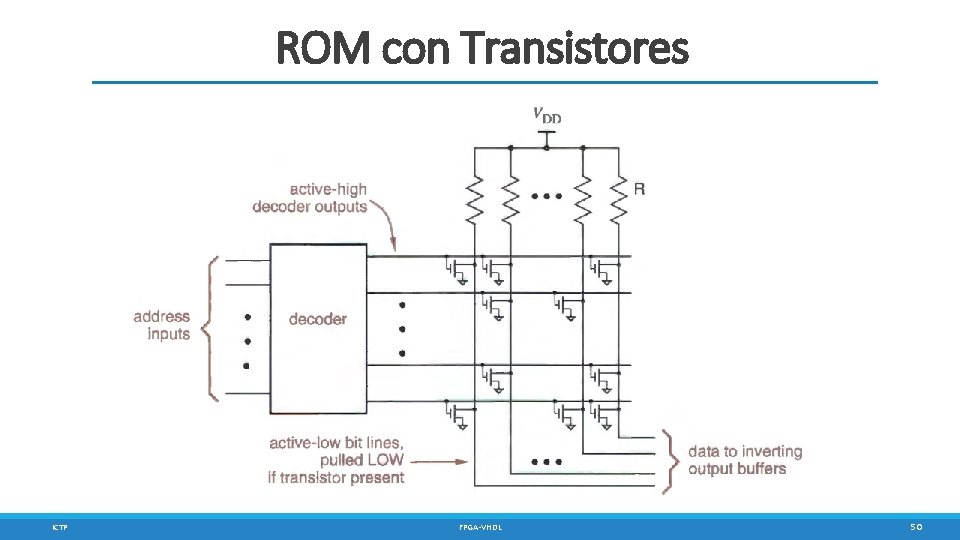

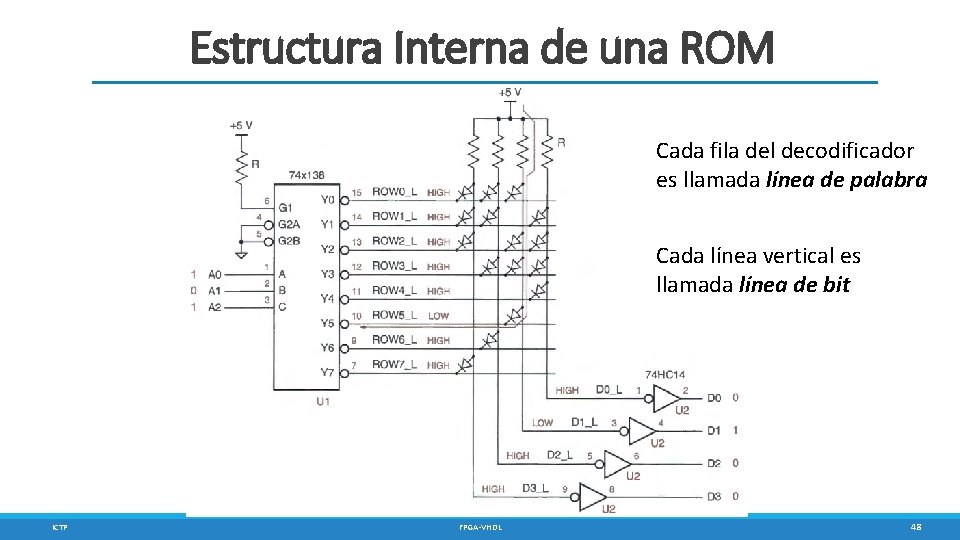

Estructura Interna de una ROM Cada fila del decodificador es llamada línea de palabra Cada línea vertical es llamada línea de bit ICTP FPGA-VHDL 48

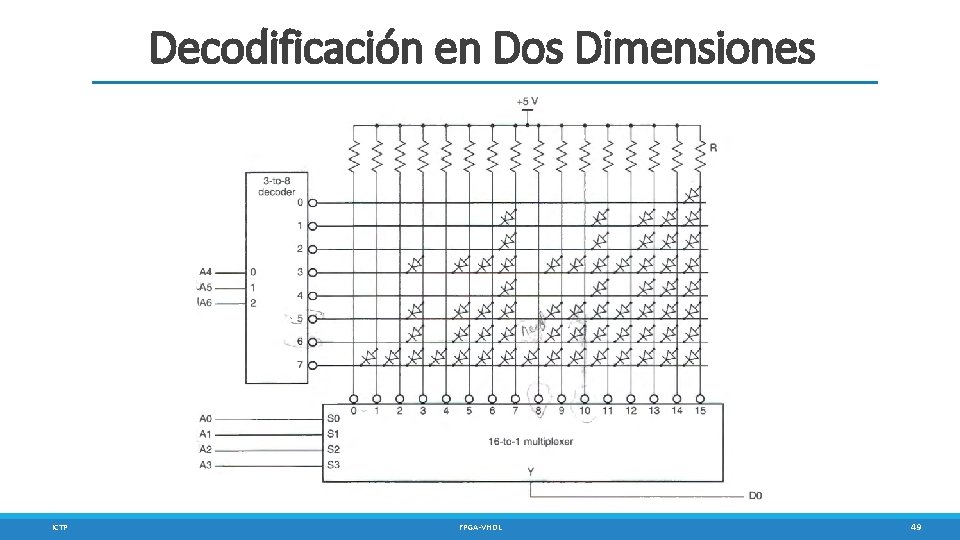

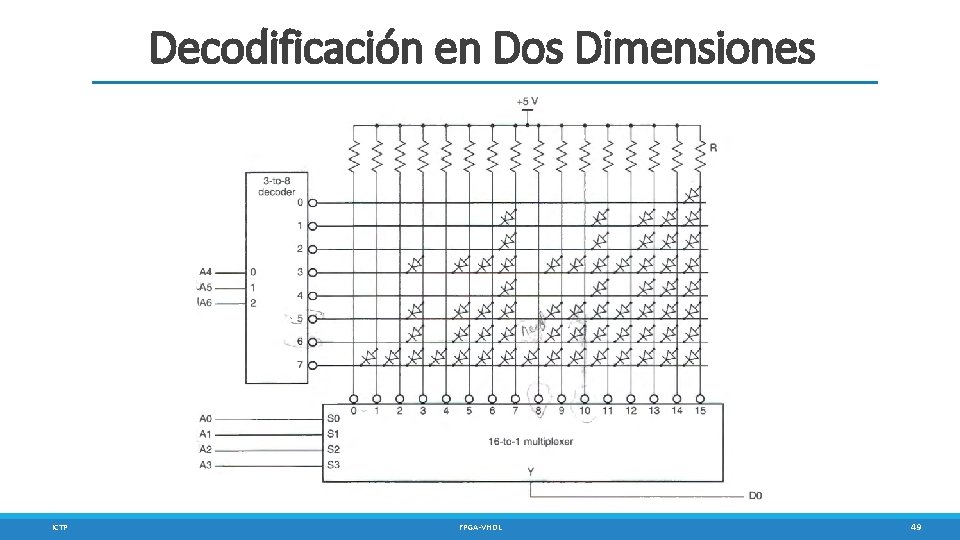

Decodificación en Dos Dimensiones ICTP FPGA-VHDL 49

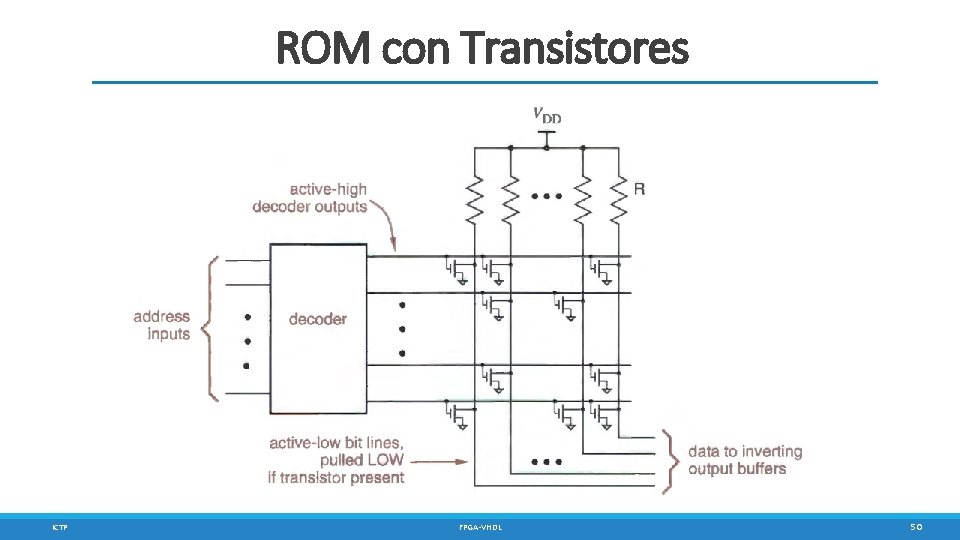

ROM con Transistores ICTP FPGA-VHDL 50

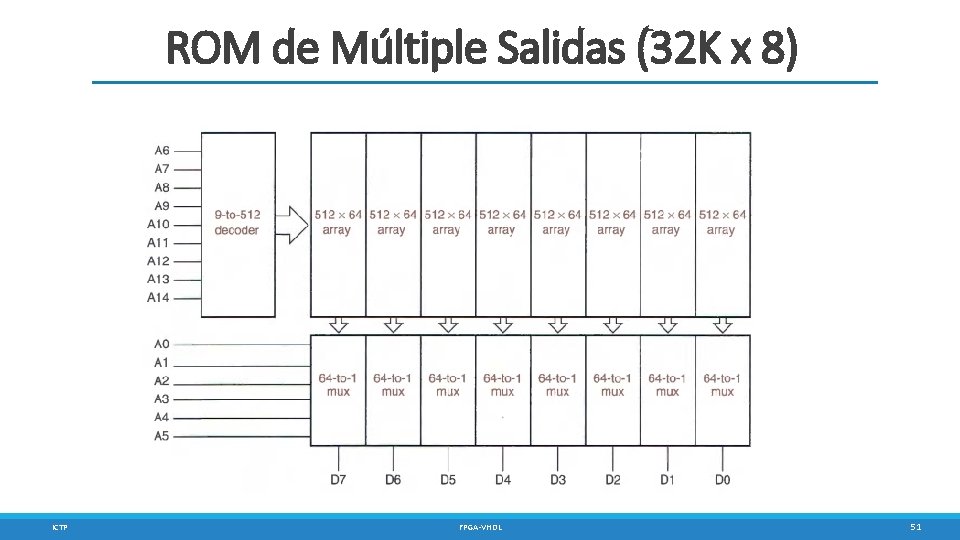

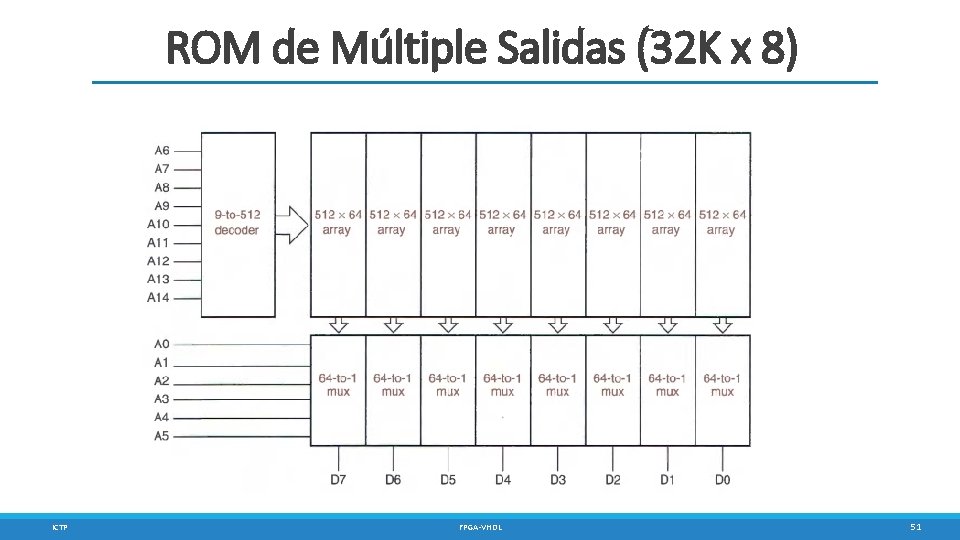

ROM de Múltiple Salidas (32 K x 8) ICTP FPGA-VHDL 51

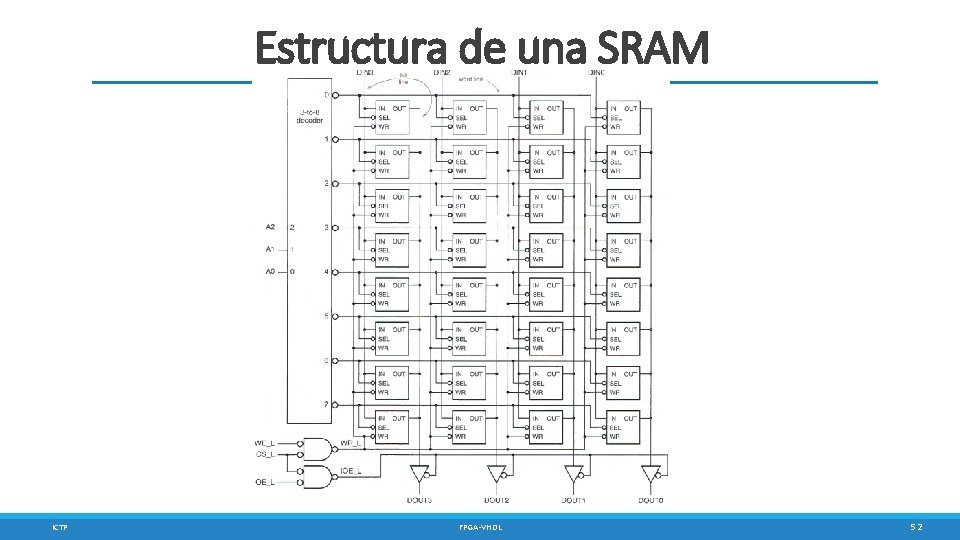

Estructura de una SRAM ICTP FPGA-VHDL 52