DigitalTechnik Grundlagen und Anwendungen Teil IV 1 bersicht

Digital-Technik Grundlagen und Anwendungen Teil IV 1

Übersicht 10 - 11 10 Zeitabhängige binäre Schaltungen 10. 1 10. 2 10. 3 10. 4 Bistabile Kippstufen (Flipflops) Zeitablaufdiagramme Monostabile Kippstufen Verzögerungsglieder 11 Anwendungsschaltungen 11. 1 Zähler 11. 2 Register FHDW G. Hellberg © 2007 2

10 Zeitabhängige binäre Schaltungen 10. 1 10. 2 10. 3 10. 4 Bistabile Kippstufen (Flipflops) Zeitablaufdiagramme Monostabile Kippstufen Verzögerungsglieder FHDW G. Hellberg © 2007 3

10. 1 Flipflops (i) Flipflops sind bistabile Kippglieder, die eine Speicherwirkung besitzen. n Sie werden überwiegend als integrierte Schaltungen hergestellt. n n Man unterscheidet Flipflops mit: n statischen Eingängen (taktzustandsgesteuert) n dynamischen Eingängen (taktflankengesteuert) FHDW G. Hellberg © 2007 4

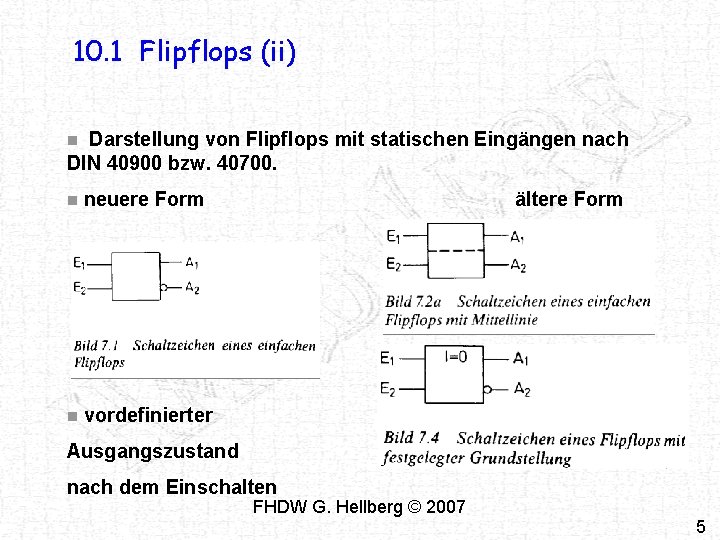

10. 1 Flipflops (ii) Darstellung von Flipflops mit statischen Eingängen nach DIN 40900 bzw. 40700. n n neuere Form n vordefinierter ältere Form Ausgangszustand nach dem Einschalten FHDW G. Hellberg © 2007 5

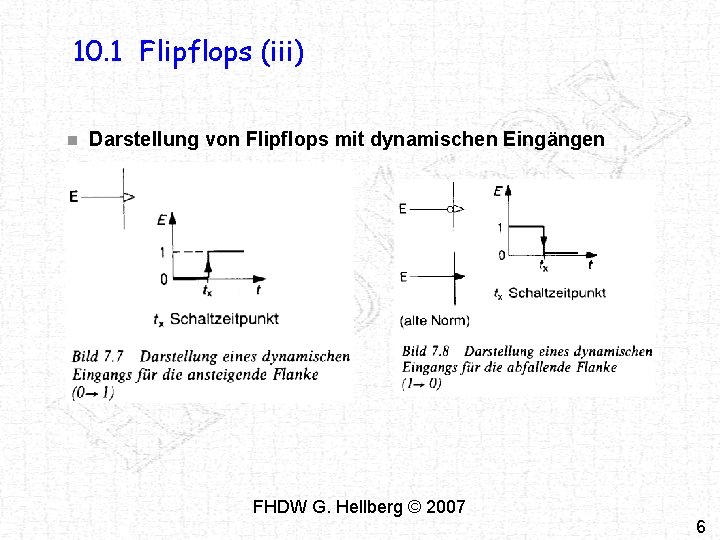

10. 1 Flipflops (iii) n Darstellung von Flipflops mit dynamischen Eingängen FHDW G. Hellberg © 2007 6

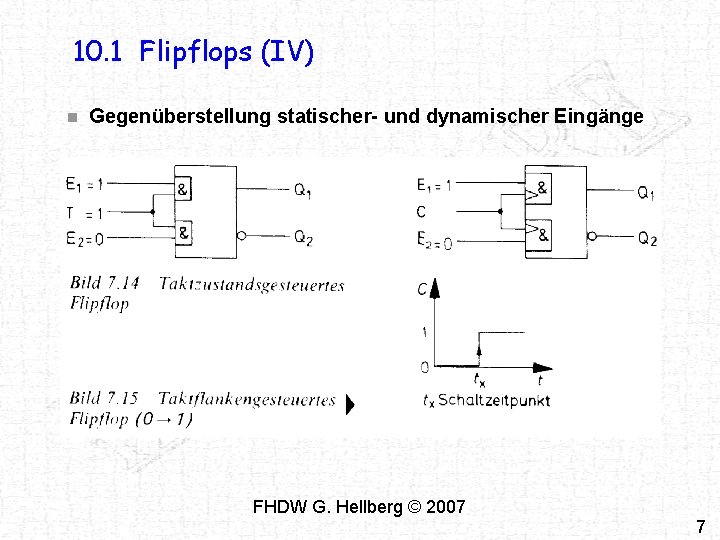

10. 1 Flipflops (IV) n Gegenüberstellung statischer- und dynamischer Eingänge FHDW G. Hellberg © 2007 7

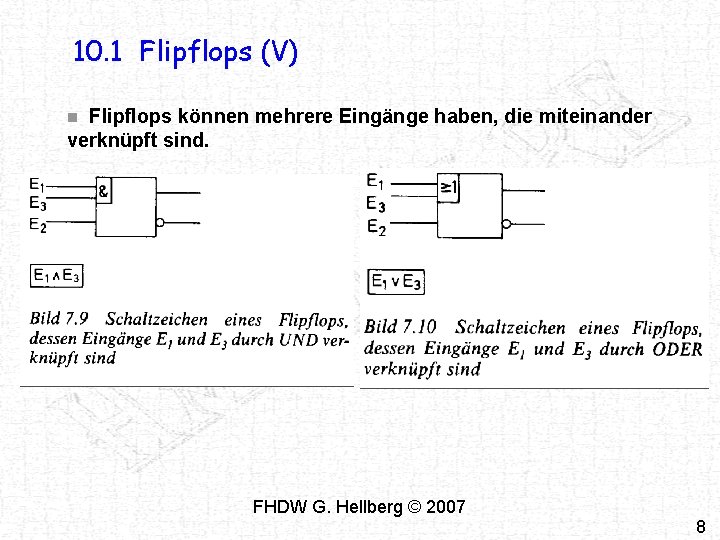

10. 1 Flipflops (V) Flipflops können mehrere Eingänge haben, die miteinander verknüpft sind. n FHDW G. Hellberg © 2007 8

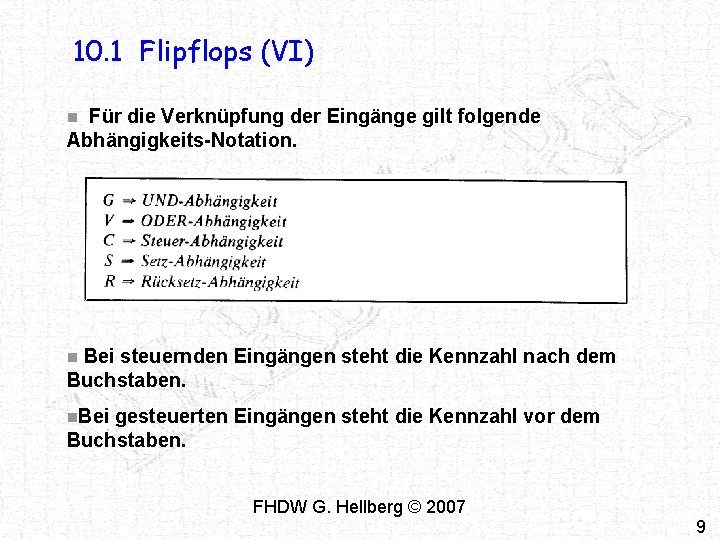

10. 1 Flipflops (VI) Für die Verknüpfung der Eingänge gilt folgende Abhängigkeits-Notation. n Bei steuernden Eingängen steht die Kennzahl nach dem Buchstaben. n n. Bei gesteuerten Eingängen steht die Kennzahl vor dem Buchstaben. FHDW G. Hellberg © 2007 9

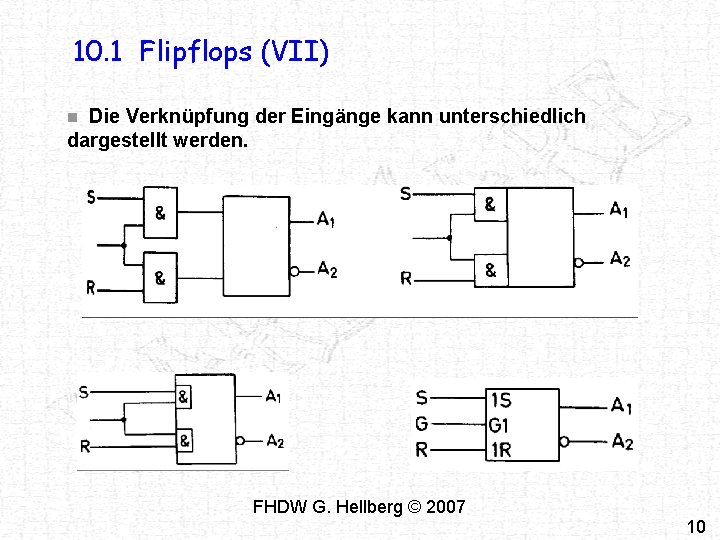

10. 1 Flipflops (VII) Die Verknüpfung der Eingänge kann unterschiedlich dargestellt werden. n FHDW G. Hellberg © 2007 10

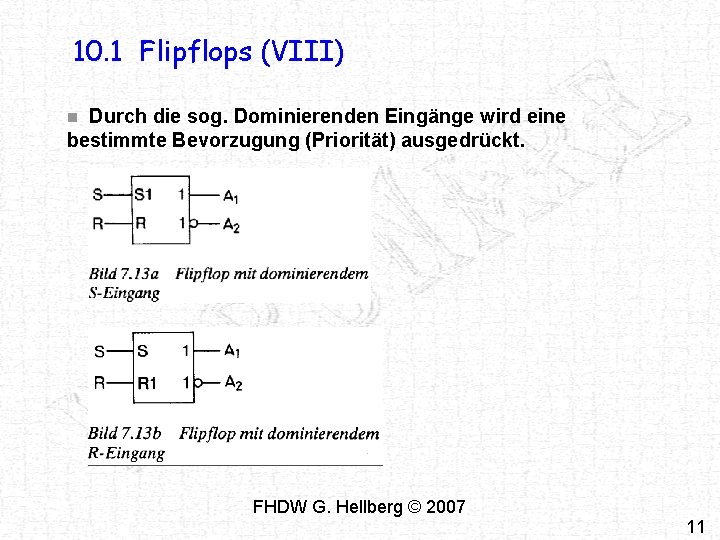

10. 1 Flipflops (VIII) Durch die sog. Dominierenden Eingänge wird eine bestimmte Bevorzugung (Priorität) ausgedrückt. n FHDW G. Hellberg © 2007 11

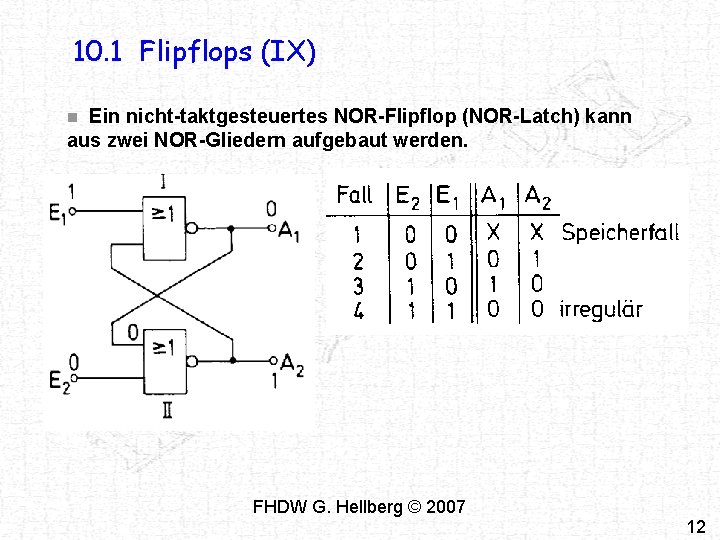

10. 1 Flipflops (IX) Ein nicht-taktgesteuertes NOR-Flipflop (NOR-Latch) kann aus zwei NOR-Gliedern aufgebaut werden. n FHDW G. Hellberg © 2007 12

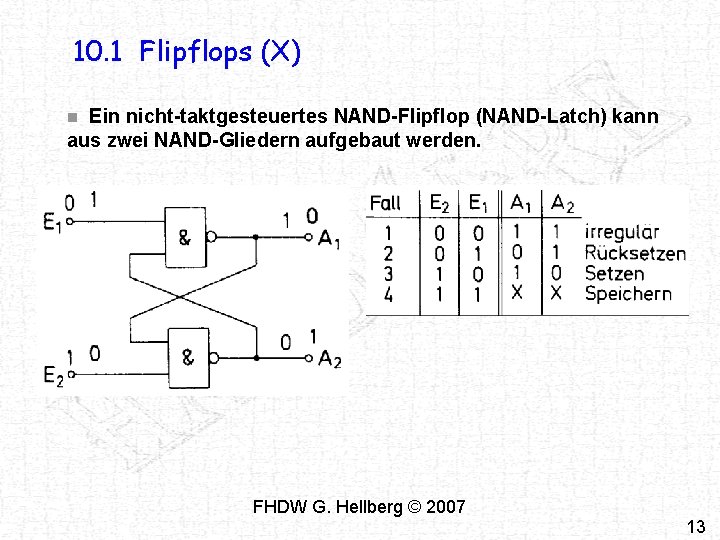

10. 1 Flipflops (X) Ein nicht-taktgesteuertes NAND-Flipflop (NAND-Latch) kann aus zwei NAND-Gliedern aufgebaut werden. n FHDW G. Hellberg © 2007 13

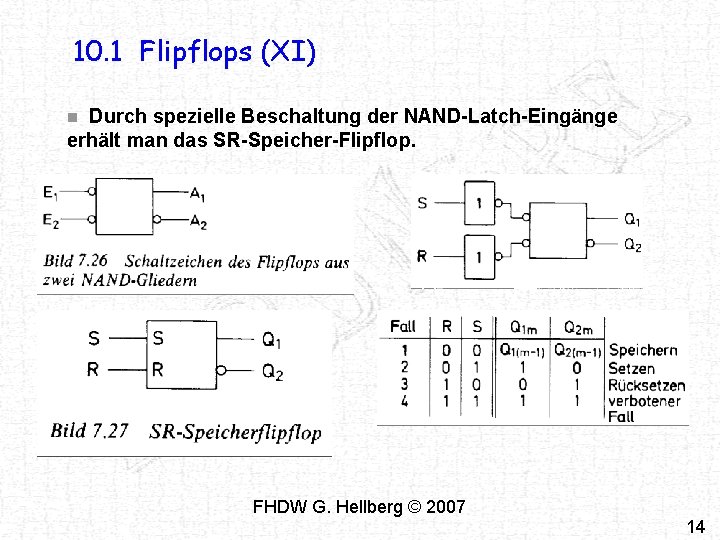

10. 1 Flipflops (XI) Durch spezielle Beschaltung der NAND-Latch-Eingänge erhält man das SR-Speicher-Flipflop. n FHDW G. Hellberg © 2007 14

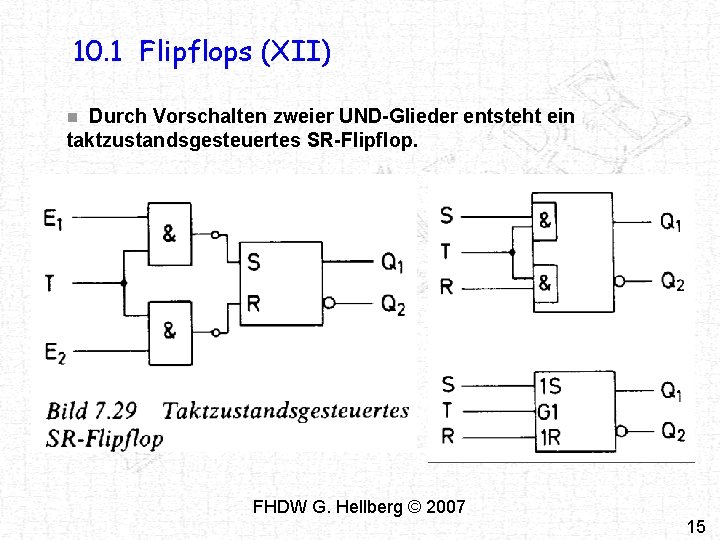

10. 1 Flipflops (XII) Durch Vorschalten zweier UND-Glieder entsteht ein taktzustandsgesteuertes SR-Flipflop. n FHDW G. Hellberg © 2007 15

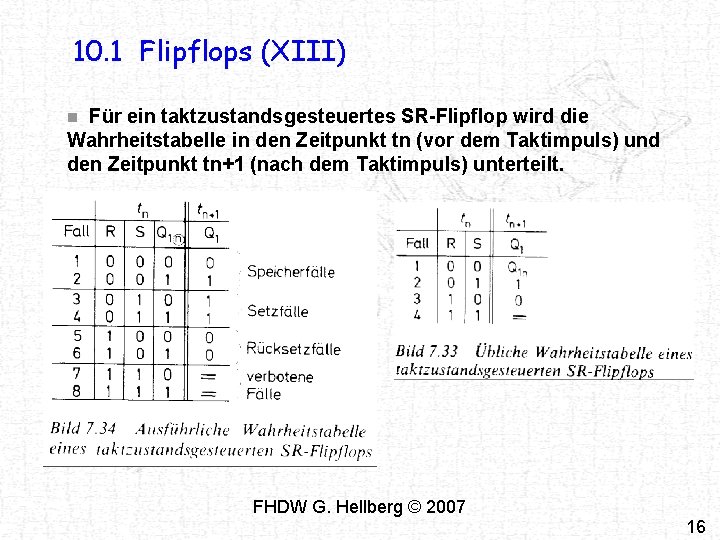

10. 1 Flipflops (XIII) Für ein taktzustandsgesteuertes SR-Flipflop wird die Wahrheitstabelle in den Zeitpunkt tn (vor dem Taktimpuls) und den Zeitpunkt tn+1 (nach dem Taktimpuls) unterteilt. n FHDW G. Hellberg © 2007 16

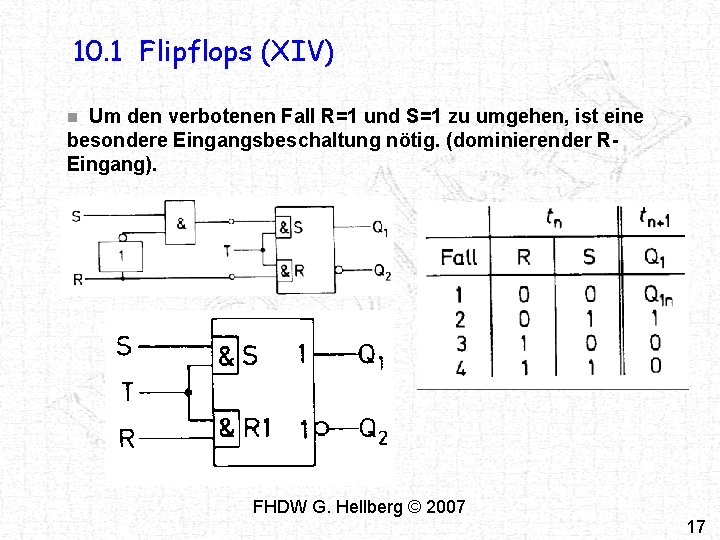

10. 1 Flipflops (XIV) Um den verbotenen Fall R=1 und S=1 zu umgehen, ist eine besondere Eingangsbeschaltung nötig. (dominierender REingang). n FHDW G. Hellberg © 2007 17

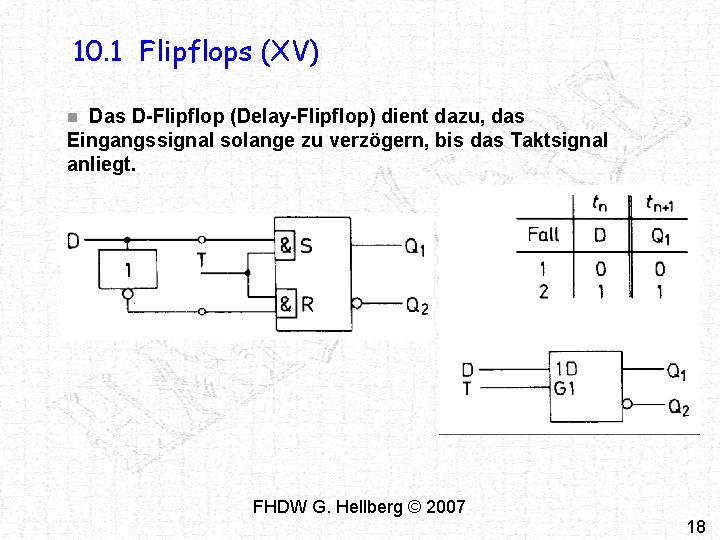

10. 1 Flipflops (XV) Das D-Flipflop (Delay-Flipflop) dient dazu, das Eingangssignal solange zu verzögern, bis das Taktsignal anliegt. n FHDW G. Hellberg © 2007 18

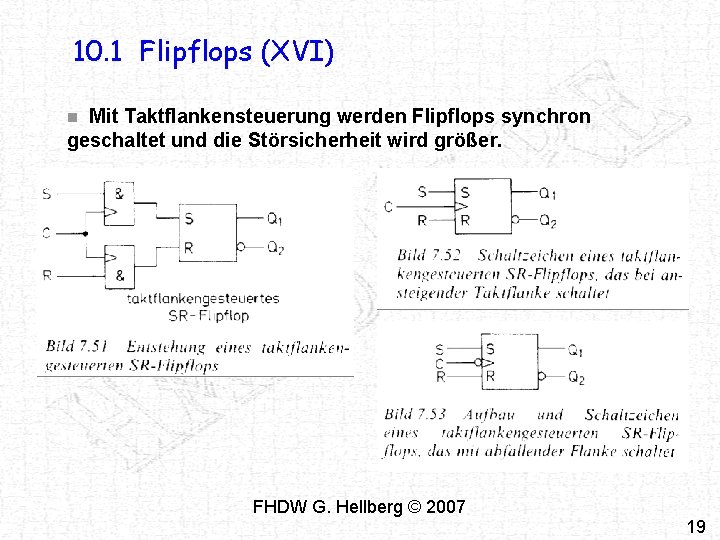

10. 1 Flipflops (XVI) Mit Taktflankensteuerung werden Flipflops synchron geschaltet und die Störsicherheit wird größer. n FHDW G. Hellberg © 2007 19

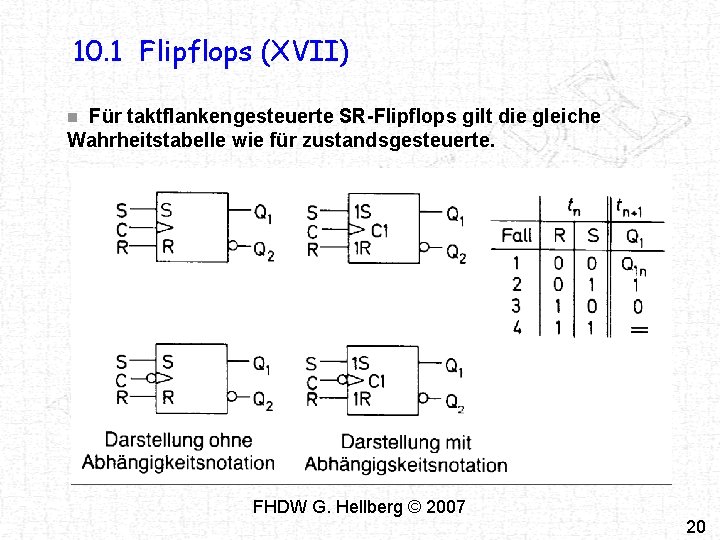

10. 1 Flipflops (XVII) Für taktflankengesteuerte SR-Flipflops gilt die gleiche Wahrheitstabelle wie für zustandsgesteuerte. n FHDW G. Hellberg © 2007 20

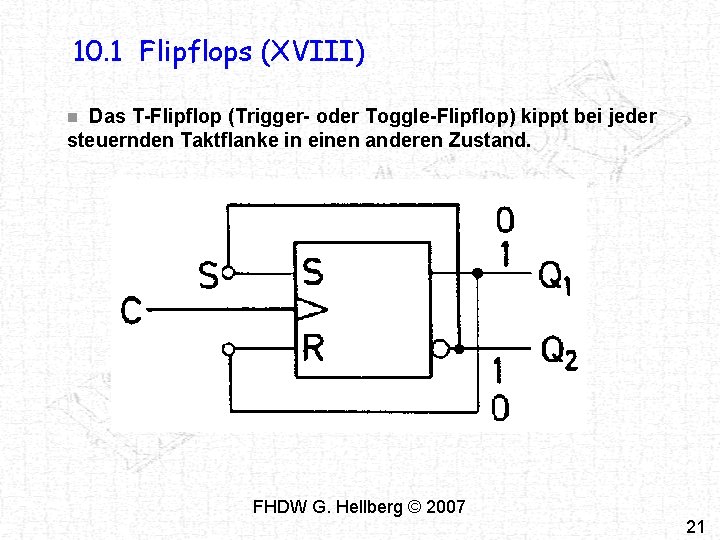

10. 1 Flipflops (XVIII) Das T-Flipflop (Trigger- oder Toggle-Flipflop) kippt bei jeder steuernden Taktflanke in einen anderen Zustand. n FHDW G. Hellberg © 2007 21

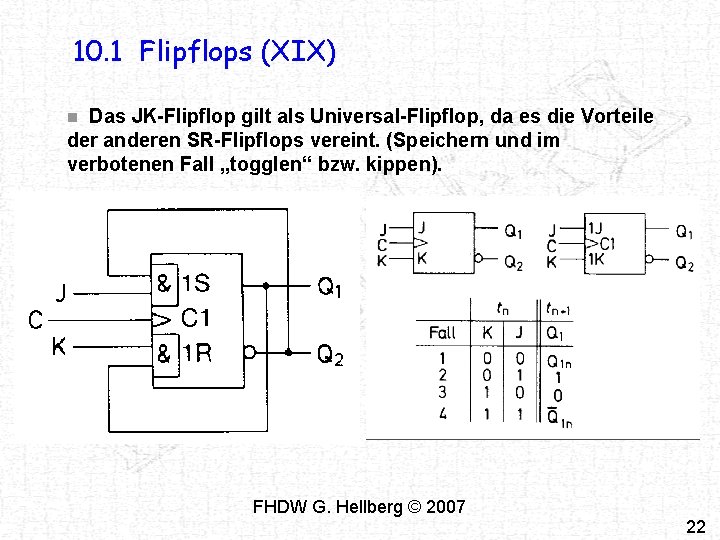

10. 1 Flipflops (XIX) Das JK-Flipflop gilt als Universal-Flipflop, da es die Vorteile der anderen SR-Flipflops vereint. (Speichern und im verbotenen Fall „togglen“ bzw. kippen). n FHDW G. Hellberg © 2007 22

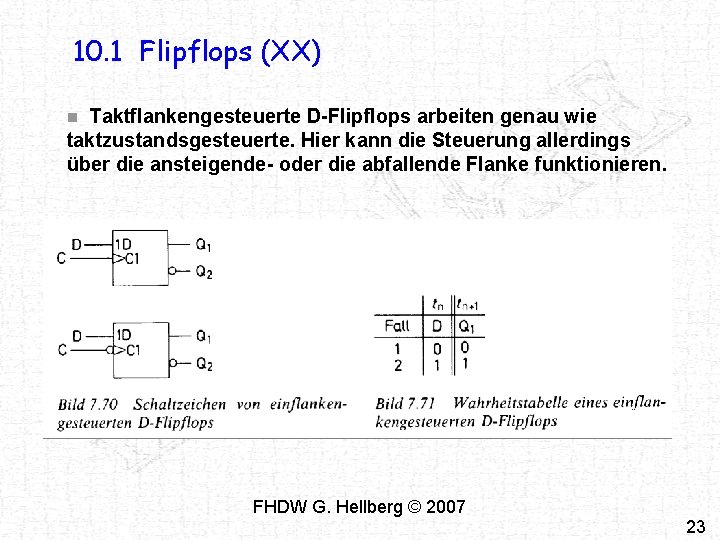

10. 1 Flipflops (XX) Taktflankengesteuerte D-Flipflops arbeiten genau wie taktzustandsgesteuerte. Hier kann die Steuerung allerdings über die ansteigende- oder die abfallende Flanke funktionieren. n FHDW G. Hellberg © 2007 23

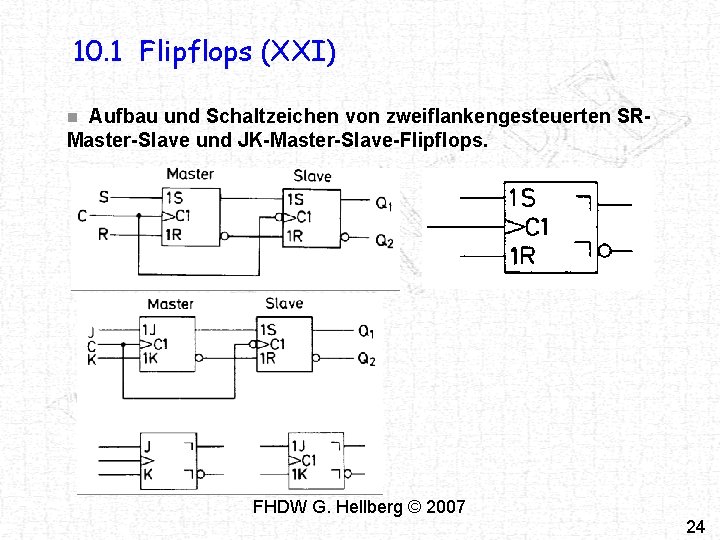

10. 1 Flipflops (XXI) Aufbau und Schaltzeichen von zweiflankengesteuerten SRMaster-Slave und JK-Master-Slave-Flipflops. n FHDW G. Hellberg © 2007 24

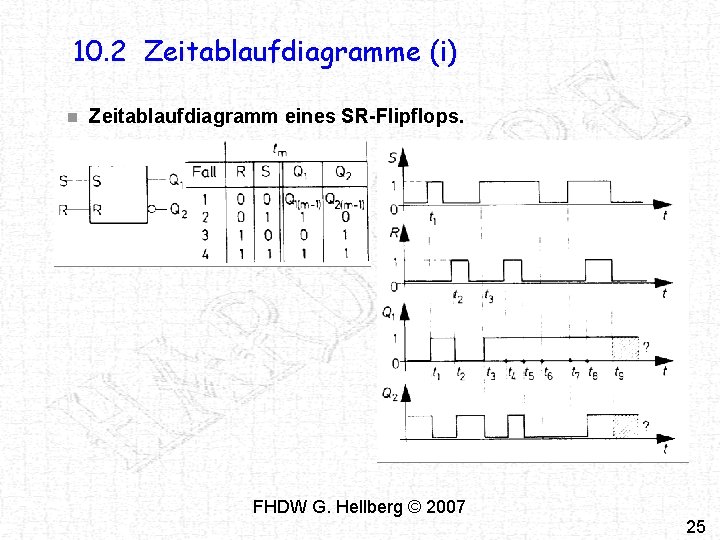

10. 2 Zeitablaufdiagramme (i) n Zeitablaufdiagramm eines SR-Flipflops. FHDW G. Hellberg © 2007 25

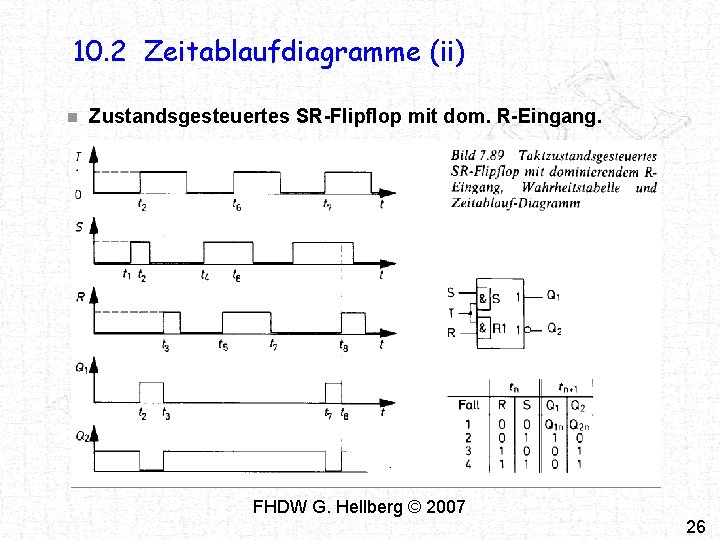

10. 2 Zeitablaufdiagramme (ii) n Zustandsgesteuertes SR-Flipflop mit dom. R-Eingang. FHDW G. Hellberg © 2007 26

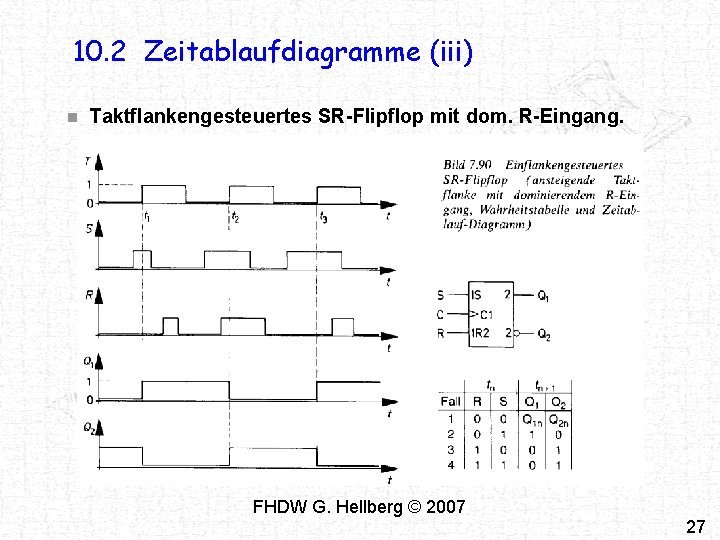

10. 2 Zeitablaufdiagramme (iii) n Taktflankengesteuertes SR-Flipflop mit dom. R-Eingang. FHDW G. Hellberg © 2007 27

10. 2 Zeitablaufdiagramme (iv) n Einflankengesteuertes JK-Flipflop. FHDW G. Hellberg © 2007 28

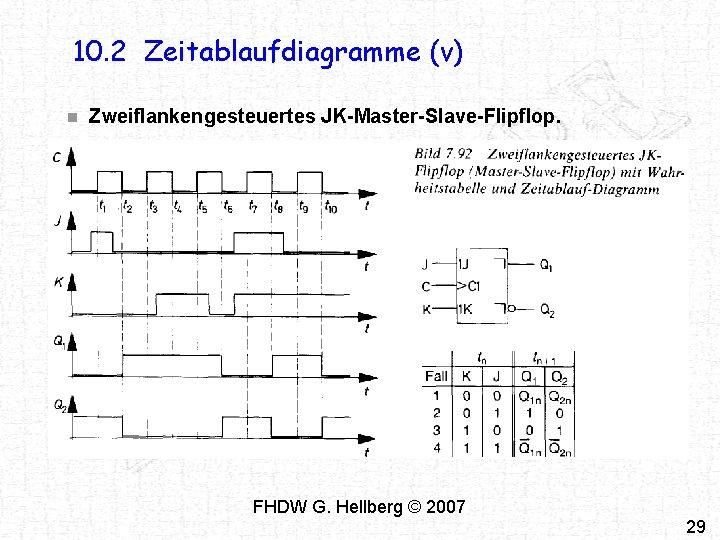

10. 2 Zeitablaufdiagramme (v) n Zweiflankengesteuertes JK-Master-Slave-Flipflop. FHDW G. Hellberg © 2007 29

10. 3 Monostabile Kippstufe (i) Im stabilen Zustand führt der Hauptausgang Q einer monostabilen Kippstufe 0 -Signal. n Im nichtstabilen Zustand führt der Hauptausgang Q einer monostabilen Kippstufe 1 -Signal. n FHDW G. Hellberg © 2007 30

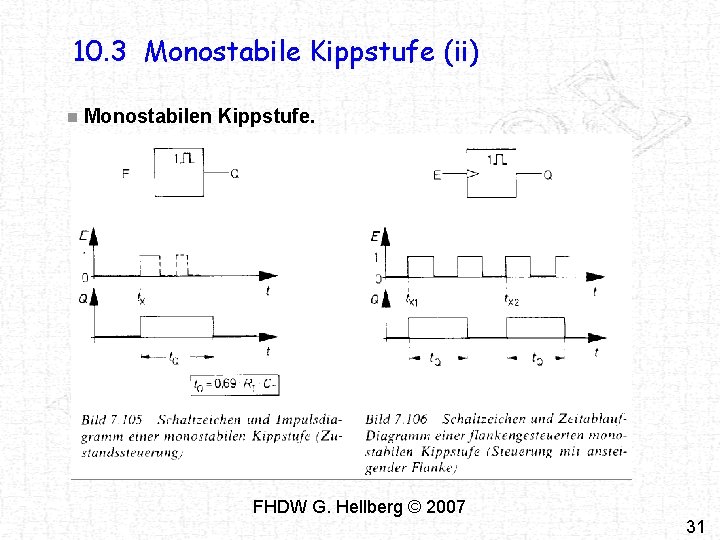

10. 3 Monostabile Kippstufe (ii) n Monostabilen Kippstufe. FHDW G. Hellberg © 2007 31

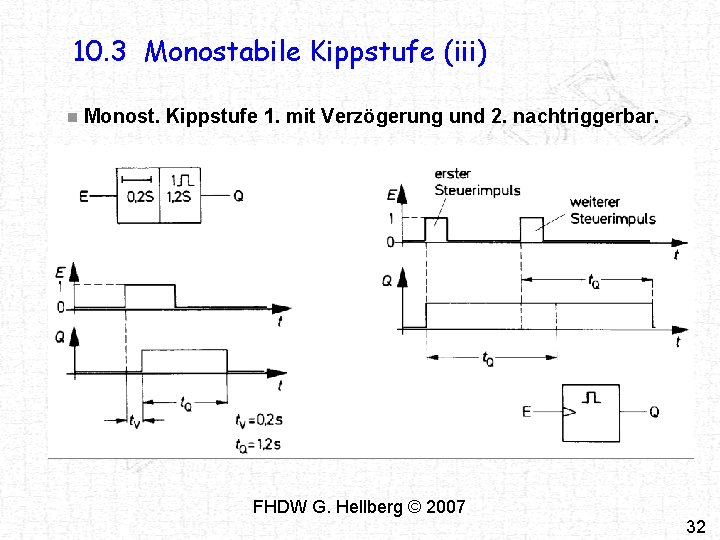

10. 3 Monostabile Kippstufe (iii) n Monost. Kippstufe 1. mit Verzögerung und 2. nachtriggerbar. FHDW G. Hellberg © 2007 32

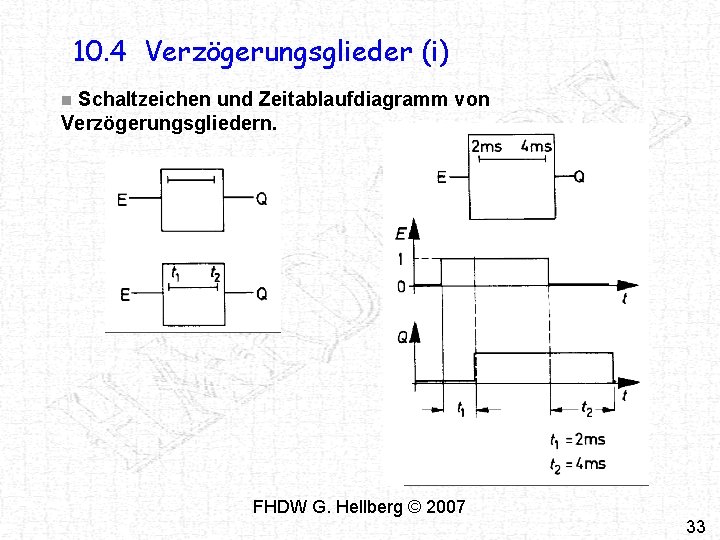

10. 4 Verzögerungsglieder (i) Schaltzeichen und Zeitablaufdiagramm von Verzögerungsgliedern. n FHDW G. Hellberg © 2007 33

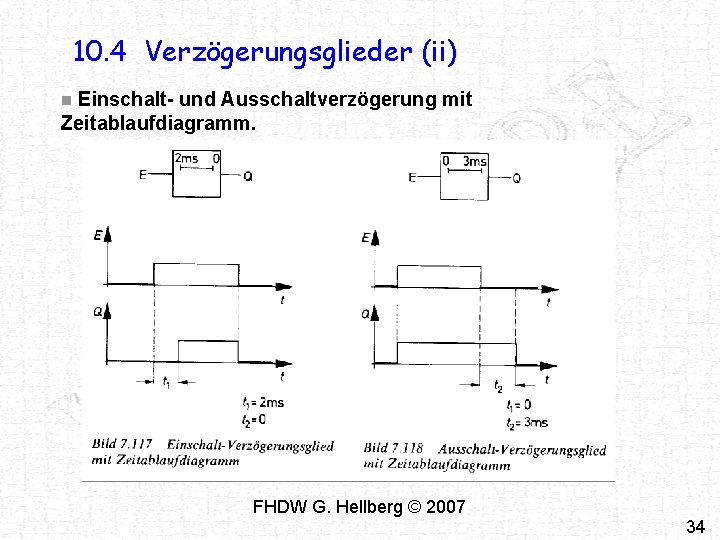

10. 4 Verzögerungsglieder (ii) Einschalt- und Ausschaltverzögerung mit Zeitablaufdiagramm. n FHDW G. Hellberg © 2007 34

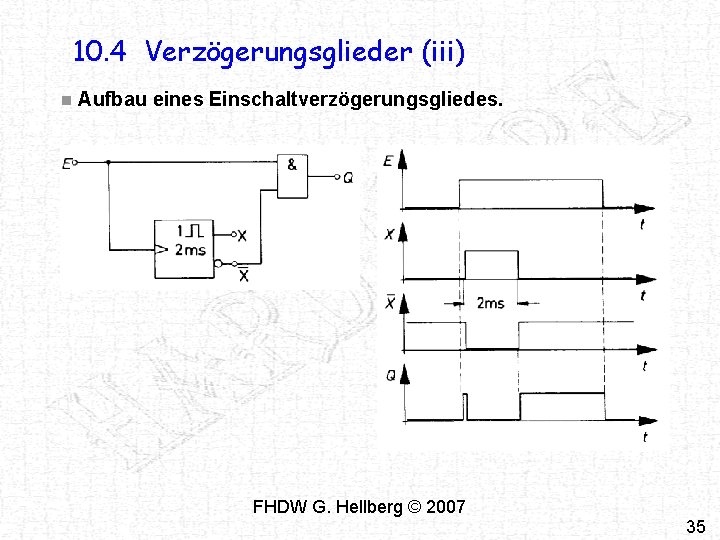

10. 4 Verzögerungsglieder (iii) n Aufbau eines Einschaltverzögerungsgliedes. FHDW G. Hellberg © 2007 35

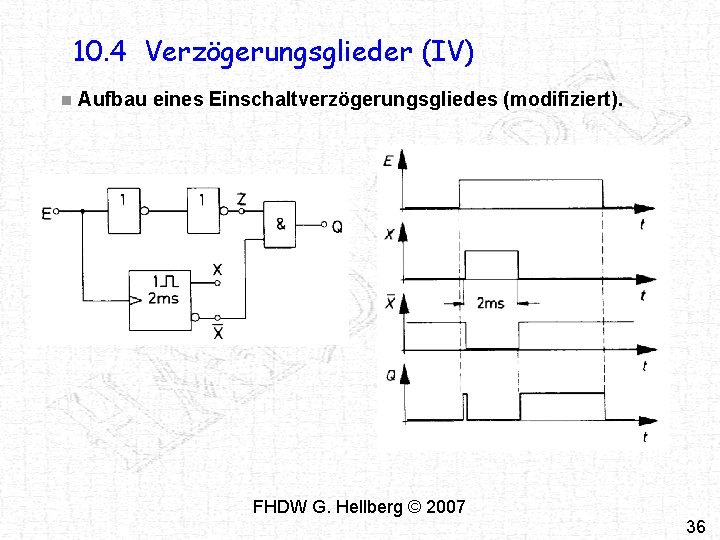

10. 4 Verzögerungsglieder (IV) n Aufbau eines Einschaltverzögerungsgliedes (modifiziert). FHDW G. Hellberg © 2007 36

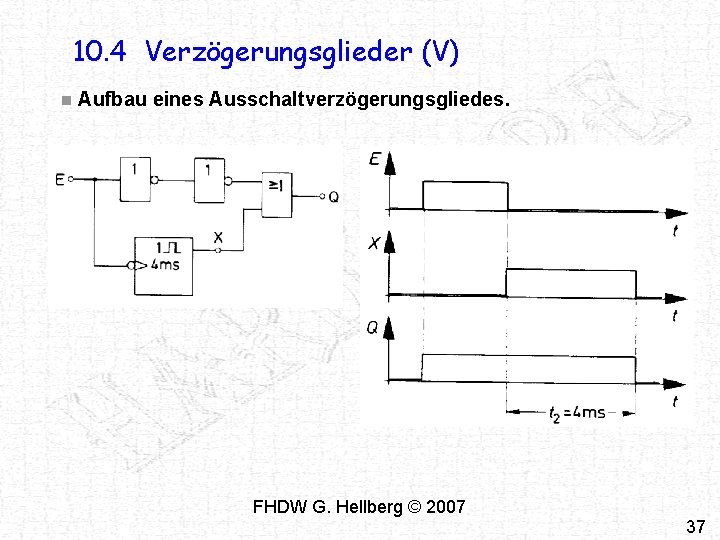

10. 4 Verzögerungsglieder (V) n Aufbau eines Ausschaltverzögerungsgliedes. FHDW G. Hellberg © 2007 37

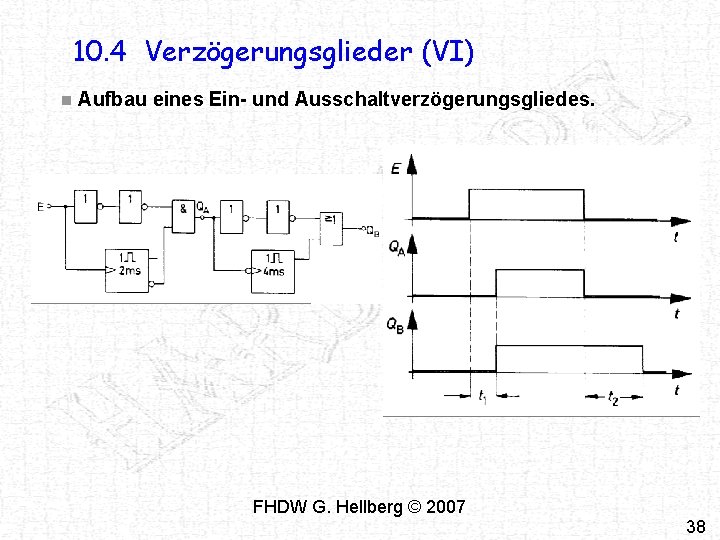

10. 4 Verzögerungsglieder (VI) n Aufbau eines Ein- und Ausschaltverzögerungsgliedes. FHDW G. Hellberg © 2007 38

11 Anwendungsschaltungen 11. 1 Zähler 11. 2 Register FHDW G. Hellberg © 2007 39

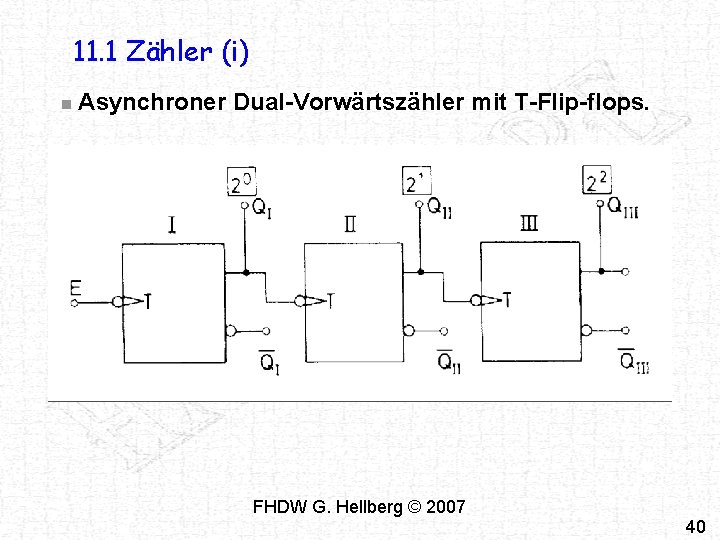

11. 1 Zähler (i) n Asynchroner Dual-Vorwärtszähler mit T-Flip-flops. FHDW G. Hellberg © 2007 40

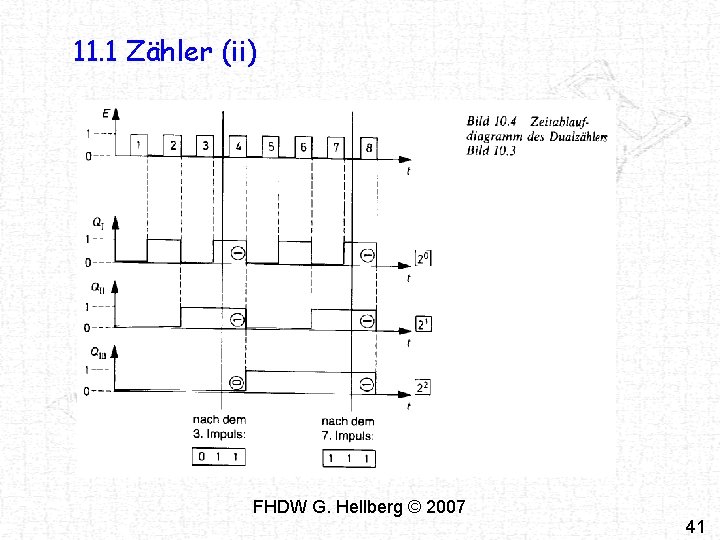

11. 1 Zähler (ii) FHDW G. Hellberg © 2007 41

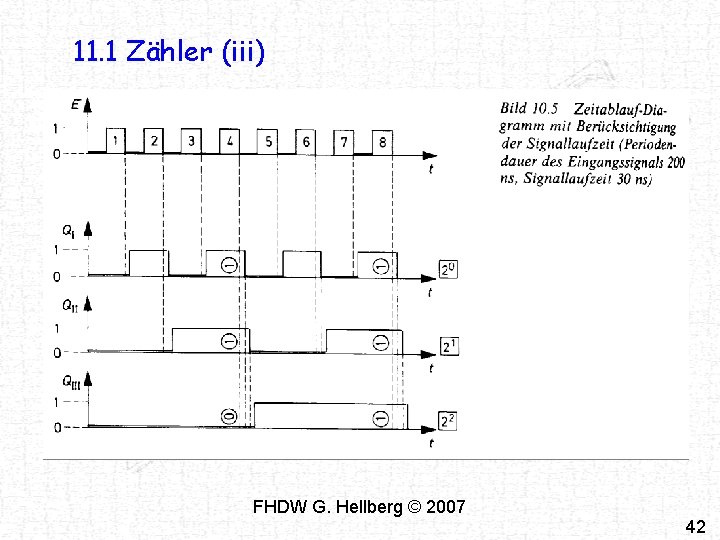

11. 1 Zähler (iii) FHDW G. Hellberg © 2007 42

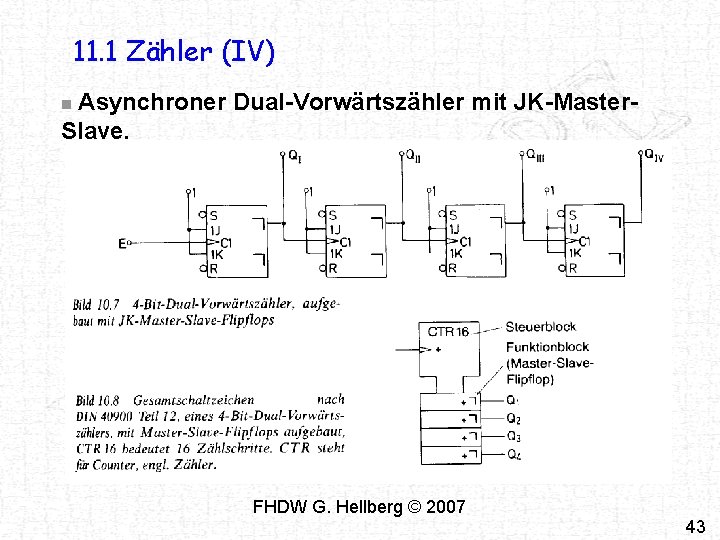

11. 1 Zähler (IV) Asynchroner Dual-Vorwärtszähler mit JK-Master. Slave. n FHDW G. Hellberg © 2007 43

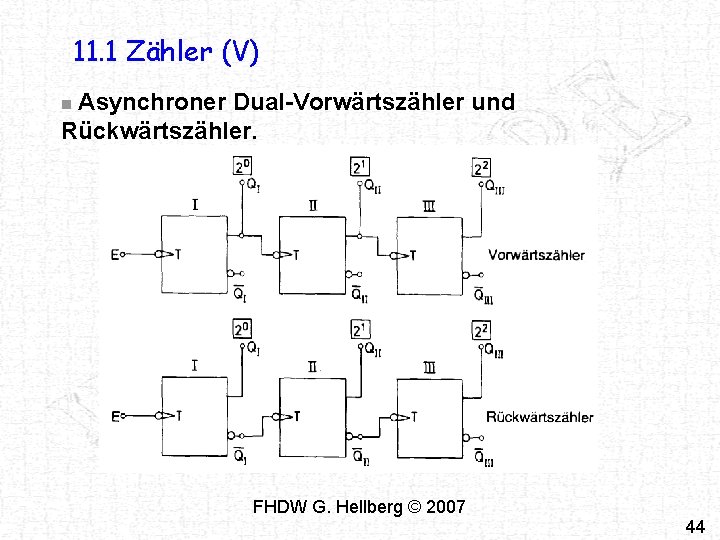

11. 1 Zähler (V) Asynchroner Dual-Vorwärtszähler und Rückwärtszähler. n FHDW G. Hellberg © 2007 44

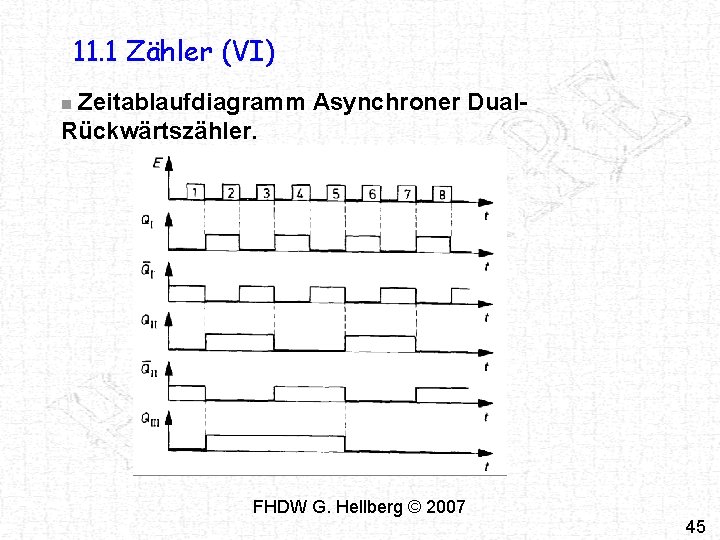

11. 1 Zähler (VI) Zeitablaufdiagramm Asynchroner Dual. Rückwärtszähler. n FHDW G. Hellberg © 2007 45

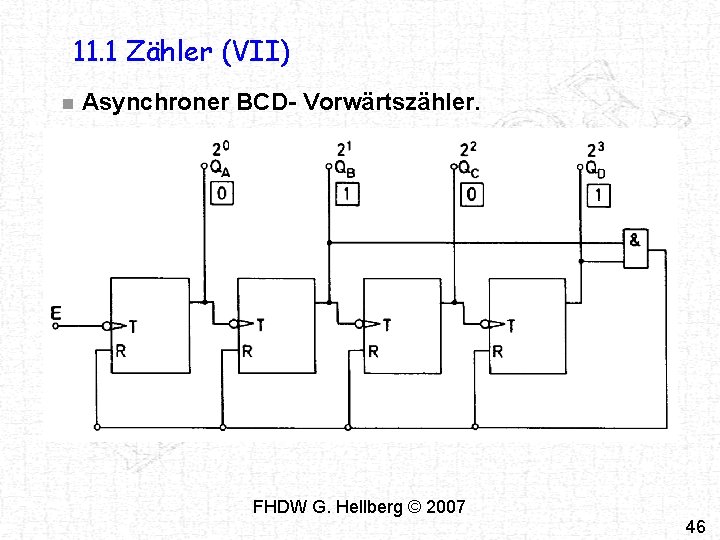

11. 1 Zähler (VII) n Asynchroner BCD- Vorwärtszähler. FHDW G. Hellberg © 2007 46

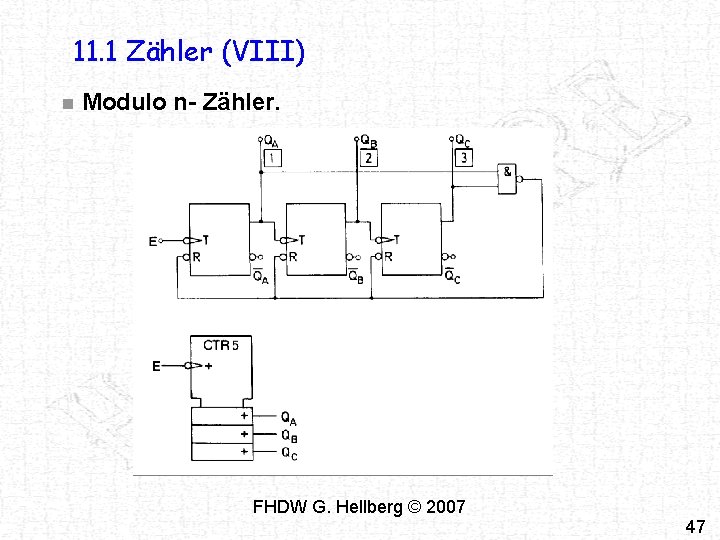

11. 1 Zähler (VIII) n Modulo n- Zähler. FHDW G. Hellberg © 2007 47

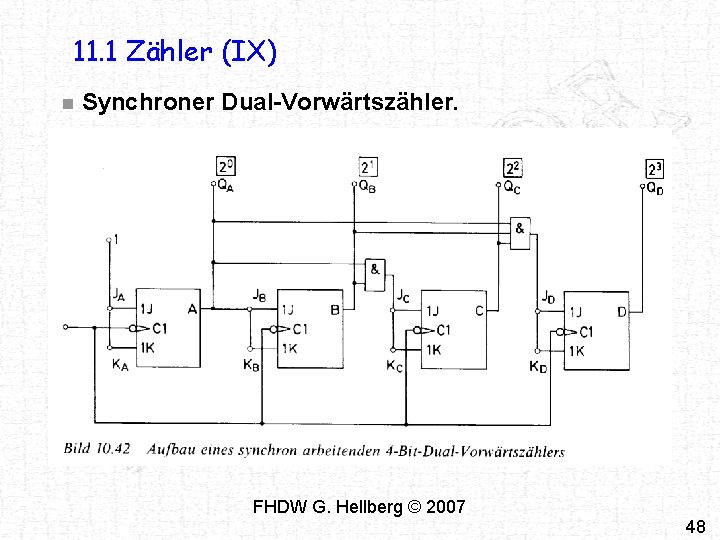

11. 1 Zähler (IX) n Synchroner Dual-Vorwärtszähler. FHDW G. Hellberg © 2007 48

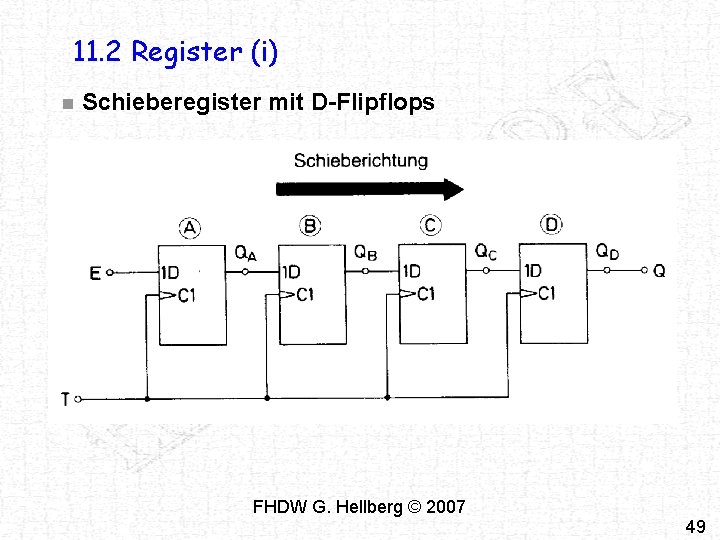

11. 2 Register (i) n Schieberegister mit D-Flipflops FHDW G. Hellberg © 2007 49

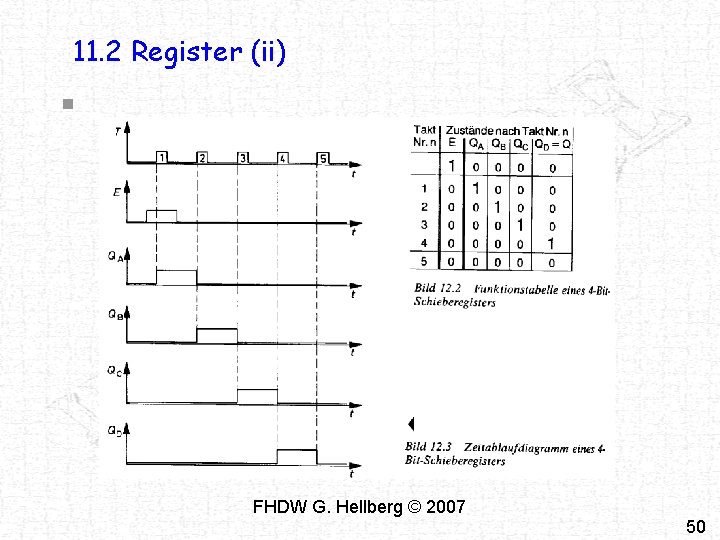

11. 2 Register (ii) n FHDW G. Hellberg © 2007 50

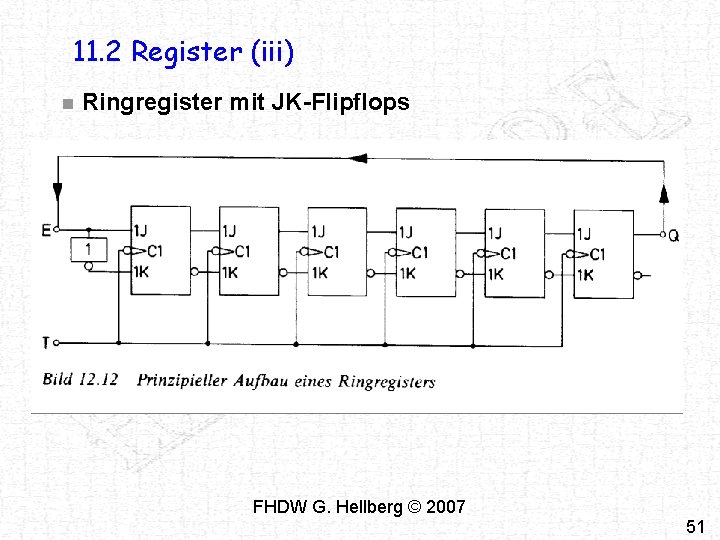

11. 2 Register (iii) n Ringregister mit JK-Flipflops FHDW G. Hellberg © 2007 51

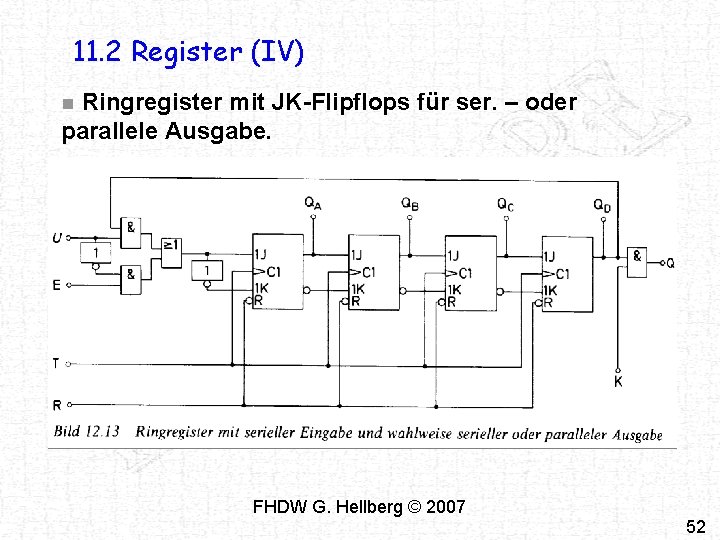

11. 2 Register (IV) Ringregister mit JK-Flipflops für ser. – oder parallele Ausgabe. n FHDW G. Hellberg © 2007 52

53

- Slides: 53