Lecture on FlipFlops LevelSensitive FlipFlop Levelsensitive flipflop also

- Slides: 14

Lecture on Flip-Flops

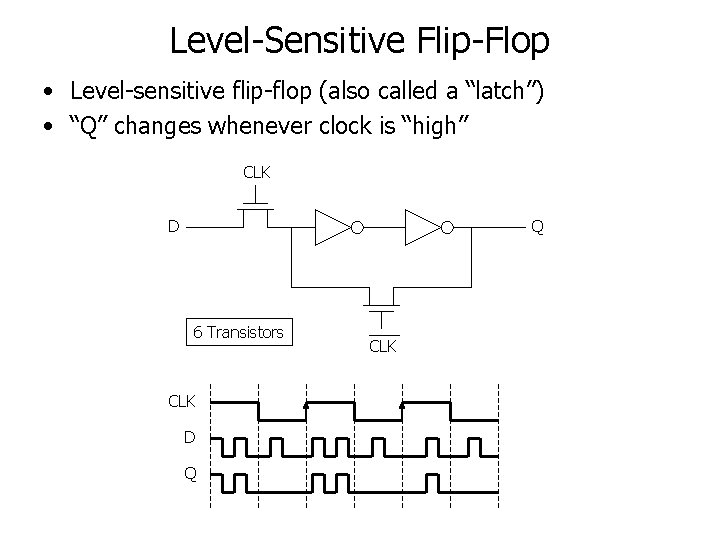

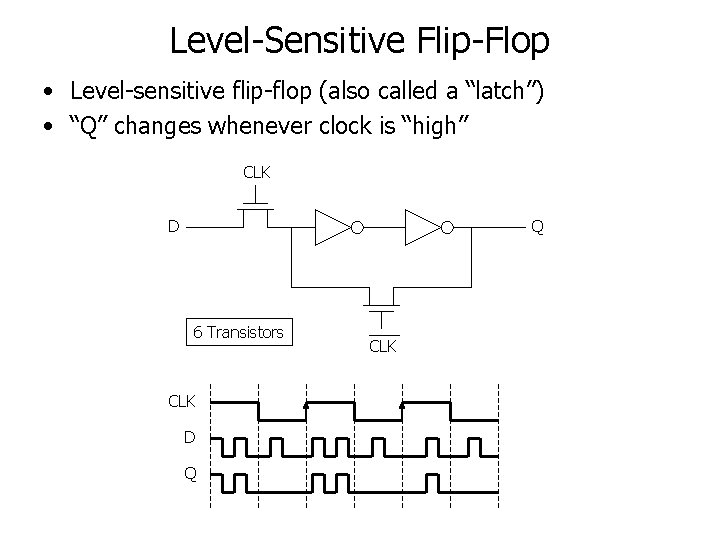

Level-Sensitive Flip-Flop • Level-sensitive flip-flop (also called a “latch”) • “Q” changes whenever clock is “high” CLK D Q 6 Transistors CLK D Q CLK

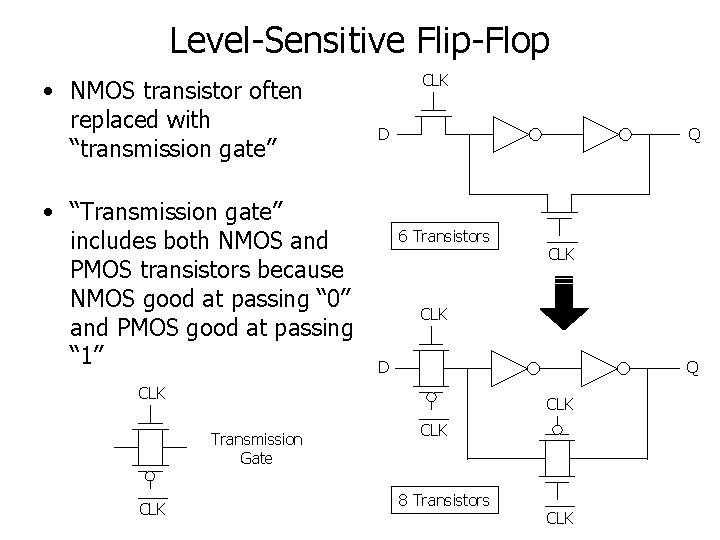

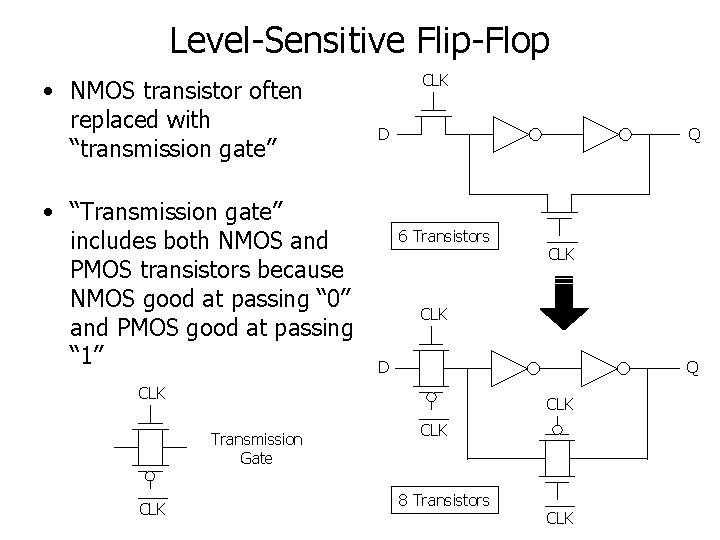

Level-Sensitive Flip-Flop • NMOS transistor often replaced with “transmission gate” • “Transmission gate” includes both NMOS and PMOS transistors because NMOS good at passing “ 0” and PMOS good at passing “ 1” CLK D Q 6 Transistors CLK D Q CLK Transmission Gate CLK CLK 8 Transistors CLK

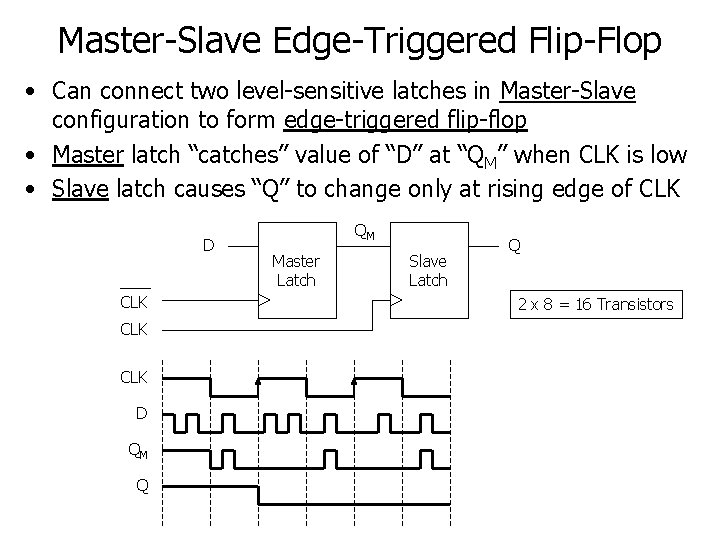

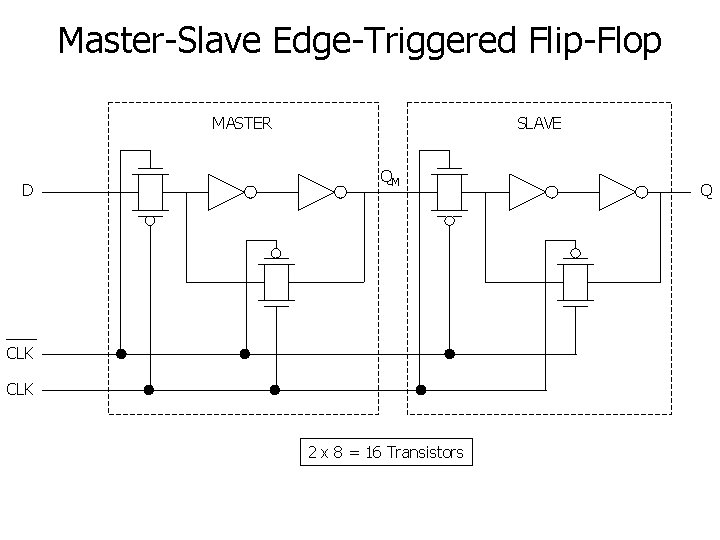

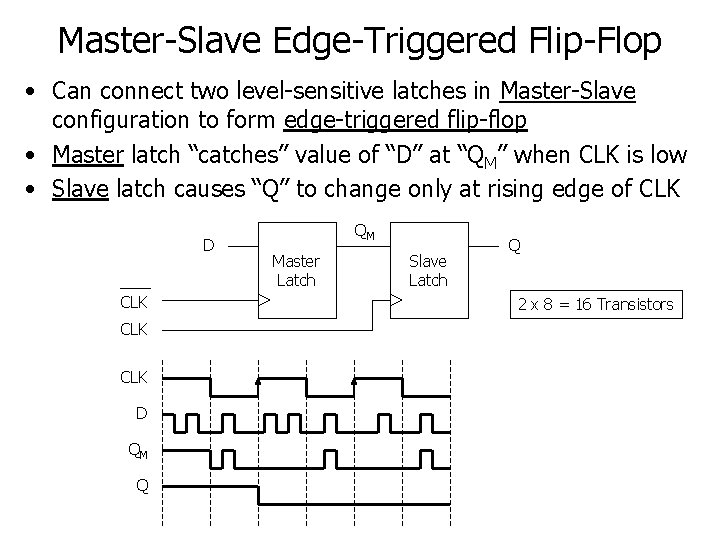

Master-Slave Edge-Triggered Flip-Flop • Can connect two level-sensitive latches in Master-Slave configuration to form edge-triggered flip-flop • Master latch “catches” value of “D” at “QM” when CLK is low • Slave latch causes “Q” to change only at rising edge of CLK D CLK CLK D QM Q QM Master Latch Slave Latch Q 2 x 8 = 16 Transistors

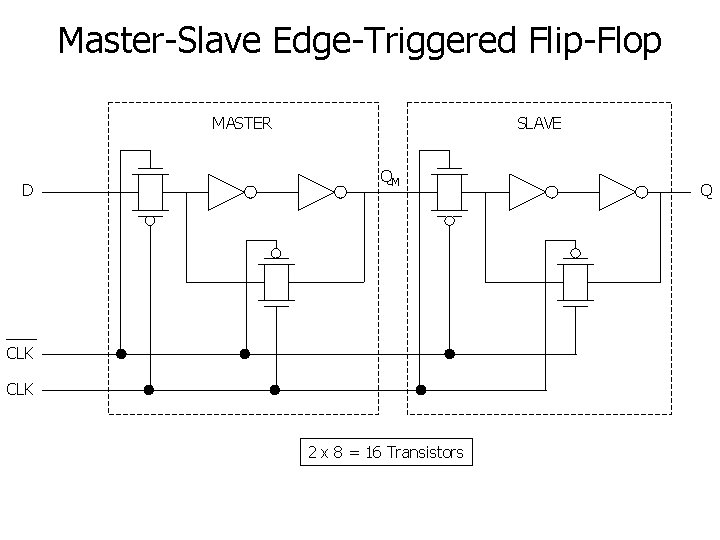

Master-Slave Edge-Triggered Flip-Flop MASTER D SLAVE QM CLK 2 x 8 = 16 Transistors Q

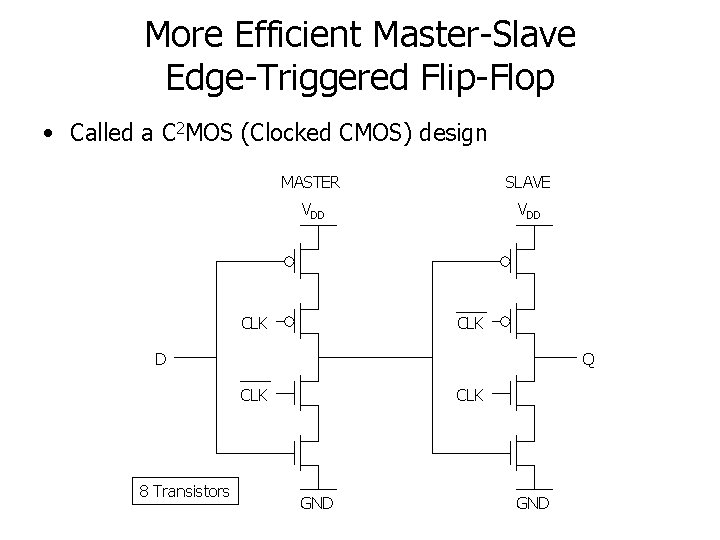

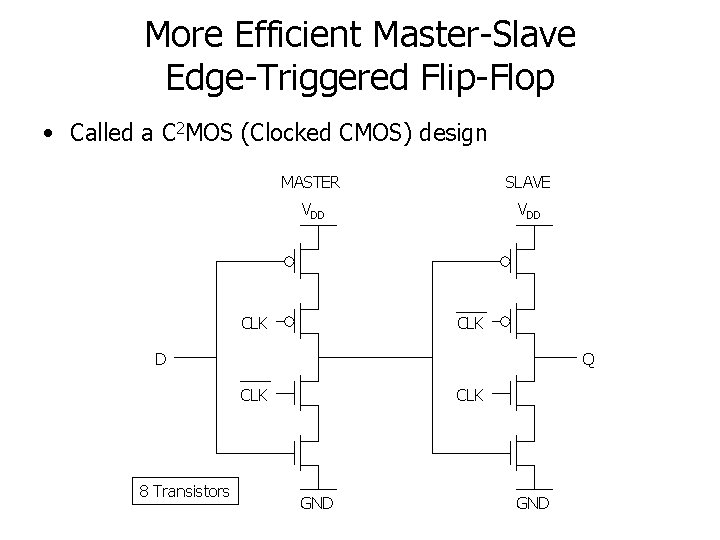

More Efficient Master-Slave Edge-Triggered Flip-Flop • Called a C 2 MOS (Clocked CMOS) design MASTER SLAVE VDD CLK D Q CLK 8 Transistors CLK GND

Using Logic Gates to Build Flip-Flops • From previous slides, you can see that it’s possible to build an edge-triggered flip-flop using just 8 transistors • In a conventional “Digital Logic” course, transistor-level flip-flop designs are not usually taught • Instead, flip-flop designs using “cross-coupled” logic gates are usually taught

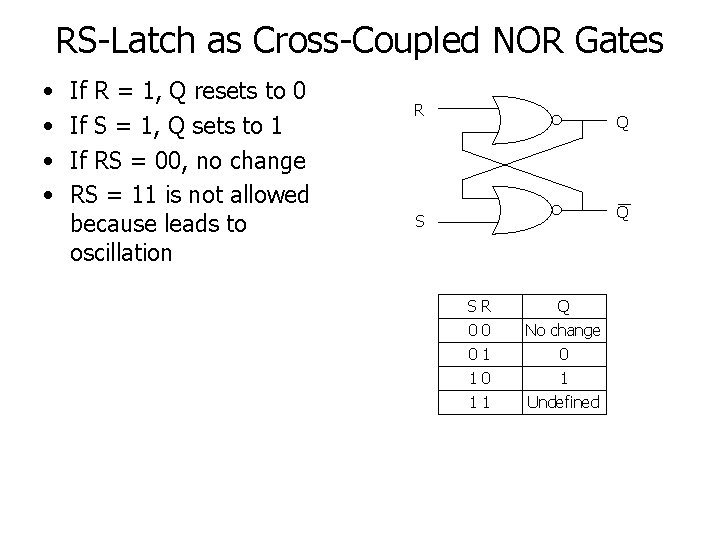

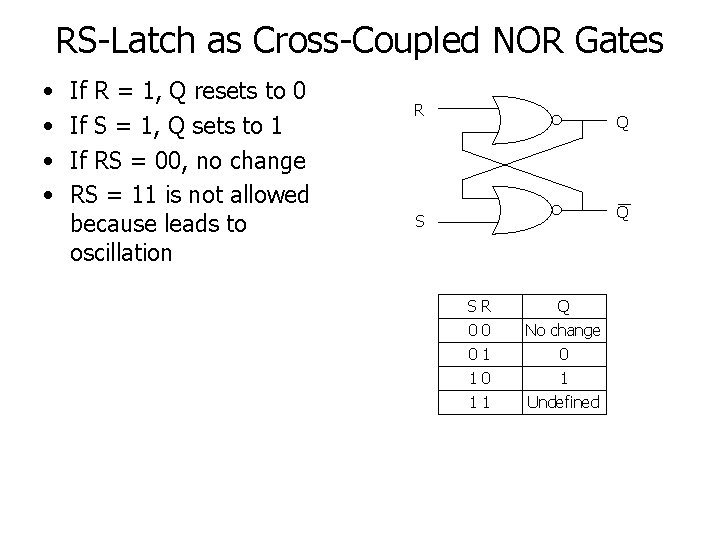

RS-Latch as Cross-Coupled NOR Gates • • If R = 1, Q resets to 0 If S = 1, Q sets to 1 If RS = 00, no change RS = 11 is not allowed because leads to oscillation R Q Q S SR 00 01 10 11 Q No change 0 1 Undefined

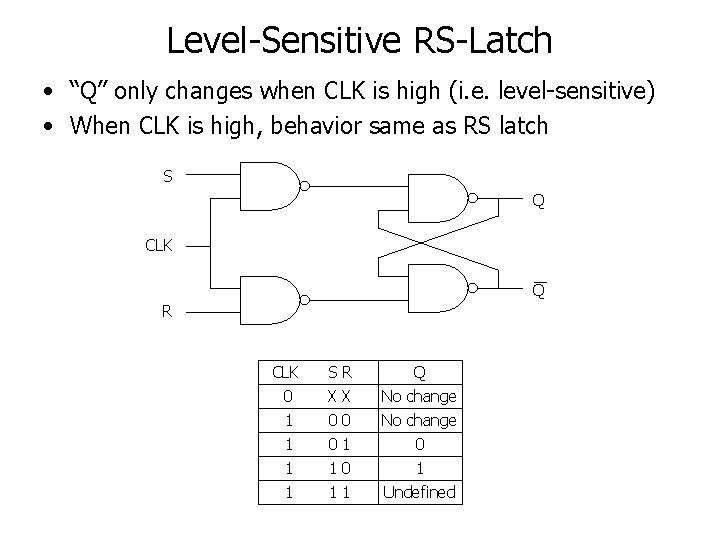

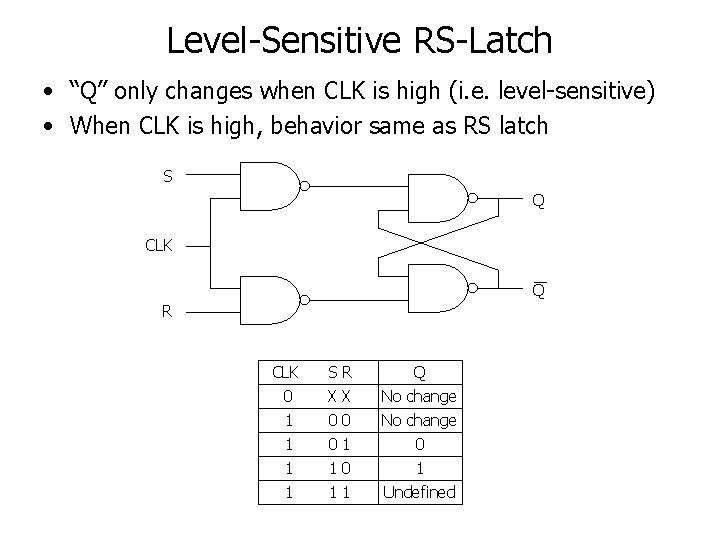

Level-Sensitive RS-Latch • “Q” only changes when CLK is high (i. e. level-sensitive) • When CLK is high, behavior same as RS latch S Q CLK Q R CLK 0 1 1 SR XX 00 01 10 11 Q No change 0 1 Undefined

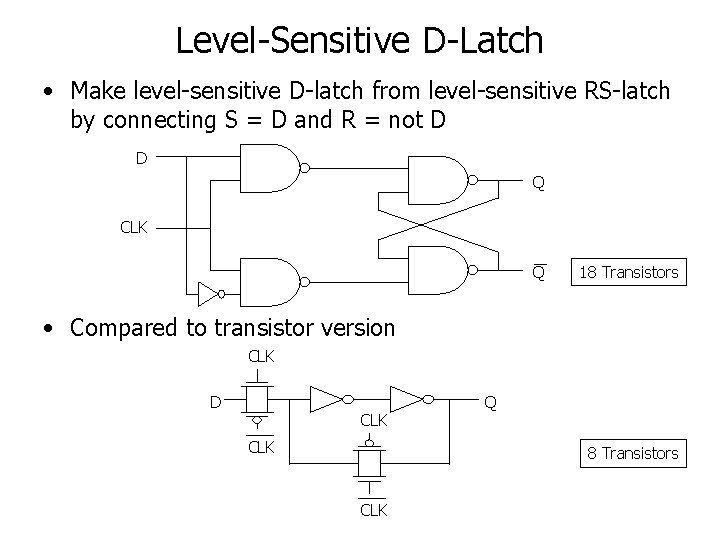

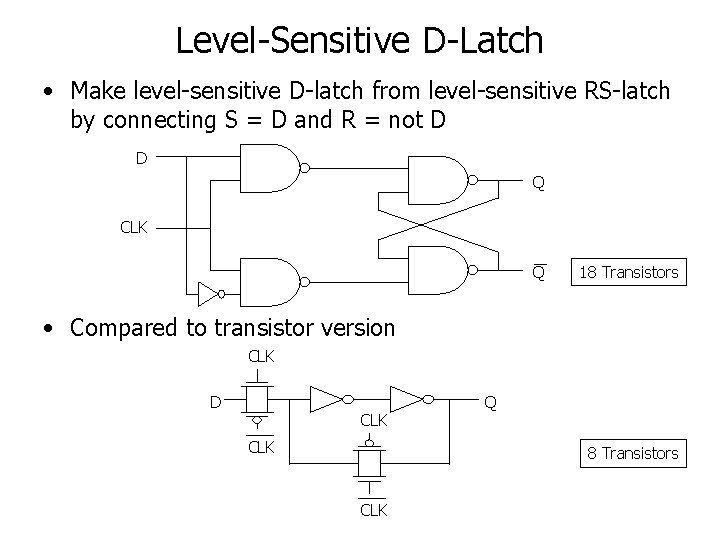

Level-Sensitive D-Latch • Make level-sensitive D-latch from level-sensitive RS-latch by connecting S = D and R = not D D Q CLK Q 18 Transistors • Compared to transistor version CLK D CLK Q 8 Transistors CLK

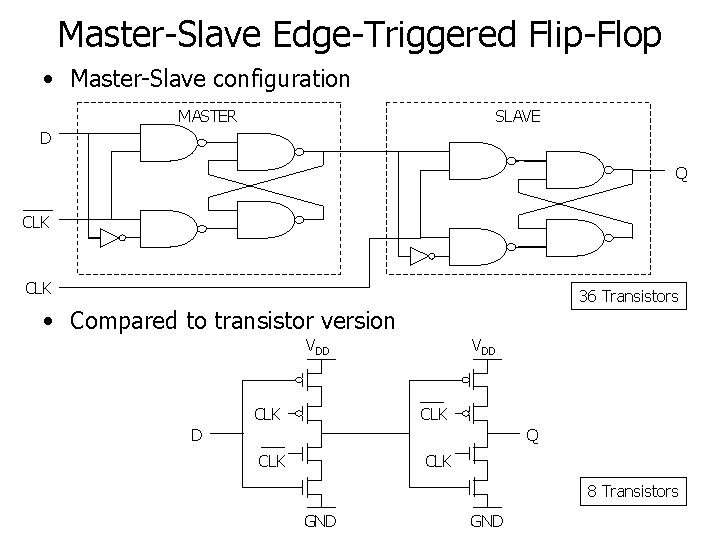

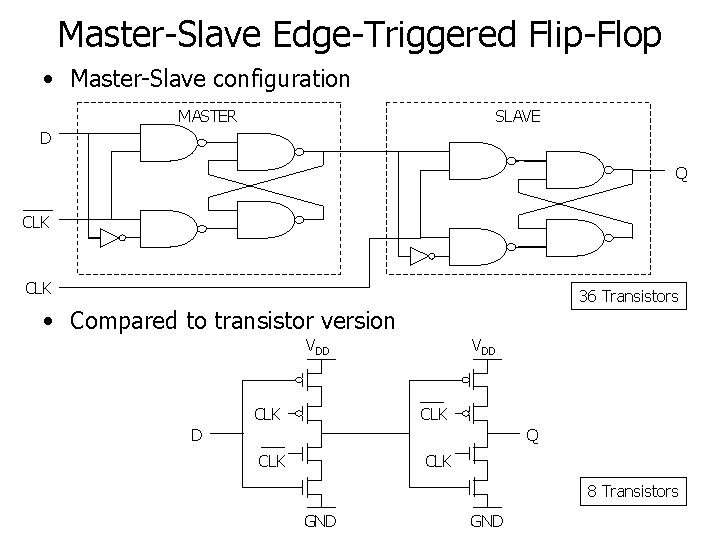

Master-Slave Edge-Triggered Flip-Flop • Master-Slave configuration MASTER SLAVE D Q CLK 36 Transistors • Compared to transistor version VDD CLK D Q CLK 8 Transistors GND

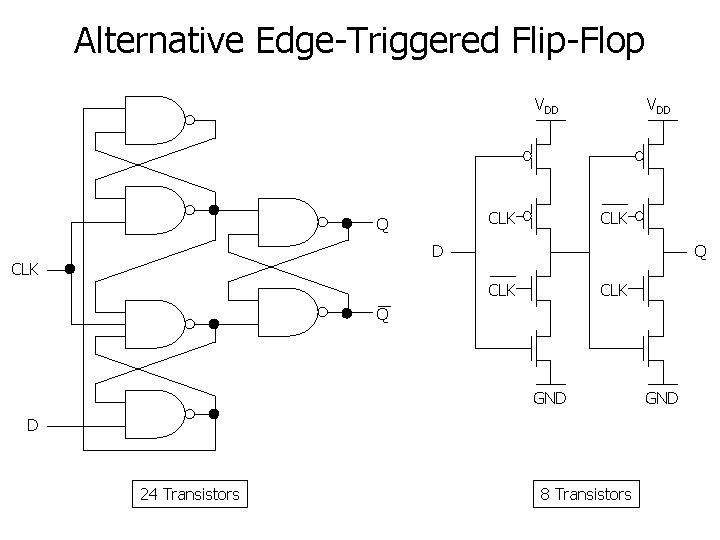

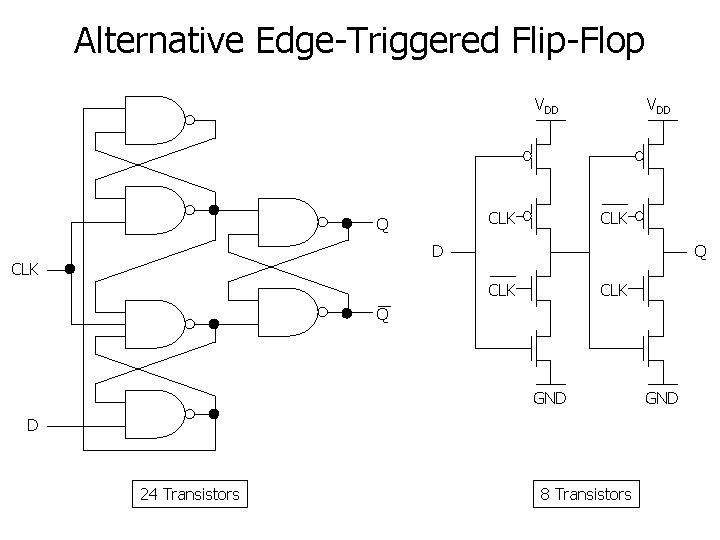

Alternative Edge-Triggered Flip-Flop VDD CLK Q CLK Q GND D 24 Transistors 8 Transistors GND

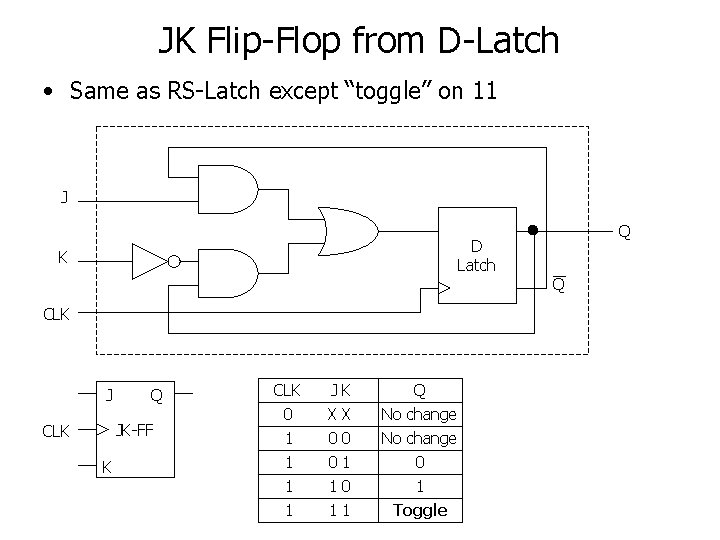

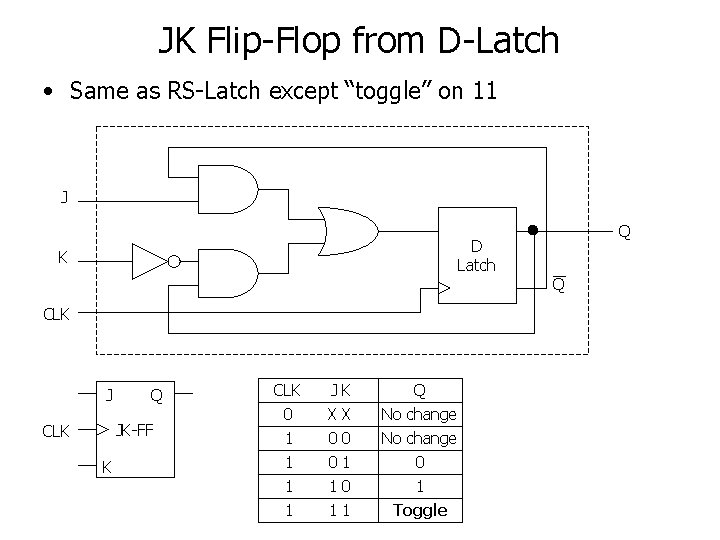

JK Flip-Flop from D-Latch • Same as RS-Latch except “toggle” on 11 J D Latch K CLK J Q JK-FF CLK K CLK 0 1 1 JK XX 00 01 10 11 Q No change 0 1 Toggle Q Q

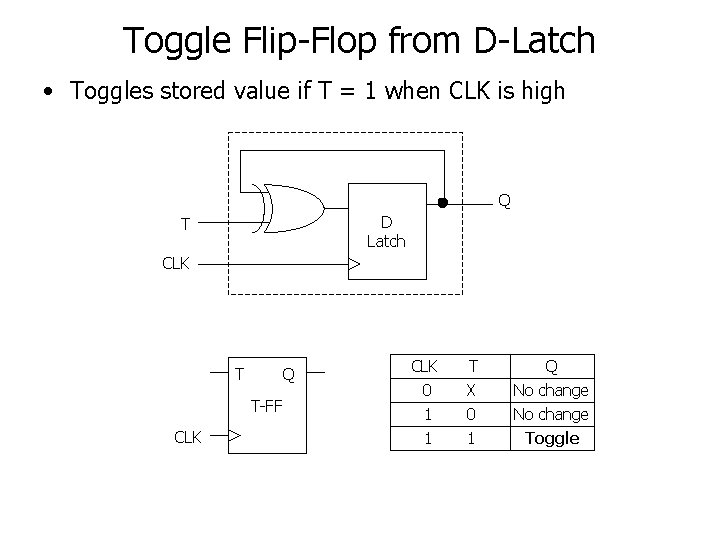

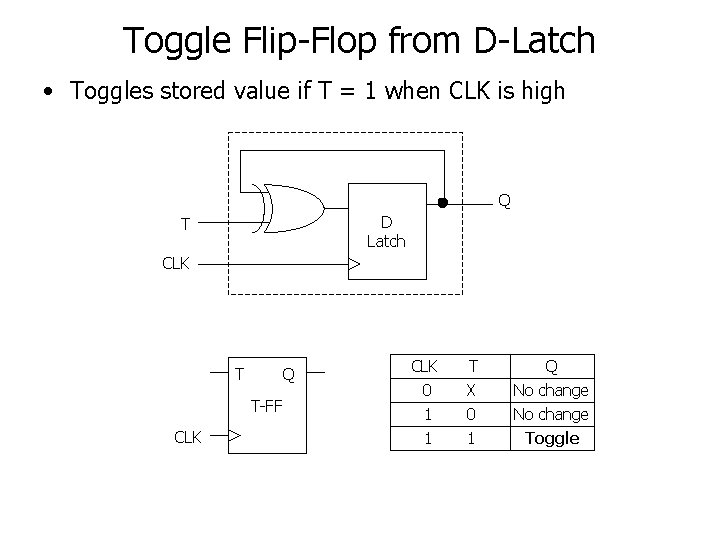

Toggle Flip-Flop from D-Latch • Toggles stored value if T = 1 when CLK is high Q D Latch T CLK T Q T-FF CLK 0 1 1 T X 0 1 Q No change Toggle