FLIPFLOP Rangkaian Flip Flop Rangkaian flipflop adalah suatu

- Slides: 16

FLIP-FLOP

Rangkaian Flip Flop Rangkaian flip-flop adalah suatu elemen logika bi-stabil yang mempunyai satu atau lebih input dan mempunyai dua output yang saling berlawanan (complementary), juga rangkaian ini biasa disebut rangkaian Mult ivibrator Bi stabil.

Fungsi Rangkaian flip-flop juga berfungsi untuk merubah keadaan dari satu posisi ke posisi lain, yaitu dari satu keadaan stabil pertama ke keadaan stabil kedua. Bilamana flip-flop ini diberi sinyal dari luar atau biasa disebut sinyal trigger, ini membuat flip-flop berubah keadaannya.

Dalam pemakaiannya rangkaian flip-flop ini digunakan dalam komputer atau counter yang digunakan sebagai penyimpan data, penghitung biner dan memindah data (shift register). Dengan demikian flip-flop merupakan dasar dari pada rangkaian digital. Flip Flop yang merupakan penggabungan rangkaian logika terdiri dari gerbang AND, OR dan NOT, dapat berupa : a. Flip-Flop RS b. Flip-Flop RS yang Berdetak c. Flip-Flop D d. Flip-Flop JK

Flip-Flop RS (RESET FLIP-FLOP) Flip-flop RS disebut juga Penahan Transparan (Transparent Latches), karena keluaran flip-flop langsung menyebabkan terjadinya perubahan terhadap masukannya. Perubahan yang cepat disebabkan karena flip-flop SR langsung menanggapi perubahan sinyal pada bagian masukan sehingga keluaran Q akan langsung berubah sejalan dengan perubahan masukan. Keadaan sinyal masukan akan diingat dengan cara menahan sinyal masukkannya ke dalam rangkaian logikanya.

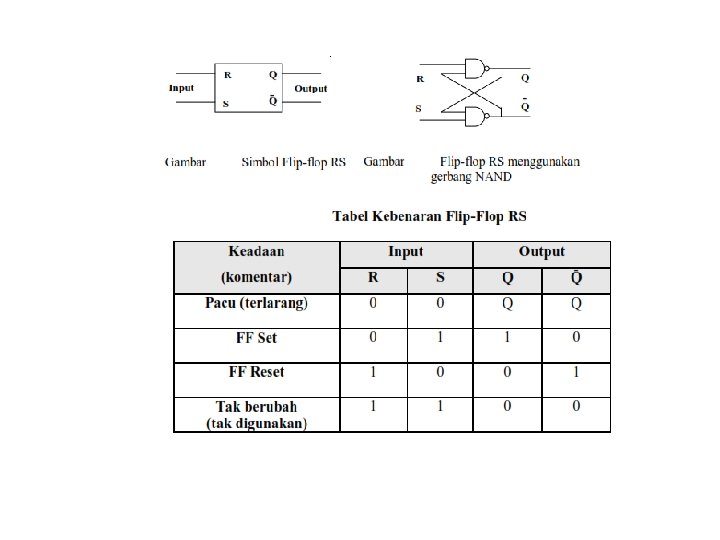

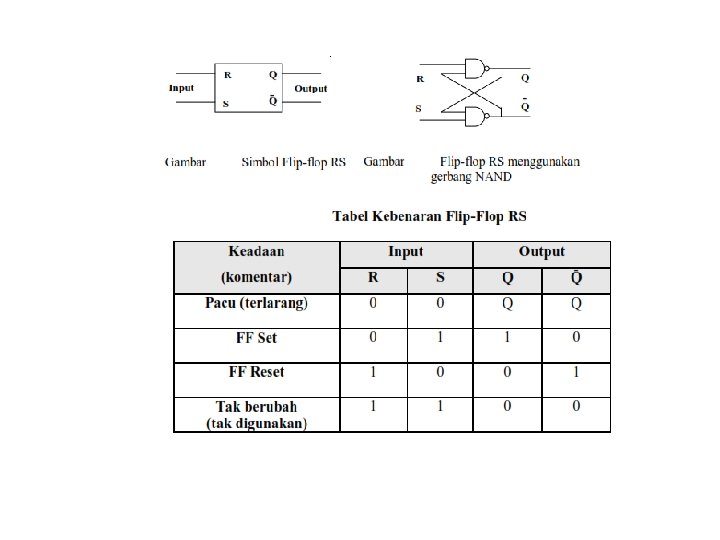

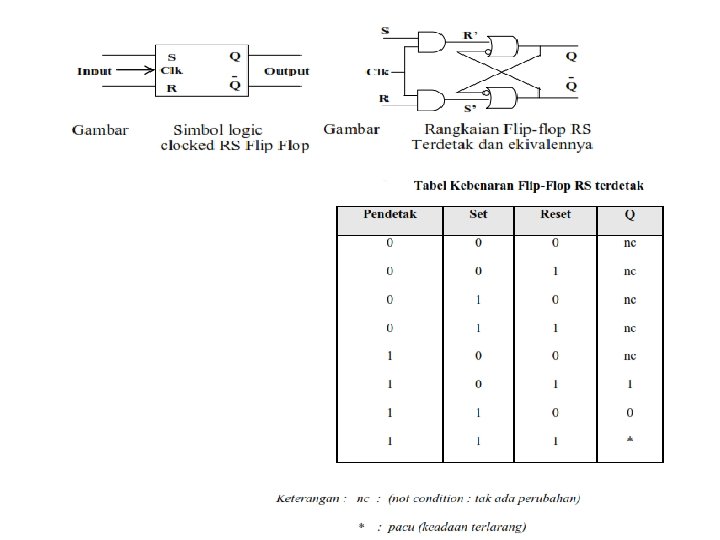

Flip-Flop RS mempunyai dua buah input yang diberi nama atau lebel SET (S) dan RESET (R) dan dua buah output yang diberi nama Q dan Q. Pada gambar di bawah memperlihatkan simbol Flip. Flop RS yang memiliki dua buah output yang saling berlawanan, tidak seperti gerbang logika yang mempunyai satu output. Output Q dinamakan output normal dan yang satunya merupakan kebalikannya dan ditulis Q yang berarti complement/berbalikan dengan output normal. Jika Q = 1 maka Q = 0 dan sebaliknya jika Q = 0 maka Q = 1.

Sebuah flip-flop RS yang terbuat dari gerbang logika NAND (NOT AND) sering disebut sebagai penahan NAND (NAND Lacth. Penahan NAND prinsip kerjanya sama dengan penahan NOR. Perbedaannya terletak pada keadaan level atau tingkat logikanya. Masukanmasukan SET dan RESET dari penahan NOR bekerja dari keadaan 0 (rendah) menjadi 1 (tinggi), sewaktu mengubah keadaan, sedangkan penahan NAND sebaliknya. Masukan-masukan SET dan RESET dari penahan NAND bekerja dari keadaan 1 (tinggi) menjadi 0 (rendah), sewaktu mengubah keadaan. Tetapi sekali lagi, prinsip kerja keduanya sama.

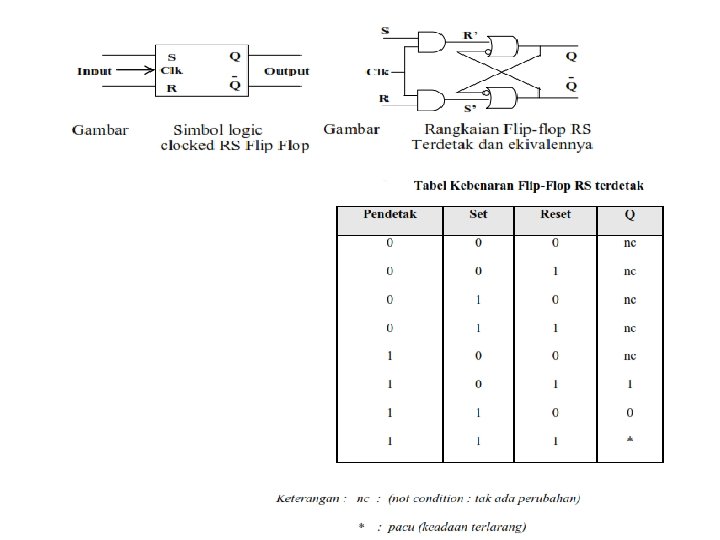

Flip-Flop RS Terdetak Flip-flop RS yang telah kita pelajari tersebut mempunyai penerapan yang terbatas, karena hanya mempunyai dua masukan yang harus dikendalikan secara silih berganti. Sebagai contoh penahan NOR, untuk mengaktifkan penahan NOR masukan SET harus diberi sinyal 1, kemudian Q akan 1. Untuk memadamkan keluaran Q dari penahan NOR masukan RESET harus diberi sinyal 1, maka keluaran Q akan 0. Masukan SET dan RESET harus silih berganti. Tidak diperkenankan bekerja secara sepihak terus-menerus dan juga tidak dapat bekerja secara bersama-sama atau berada dalam keadaan terlarang atau pacu. Maka pengoperasian Flip-Flop RS tanpa sinyal pendetak disebut tak serempak atau asinkron.

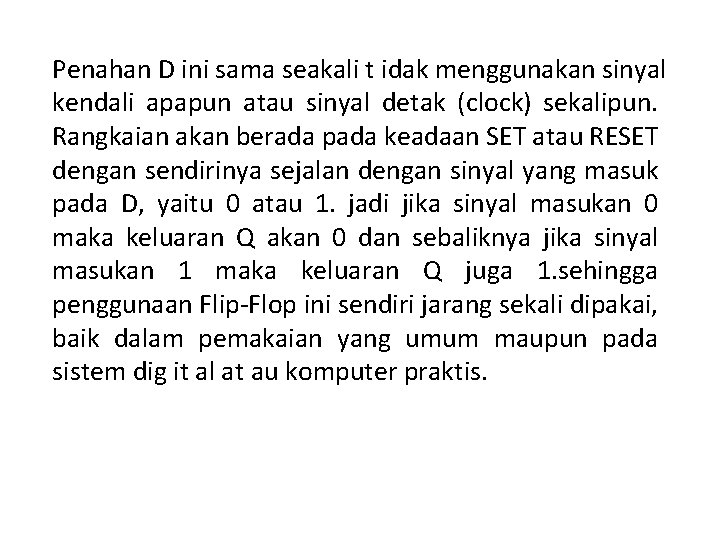

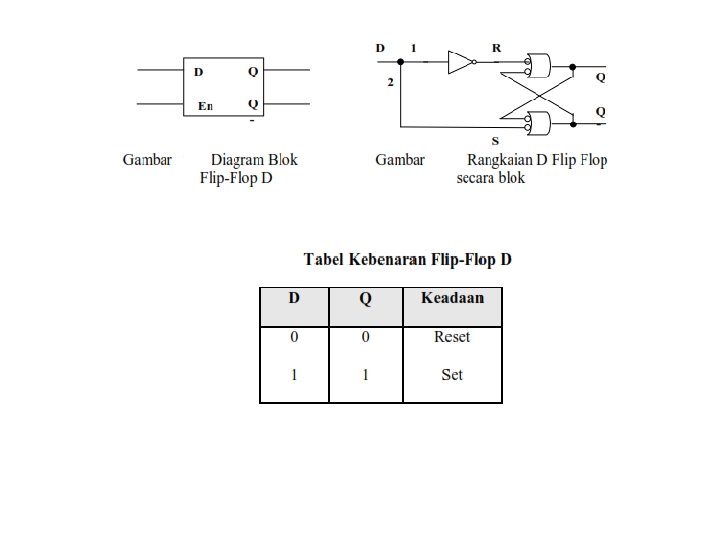

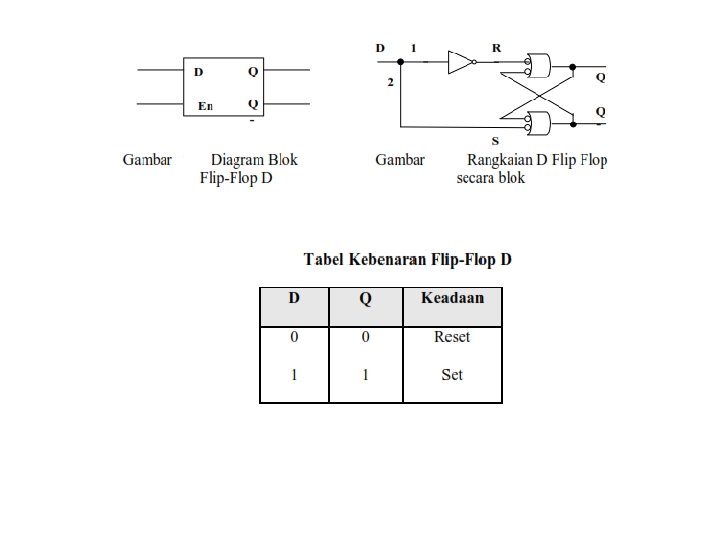

Flip-Flop D (Data Flip-Flop atau Delayed Flip-Flop) Penahan D yang paling sederhana dapat dibangun dengan menggunakan gerbang logika yang membentuk ekivalen penahan NAND (lihat Flip-flop RS pada pembahasan sebelumnya). Sedangkan prinsip kerja penahan D jenis ini juga tak kalah sederhana. Isyarat-isyarat digital yang masuk pada D akan dibagi menjadi dua jalur. Jalur pertama (1) melewati gerbang Inverter kemudian melewati gerbang NAND (atau OR dengan kedua masukan dibalik) yang berada dibagian atas, yaitu RESET. Sedangkan jalur yang kedua (2) langsung menuju kegerbang NAND (atau ekivalen OR dengan kedua masukan dibalik) yang dibagian bawah, yaitu SET.

Jika masukan D adalah 0 (atau low atau rendah) maka gerbang NAND yang di atas (atau RESET) akan 0 dan gerbang logika NAND yang di bawah (atau SET) akan 1, maka keluaran Q akan 0. Flip-Flop dalam keadaan RESET. Tetapi jika masukan 1 (high = tinggi) maka gerbang logika NAND yang atas (RESET) akan 1 dan gerbang logika yang bawah (SET) akan 0, maka keluaran Q akan 1. Flip-Flop dalam keadaan SET.

Penahan D ini sama seakali t idak menggunakan sinyal kendali apapun atau sinyal detak (clock) sekalipun. Rangkaian akan berada pada keadaan SET atau RESET dengan sendirinya sejalan dengan sinyal yang masuk pada D, yaitu 0 atau 1. jadi jika sinyal masukan 0 maka keluaran Q akan 0 dan sebaliknya jika sinyal masukan 1 maka keluaran Q juga 1. sehingga penggunaan Flip-Flop ini sendiri jarang sekali dipakai, baik dalam pemakaian yang umum maupun pada sistem dig it al at au komputer praktis.

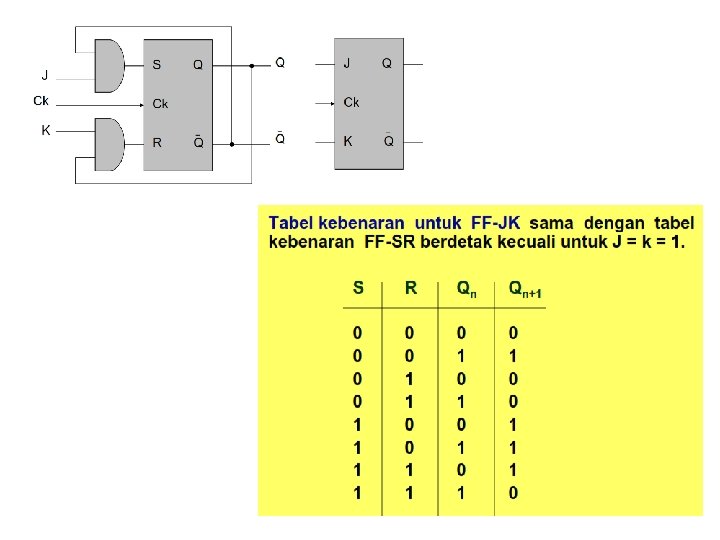

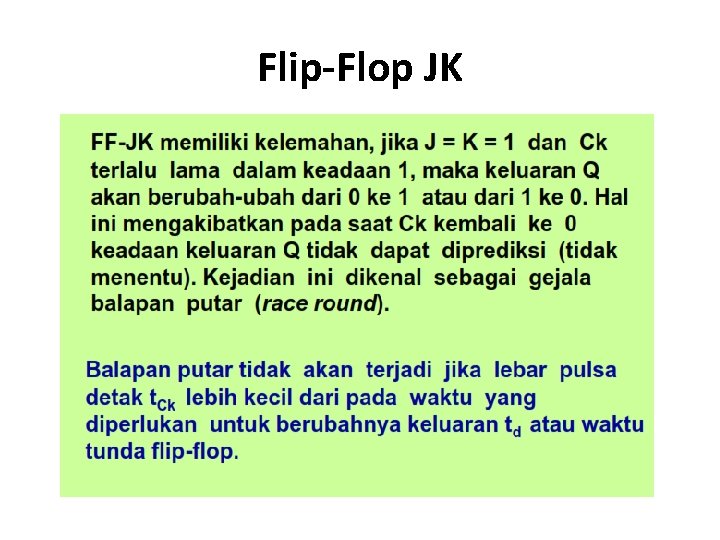

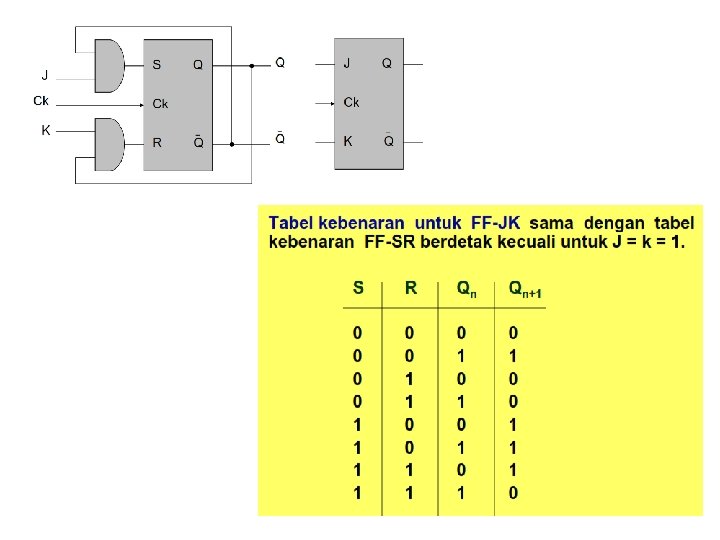

Flip-Flop JK