Diseo Microelectrnico I Captulo 6 Diseo de Circuitos

- Slides: 42

Diseño Microelectrónico I Capítulo 6: Diseño de Circuitos de LÓGICA SECUENCIAL Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

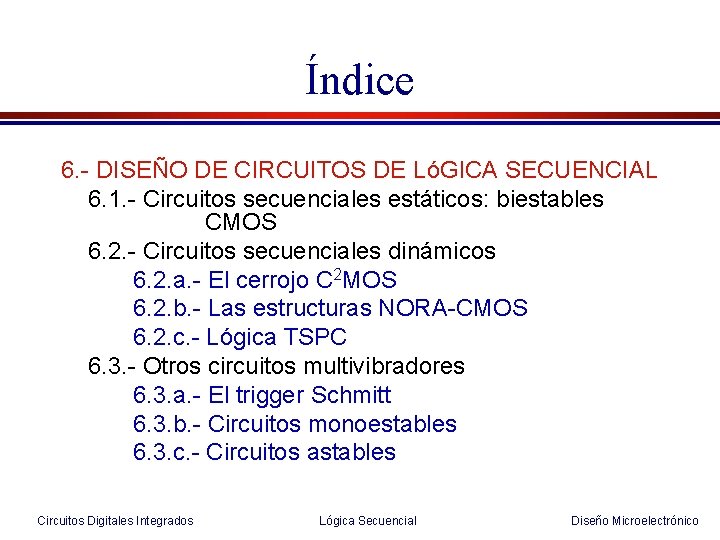

Índice 6. - DISEÑO DE CIRCUITOS DE LóGICA SECUENCIAL 6. 1. - Circuitos secuenciales estáticos: biestables CMOS 6. 2. - Circuitos secuenciales dinámicos 6. 2. a. - El cerrojo C 2 MOS 6. 2. b. - Las estructuras NORA-CMOS 6. 2. c. - Lógica TSPC 6. 3. - Otros circuitos multivibradores 6. 3. a. - El trigger Schmitt 6. 3. b. - Circuitos monoestables 6. 3. c. - Circuitos astables Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

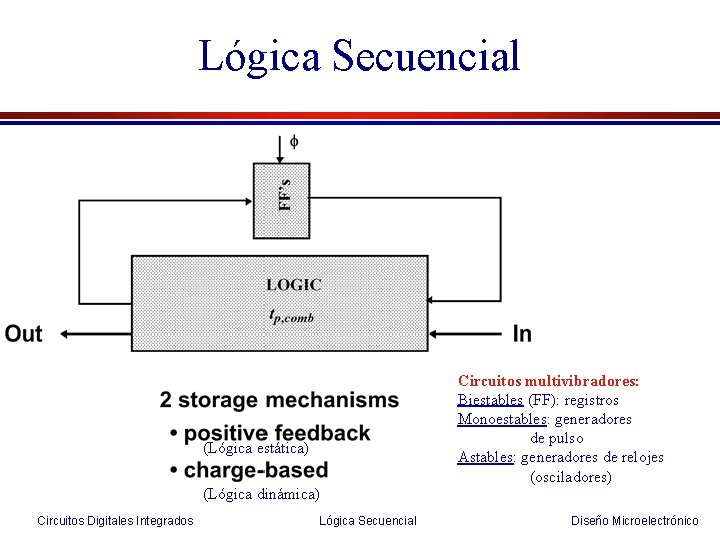

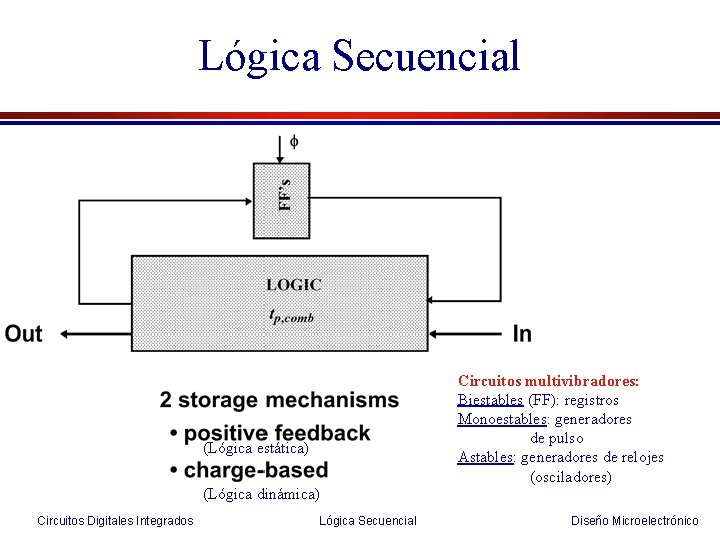

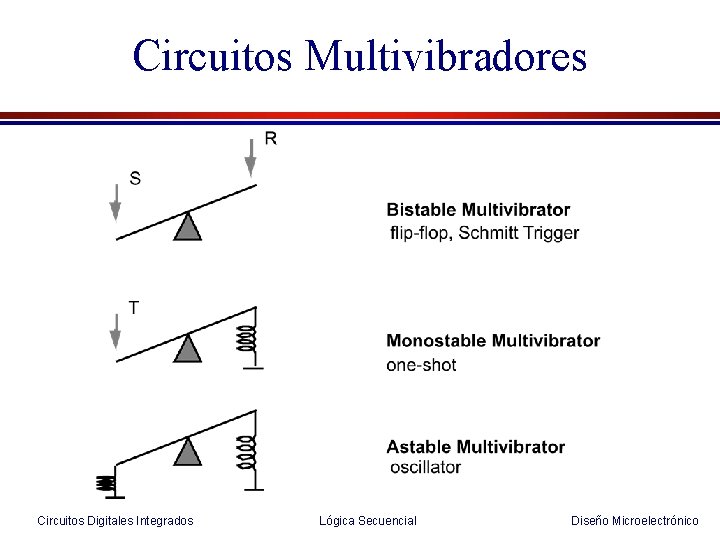

Lógica Secuencial (Lógica estática) (Lógica dinámica) Circuitos Digitales Integrados Lógica Secuencial Circuitos multivibradores: Biestables (FF): registros Monoestables: generadores de pulso Astables: generadores de relojes (osciladores) Diseño Microelectrónico

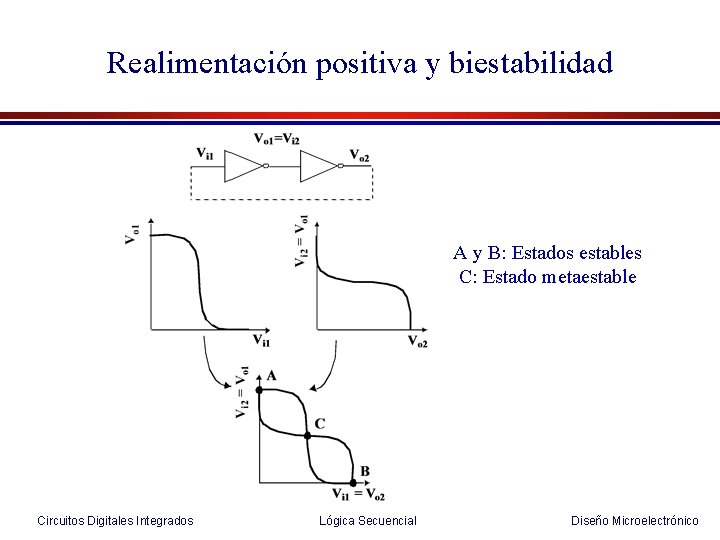

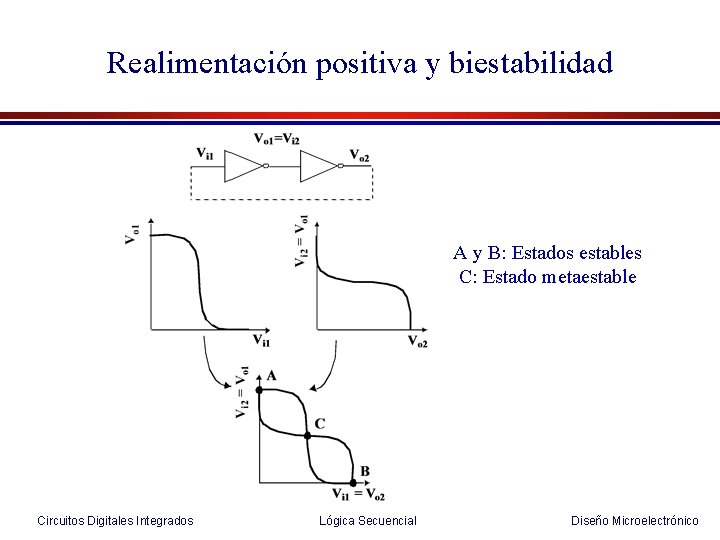

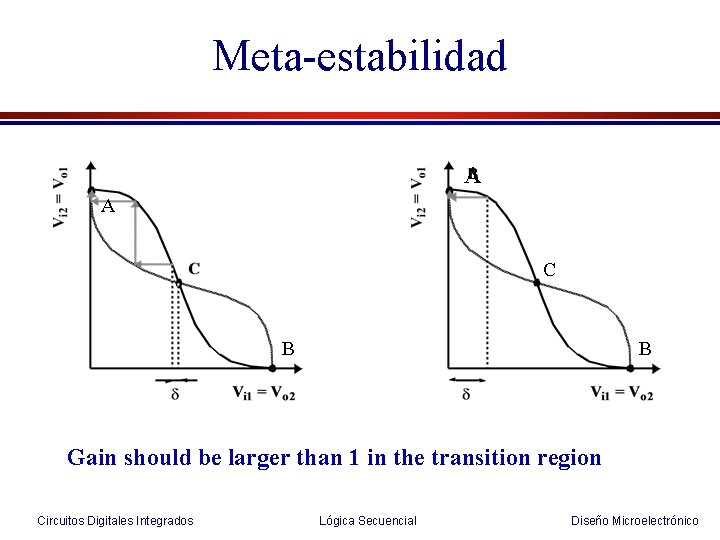

Realimentación positiva y biestabilidad A y B: Estados estables C: Estado metaestable Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

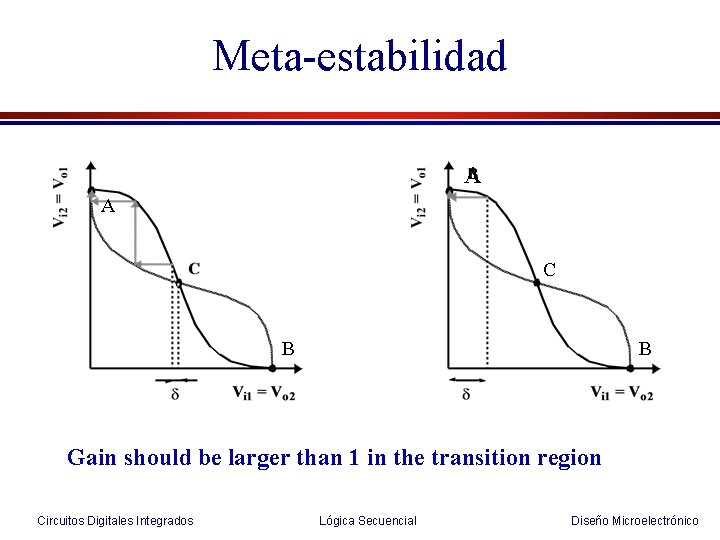

Meta-estabilidad A A C B B Gain should be larger than 1 in the transition region Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

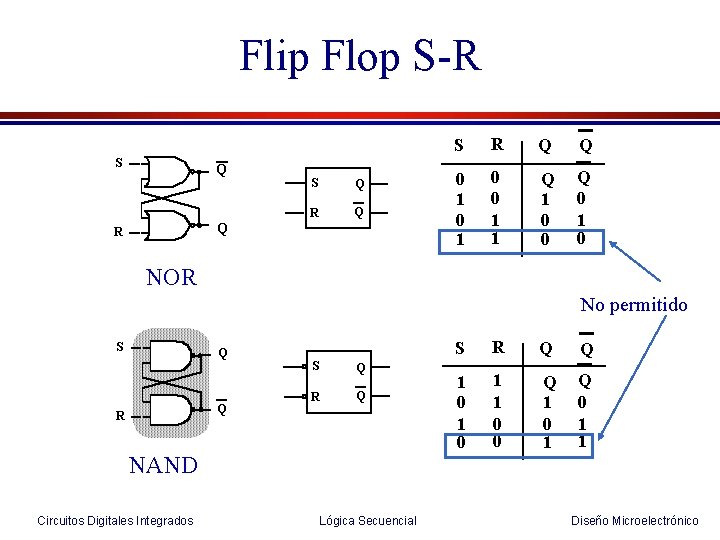

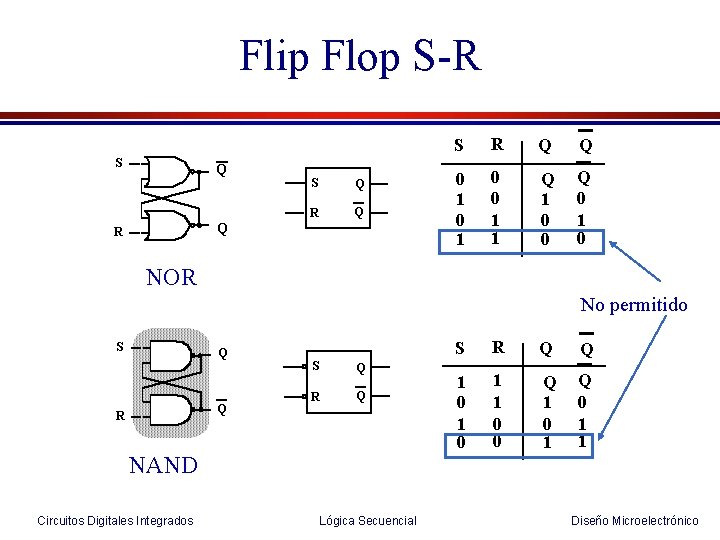

Flip Flop S-R S Q R Q Q R S R Q Q 0 1 0 0 1 1 Q 1 0 0 Q 0 1 0 NOR No permitido S Q Q R S Q R Q NAND Circuitos Digitales Integrados Lógica Secuencial S R Q Q 1 0 1 1 0 0 Q 1 0 1 Q 0 1 1 Diseño Microelectrónico

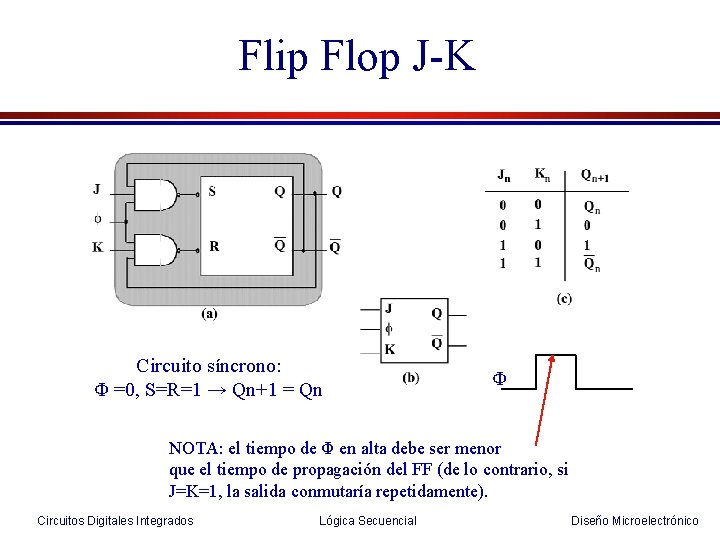

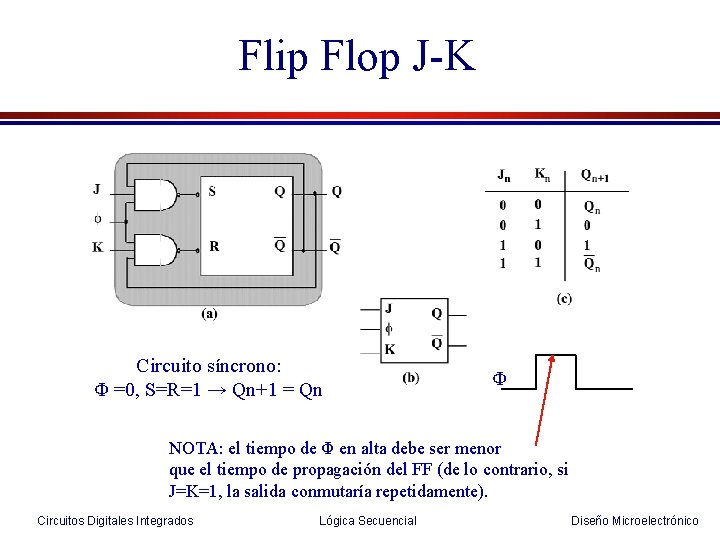

Flip Flop J-K Circuito síncrono: Φ =0, S=R=1 → Qn+1 = Qn Φ NOTA: el tiempo de Φ en alta debe ser menor que el tiempo de propagación del FF (de lo contrario, si J=K=1, la salida conmutaría repetidamente). Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

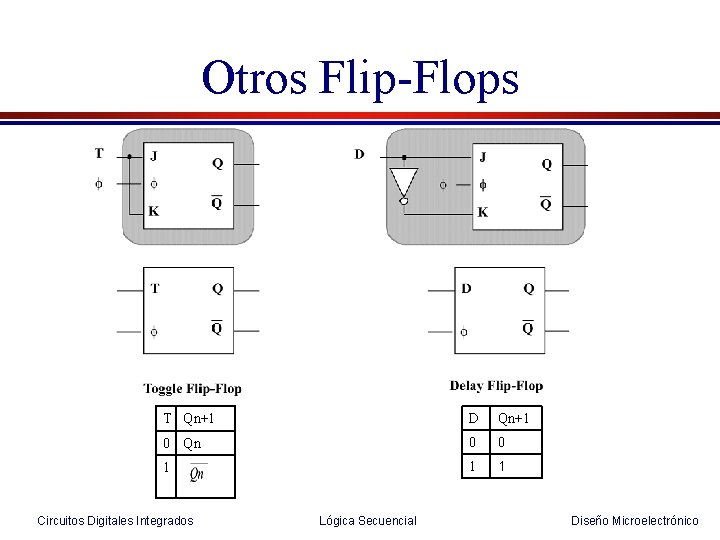

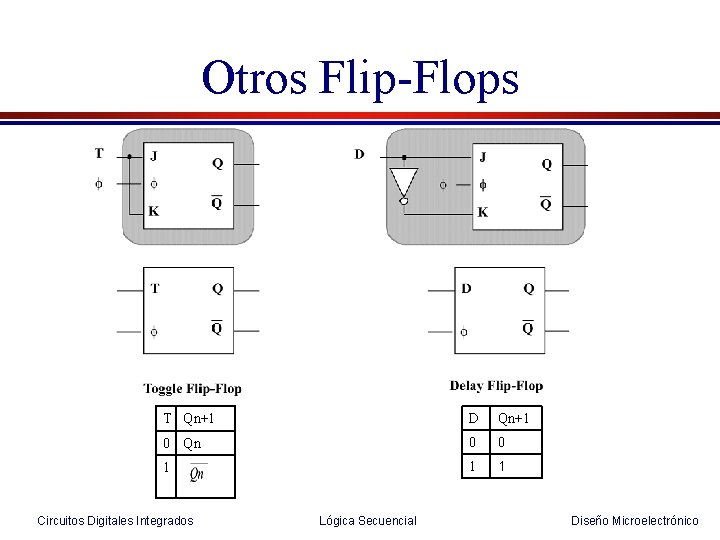

Otros Flip-Flops T Qn+1 D Qn+1 0 Qn 0 0 1 1 1 Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

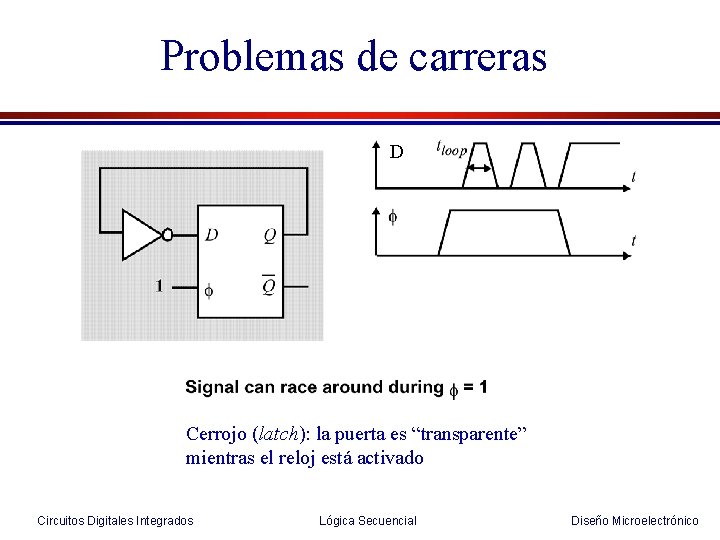

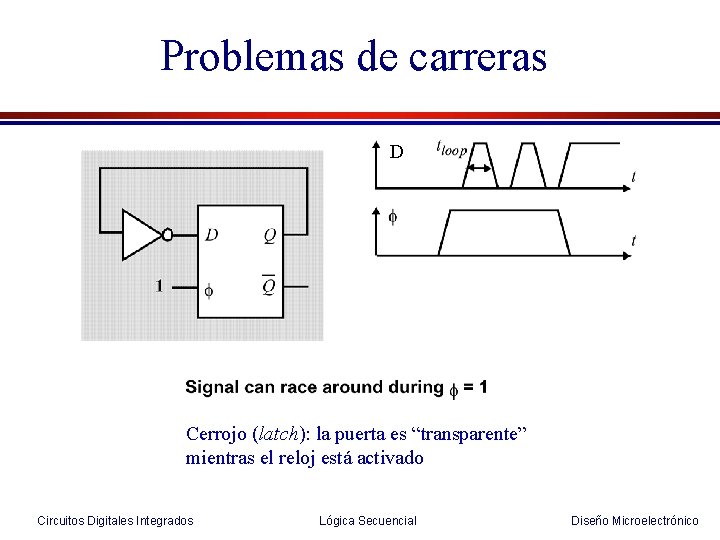

Problemas de carreras D Cerrojo (latch): la puerta es “transparente” mientras el reloj está activado Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

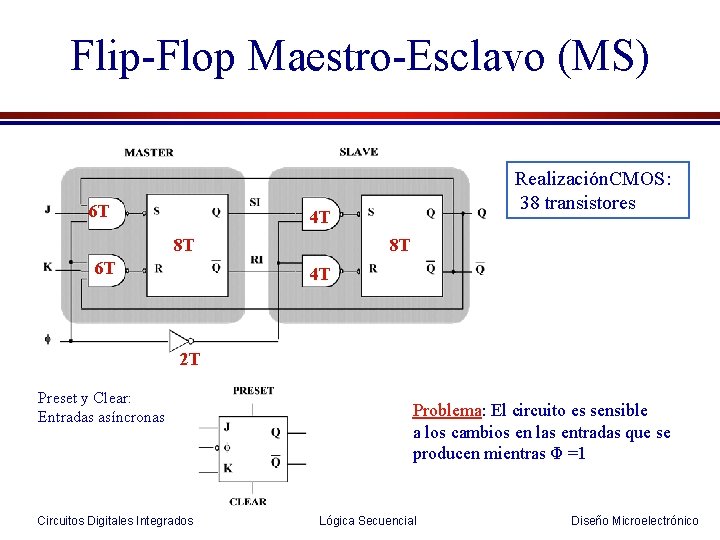

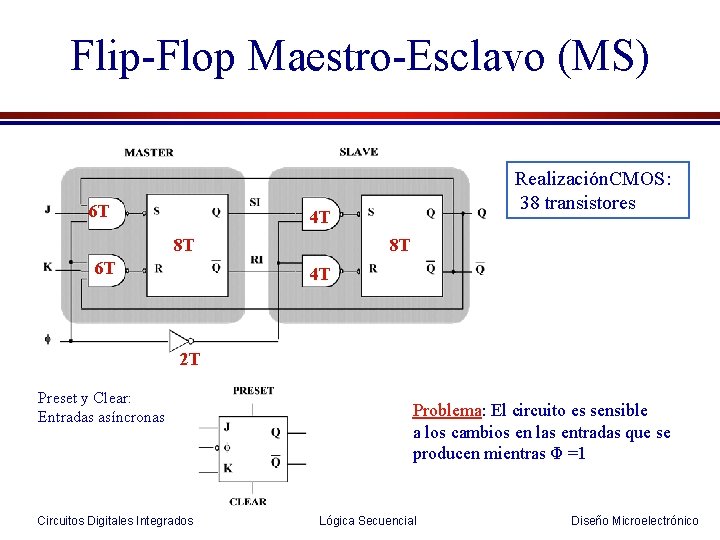

Flip-Flop Maestro-Esclavo (MS) 6 T Realización. CMOS: 38 transistores 4 T 8 T 6 T 8 T 4 T 2 T Preset y Clear: Entradas asíncronas Circuitos Digitales Integrados Problema: El circuito es sensible a los cambios en las entradas que se producen mientras Φ =1 Lógica Secuencial Diseño Microelectrónico

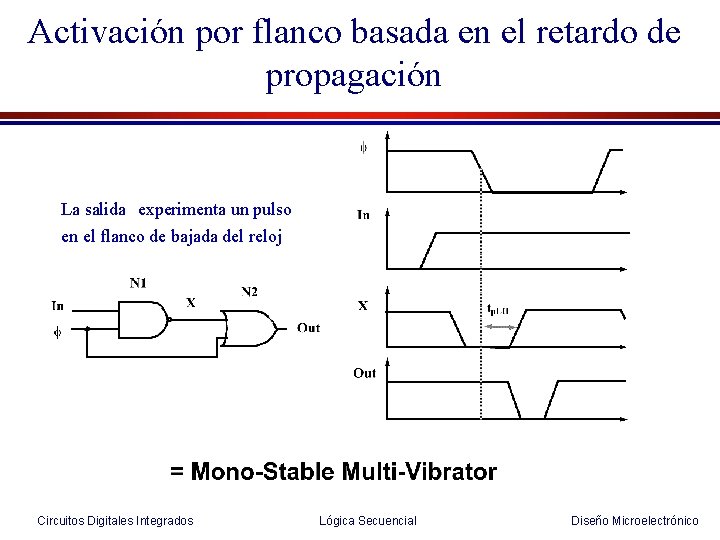

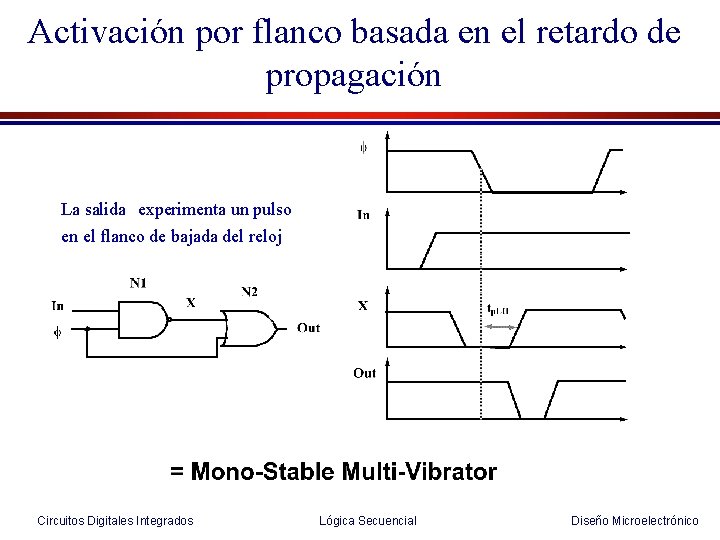

Activación por flanco basada en el retardo de propagación La salida experimenta un pulso en el flanco de bajada del reloj Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

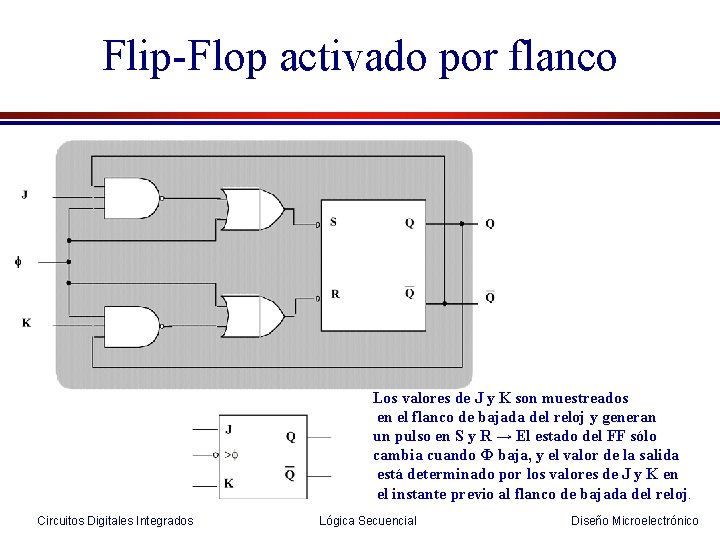

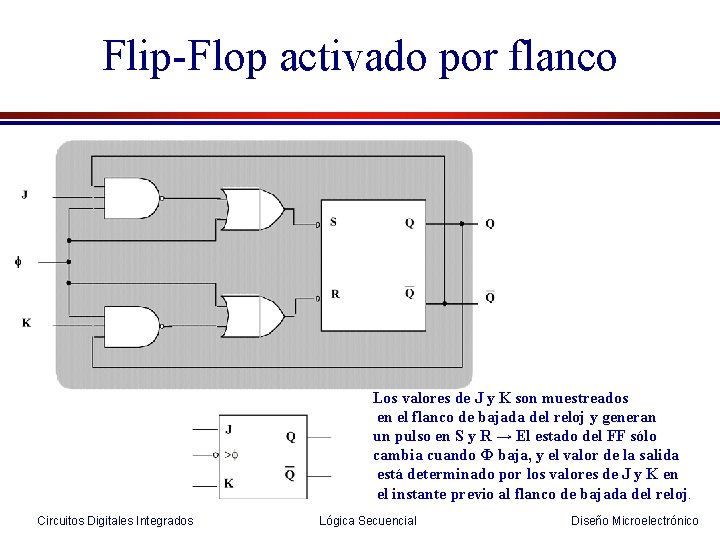

Flip-Flop activado por flanco Los valores de J y K son muestreados en el flanco de bajada del reloj y generan un pulso en S y R → El estado del FF sólo cambia cuando Φ baja, y el valor de la salida está determinado por los valores de J y K en el instante previo al flanco de bajada del reloj. Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

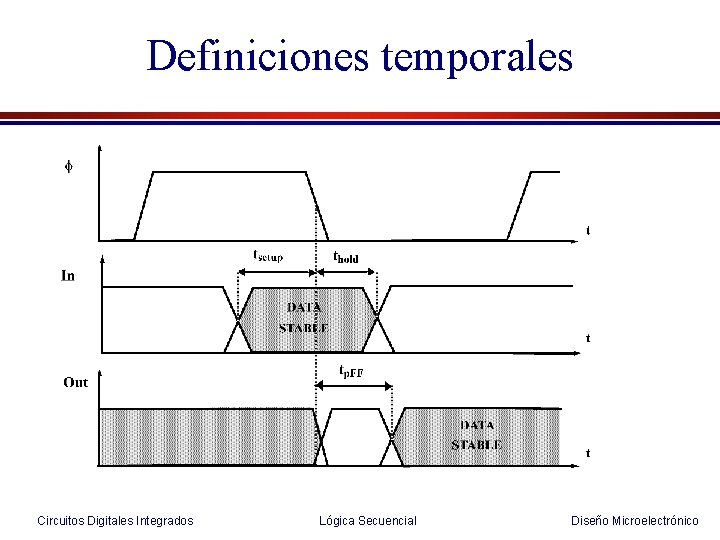

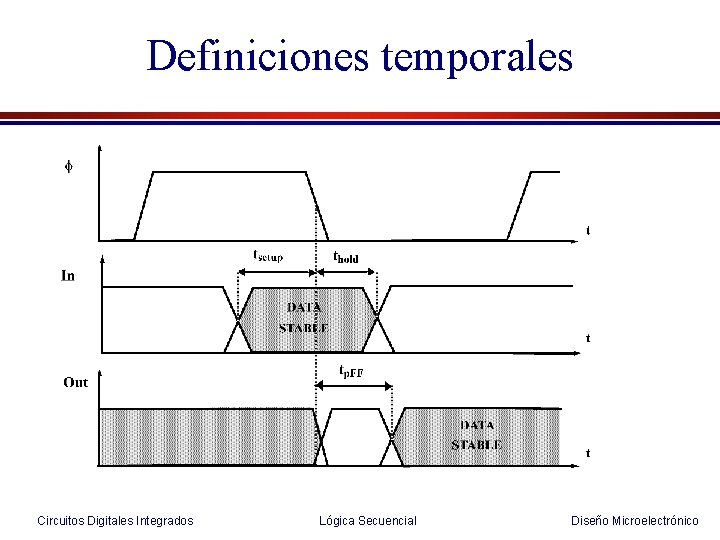

Definiciones temporales Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

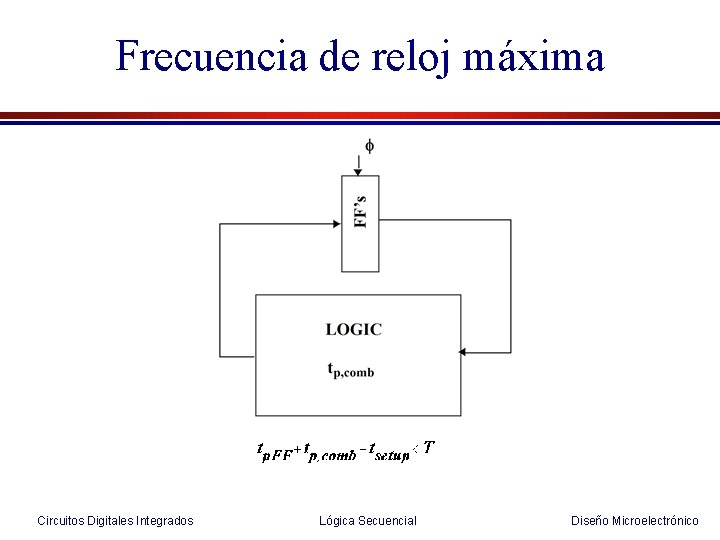

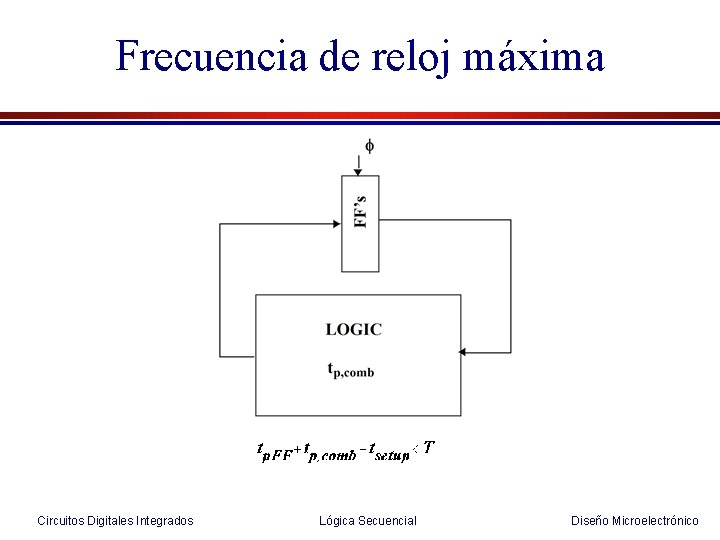

Frecuencia de reloj máxima Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

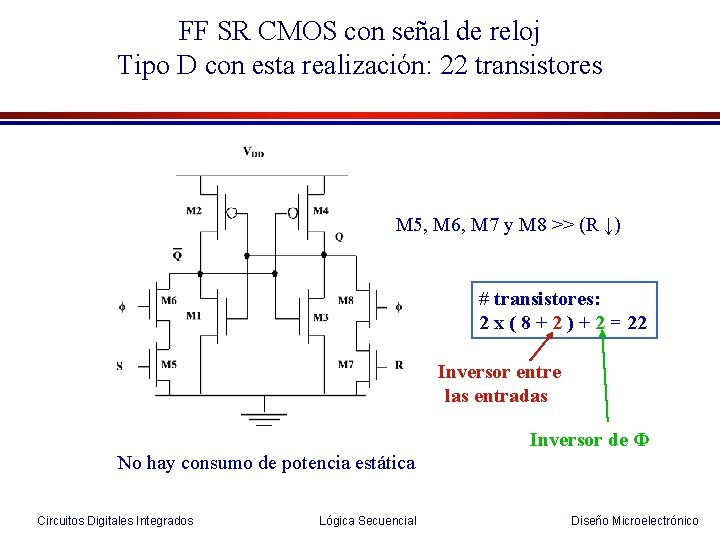

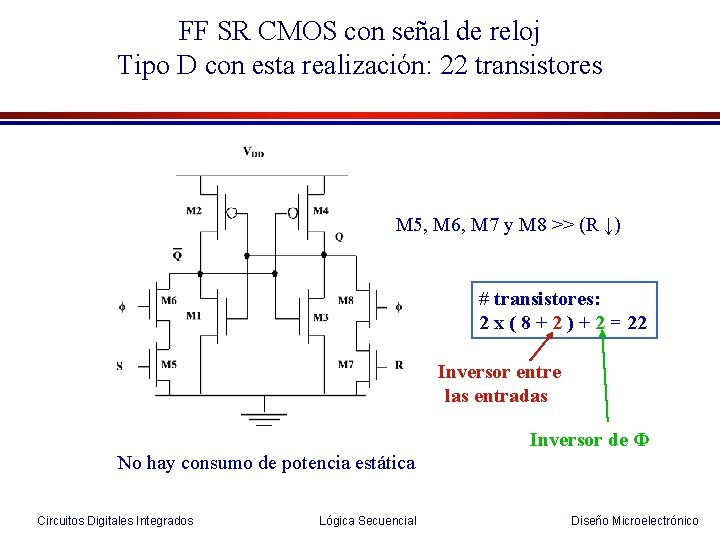

FF SR CMOS con señal de reloj Tipo D con esta realización: 22 transistores M 5, M 6, M 7 y M 8 >> (R ↓) # transistores: 2 x ( 8 + 2 ) + 2 = 22 Inversor entre las entradas Inversor de Φ No hay consumo de potencia estática Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

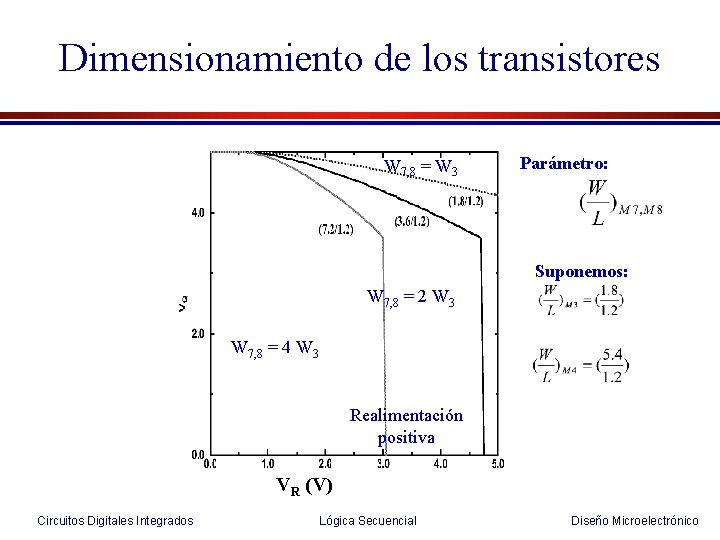

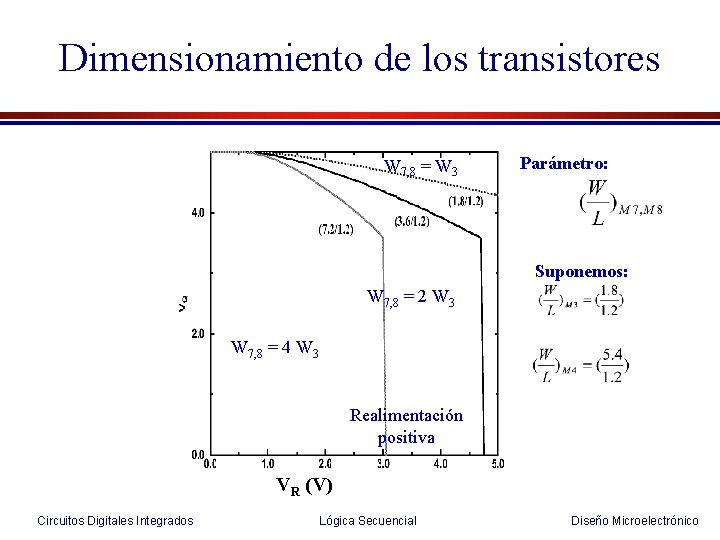

Dimensionamiento de los transistores W 7, 8 = W 3 Parámetro: Suponemos: W 7, 8 = 2 W 3 W 7, 8 = 4 W 3 Realimentación positiva VR (V) Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

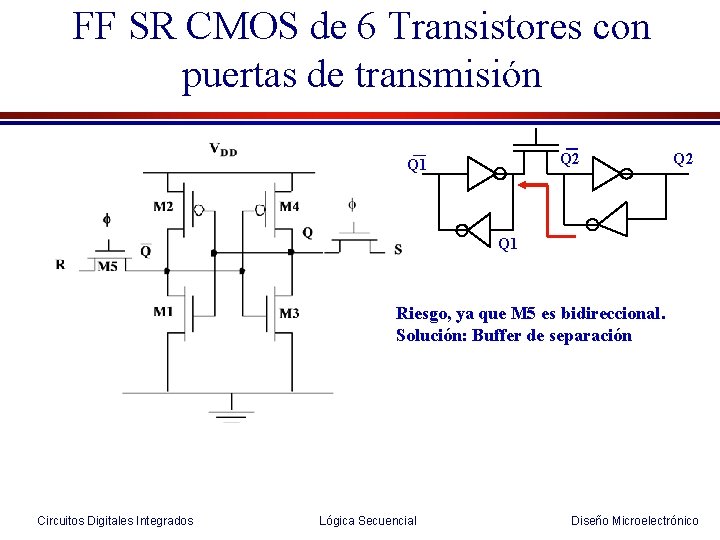

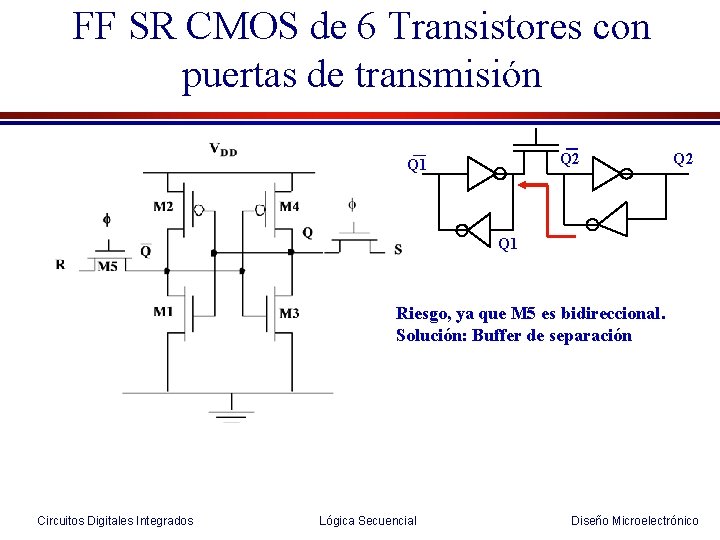

FF SR CMOS de 6 Transistores con puertas de transmisión ─ Q 2 ─ Q 1 Q 2 Q 1 Riesgo, ya que M 5 es bidireccional. Solución: Buffer de separación Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

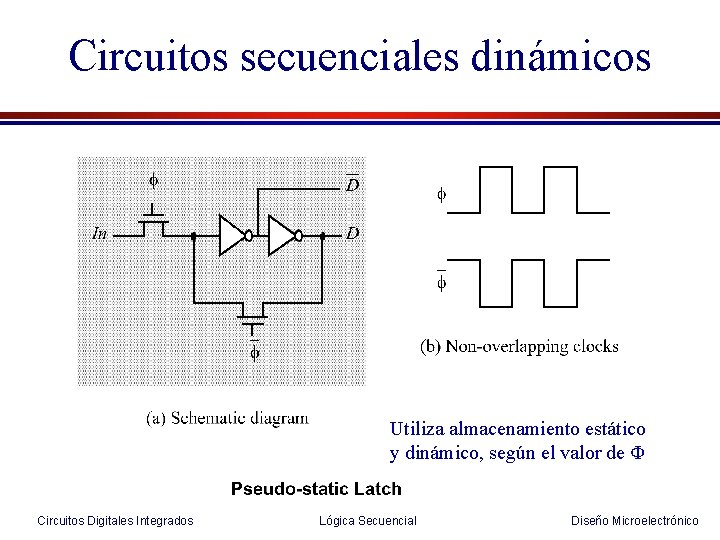

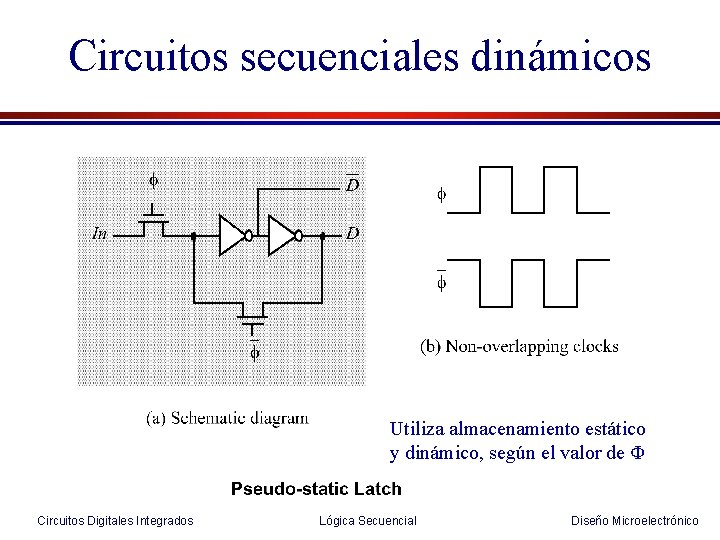

Circuitos secuenciales dinámicos Utiliza almacenamiento estático y dinámico, según el valor de Φ Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

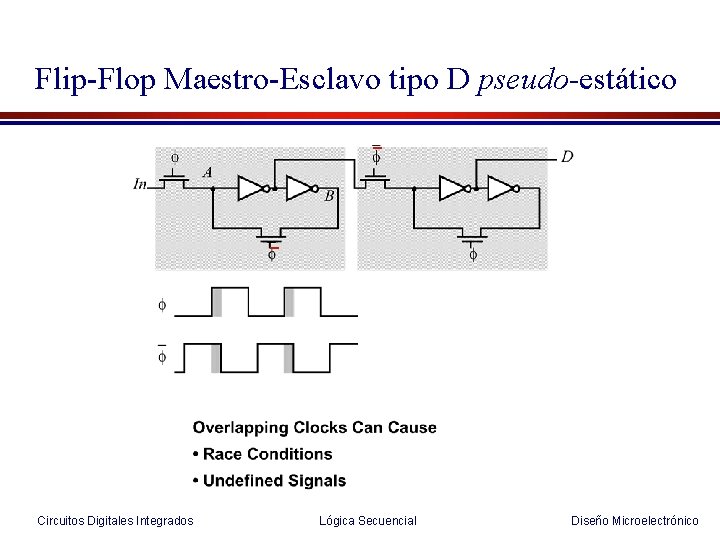

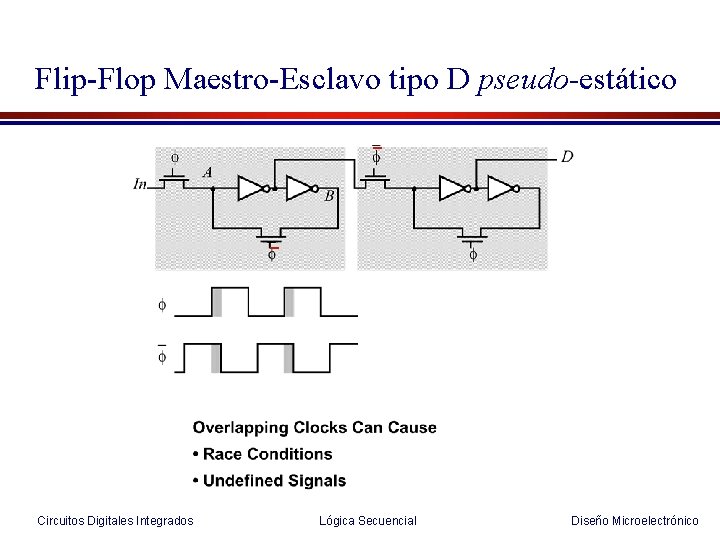

Flip-Flop Maestro-Esclavo tipo D pseudo-estático - Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

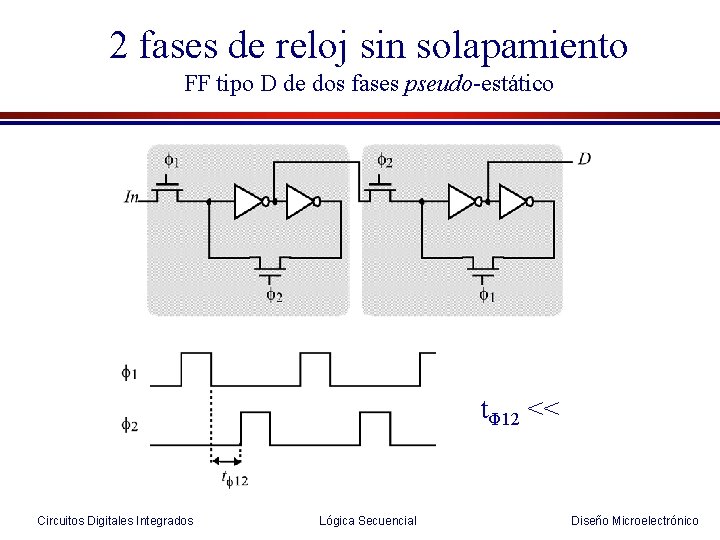

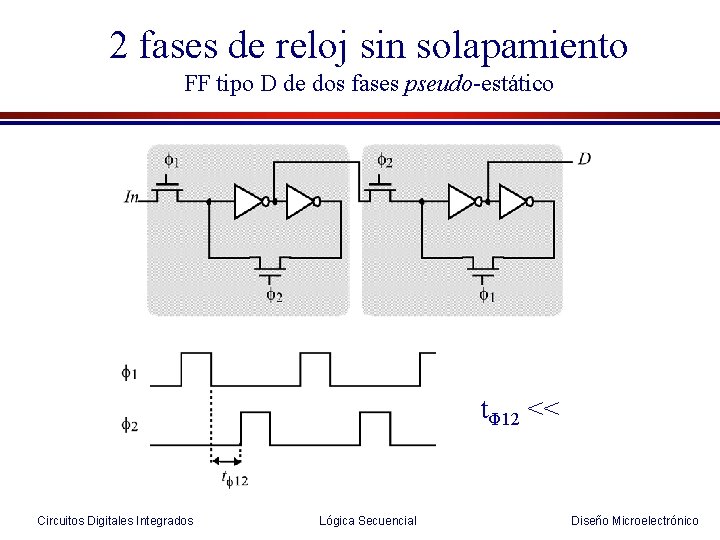

2 fases de reloj sin solapamiento FF tipo D de dos fases pseudo-estático tΦ 12 << Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

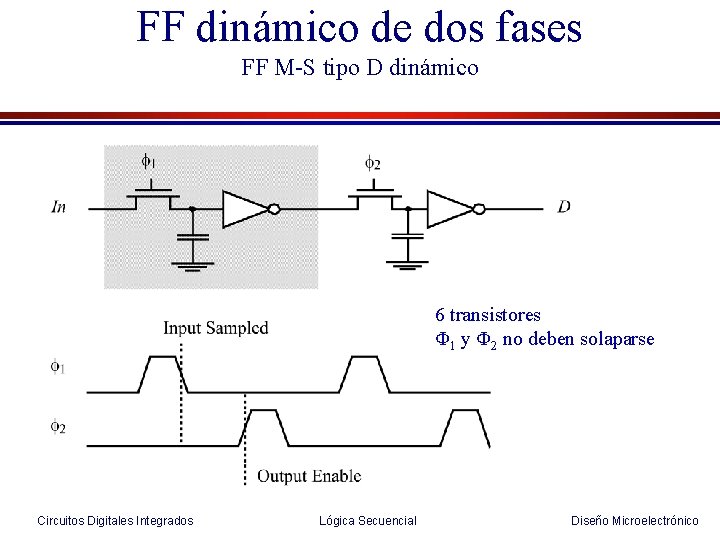

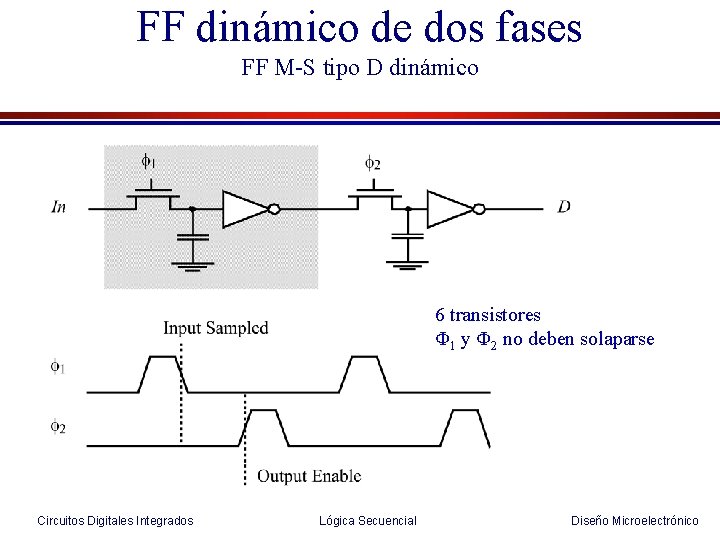

FF dinámico de dos fases FF M-S tipo D dinámico 6 transistores Φ 1 y Φ 2 no deben solaparse Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

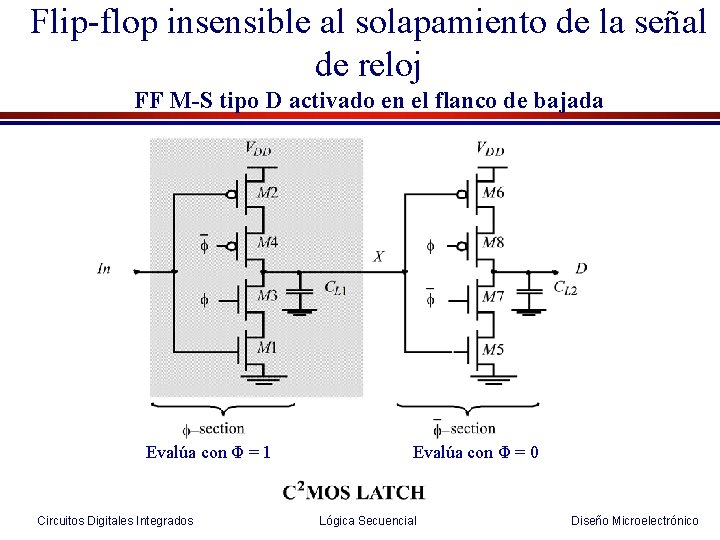

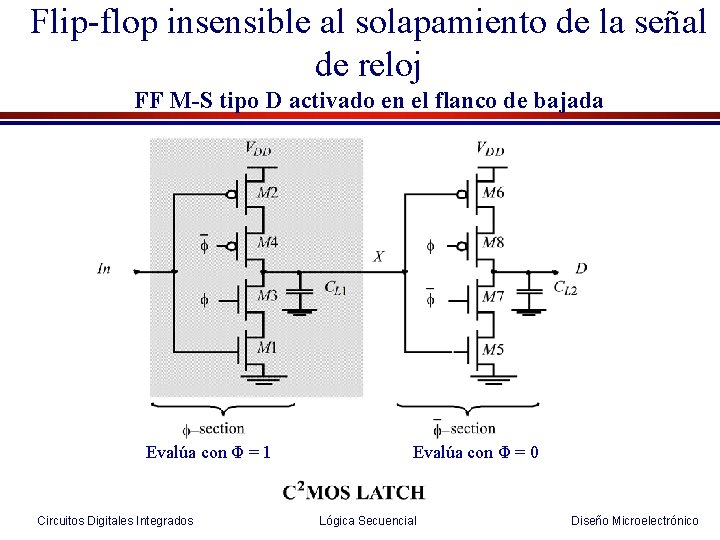

Flip-flop insensible al solapamiento de la señal de reloj FF M-S tipo D activado en el flanco de bajada Evalúa con Φ = 1 Circuitos Digitales Integrados Evalúa con Φ = 0 Lógica Secuencial Diseño Microelectrónico

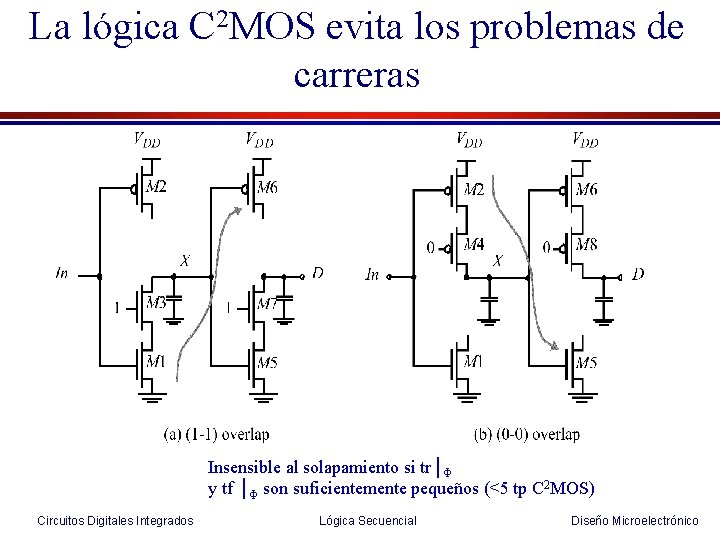

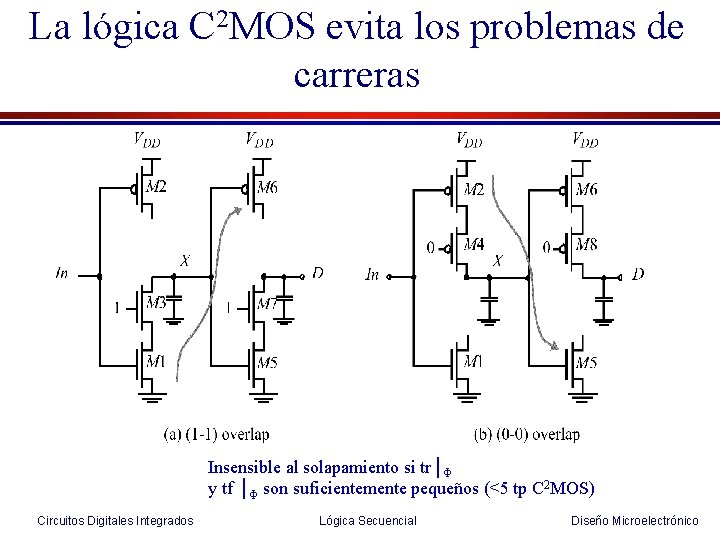

La lógica C 2 MOS evita los problemas de carreras Insensible al solapamiento si tr│Φ y tf │Φ son suficientemente pequeños (<5 tp C 2 MOS) Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

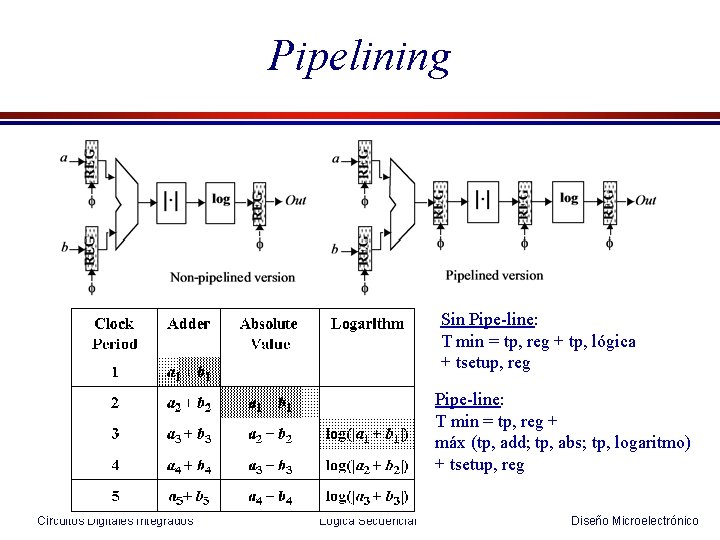

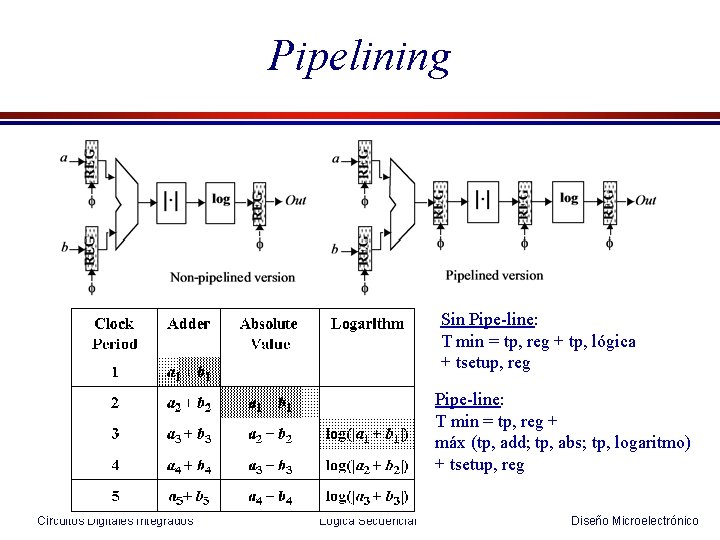

Pipelining Sin Pipe-line: T min = tp, reg + tp, lógica + tsetup, reg Pipe-line: T min = tp, reg + máx (tp, add; tp, abs; tp, logaritmo) + tsetup, reg Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

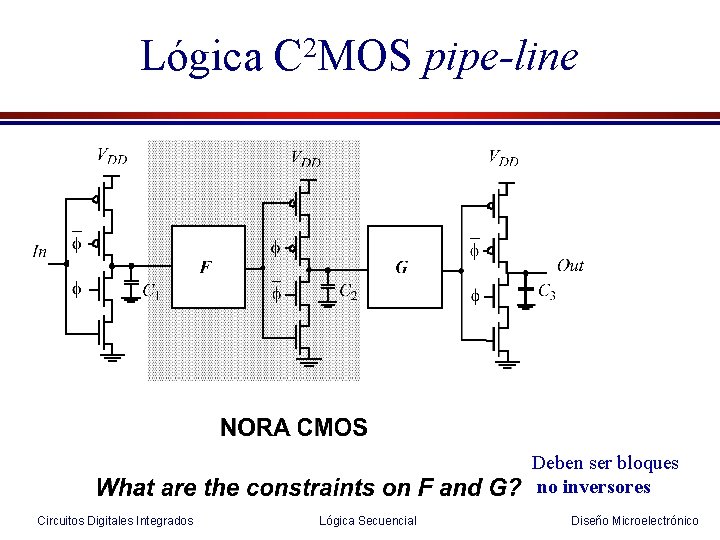

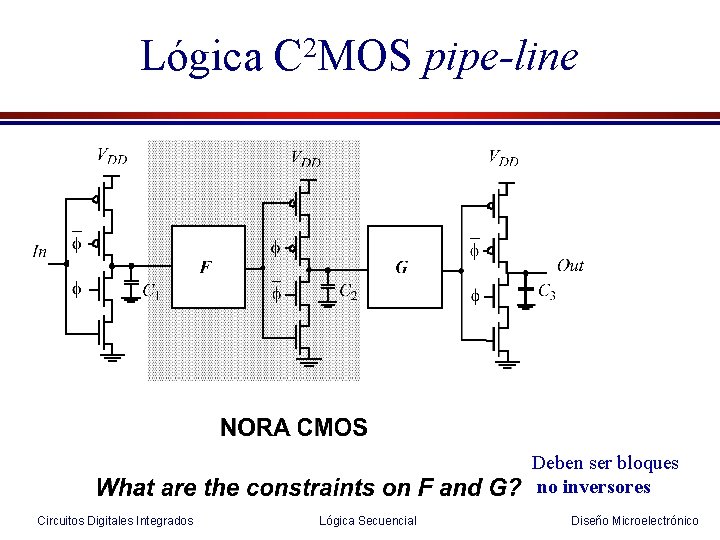

Lógica C 2 MOS pipe-line Deben ser bloques no inversores Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

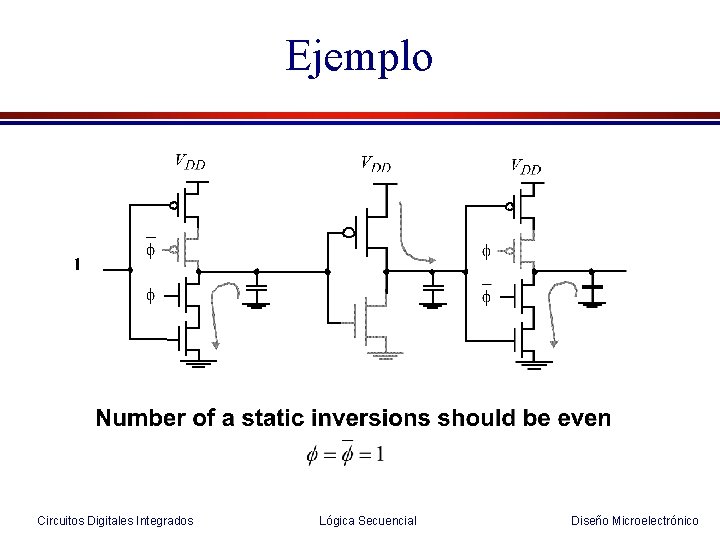

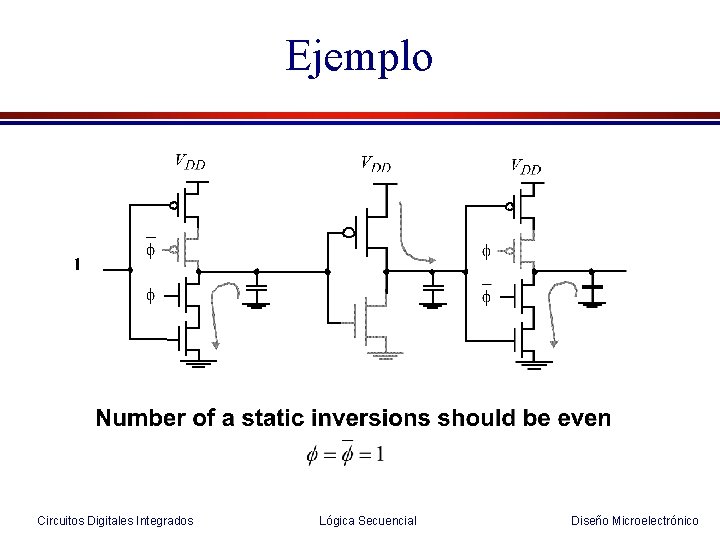

Ejemplo Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

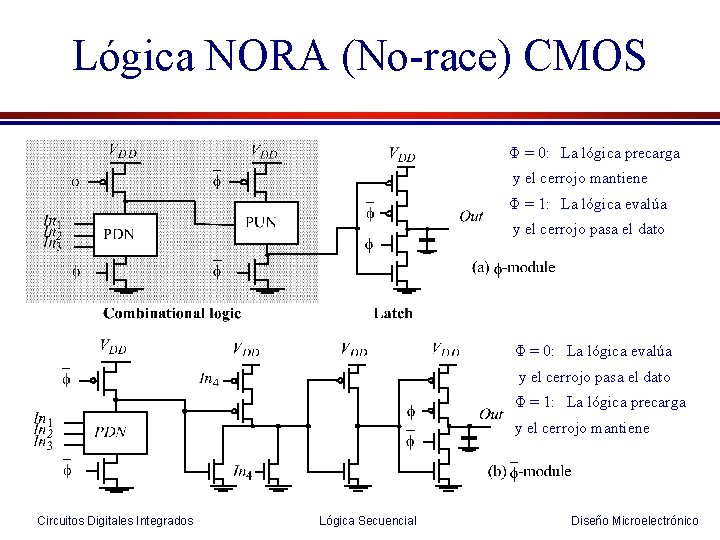

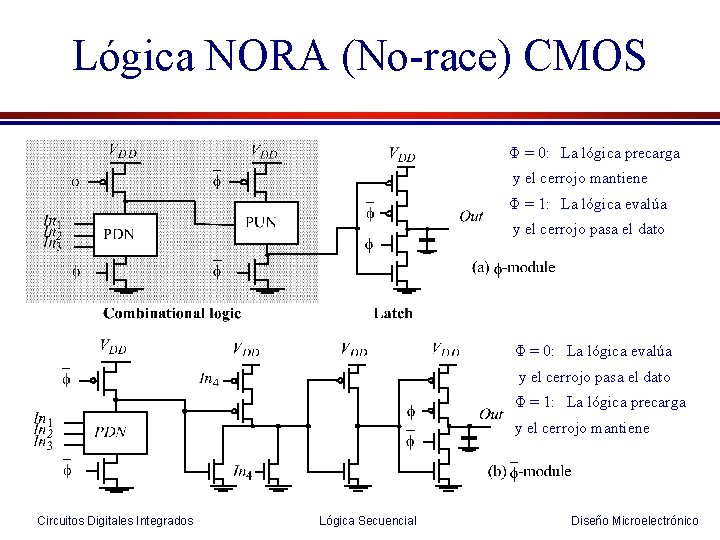

Lógica NORA (No-race) CMOS Φ = 0: La lógica precarga y el cerrojo mantiene Φ = 1: La lógica evalúa y el cerrojo pasa el dato Φ = 0: La lógica evalúa y el cerrojo pasa el dato Φ = 1: La lógica precarga y el cerrojo mantiene Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

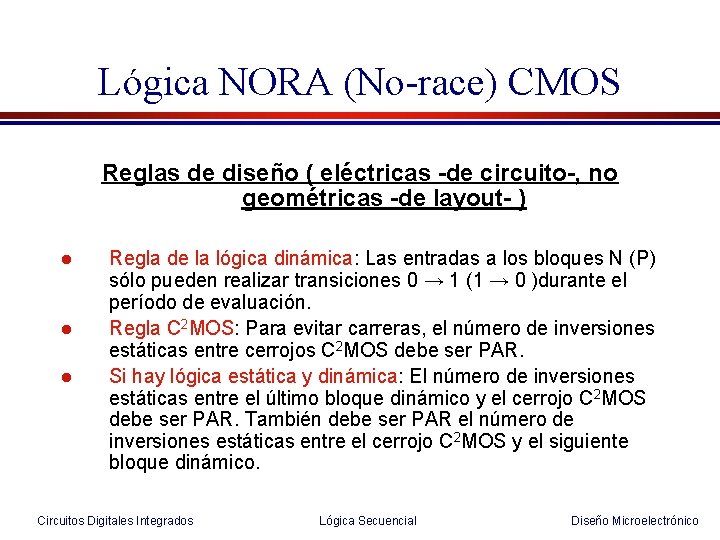

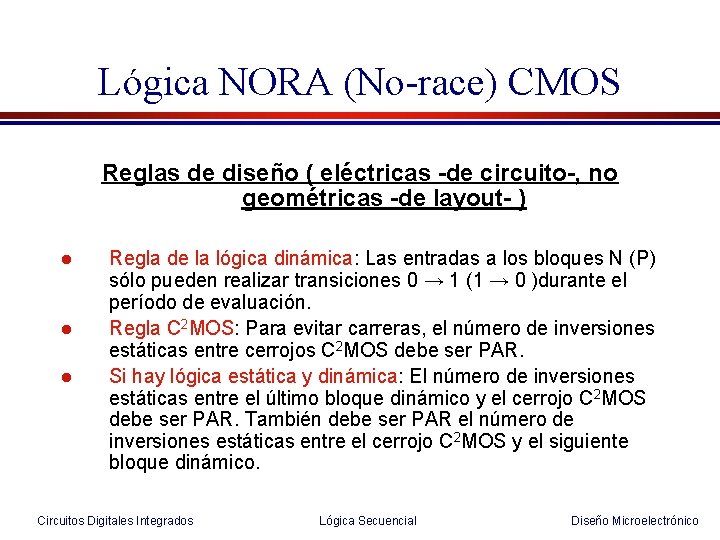

Lógica NORA (No-race) CMOS Reglas de diseño ( eléctricas -de circuito-, no geométricas -de layout- ) l l l Regla de la lógica dinámica: Las entradas a los bloques N (P) sólo pueden realizar transiciones 0 → 1 (1 → 0 )durante el período de evaluación. Regla C 2 MOS: Para evitar carreras, el número de inversiones estáticas entre cerrojos C 2 MOS debe ser PAR. Si hay lógica estática y dinámica: El número de inversiones estáticas entre el último bloque dinámico y el cerrojo C 2 MOS debe ser PAR. También debe ser PAR el número de inversiones estáticas entre el cerrojo C 2 MOS y el siguiente bloque dinámico. Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

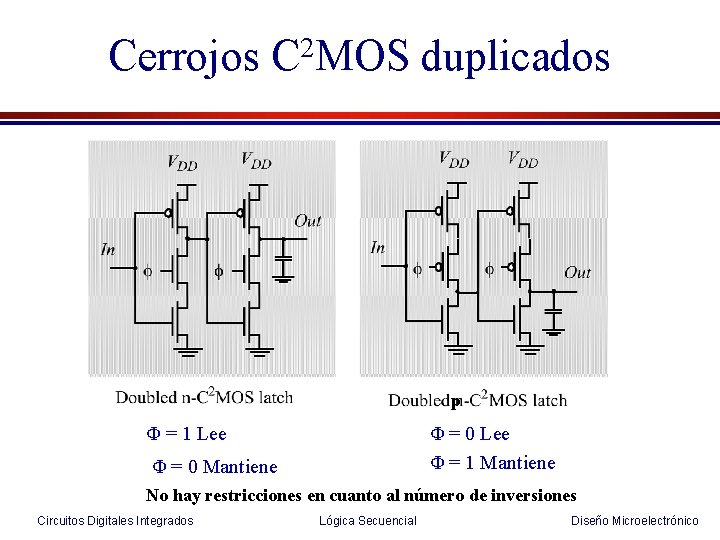

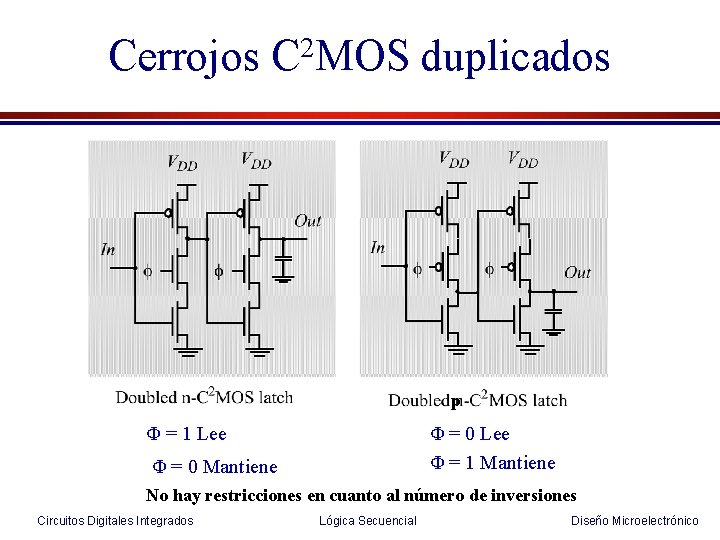

Cerrojos C 2 MOS duplicados p Φ = 1 Lee Φ = 0 Lee Φ = 1 Mantiene Φ = 0 Mantiene No hay restricciones en cuanto al número de inversiones Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

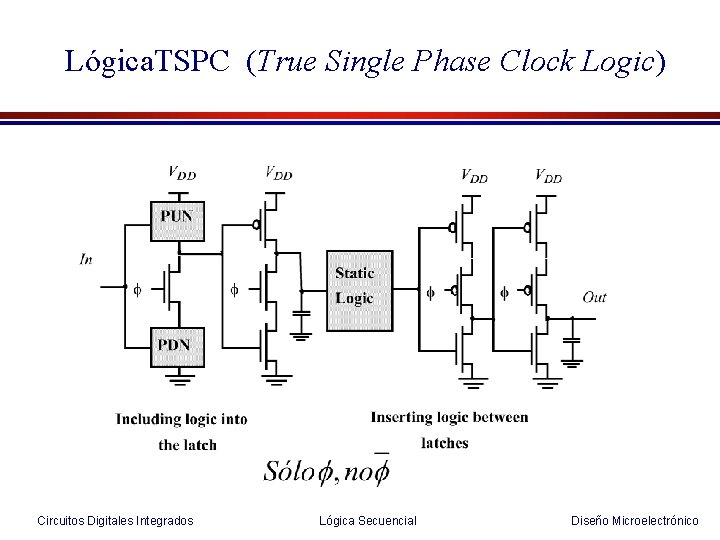

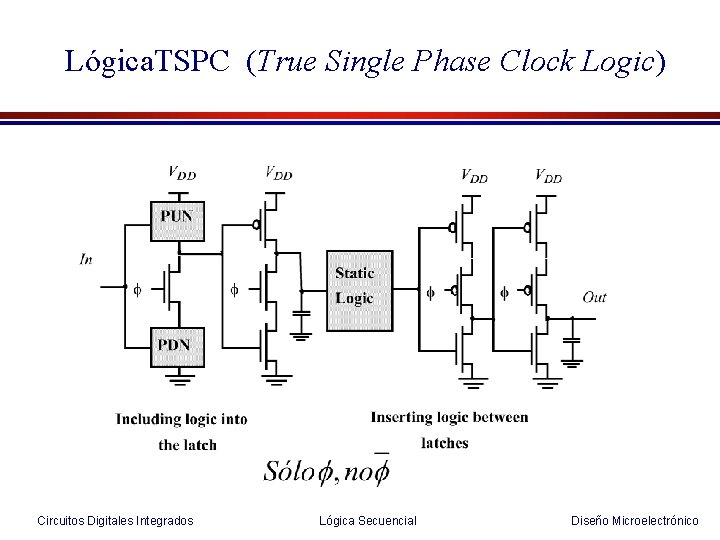

Lógica. TSPC (True Single Phase Clock Logic) Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

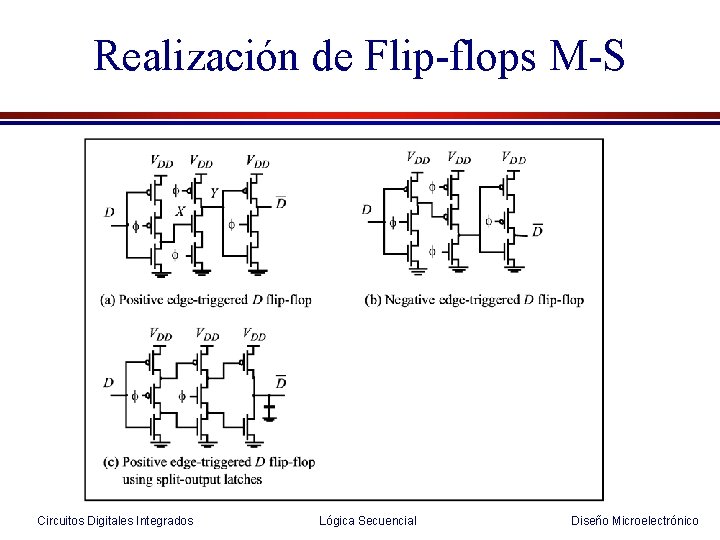

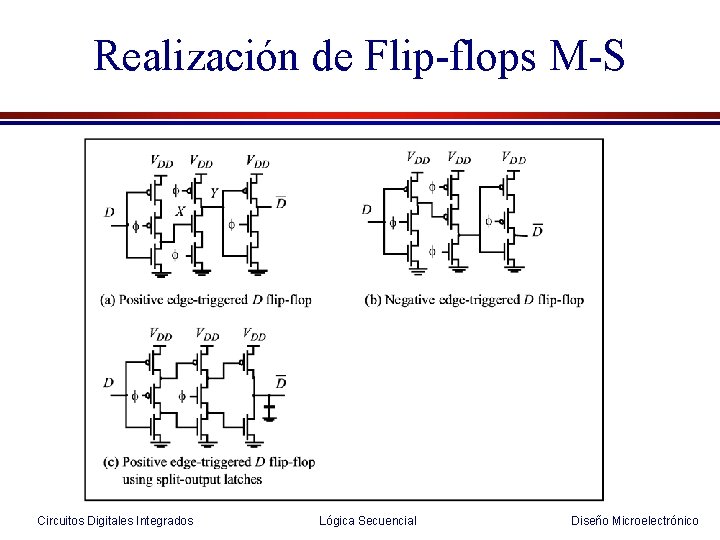

Realización de Flip-flops M-S Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

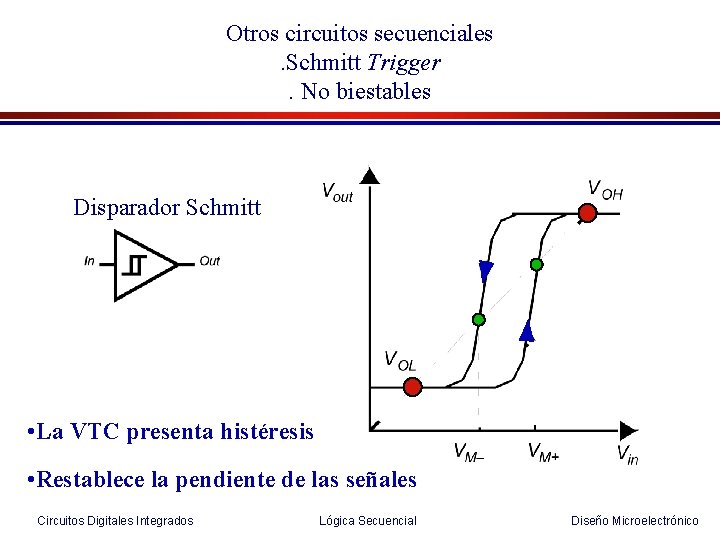

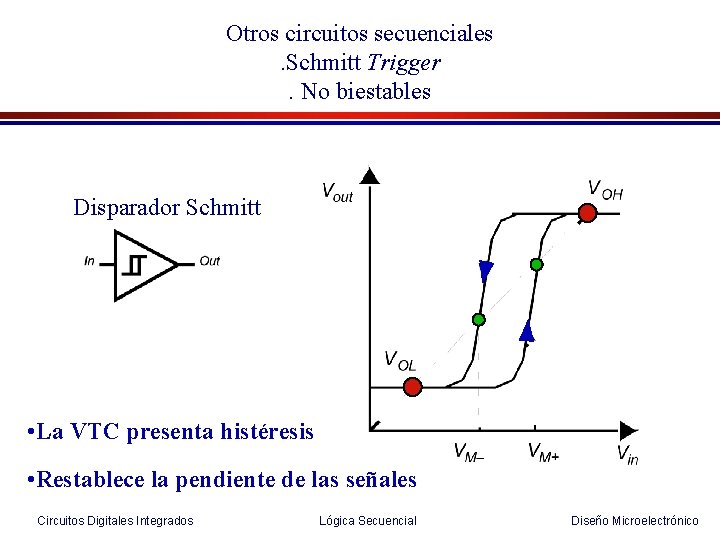

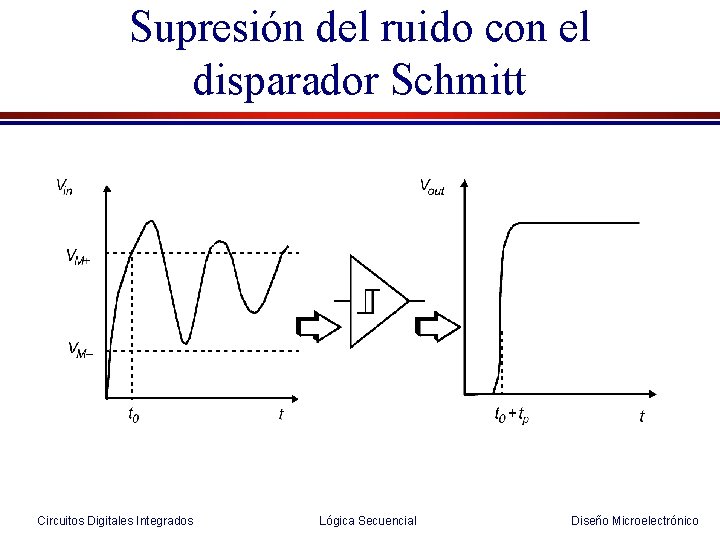

Otros circuitos secuenciales. Schmitt Trigger. No biestables Disparador Schmitt • La VTC presenta histéresis • Restablece la pendiente de las señales Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

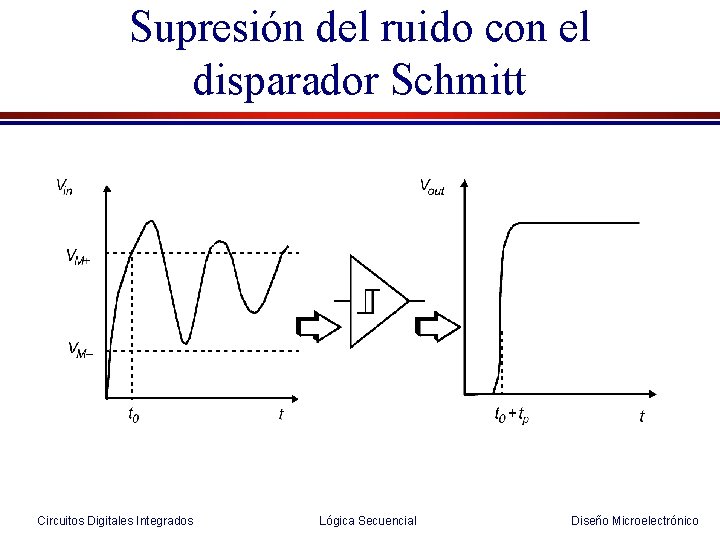

Supresión del ruido con el disparador Schmitt Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

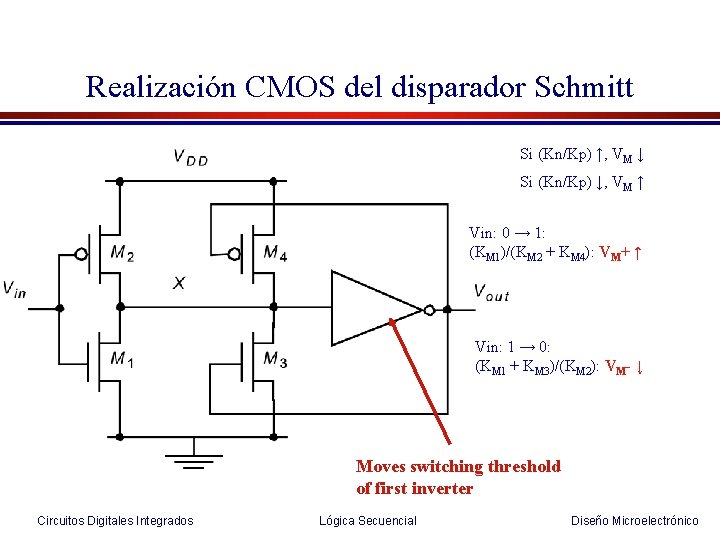

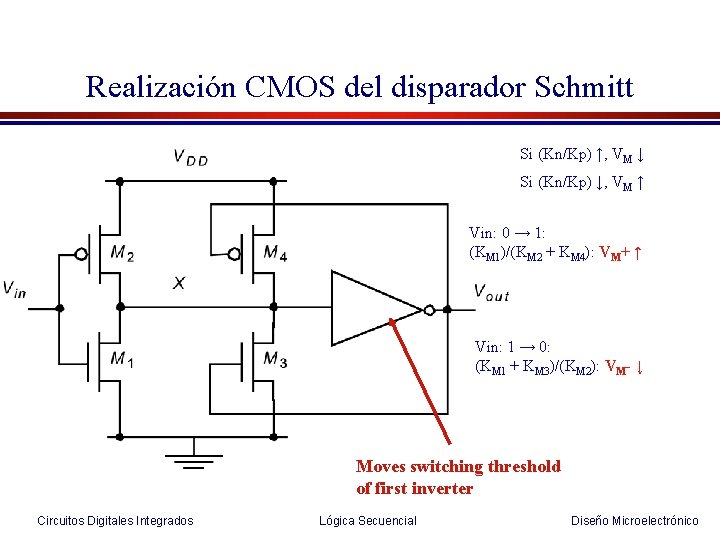

Realización CMOS del disparador Schmitt Si (Kn/Kp) ↑, VM ↓ Si (Kn/Kp) ↓, VM ↑ Vin: 0 → 1: (KM 1)/(KM 2 + KM 4): VM+ ↑ Vin: 1 → 0: (KM 1 + KM 3)/(KM 2): VM- ↓ Moves switching threshold of first inverter Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

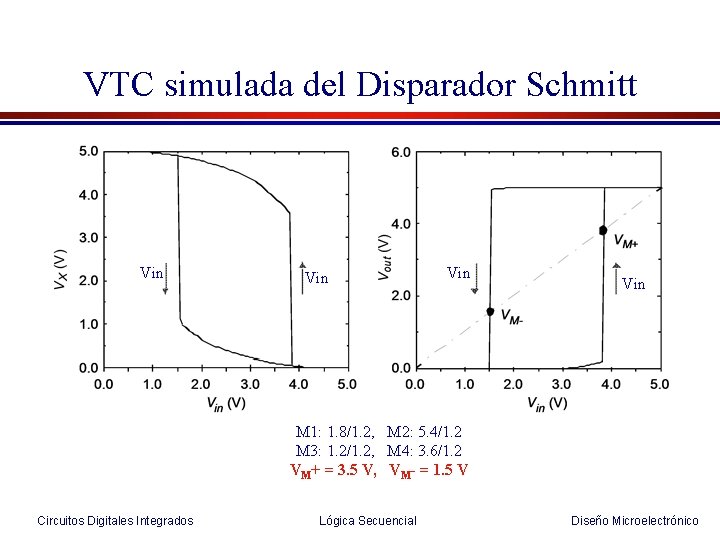

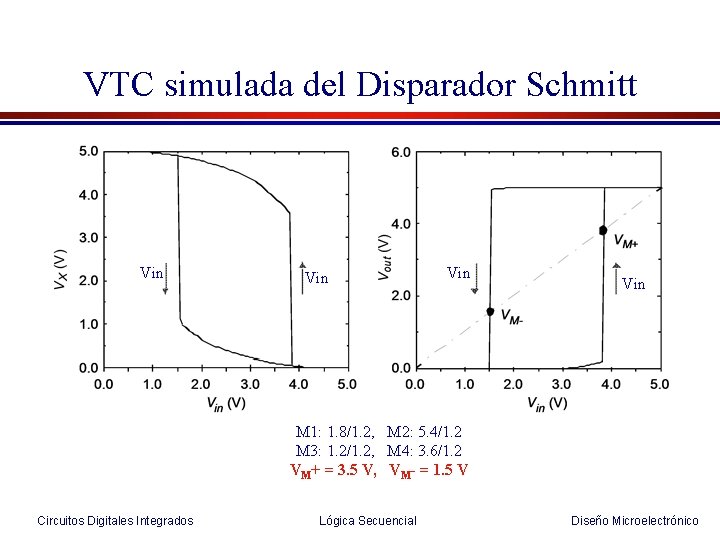

VTC simulada del Disparador Schmitt Vin Vin M 1: 1. 8/1. 2, M 2: 5. 4/1. 2 M 3: 1. 2/1. 2, M 4: 3. 6/1. 2 VM+ = 3. 5 V, VM- = 1. 5 V Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

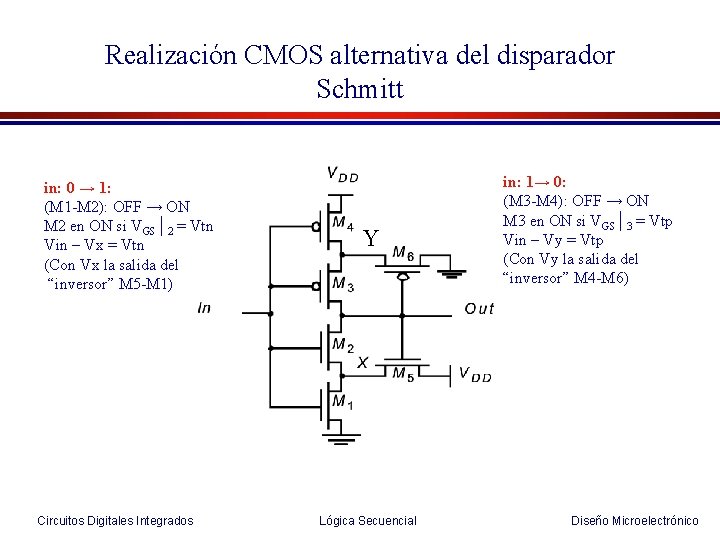

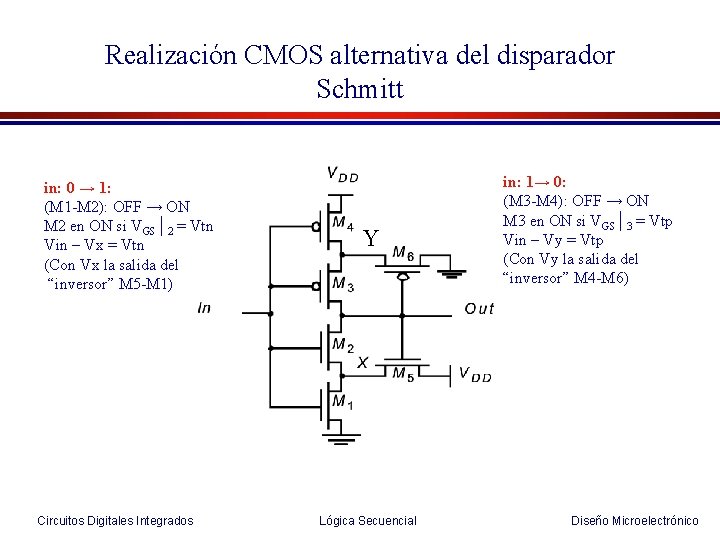

Realización CMOS alternativa del disparador Schmitt in: 0 → 1: (M 1 -M 2): OFF → ON M 2 en ON si VGS│2 = Vtn Vin – Vx = Vtn (Con Vx la salida del “inversor” M 5 -M 1) Circuitos Digitales Integrados Y Lógica Secuencial in: 1→ 0: (M 3 -M 4): OFF → ON M 3 en ON si VGS│3 = Vtp Vin – Vy = Vtp (Con Vy la salida del “inversor” M 4 -M 6) Diseño Microelectrónico

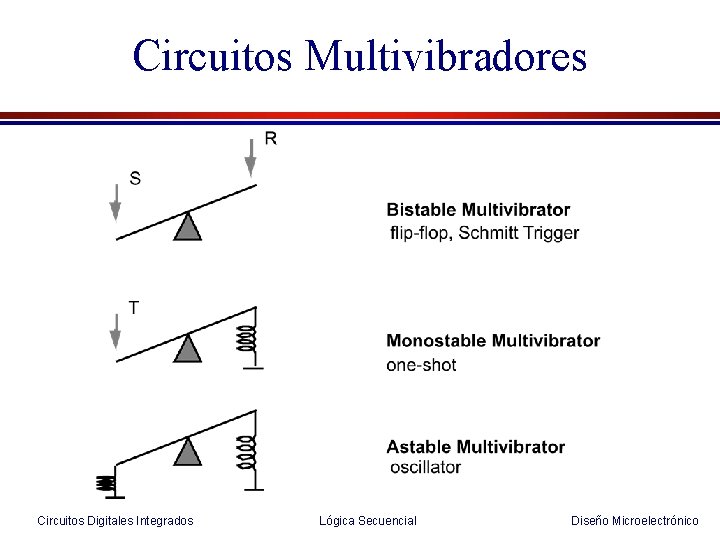

Circuitos Multivibradores Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

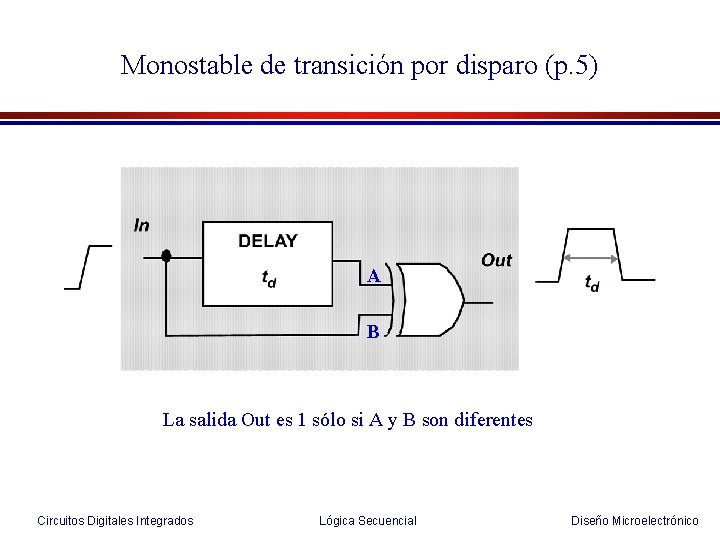

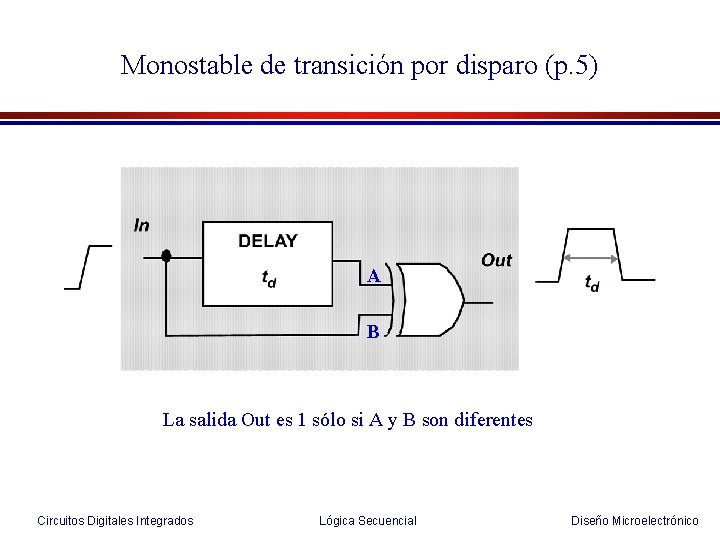

Monostable de transición por disparo (p. 5) A B La salida Out es 1 sólo si A y B son diferentes Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

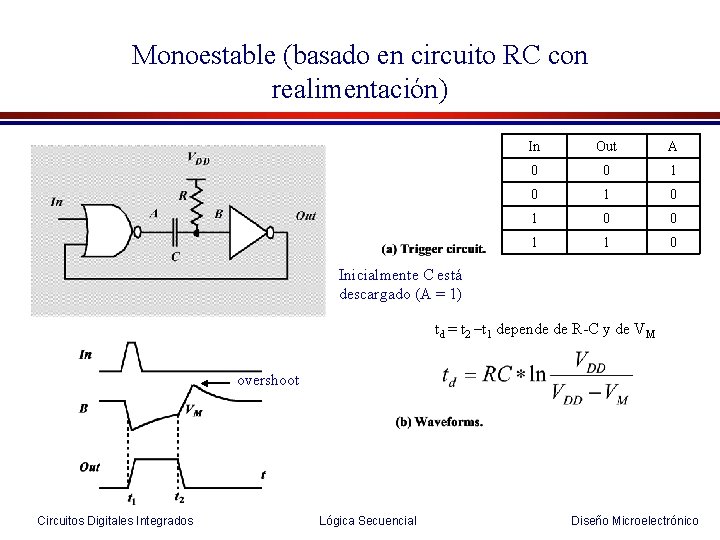

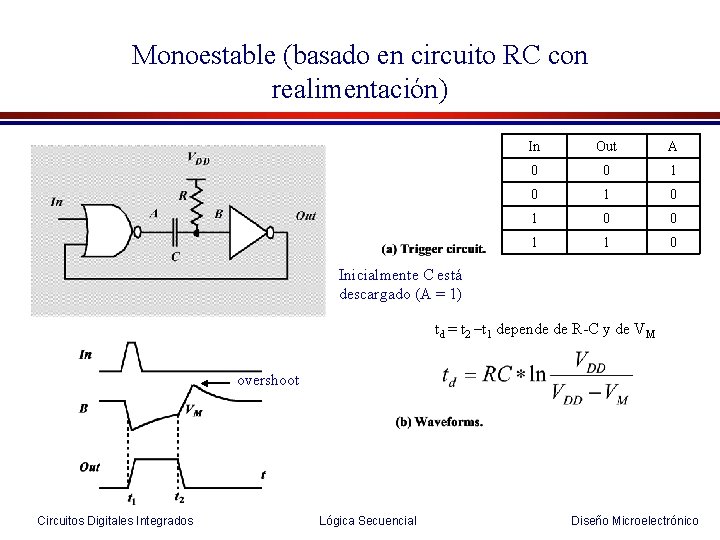

Monoestable (basado en circuito RC con realimentación) In Out A 0 0 1 0 1 0 0 1 1 0 Inicialmente C está descargado (A = 1) td = t 2 –t 1 depende de R-C y de VM overshoot Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

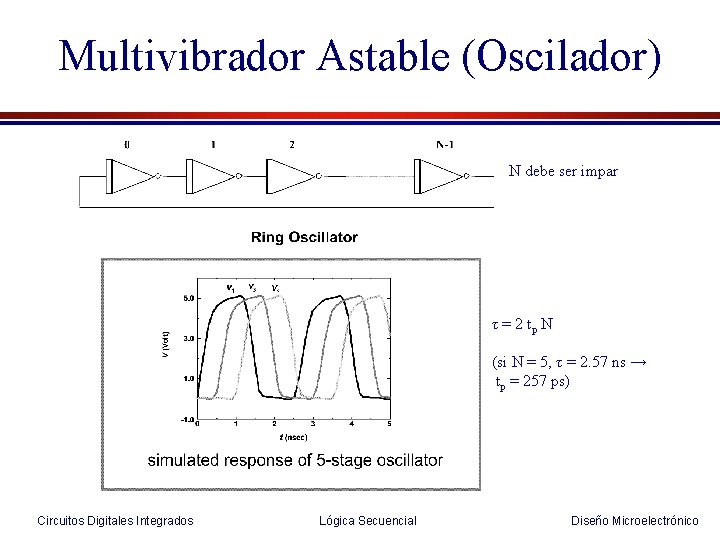

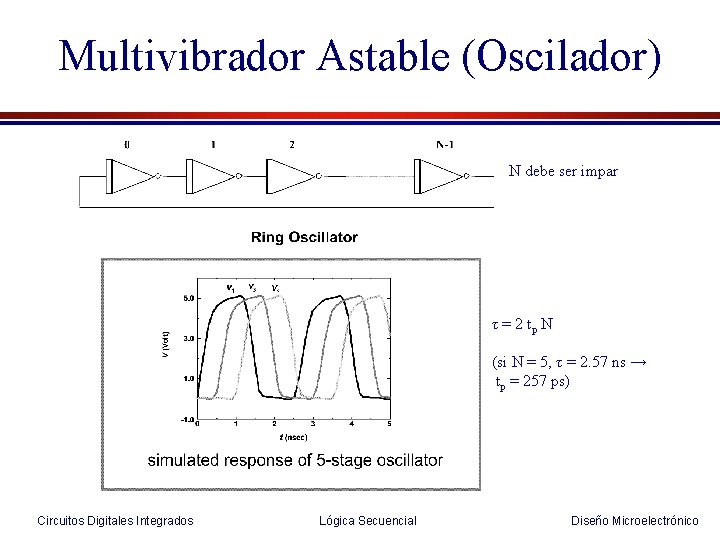

Multivibrador Astable (Oscilador) N debe ser impar τ = 2 tp N (si N = 5, τ = 2. 57 ns → tp = 257 ps) Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

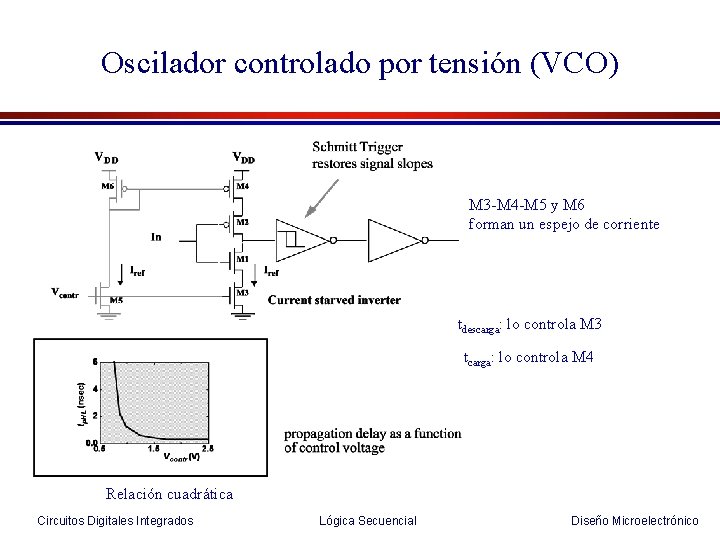

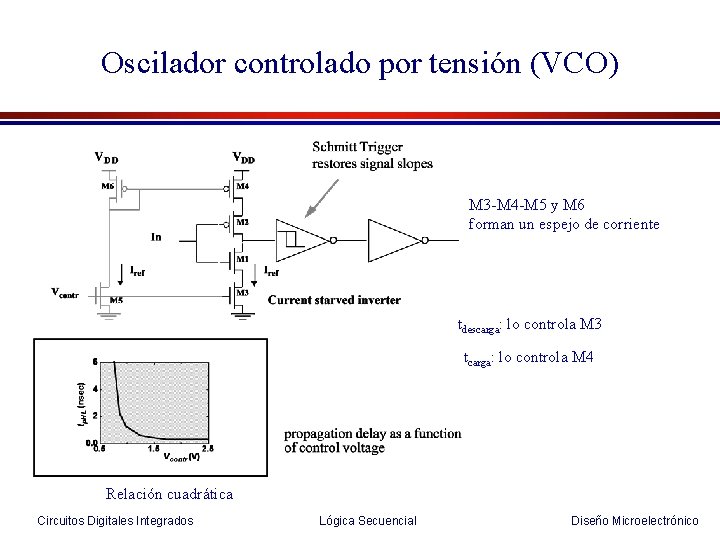

Oscilador controlado por tensión (VCO) M 3 -M 4 -M 5 y M 6 forman un espejo de corriente tdescarga: lo controla M 3 tcarga: lo controla M 4 Relación cuadrática Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico

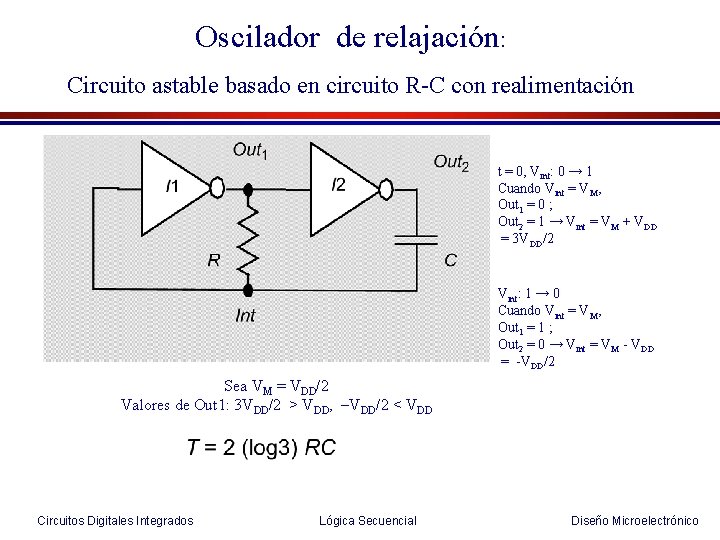

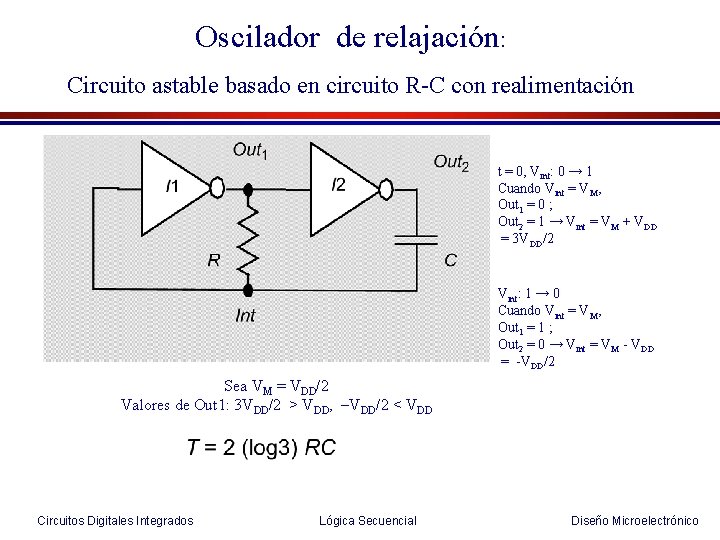

Oscilador de relajación: Circuito astable basado en circuito R-C con realimentación t = 0, Vint: 0 → 1 Cuando Vint = VM, Out 1 = 0 ; Out 2 = 1 → Vint = VM + VDD = 3 VDD/2 Vint: 1 → 0 Cuando Vint = VM, Out 1 = 1 ; Out 2 = 0 → Vint = VM - VDD = -VDD/2 Sea VM = VDD/2 Valores de Out 1: 3 VDD/2 > VDD, –VDD/2 < VDD Circuitos Digitales Integrados Lógica Secuencial Diseño Microelectrónico