Chapter 6 Interrupt and Exception Programming 1 Polling

- Slides: 41

Chapter 6 Interrupt and Exception Programming 1

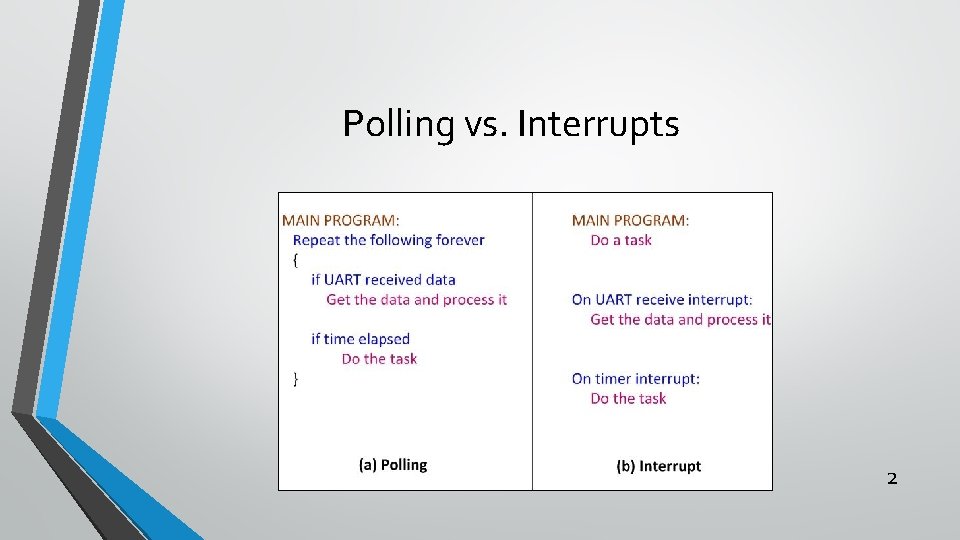

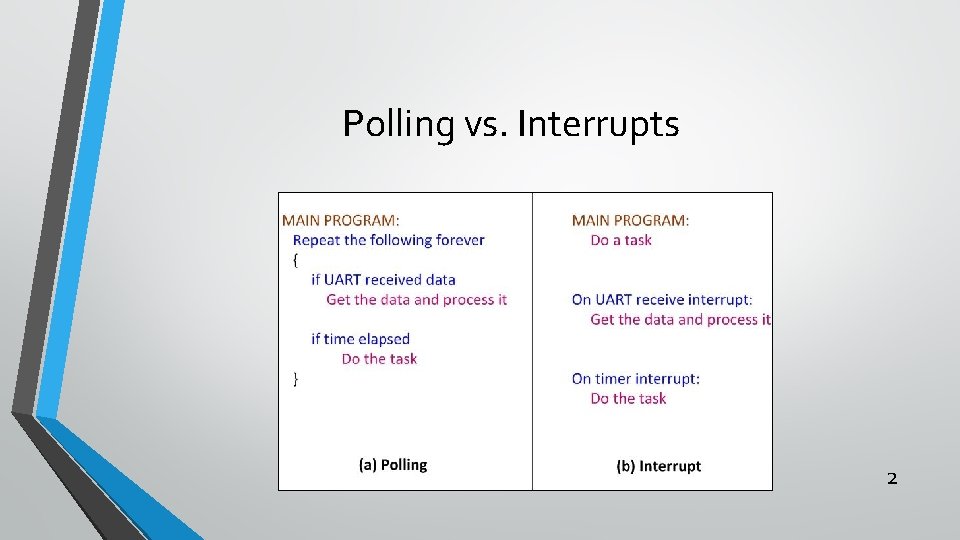

Polling vs. Interrupts 2

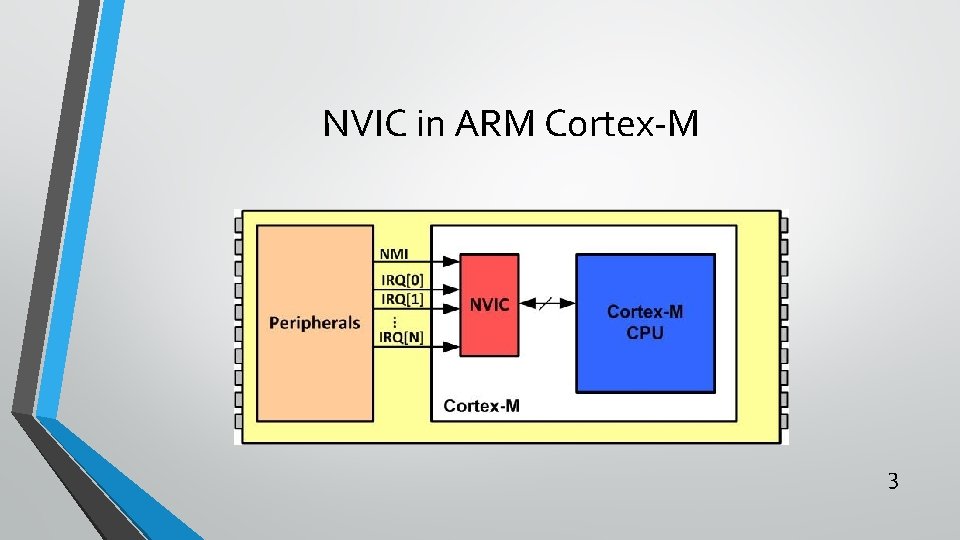

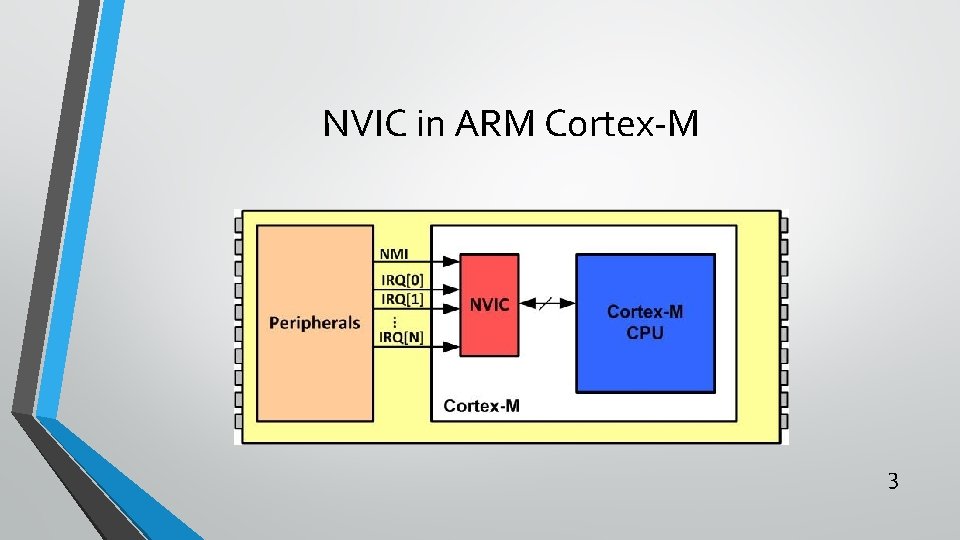

NVIC in ARM Cortex-M 3

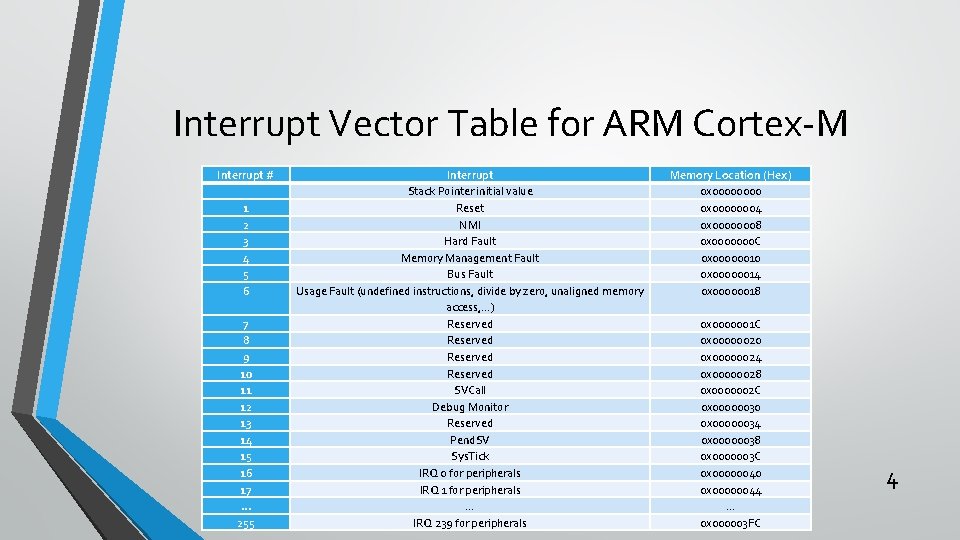

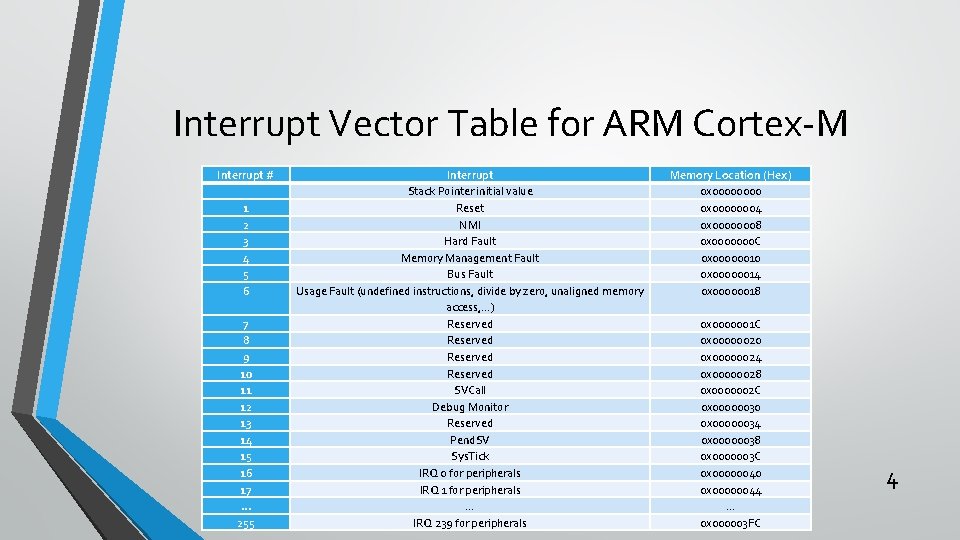

Interrupt Vector Table for ARM Cortex-M Interrupt # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Memory Location (Hex) 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C 0 x 00000020 0 x 00000024 0 x 00000028 0 x 0000002 C 0 x 00000030 0 x 00000034 0 x 00000038 0 x 0000003 C 0 x 00000040 0 x 00000044 … 0 x 000003 FC 4

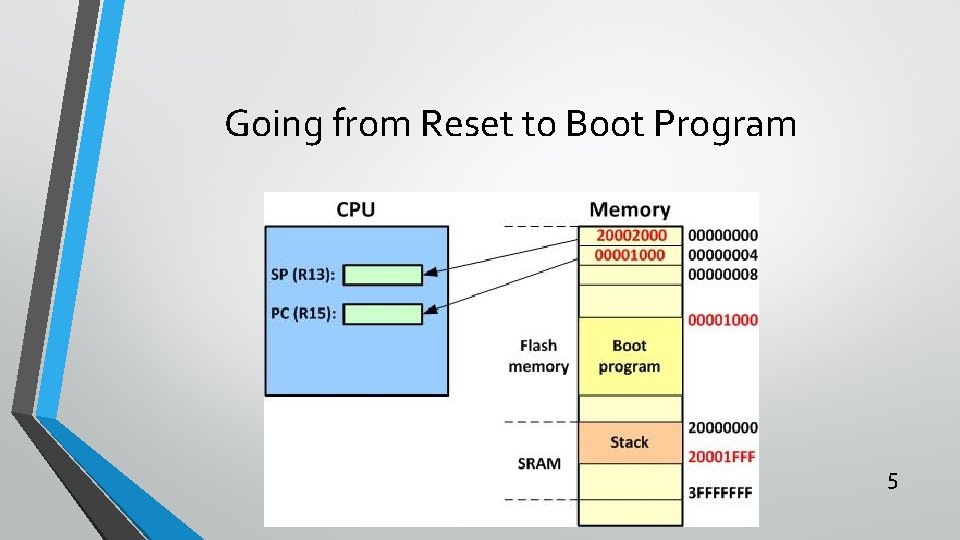

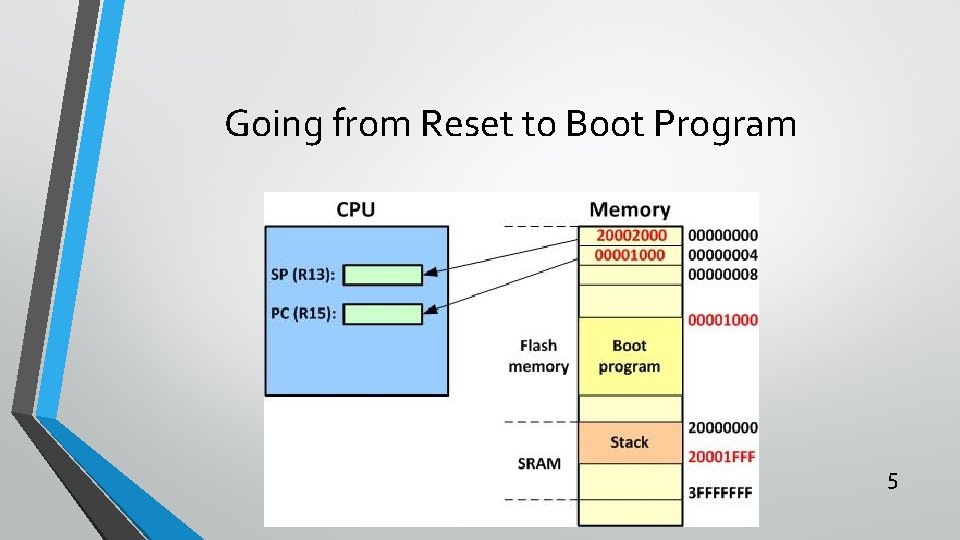

Going from Reset to Boot Program 5

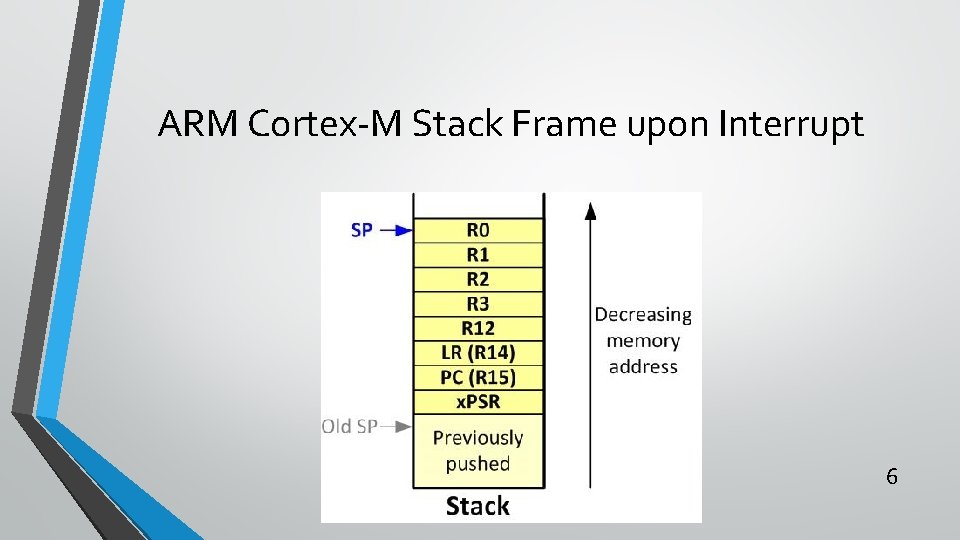

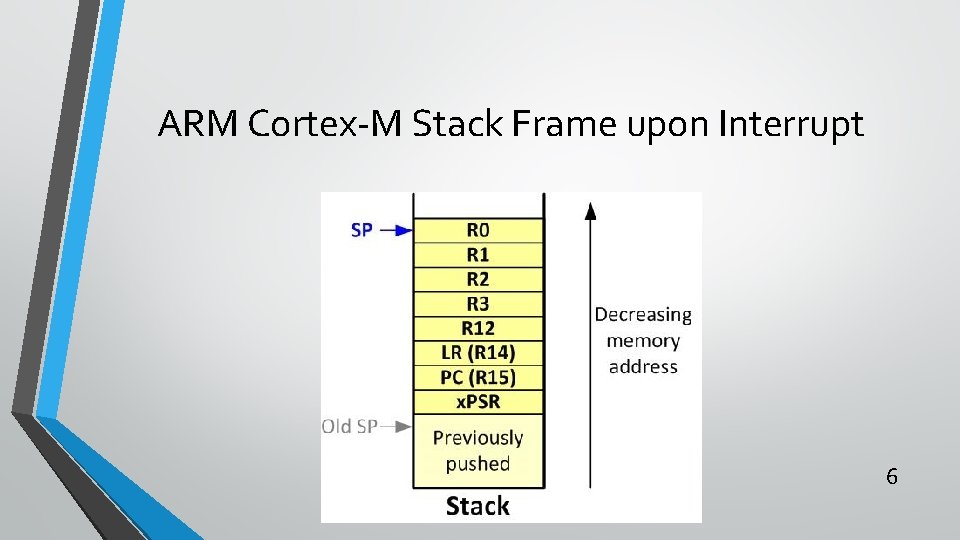

ARM Cortex-M Stack Frame upon Interrupt 6

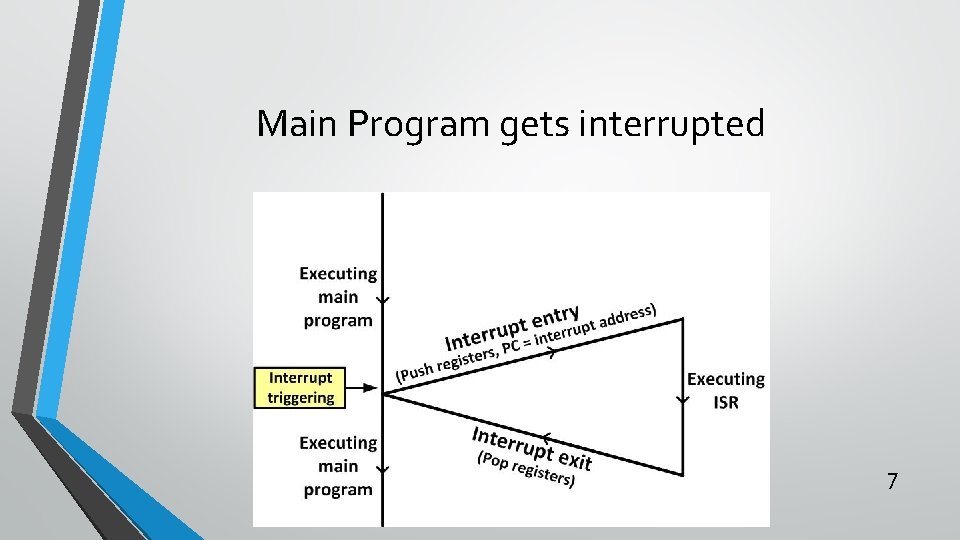

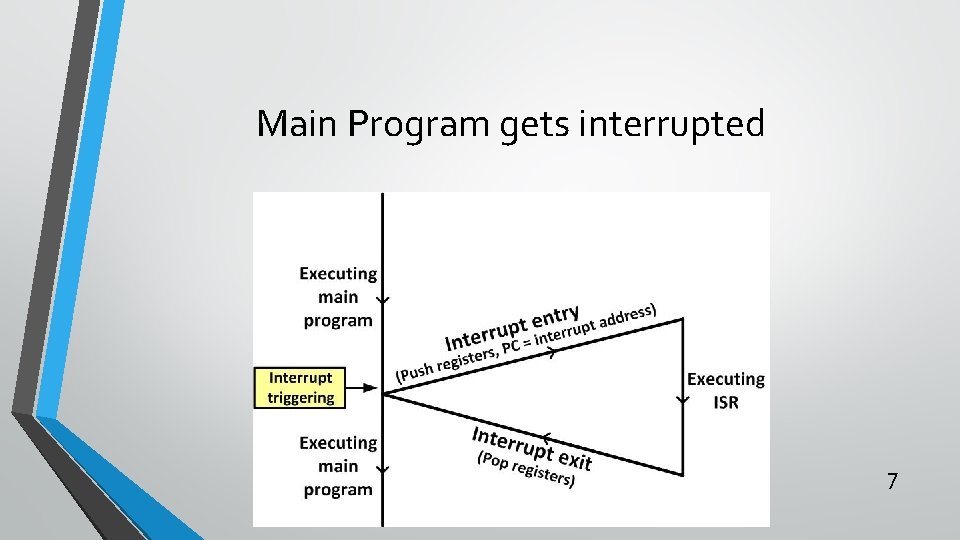

Main Program gets interrupted 7

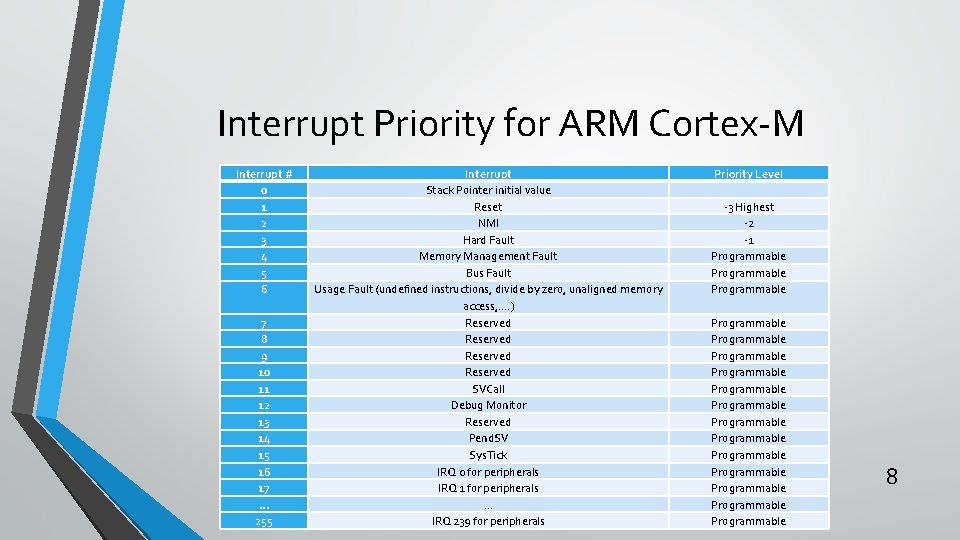

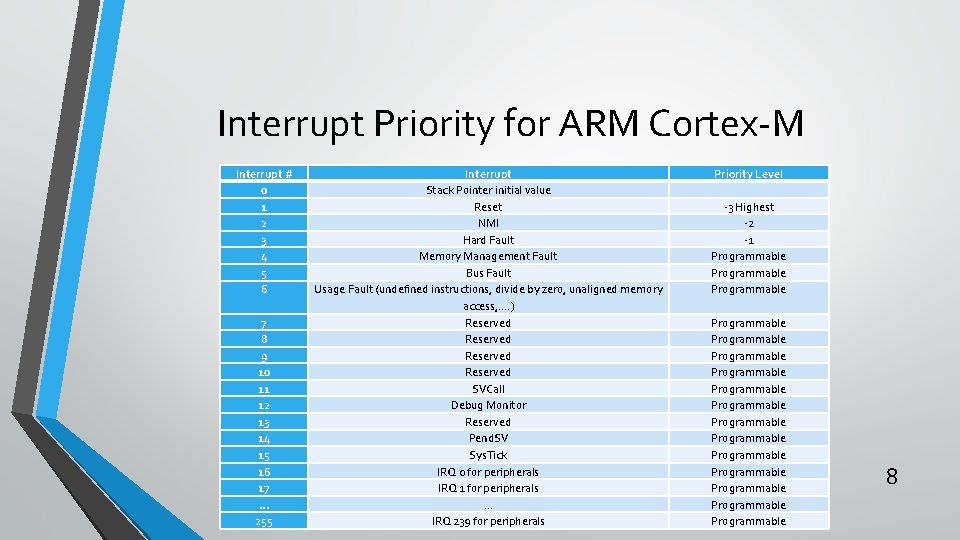

Interrupt Priority for ARM Cortex-M Interrupt # 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Priority Level -3 Highest -2 -1 Programmable Programmable Programmable Programmable 8

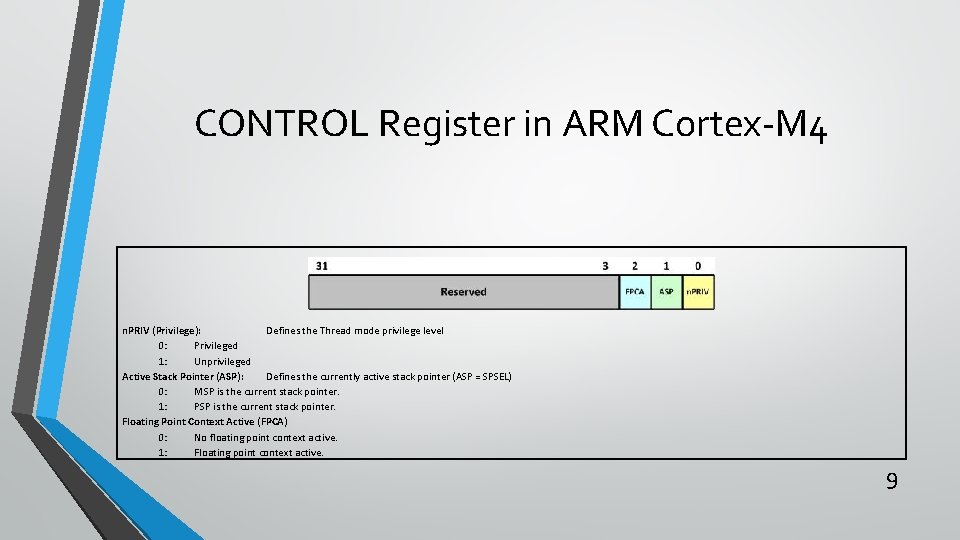

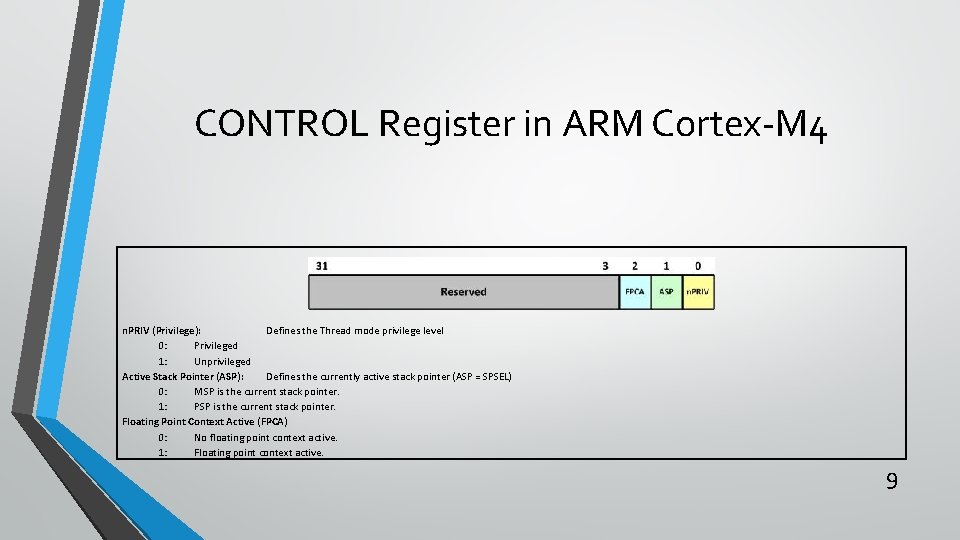

CONTROL Register in ARM Cortex-M 4 n. PRIV (Privilege): Defines the Thread mode privilege level 0: Privileged 1: Unprivileged Active Stack Pointer (ASP): Defines the currently active stack pointer (ASP = SPSEL) 0: MSP is the current stack pointer. 1: PSP is the current stack pointer. Floating Point Context Active (FPCA) 0: No floating point context active. 1: Floating point context active. 9

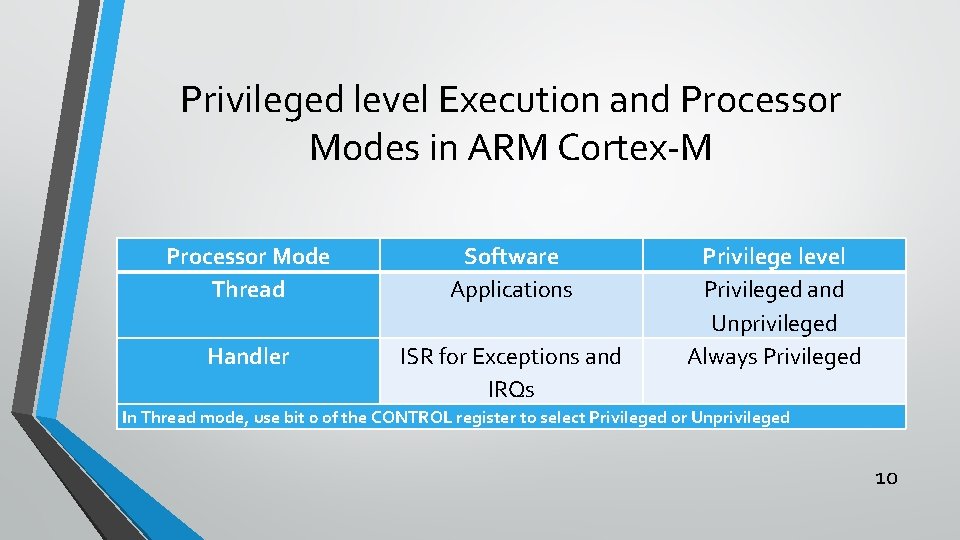

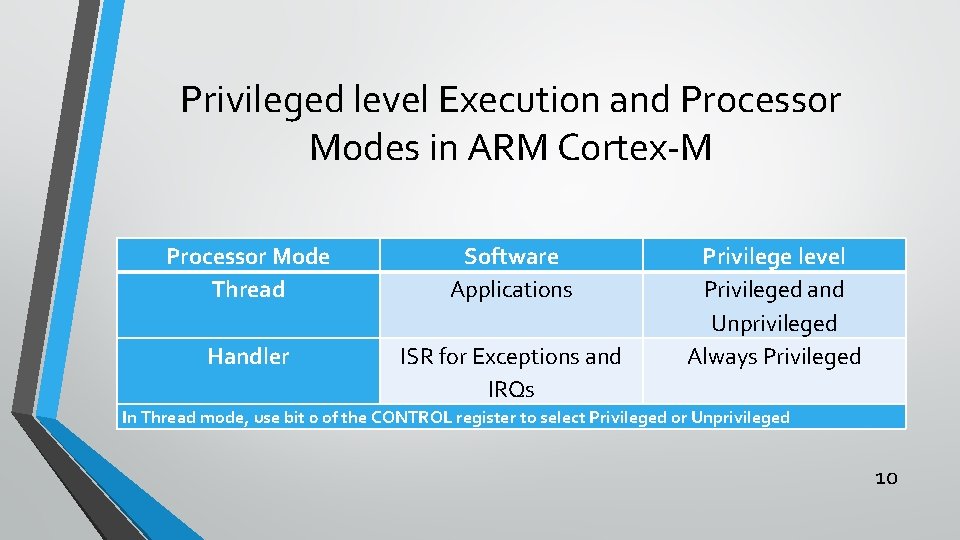

Privileged level Execution and Processor Modes in ARM Cortex-M Processor Mode Thread Software Applications Handler ISR for Exceptions and IRQs Privilege level Privileged and Unprivileged Always Privileged In Thread mode, use bit 0 of the CONTROL register to select Privileged or Unprivileged 10

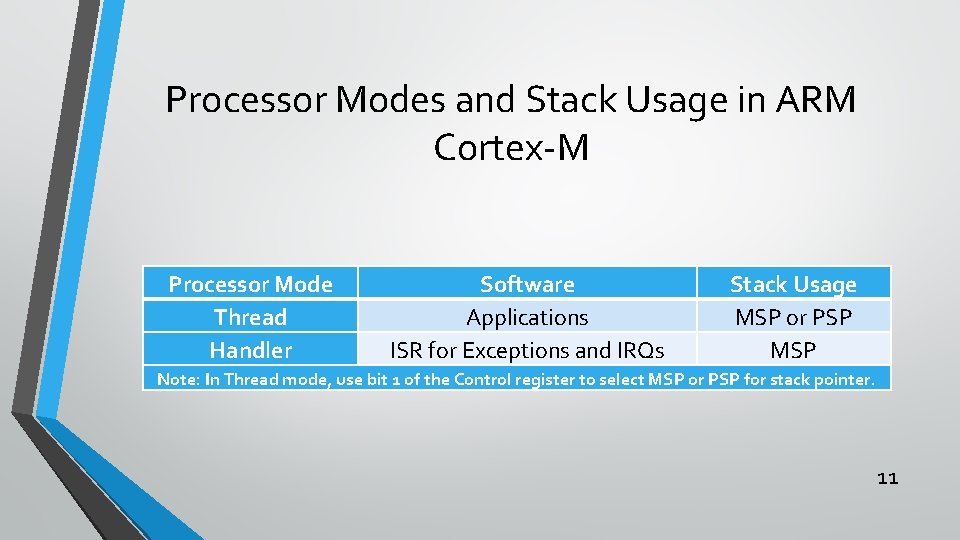

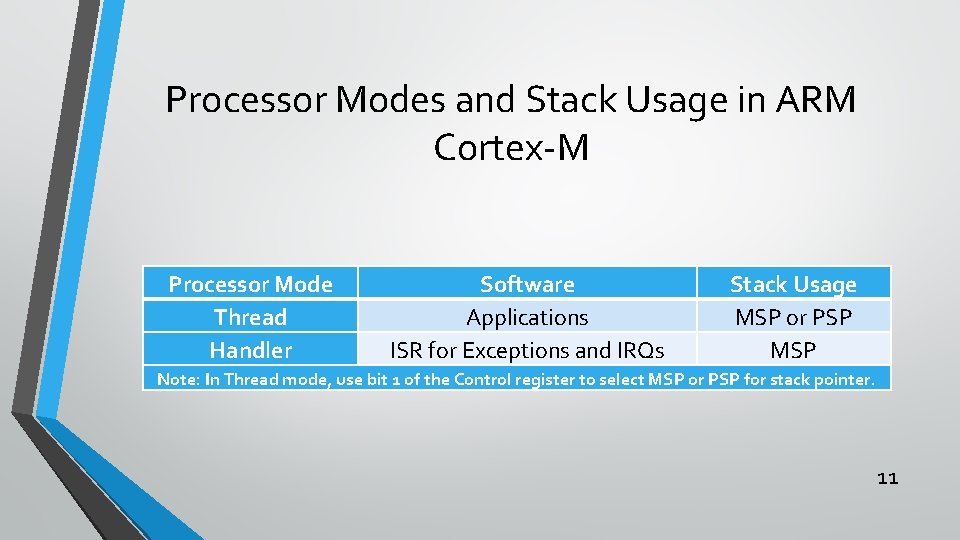

Processor Modes and Stack Usage in ARM Cortex-M Processor Mode Thread Handler Software Applications ISR for Exceptions and IRQs Stack Usage MSP or PSP MSP Note: In Thread mode, use bit 1 of the Control register to select MSP or PSP for stack pointer. 11

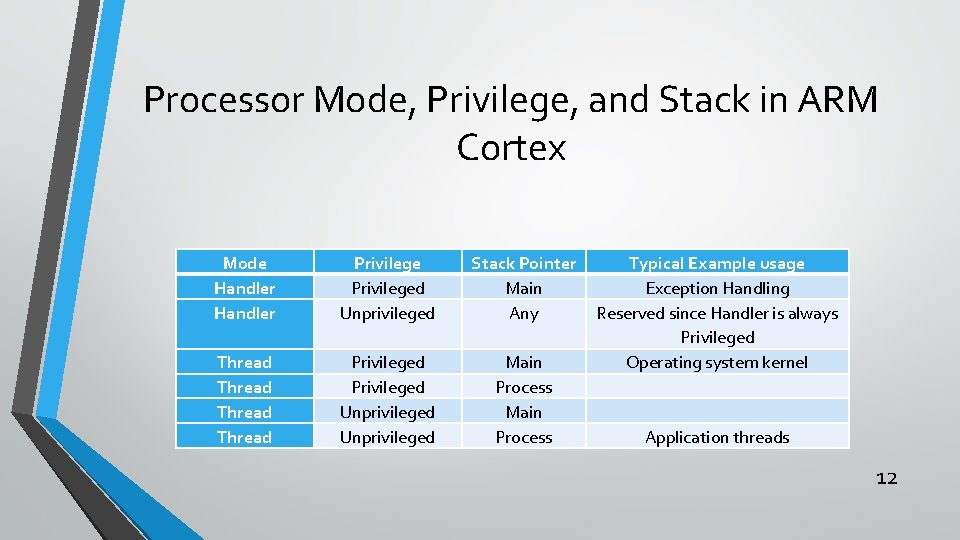

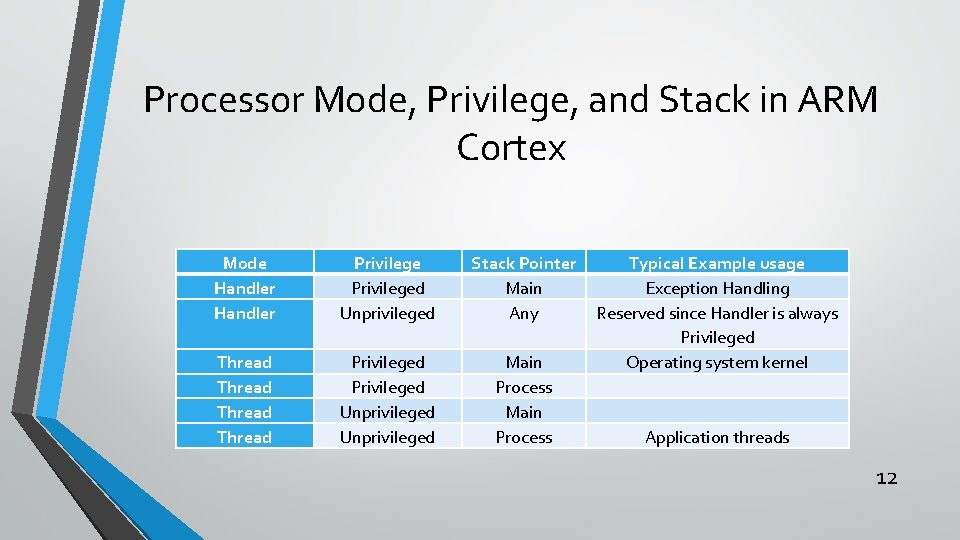

Processor Mode, Privilege, and Stack in ARM Cortex Mode Handler Privileged Unprivileged Stack Pointer Main Any Thread Privileged Unprivileged Main Process Typical Example usage Exception Handling Reserved since Handler is always Privileged Operating system kernel Application threads 12

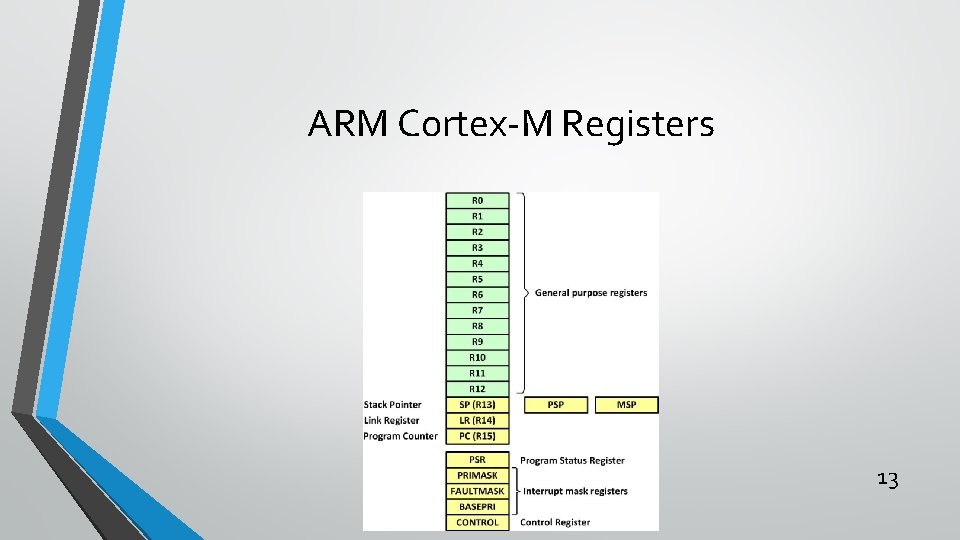

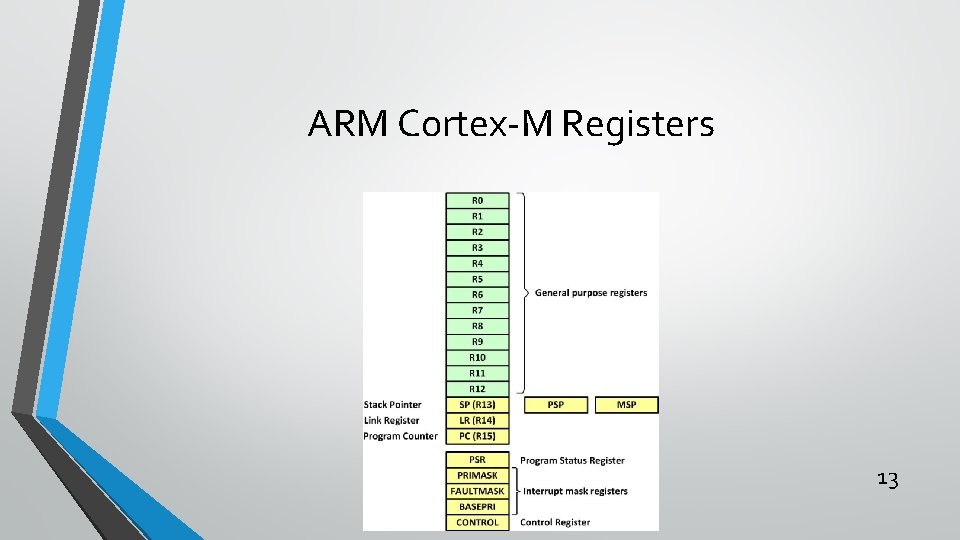

ARM Cortex-M Registers 13

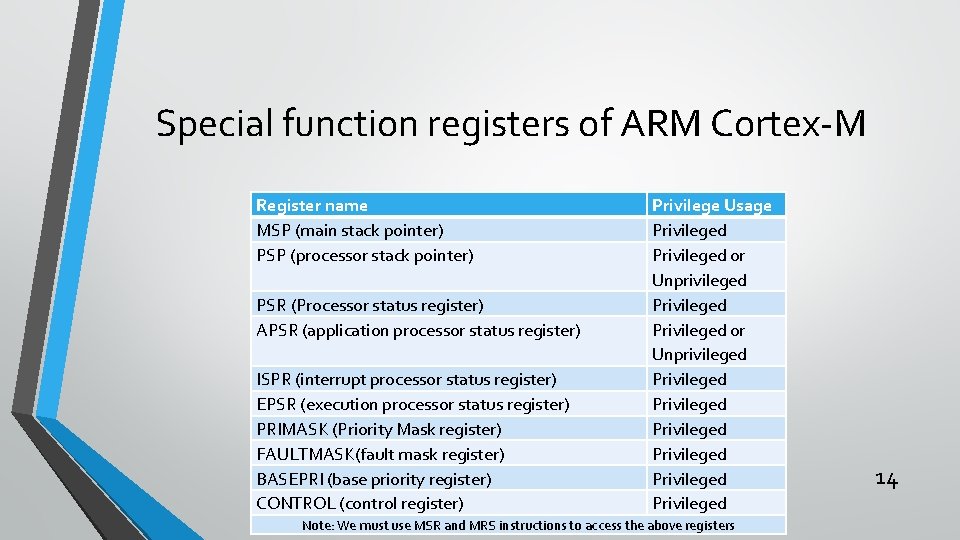

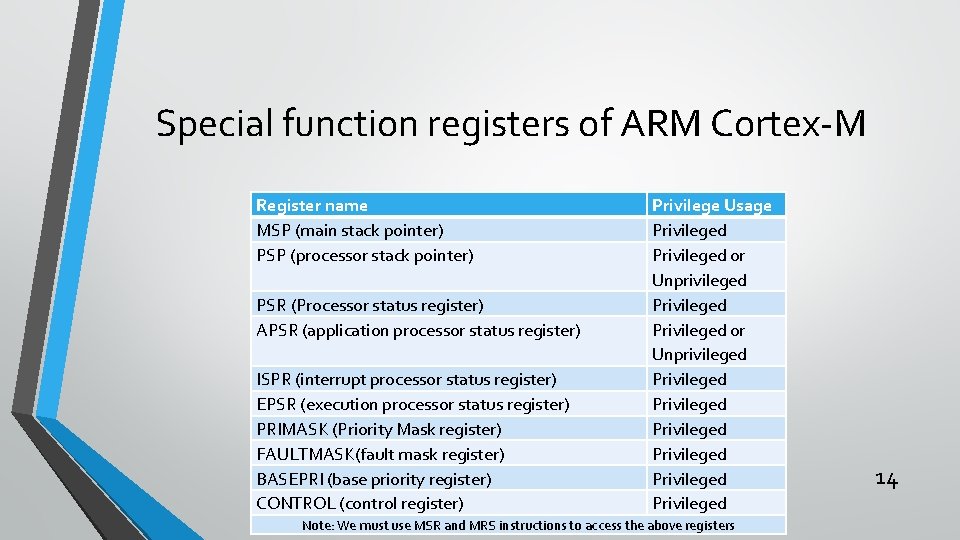

Special function registers of ARM Cortex-M Register name MSP (main stack pointer) PSP (processor stack pointer) PSR (Processor status register) APSR (application processor status register) ISPR (interrupt processor status register) EPSR (execution processor status register) PRIMASK (Priority Mask register) FAULTMASK(fault mask register) BASEPRI (base priority register) CONTROL (control register) Privilege Usage Privileged or Unprivileged Privileged Privileged Note: We must use MSR and MRS instructions to access the above registers 14

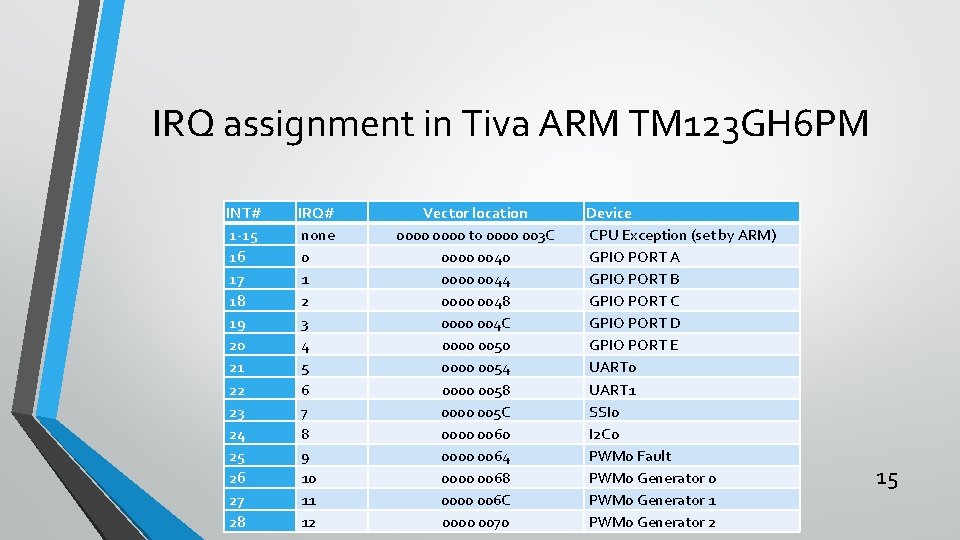

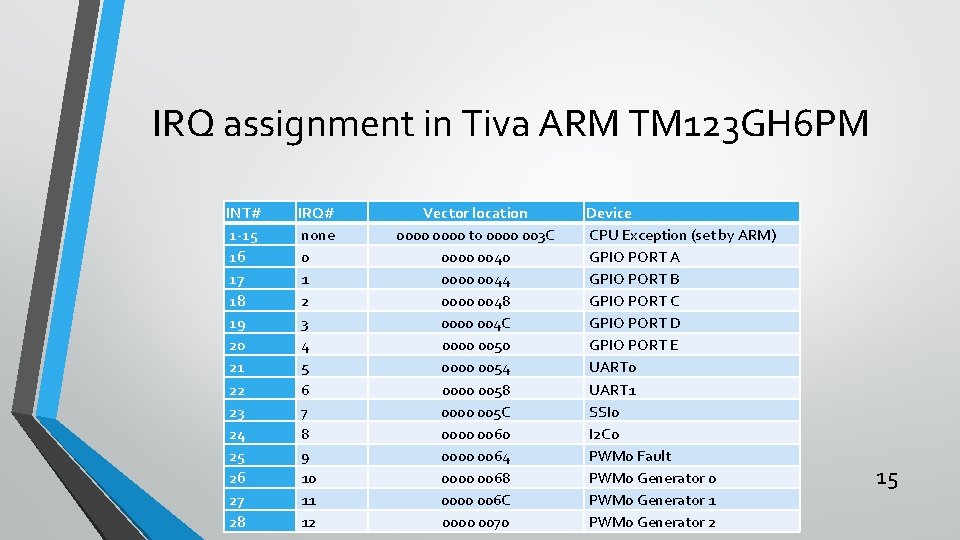

IRQ assignment in Tiva ARM TM 123 GH 6 PM INT# 1 -15 16 17 18 19 20 21 22 23 24 25 26 27 28 IRQ# none 0 1 2 3 4 5 6 7 8 9 10 11 12 Vector location 0000 to 0000 003 C 0000 0040 0000 0044 0000 0048 0000 004 C 0000 0050 0000 0054 0000 0058 0000 005 C 0000 0060 0000 0064 0000 0068 0000 006 C 0000 0070 Device CPU Exception (set by ARM) GPIO PORT A GPIO PORT B GPIO PORT C GPIO PORT D GPIO PORT E UART 0 UART 1 SSI 0 I 2 C 0 PWM 0 Fault PWM 0 Generator 0 PWM 0 Generator 1 PWM 0 Generator 2 15

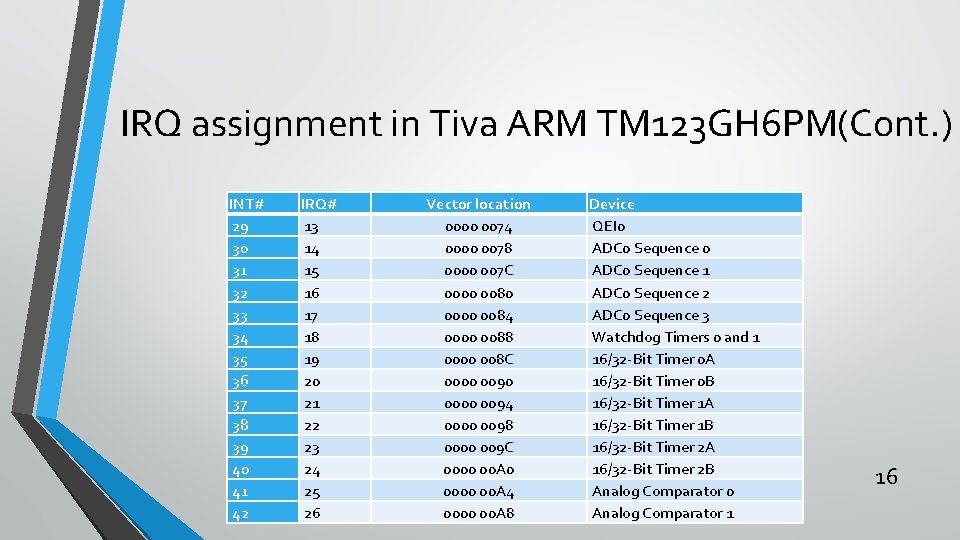

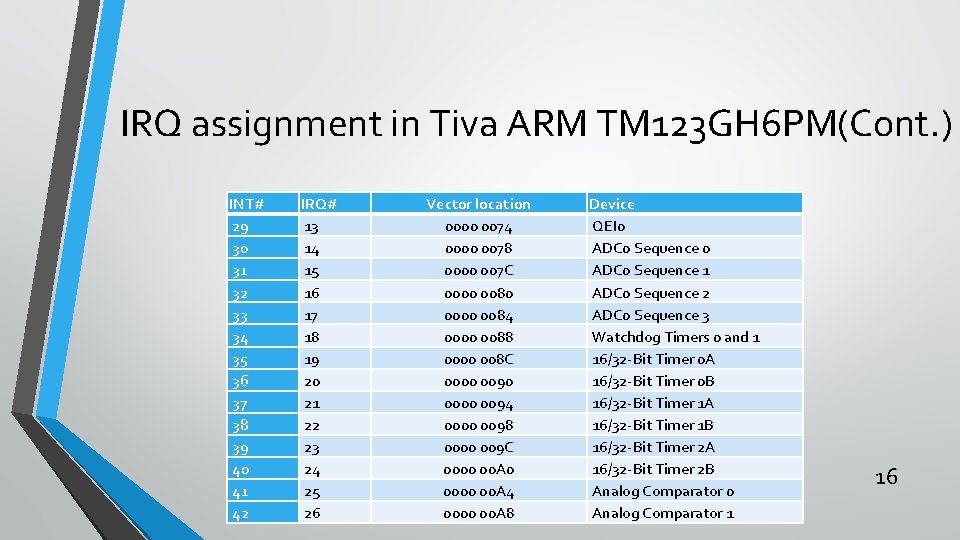

IRQ assignment in Tiva ARM TM 123 GH 6 PM(Cont. ) INT# 29 30 31 32 33 34 35 36 37 38 39 40 41 42 IRQ# 13 14 15 16 17 18 19 20 21 22 23 24 25 26 Vector location 0000 0074 0000 0078 0000 007 C 0000 0080 0000 0084 0000 0088 0000 008 C 0000 0090 0000 0094 0000 0098 0000 009 C 0000 00 A 0 0000 00 A 4 0000 00 A 8 Device QEI 0 ADC 0 Sequence 1 ADC 0 Sequence 2 ADC 0 Sequence 3 Watchdog Timers 0 and 1 16/32 -Bit Timer 0 A 16/32 -Bit Timer 0 B 16/32 -Bit Timer 1 A 16/32 -Bit Timer 1 B 16/32 -Bit Timer 2 A 16/32 -Bit Timer 2 B Analog Comparator 0 Analog Comparator 1 16

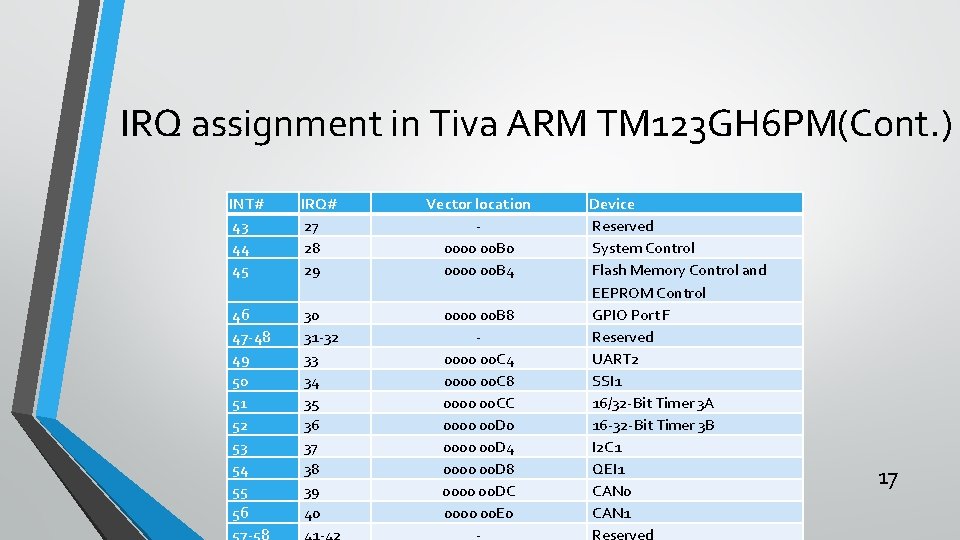

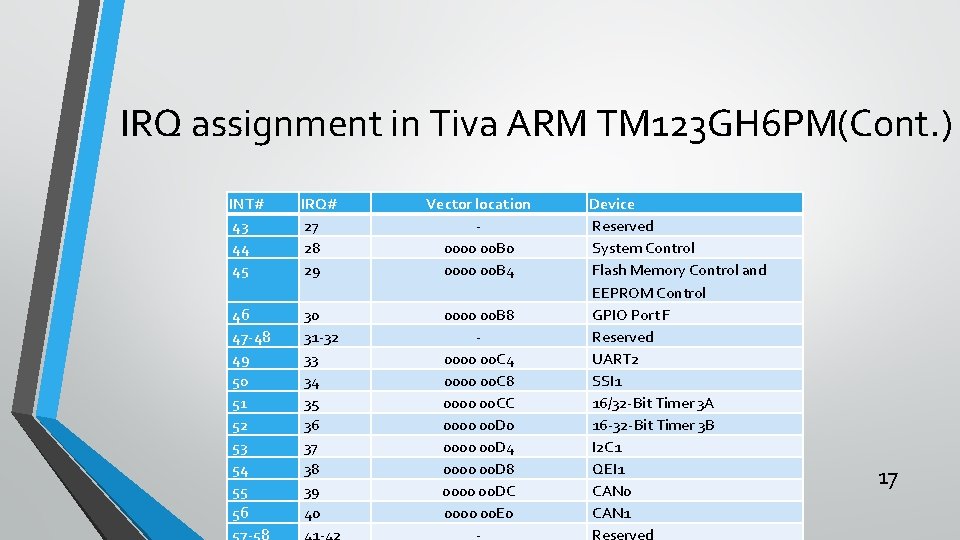

IRQ assignment in Tiva ARM TM 123 GH 6 PM(Cont. ) INT# 43 44 45 IRQ# 27 28 29 Vector location 0000 00 B 0 0000 00 B 4 46 47 -48 49 50 51 52 53 54 55 56 30 31 -32 33 34 35 36 37 38 39 40 0000 00 B 8 0000 00 C 4 0000 00 C 8 0000 00 CC 0000 00 D 0 0000 00 D 4 0000 00 D 8 0000 00 DC 0000 00 E 0 Device Reserved System Control Flash Memory Control and EEPROM Control GPIO Port F Reserved UART 2 SSI 1 16/32 -Bit Timer 3 A 16 -32 -Bit Timer 3 B I 2 C 1 QEI 1 CAN 0 CAN 1 17

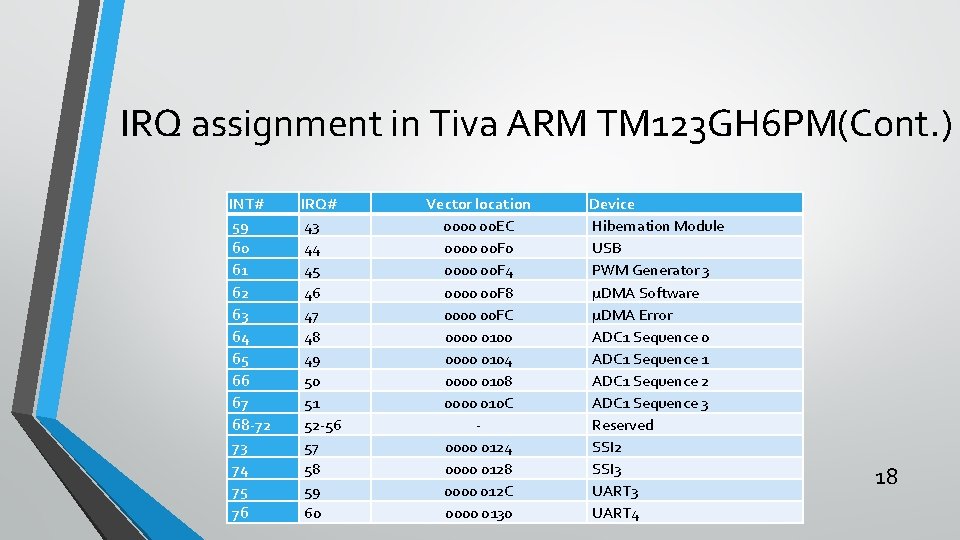

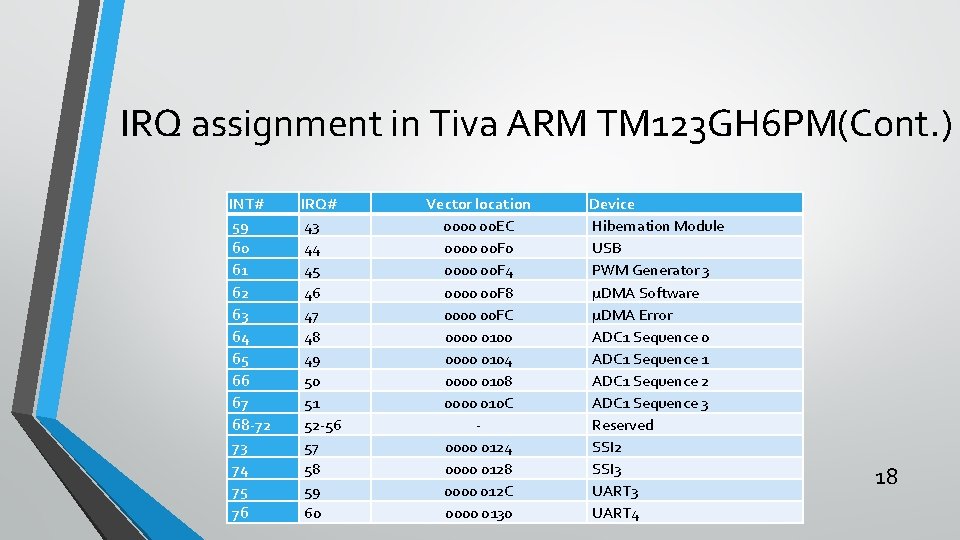

IRQ assignment in Tiva ARM TM 123 GH 6 PM(Cont. ) INT# 59 60 61 62 63 64 65 66 67 68 -72 73 74 75 76 IRQ# 43 44 45 46 47 48 49 50 51 52 -56 57 58 59 60 Vector location 0000 00 EC 0000 00 F 0 0000 00 F 4 0000 00 F 8 0000 00 FC 0000 0100 0000 0104 0000 0108 0000 010 C 0000 0124 0000 0128 0000 012 C 0000 0130 Device Hibernation Module USB PWM Generator 3 µDMA Software µDMA Error ADC 1 Sequence 0 ADC 1 Sequence 1 ADC 1 Sequence 2 ADC 1 Sequence 3 Reserved SSI 2 SSI 3 UART 4 18

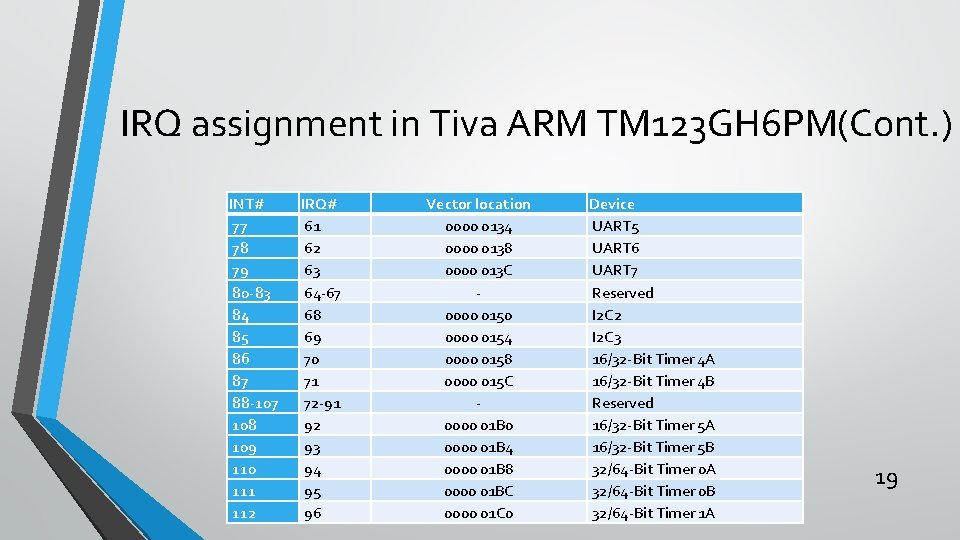

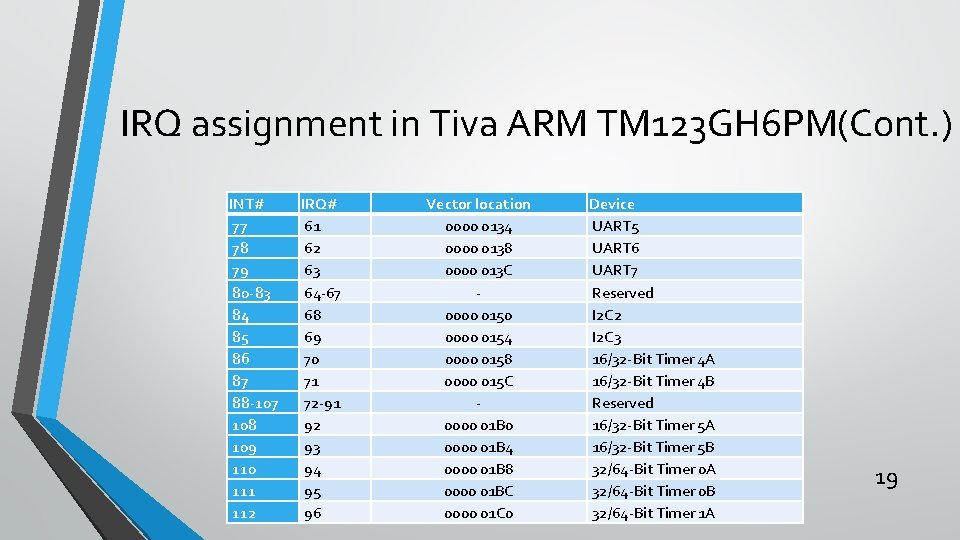

IRQ assignment in Tiva ARM TM 123 GH 6 PM(Cont. ) INT# 77 78 79 80 -83 84 85 86 87 88 -107 108 109 110 111 112 IRQ# 61 62 63 64 -67 68 69 70 71 72 -91 92 93 94 95 96 Vector location 0000 0134 0000 0138 0000 013 C 0000 0150 0000 0154 0000 0158 0000 015 C 0000 01 B 0 0000 01 B 4 0000 01 B 8 0000 01 BC 0000 01 C 0 Device UART 5 UART 6 UART 7 Reserved I 2 C 2 I 2 C 3 16/32 -Bit Timer 4 A 16/32 -Bit Timer 4 B Reserved 16/32 -Bit Timer 5 A 16/32 -Bit Timer 5 B 32/64 -Bit Timer 0 A 32/64 -Bit Timer 0 B 32/64 -Bit Timer 1 A 19

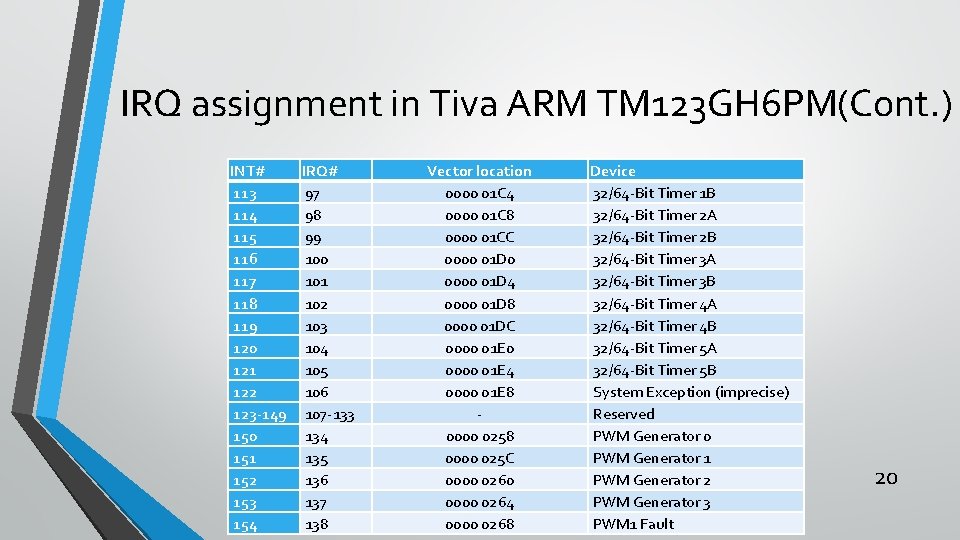

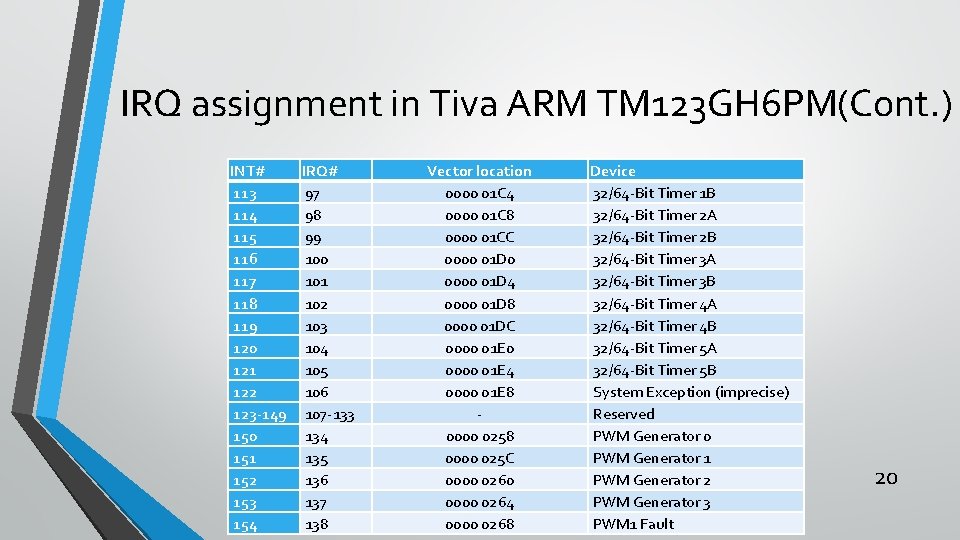

IRQ assignment in Tiva ARM TM 123 GH 6 PM(Cont. ) INT# IRQ# 113 97 114 98 115 99 116 100 117 101 118 102 119 103 120 104 121 105 122 106 123 -149 107 -133 150 134 151 135 152 136 153 137 154 138 Vector location 0000 01 C 4 0000 01 C 8 0000 01 CC 0000 01 D 0 0000 01 D 4 0000 01 D 8 0000 01 DC 0000 01 E 0 0000 01 E 4 0000 01 E 8 0000 025 C 0000 0260 0000 0264 0000 0268 Device 32/64 -Bit Timer 1 B 32/64 -Bit Timer 2 A 32/64 -Bit Timer 2 B 32/64 -Bit Timer 3 A 32/64 -Bit Timer 3 B 32/64 -Bit Timer 4 A 32/64 -Bit Timer 4 B 32/64 -Bit Timer 5 A 32/64 -Bit Timer 5 B System Exception (imprecise) Reserved PWM Generator 0 PWM Generator 1 PWM Generator 2 PWM Generator 3 PWM 1 Fault 20

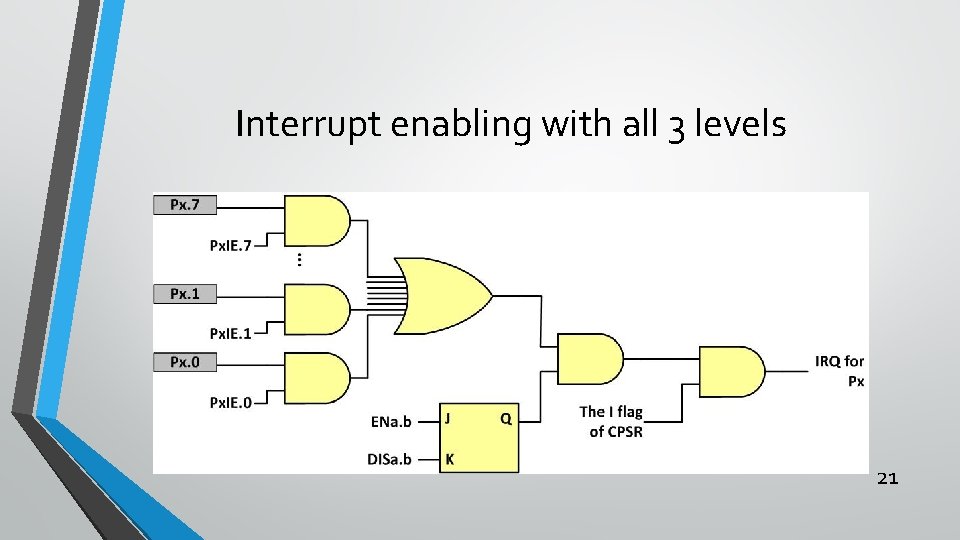

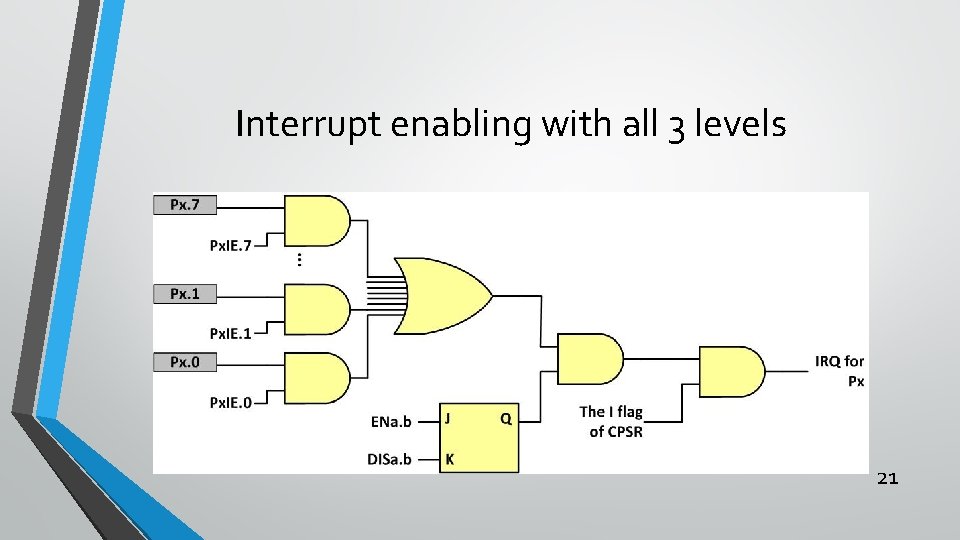

Interrupt enabling with all 3 levels 21

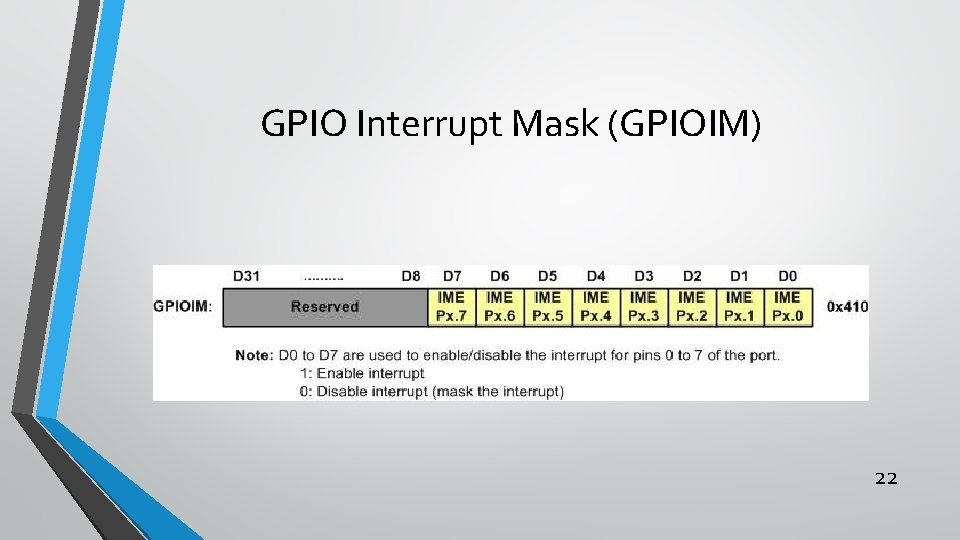

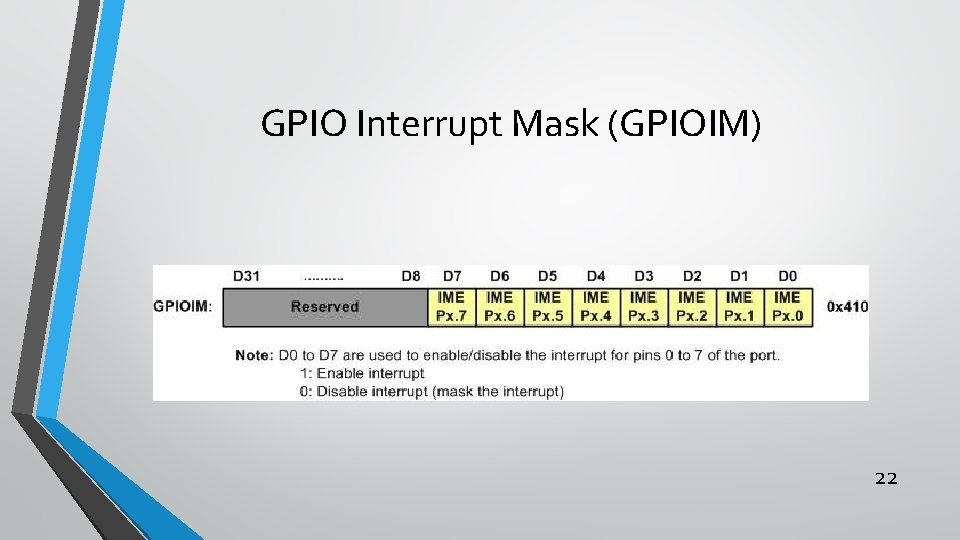

GPIO Interrupt Mask (GPIOIM) 22

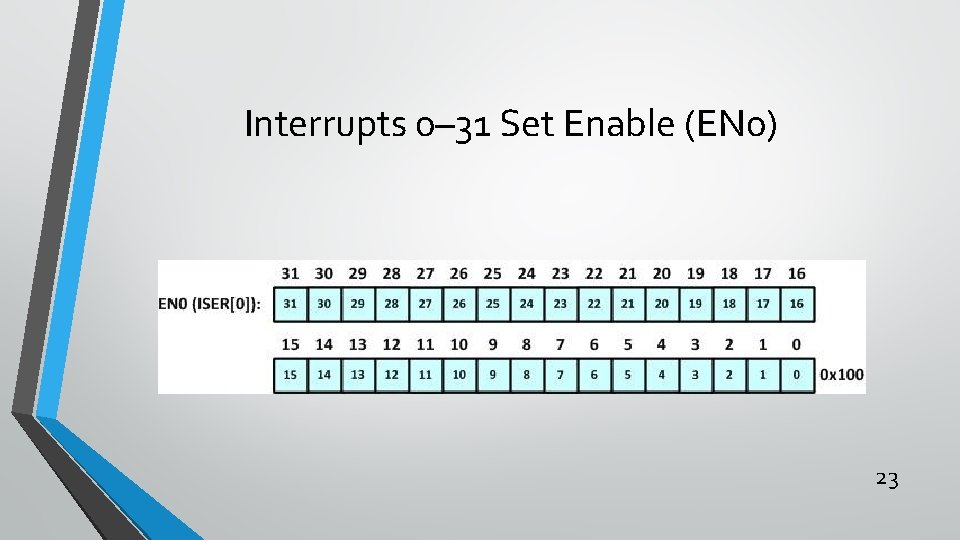

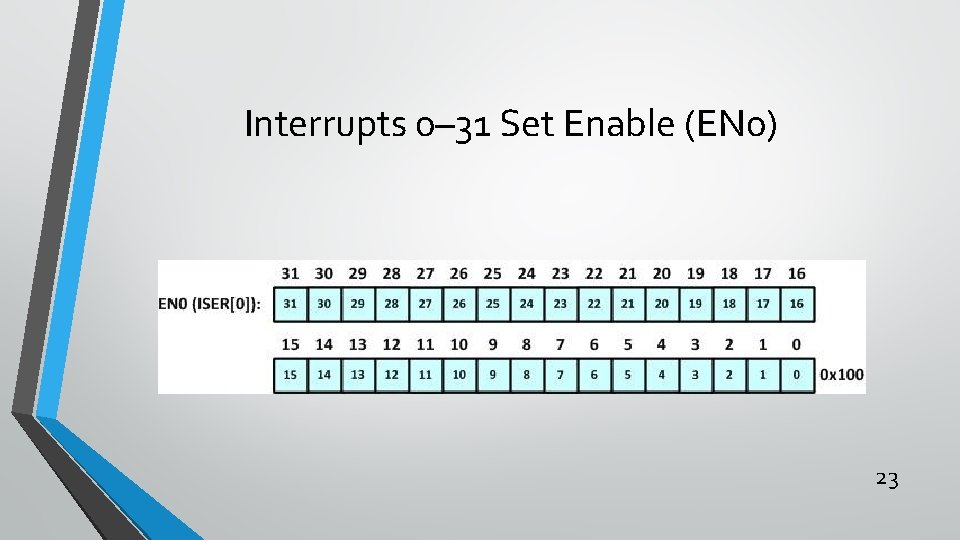

Interrupts 0– 31 Set Enable (EN 0) 23

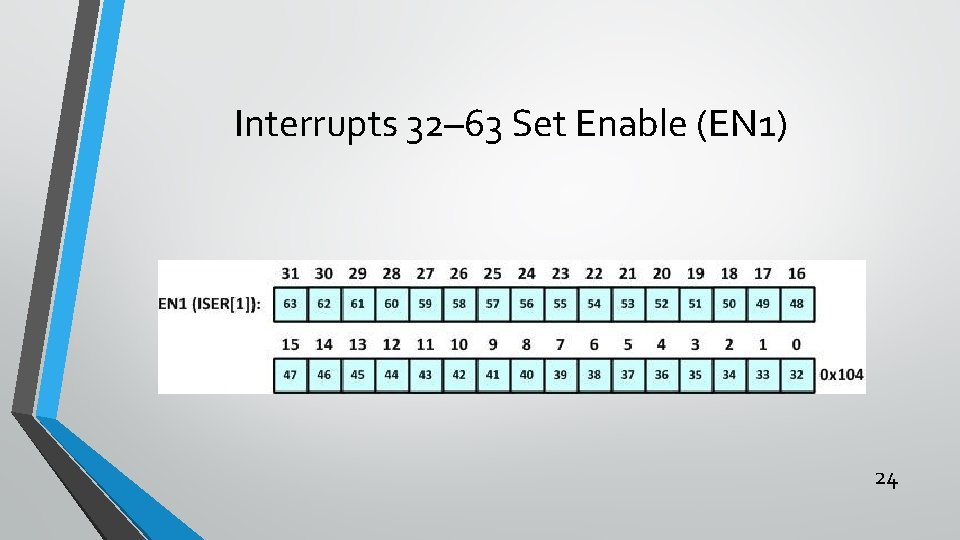

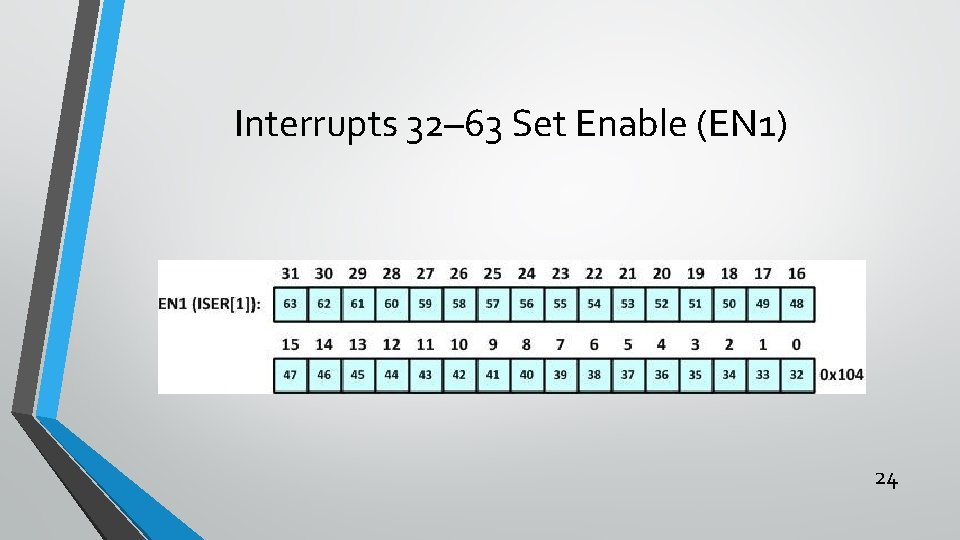

Interrupts 32– 63 Set Enable (EN 1) 24

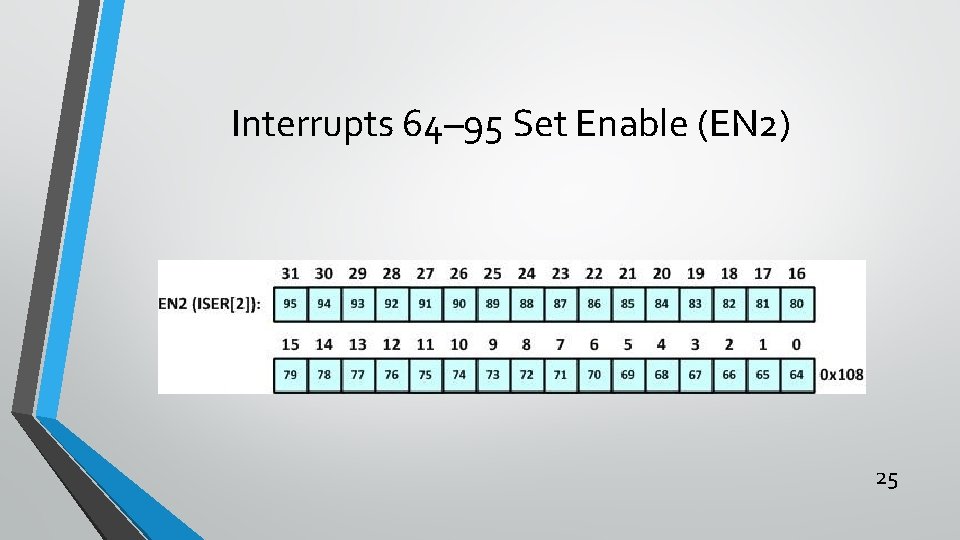

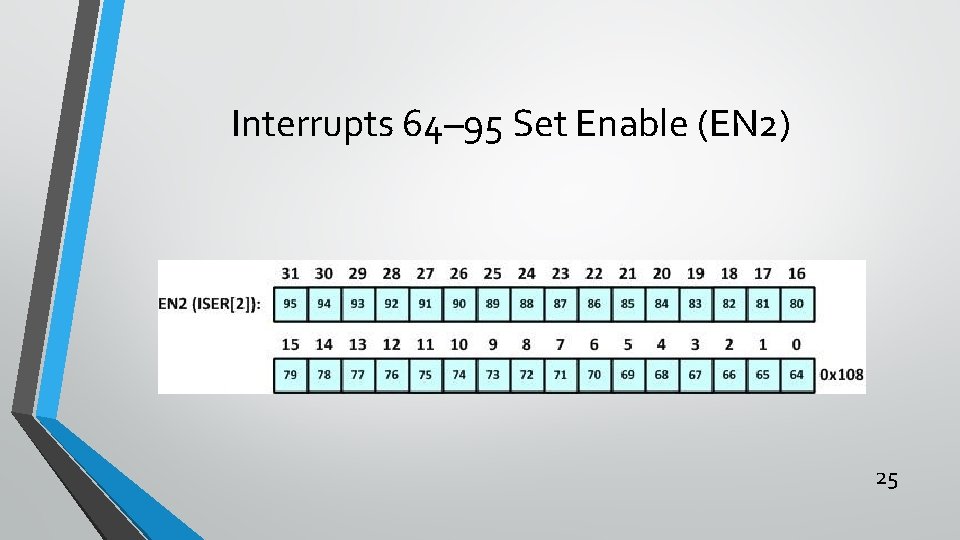

Interrupts 64– 95 Set Enable (EN 2) 25

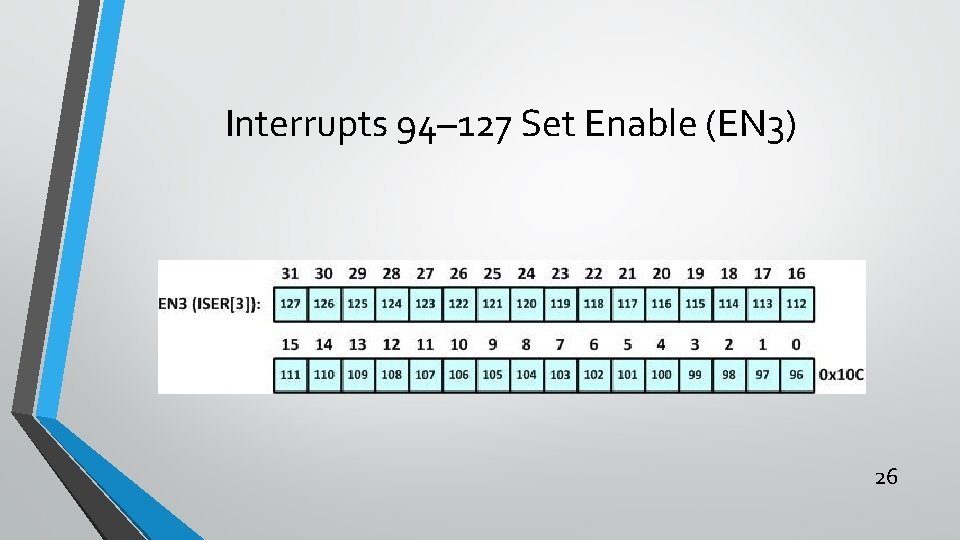

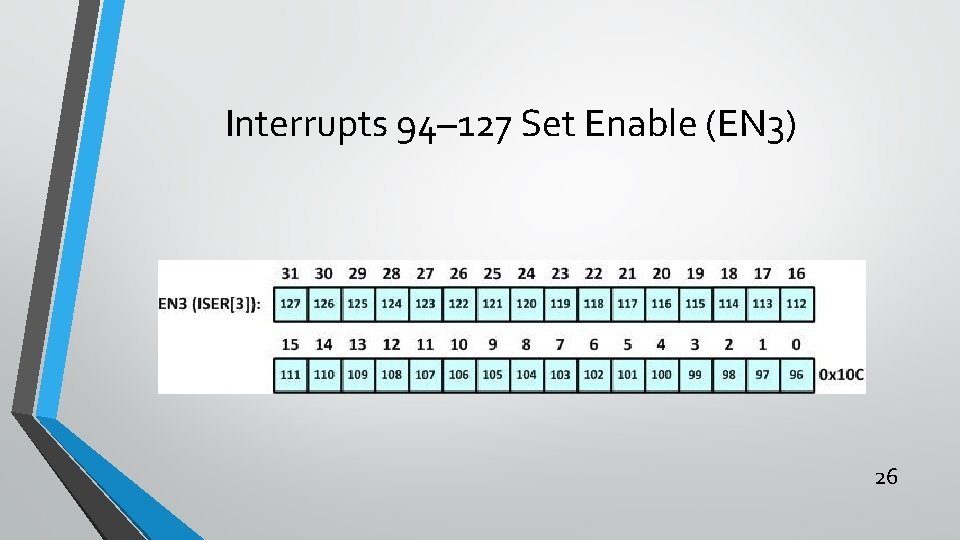

Interrupts 94– 127 Set Enable (EN 3) 26

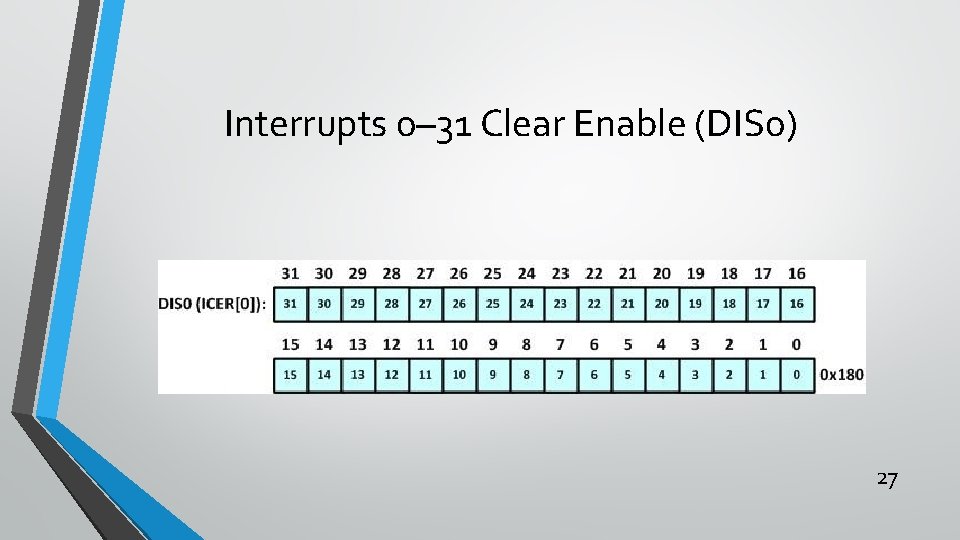

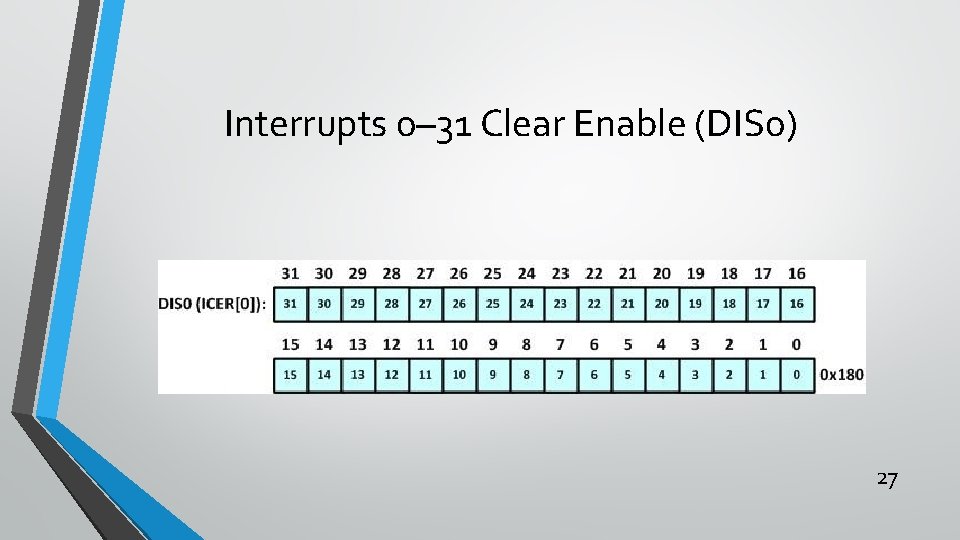

Interrupts 0– 31 Clear Enable (DIS 0) 27

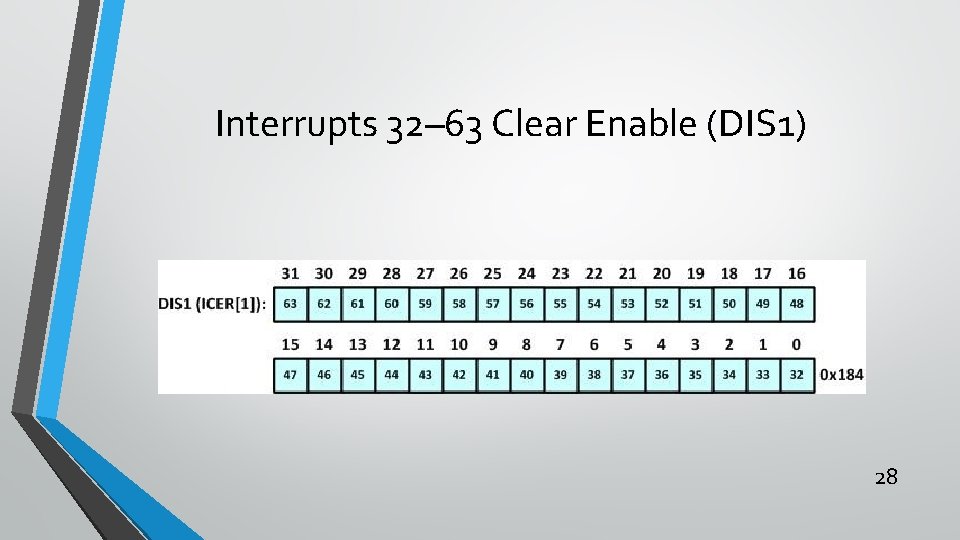

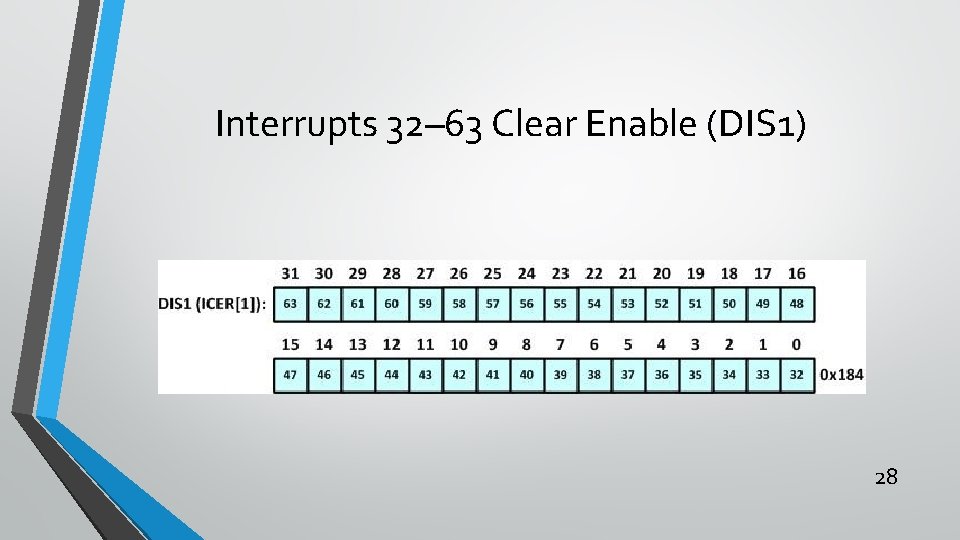

Interrupts 32– 63 Clear Enable (DIS 1) 28

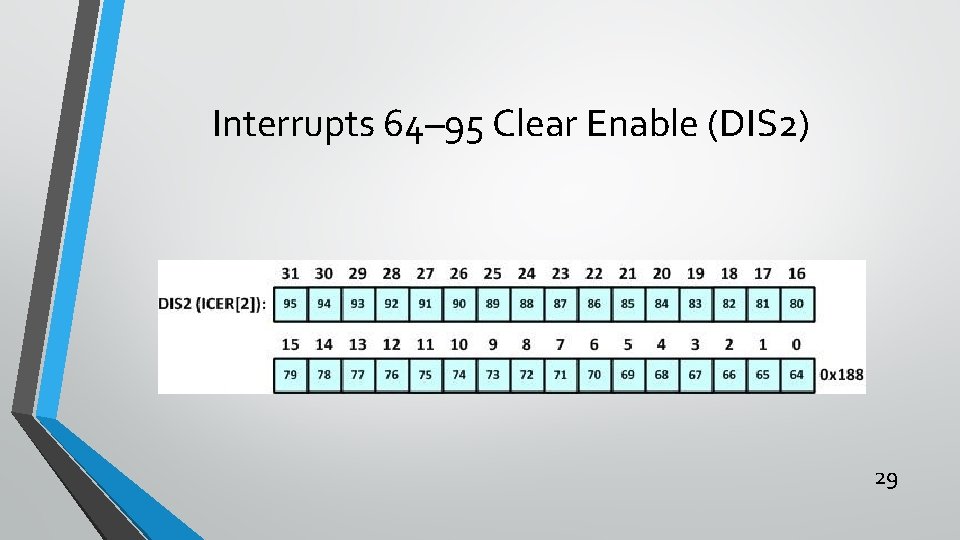

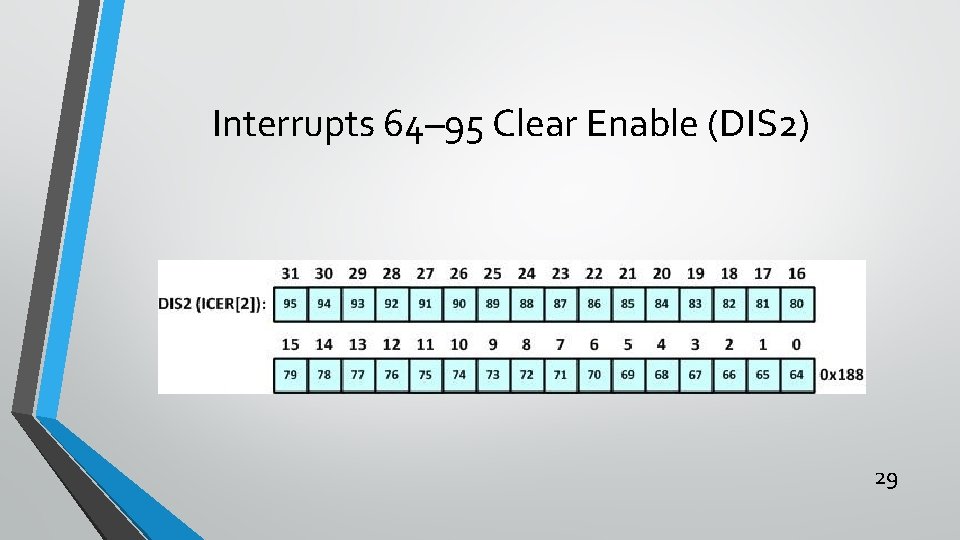

Interrupts 64– 95 Clear Enable (DIS 2) 29

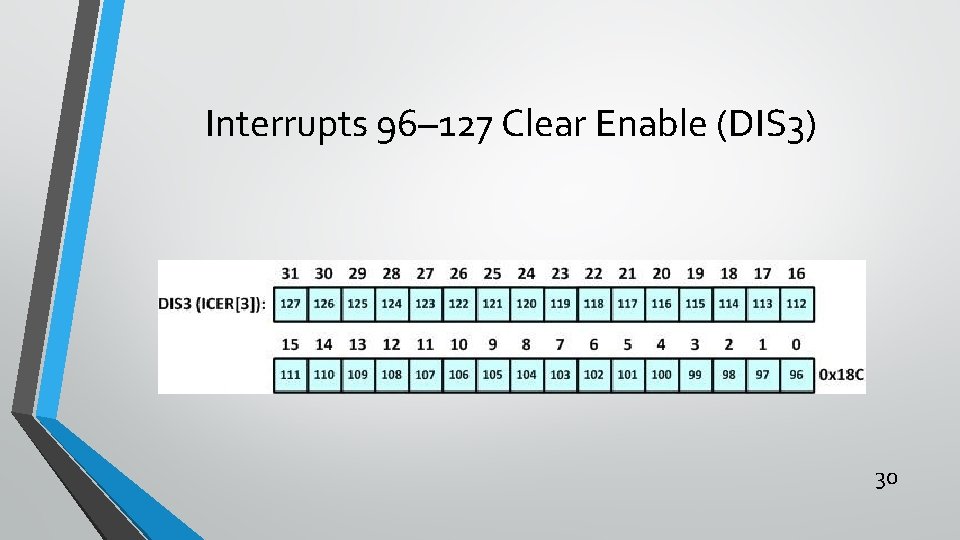

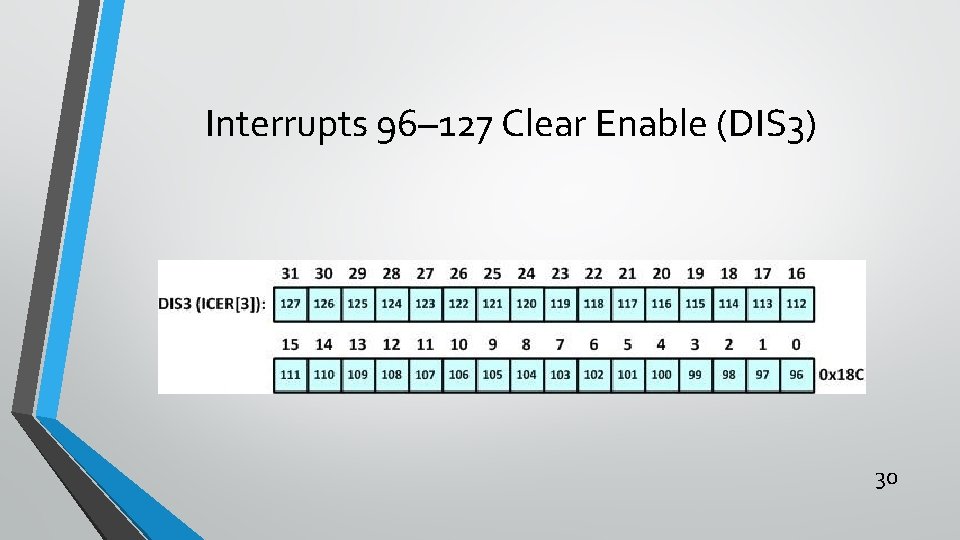

Interrupts 96– 127 Clear Enable (DIS 3) 30

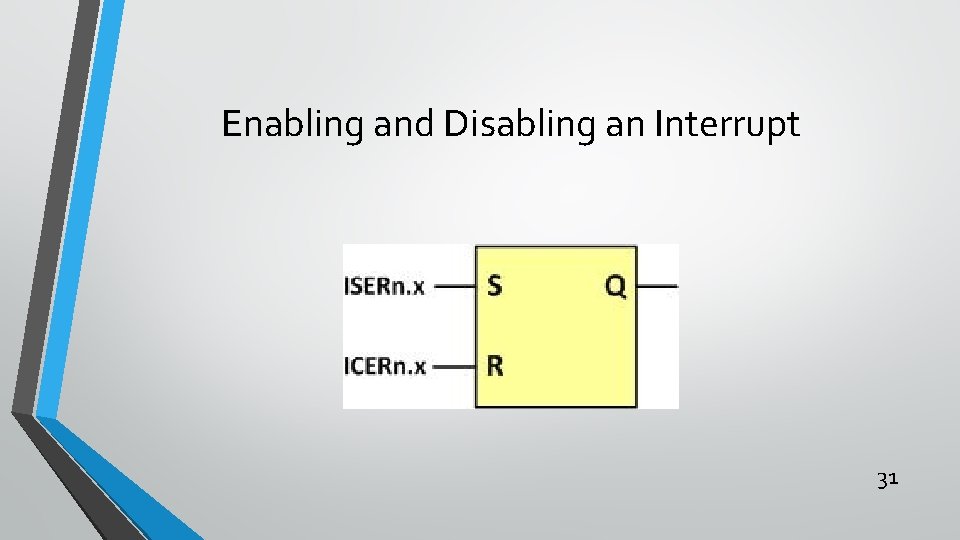

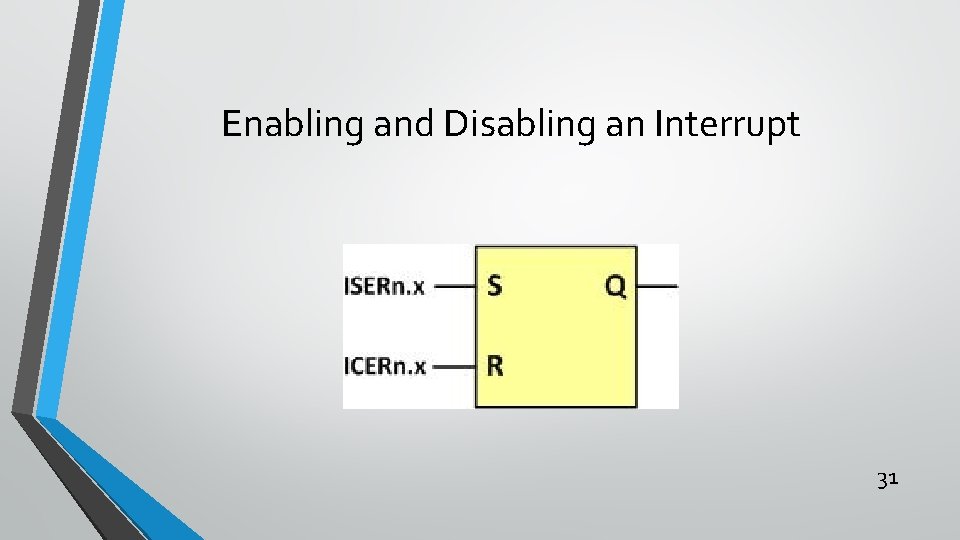

Enabling and Disabling an Interrupt 31

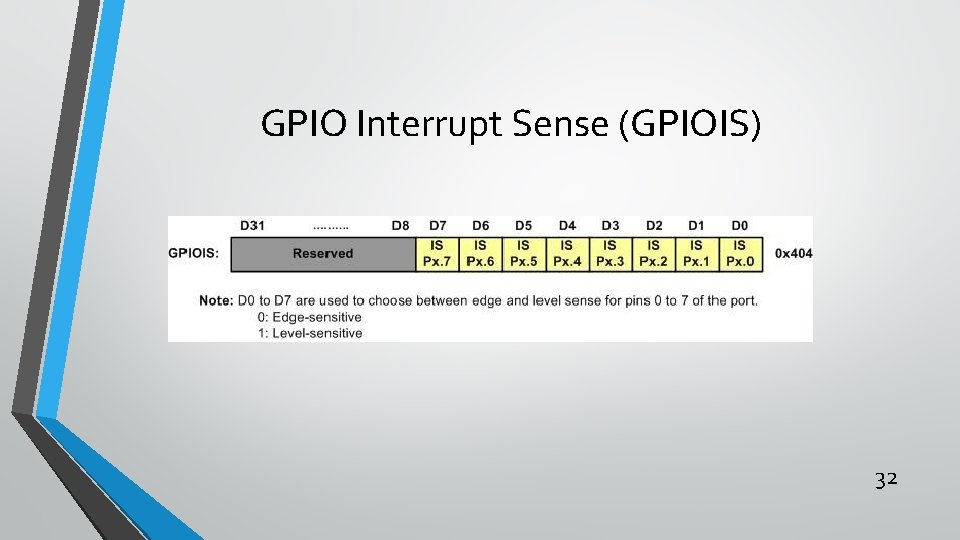

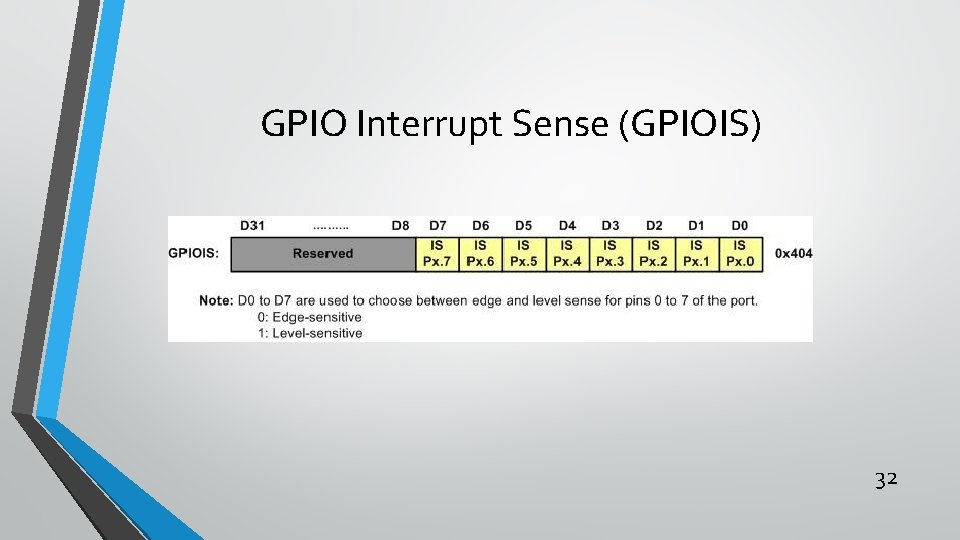

GPIO Interrupt Sense (GPIOIS) 32

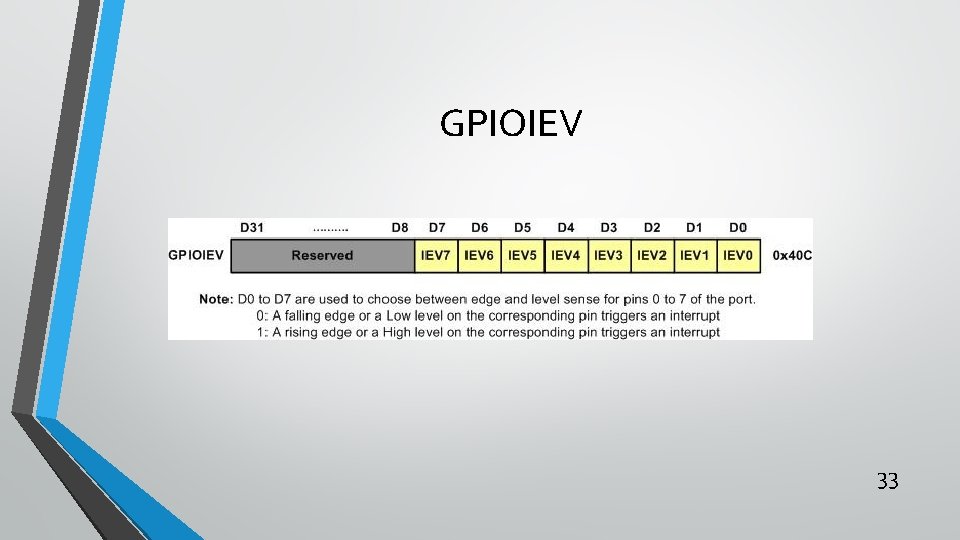

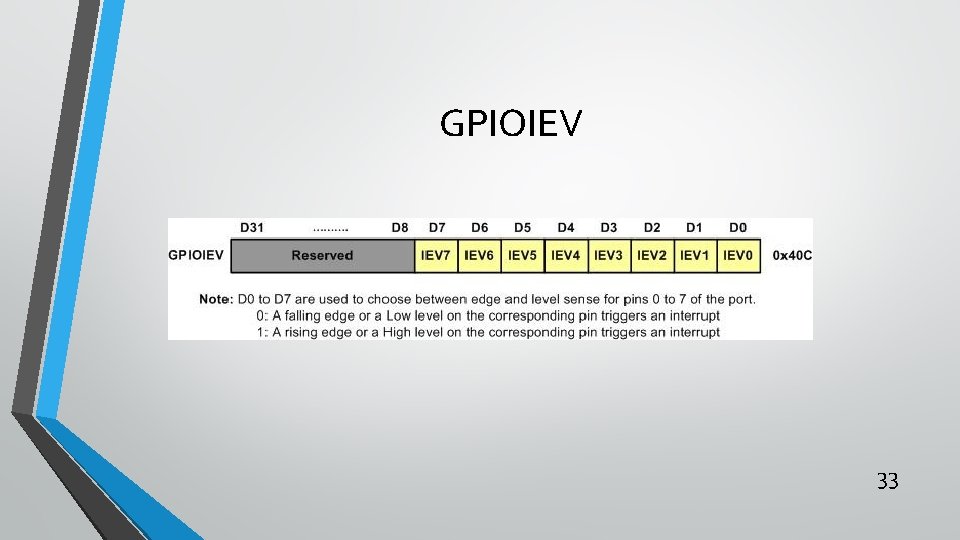

GPIOIEV 33

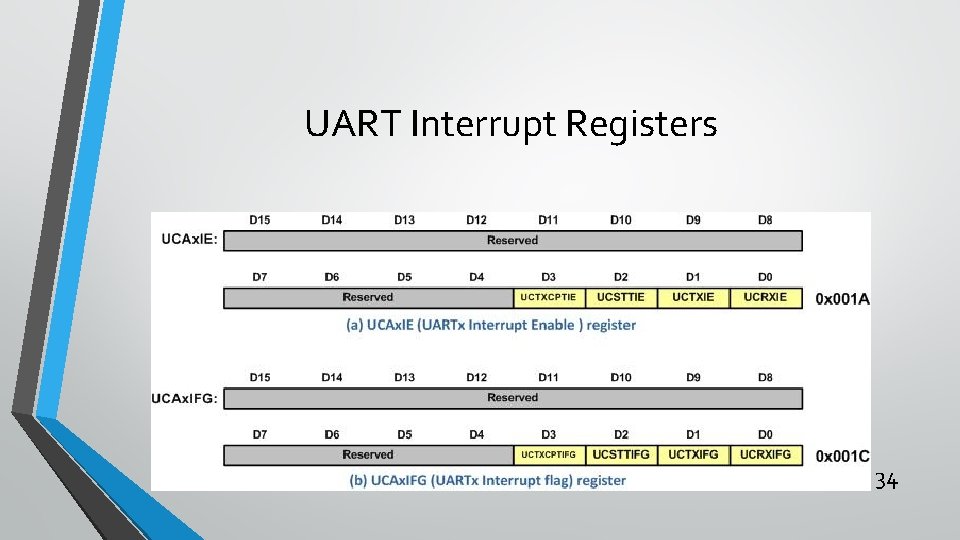

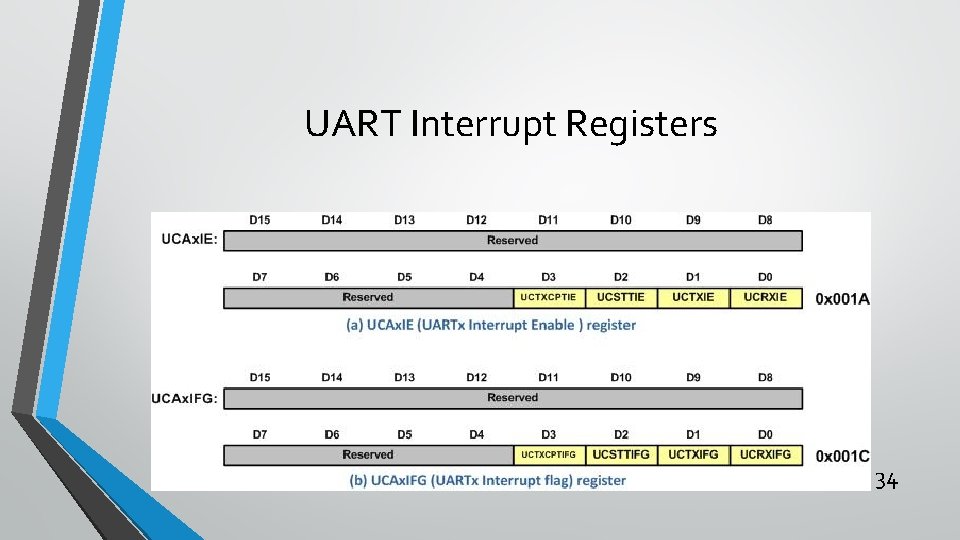

UART Interrupt Registers 34

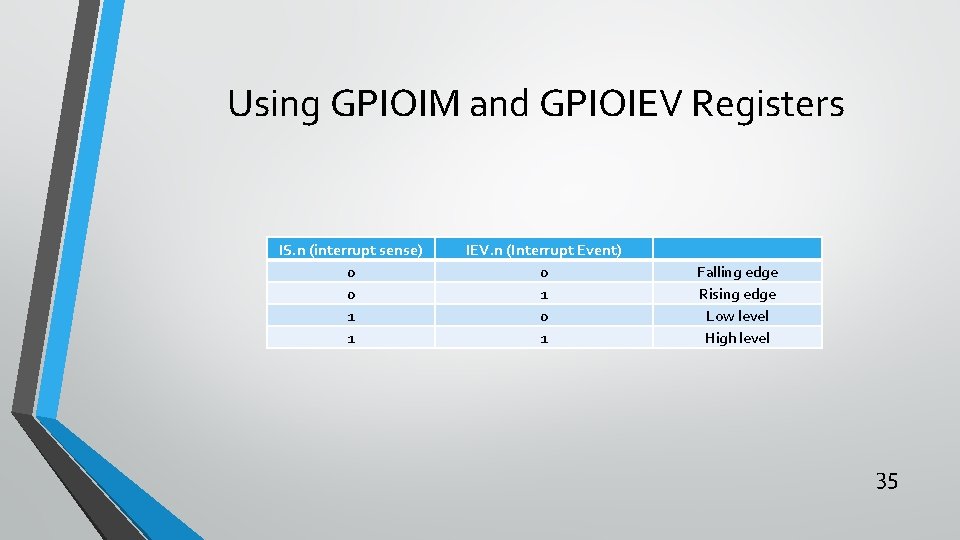

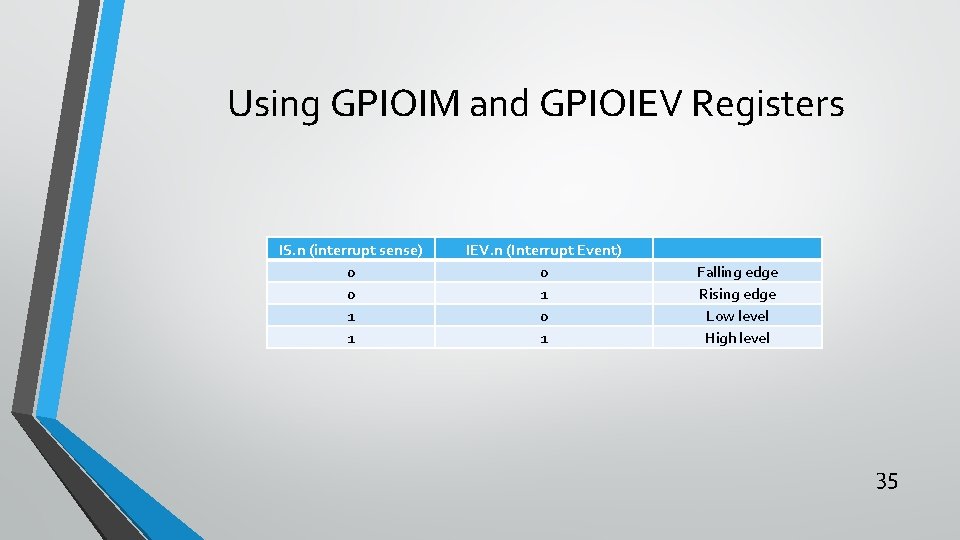

Using GPIOIM and GPIOIEV Registers IS. n (interrupt sense) 0 0 1 1 IEV. n (Interrupt Event) 0 1 Falling edge Rising edge Low level High level 35

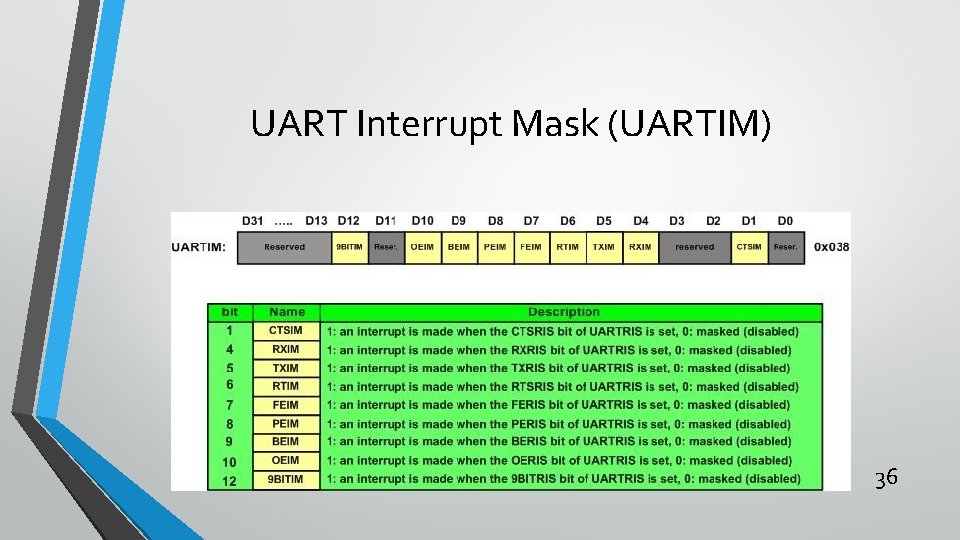

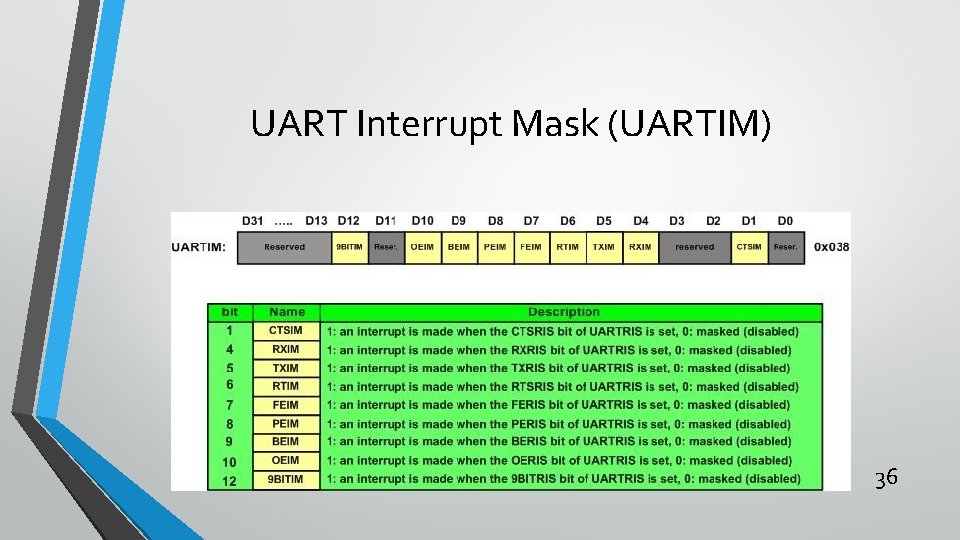

UART Interrupt Mask (UARTIM) 36

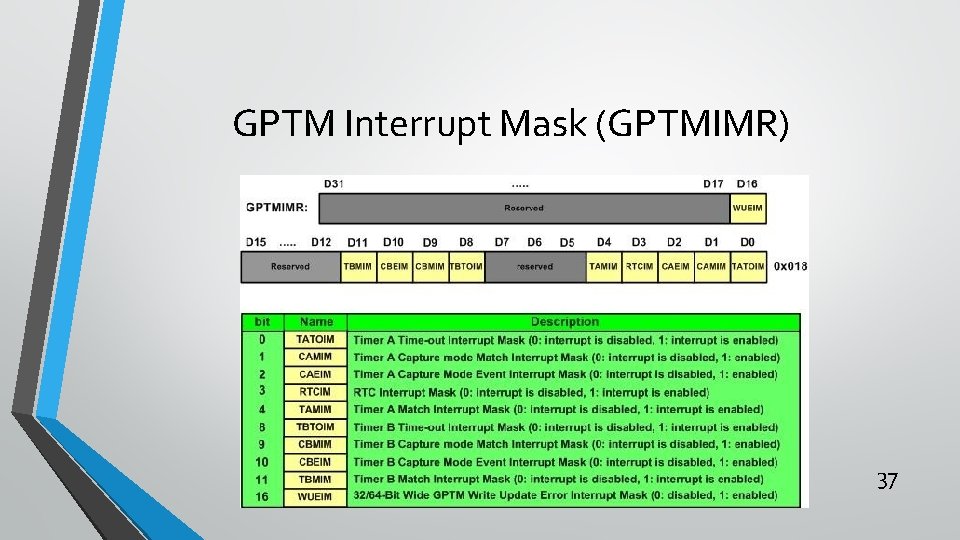

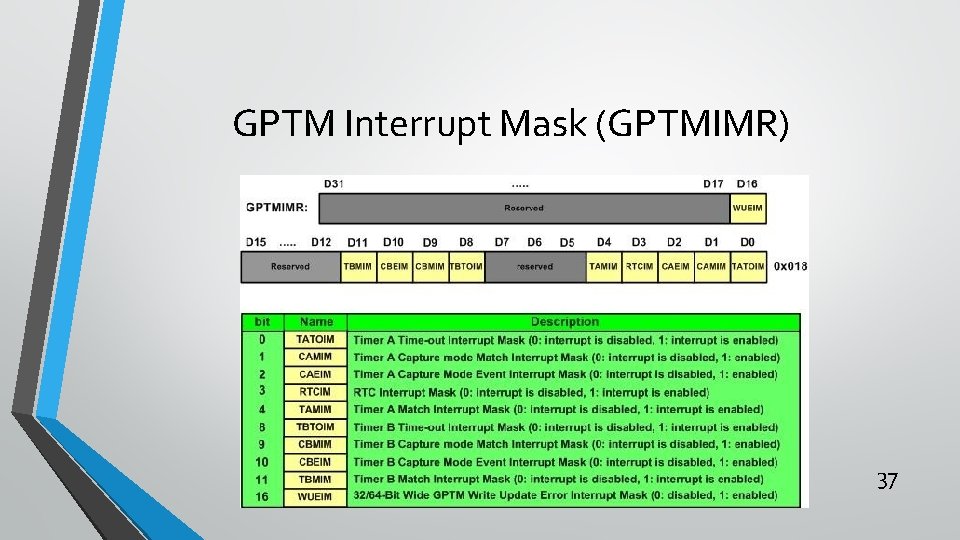

GPTM Interrupt Mask (GPTMIMR) 37

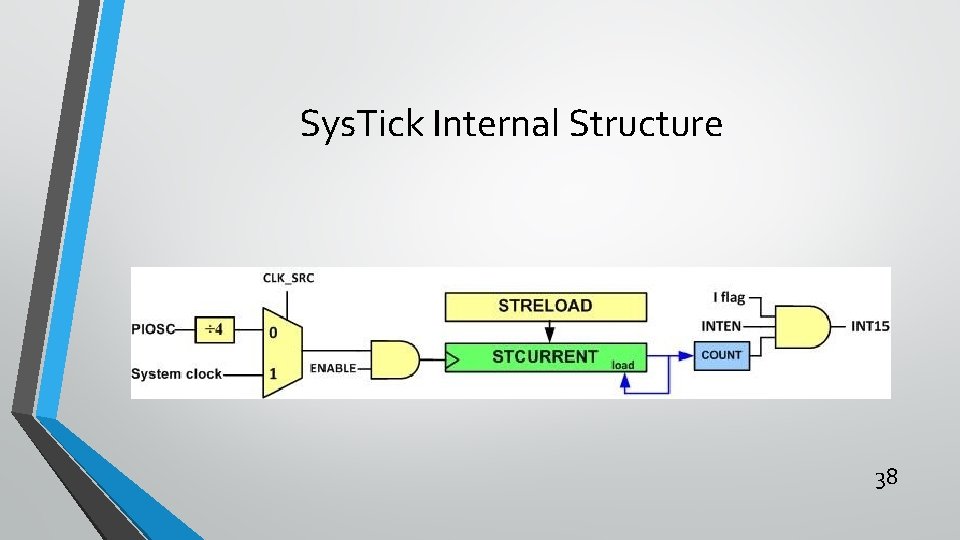

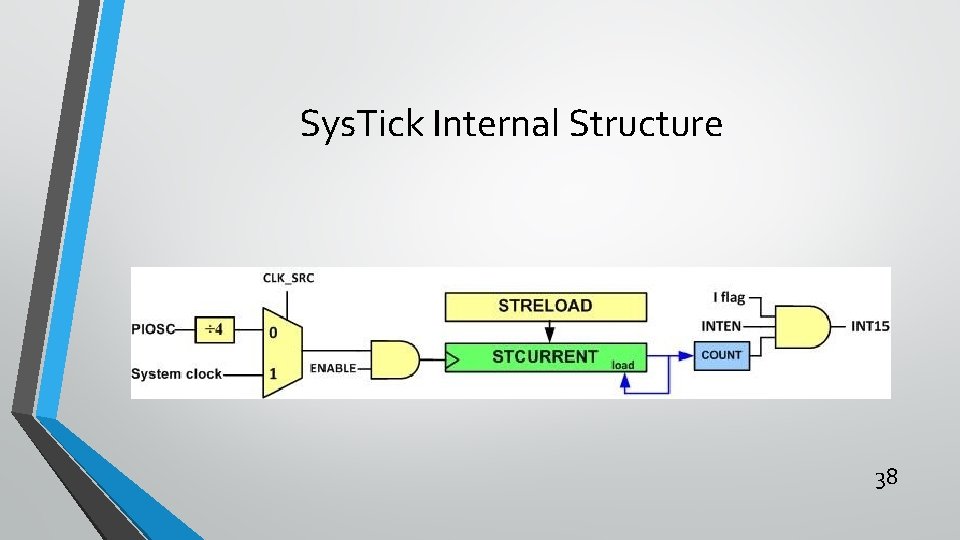

Sys. Tick Internal Structure 38

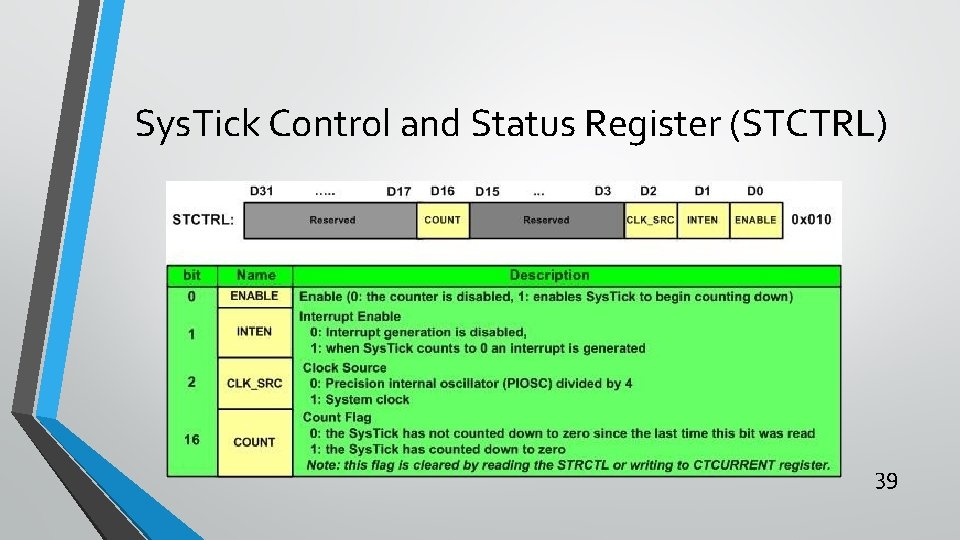

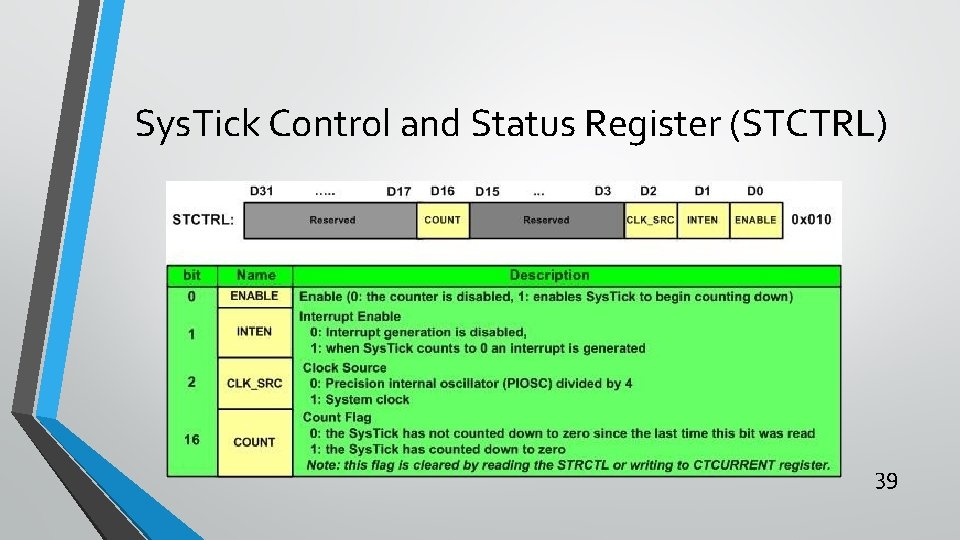

Sys. Tick Control and Status Register (STCTRL) 39

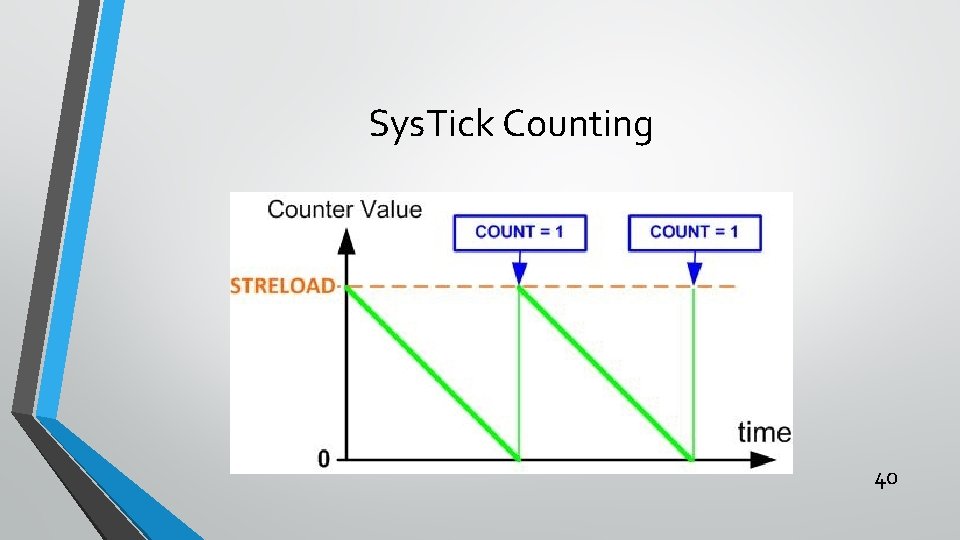

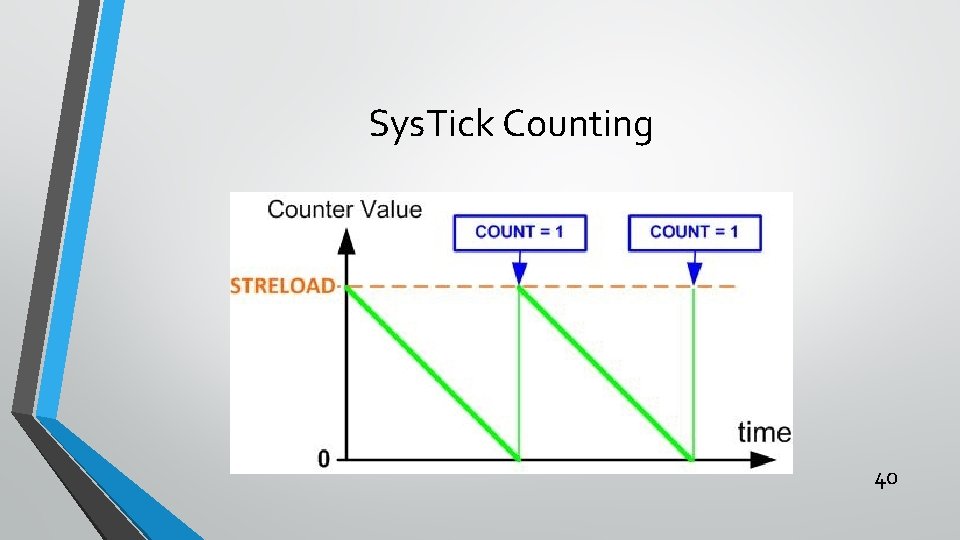

Sys. Tick Counting 40

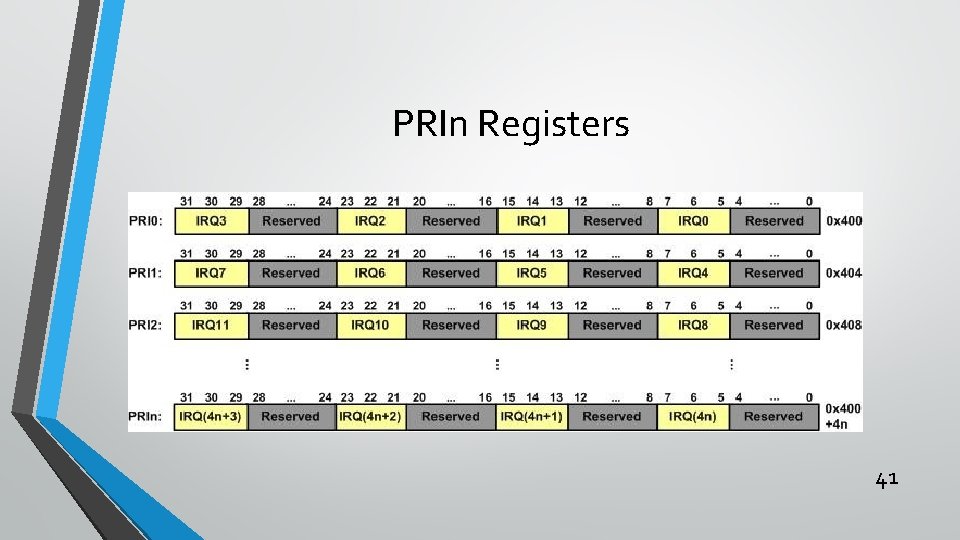

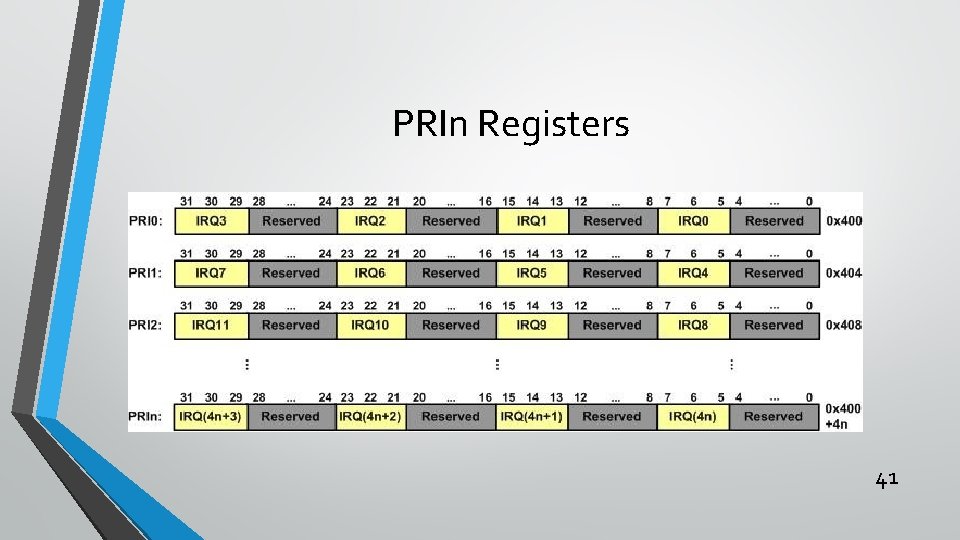

PRIn Registers 41