Chapter 6 Interrupt and Exception Programming 1 Polling

- Slides: 31

Chapter 6 Interrupt and Exception Programming 1

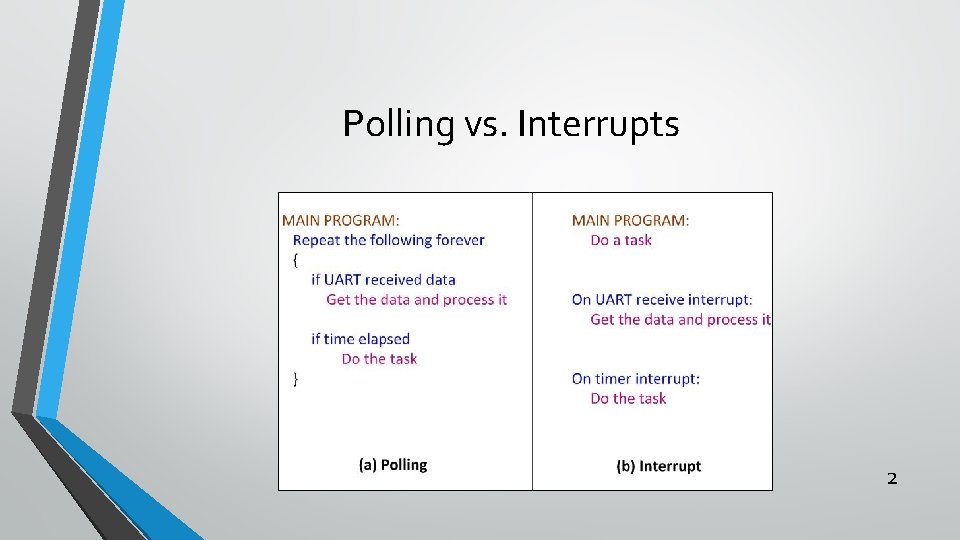

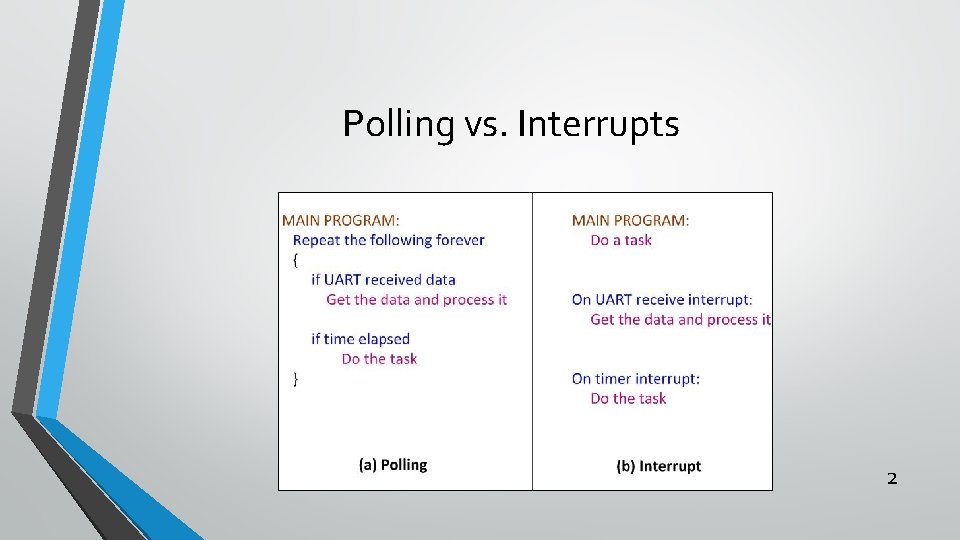

Polling vs. Interrupts 2

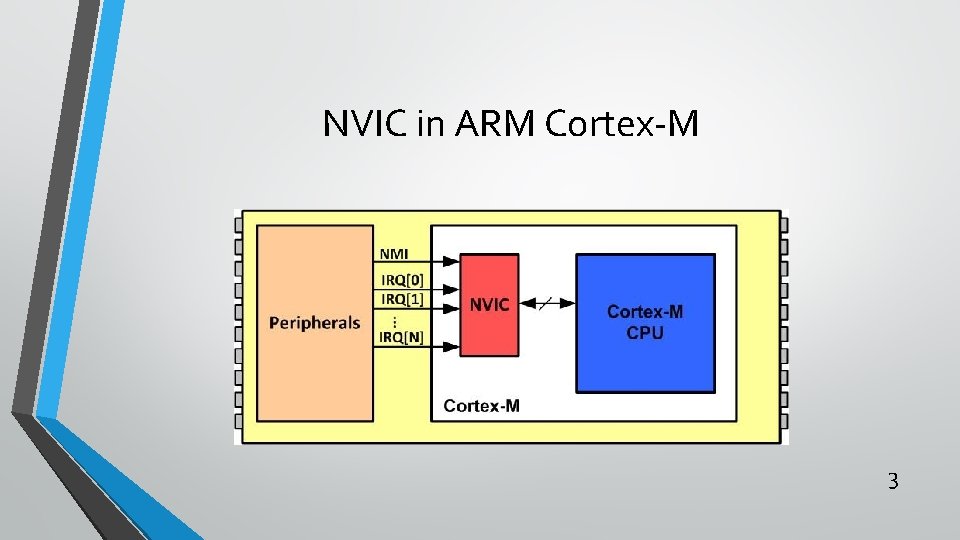

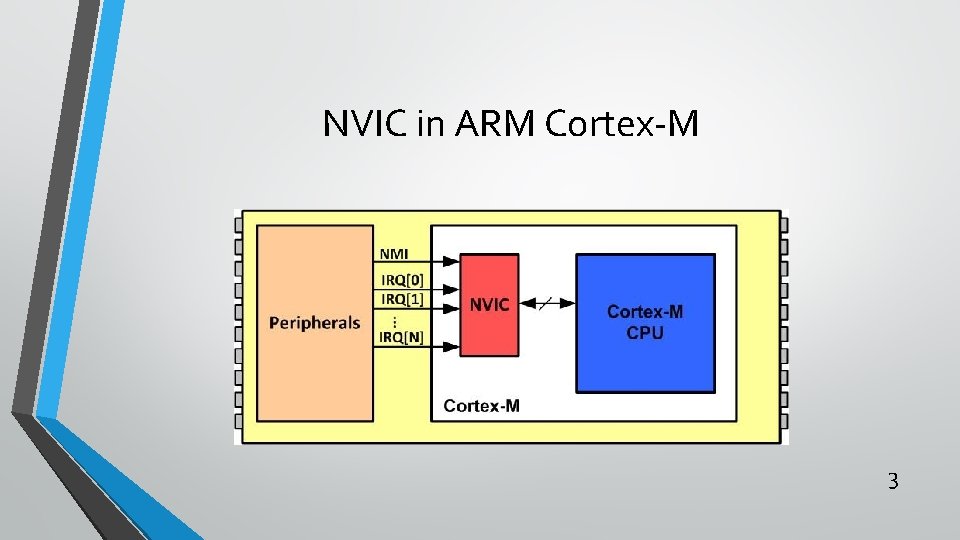

NVIC in ARM Cortex-M 3

Interrupt Vector Table for ARM Cortex-M Interrupt # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Memory Location (Hex) 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C 0 x 00000020 0 x 00000024 0 x 00000028 0 x 0000002 C 0 x 00000030 0 x 00000034 0 x 00000038 0 x 0000003 C 0 x 00000040 0 x 00000044 … 0 x 000003 FC 4

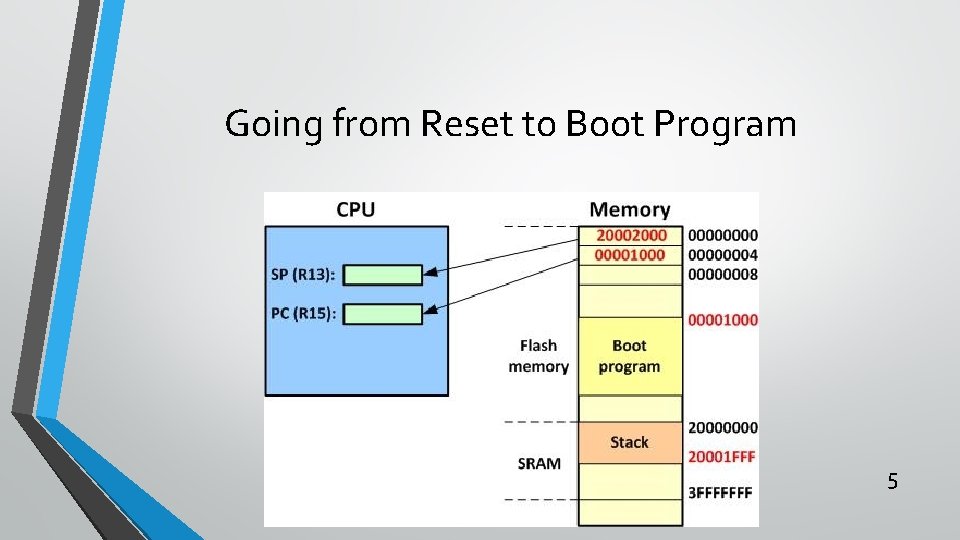

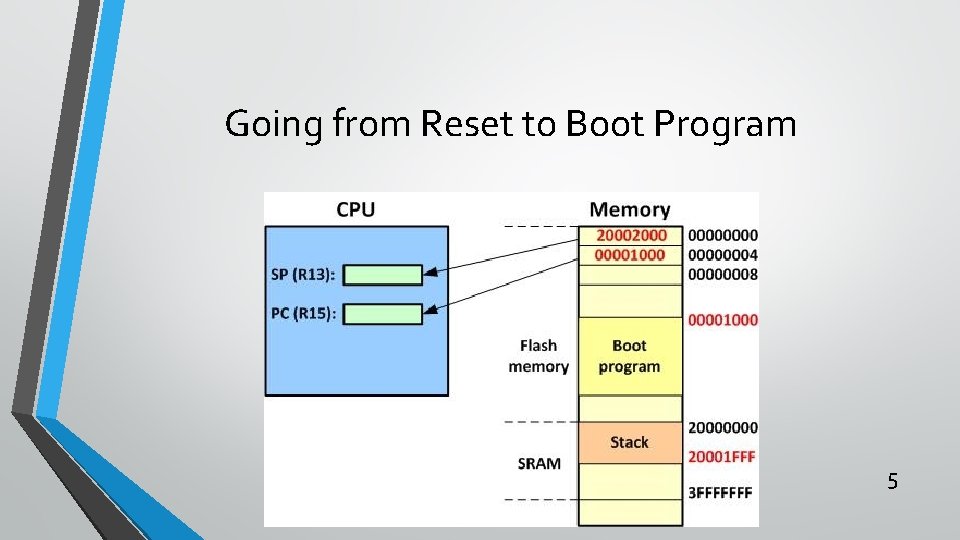

Going from Reset to Boot Program 5

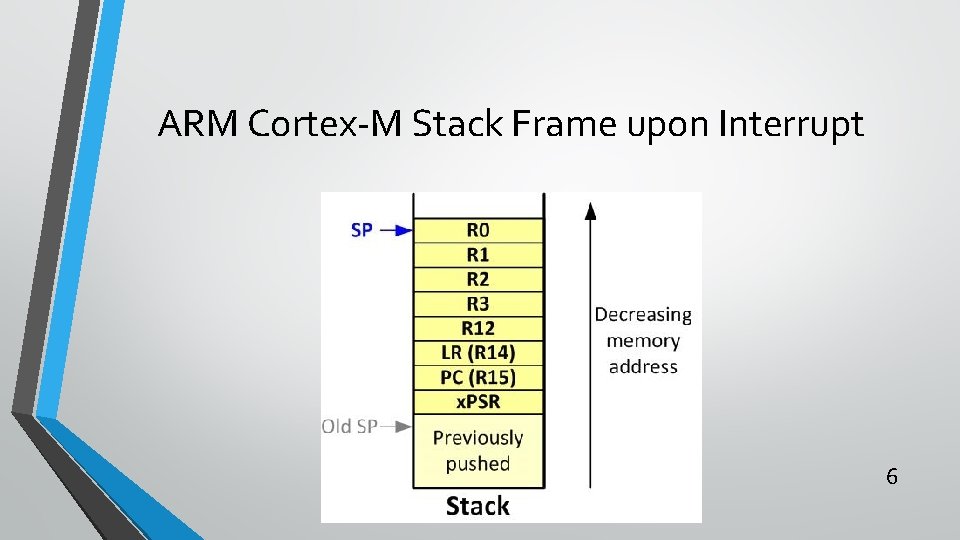

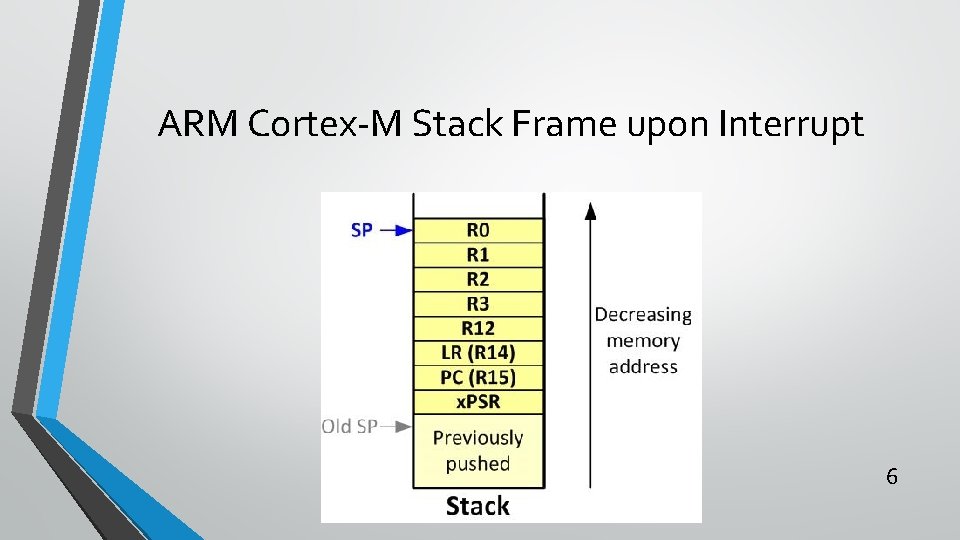

ARM Cortex-M Stack Frame upon Interrupt 6

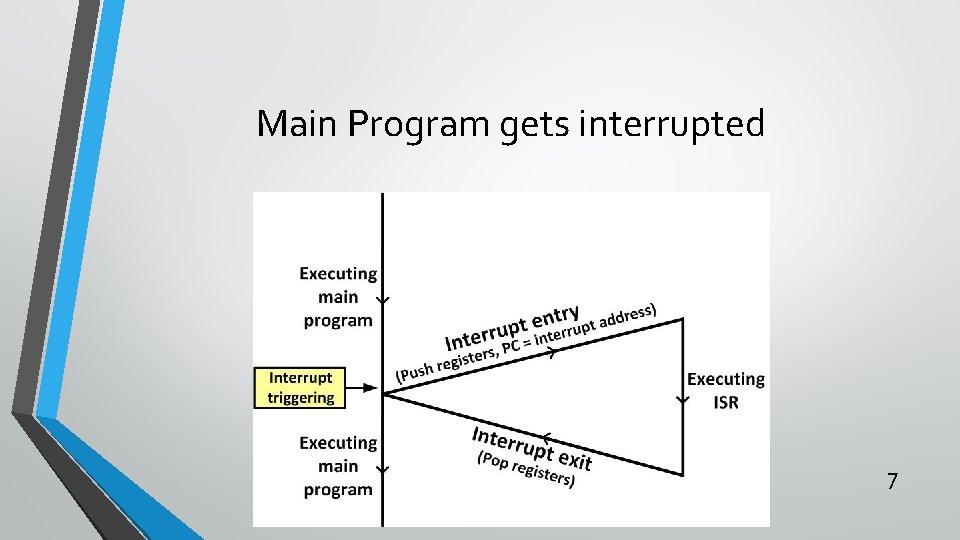

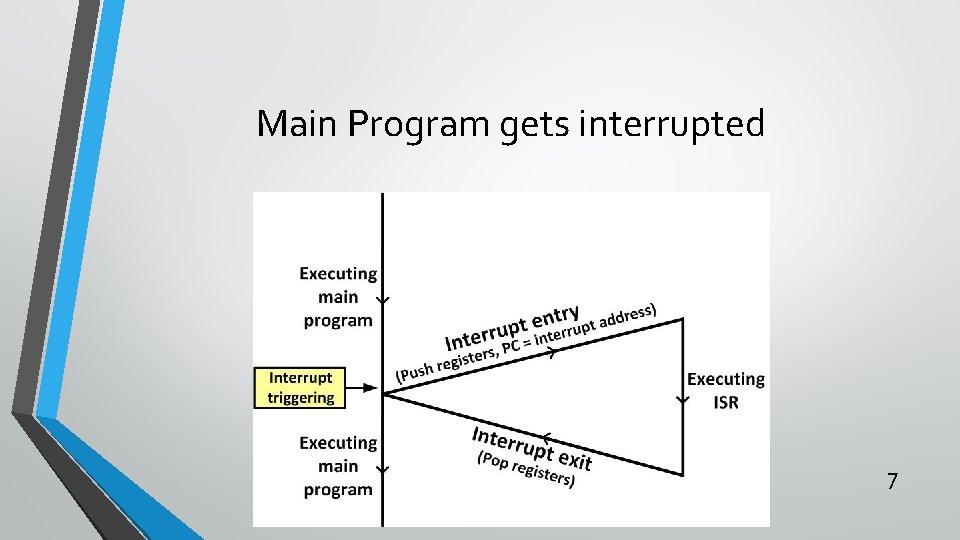

Main Program gets interrupted 7

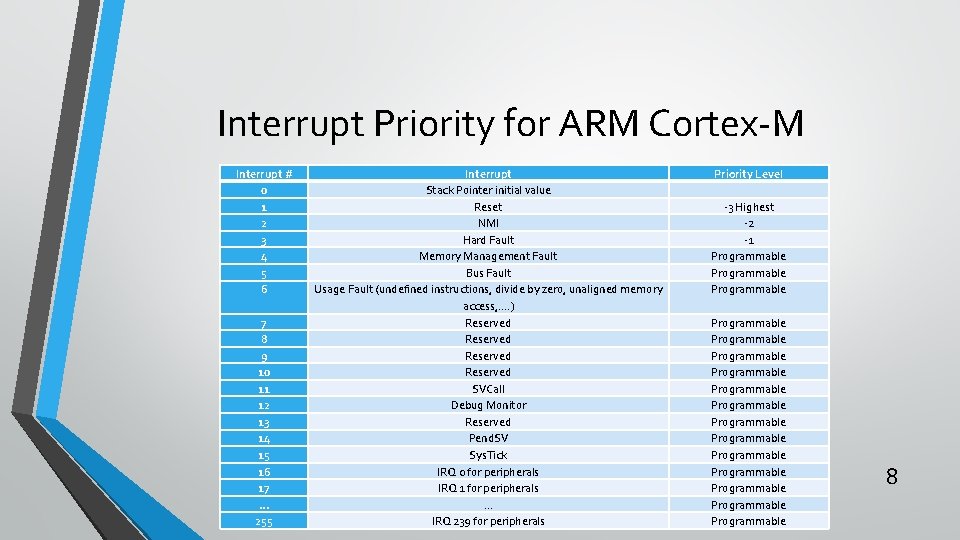

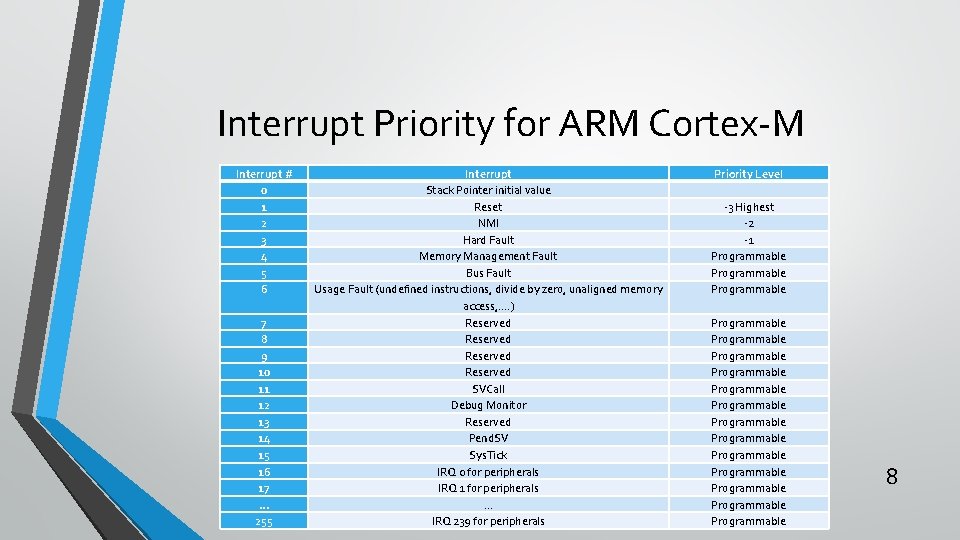

Interrupt Priority for ARM Cortex-M Interrupt # 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Priority Level -3 Highest -2 -1 Programmable Programmable Programmable Programmable 8

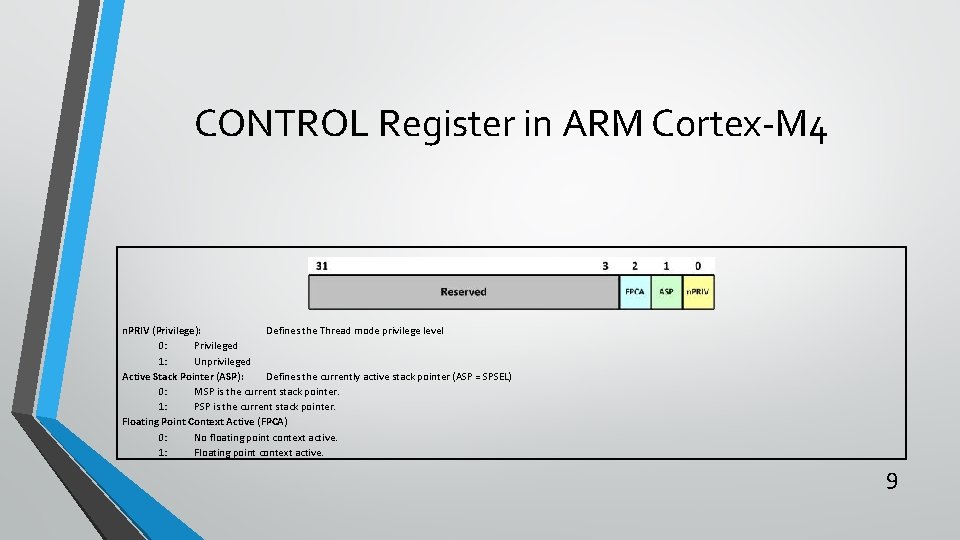

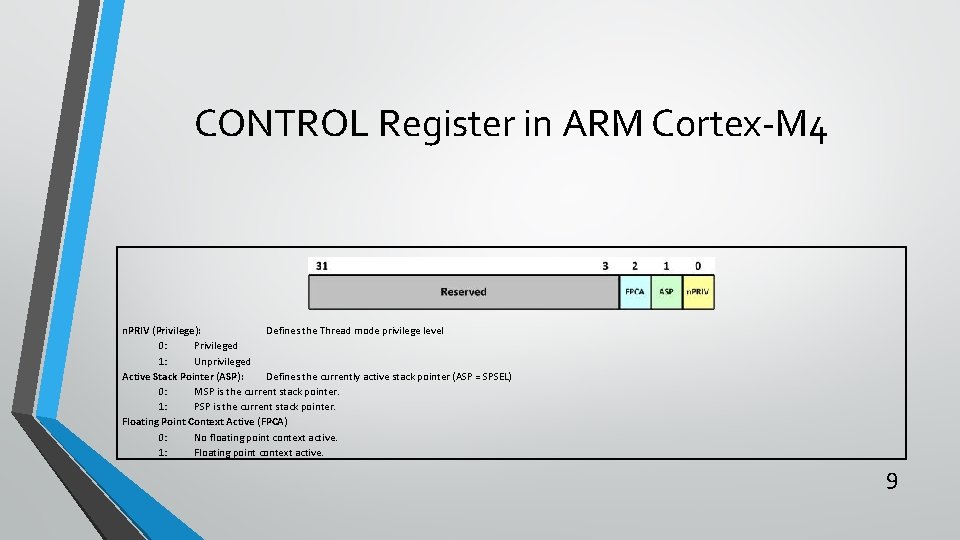

CONTROL Register in ARM Cortex-M 4 n. PRIV (Privilege): Defines the Thread mode privilege level 0: Privileged 1: Unprivileged Active Stack Pointer (ASP): Defines the currently active stack pointer (ASP = SPSEL) 0: MSP is the current stack pointer. 1: PSP is the current stack pointer. Floating Point Context Active (FPCA) 0: No floating point context active. 1: Floating point context active. 9

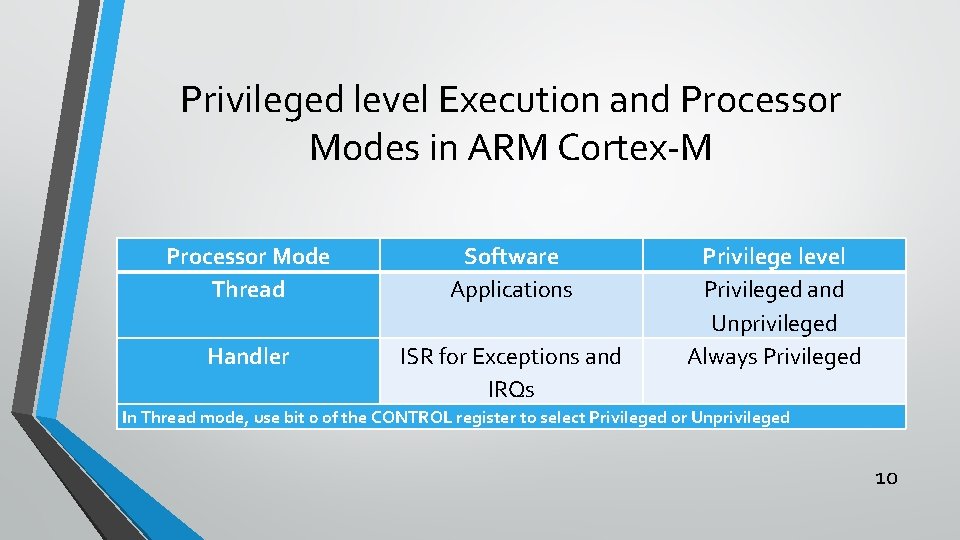

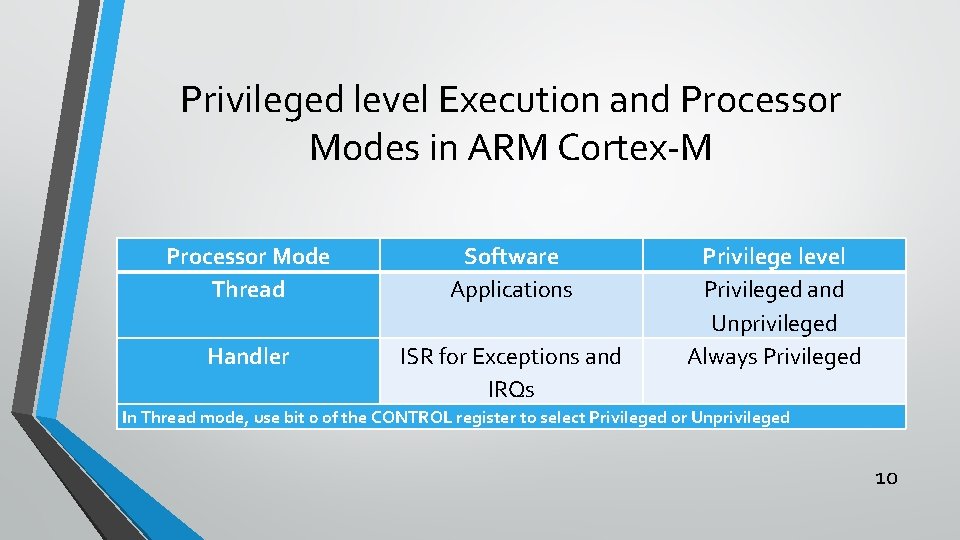

Privileged level Execution and Processor Modes in ARM Cortex-M Processor Mode Thread Software Applications Handler ISR for Exceptions and IRQs Privilege level Privileged and Unprivileged Always Privileged In Thread mode, use bit 0 of the CONTROL register to select Privileged or Unprivileged 10

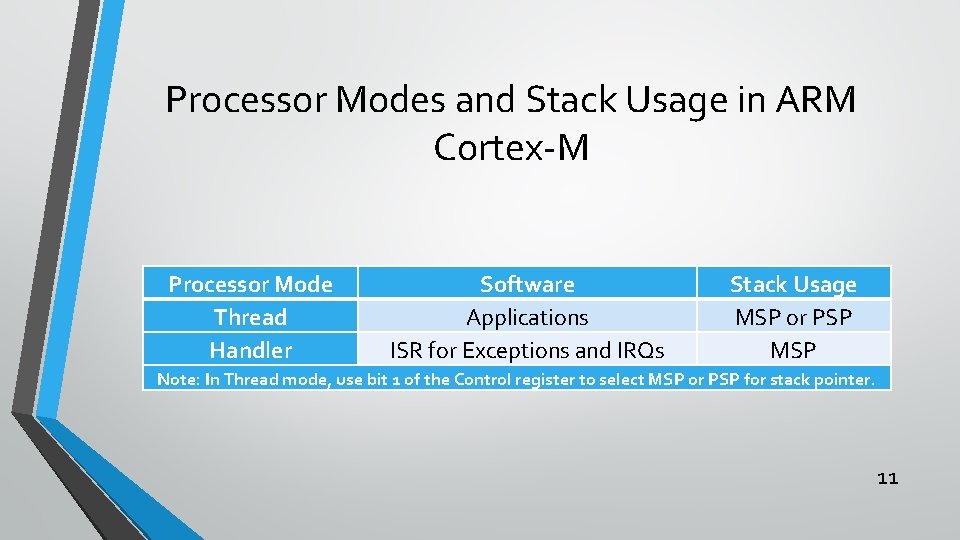

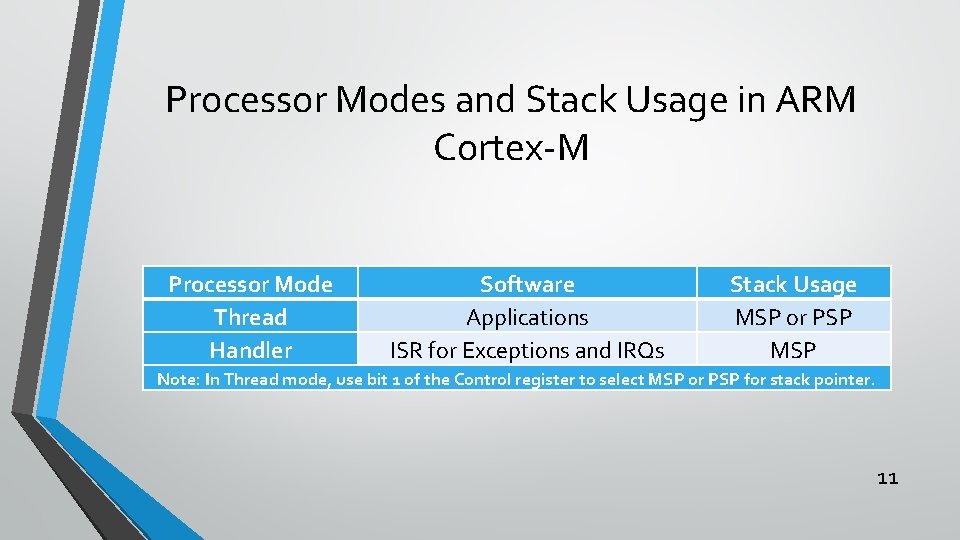

Processor Modes and Stack Usage in ARM Cortex-M Processor Mode Thread Handler Software Applications ISR for Exceptions and IRQs Stack Usage MSP or PSP MSP Note: In Thread mode, use bit 1 of the Control register to select MSP or PSP for stack pointer. 11

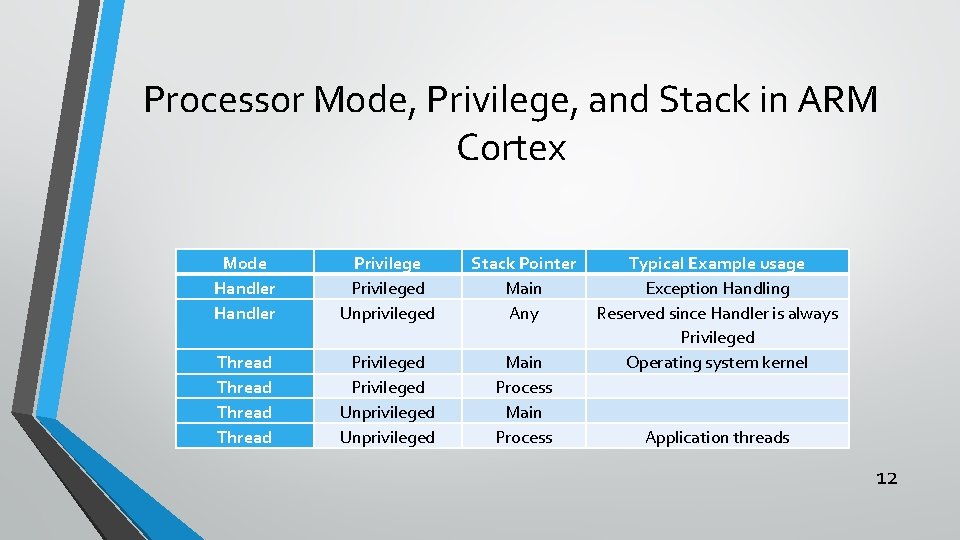

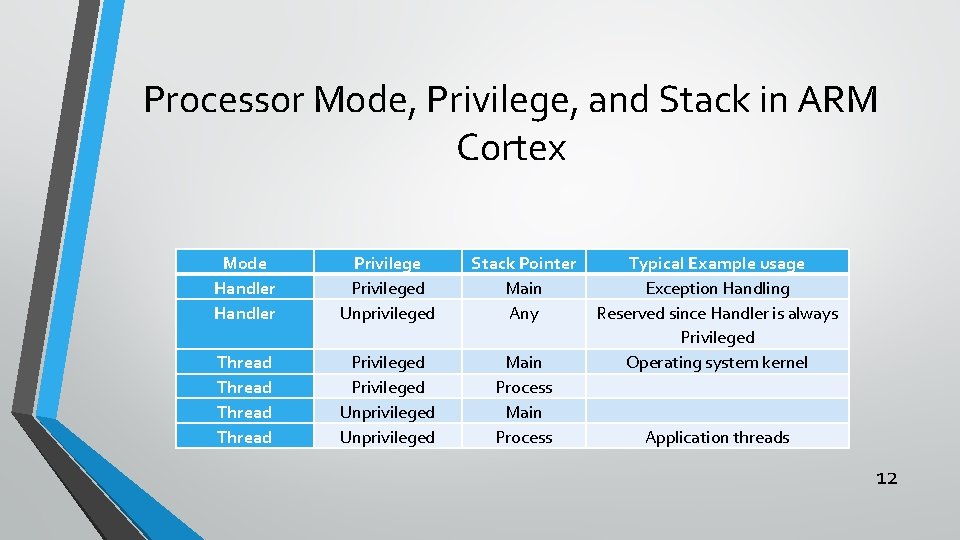

Processor Mode, Privilege, and Stack in ARM Cortex Mode Handler Privileged Unprivileged Stack Pointer Main Any Thread Privileged Unprivileged Main Process Typical Example usage Exception Handling Reserved since Handler is always Privileged Operating system kernel Application threads 12

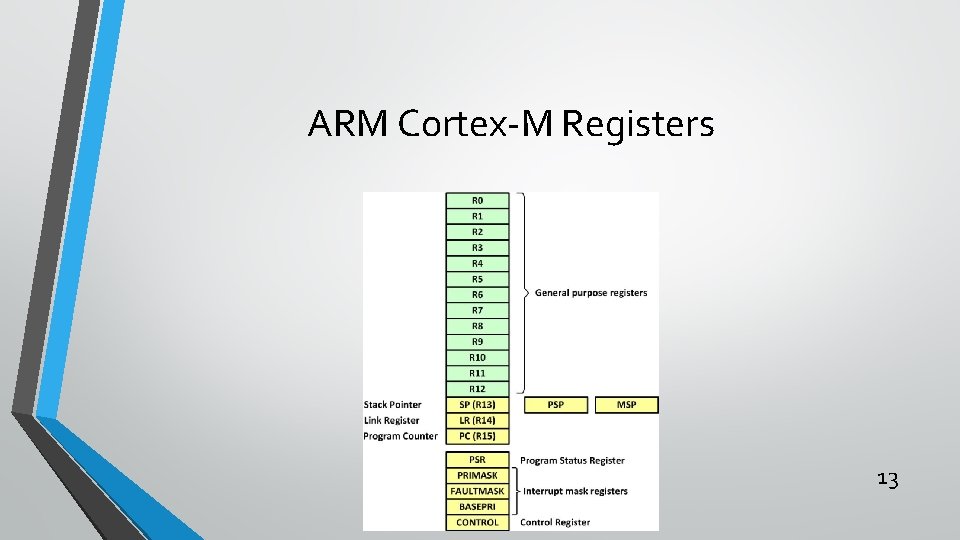

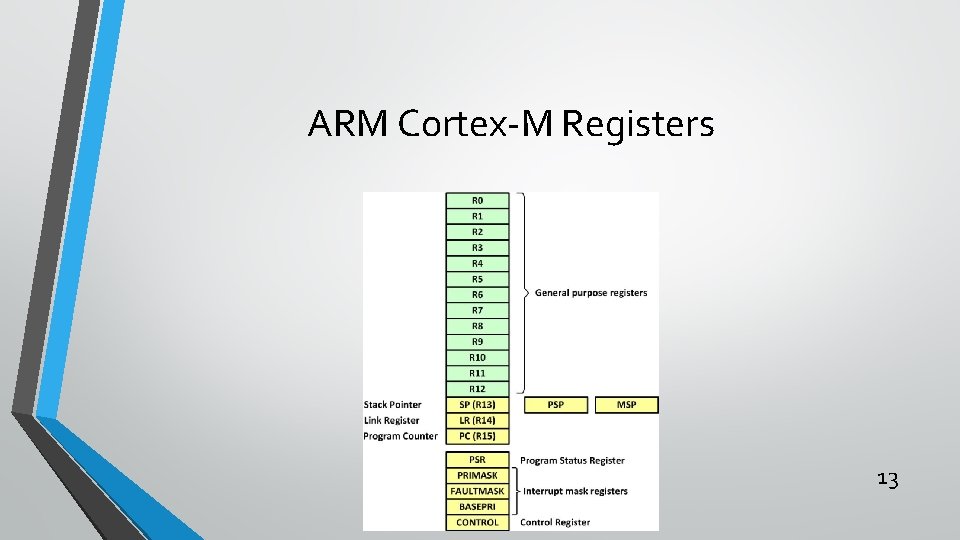

ARM Cortex-M Registers 13

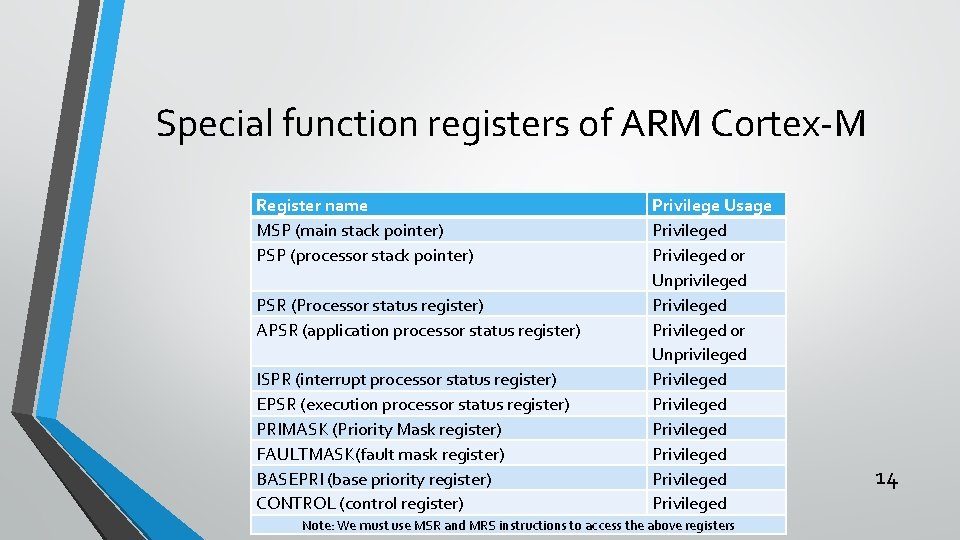

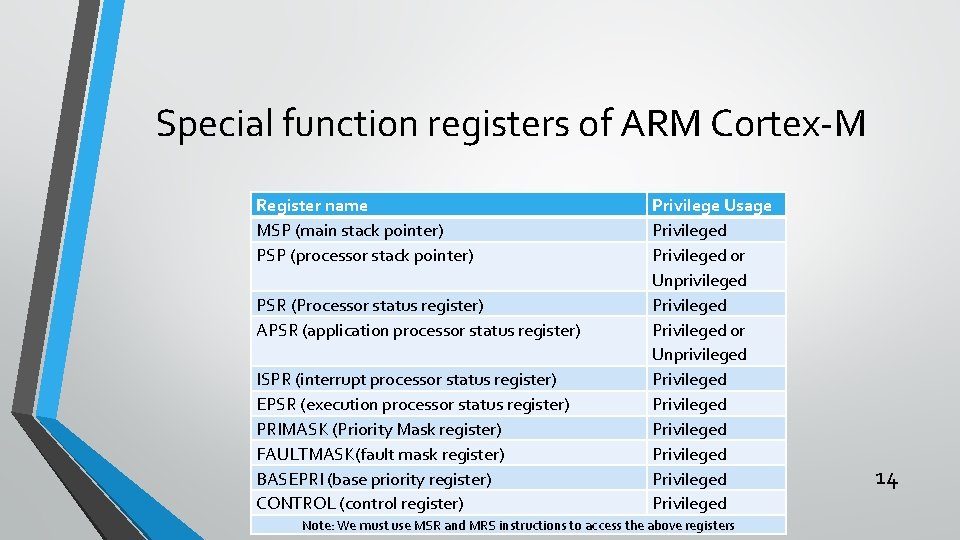

Special function registers of ARM Cortex-M Register name MSP (main stack pointer) PSP (processor stack pointer) PSR (Processor status register) APSR (application processor status register) ISPR (interrupt processor status register) EPSR (execution processor status register) PRIMASK (Priority Mask register) FAULTMASK(fault mask register) BASEPRI (base priority register) CONTROL (control register) Privilege Usage Privileged or Unprivileged Privileged Privileged Note: We must use MSR and MRS instructions to access the above registers 14

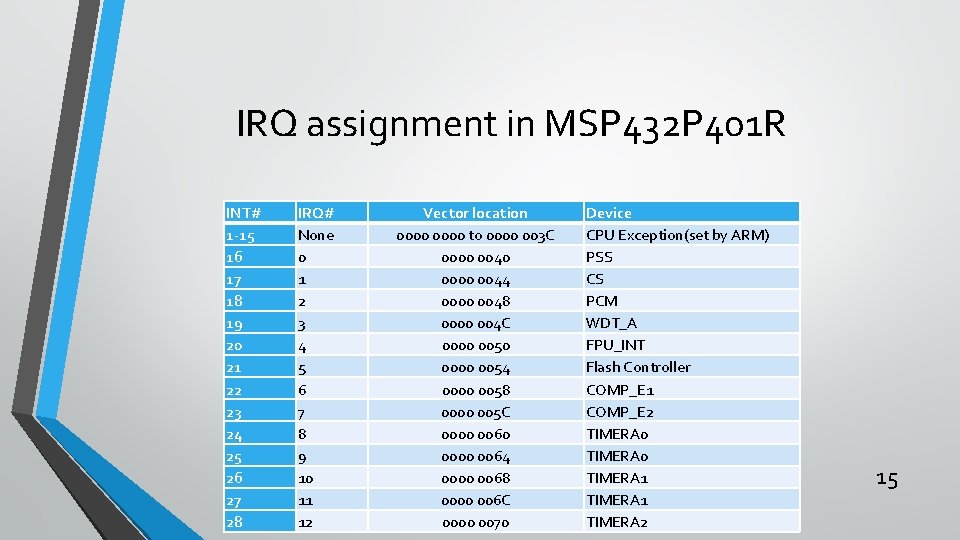

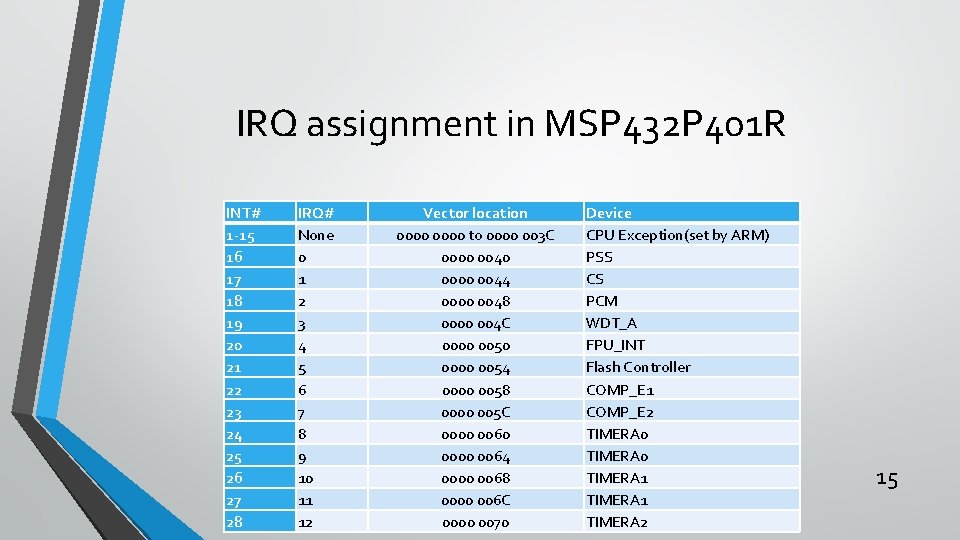

IRQ assignment in MSP 432 P 401 R INT# 1 -15 16 17 18 19 20 21 22 23 24 25 26 27 28 IRQ# None 0 1 2 3 4 5 6 7 8 9 10 11 12 Vector location 0000 to 0000 003 C 0000 0040 0000 0044 0000 0048 0000 004 C 0000 0050 0000 0054 0000 0058 0000 005 C 0000 0060 0000 0064 0000 0068 0000 006 C 0000 0070 Device CPU Exception(set by ARM) PSS CS PCM WDT_A FPU_INT Flash Controller COMP_E 1 COMP_E 2 TIMERA 0 TIMERA 1 TIMERA 2 15

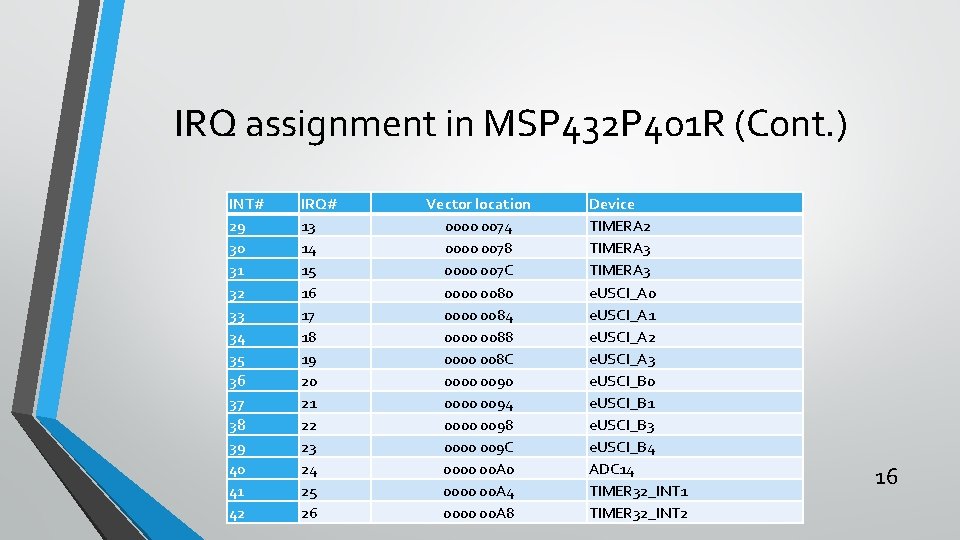

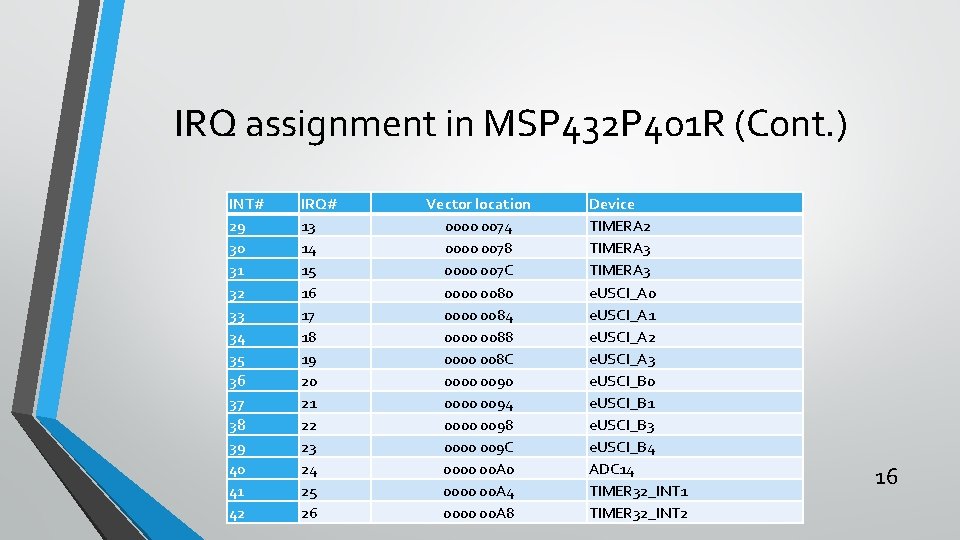

IRQ assignment in MSP 432 P 401 R (Cont. ) INT# 29 30 31 32 33 34 35 36 37 38 39 40 41 42 IRQ# 13 14 15 16 17 18 19 20 21 22 23 24 25 26 Vector location 0000 0074 0000 0078 0000 007 C 0000 0080 0000 0084 0000 0088 0000 008 C 0000 0090 0000 0094 0000 0098 0000 009 C 0000 00 A 0 0000 00 A 4 0000 00 A 8 Device TIMERA 2 TIMERA 3 e. USCI_A 0 e. USCI_A 1 e. USCI_A 2 e. USCI_A 3 e. USCI_B 0 e. USCI_B 1 e. USCI_B 3 e. USCI_B 4 ADC 14 TIMER 32_INT 1 TIMER 32_INT 2 16

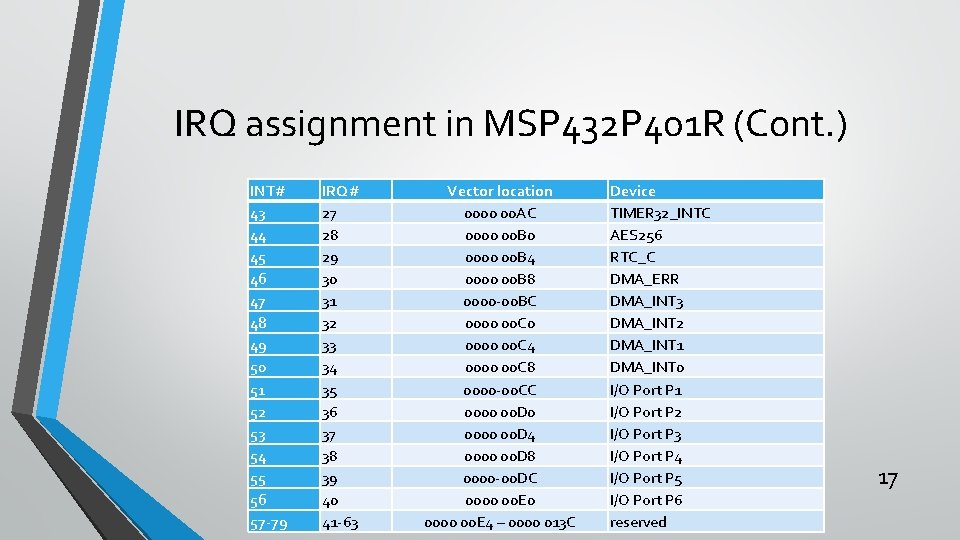

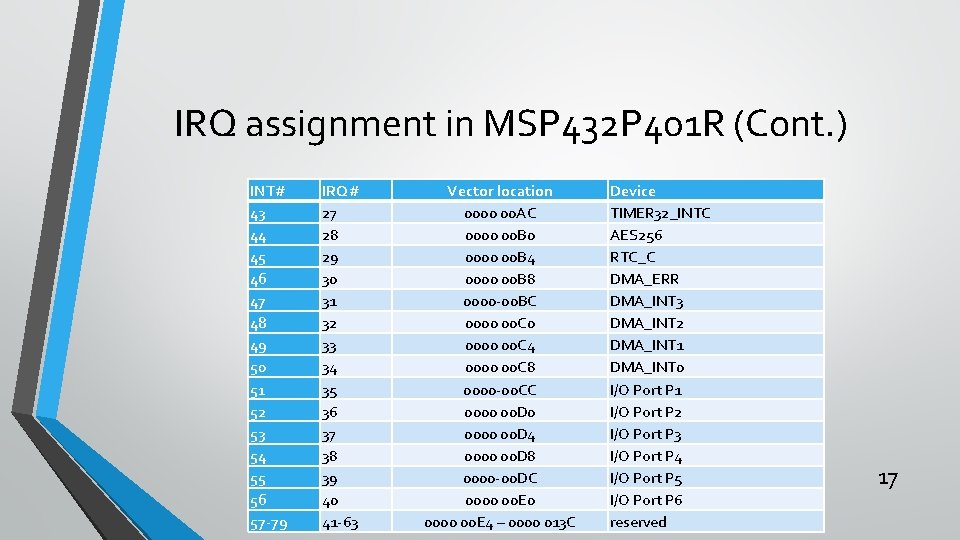

IRQ assignment in MSP 432 P 401 R (Cont. ) INT# 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 -79 IRQ# 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 -63 Vector location 0000 00 AC 0000 00 B 0 0000 00 B 4 0000 00 B 8 0000 -00 BC 0000 00 C 0 0000 00 C 4 0000 00 C 8 0000 -00 CC 0000 00 D 0 0000 00 D 4 0000 00 D 8 0000 -00 DC 0000 00 E 0 0000 00 E 4 – 0000 013 C Device TIMER 32_INTC AES 256 RTC_C DMA_ERR DMA_INT 3 DMA_INT 2 DMA_INT 1 DMA_INT 0 I/O Port P 1 I/O Port P 2 I/O Port P 3 I/O Port P 4 I/O Port P 5 I/O Port P 6 reserved 17

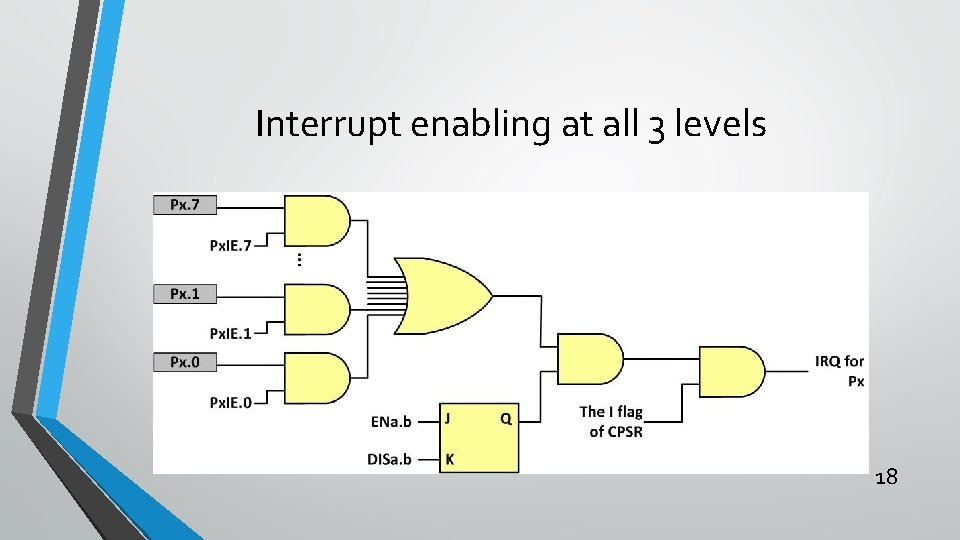

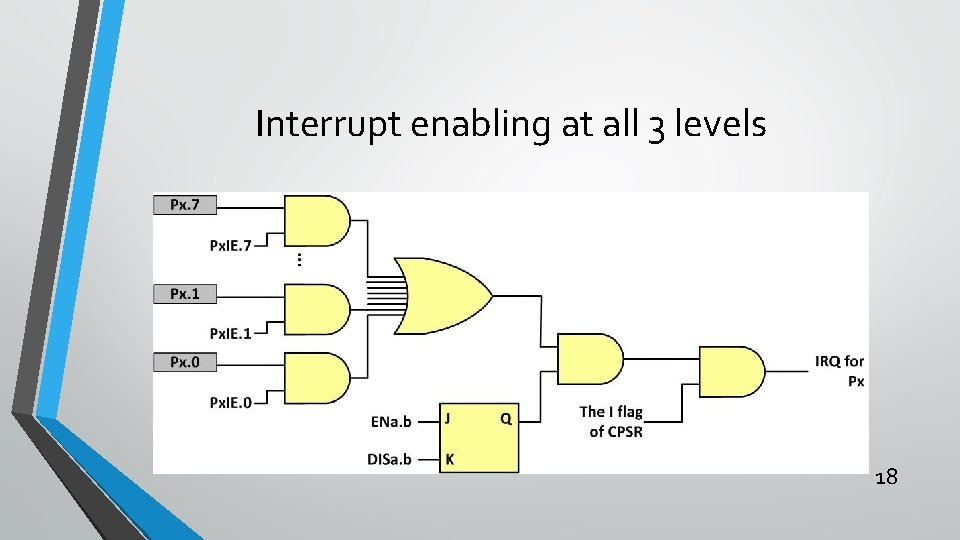

Interrupt enabling at all 3 levels 18

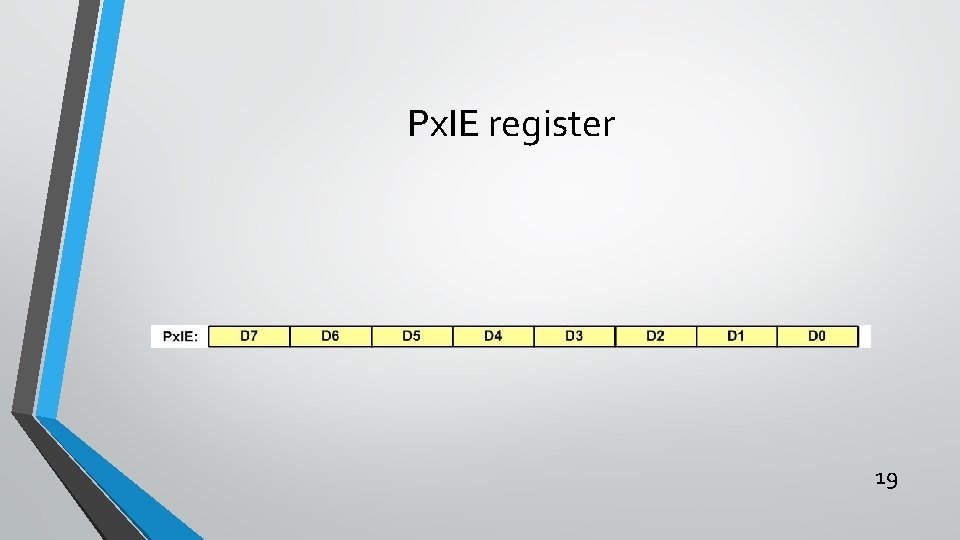

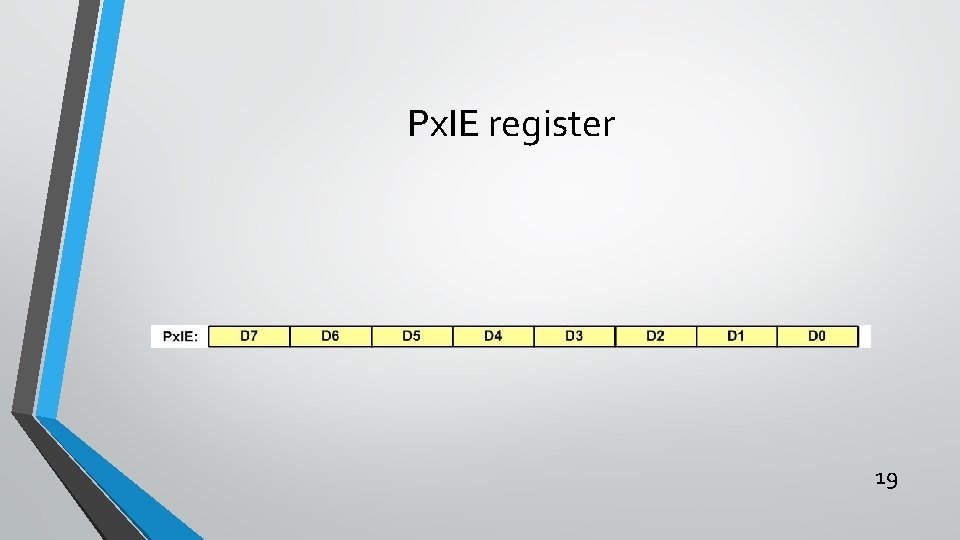

Px. IE register 19

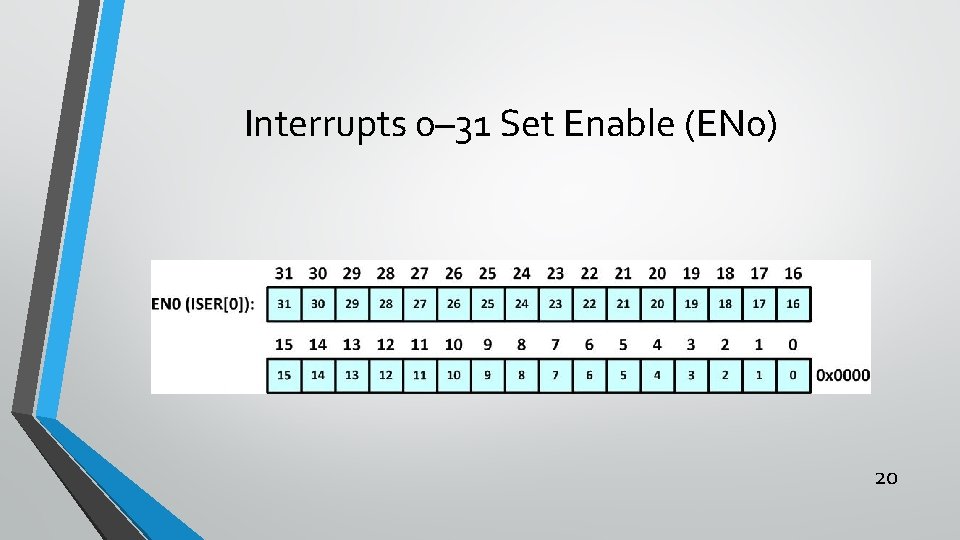

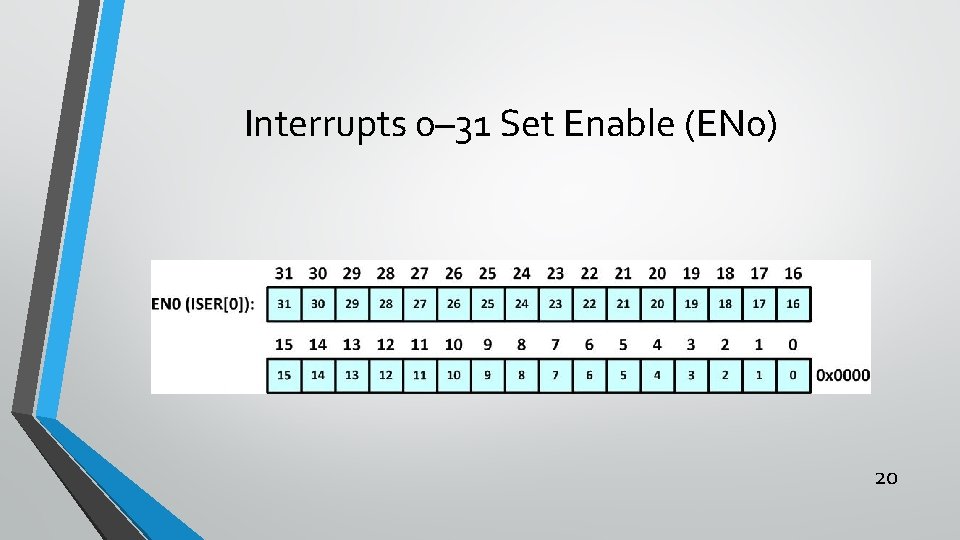

Interrupts 0– 31 Set Enable (EN 0) 20

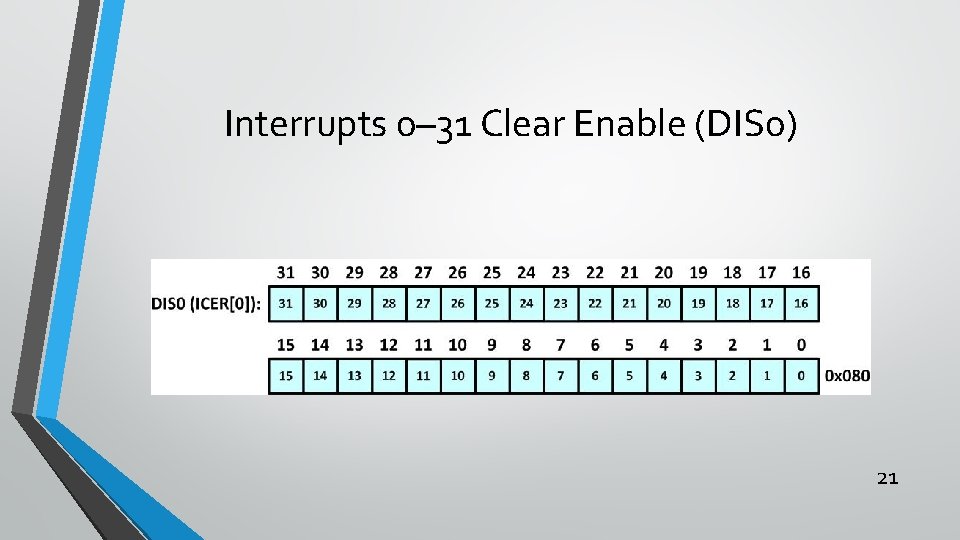

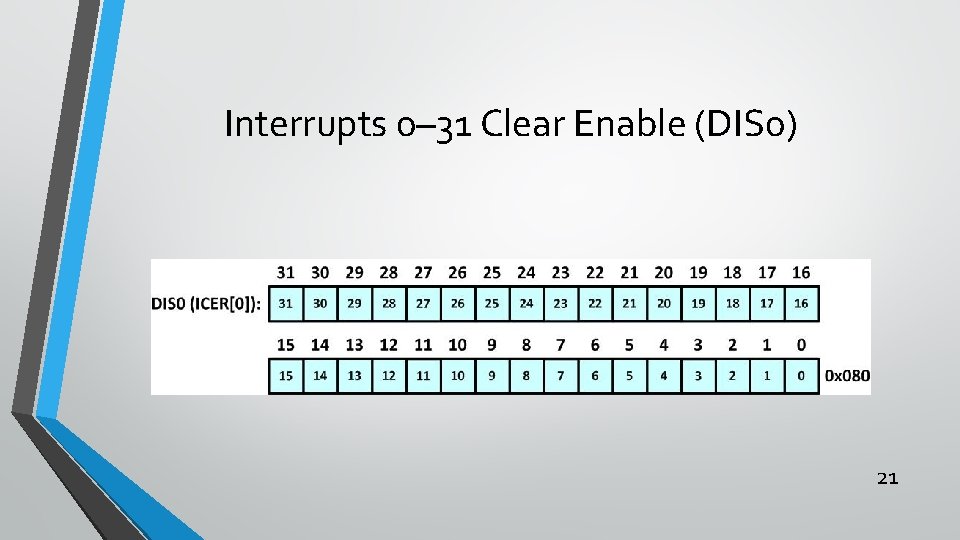

Interrupts 0– 31 Clear Enable (DIS 0) 21

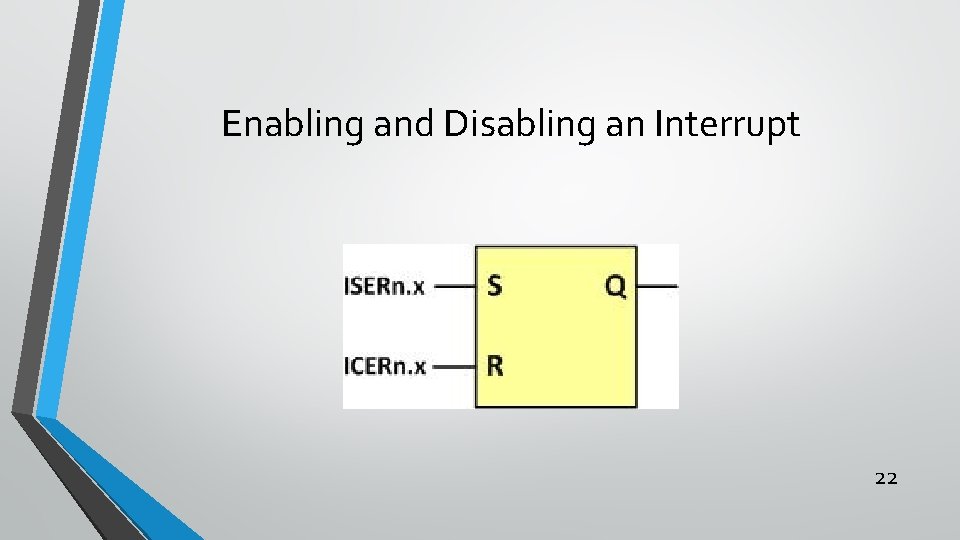

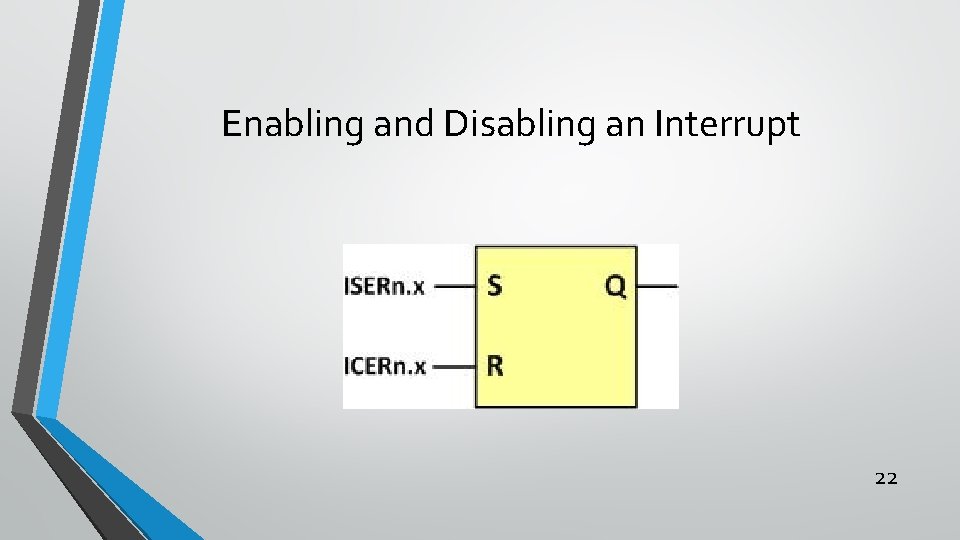

Enabling and Disabling an Interrupt 22

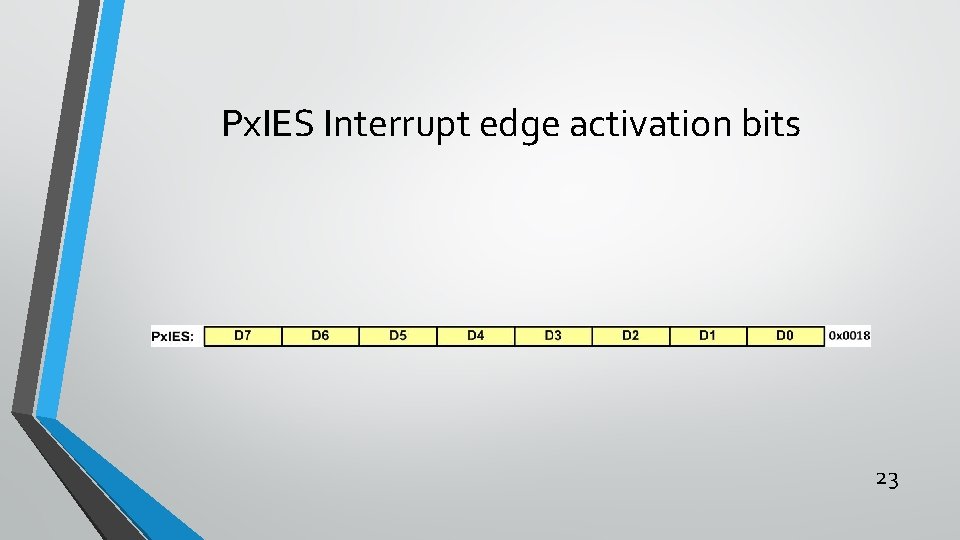

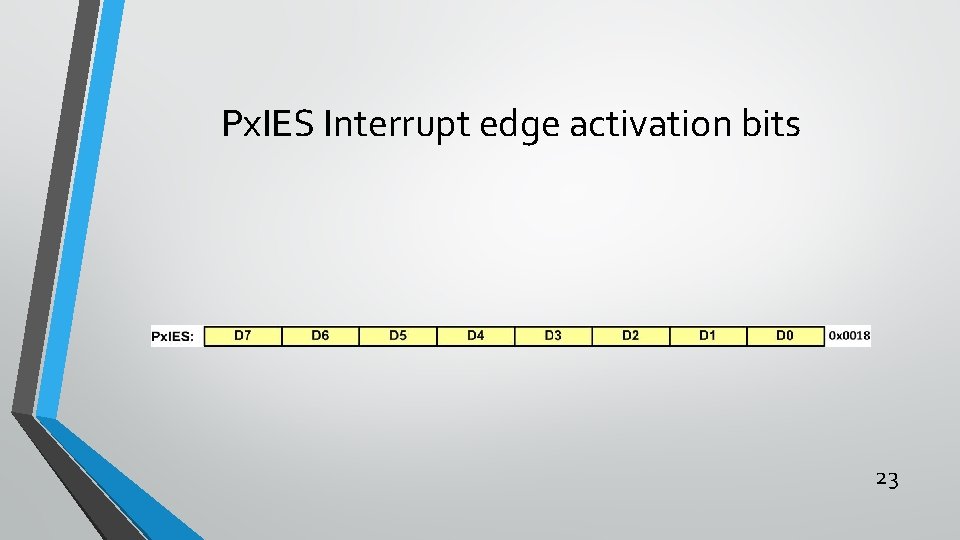

Px. IES Interrupt edge activation bits 23

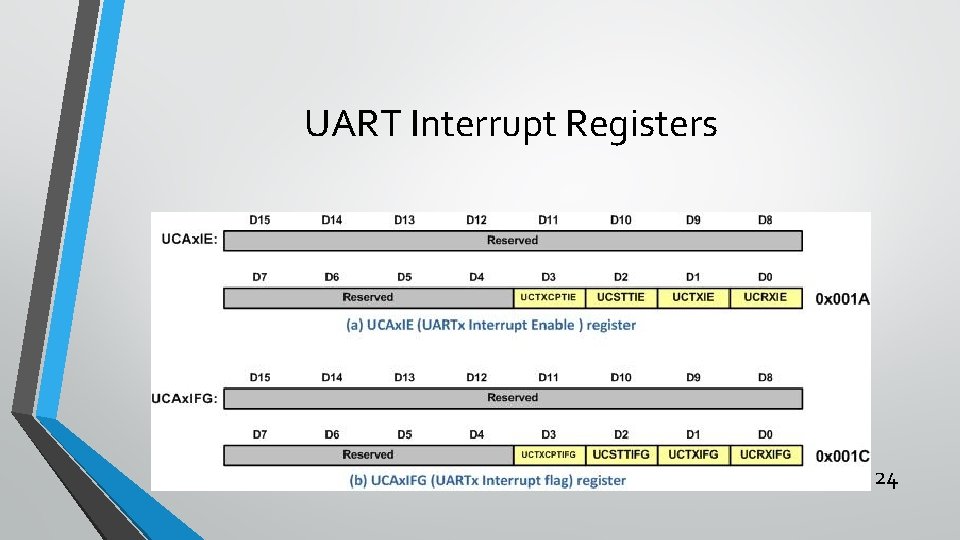

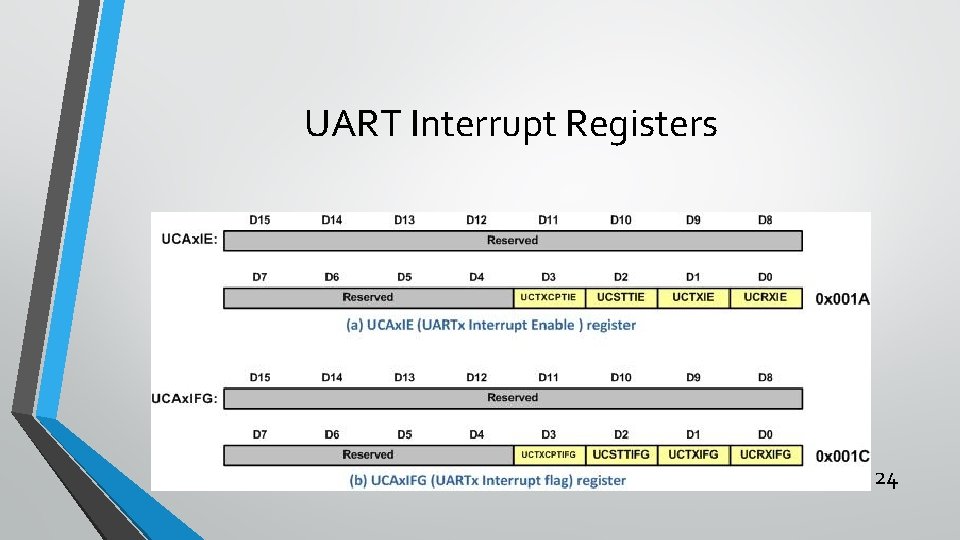

UART Interrupt Registers 24

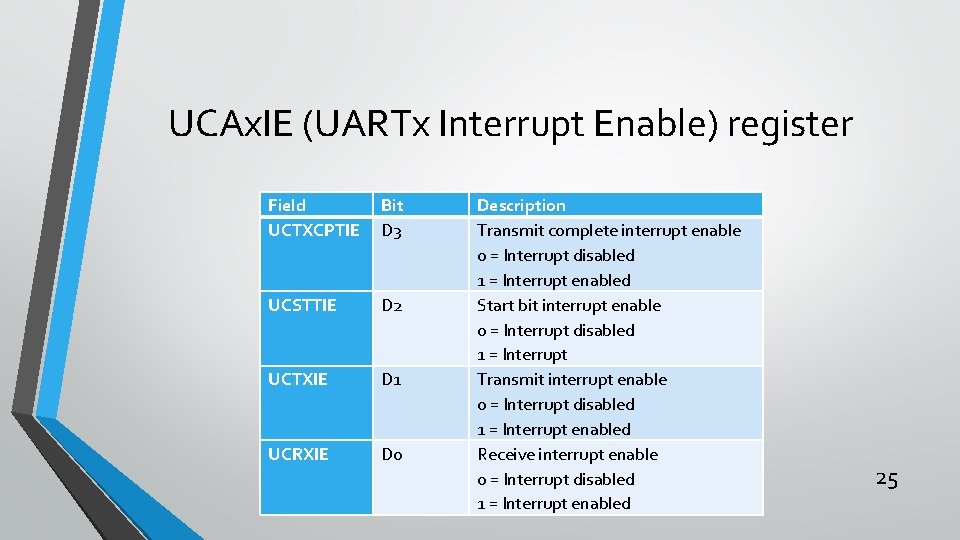

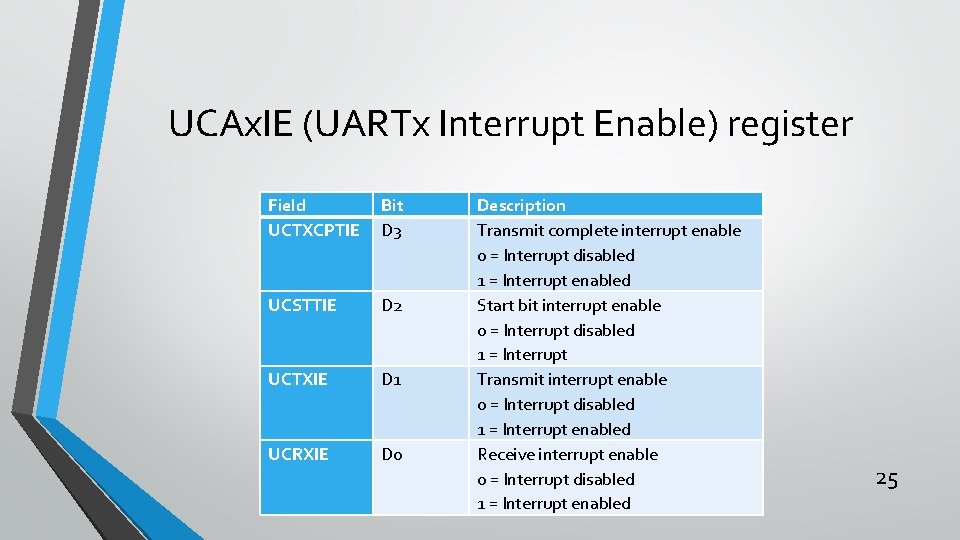

UCAx. IE (UARTx Interrupt Enable) register Field UCTXCPTIE Bit D 3 UCSTTIE D 2 UCTXIE D 1 UCRXIE D 0 Description Transmit complete interrupt enable 0 = Interrupt disabled 1 = Interrupt enabled Start bit interrupt enable 0 = Interrupt disabled 1 = Interrupt Transmit interrupt enable 0 = Interrupt disabled 1 = Interrupt enabled Receive interrupt enable 0 = Interrupt disabled 1 = Interrupt enabled 25

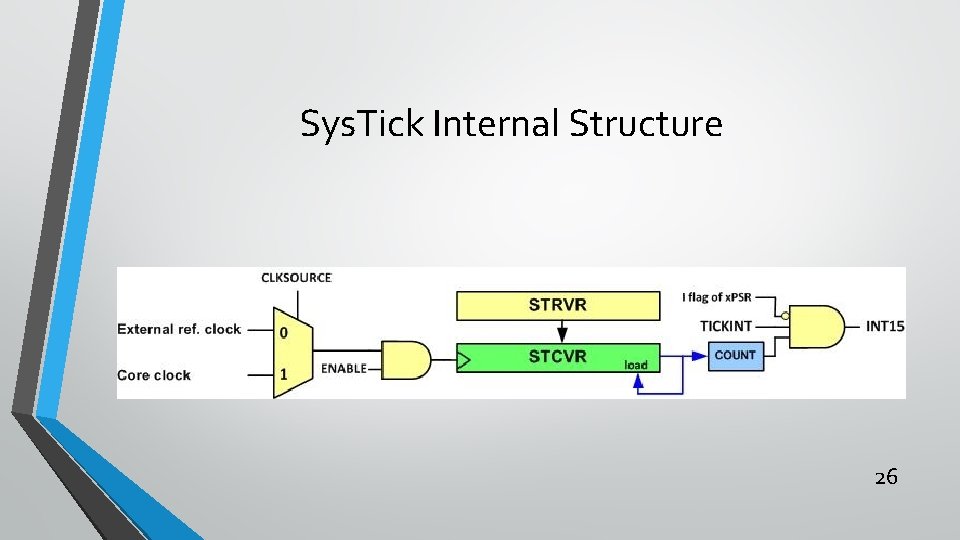

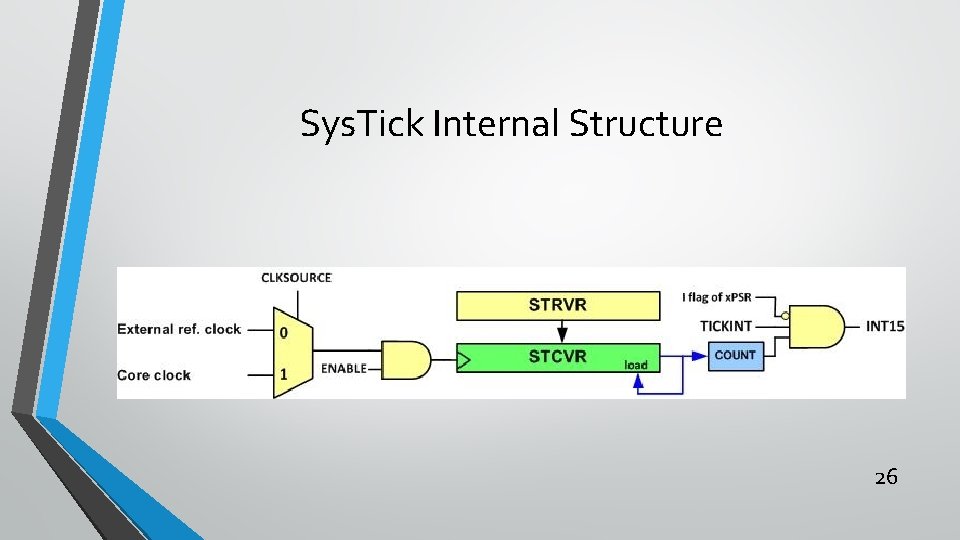

Sys. Tick Internal Structure 26

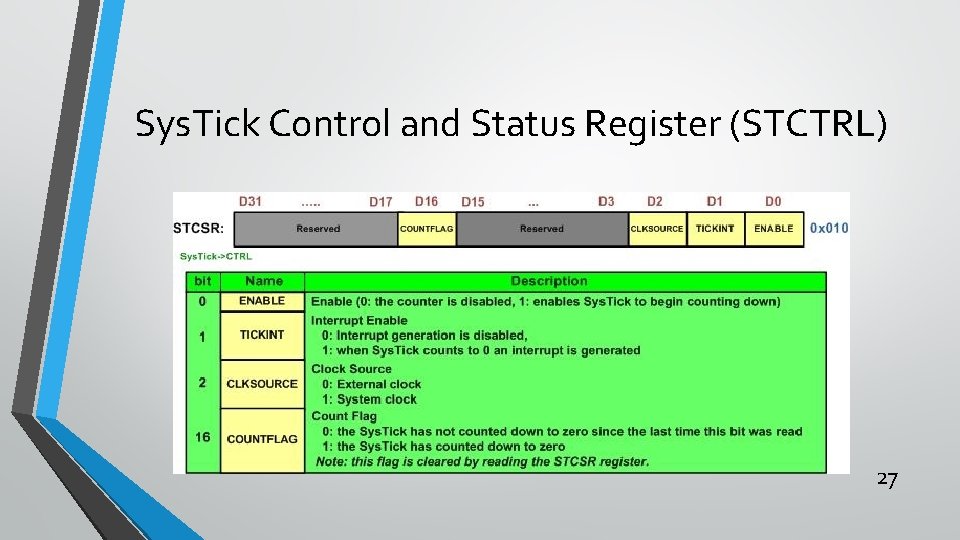

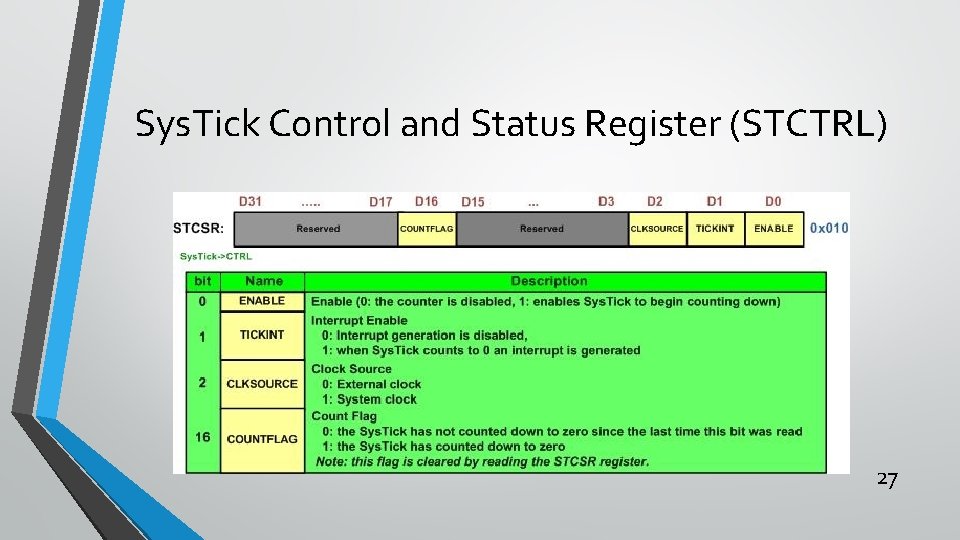

Sys. Tick Control and Status Register (STCTRL) 27

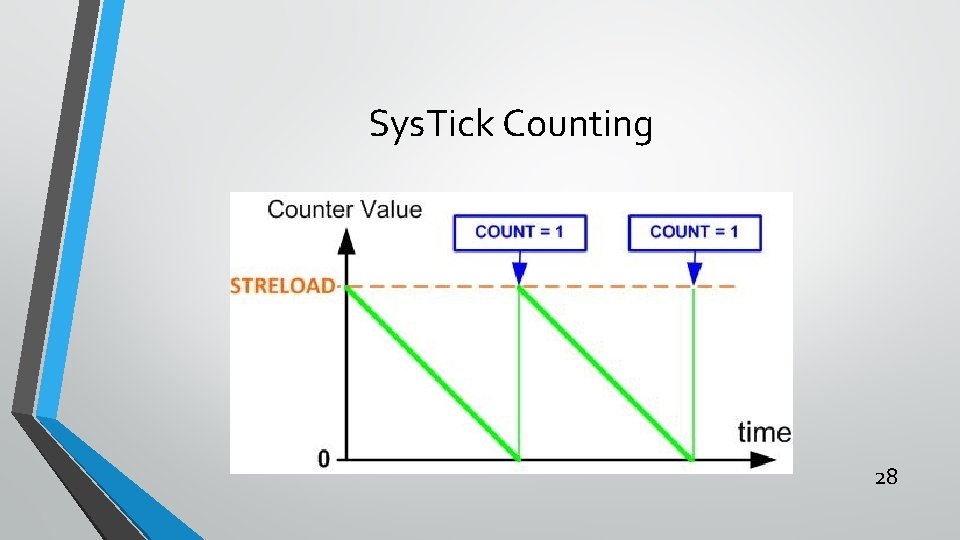

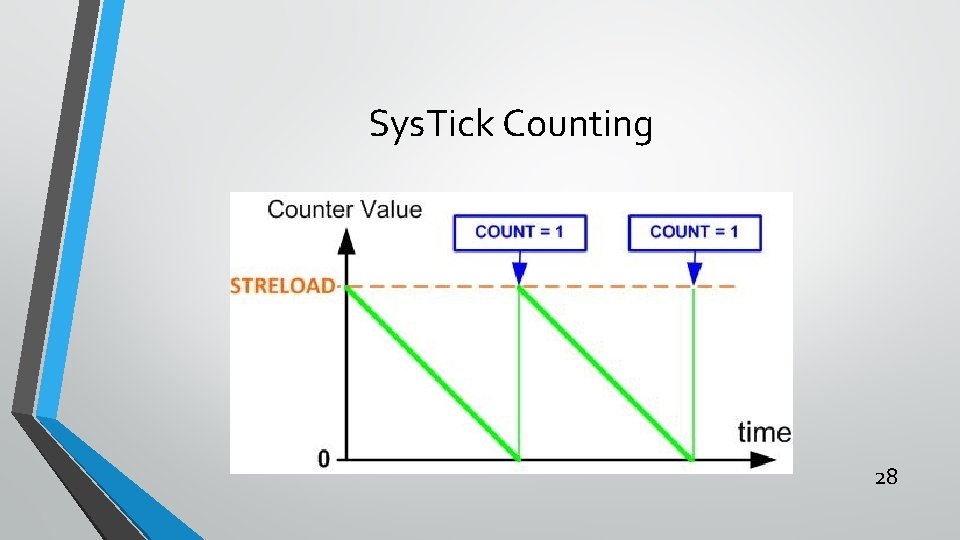

Sys. Tick Counting 28

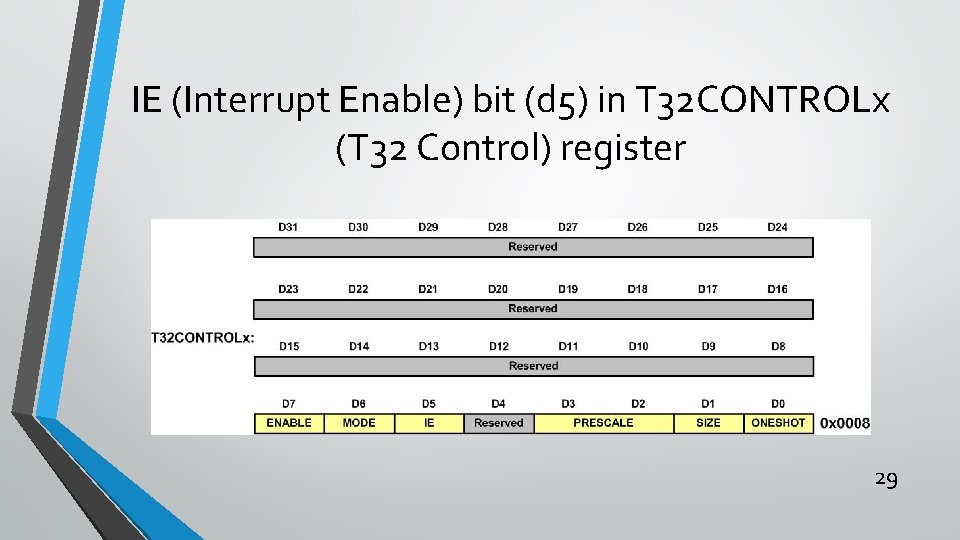

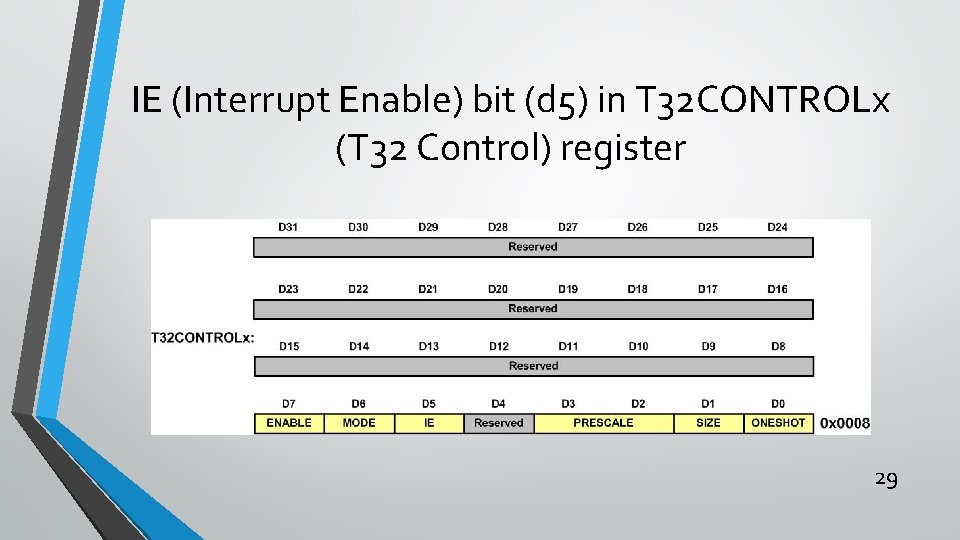

IE (Interrupt Enable) bit (d 5) in T 32 CONTROLx (T 32 Control) register 29

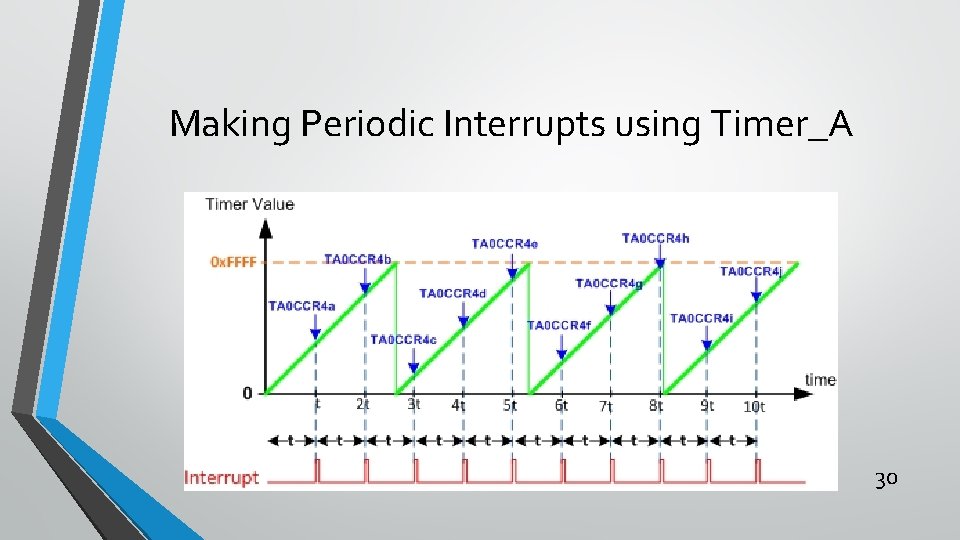

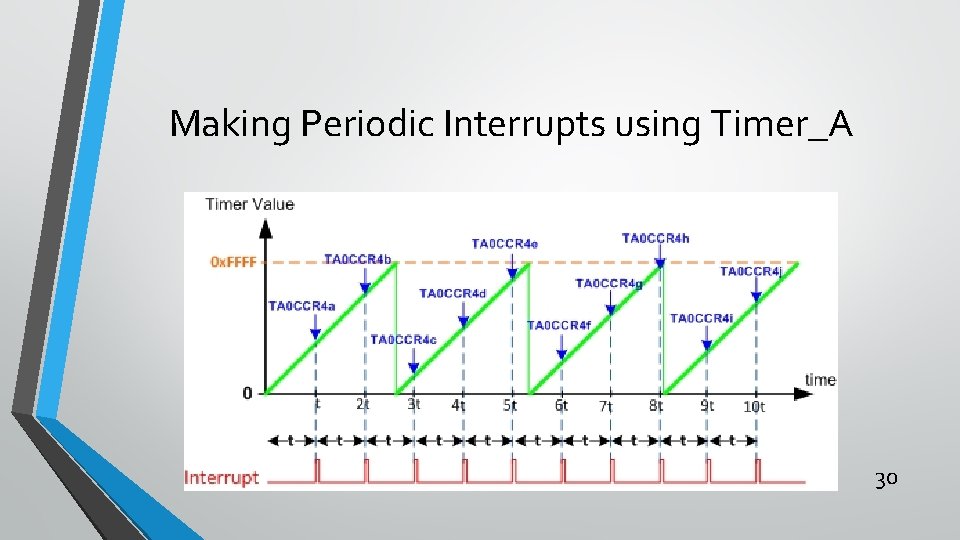

Making Periodic Interrupts using Timer_A 30

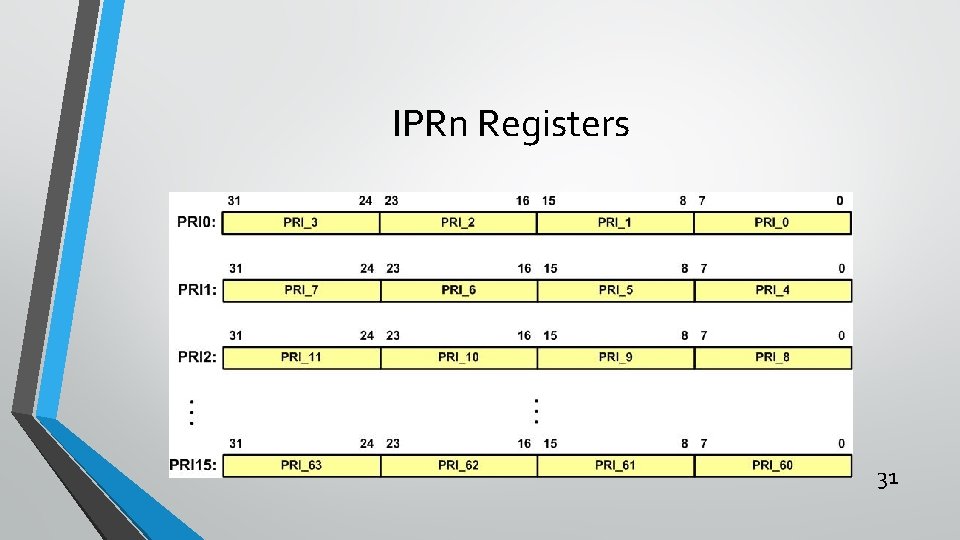

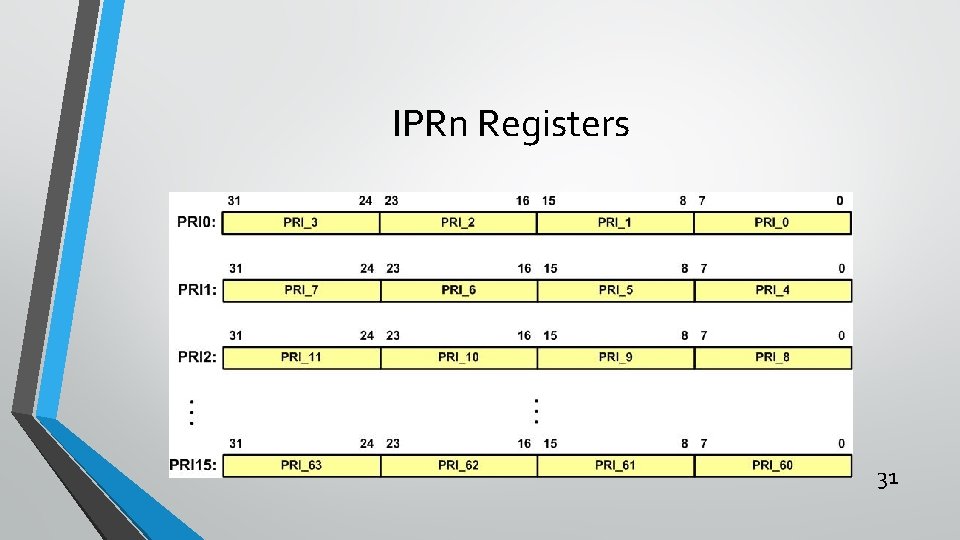

IPRn Registers 31