Chapter 6 Interrupt and Exception Programming 1 Polling

- Slides: 11

Chapter 6 Interrupt and Exception Programming 1

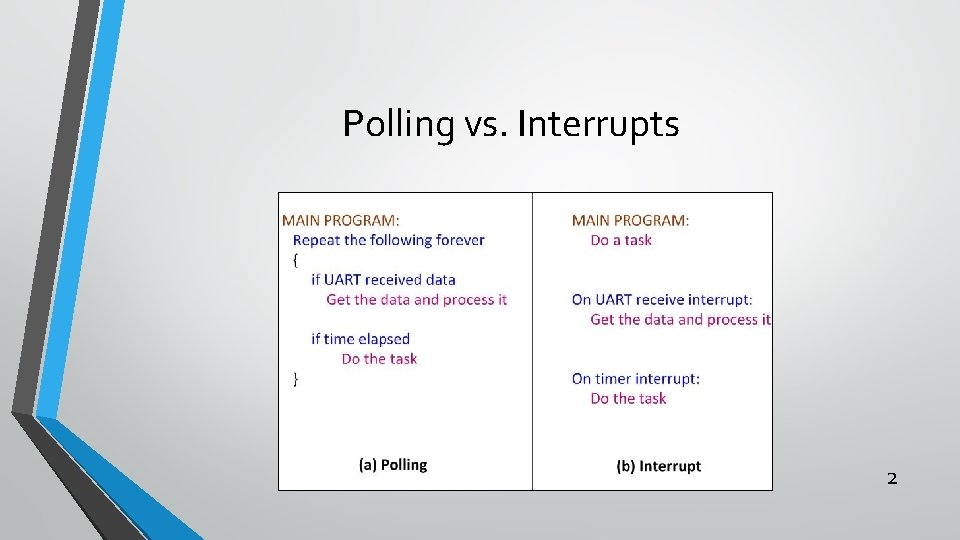

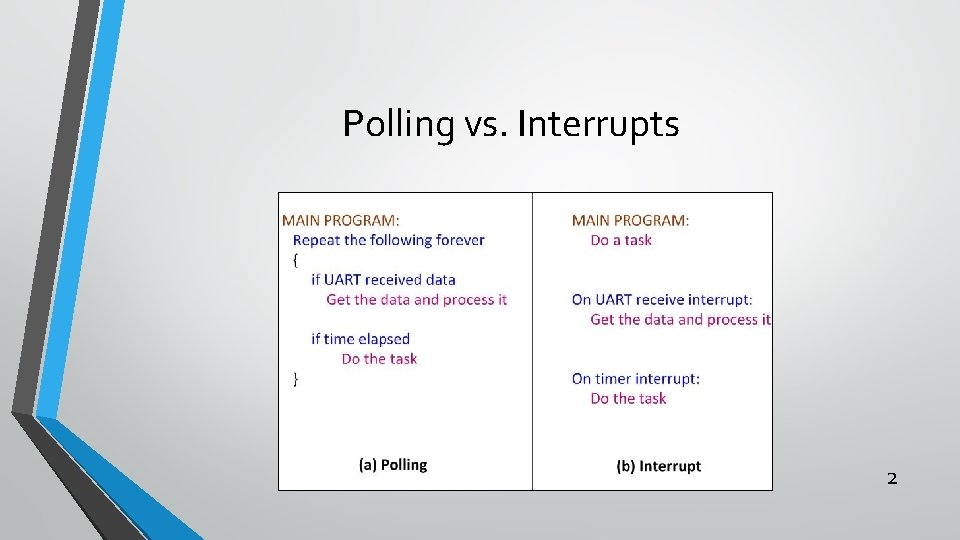

Polling vs. Interrupts 2

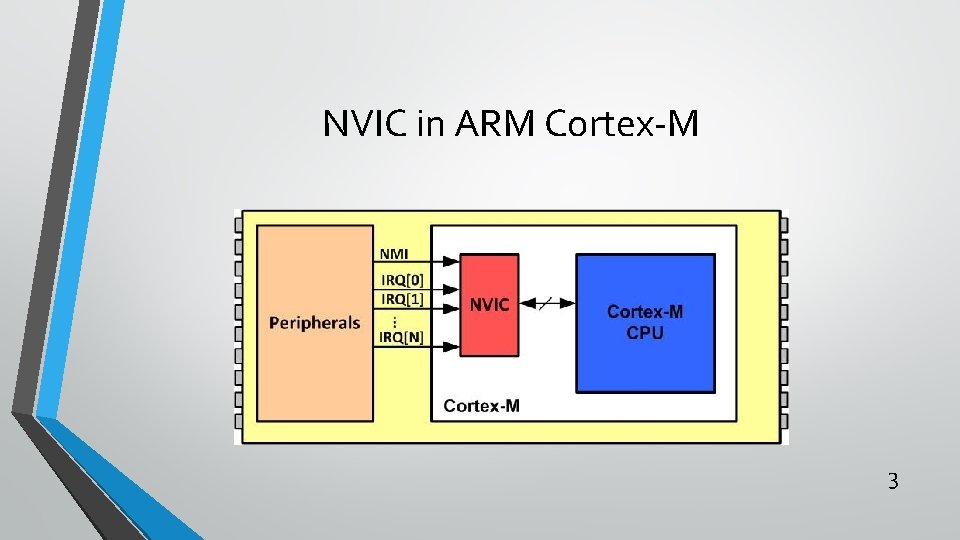

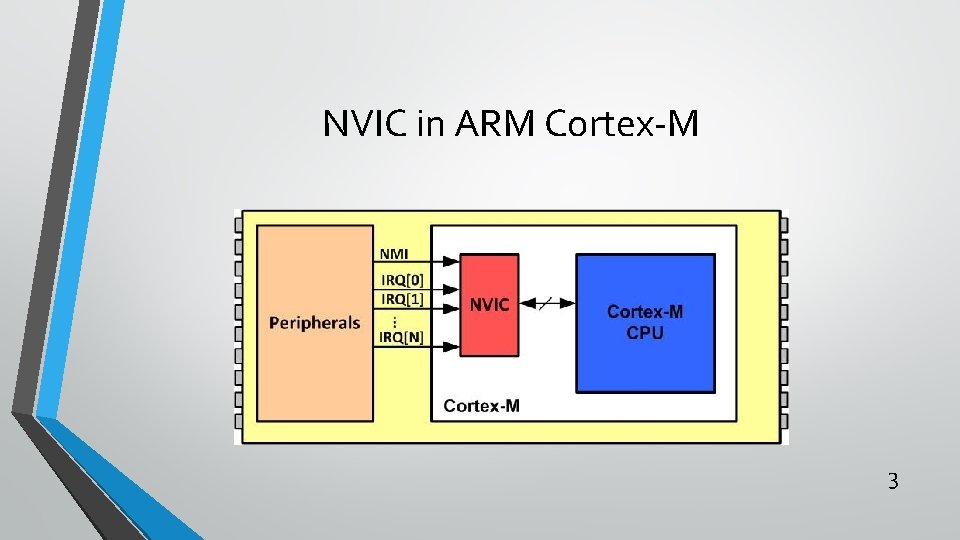

NVIC in ARM Cortex-M 3

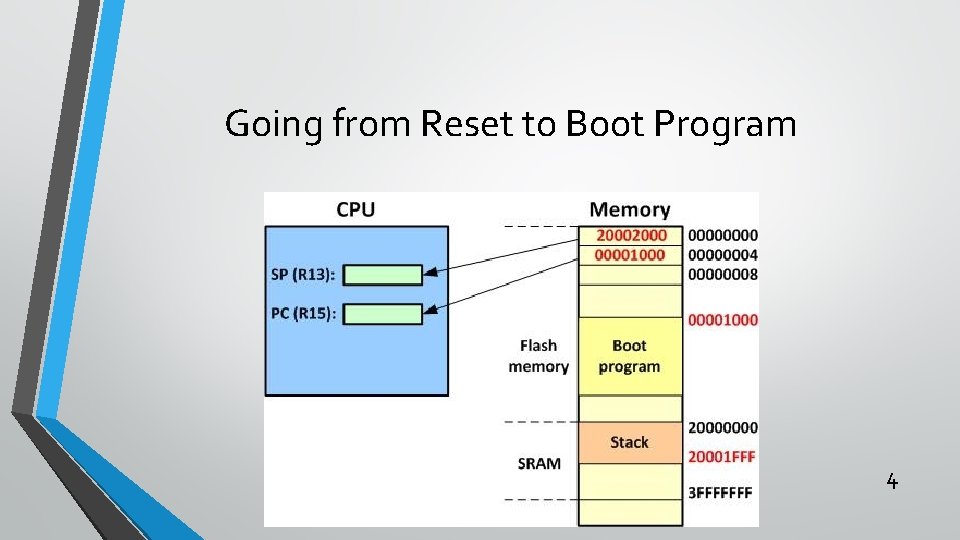

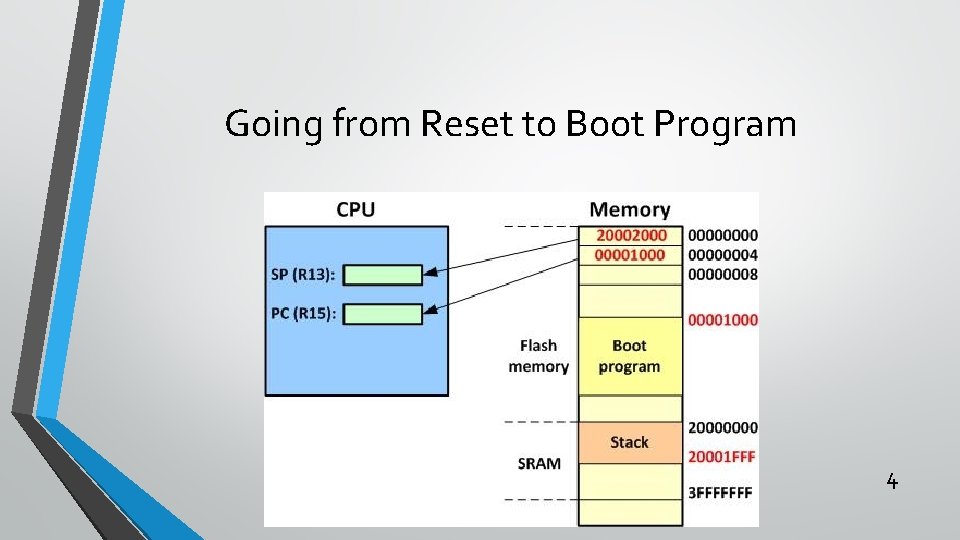

Going from Reset to Boot Program 4

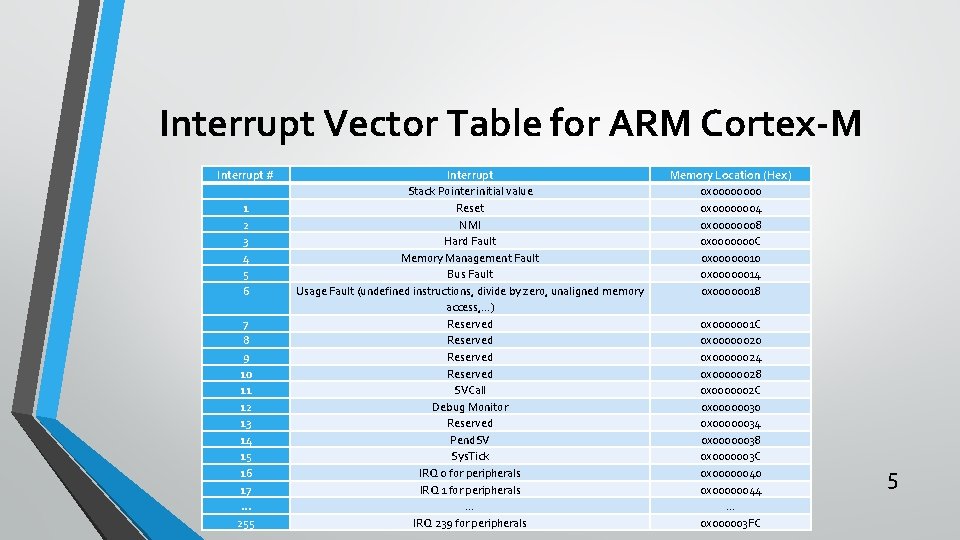

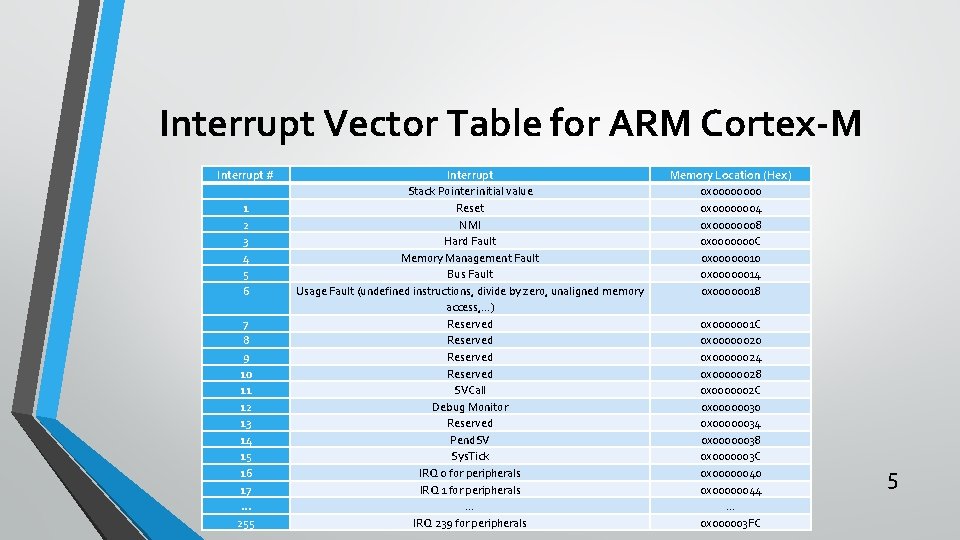

Interrupt Vector Table for ARM Cortex-M Interrupt # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Memory Location (Hex) 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C 0 x 00000020 0 x 00000024 0 x 00000028 0 x 0000002 C 0 x 00000030 0 x 00000034 0 x 00000038 0 x 0000003 C 0 x 00000040 0 x 00000044 … 0 x 000003 FC 5

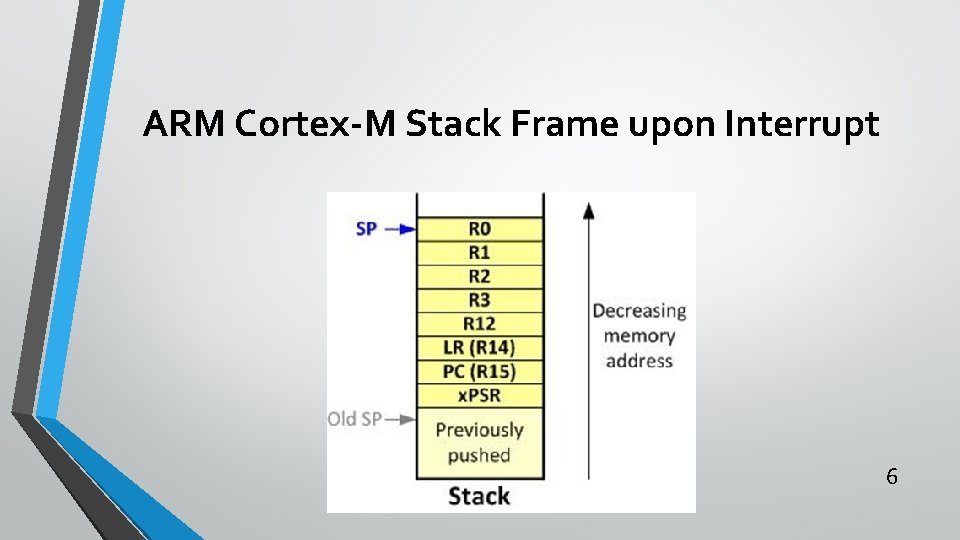

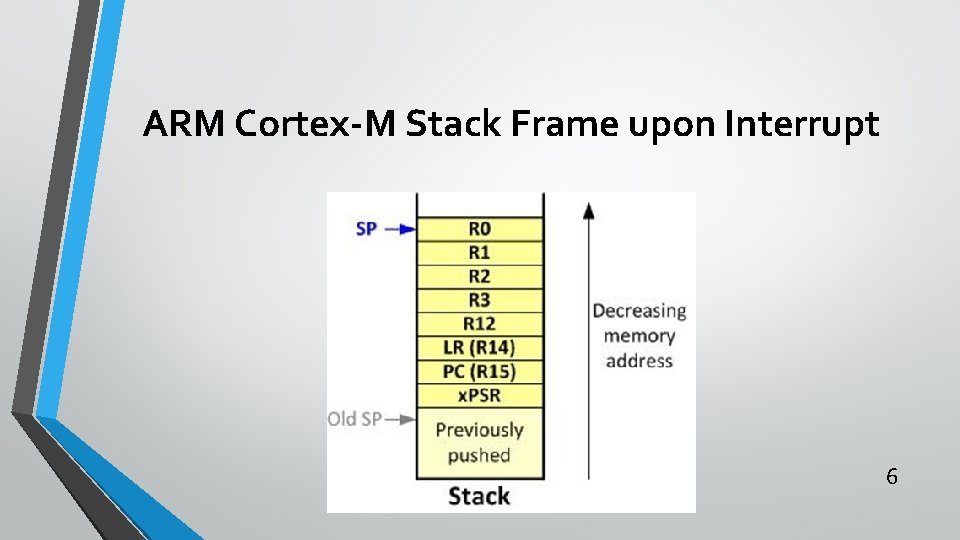

ARM Cortex-M Stack Frame upon Interrupt 6

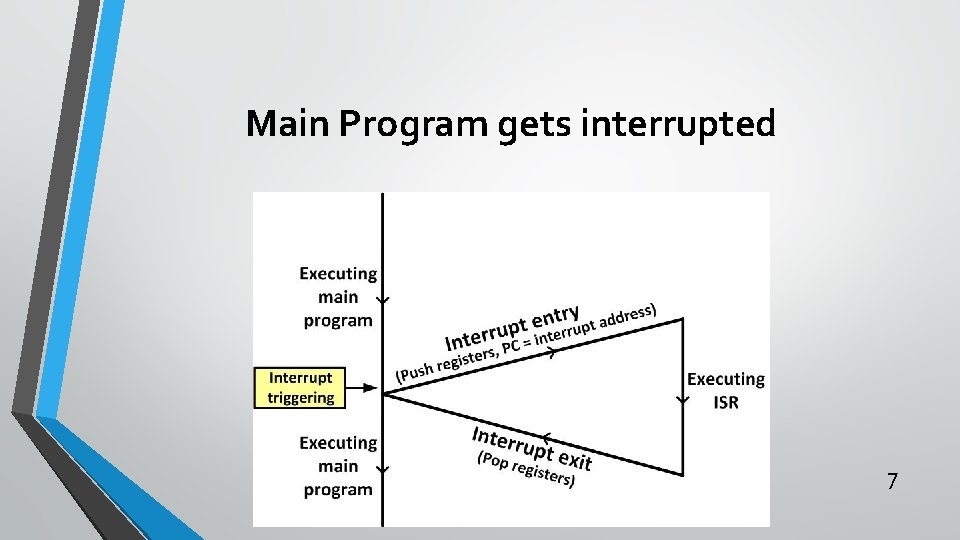

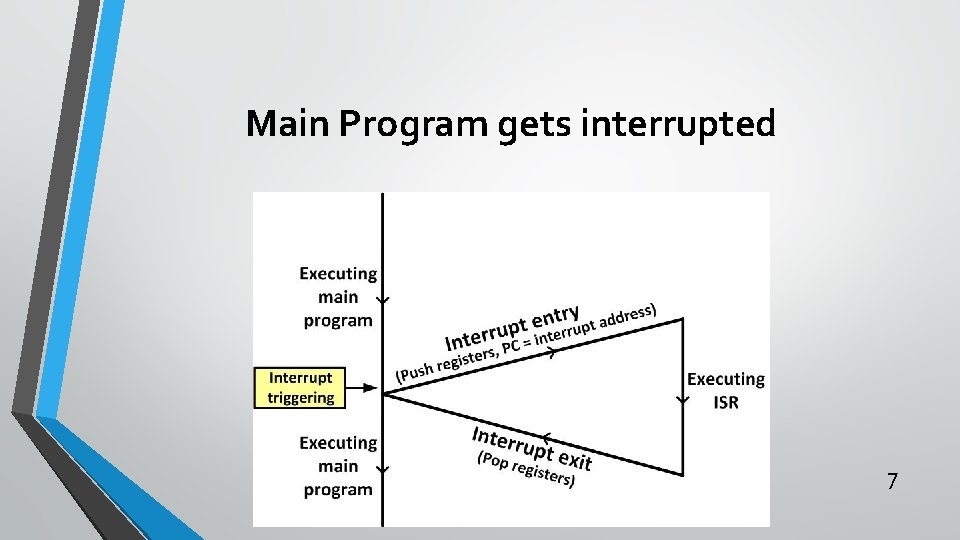

Main Program gets interrupted 7

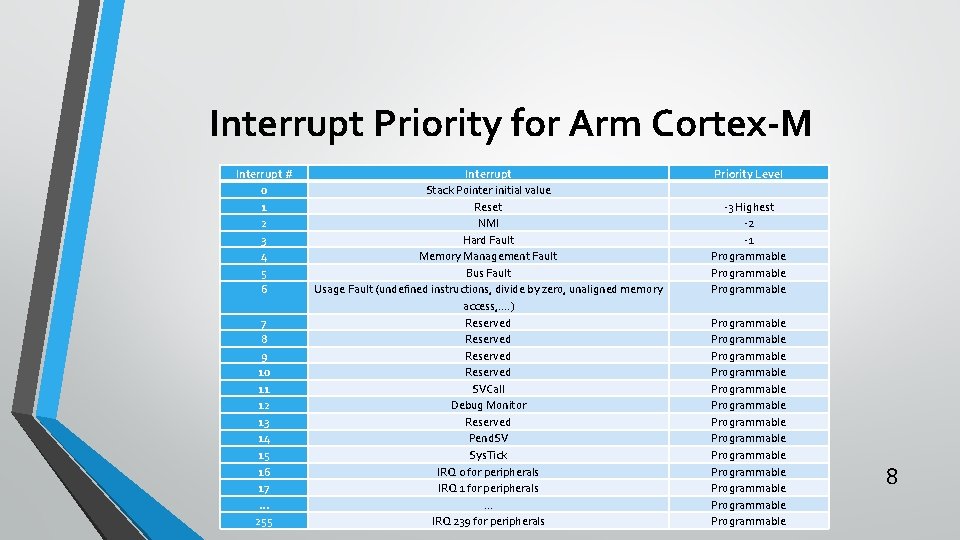

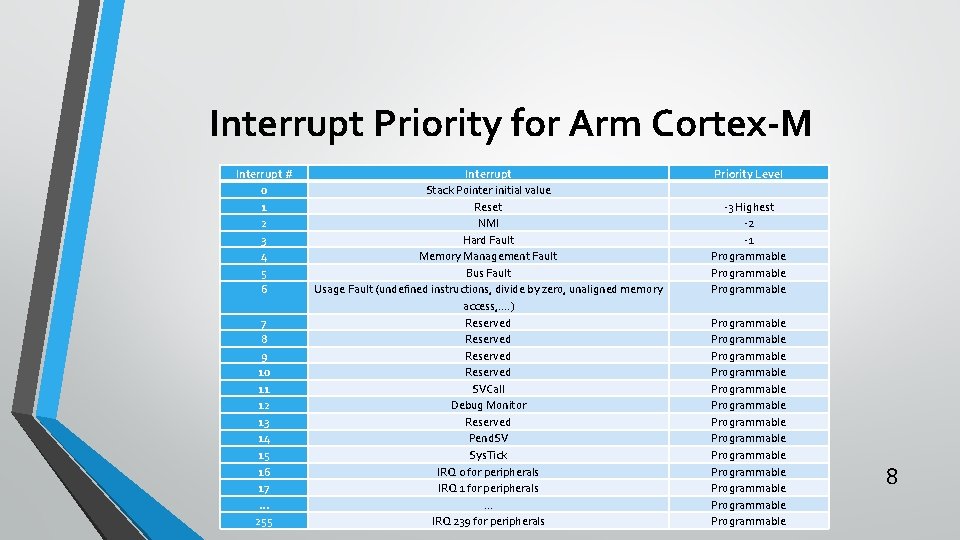

Interrupt Priority for Arm Cortex-M Interrupt # 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Priority Level -3 Highest -2 -1 Programmable Programmable Programmable Programmable 8

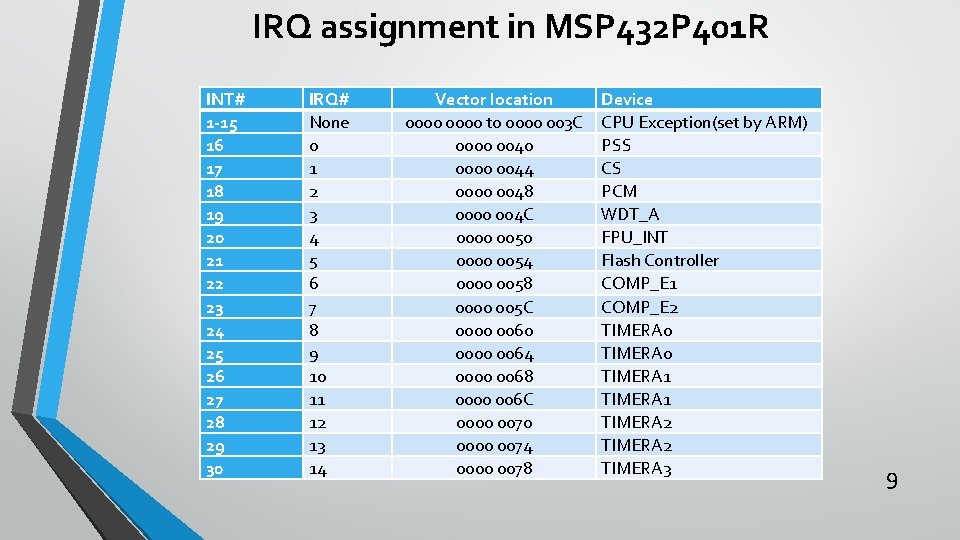

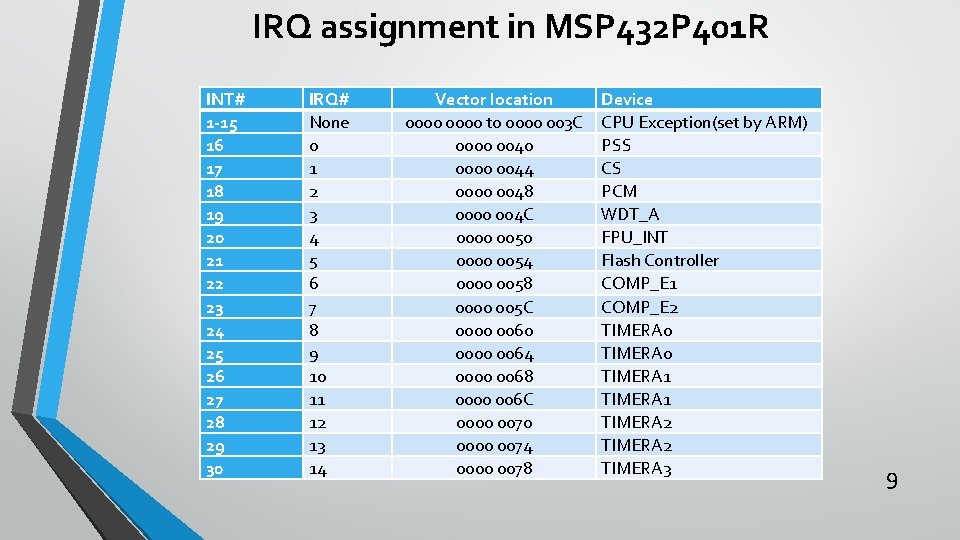

IRQ assignment in MSP 432 P 401 R INT# 1 -15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 IRQ# None 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 Vector location 0000 to 0000 003 C 0000 0040 0000 0044 0000 0048 0000 004 C 0000 0050 0000 0054 0000 0058 0000 005 C 0000 0060 0000 0064 0000 0068 0000 006 C 0000 0070 0000 0074 0000 0078 Device CPU Exception(set by ARM) PSS CS PCM WDT_A FPU_INT Flash Controller COMP_E 1 COMP_E 2 TIMERA 0 TIMERA 1 TIMERA 2 TIMERA 3 9

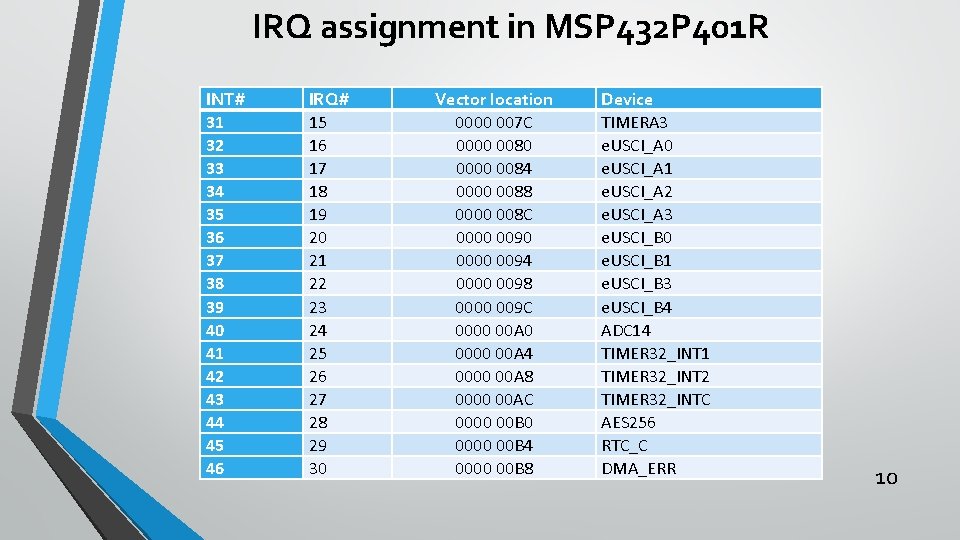

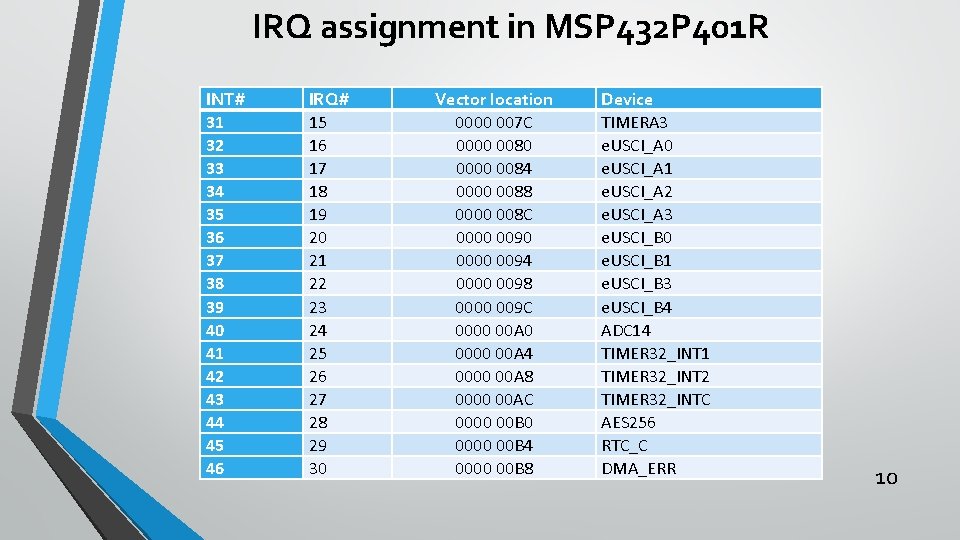

IRQ assignment in MSP 432 P 401 R INT# 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 IRQ# 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 Vector location 0000 007 C 0000 0080 0000 0084 0000 0088 0000 008 C 0000 0090 0000 0094 0000 0098 0000 009 C 0000 00 A 0 0000 00 A 4 0000 00 A 8 0000 00 AC 0000 00 B 0 0000 00 B 4 0000 00 B 8 Device TIMERA 3 e. USCI_A 0 e. USCI_A 1 e. USCI_A 2 e. USCI_A 3 e. USCI_B 0 e. USCI_B 1 e. USCI_B 3 e. USCI_B 4 ADC 14 TIMER 32_INT 1 TIMER 32_INT 2 TIMER 32_INTC AES 256 RTC_C DMA_ERR 10

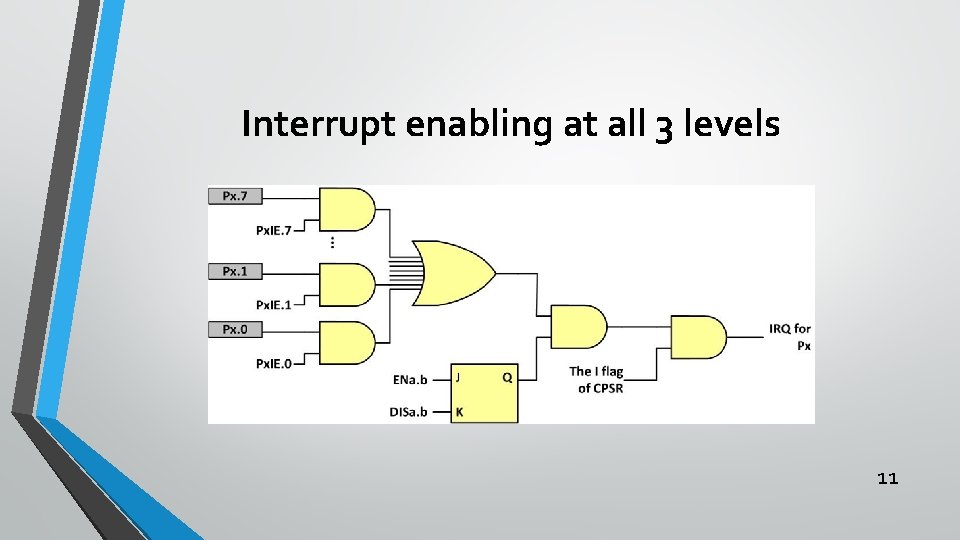

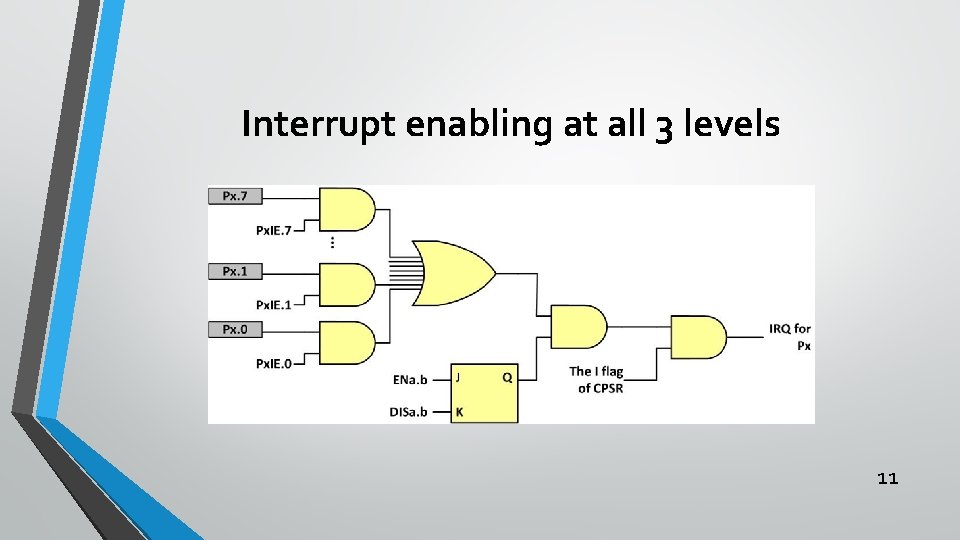

Interrupt enabling at all 3 levels 11