Chapter 6 Interrupt and Exception Programming 1 Polling

![Set Enable Register (ISER[1]) for IRQ 32– 63 24 Set Enable Register (ISER[1]) for IRQ 32– 63 24](https://slidetodoc.com/presentation_image_h/23fdb53fa6aa2cd866ae3ff7cebcfb2c/image-24.jpg)

![Clear Enable Register (ICER[1]) for IRQ 32– 63 25 Clear Enable Register (ICER[1]) for IRQ 32– 63 25](https://slidetodoc.com/presentation_image_h/23fdb53fa6aa2cd866ae3ff7cebcfb2c/image-25.jpg)

- Slides: 31

Chapter 6 Interrupt and Exception Programming 1

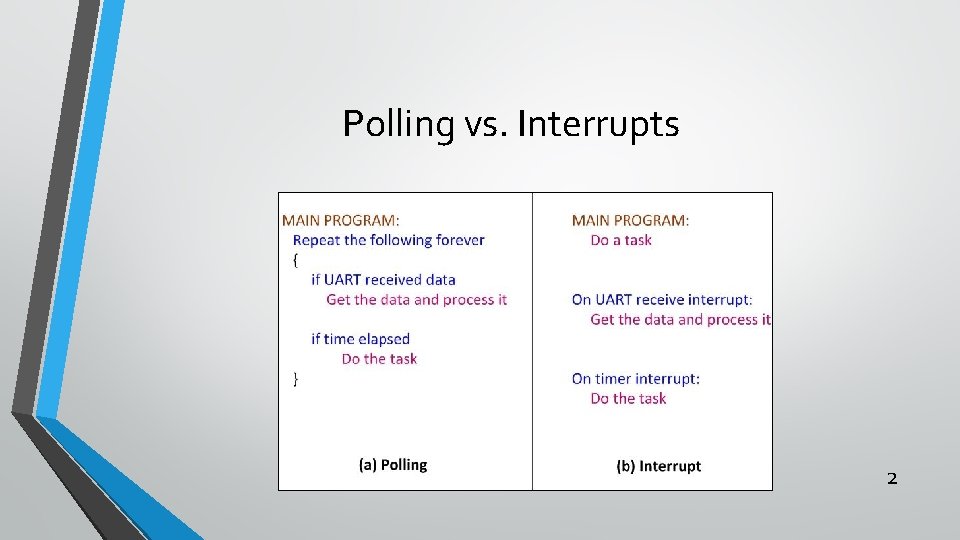

Polling vs. Interrupts 2

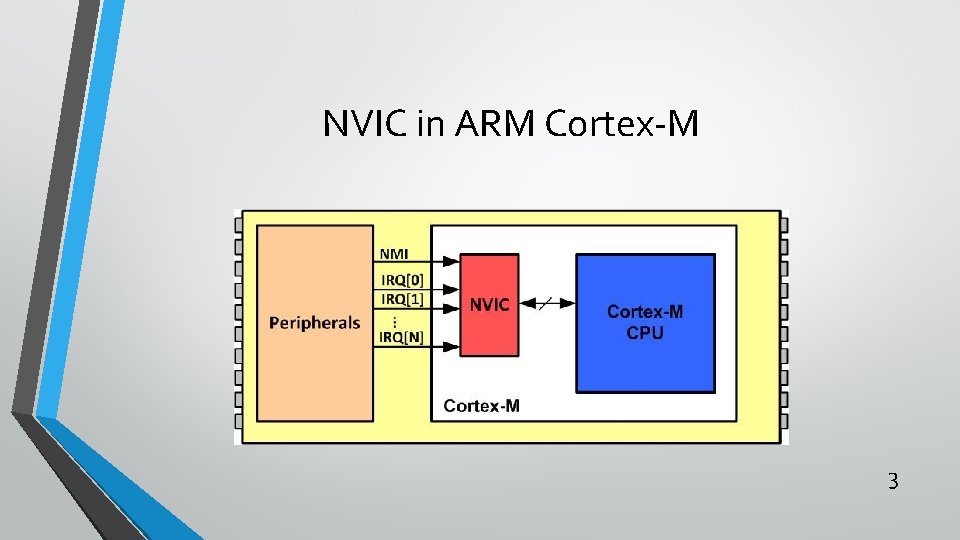

NVIC in ARM Cortex-M 3

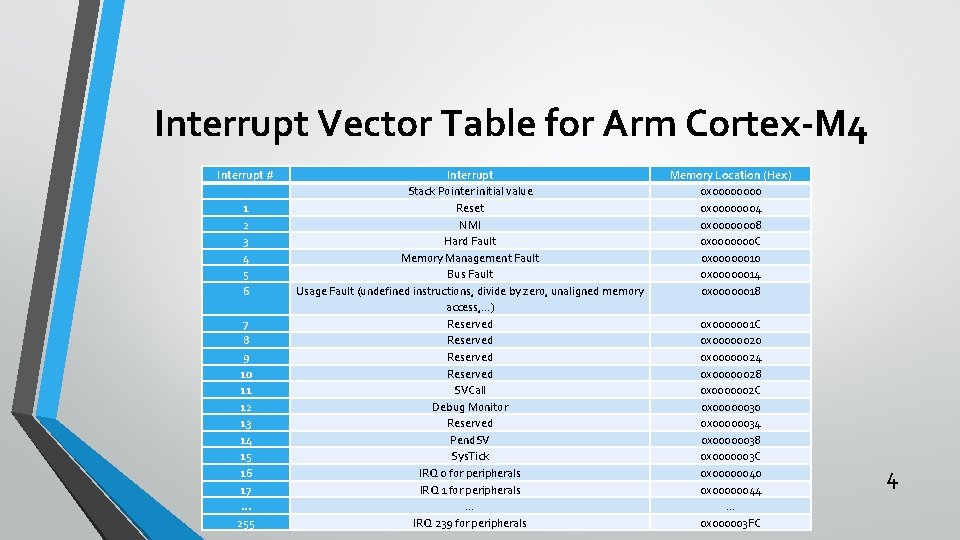

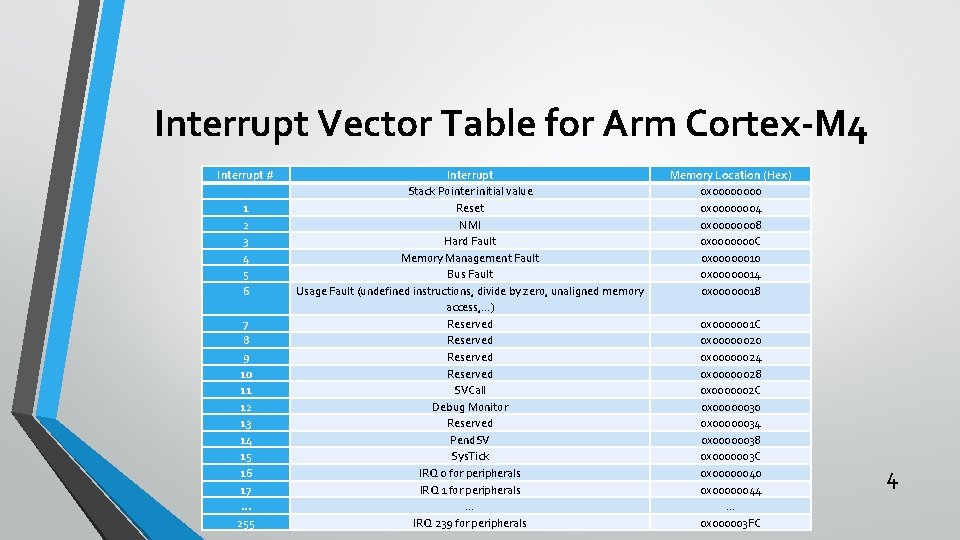

Interrupt Vector Table for Arm Cortex-M 4 Interrupt # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Memory Location (Hex) 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C 0 x 00000020 0 x 00000024 0 x 00000028 0 x 0000002 C 0 x 00000030 0 x 00000034 0 x 00000038 0 x 0000003 C 0 x 00000040 0 x 00000044 … 0 x 000003 FC 4

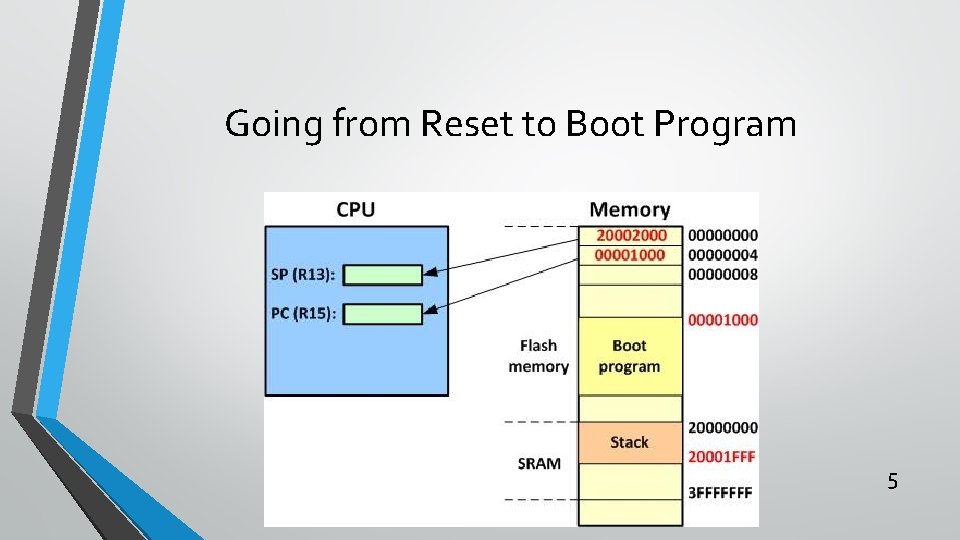

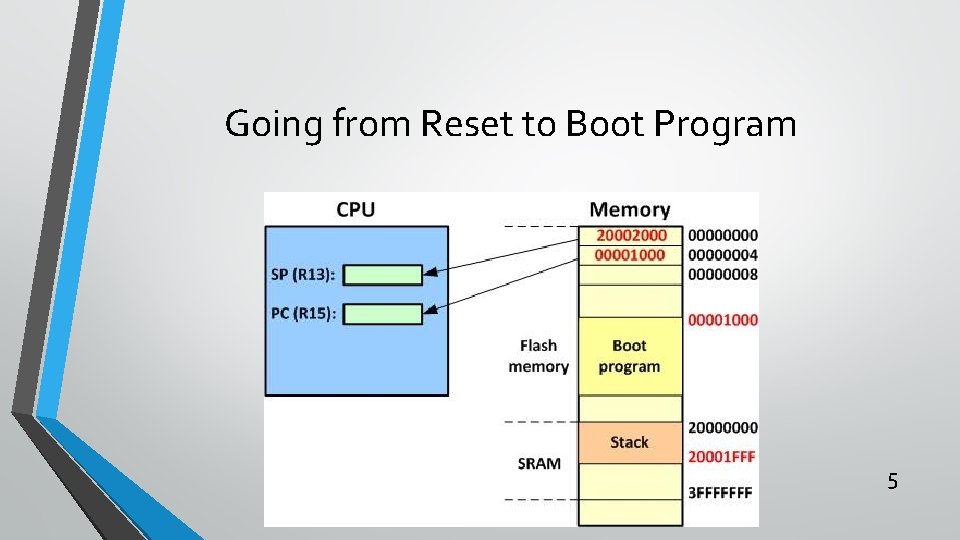

Going from Reset to Boot Program 5

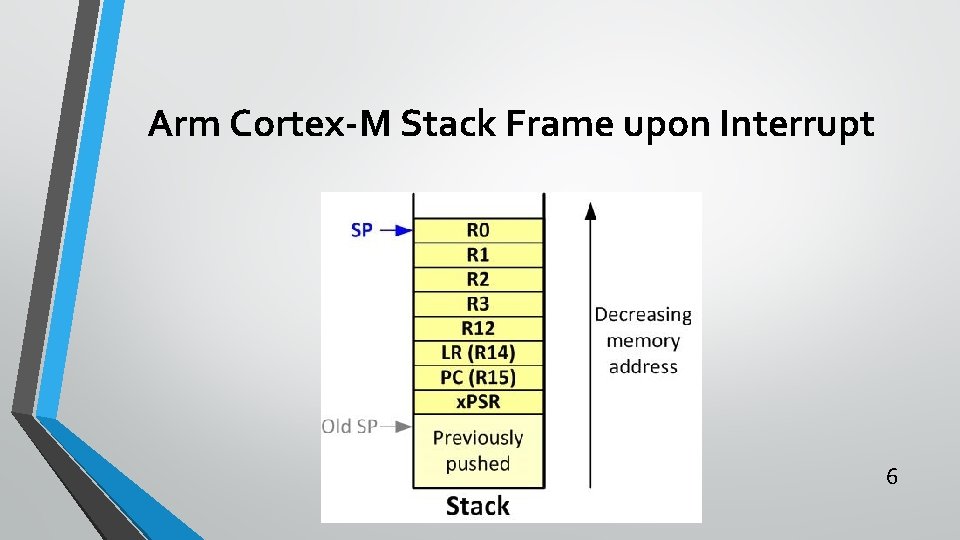

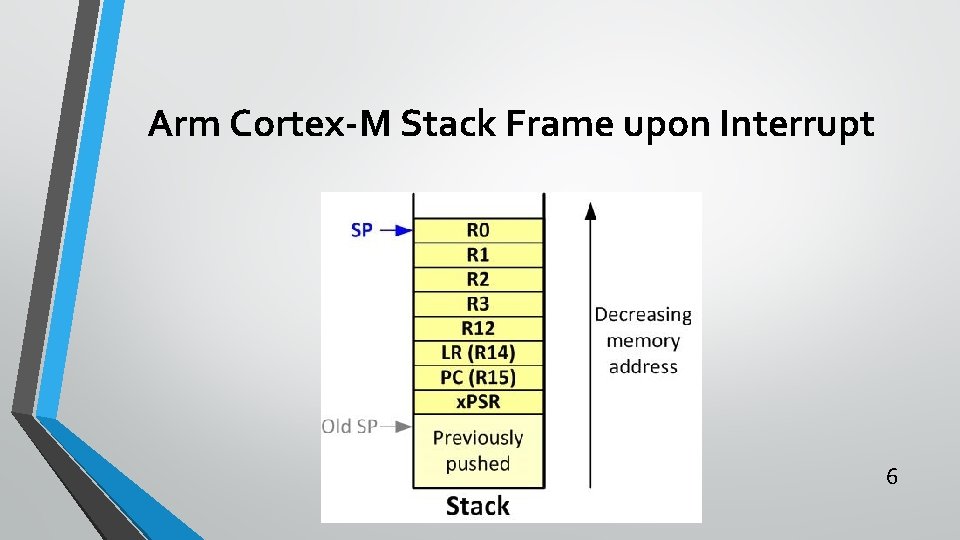

Arm Cortex-M Stack Frame upon Interrupt 6

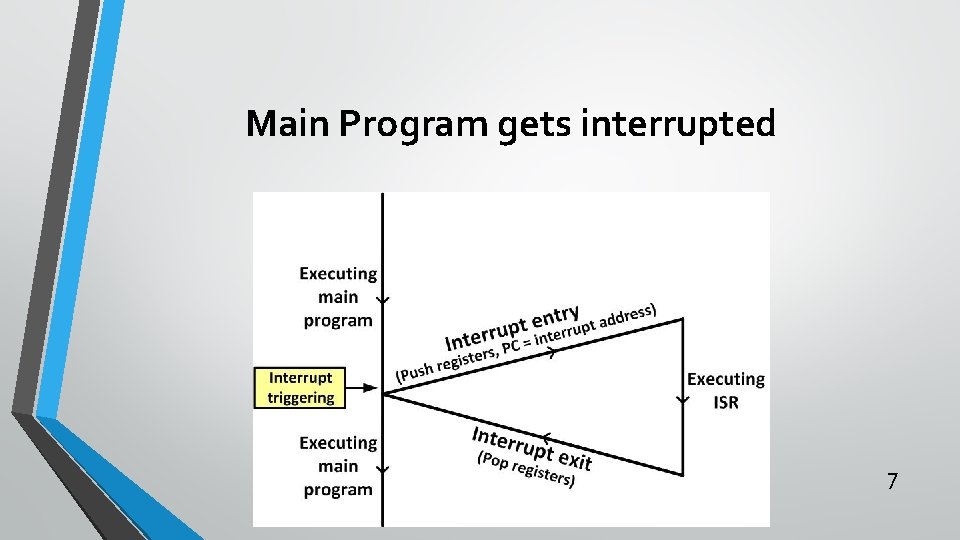

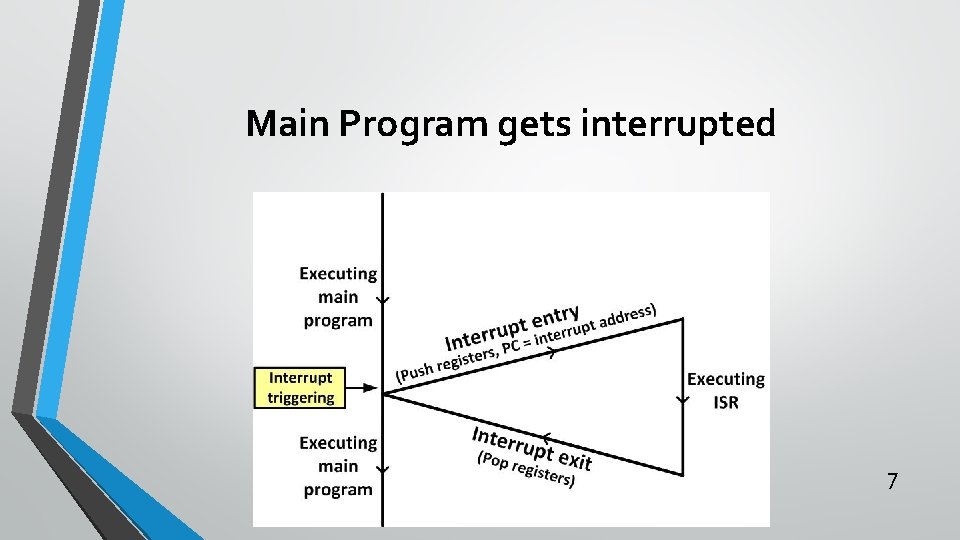

Main Program gets interrupted 7

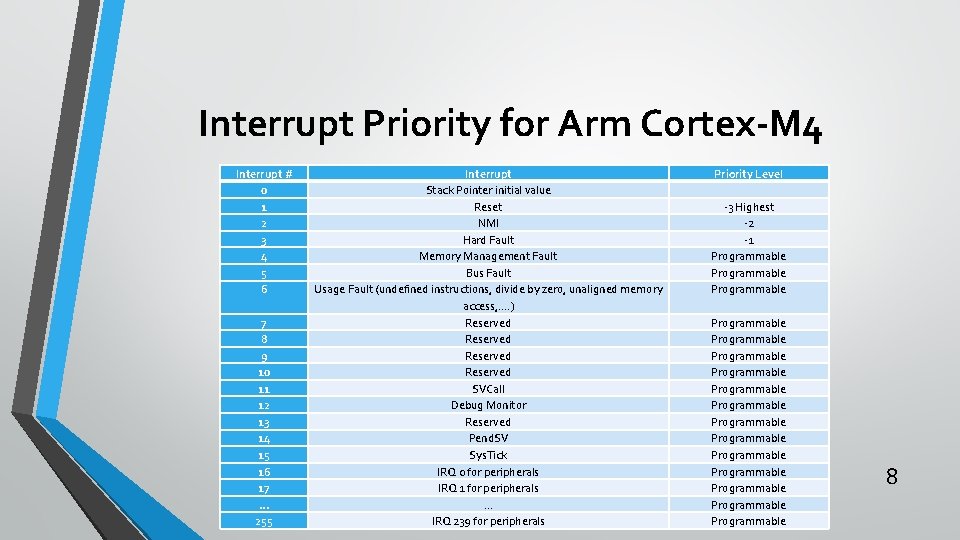

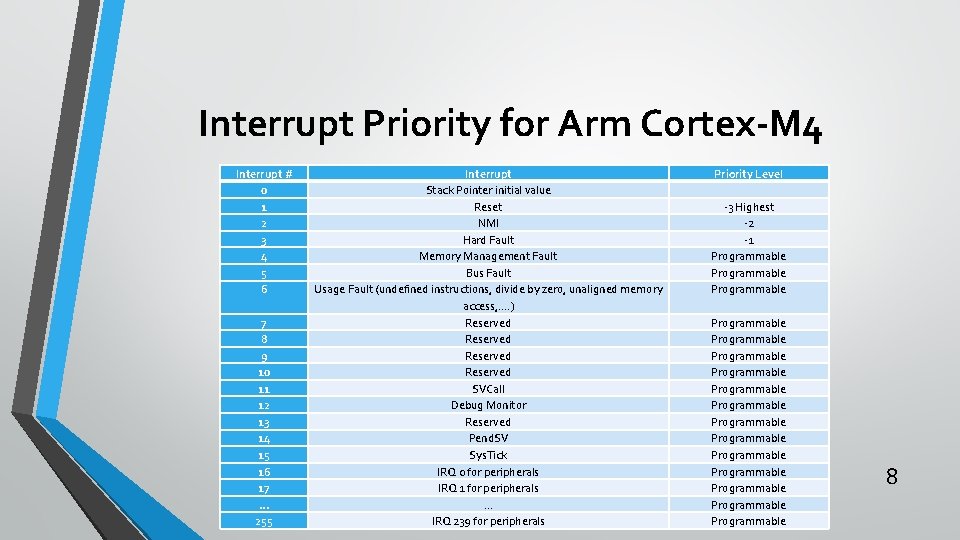

Interrupt Priority for Arm Cortex-M 4 Interrupt # 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 … 255 Interrupt Stack Pointer initial value Reset NMI Hard Fault Memory Management Fault Bus Fault Usage Fault (undefined instructions, divide by zero, unaligned memory access, . . ) Reserved SVCall Debug Monitor Reserved Pend. SV Sys. Tick IRQ 0 for peripherals IRQ 1 for peripherals … IRQ 239 for peripherals Priority Level -3 Highest -2 -1 Programmable Programmable Programmable Programmable 8

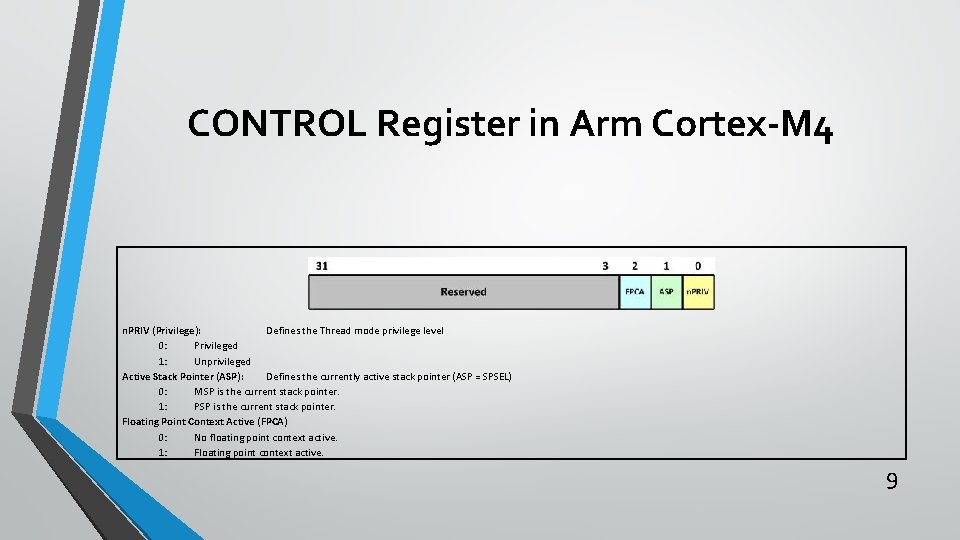

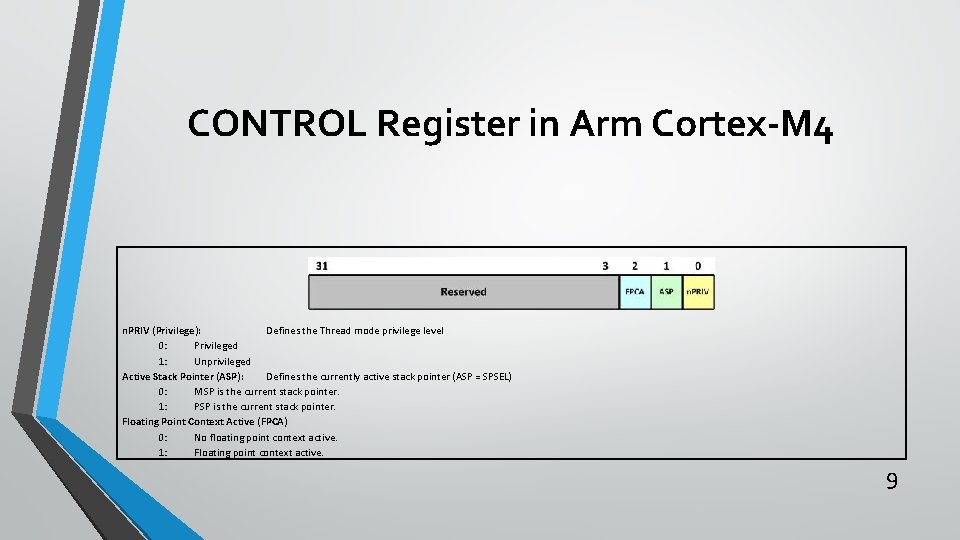

CONTROL Register in Arm Cortex-M 4 n. PRIV (Privilege): Defines the Thread mode privilege level 0: Privileged 1: Unprivileged Active Stack Pointer (ASP): Defines the currently active stack pointer (ASP = SPSEL) 0: MSP is the current stack pointer. 1: PSP is the current stack pointer. Floating Point Context Active (FPCA) 0: No floating point context active. 1: Floating point context active. 9

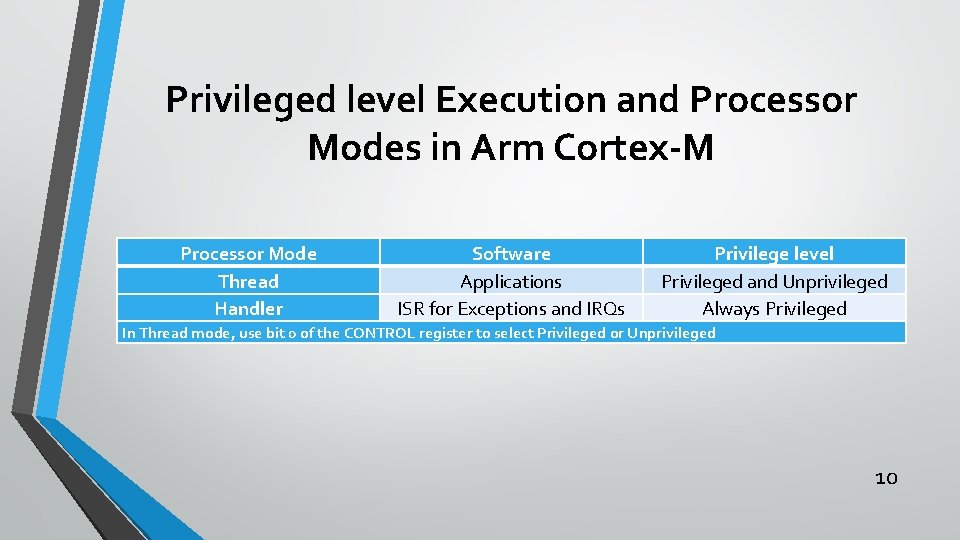

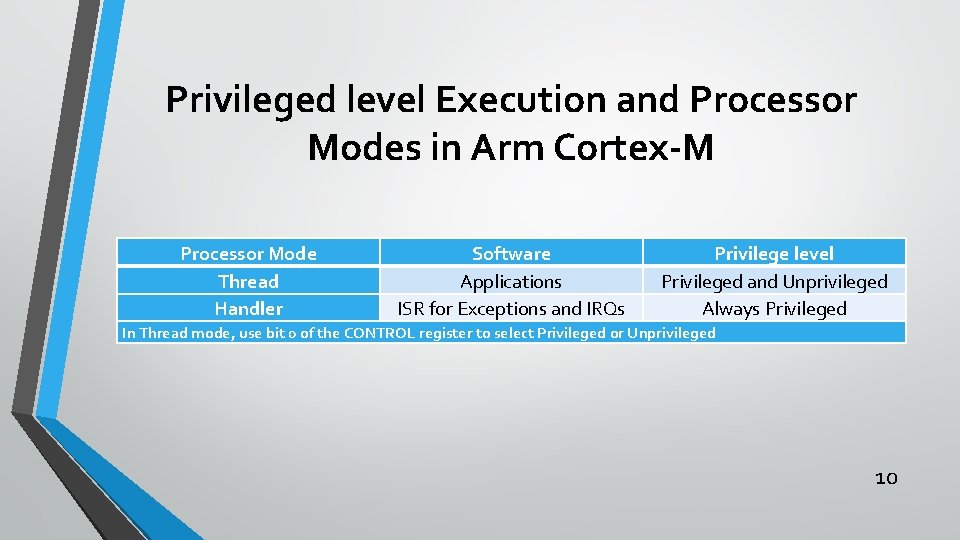

Privileged level Execution and Processor Modes in Arm Cortex-M Processor Mode Thread Handler Software Applications ISR for Exceptions and IRQs Privilege level Privileged and Unprivileged Always Privileged In Thread mode, use bit 0 of the CONTROL register to select Privileged or Unprivileged 10

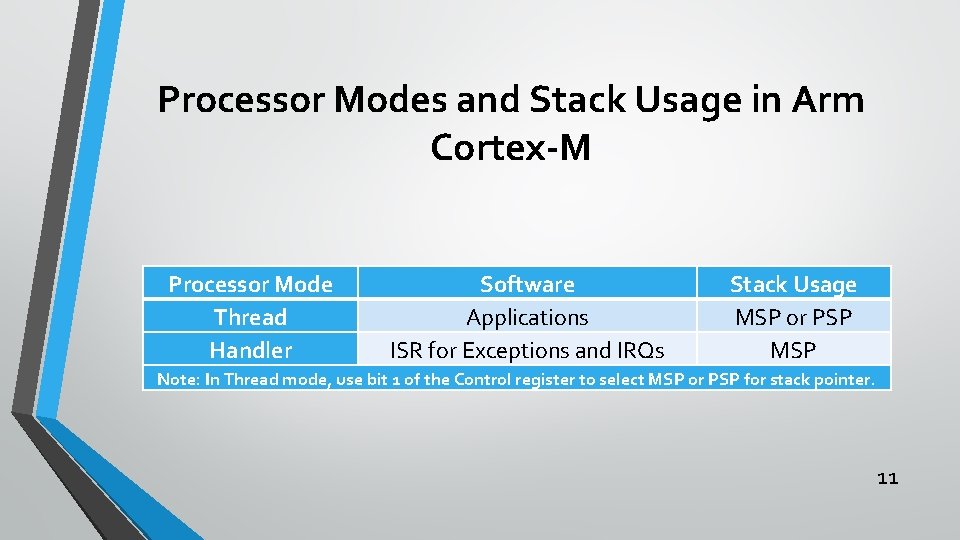

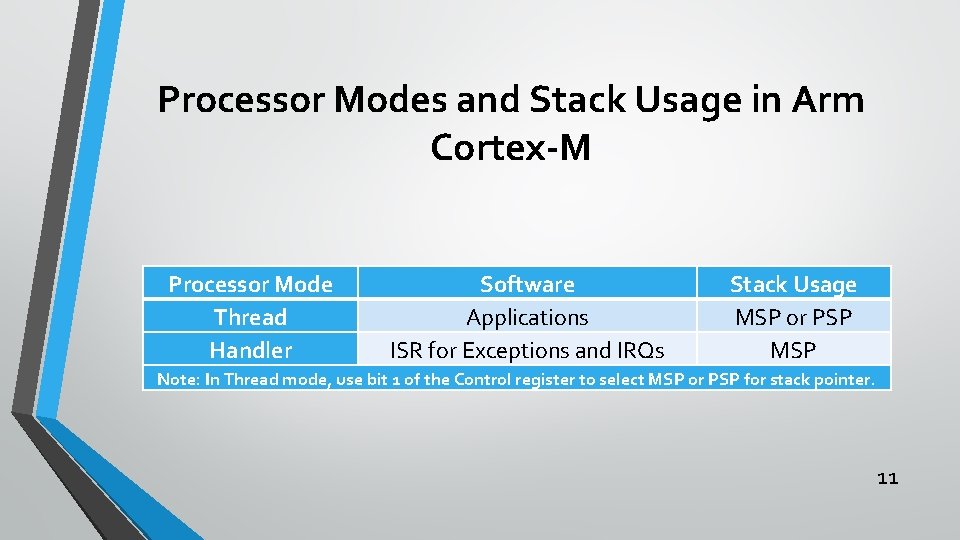

Processor Modes and Stack Usage in Arm Cortex-M Processor Mode Thread Handler Software Applications ISR for Exceptions and IRQs Stack Usage MSP or PSP MSP Note: In Thread mode, use bit 1 of the Control register to select MSP or PSP for stack pointer. 11

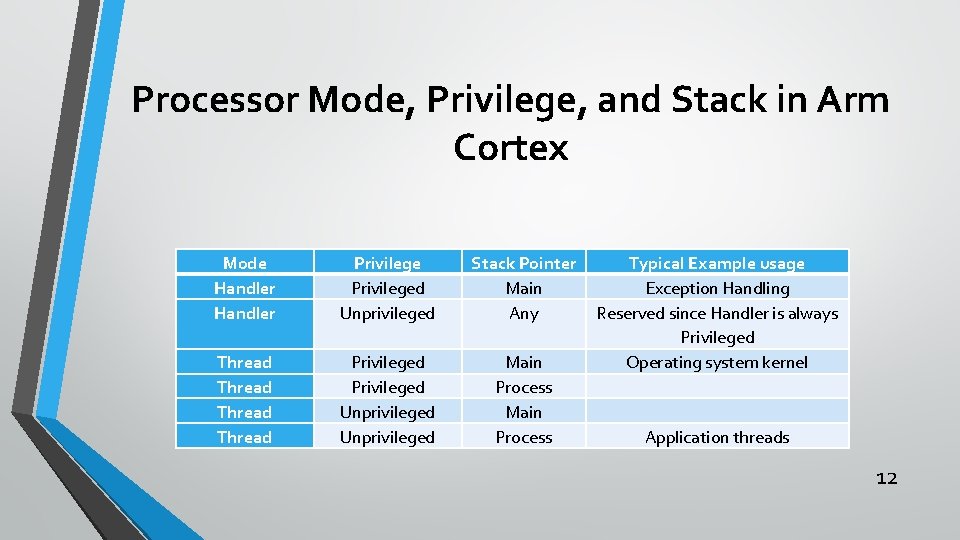

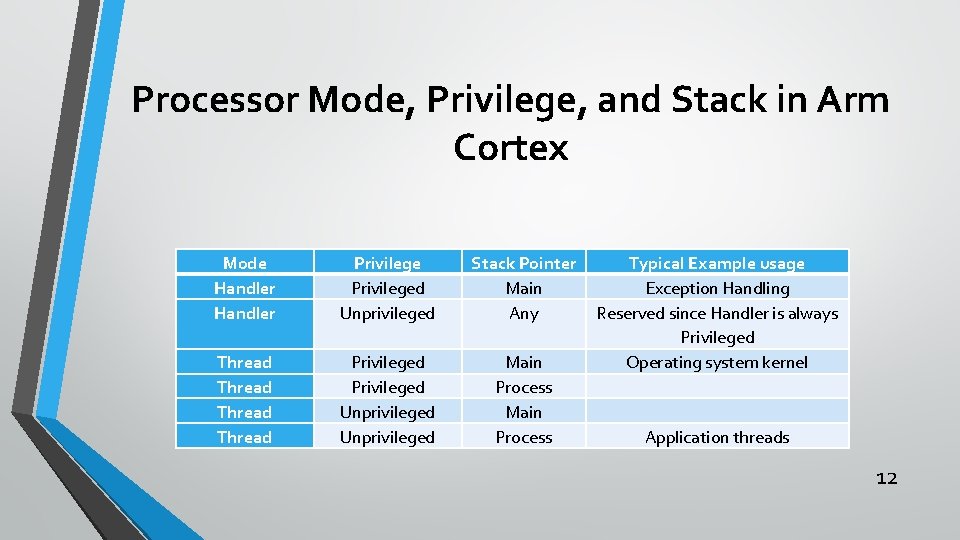

Processor Mode, Privilege, and Stack in Arm Cortex Mode Handler Privileged Unprivileged Stack Pointer Main Any Thread Privileged Unprivileged Main Process Typical Example usage Exception Handling Reserved since Handler is always Privileged Operating system kernel Application threads 12

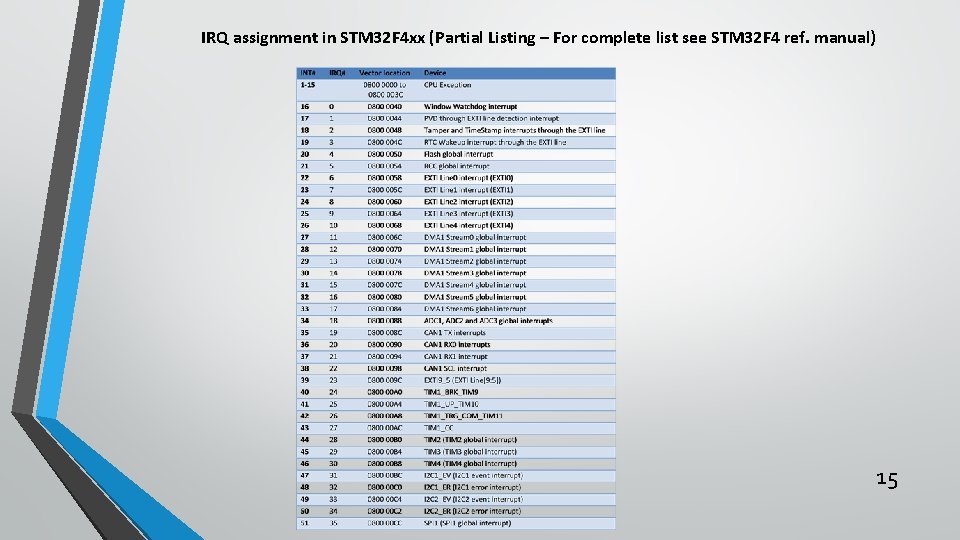

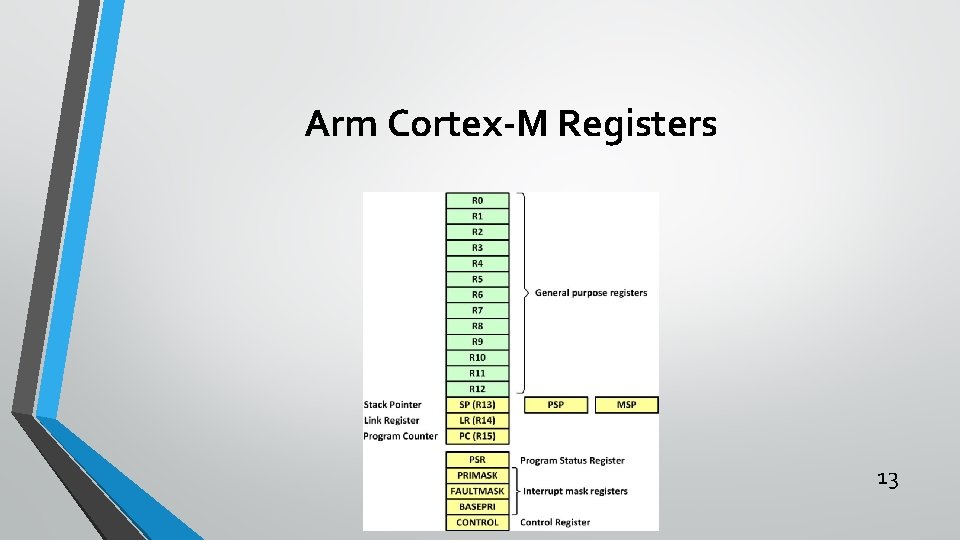

Arm Cortex-M Registers 13

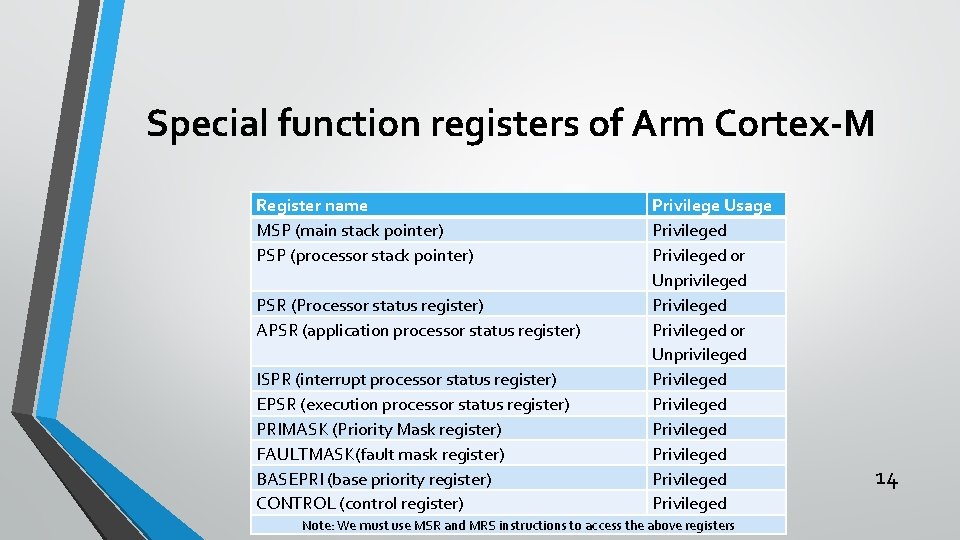

Special function registers of Arm Cortex-M Register name MSP (main stack pointer) PSP (processor stack pointer) PSR (Processor status register) APSR (application processor status register) ISPR (interrupt processor status register) EPSR (execution processor status register) PRIMASK (Priority Mask register) FAULTMASK(fault mask register) BASEPRI (base priority register) CONTROL (control register) Privilege Usage Privileged or Unprivileged Privileged Privileged Note: We must use MSR and MRS instructions to access the above registers 14

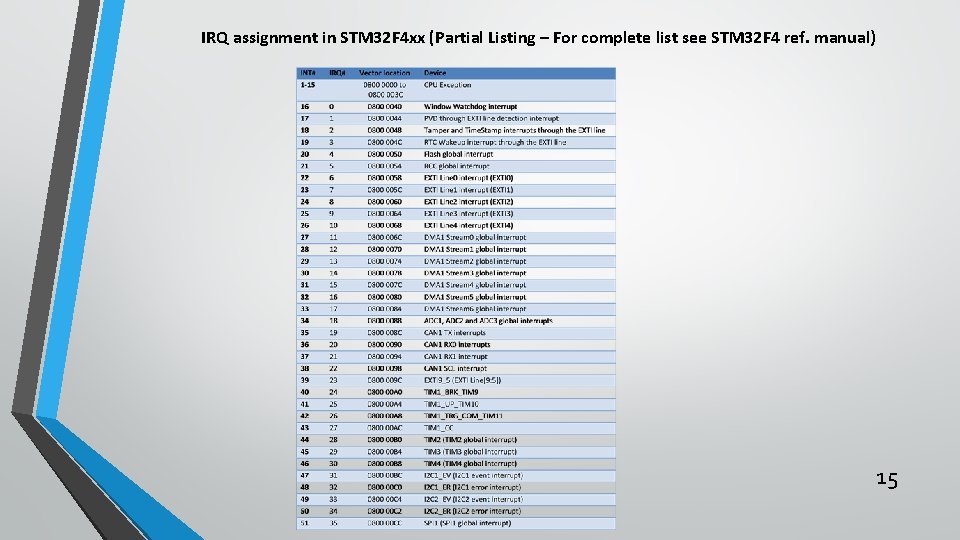

IRQ assignment in STM 32 F 4 xx (Partial Listing – For complete list see STM 32 F 4 ref. manual) 15

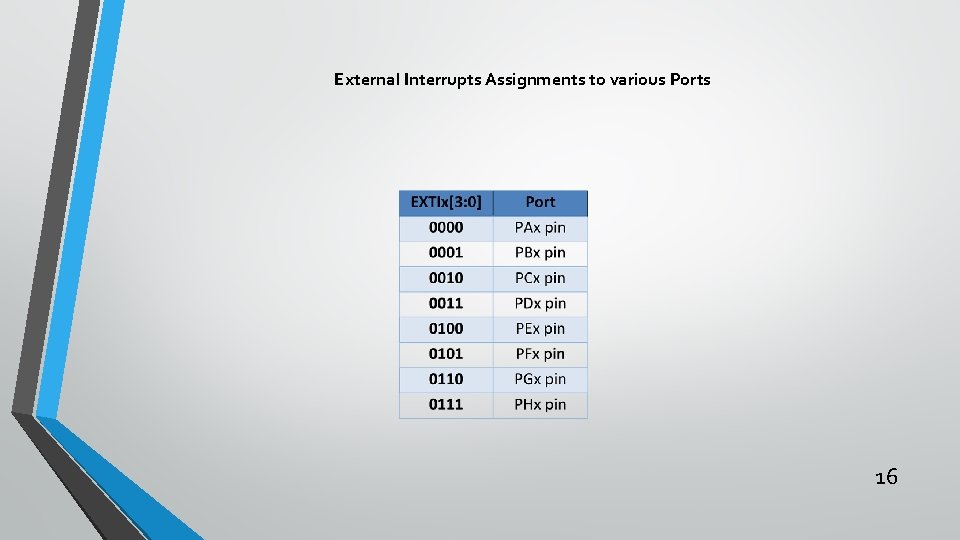

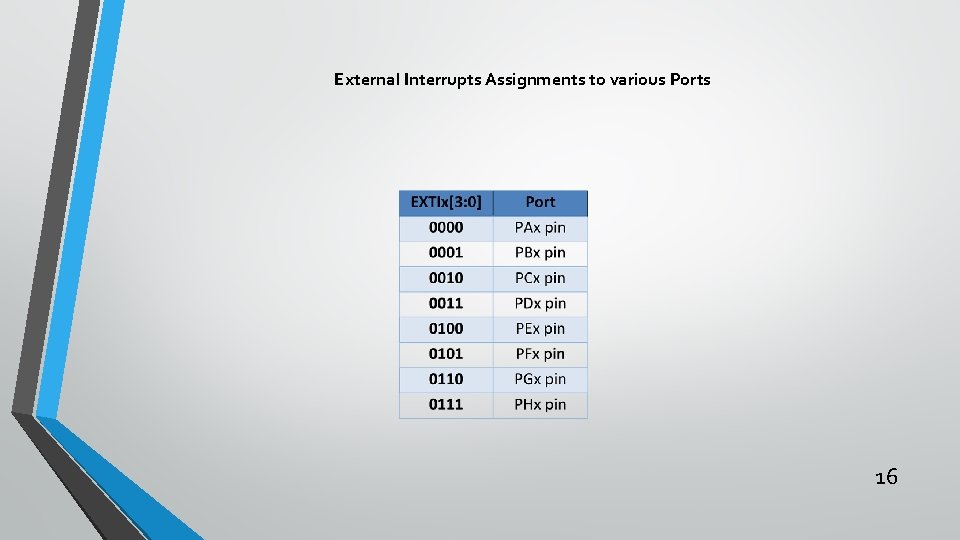

External Interrupts Assignments to various Ports 16

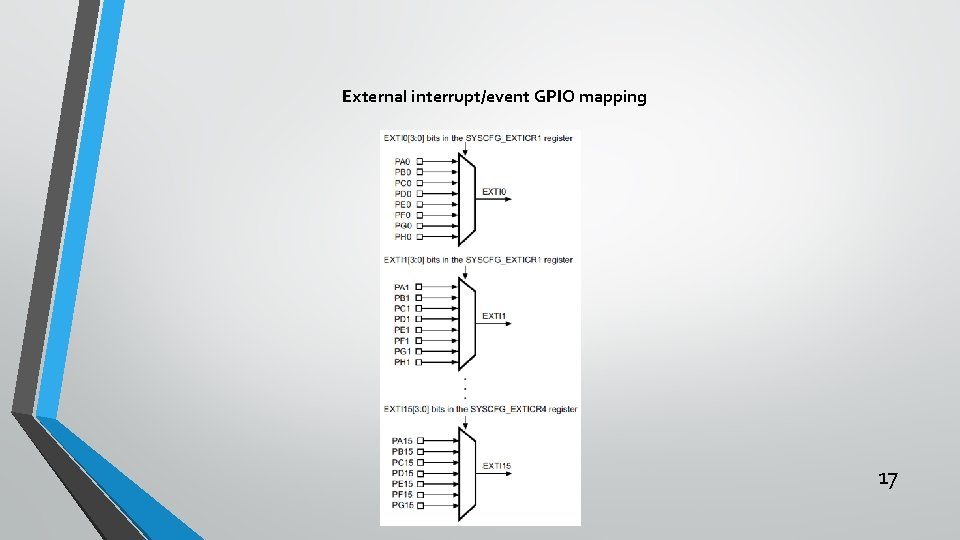

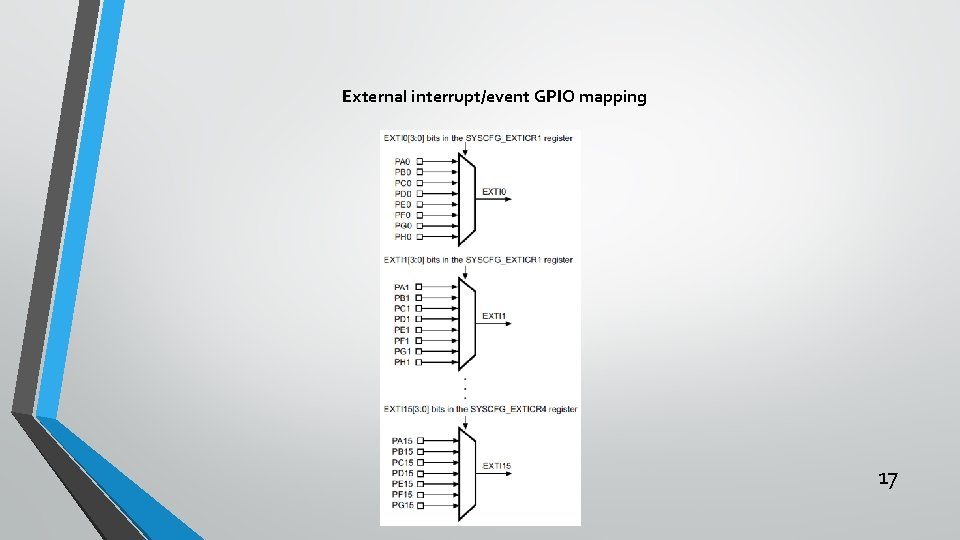

External interrupt/event GPIO mapping 17

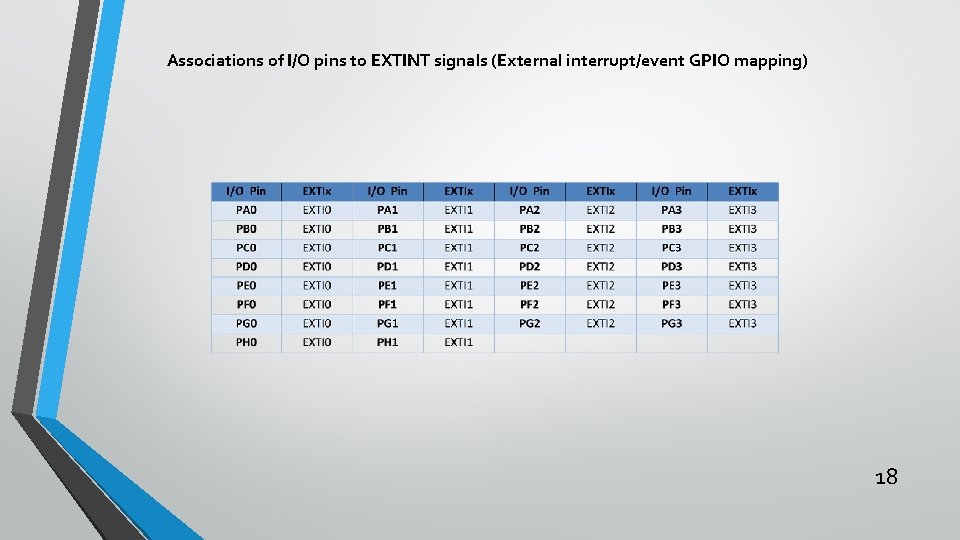

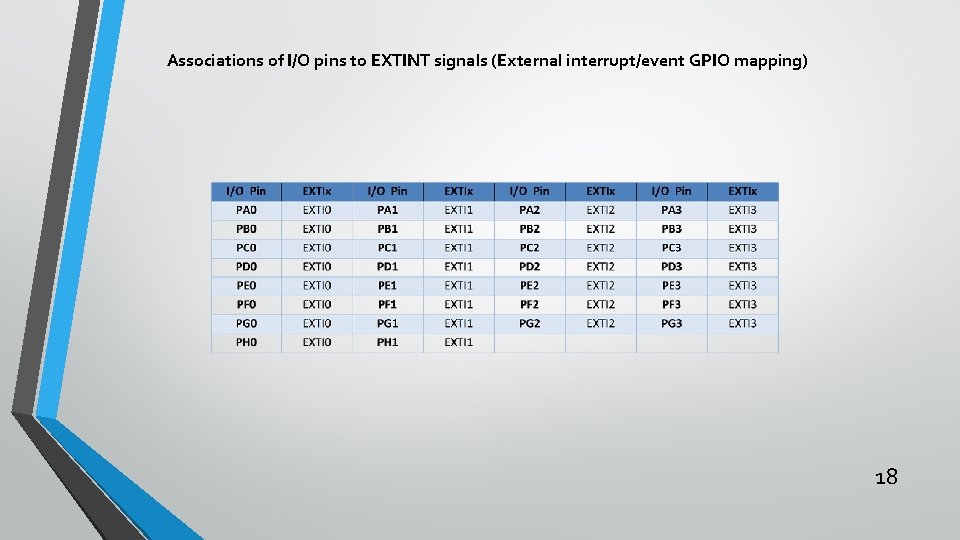

Associations of I/O pins to EXTINT signals (External interrupt/event GPIO mapping) 18

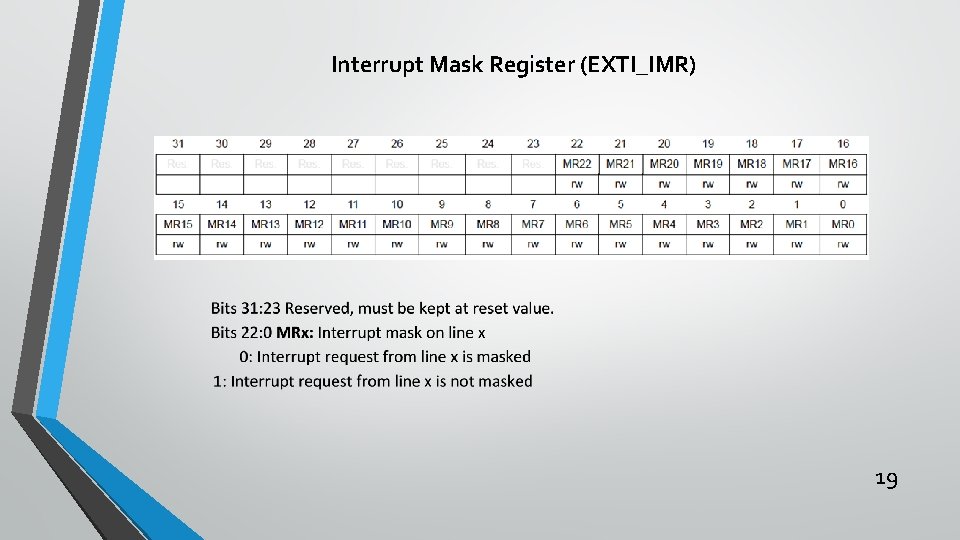

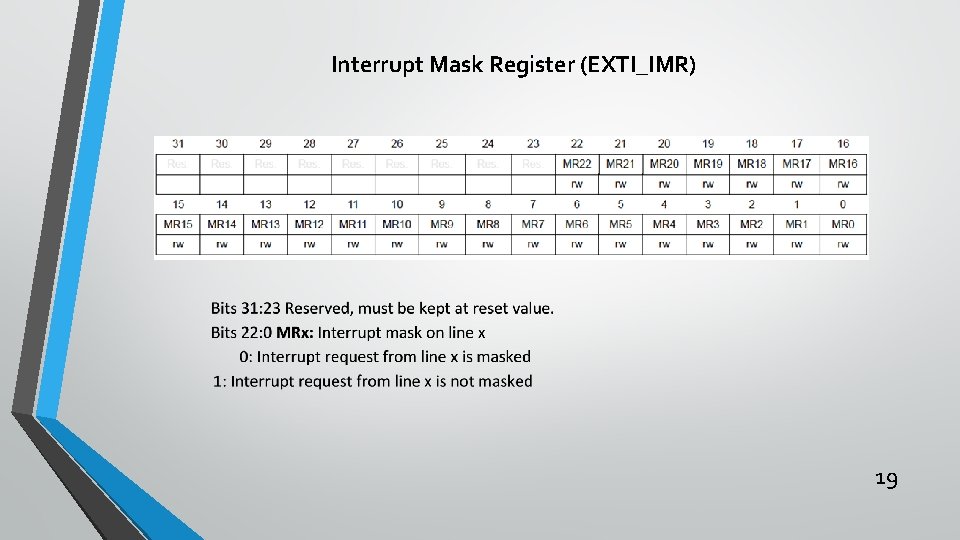

Interrupt Mask Register (EXTI_IMR) 19

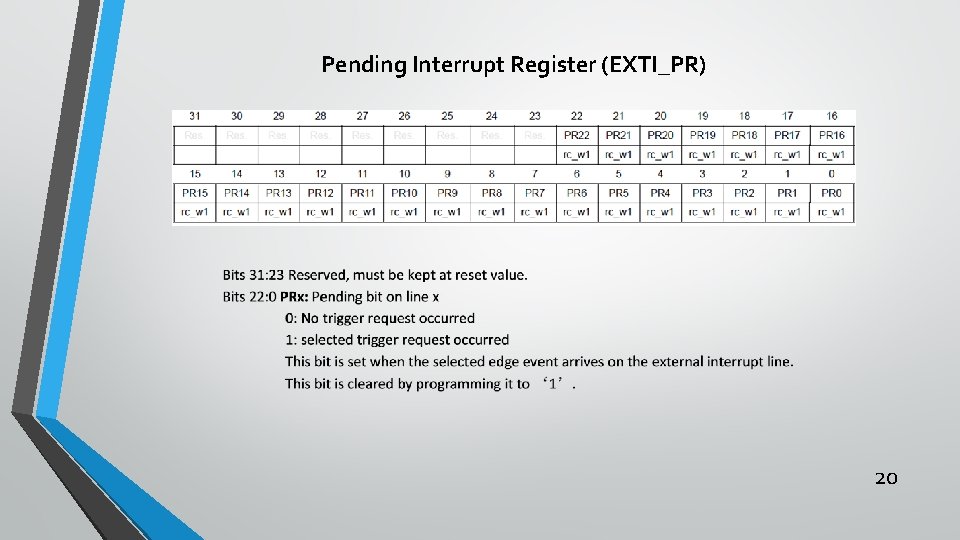

Pending Interrupt Register (EXTI_PR) 20

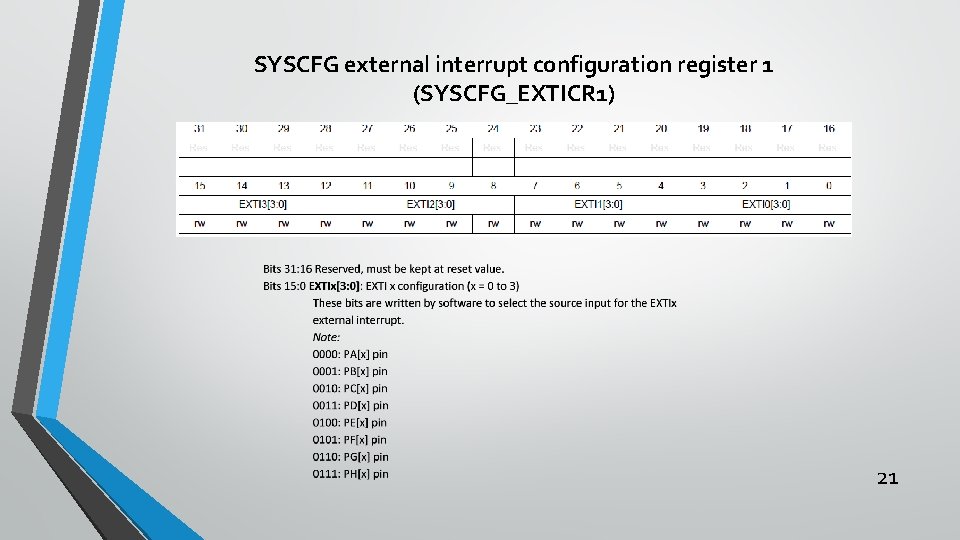

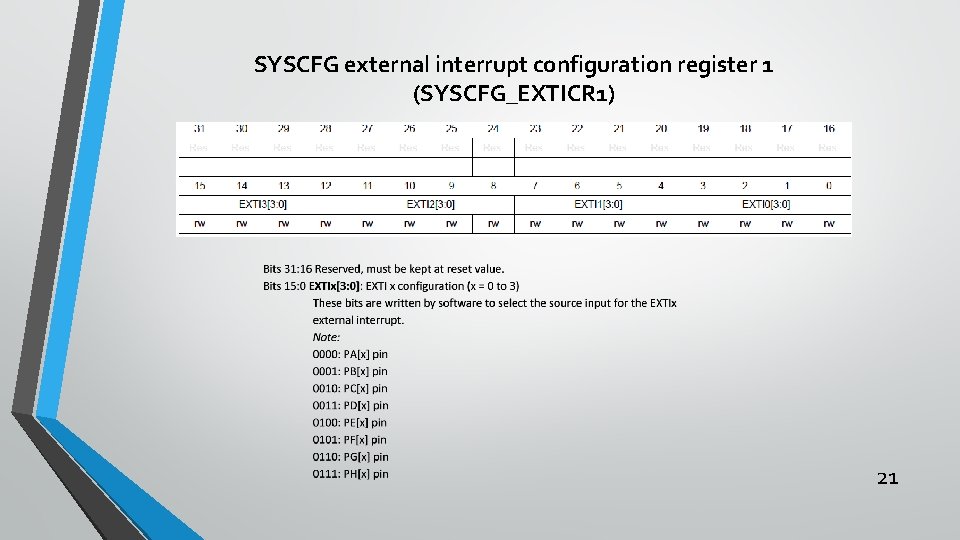

SYSCFG external interrupt configuration register 1 (SYSCFG_EXTICR 1) 21

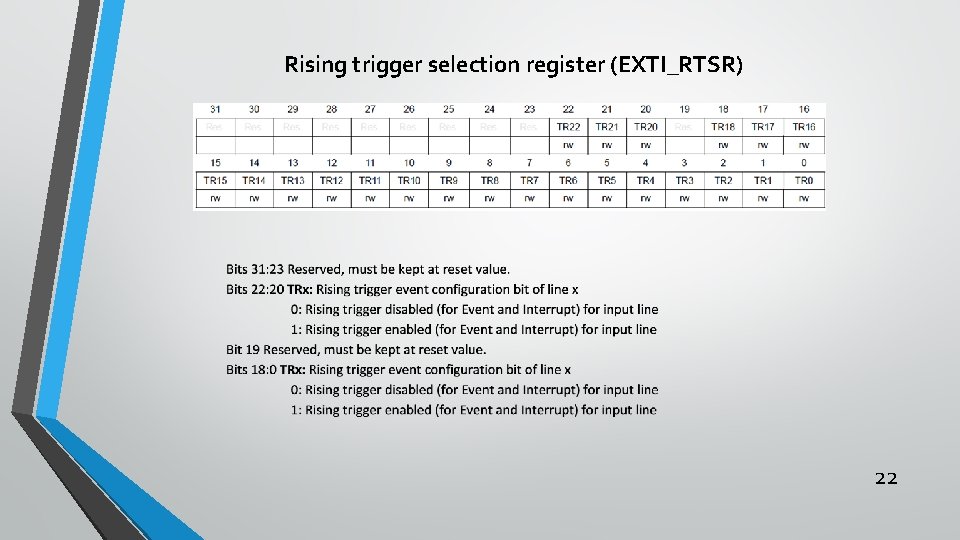

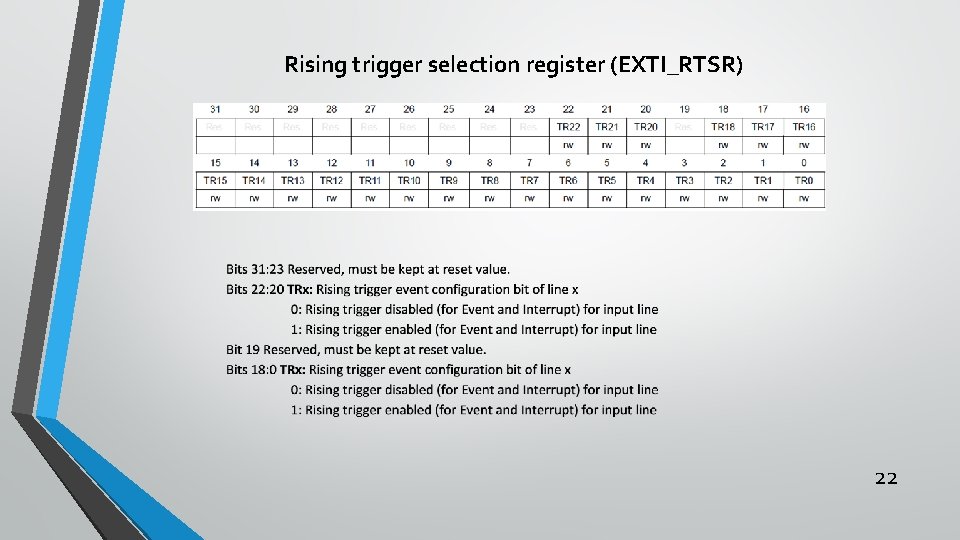

Rising trigger selection register (EXTI_RTSR) 22

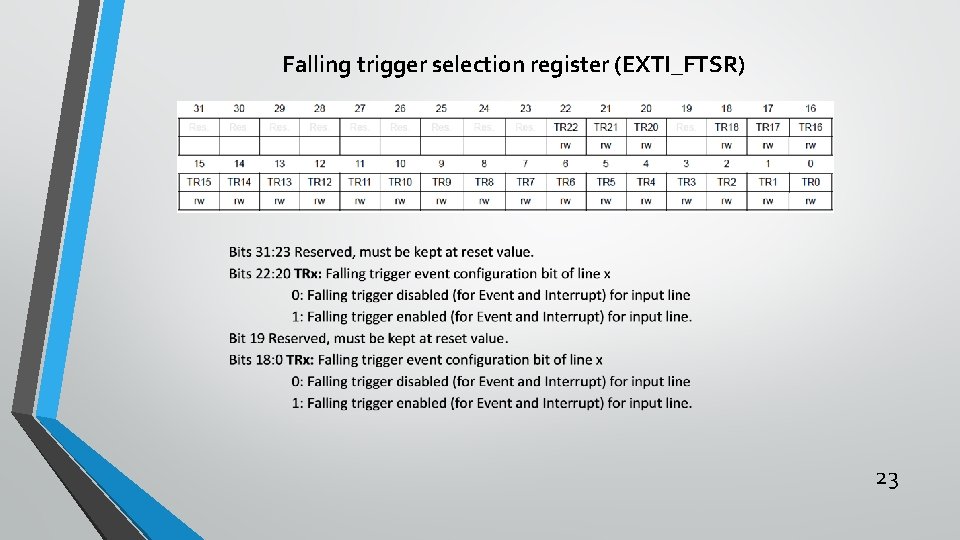

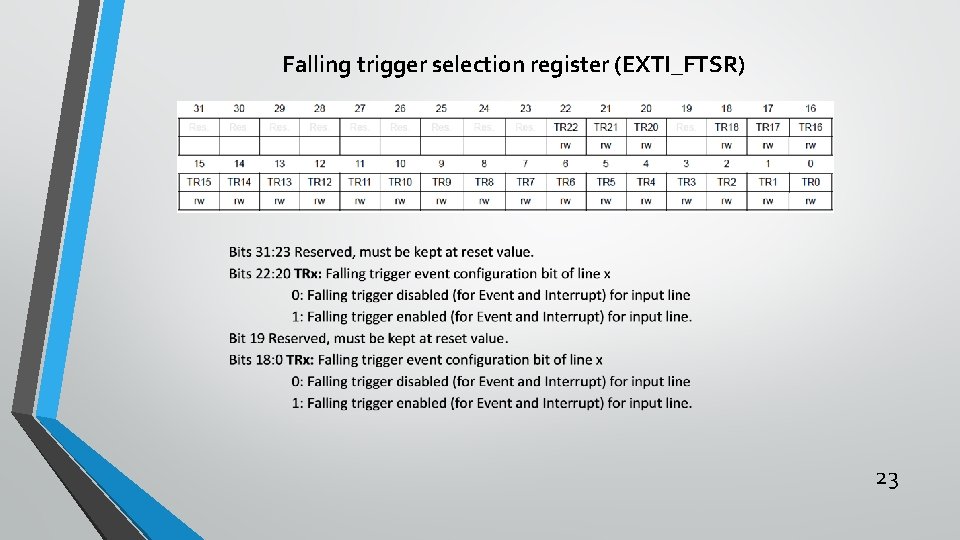

Falling trigger selection register (EXTI_FTSR) 23

![Set Enable Register ISER1 for IRQ 32 63 24 Set Enable Register (ISER[1]) for IRQ 32– 63 24](https://slidetodoc.com/presentation_image_h/23fdb53fa6aa2cd866ae3ff7cebcfb2c/image-24.jpg)

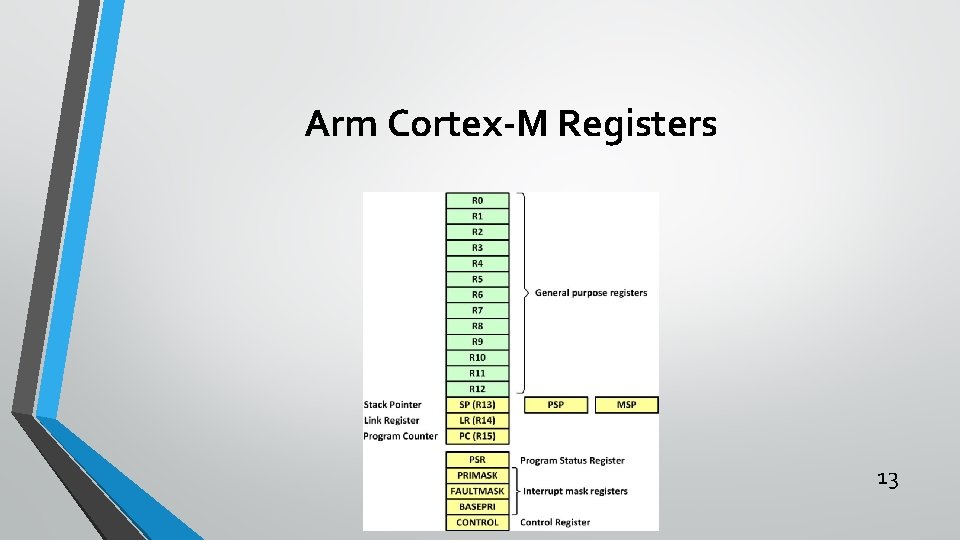

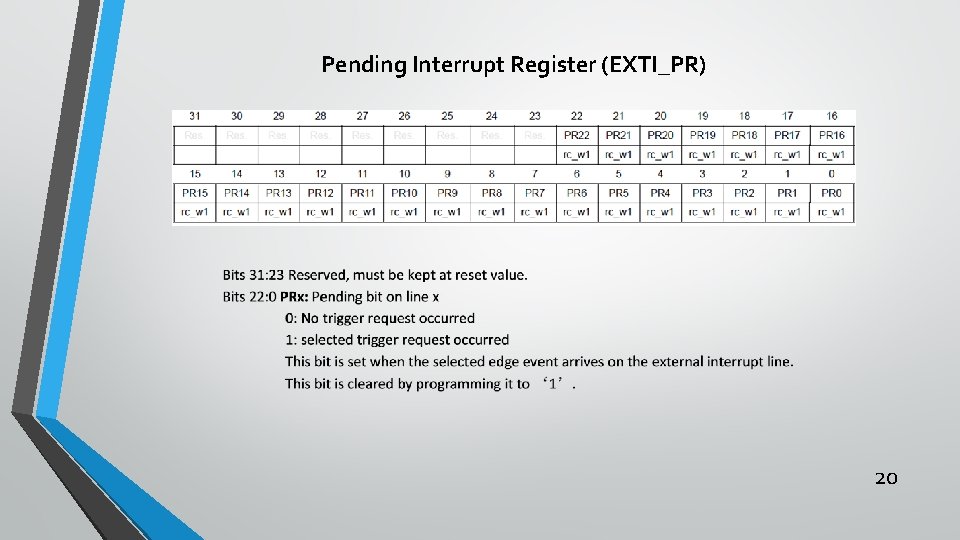

Set Enable Register (ISER[1]) for IRQ 32– 63 24

![Clear Enable Register ICER1 for IRQ 32 63 25 Clear Enable Register (ICER[1]) for IRQ 32– 63 25](https://slidetodoc.com/presentation_image_h/23fdb53fa6aa2cd866ae3ff7cebcfb2c/image-25.jpg)

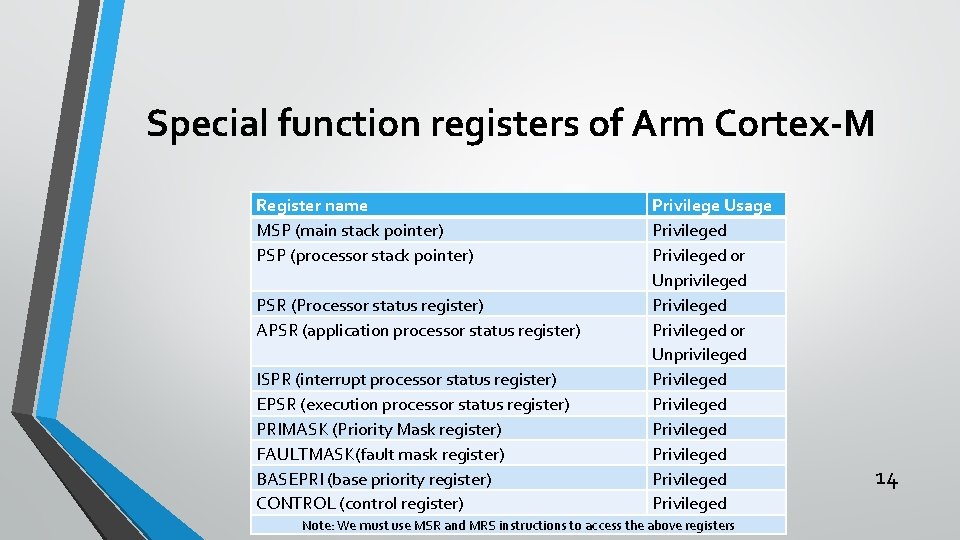

Clear Enable Register (ICER[1]) for IRQ 32– 63 25

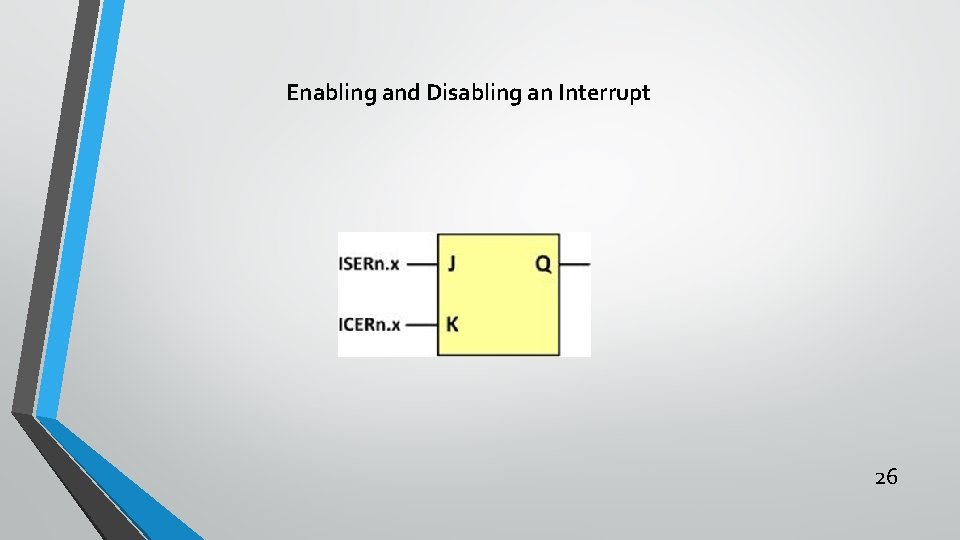

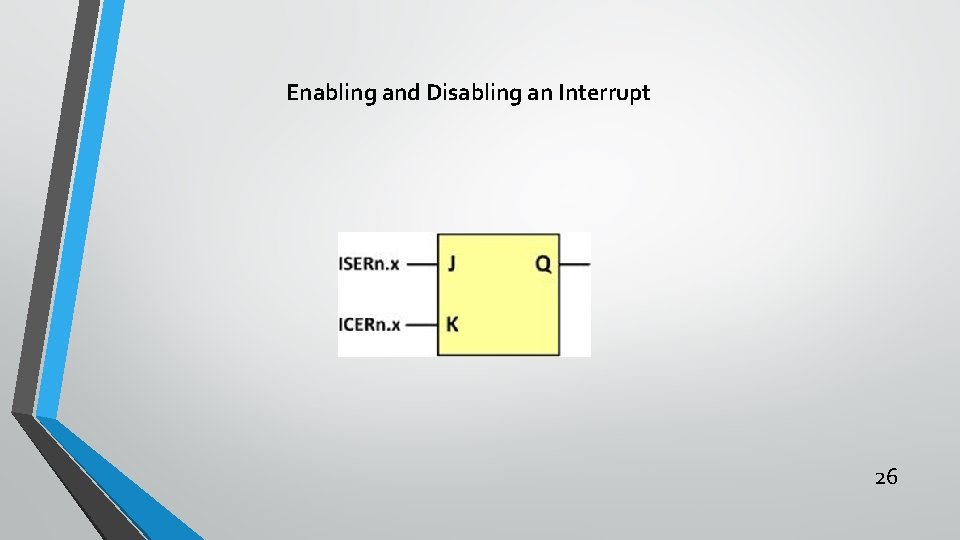

Enabling and Disabling an Interrupt 26

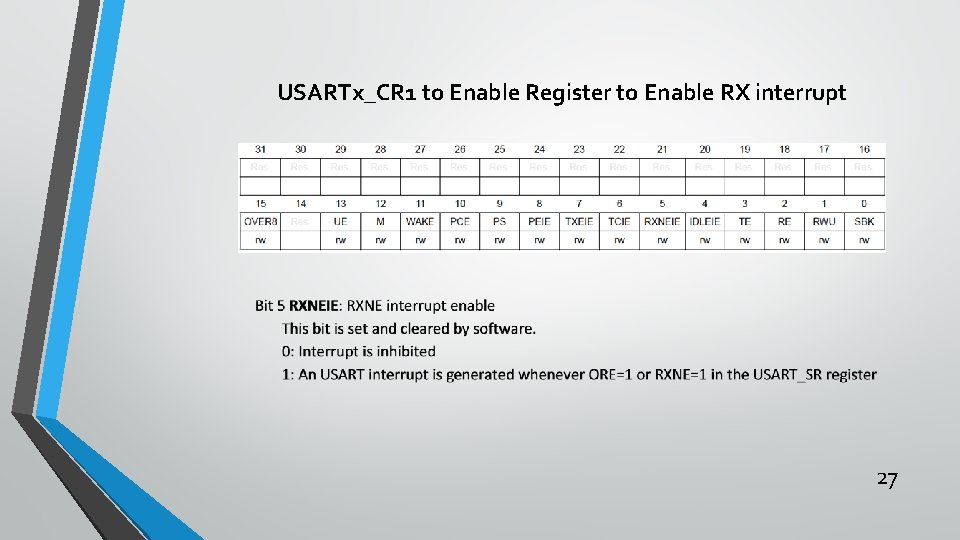

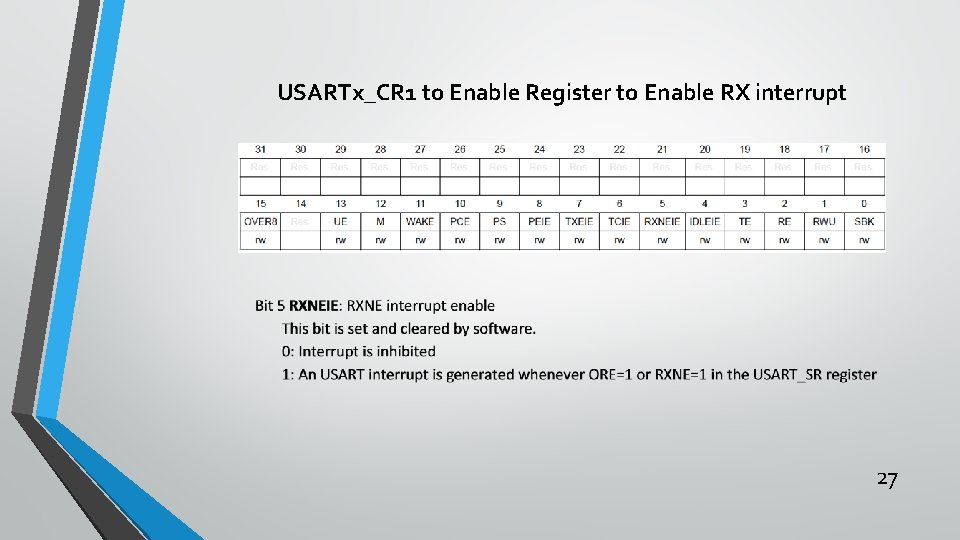

USARTx_CR 1 to Enable Register to Enable RX interrupt 27

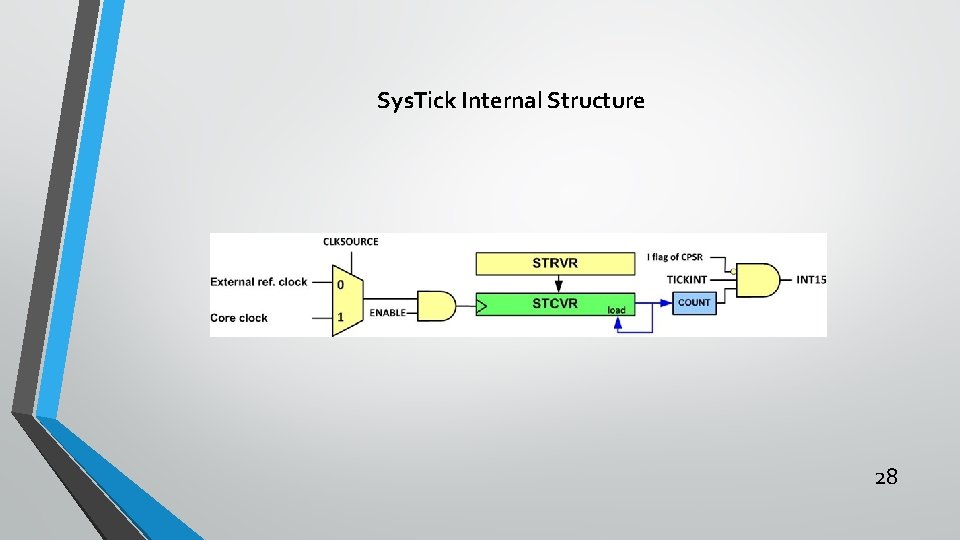

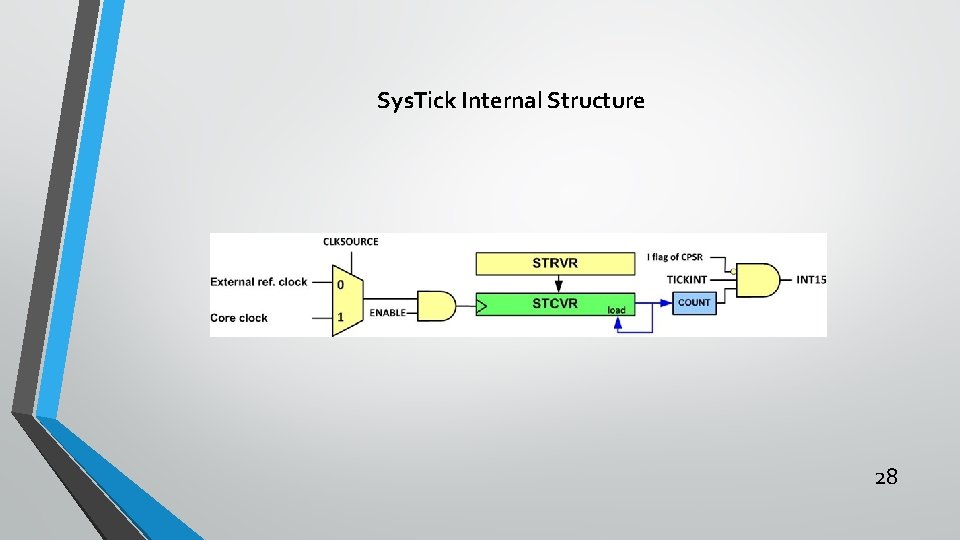

Sys. Tick Internal Structure 28

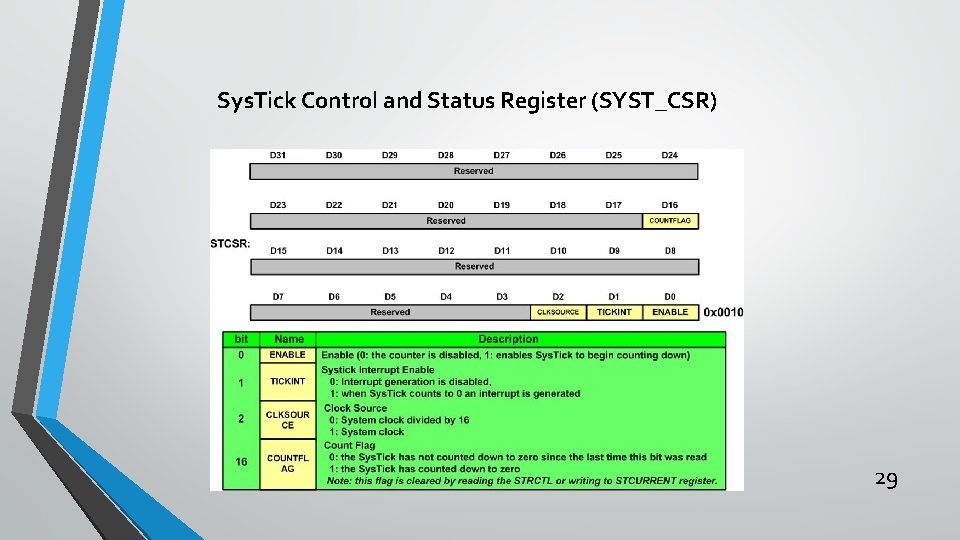

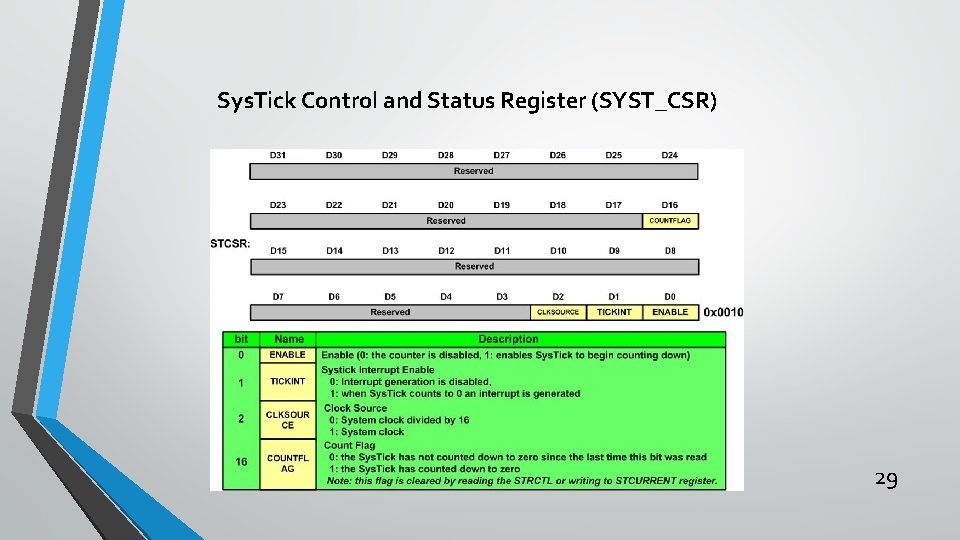

Sys. Tick Control and Status Register (SYST_CSR) 29

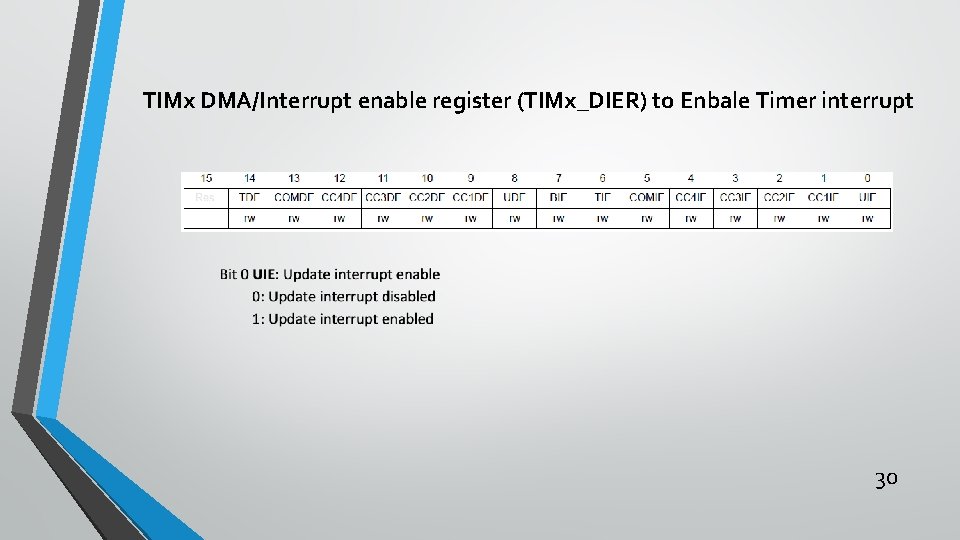

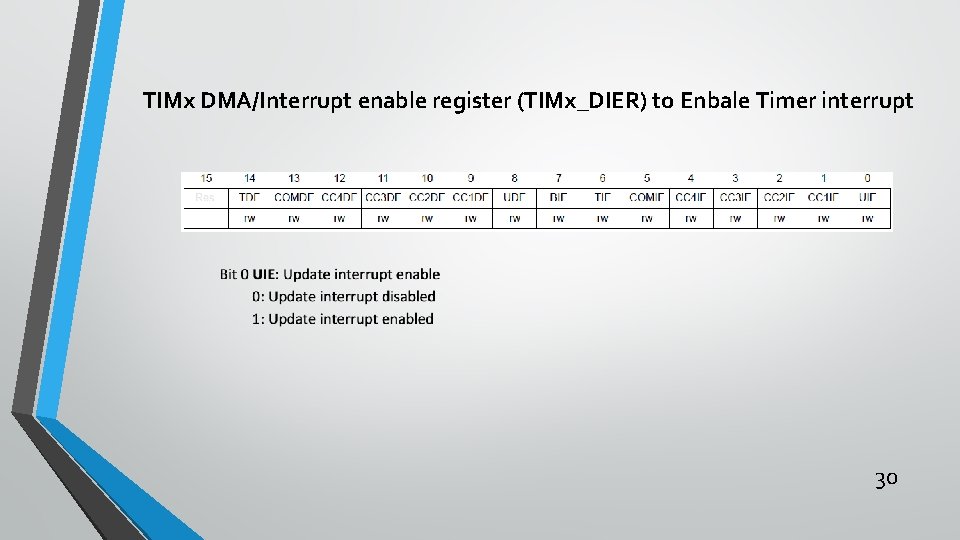

TIMx DMA/Interrupt enable register (TIMx_DIER) to Enbale Timer interrupt 30

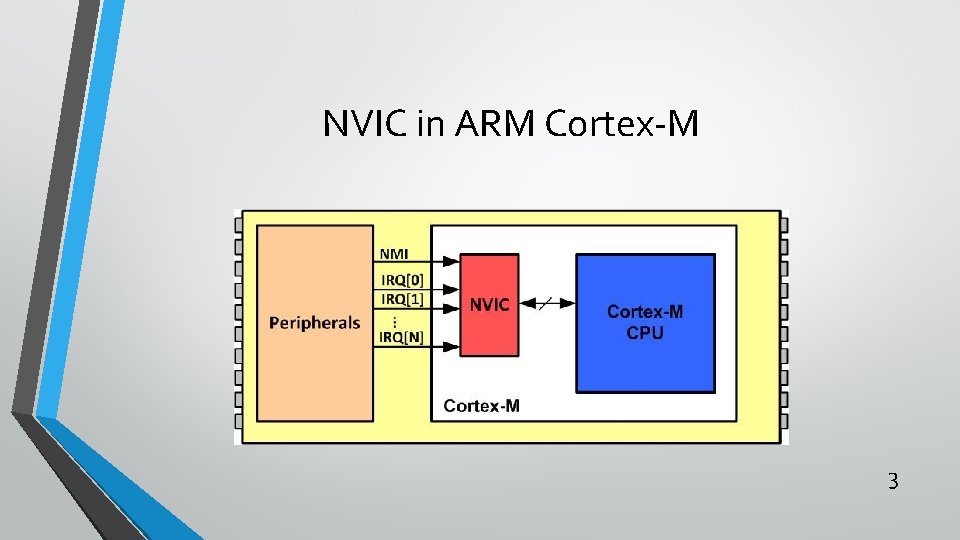

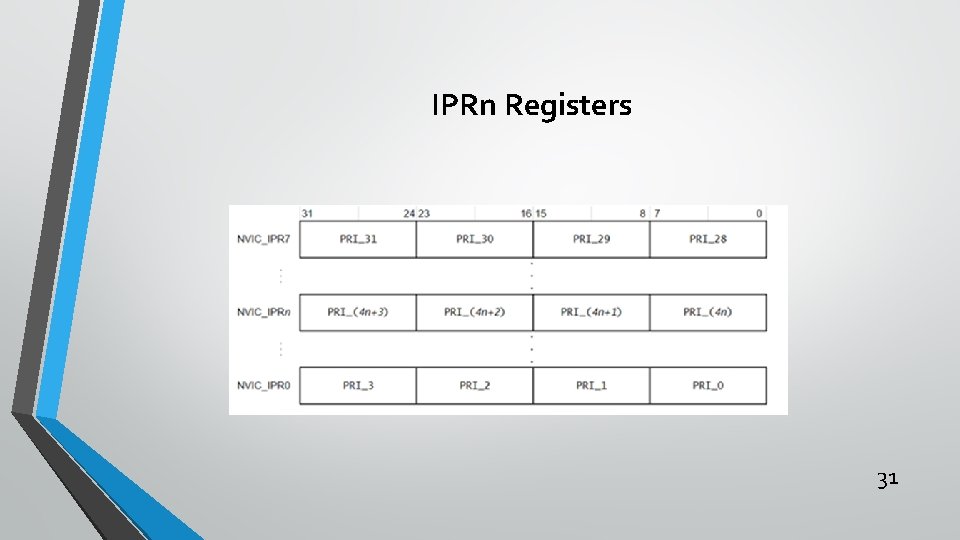

IPRn Registers 31