Analogni i digitalni signali Kod analognog signala informacija

- Slides: 44

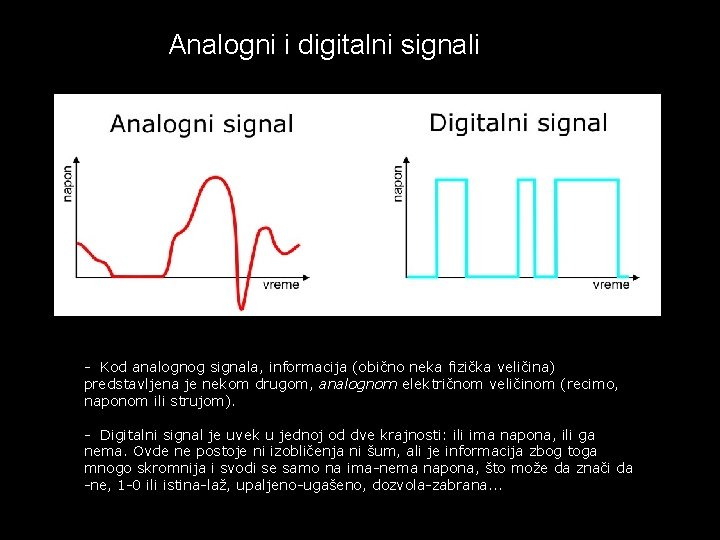

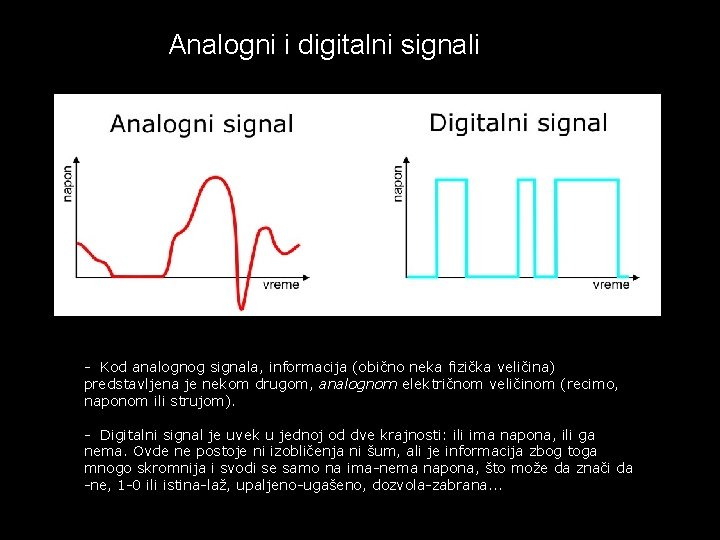

Analogni i digitalni signali - Kod analognog signala, informacija (obično neka fizička veličina) predstavljena je nekom drugom, analognom električnom veličinom (recimo, naponom ili strujom). - Digitalni signal je uvek u jednoj od dve krajnosti: ili ima napona, ili ga nema. Ovde ne postoje ni izobličenja ni šum, ali je informacija zbog toga mnogo skromnija i svodi se samo na ima-nema napona, što može da znači da -ne, 1 -0 ili istina-laž, upaljeno-ugašeno, dozvola-zabrana. . .

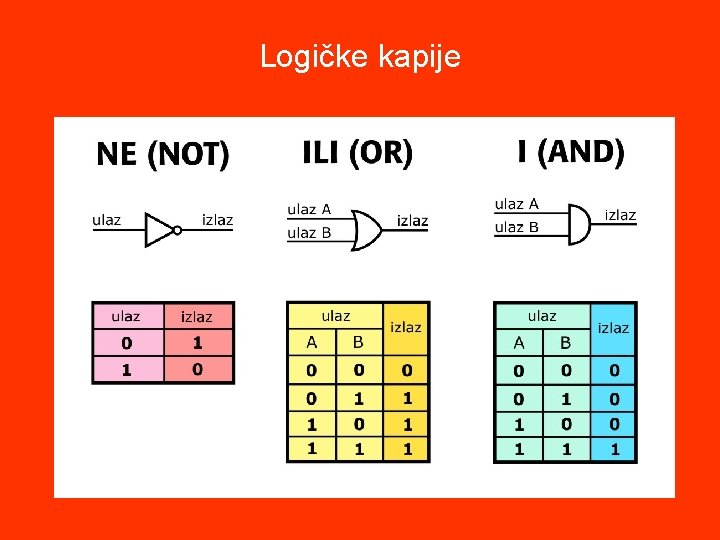

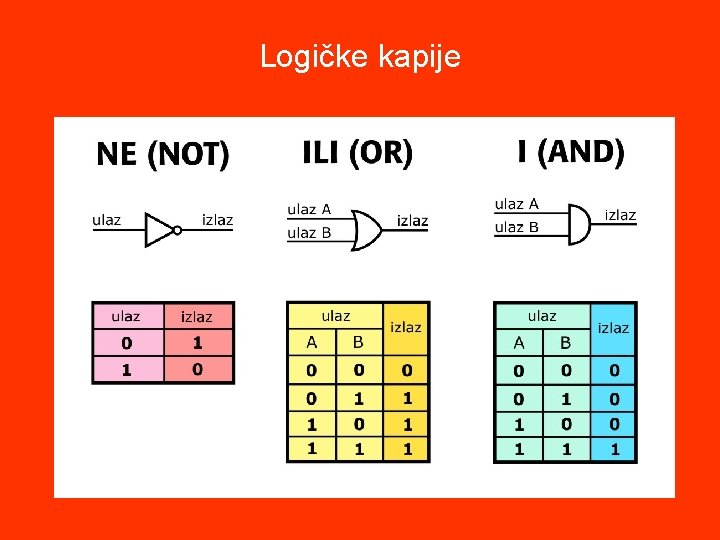

Logičke kapije

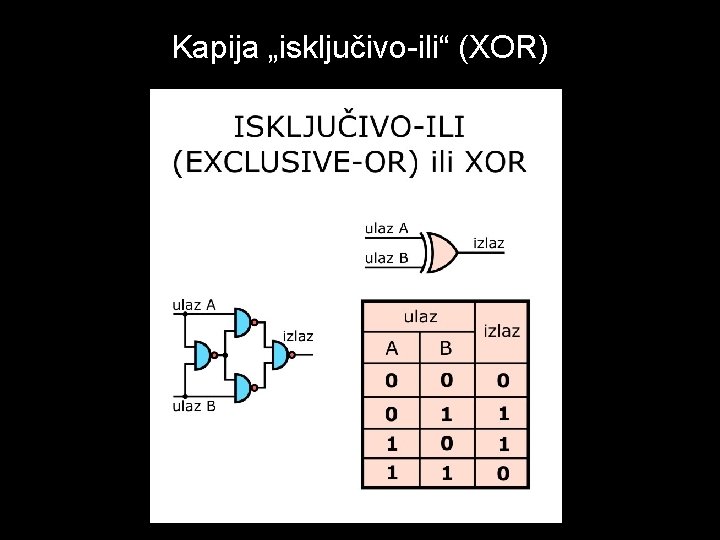

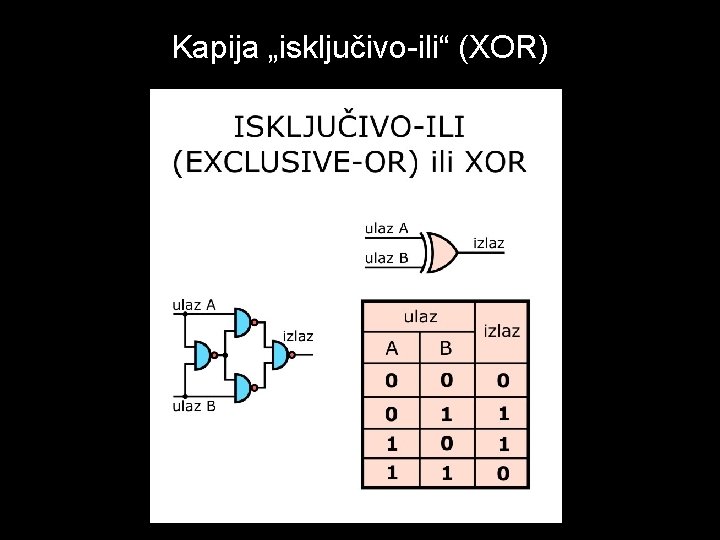

Kapija „isključivo-ili“ (XOR)

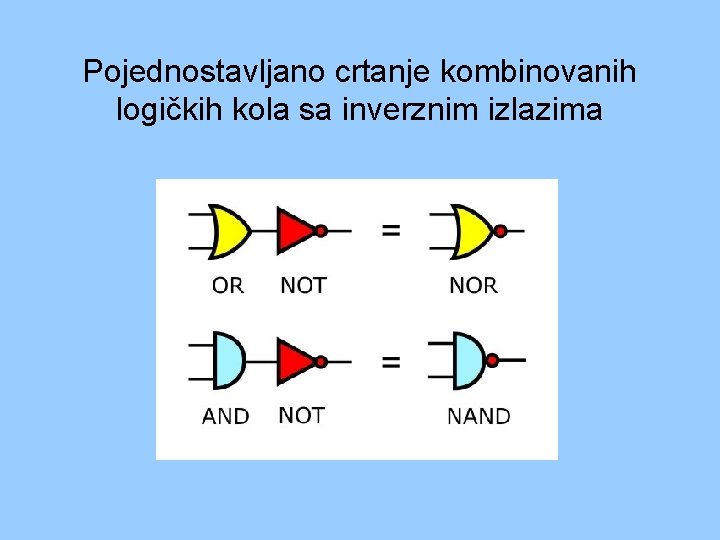

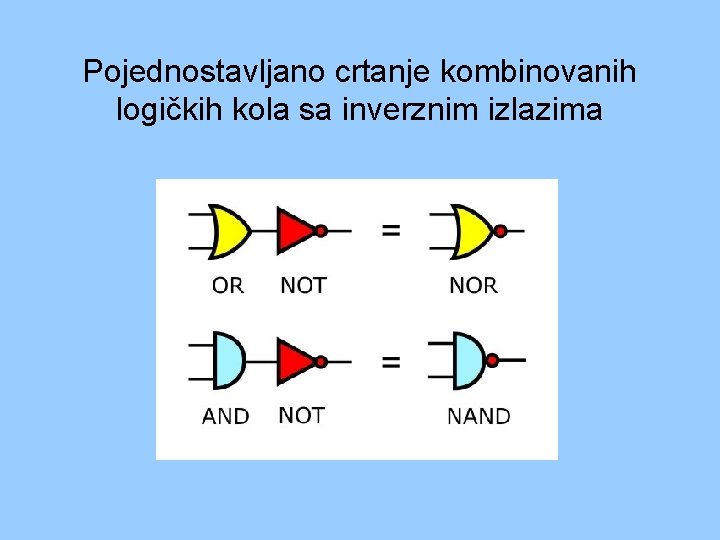

Pojednostavljano crtanje kombinovanih logičkih kola sa inverznim izlazima

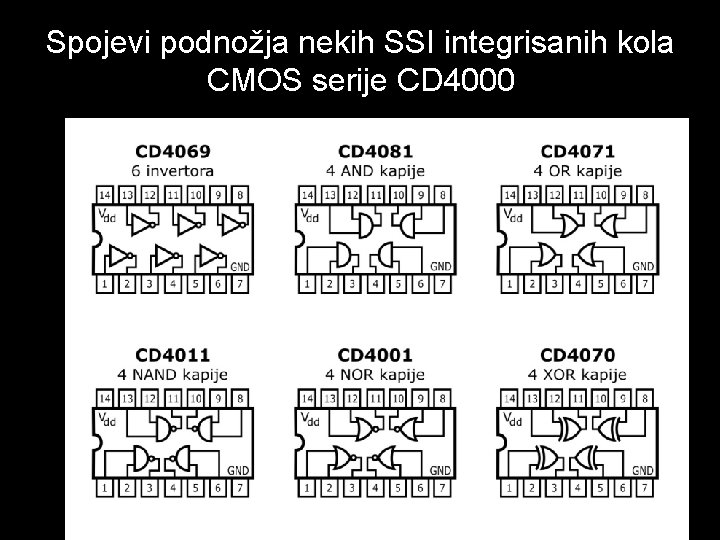

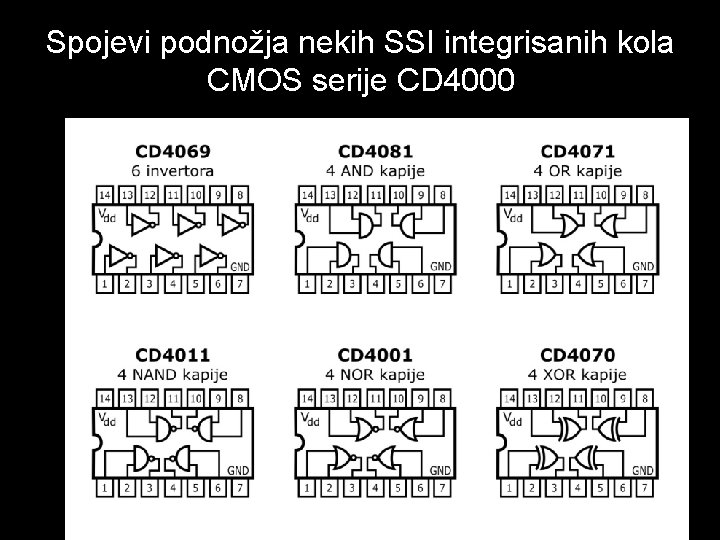

Spojevi podnožja nekih SSI integrisanih kola CMOS serije CD 4000

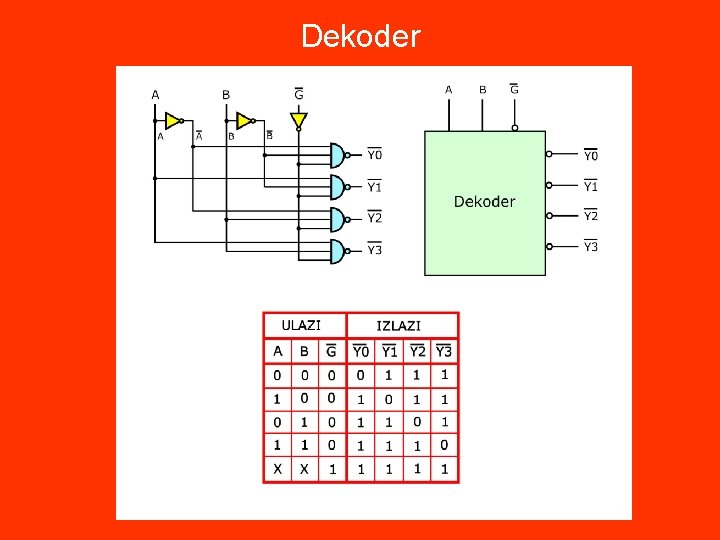

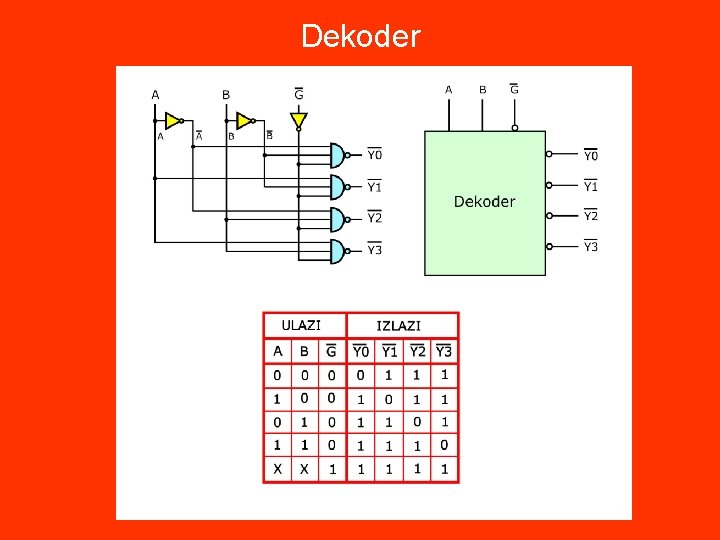

Dekoder

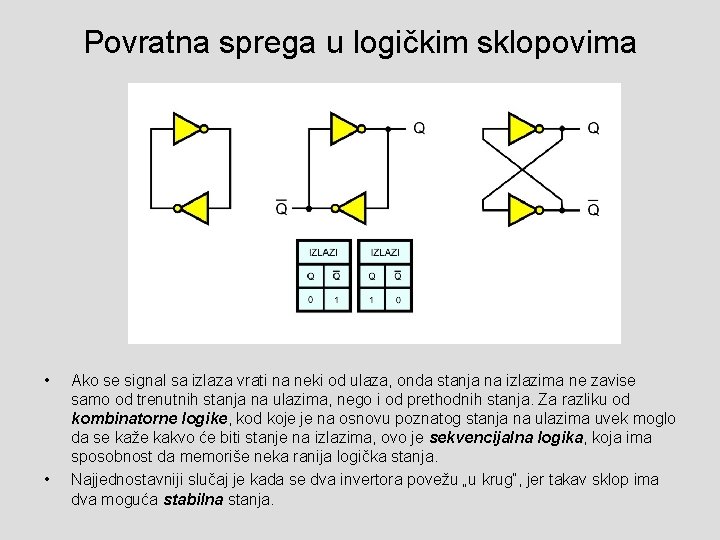

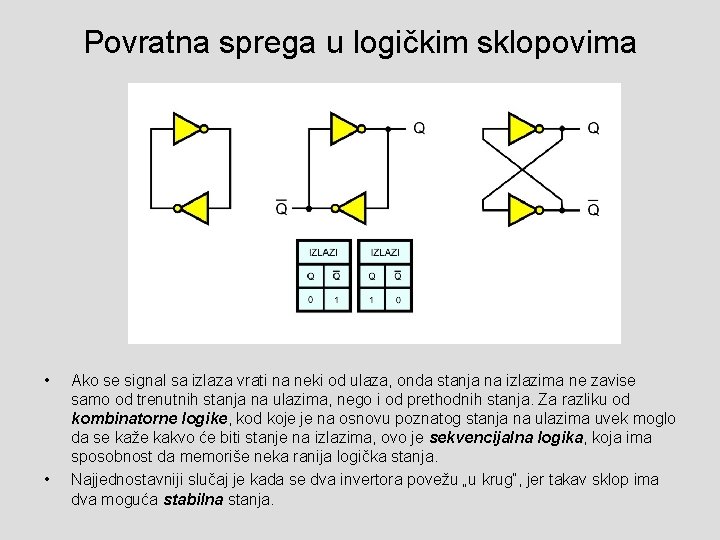

Povratna sprega u logičkim sklopovima • • Ako se signal sa izlaza vrati na neki od ulaza, onda stanja na izlazima ne zavise samo od trenutnih stanja na ulazima, nego i od prethodnih stanja. Za razliku od kombinatorne logike, kod koje je na osnovu poznatog stanja na ulazima uvek moglo da se kaže kakvo će biti stanje na izlazima, ovo je sekvencijalna logika, koja ima sposobnost da memoriše neka ranija logička stanja. Najjednostavniji slučaj je kada se dva invertora povežu „u krug“, jer takav sklop ima dva moguća stabilna stanja.

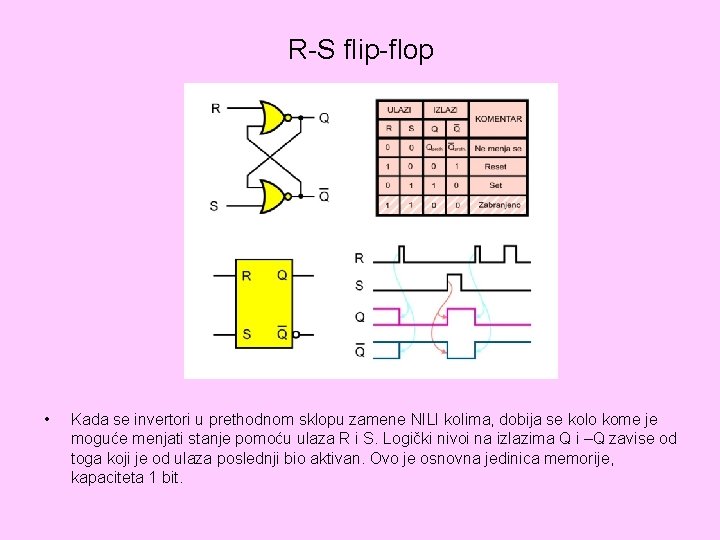

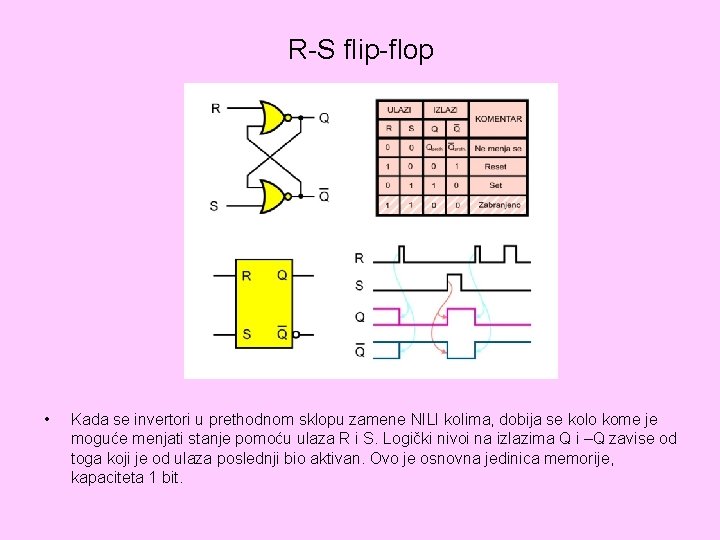

R-S flip-flop • Kada se invertori u prethodnom sklopu zamene NILI kolima, dobija se kolo kome je moguće menjati stanje pomoću ulaza R i S. Logički nivoi na izlazima Q i –Q zavise od toga koji je od ulaza poslednji bio aktivan. Ovo je osnovna jedinica memorije, kapaciteta 1 bit.

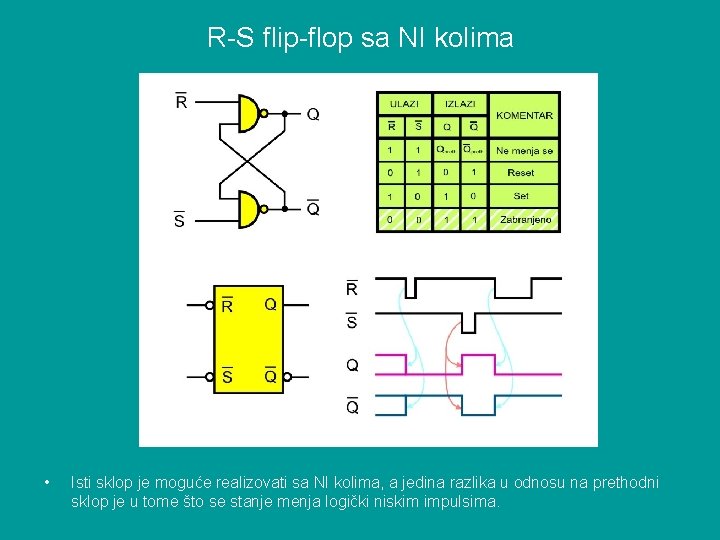

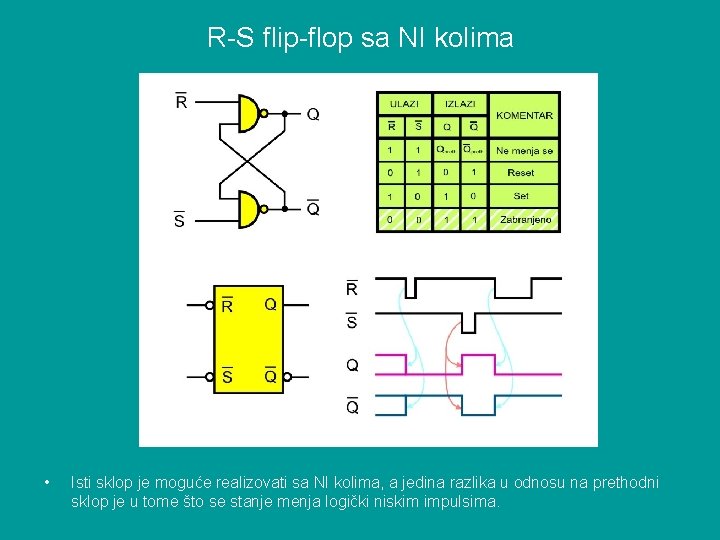

R-S flip-flop sa NI kolima • Isti sklop je moguće realizovati sa NI kolima, a jedina razlika u odnosu na prethodni sklop je u tome što se stanje menja logički niskim impulsima.

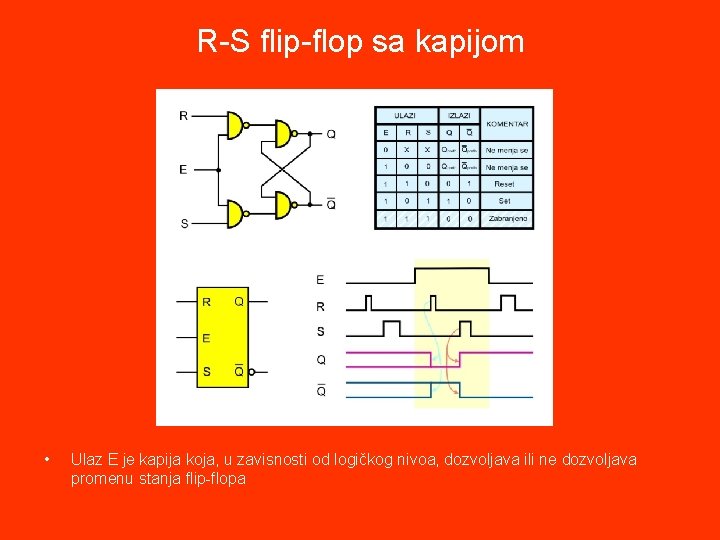

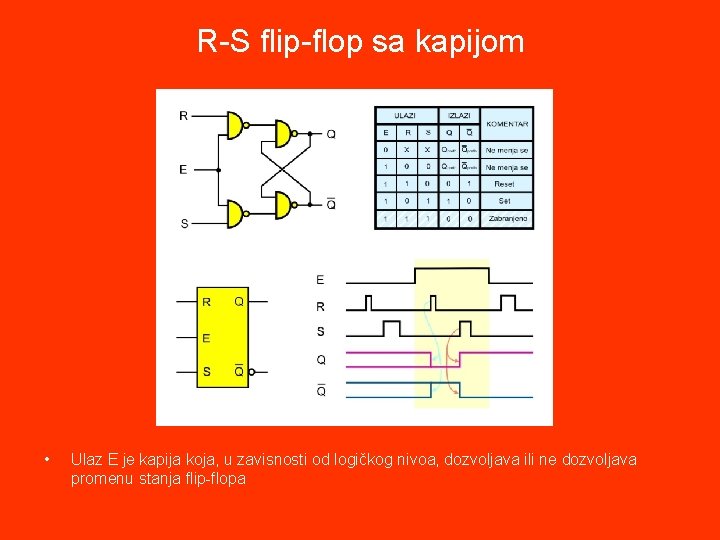

R-S flip-flop sa kapijom • Ulaz E je kapija koja, u zavisnosti od logičkog nivoa, dozvoljava ili ne dozvoljava promenu stanja flip-flopa

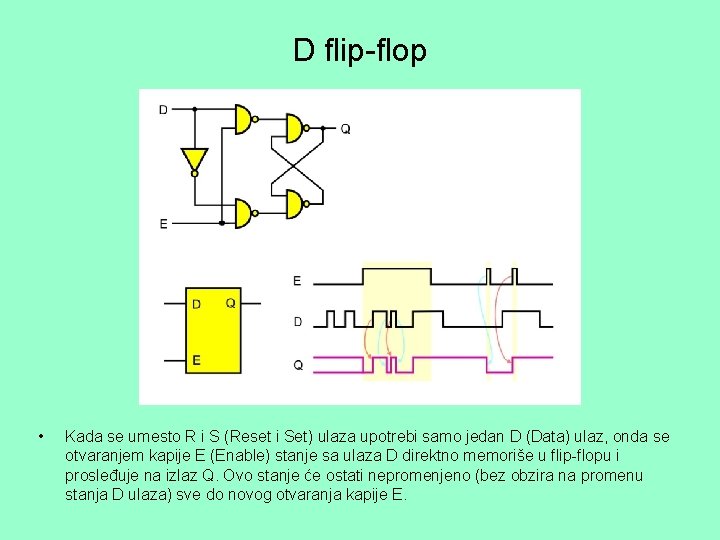

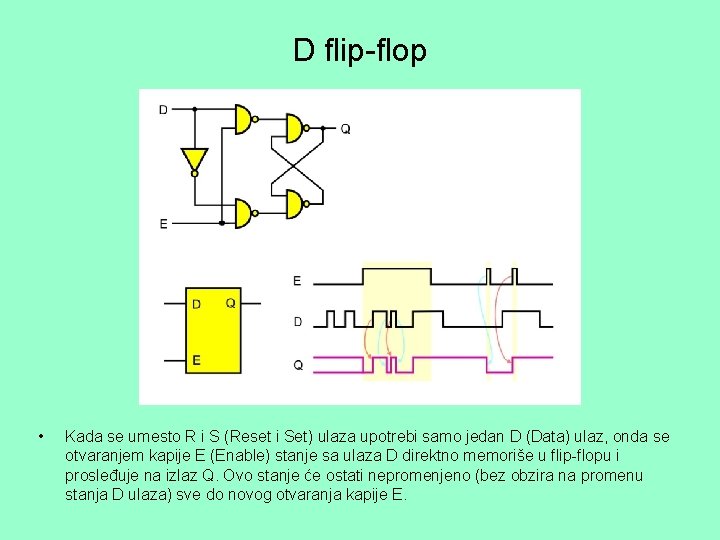

D flip-flop • Kada se umesto R i S (Reset i Set) ulaza upotrebi samo jedan D (Data) ulaz, onda se otvaranjem kapije E (Enable) stanje sa ulaza D direktno memoriše u flip-flopu i prosleđuje na izlaz Q. Ovo stanje će ostati nepromenjeno (bez obzira na promenu stanja D ulaza) sve do novog otvaranja kapije E.

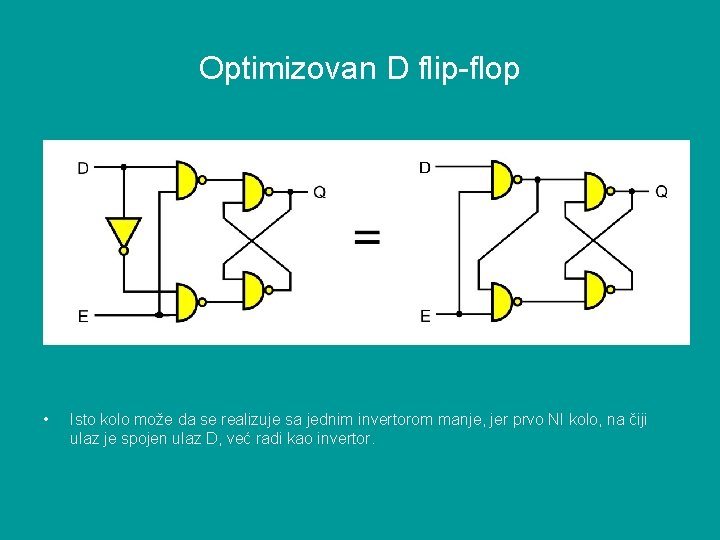

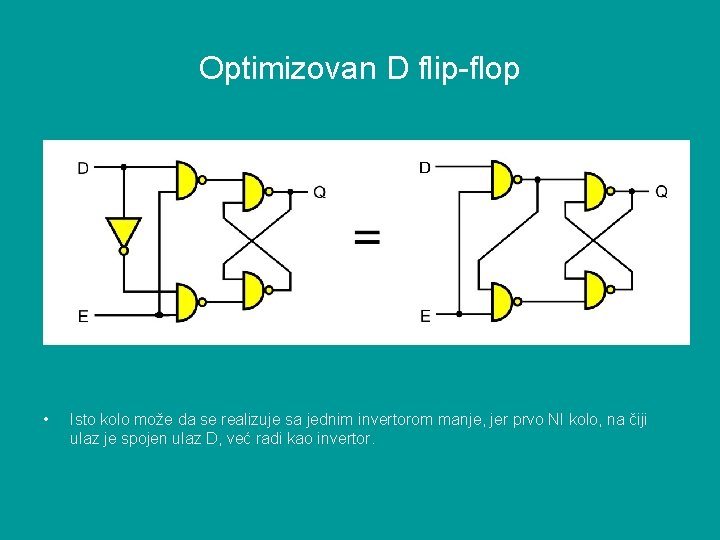

Optimizovan D flip-flop • Isto kolo može da se realizuje sa jednim invertorom manje, jer prvo NI kolo, na čiji ulaz je spojen ulaz D, već radi kao invertor.

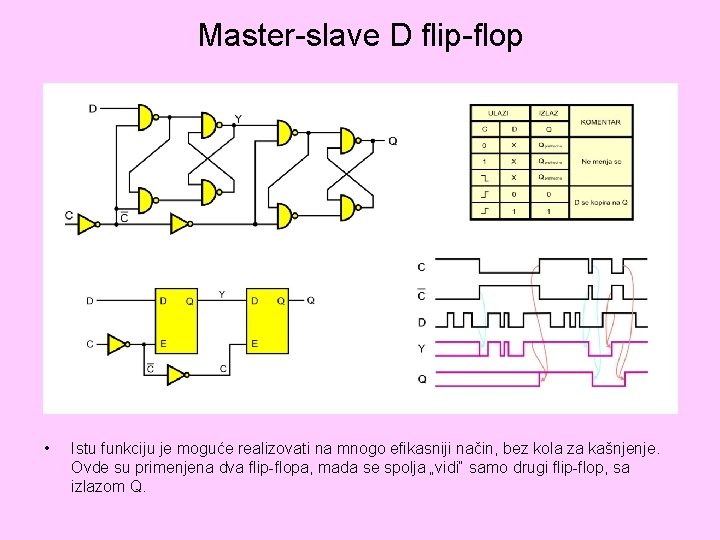

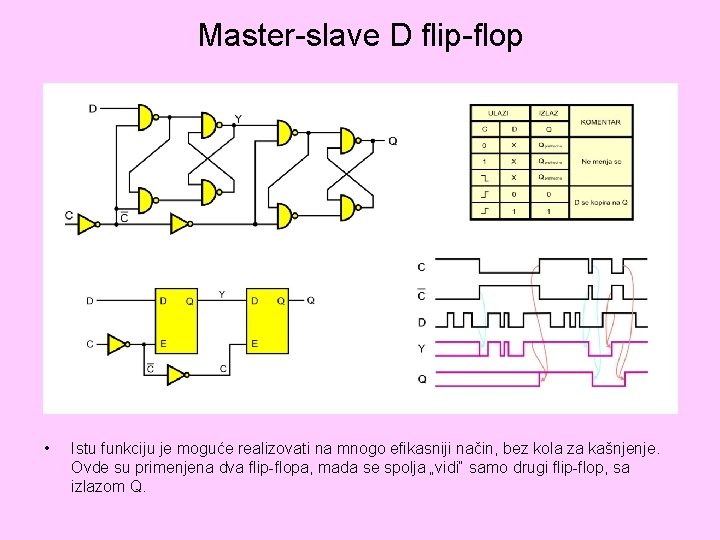

Master-slave D flip-flop • Istu funkciju je moguće realizovati na mnogo efikasniji način, bez kola za kašnjenje. Ovde su primenjena dva flip-flopa, mada se spolja „vidi“ samo drugi flip-flop, sa izlazom Q.

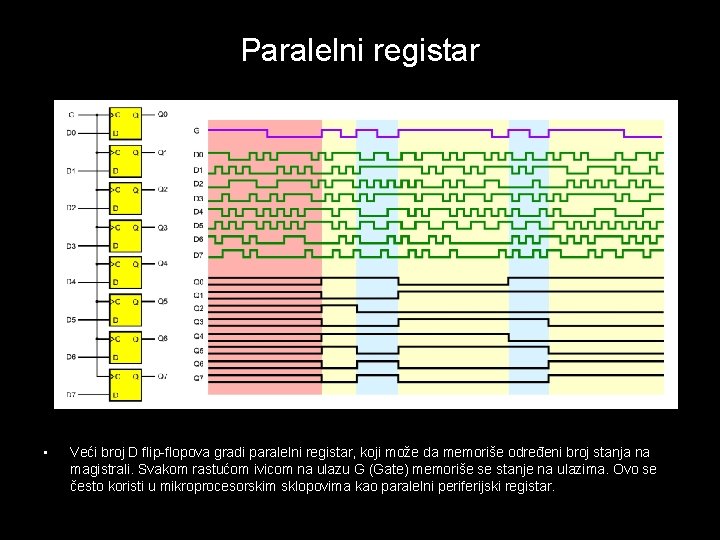

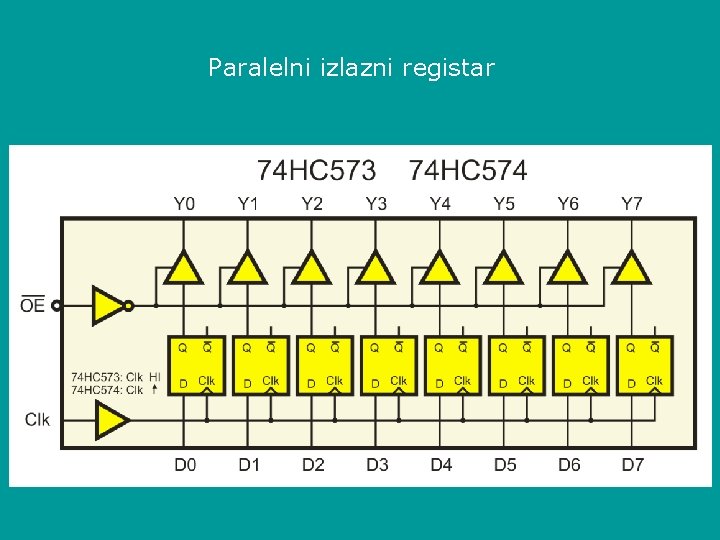

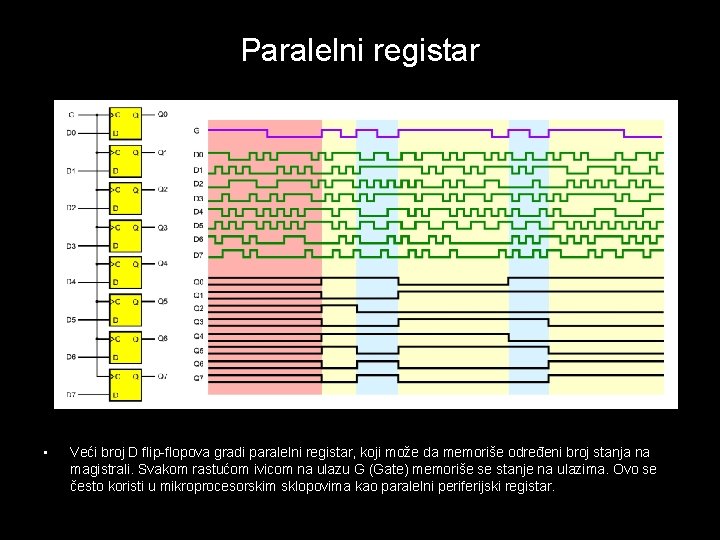

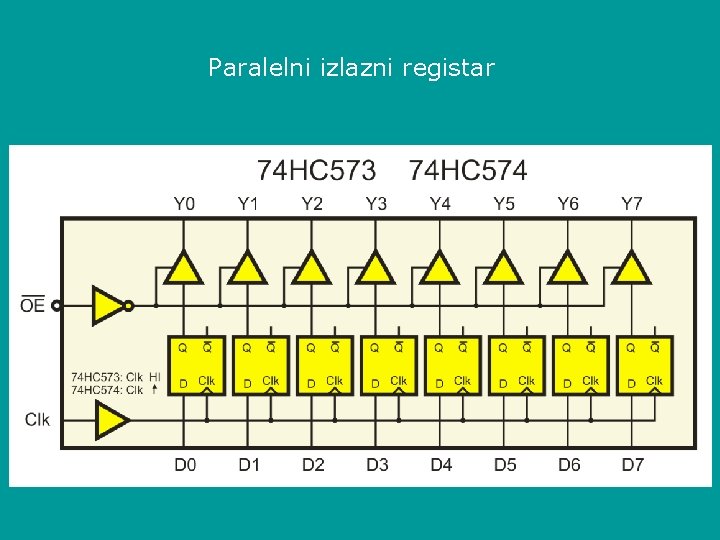

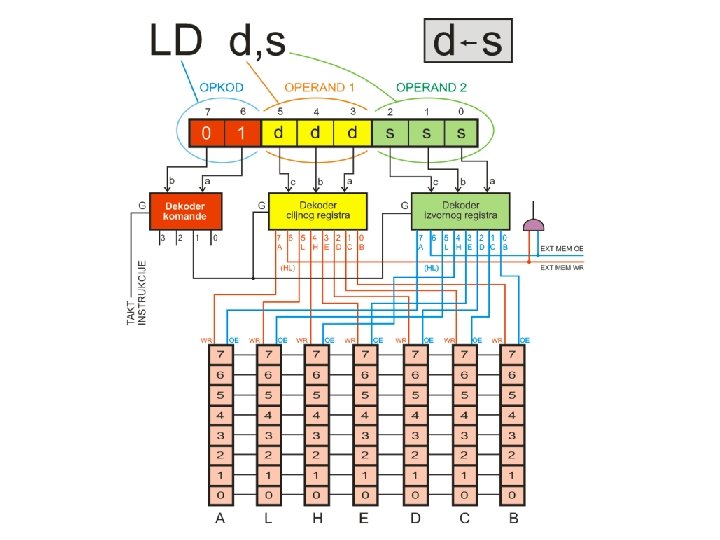

Paralelni registar • Veći broj D flip-flopova gradi paralelni registar, koji može da memoriše određeni broj stanja na magistrali. Svakom rastućom ivicom na ulazu G (Gate) memoriše se stanje na ulazima. Ovo se često koristi u mikroprocesorskim sklopovima kao paralelni periferijski registar.

Paralelni izlazni registar

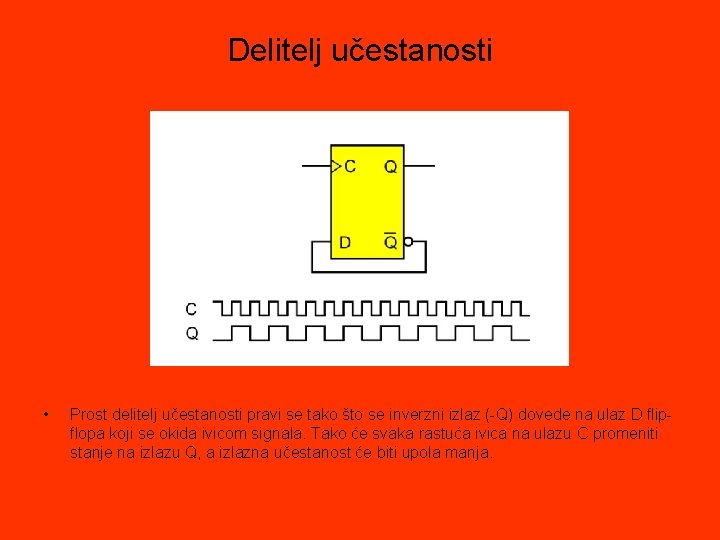

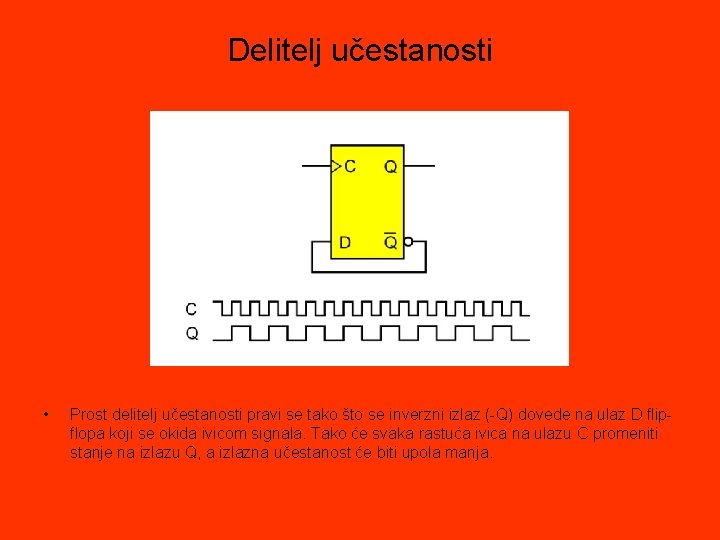

Delitelj učestanosti • Prost delitelj učestanosti pravi se tako što se inverzni izlaz (-Q) dovede na ulaz D flipflopa koji se okida ivicom signala. Tako će svaka rastuća ivica na ulazu C promeniti stanje na izlazu Q, a izlazna učestanost će biti upola manja.

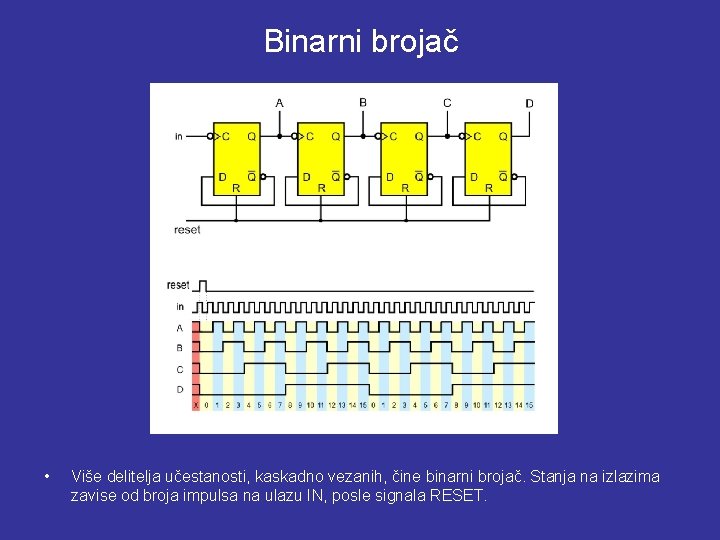

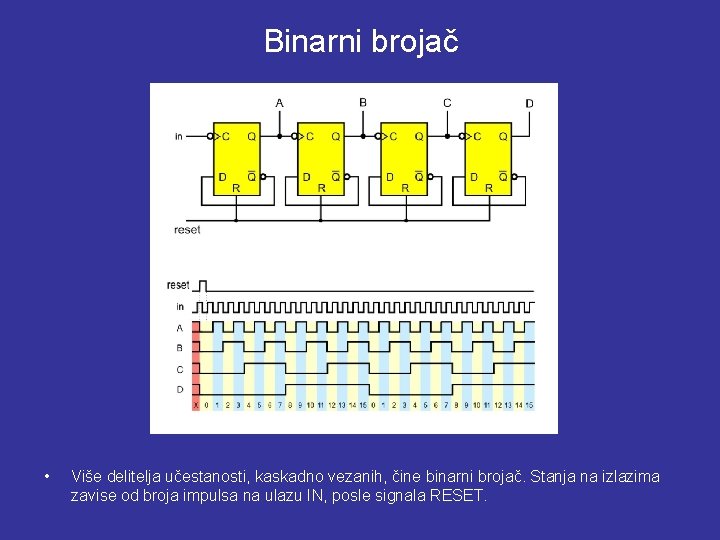

Binarni brojač • Više delitelja učestanosti, kaskadno vezanih, čine binarni brojač. Stanja na izlazima zavise od broja impulsa na ulazu IN, posle signala RESET.

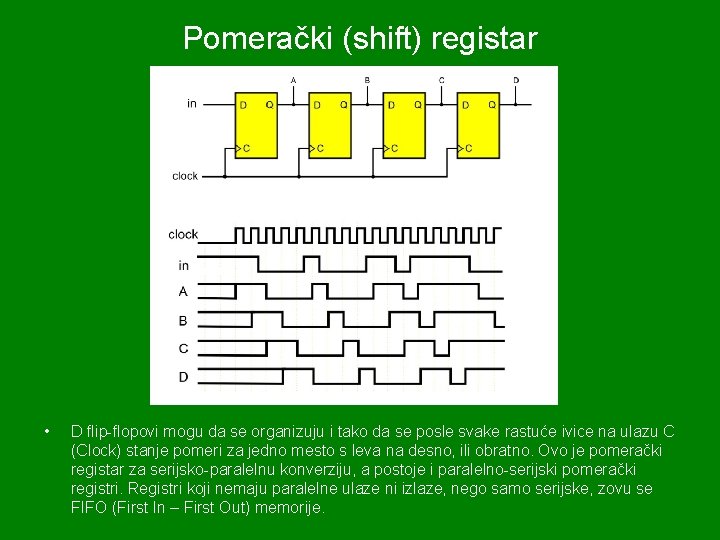

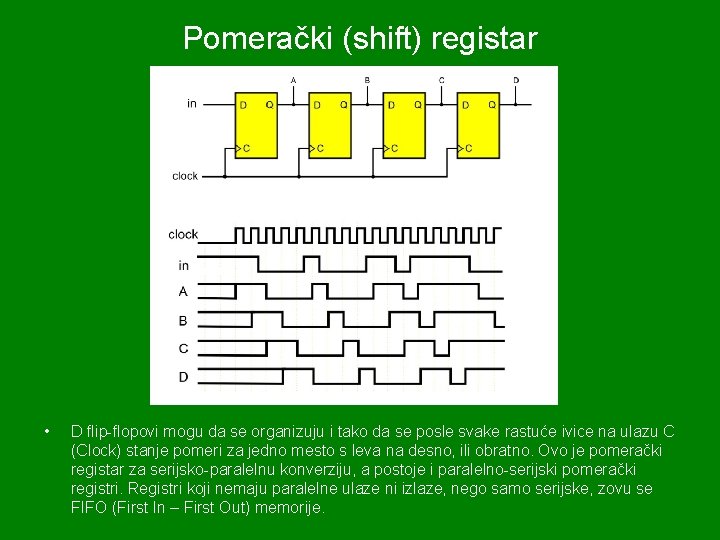

Pomerački (shift) registar • D flip-flopovi mogu da se organizuju i tako da se posle svake rastuće ivice na ulazu C (Clock) stanje pomeri za jedno mesto s leva na desno, ili obratno. Ovo je pomerački registar za serijsko-paralelnu konverziju, a postoje i paralelno-serijski pomerački registri. Registri koji nemaju paralelne ulaze ni izlaze, nego samo serijske, zovu se FIFO (First In – First Out) memorije.

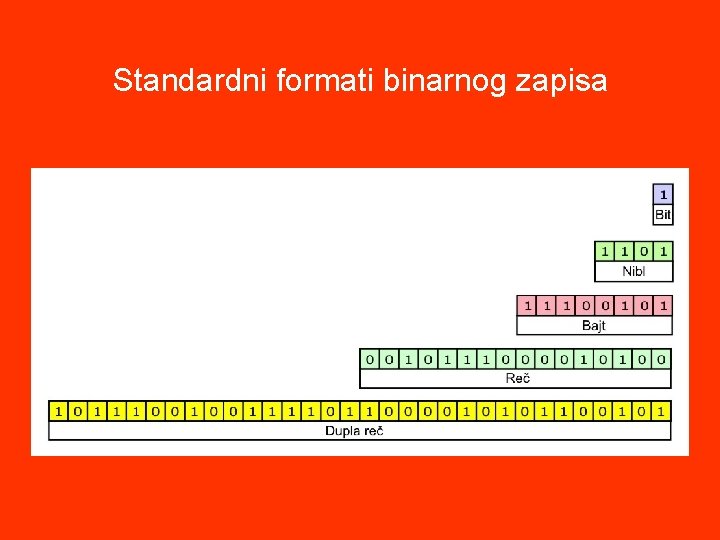

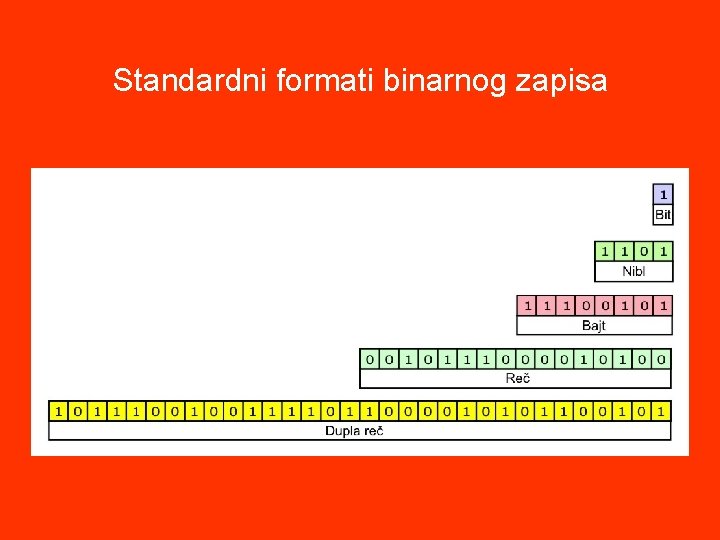

Standardni formati binarnog zapisa

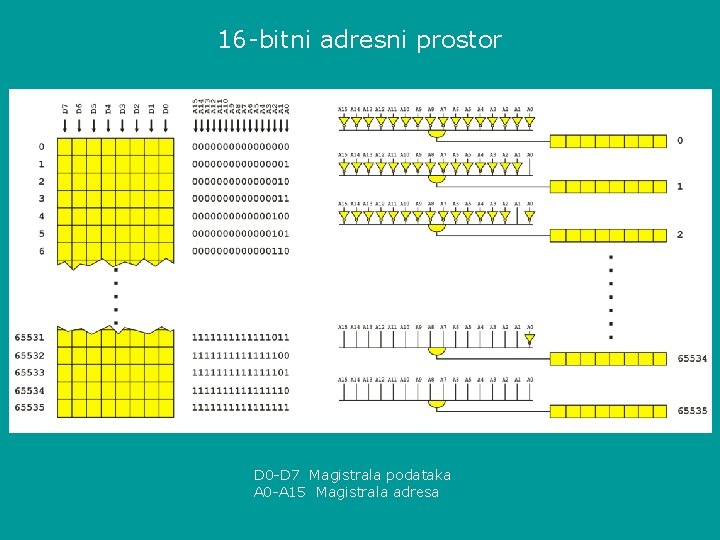

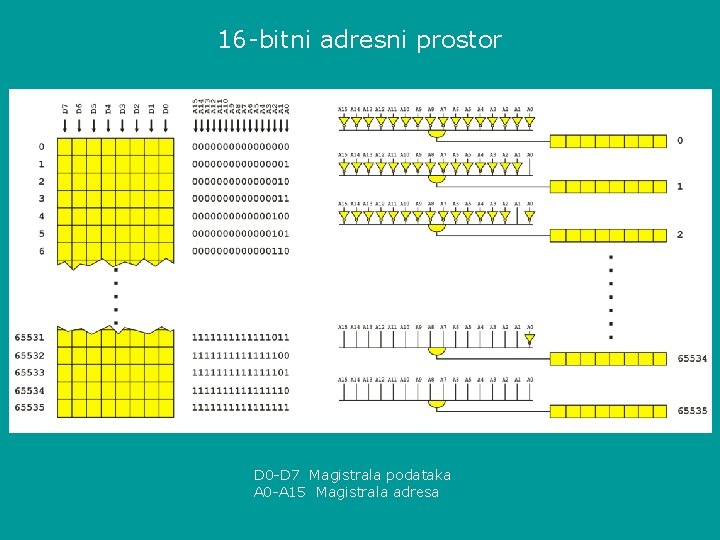

16 -bitni adresni prostor D 0 -D 7 Magistrala podataka A 0 -A 15 Magistrala adresa

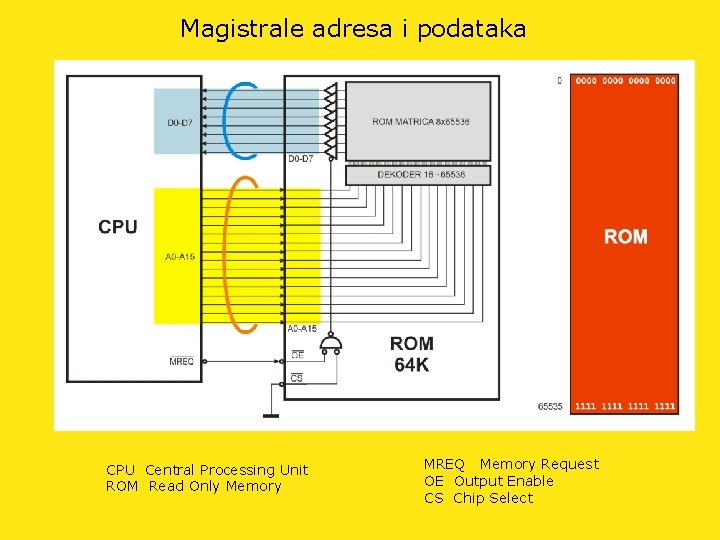

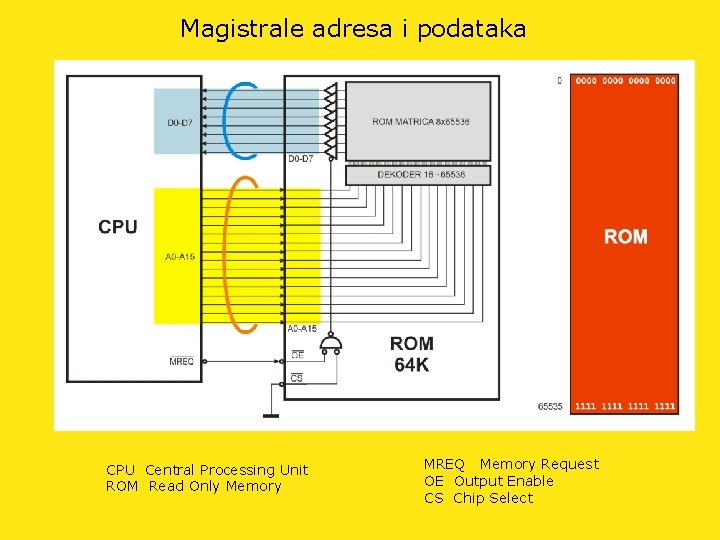

Magistrale adresa i podataka CPU Central Processing Unit ROM Read Only Memory MREQ Memory Request OE Output Enable CS Chip Select

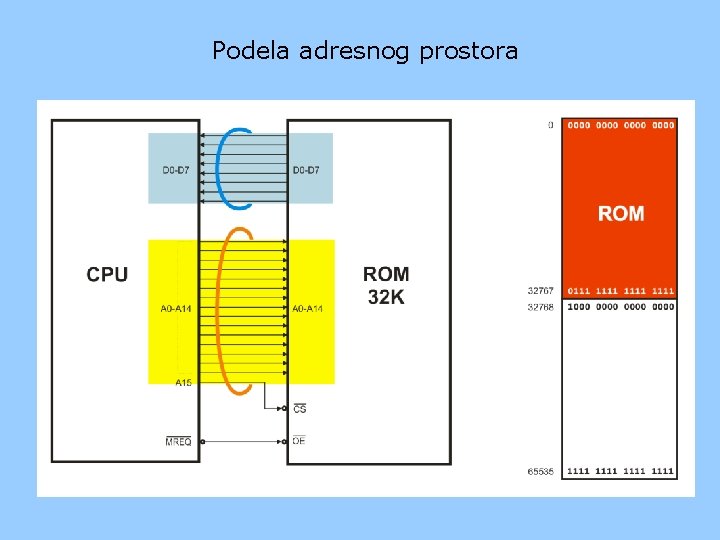

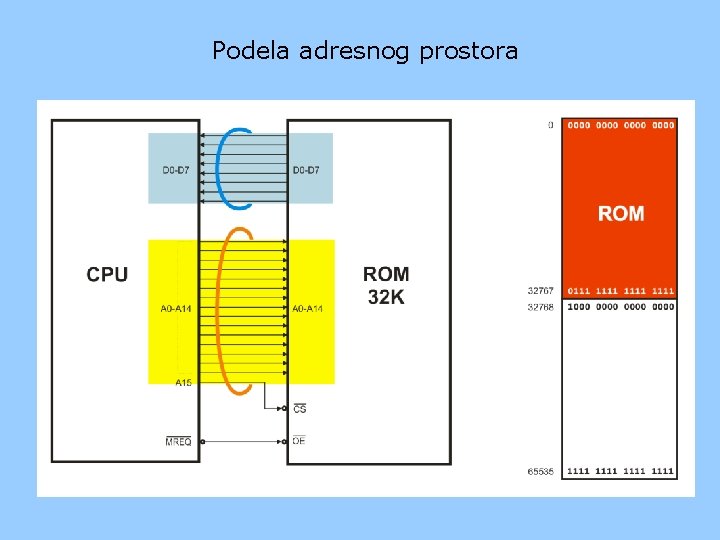

Podela adresnog prostora

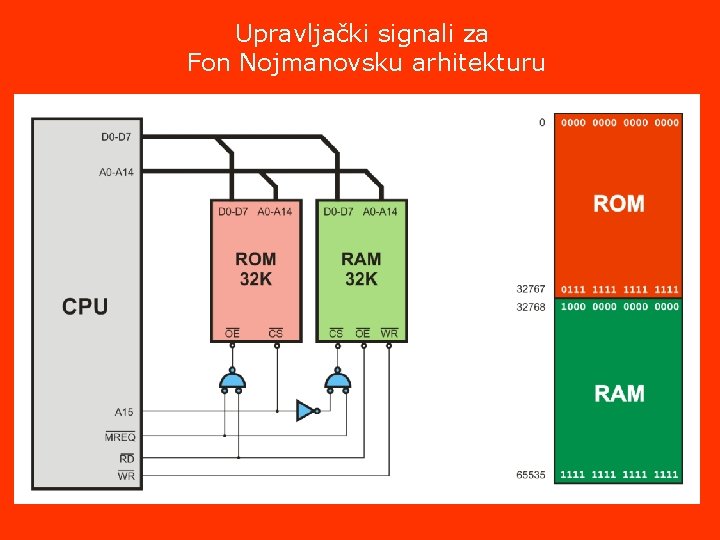

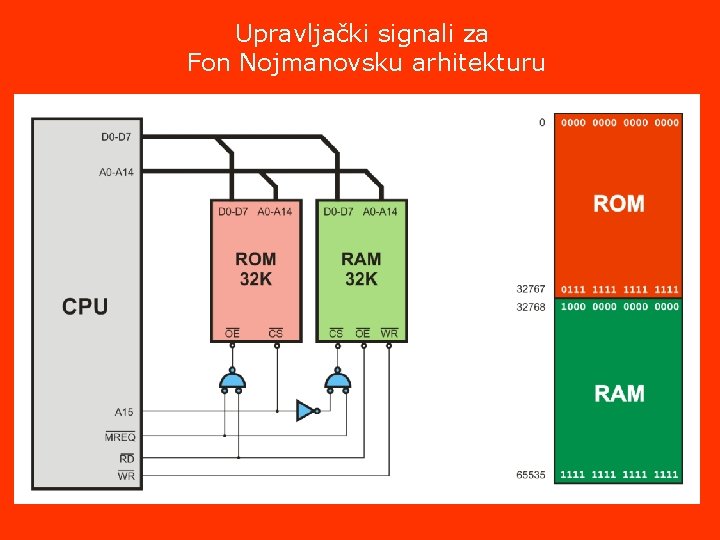

Upravljački signali za Fon Nojmanovsku arhitekturu

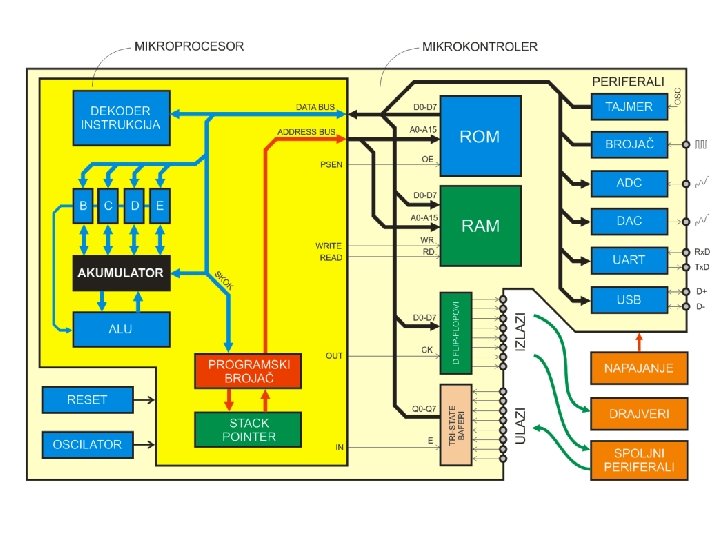

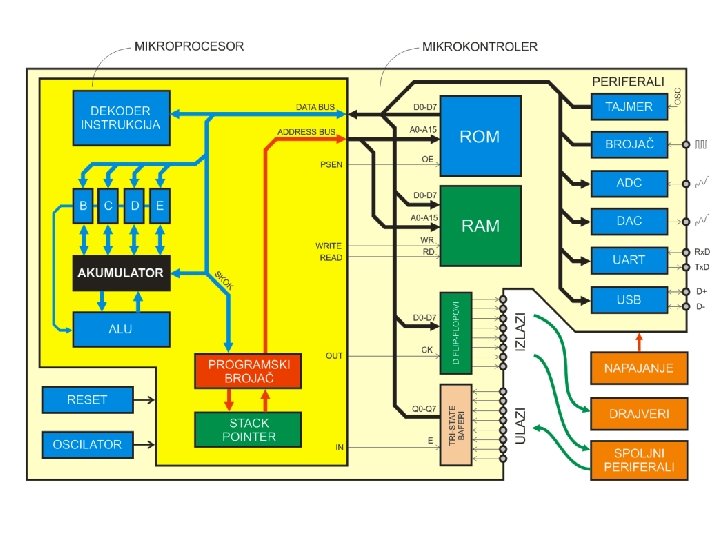

Fon Nojmanovska arhitektura mikroprocesora Programska memorija i memorija za podatke dele isti adresni prostor Moguće je izvršavanje programa iz memorije za podatke Postoji jedan glavni upravljački vod za sve memorije Moguće je smestiti ulazno-izlazne jedinice u zajednički adresni prostor

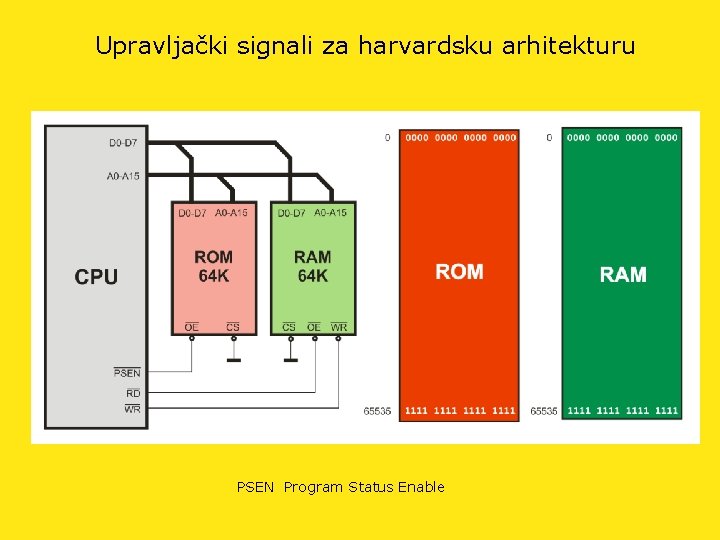

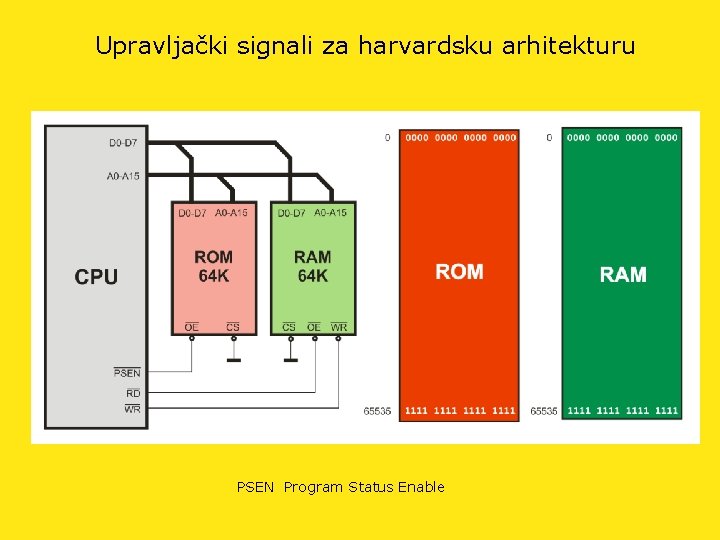

Upravljački signali za harvardsku arhitekturu PSEN Program Status Enable

Harvardska arhitektura mikroprocesora Programska memorija i memorija za podatke su u odvojenim adresnim prostorima Nije moguće izvršavanje programa iz memorije za podatke Postoje zasebni upravljački vodovi za programsku memoriju i memoriju za podatke Ulazno-izlazne jedinice je moguće smestiti samo u adresni prostor memorije za podatke

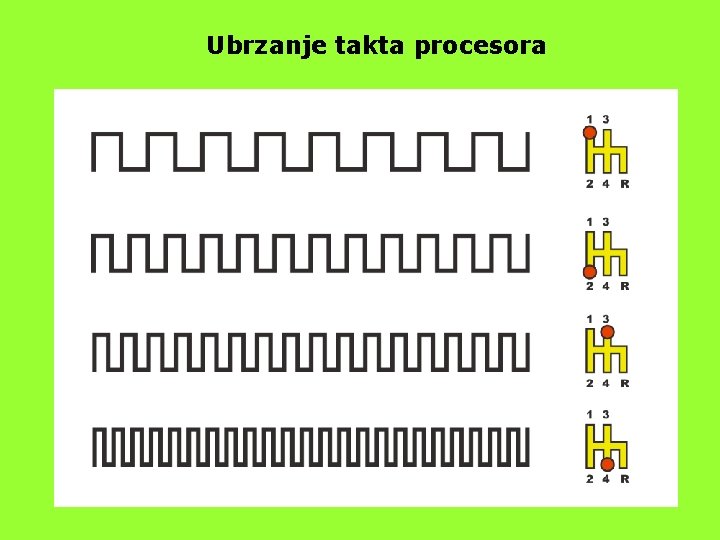

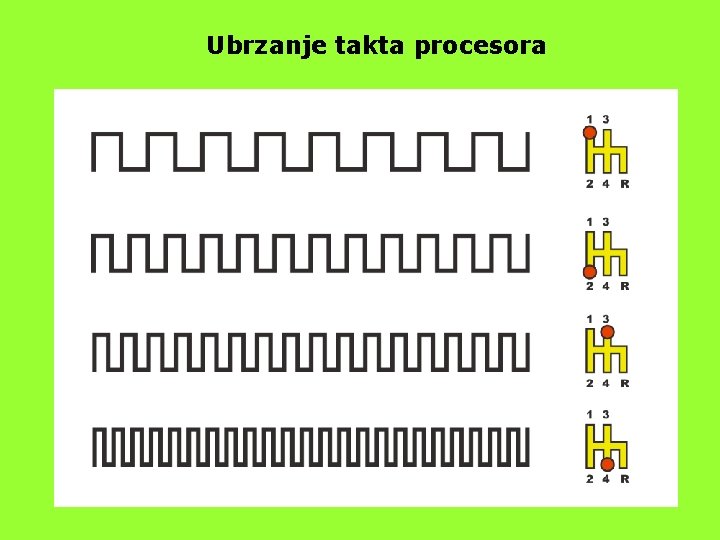

Ubrzanje takta procesora

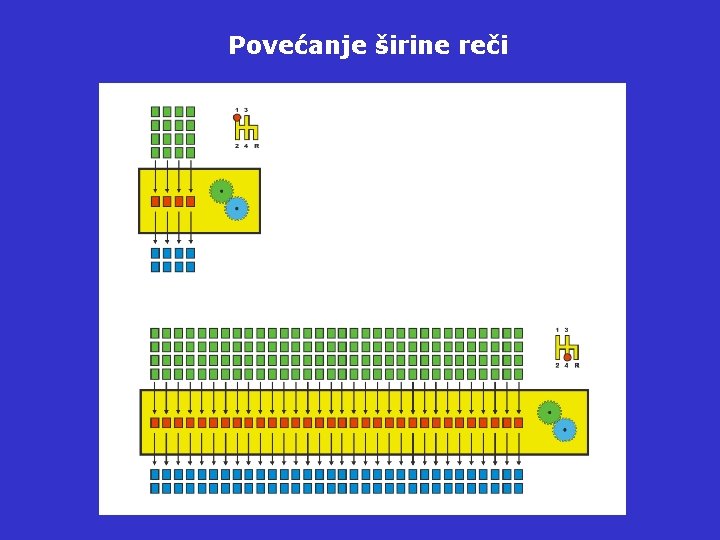

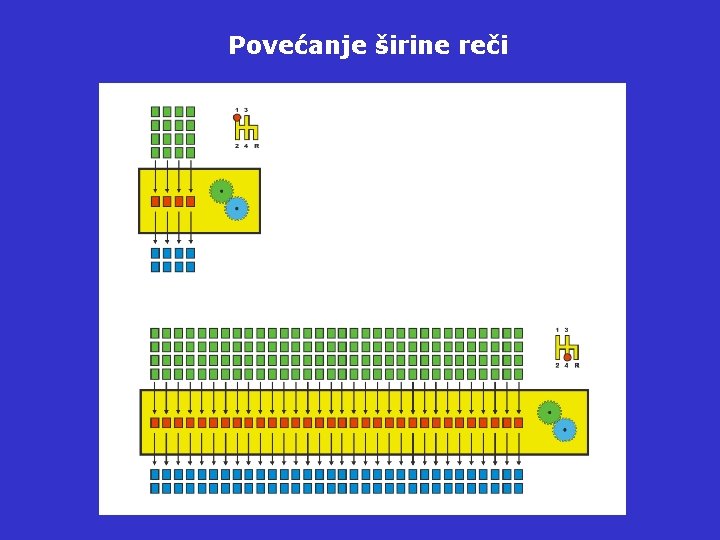

Povećanje širine reči

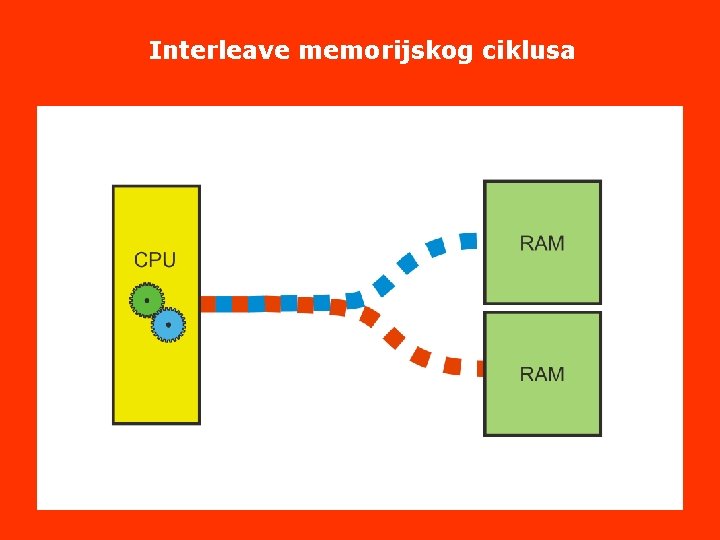

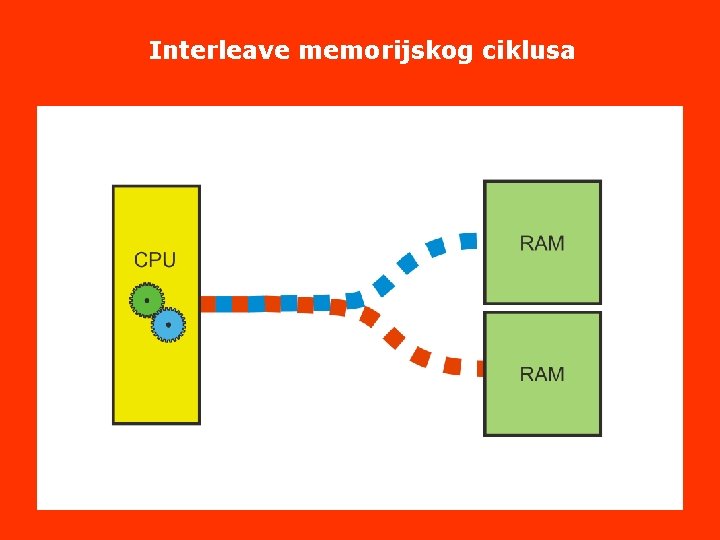

Interleave memorijskog ciklusa

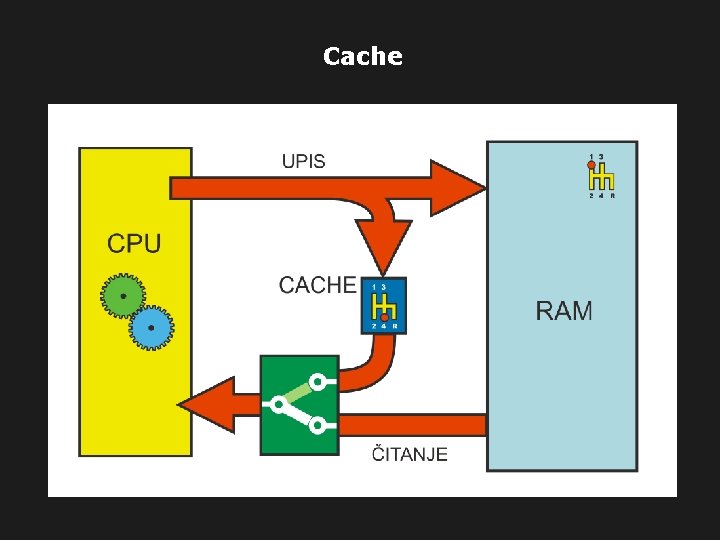

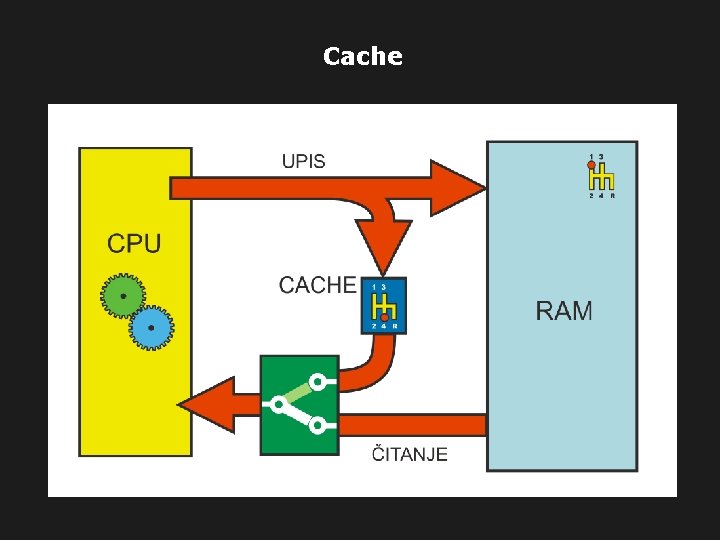

Cache

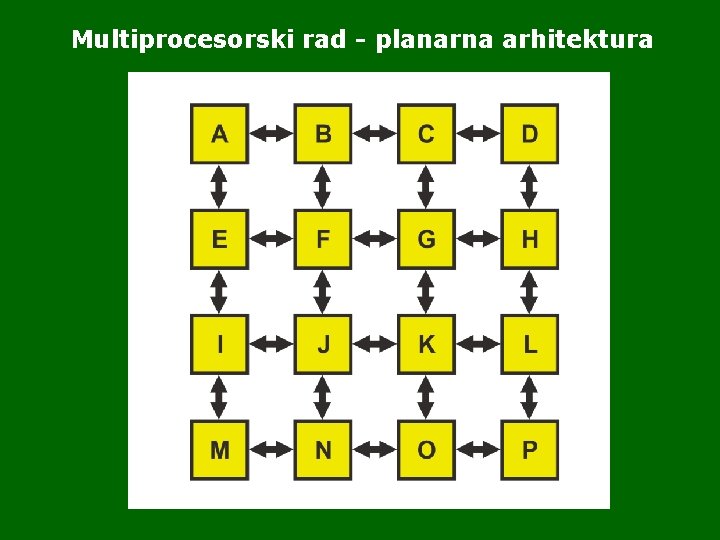

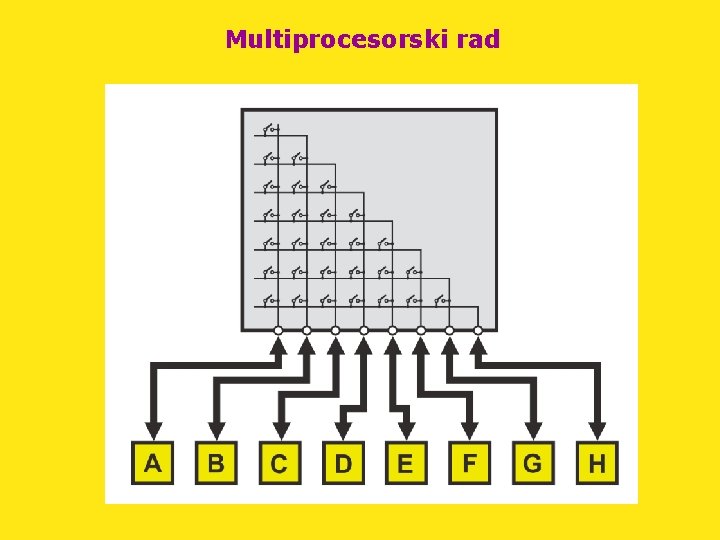

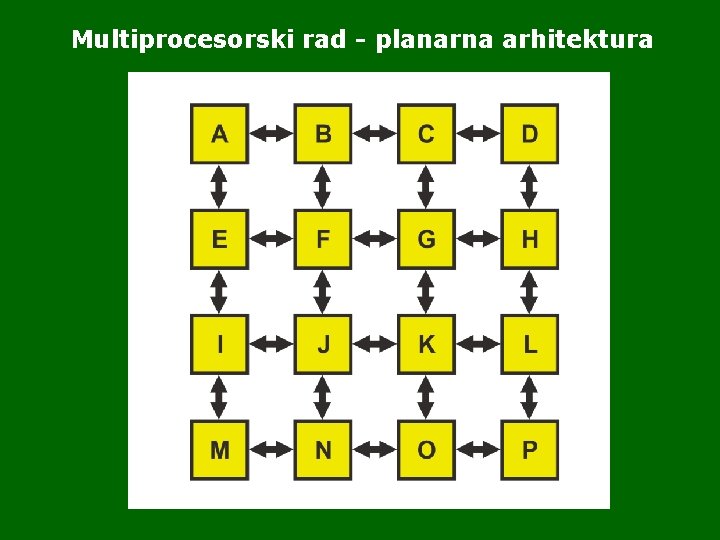

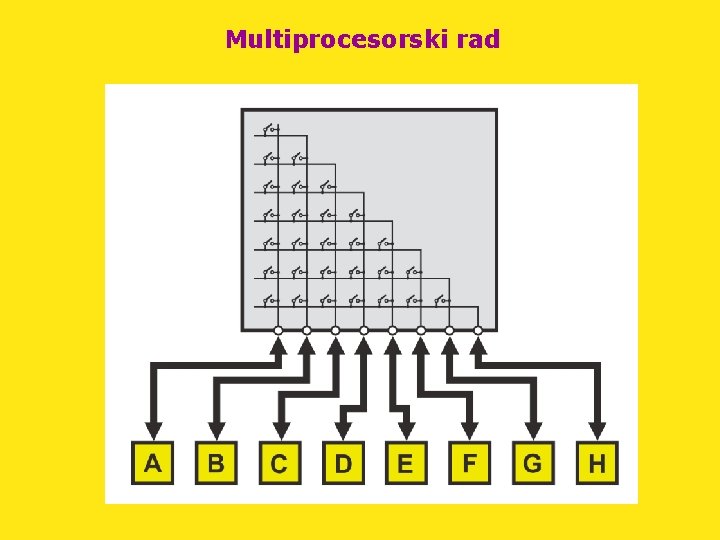

Multiprocesorski rad - planarna arhitektura

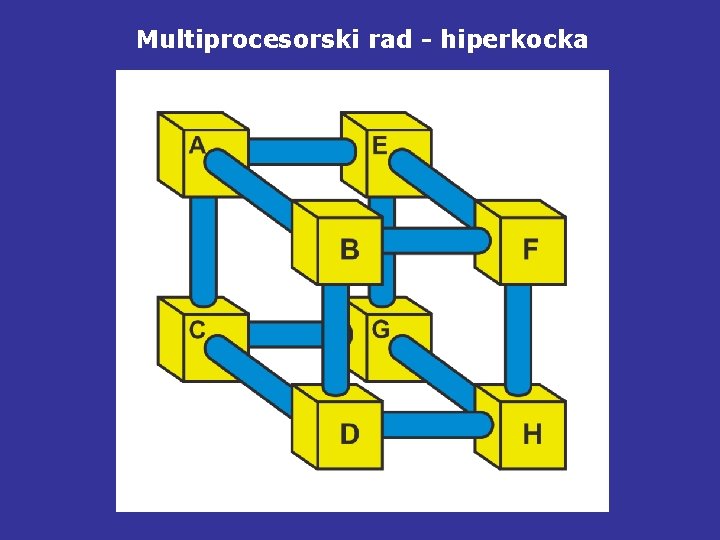

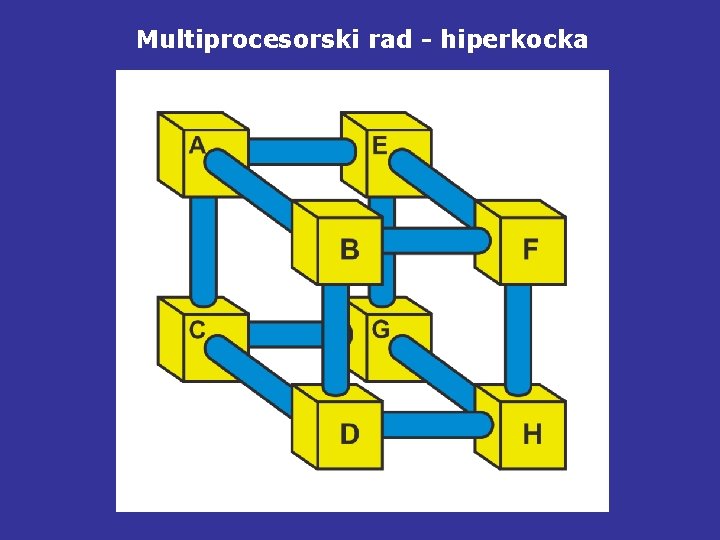

Multiprocesorski rad - hiperkocka

Multiprocesorski rad

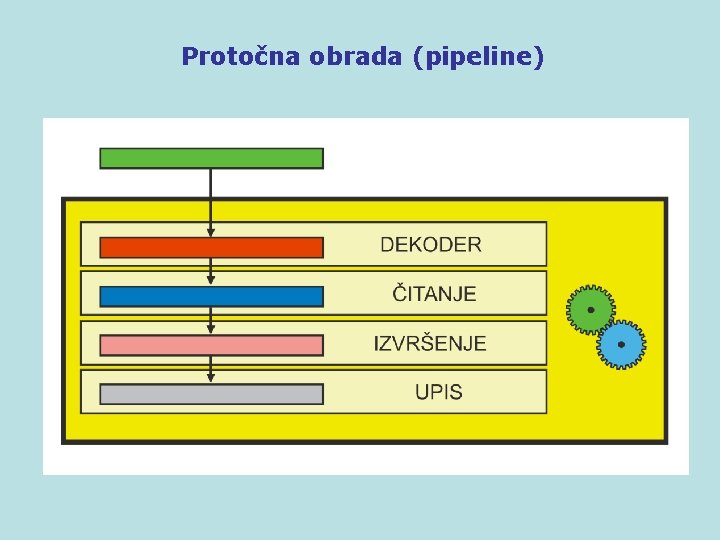

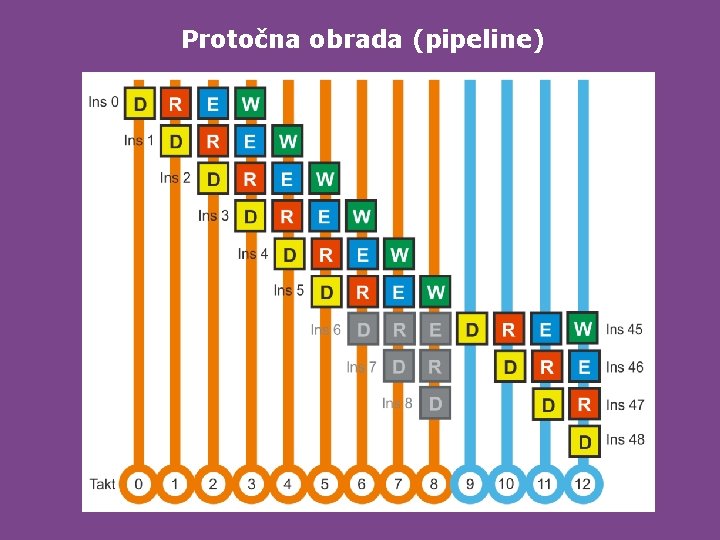

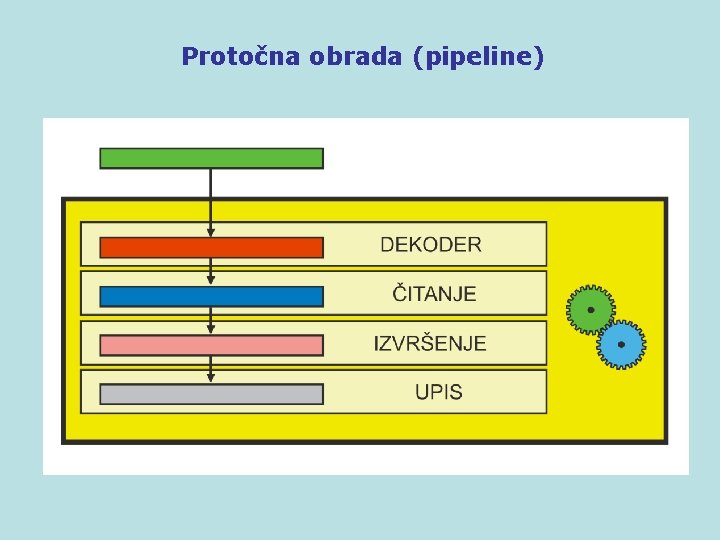

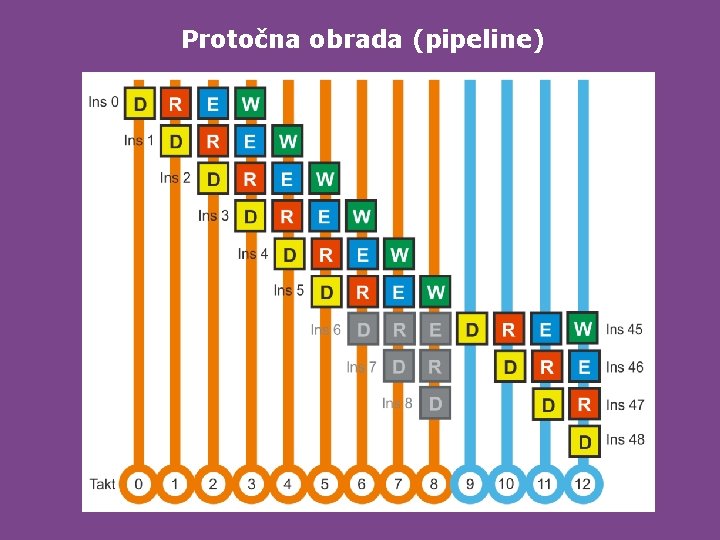

Protočna obrada (pipeline)

Protočna obrada (pipeline)

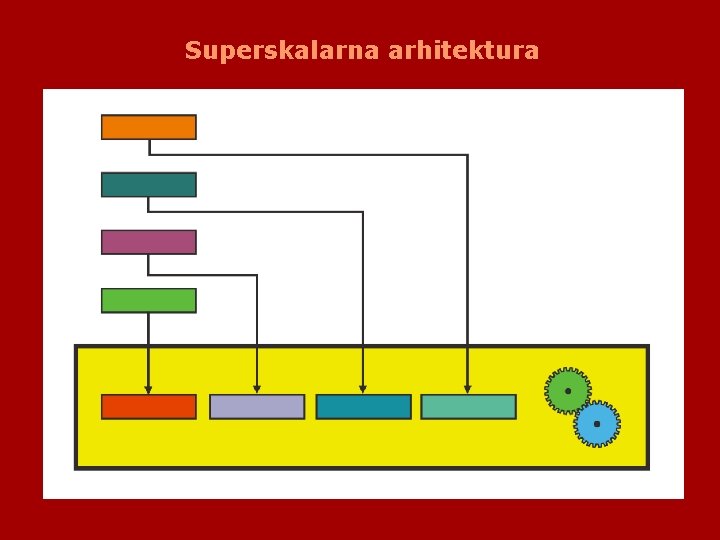

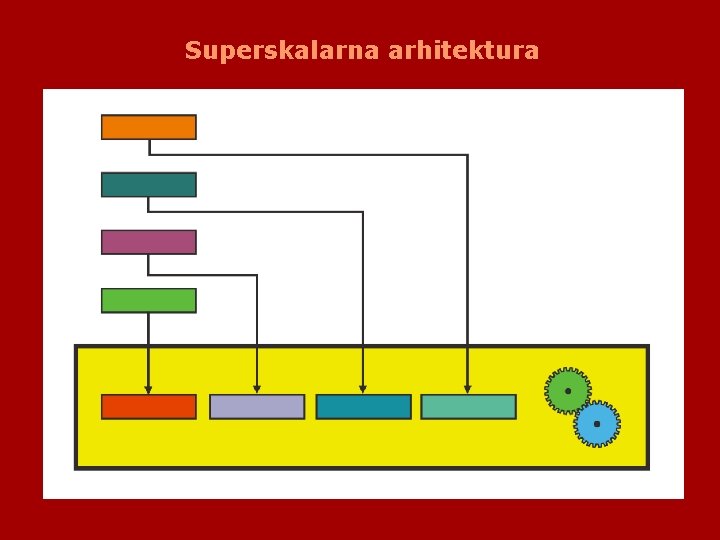

Superskalarna arhitektura

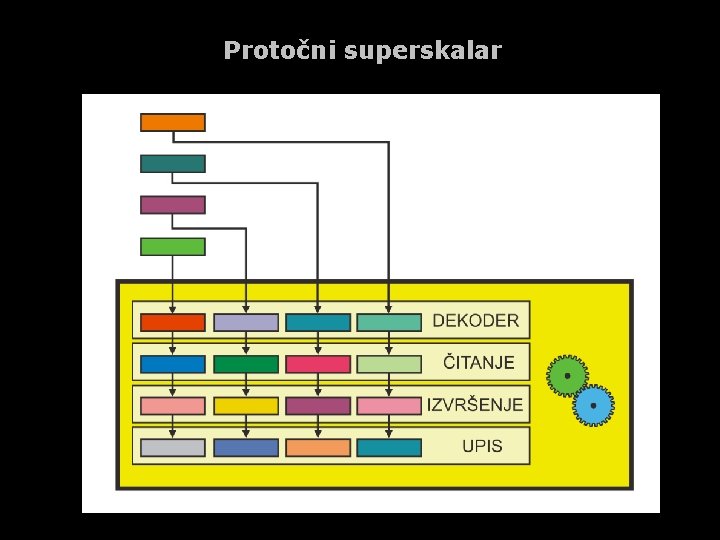

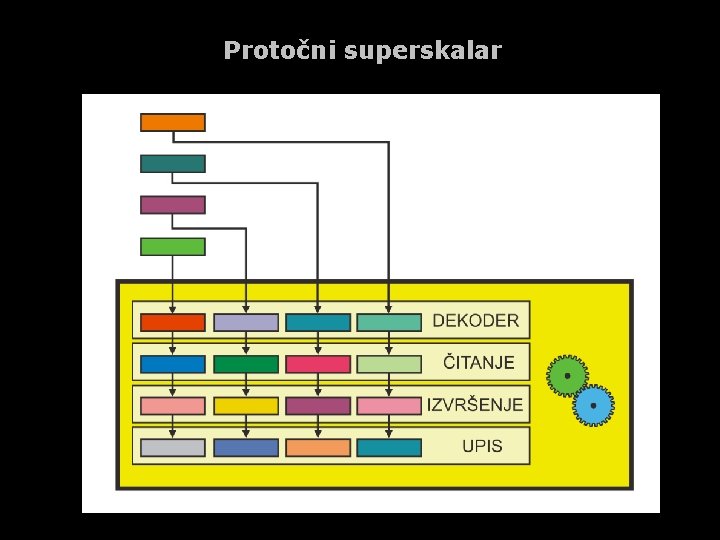

Protočni superskalar

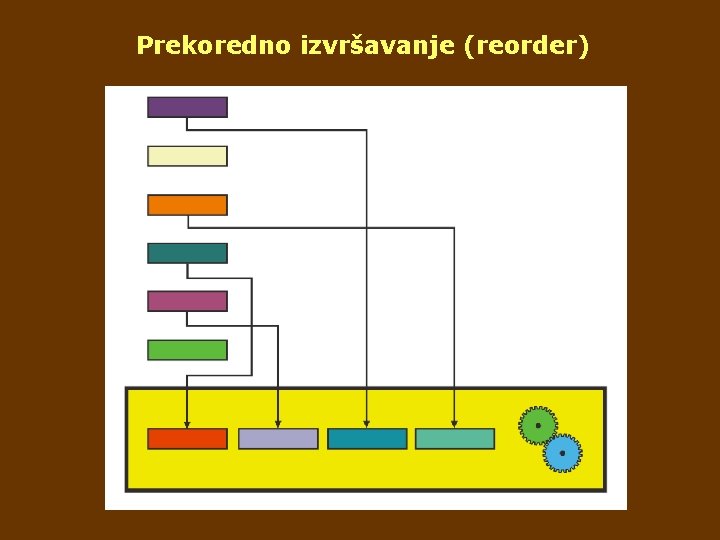

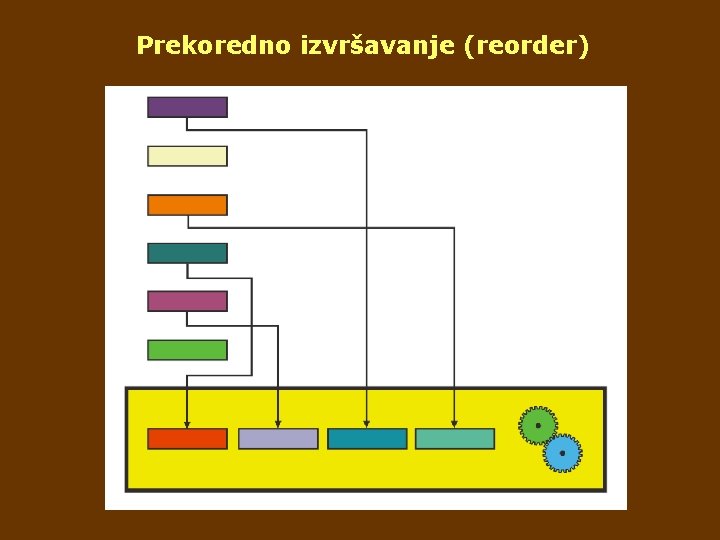

Prekoredno izvršavanje (reorder)

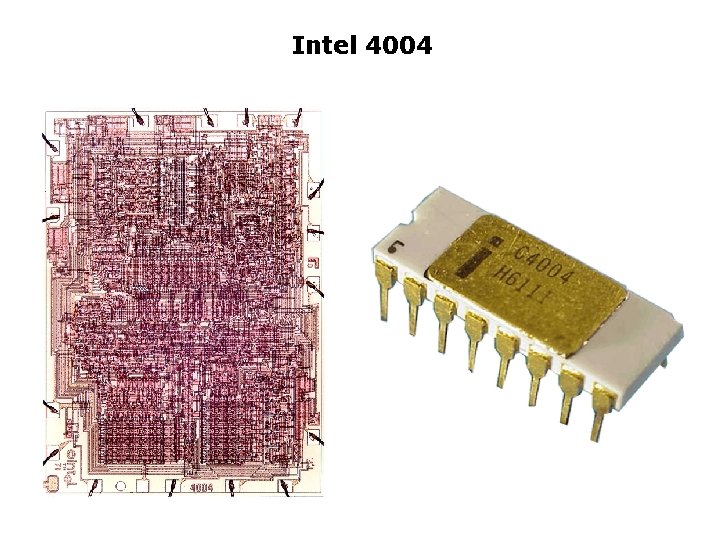

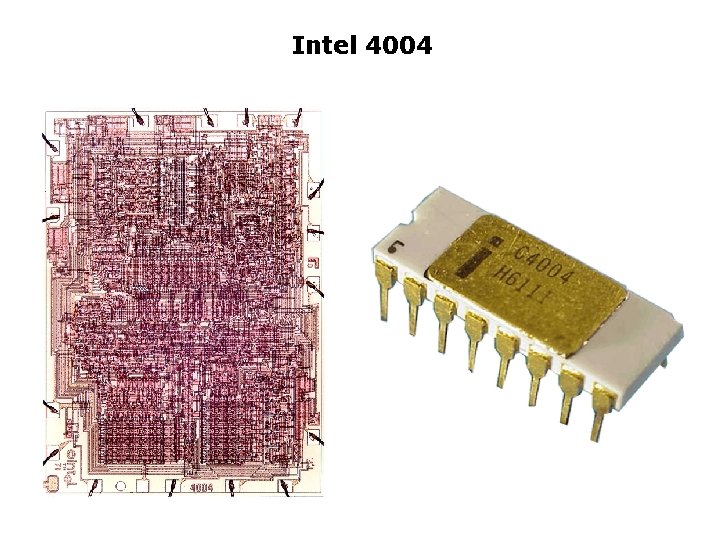

Intel 4004

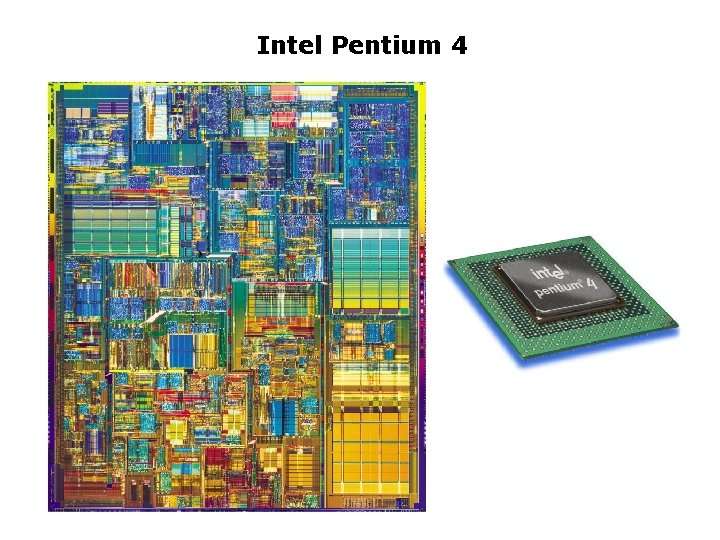

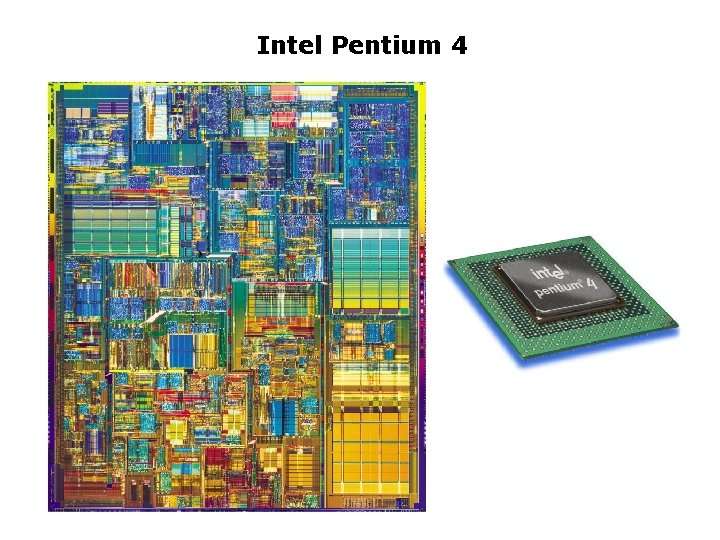

Intel Pentium 4