Xilinx Alliance Series XilinxSynopsys Powerful High Density Solutions

![Xilinx Specific Features w FPGA Express Automatically Infers Global [Asynchronous] Set/Reset Line l l Xilinx Specific Features w FPGA Express Automatically Infers Global [Asynchronous] Set/Reset Line l l](https://slidetodoc.com/presentation_image_h2/4ca28b7a0a6ec1ddae68cd6f7d6f81aa/image-12.jpg)

- Slides: 32

Xilinx Alliance Series Xilinx/Synopsys Powerful High Density Solutions http: //www. xilinx. com/products/alliance. htm

The Synopsys Advantage w Synopsys - Committed to Synthesis l l Own 90% Synthesis Market 14, 000 FPGA design seats w Comprehensive Product Offering l l Synopsys ASIC & FPGA VIEWlogic System Level & FPGA LMG Simulation Modeling Quad. Motive Static Timing Analyzer w Path to Higher Level Synthesis Tools w Verification at Every Stage of Design l Post Synthesis, Post P&R, Timing Analysis

The Xilinx Synopsys Advantage w OEM Agreement for FPGA Express - Device support upon introduction w Enhanced Design Performance - Joint development teams - Xilinx specific optimization - Advanced implementation technology w QOR Improvements - Ongoing synthesis benchmark feedback The Key to Success is A Strong Committed Partnership!

FPGA Express

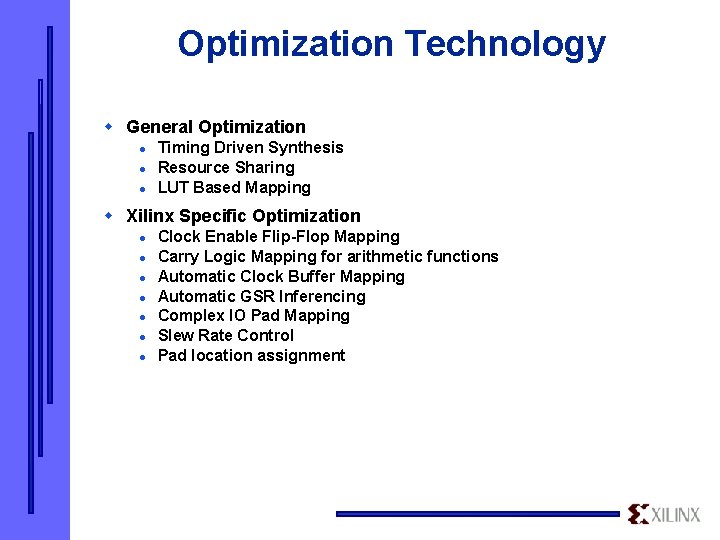

Optimization Technology w General Optimization l l l Timing Driven Synthesis Resource Sharing LUT Based Mapping w Xilinx Specific Optimization l l l l Clock Enable Flip-Flop Mapping Carry Logic Mapping for arithmetic functions Automatic Clock Buffer Mapping Automatic GSR Inferencing Complex IO Pad Mapping Slew Rate Control Pad location assignment

Datapath Synthesis - Module Generation & Mapping w Operators l l Adders, subtractors, comparators, counters. Multipliers w Instantiate using Logi. Blox and/or COREgen l l l RAM FIFO Multipliers (pipeline)

State Machine Optimization w Automatic FSM Encoding l l One Hot or Binary User selectable option w Coding Style Template l l l Templates in On-Line Help Enumerated type in VHDL parameter in Verilog

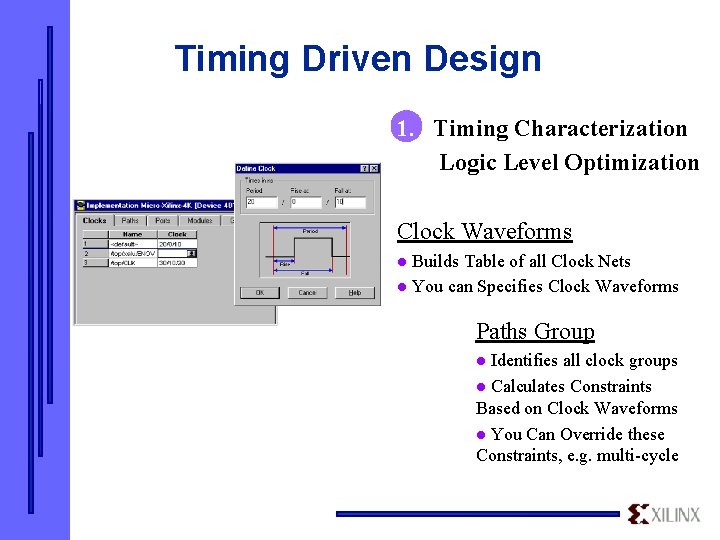

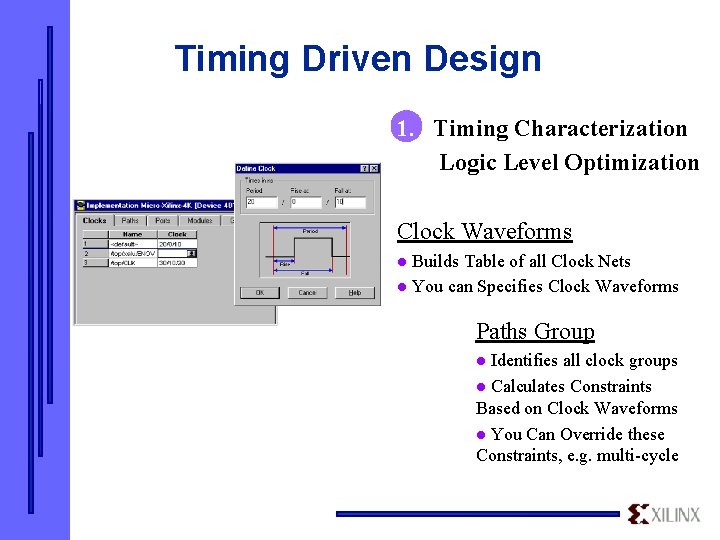

Timing Driven Design 1. Timing Characterization Logic Level Optimization Clock Waveforms Builds Table of all Clock Nets l You can Specifies Clock Waveforms l Paths Group Identifies all clock groups l Calculates Constraints Based on Clock Waveforms l You Can Override these Constraints, e. g. multi-cycle l

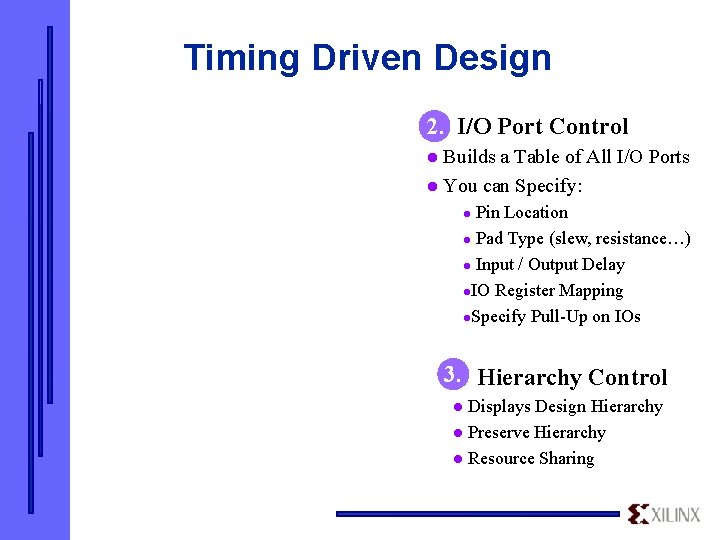

Timing Driven Design 2. I/O Port Control Builds a Table of All I/O Ports l You can Specify: l Pin Location l Pad Type (slew, resistance…) l Input / Output Delay l. IO Register Mapping l. Specify Pull-Up on IOs l 3. Hierarchy Control Displays Design Hierarchy l Preserve Hierarchy l Resource Sharing l

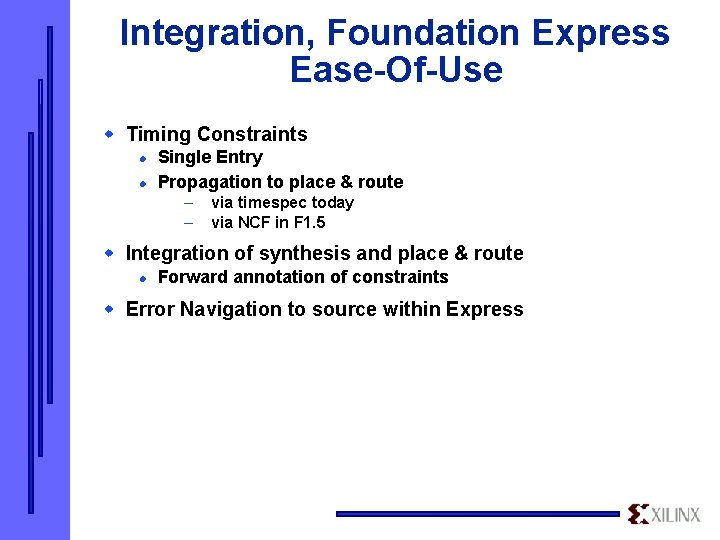

Integration, Foundation Express Ease-Of-Use w Timing Constraints l l Single Entry Propagation to place & route – – via timespec today via NCF in F 1. 5 w Integration of synthesis and place & route l Forward annotation of constraints w Error Navigation to source within Express

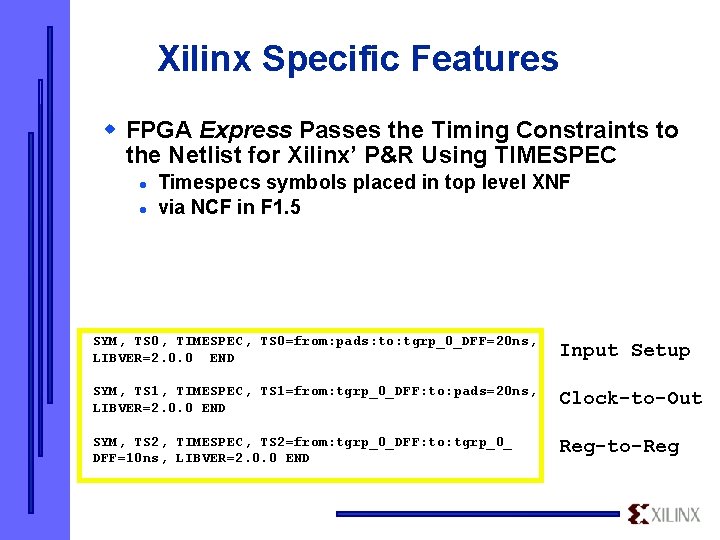

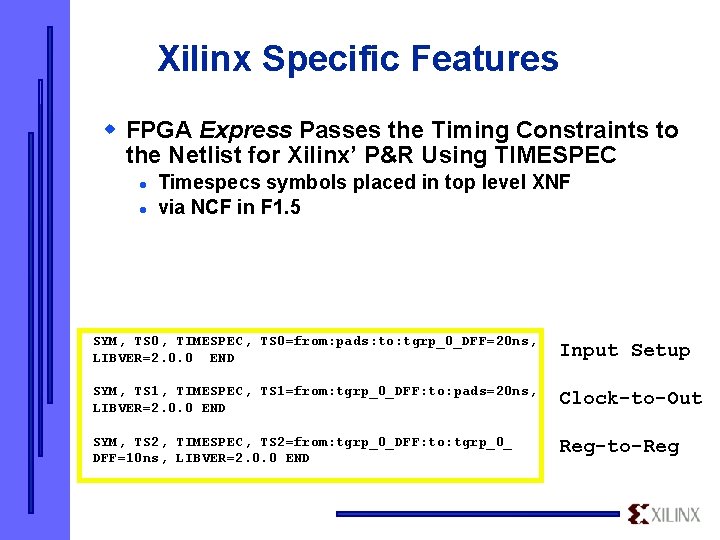

Xilinx Specific Features w FPGA Express Passes the Timing Constraints to the Netlist for Xilinx’ P&R Using TIMESPEC l l Timespecs symbols placed in top level XNF via NCF in F 1. 5 SYM, TS 0, TIMESPEC, TS 0=from: pads: to: tgrp_0_DFF=20 ns, LIBVER=2. 0. 0 END Input Setup SYM, TS 1, TIMESPEC, TS 1=from: tgrp_0_DFF: to: pads=20 ns, LIBVER=2. 0. 0 END Clock-to-Out SYM, TS 2, TIMESPEC, TS 2=from: tgrp_0_DFF: to: tgrp_0_ DFF=10 ns, LIBVER=2. 0. 0 END Reg-to-Reg

![Xilinx Specific Features w FPGA Express Automatically Infers Global Asynchronous SetReset Line l l Xilinx Specific Features w FPGA Express Automatically Infers Global [Asynchronous] Set/Reset Line l l](https://slidetodoc.com/presentation_image_h2/4ca28b7a0a6ec1ddae68cd6f7d6f81aa/image-12.jpg)

Xilinx Specific Features w FPGA Express Automatically Infers Global [Asynchronous] Set/Reset Line l l Initializes Each Register to Either Set or Reset Dedicated Distribution Network Reduces Routing Congestion Reset signal must source all FF’s

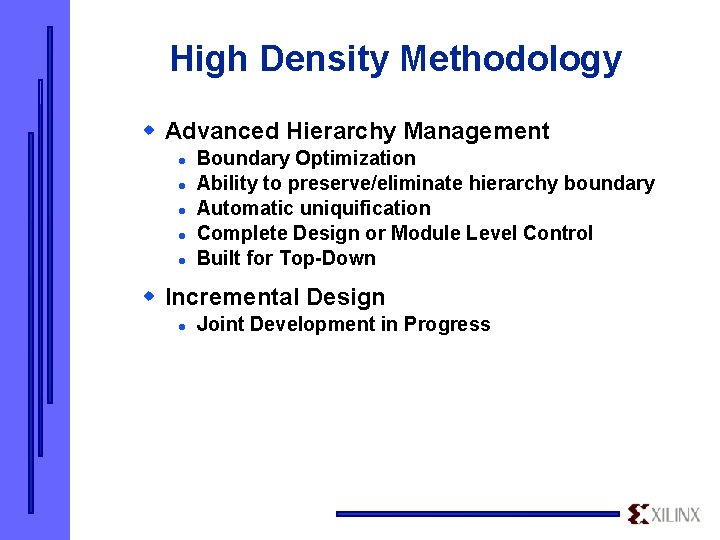

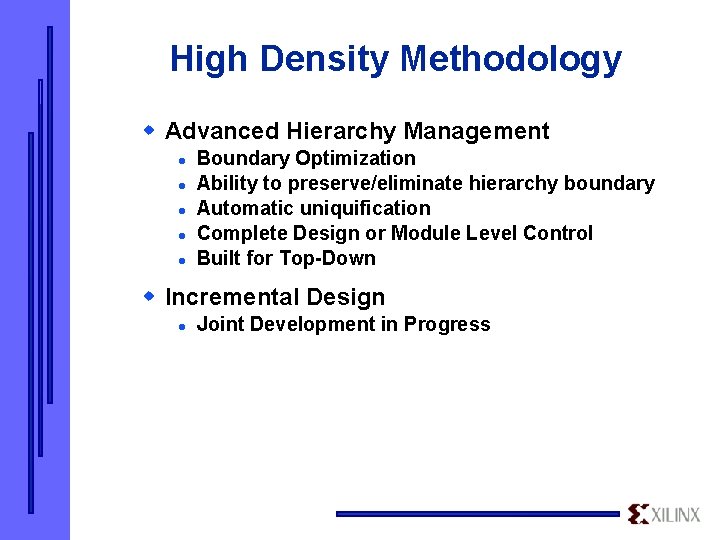

High Density Methodology w Advanced Hierarchy Management l l l Boundary Optimization Ability to preserve/eliminate hierarchy boundary Automatic uniquification Complete Design or Module Level Control Built for Top-Down w Incremental Design l Joint Development in Progress

Synopsys FPGA Compiler

High Density Methodology w Advanced Hierarchy Management l l l Boundary Optimization Ability to preserve/eliminate hierarchy boundary Automatic uniquification Complete Design or Module Level Control Built for Top-Down w Incremental Design l Joint Development in Progress

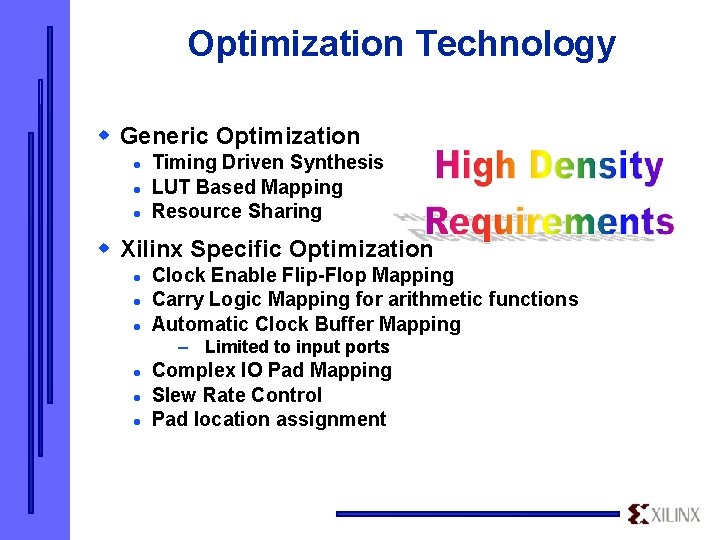

Optimization Technology w Generic Optimization l l l Timing Driven Synthesis LUT Based Mapping Resource Sharing w Xilinx Specific Optimization l l l Clock Enable Flip-Flop Mapping Carry Logic Mapping for arithmetic functions Automatic Clock Buffer Mapping – Limited to input ports l l l Complex IO Pad Mapping Slew Rate Control Pad location assignment

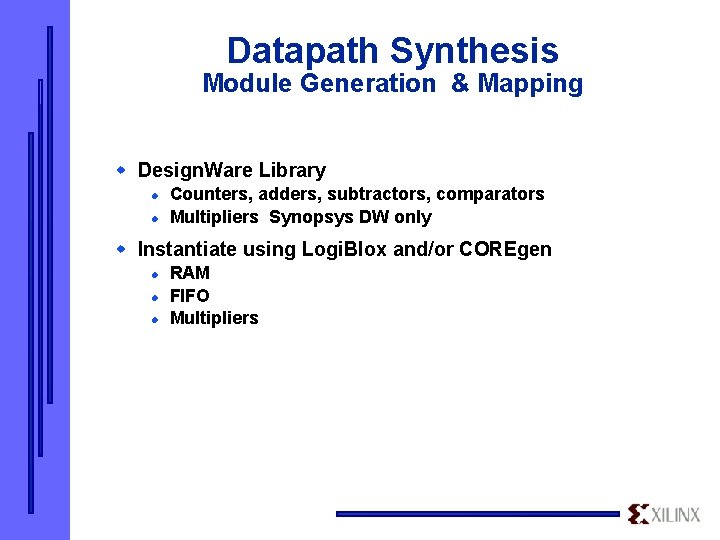

Datapath Synthesis Module Generation & Mapping w Design. Ware Library l l Counters, adders, subtractors, comparators Multipliers Synopsys DW only w Instantiate using Logi. Blox and/or COREgen l l l RAM FIFO Multipliers

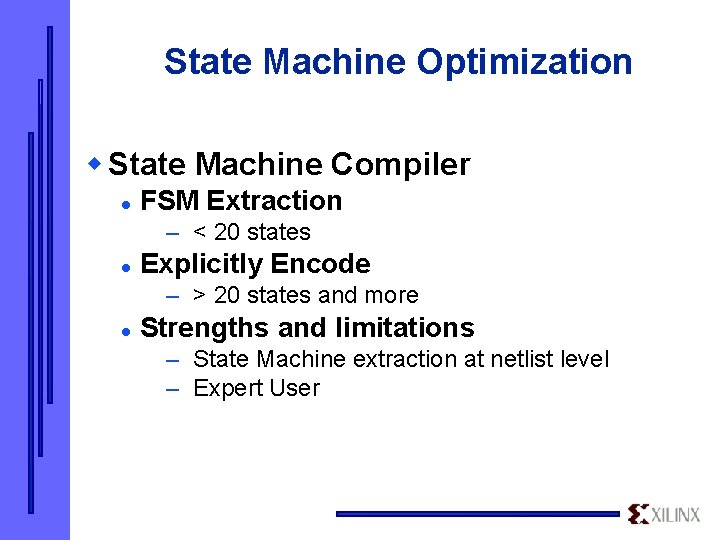

State Machine Optimization w State Machine Compiler l FSM Extraction – < 20 states l Explicitly Encode – > 20 states and more l Strengths and limitations – State Machine extraction at netlist level – Expert User

State Machine Optimization w State Machine Compiler l FSM Extraction – < 20 states l Explicitly Encode – > 20 states and more l Strengths and limitations – State Machine extraction at netlist level – Expert User

Xilinx Specific Features w Passing Constraints to Place and Route l dc 2 ncf w Design Recommendations l l Do not Overconstrain design Flatten Design for translation

Timing Driven Design w Design Constraints l l clocks input setup clock-to-out multi-cycle path w Optimization Directives l l l Boundary Optimization Mapping Effort re-timing using balance_registers (for XC 4000) w Scripting Capability l dc_shell, ASIC migration

High Density Methodology w Boundary Optimization l Maintain large hierarchical blocks w Group l Based on critical path w Ungroup l l Enable dc 2 ncf Faster ngdbuild runtimes w Fanout Control l Module Level Control

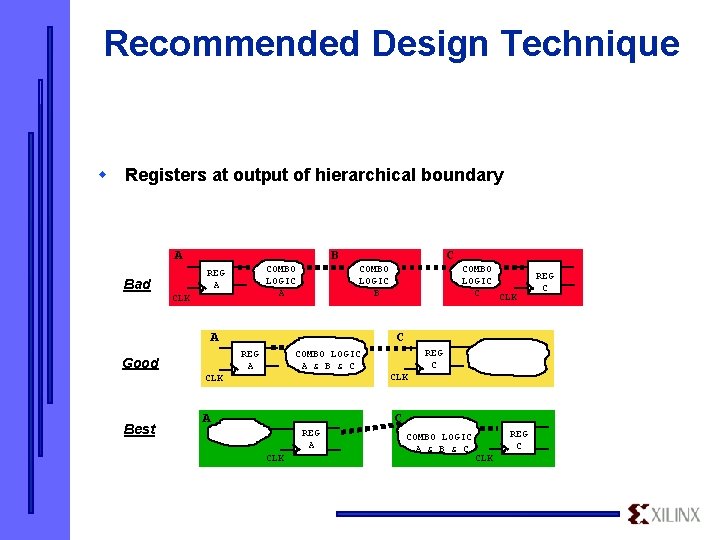

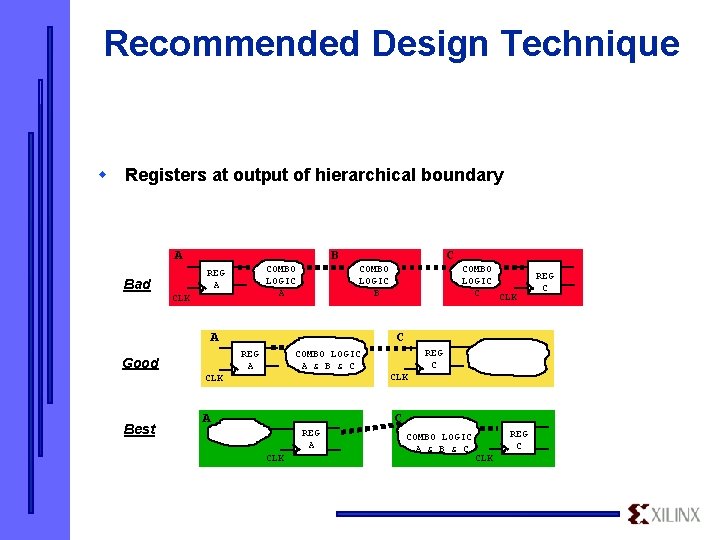

Recommended Design Technique w Registers at output of hierarchical boundary A B COMBO LOGIC A REG A Bad CLK A COMBO LOGIC A & B & C CLK Best COMBO LOGIC C CLK C REG A Good C COMBO LOGIC B A REG C CLK C REG A CLK COMBO LOGIC A & B & C REG C CLK REG C

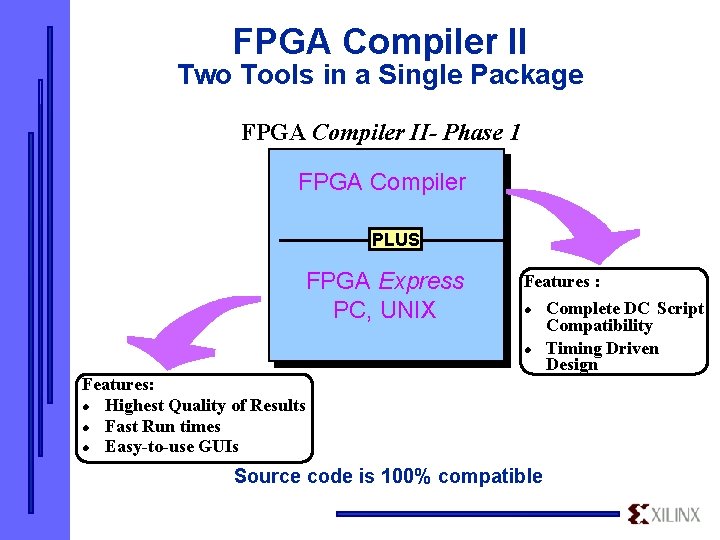

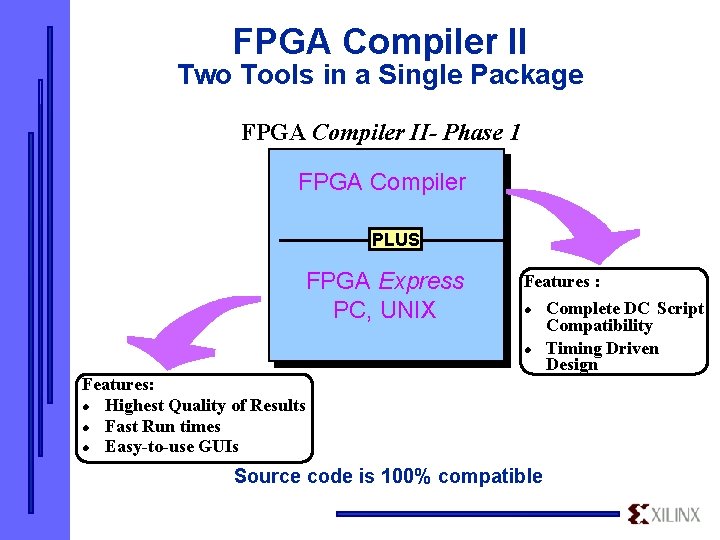

FPGA Compiler II Two Tools in a Single Package FPGA Compiler II- Phase 1 FPGA Compiler PLUS FPGA Express PC, UNIX Features : l l Features: l Highest Quality of Results l Fast Run times l Easy-to-use GUIs Source code is 100% compatible Complete DC Script Compatibility Timing Driven Design

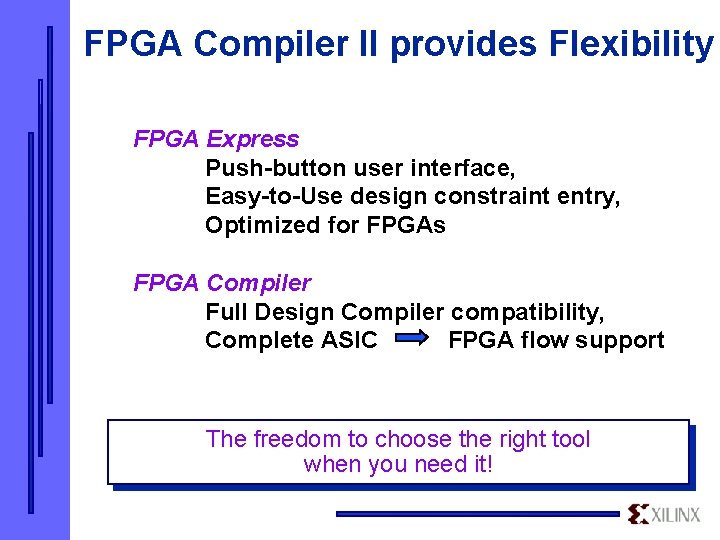

FPGA Compiler II provides Flexibility FPGA Express Push-button user interface, Easy-to-Use design constraint entry, Optimized for FPGAs FPGA Compiler Full Design Compiler compatibility, Complete ASIC FPGA flow support The freedom to choose the right tool when you need it!

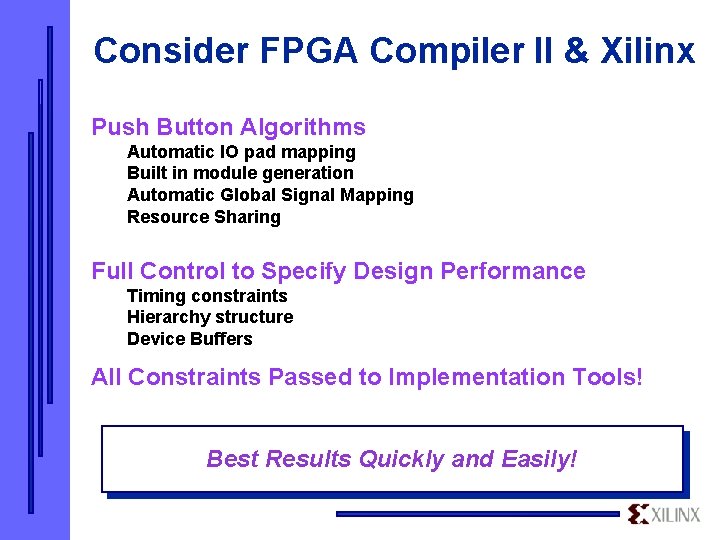

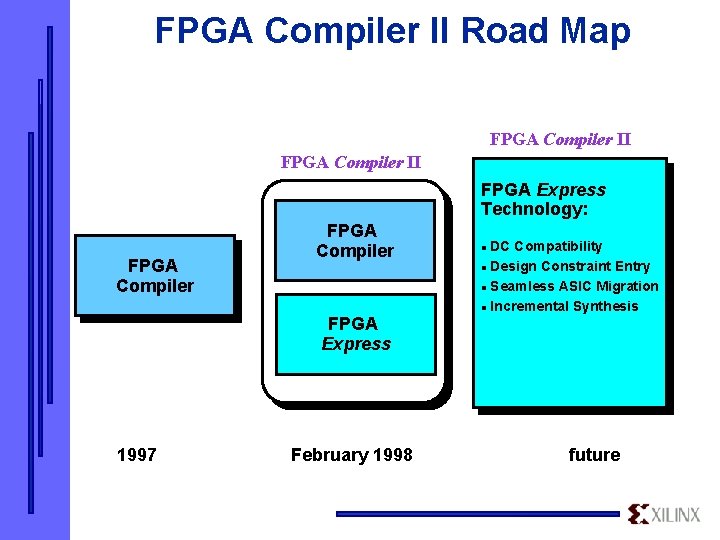

FPGA Compiler II Road Map FPGA Compiler II FPGA Express Technology: FPGA Compiler FPGA Express 1997 February 1998 DC Compatibility l Design Constraint Entry l Seamless ASIC Migration l Incremental Synthesis l future

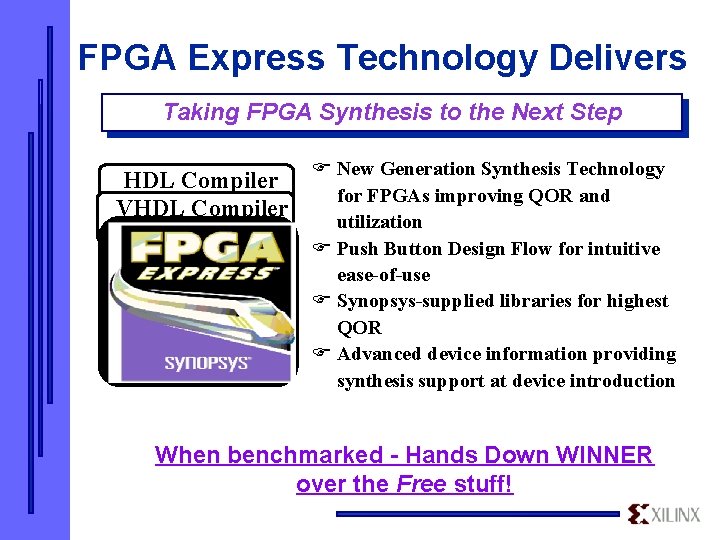

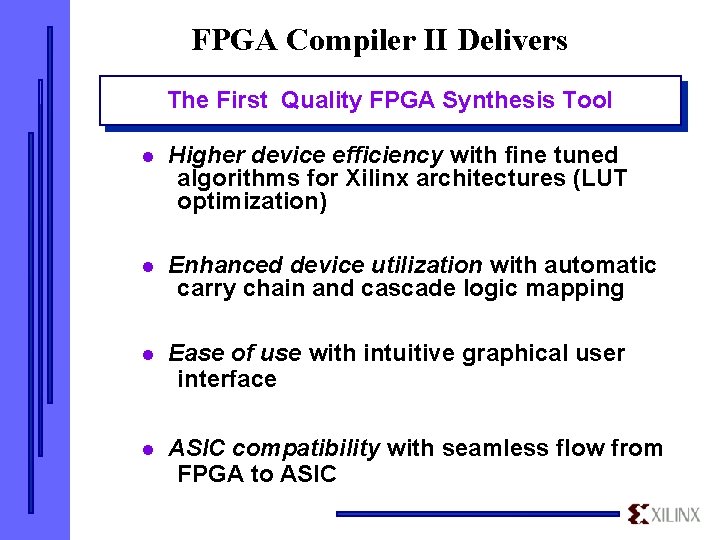

Consider FPGA Compiler II & Xilinx Push Button Algorithms Automatic IO pad mapping Built in module generation Automatic Global Signal Mapping Resource Sharing Full Control to Specify Design Performance Timing constraints Hierarchy structure Device Buffers All Constraints Passed to Implementation Tools! Best Results Quickly and Easily!

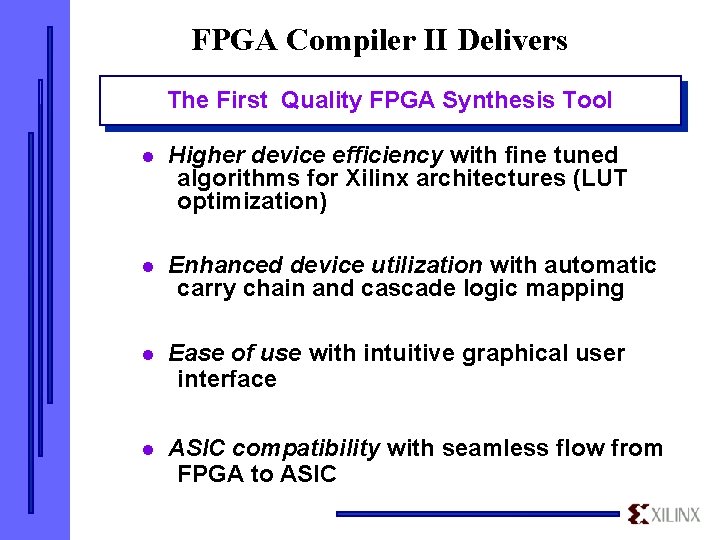

FPGA Express Technology Delivers Taking FPGA Synthesis to the Next Step HDL Compiler VHDL Compiler F New Generation Synthesis Technology for FPGAs improving QOR and utilization F Push Button Design Flow for intuitive ease-of-use F Synopsys-supplied libraries for highest QOR F Advanced device information providing synthesis support at device introduction When benchmarked - Hands Down WINNER over the Free stuff!

FPGA Compiler II Delivers The First Quality FPGA Synthesis Tool l Higher device efficiency with fine tuned algorithms for Xilinx architectures (LUT optimization) l Enhanced device utilization with automatic carry chain and cascade logic mapping l Ease of use with intuitive graphical user interface l ASIC compatibility with seamless flow from FPGA to ASIC

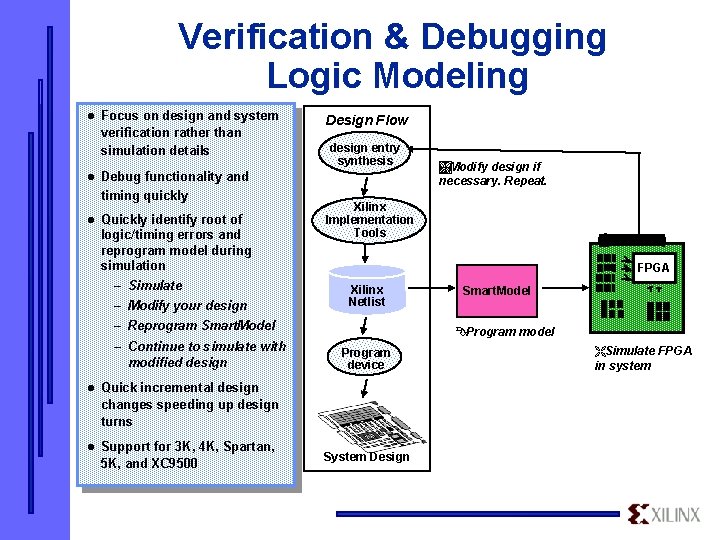

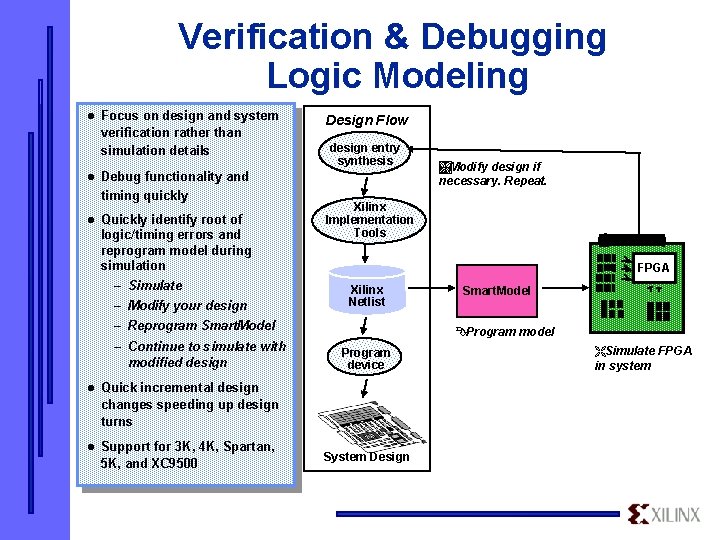

Verification & Debugging Logic Modeling l Focus on design and system verification rather than simulation details l Debug functionality and timing quickly l Quickly identify root of logic/timing errors and reprogram model during simulation – Simulate – Modify your design Design Flow design entry synthesis Xilinx Implementation Tools FPGA Xilinx Netlist – Reprogram Smart. Model – Continue to simulate with modified design l Quick incremental design changes speeding up design turns l Support for 3 K, 4 K, Spartan, 5 K, and XC 9500 ÌModify design if necessary. Repeat. Smart. Model ÊProgram model Program device System Design ËSimulate FPGA in system

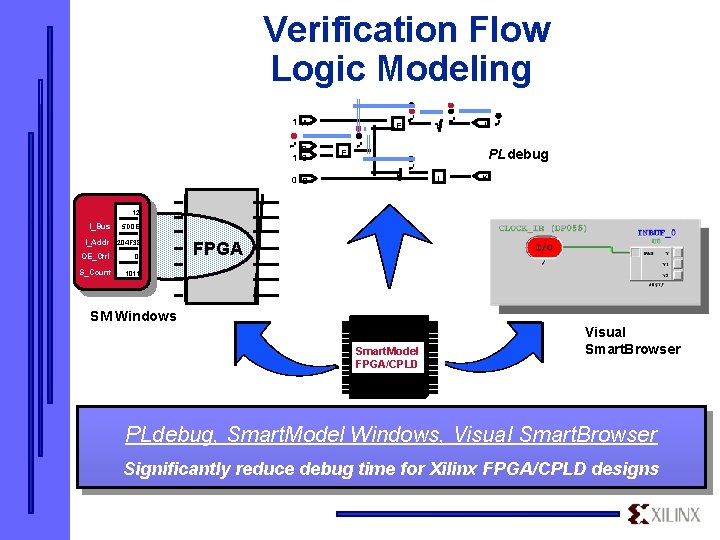

Verification Flow Logic Modeling 1 A B 1 C 0 D F H J PLdebug E G I K 12 I_Bus 5 D 0 E I_Addr 204 F 38 OE_Ctrl 0 S_Count 1011 FPGA SM Windows Smart. Model FPGA/CPLD Visual Smart. Browser PLdebug, Smart. Model Windows, Visual Smart. Browser Significantly reduce debug time for Xilinx FPGA/CPLD designs

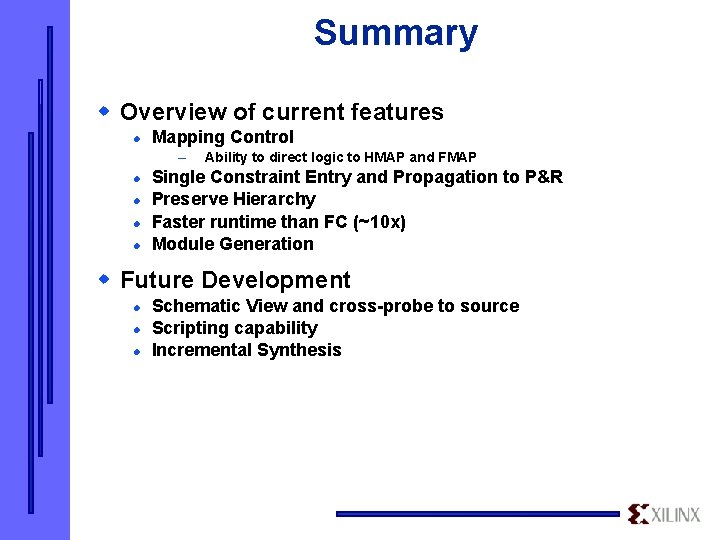

Summary w Overview of current features l Mapping Control – l l Ability to direct logic to HMAP and FMAP Single Constraint Entry and Propagation to P&R Preserve Hierarchy Faster runtime than FC (~10 x) Module Generation w Future Development l l l Schematic View and cross-probe to source Scripting capability Incremental Synthesis