Selling Xilinx Software vs Altera Xilinx Academy February

Selling Xilinx Software vs. Altera Xilinx Academy February 24 th, 1999 1 2/1/99 Confidential

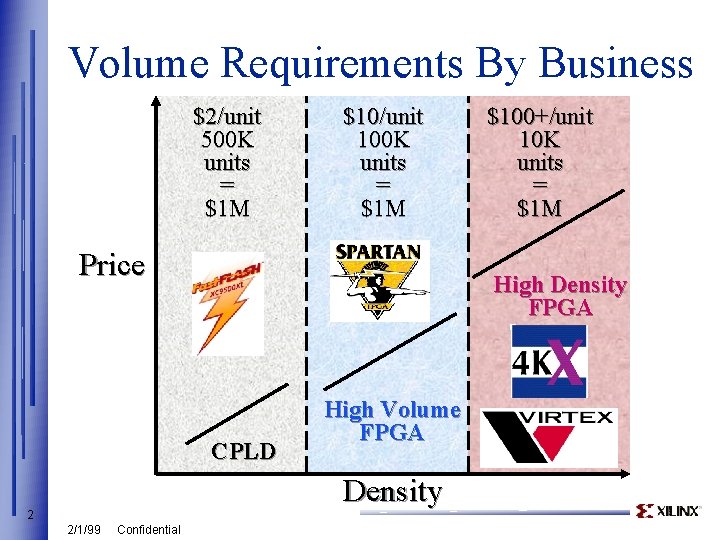

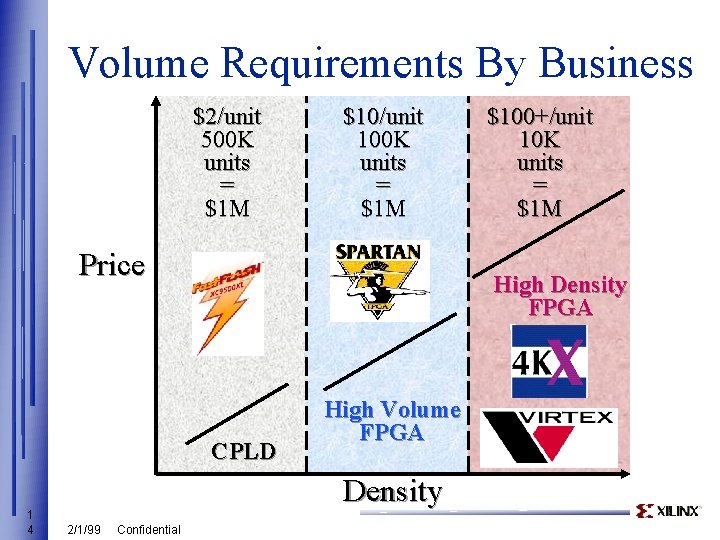

Volume Requirements By Business $2/unit 500 K units = $1 M $10/unit 100 K units = $1 M Price High Density FPGA CPLD High Volume FPGA Density 2 2/1/99 Confidential $100+/unit 10 K units = $1 M

XILINX ALTERA vs. FLEX 6 K vs. FLEX 10 K vs. Raphael vs. MAX PLUS+ 3 2/1/99 Confidential

Xilinx Software How to Compete and Win Against Altera

Xilinx Software w Intuitive Design Environment; Easy to Use w Superior HDL Design Solutions w Best Push-Button Results plus Performance Driven “When You Need it” w Best Value Software Configurations 5 2/1/99 Confidential

Xilinx Software w Intuitive Design Environment; Easy to Use Superior HDL Design Solutions w Best Push-Button Results plus Performance Driven “When You Need it” w Best Value Software 6 2/1/99 Confidential

Xilinx Ease-of-Use Xilinx Push Button Design Flows Design Wizards Graphical State Diagram Entry High Volume Solution Interactive Web Enabled Software 7 2/1/99 Confidential Altera 4 4 4 Very Limited 4 4 NO! Limited Device Support Proprietary Synthesis

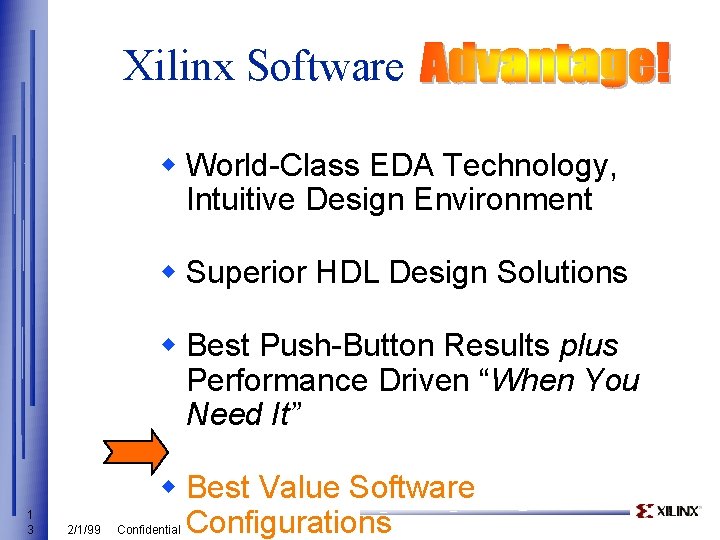

Xilinx Software w World-Class EDA Technology, Intuitive Design Environment w Superior HDL Design Solutions w Best Push-Button Results plus Performance Driven “When You Need it” 8 2/1/99 w Best Value Software Configurations Confidential

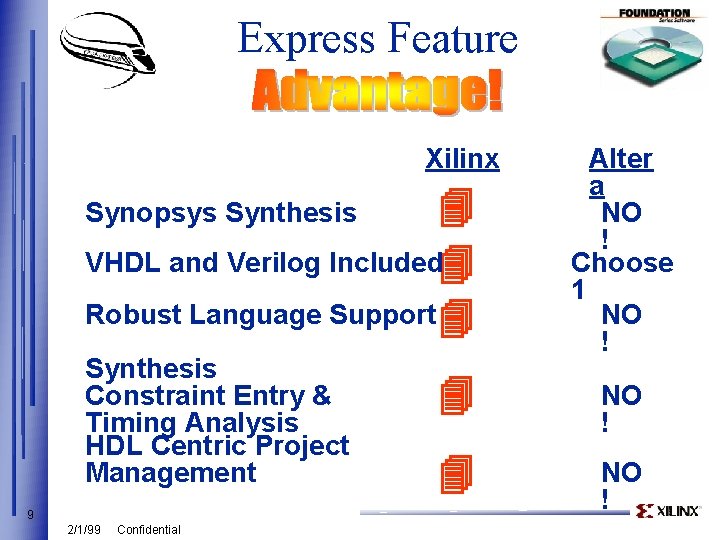

Express Feature Xilinx 4 VHDL and Verilog Included 4 Robust Language Support 4 Synopsys Synthesis Constraint Entry & Timing Analysis HDL Centric Project Management 9 2/1/99 Confidential Alter a NO ! Choose 1 NO ! 4 NO !

Xilinx Software w World-Class EDA Technology, Intuitive Design Environment w Superior HDL Design Solutions w Best Push-Button Results plus Performance Driven “When You Need It” 1 0 2/1/99 w Best Value Software Configurations Confidential

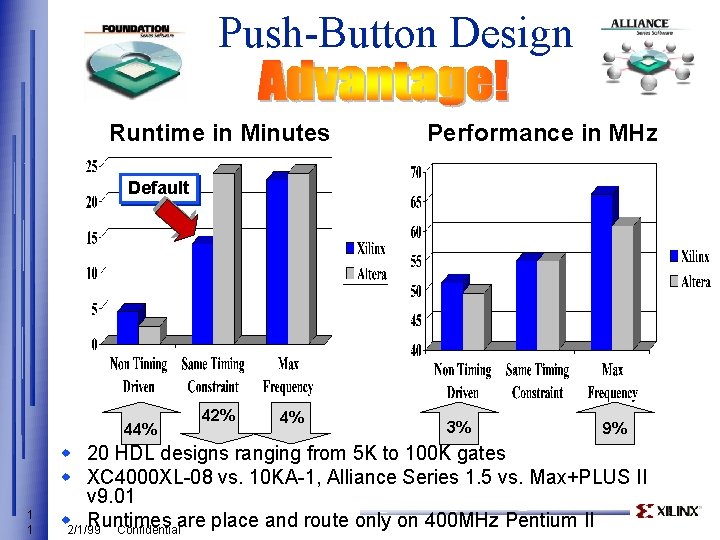

Push-Button Design Runtime in Minutes Performance in MHz Default 44% 1 1 42% 4% 3% 9% w 20 HDL designs ranging from 5 K to 100 K gates w XC 4000 XL-08 vs. 10 KA-1, Alliance Series 1. 5 vs. Max+PLUS II v 9. 01 w 2/1/99 Runtimes are place and route only on 400 MHz Pentium II Confidential

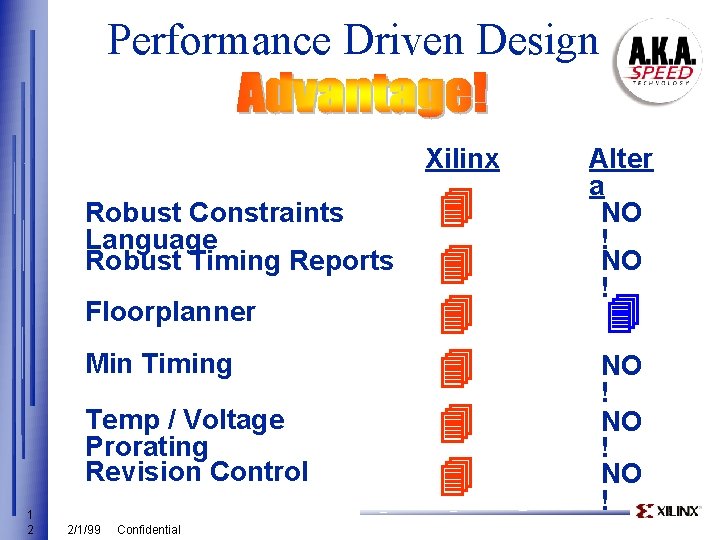

Performance Driven Design Xilinx Robust Constraints Language Robust Timing Reports Floorplanner Min Timing Temp / Voltage Prorating Revision Control 1 2 2/1/99 Confidential 4 4 4 Alter a NO ! 4 NO !

Xilinx Software w World-Class EDA Technology, Intuitive Design Environment w Superior HDL Design Solutions w Best Push-Button Results plus Performance Driven “When You Need It” 1 3 2/1/99 w Best Value Software Configurations Confidential

Volume Requirements By Business $2/unit 500 K units = $1 M $10/unit 100 K units = $1 M Price High Density FPGA CPLD 1 4 High Volume FPGA Density 2/1/99 Confidential $100+/unit 10 K units = $1 M

Target Markets / Solutions 95 4 $ , 5 $9 FND-BAS ! $495 FND-BSX ALI-STD FND-EXP FND-BSX Price High-End FPGA CPLD 1 5 High-Volume FPGA Density 2/1/99 Confidential 5! 9 9 , 4 $

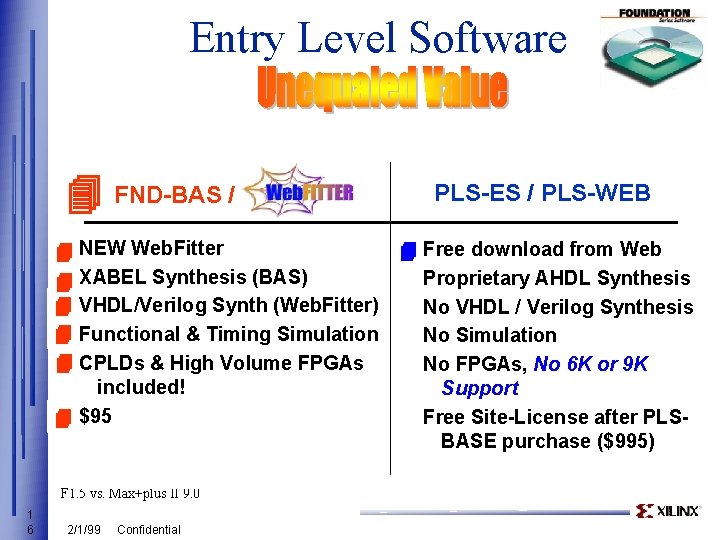

Entry Level Software 4 FND-BAS / NEW Web. Fitter XABEL Synthesis (BAS) VHDL/Verilog Synth (Web. Fitter) Functional & Timing Simulation CPLDs & High Volume FPGAs included! 4 $95 4 4 4 F 1. 5 vs. Max+plus II 9. 0 1 6 2/1/99 Confidential PLS-ES / PLS-WEB 4 Free download from Web Proprietary AHDL Synthesis No VHDL / Verilog Synthesis No Simulation No FPGAs, No 6 K or 9 K Support Free Site-License after PLSBASE purchase ($995)

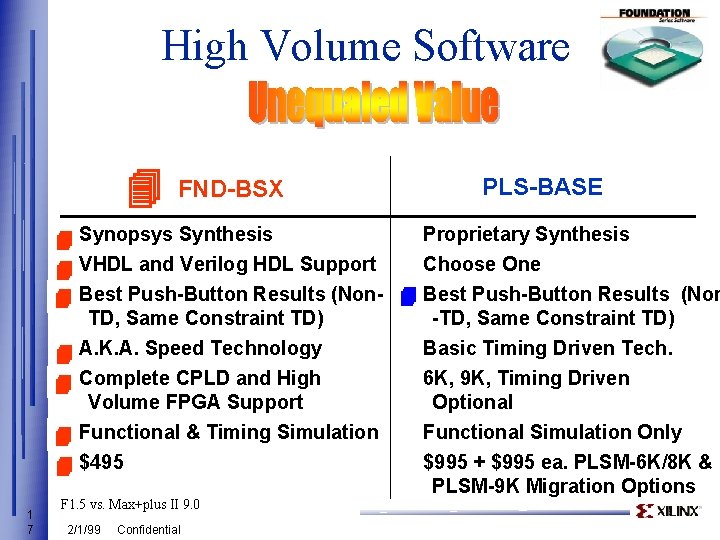

High Volume Software 4 FND-BSX PLS-BASE Proprietary Synthesis 4 Synopsys Synthesis Choose One 4 VHDL and Verilog HDL Support 4 Best Push-Button Results (Non- 4 Best Push-Button Results (Non TD, Same Constraint TD) -TD, Same Constraint TD) Basic Timing Driven Tech. 4 A. K. A. Speed Technology 6 K, 9 K, Timing Driven 4 Complete CPLD and High Volume FPGA Support Optional Functional Simulation Only 4 Functional & Timing Simulation $995 + $995 ea. PLSM-6 K/8 K & 4 $495 PLSM-9 K Migration Options 1 7 F 1. 5 vs. Max+plus II 9. 0 2/1/99 Confidential

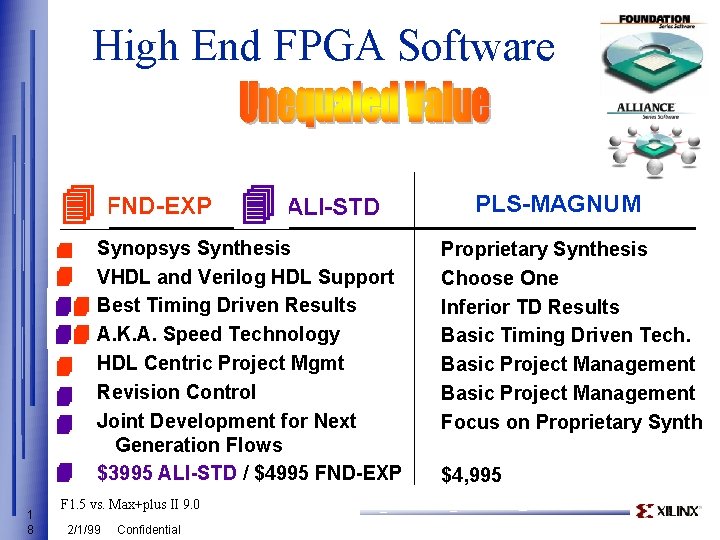

High End FPGA Software 4 FND-EXP 4 ALI-STD 4 4 44 44 4 4 1 8 Synopsys Synthesis VHDL and Verilog HDL Support Best Timing Driven Results A. K. A. Speed Technology HDL Centric Project Mgmt Revision Control Joint Development for Next Generation Flows $3995 ALI-STD / $4995 FND-EXP F 1. 5 vs. Max+plus II 9. 0 2/1/99 Confidential PLS-MAGNUM Proprietary Synthesis Choose One Inferior TD Results Basic Timing Driven Tech. Basic Project Management Focus on Proprietary Synth $4, 995

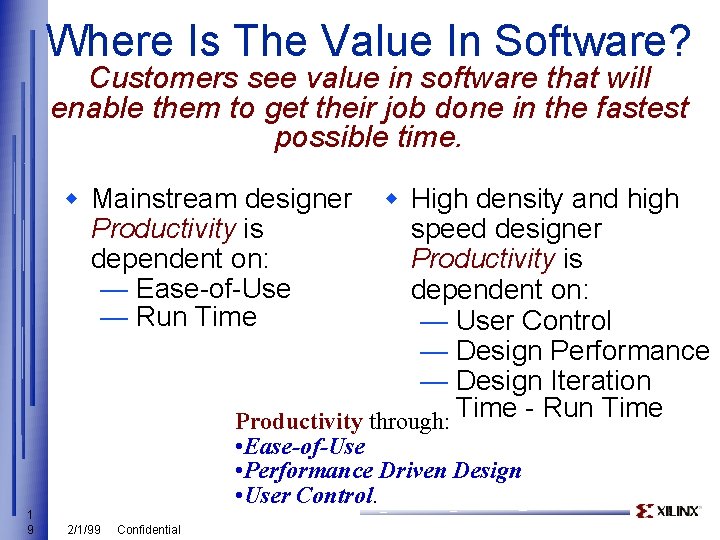

Where Is The Value In Software? Customers see value in software that will enable them to get their job done in the fastest possible time. w Mainstream designer Productivity is dependent on: — Ease-of-Use — Run Time w High density and high speed designer Productivity is dependent on: — User Control — Design Performance — Design Iteration Productivity through: Time - Run Time • Ease-of-Use • Performance Driven Design • User Control. 1 9 2/1/99 Confidential

Where’s the Value in 1. 5? Ease of Use w Constraints Editor — Simple control over powerful constraints w Automatic Pin Locking — When you’re ready for board layout w Improved Reporting — Important information first 2 0 2/1/99 Confidential

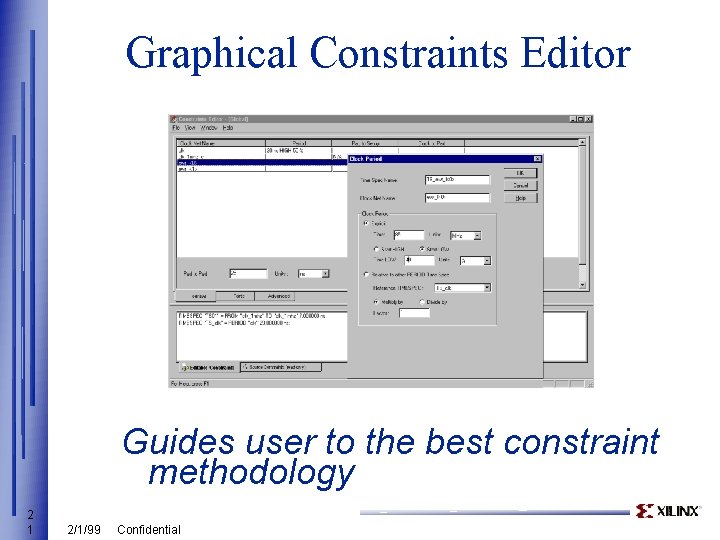

Graphical Constraints Editor Guides user to the best constraint methodology 2 1 2/1/99 Confidential

Where’s the Value in 1. 5? Performance w Minimum Delays w Temperature and Voltage Prorating — Faster performance at more optimal operating conditions w Dramatic Improvements to PAR 2 2 2/1/99 Confidential

Where’s the Value in 1. 5? Performance - PAR Improvements w Average 2 -3 x runtime improvement, 10 x on some designs w Faster timing analysis with K-path algorithm w Achieves higher clock rates more easily All this means…. More Turns Per Day Faster Design Cycles 2 3 2/1/99 Confidential

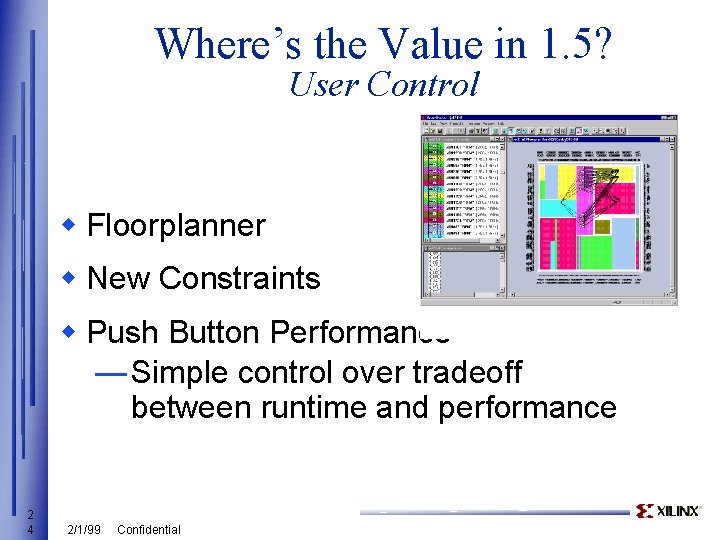

Where’s the Value in 1. 5? User Control w Floorplanner w New Constraints w Push Button Performance — Simple control over tradeoff between runtime and performance 2 4 2/1/99 Confidential

Foundation & Alliance Series Unparalleled Productivity Key Features in Version 1. 5 2 5 w 4 New FPGA/CPLD Families w 50% Runtime Reduction w Graphical Constraints Editor w Floorplanner w Automatic Pin Locking w 6 x Faster Timing Analysis (Kpaths algorithm) w New Reporting of Minimum Delays w Voltage and Temperature Speed Pro- 2/1/99 Confidential

Key Messages For Alliance w Standards Based Design Interfaces Allows customers to work in their chosen EDA environment. w A. K. A. speedtm TECHNOLOGY Faster compile times and increased clock speed lets customers meet their specifications and get their product to market more quickly. w Integrated Core Generator Software And Logi. BLOX Customers can achieve higher performance and get their designs done faster. w World Class Technical Support Instant support over the Web and via the phone to assist customers in completing designs. 2 6 2/1/99 Confidential

Key Messages For Foundation w Complete Front-To-Back Design Environment The tightly integrated tool set makes it easy for customer to and use the tools. w Powerful VHDL And Verilog Synthesis - Synopsys FPGA Express Robust language support and optimization technology allows customers to get the most speed out of their design. w Graphical HDL Editor And Integrated Language Wizard Simple graphical tools help to reduce the time it takes for customers to complete their design. w World Class Technical Support Instant support over the Web and via the phone to assist customers in completing designs. 2 7 learn 2/1/99 Confidential

- Slides: 27