Synchronous Design Techniques 2003 Xilinx Inc All Rights

- Slides: 27

Synchronous Design Techniques © 2003 Xilinx, Inc. All Rights Reserved

Objectives After completing this module, you will be able to: • • Use hierarchy effectively Increase circuit reliability and performance by applying synchronous design techniques Synchronous Design Techniques 11 - 3 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Outline • • • Synchronous Design Techniques 11 - 4 Hierarchical Design Synchronous Design for Xilinx FPGAs Summary © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

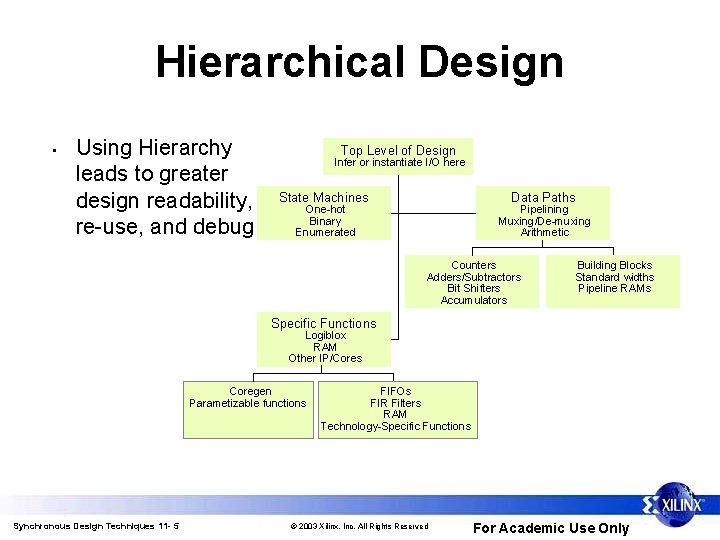

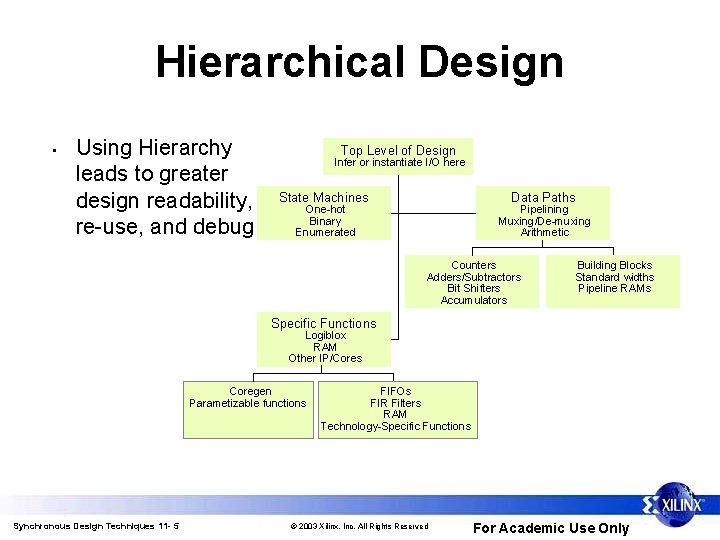

Hierarchical Design • Using Hierarchy leads to greater design readability, re-use, and debug Top Level of Design Infer or instantiate I/O here State Machines Data Paths One-hot Binary Enumerated Pipelining Muxing/De-muxing Arithmetic Counters Adders/Subtractors Bit Shifters Accumulators Building Blocks Standard widths Pipeline RAMs Specific Functions Logiblox RAM Other IP/Cores Coregen Parametizable functions Synchronous Design Techniques 11 - 5 FIFOs FIR Filters RAM Technology-Specific Functions © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Benefits of Using Hierarchy • Design readability – – • Easier to understand design functionality and data flow Easier to debug Easy to reuse parts of a design Synchronous Design Techniques 11 - 6 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

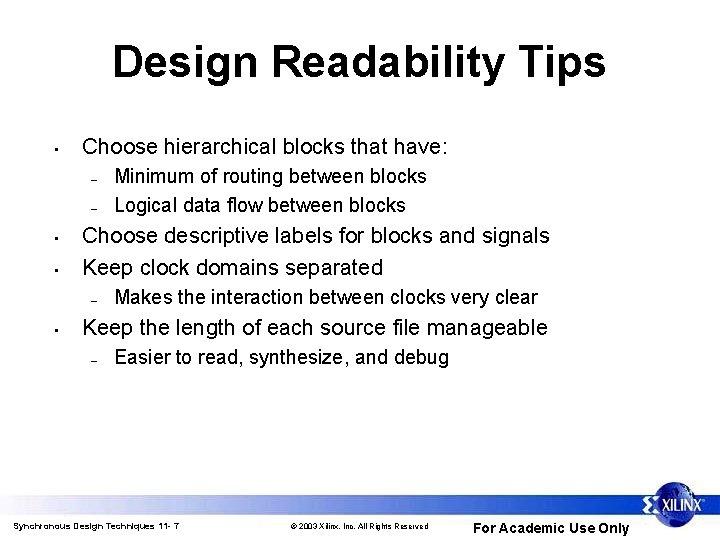

Design Readability Tips • Choose hierarchical blocks that have: – – • • Choose descriptive labels for blocks and signals Keep clock domains separated – • Minimum of routing between blocks Logical data flow between blocks Makes the interaction between clocks very clear Keep the length of each source file manageable – Easier to read, synthesize, and debug Synchronous Design Techniques 11 - 7 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

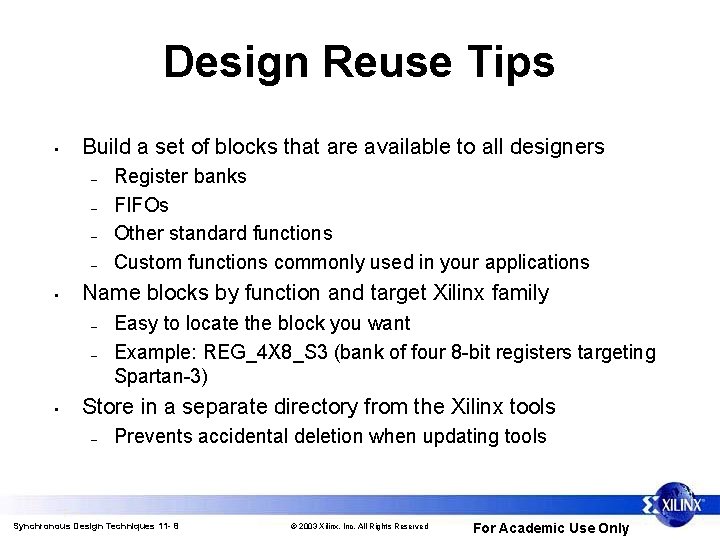

Design Reuse Tips • Build a set of blocks that are available to all designers – – • Name blocks by function and target Xilinx family – – • Register banks FIFOs Other standard functions Custom functions commonly used in your applications Easy to locate the block you want Example: REG_4 X 8_S 3 (bank of four 8 -bit registers targeting Spartan-3) Store in a separate directory from the Xilinx tools – Prevents accidental deletion when updating tools Synchronous Design Techniques 11 - 8 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Outline • • • Synchronous Design Techniques 11 - 9 Hierarchical Design Synchronous Design for Xilinx FPGAs Summary © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

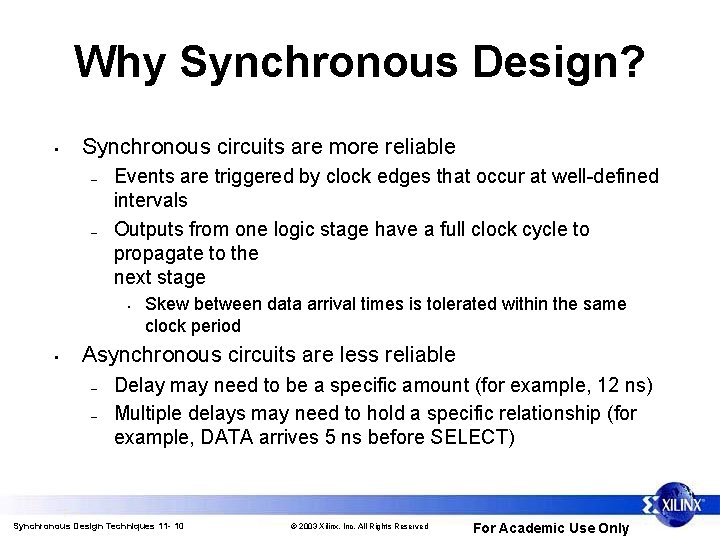

Why Synchronous Design? • Synchronous circuits are more reliable – – Events are triggered by clock edges that occur at well-defined intervals Outputs from one logic stage have a full clock cycle to propagate to the next stage • • Skew between data arrival times is tolerated within the same clock period Asynchronous circuits are less reliable – – Delay may need to be a specific amount (for example, 12 ns) Multiple delays may need to hold a specific relationship (for example, DATA arrives 5 ns before SELECT) Synchronous Design Techniques 11 - 10 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Asynchronous Design: Case Studies • The design I created two years ago no longer works. What did Xilinx change in their FPGAs? – – • SRAM process improvements and geometry shrinks increase speed Normal variations between wafer lots My design passes a timing simulation test but fails in-circuit. Is the timing simulation accurate? YES – – Timing simulation uses worst-case delays Actual board-level conditions are usually better Synchronous Design Techniques 11 - 11 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

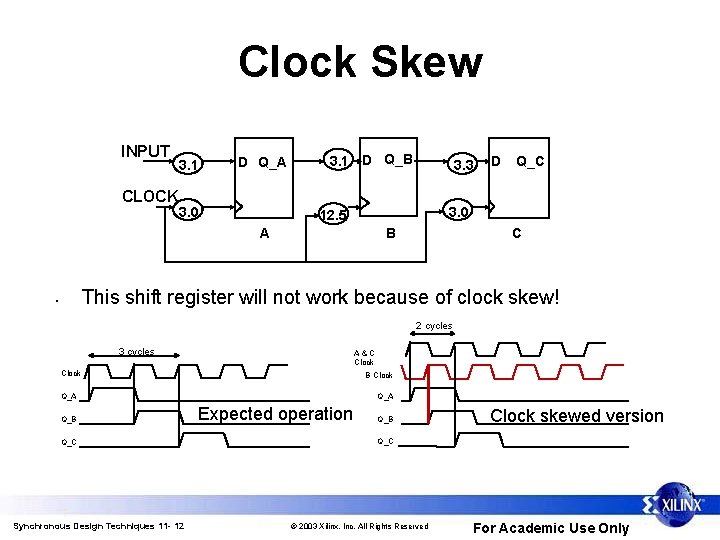

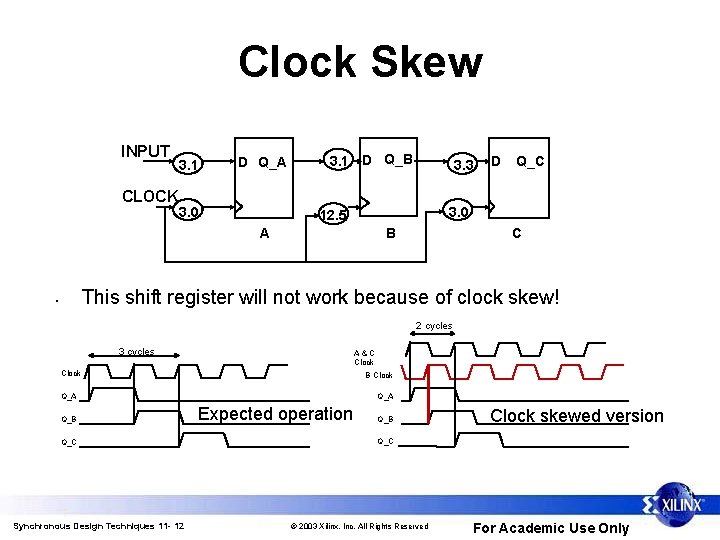

Clock Skew INPUT CLOCK 3. 1 D Q_A 3. 0 3. 1 D Q_B 3. 3 D Q_C 3. 0 12. 5 A B C This shift register will not work because of clock skew! • 2 cycles 3 cycles A&C Clock B Clock Q_A Q_B Q_C Synchronous Design Techniques 11 - 12 Q_A Expected operation Q_B Clock skewed version Q_C © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

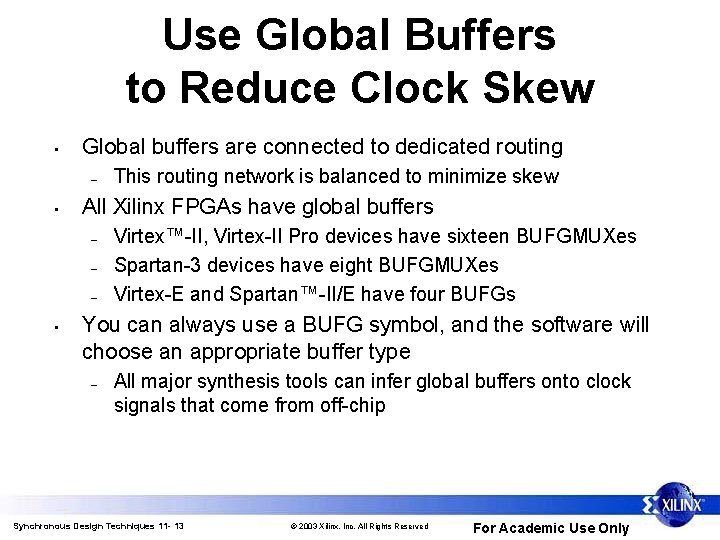

Use Global Buffers to Reduce Clock Skew • Global buffers are connected to dedicated routing – • All Xilinx FPGAs have global buffers – – – • This routing network is balanced to minimize skew Virtex™-II, Virtex-II Pro devices have sixteen BUFGMUXes Spartan-3 devices have eight BUFGMUXes Virtex-E and Spartan™-II/E have four BUFGs You can always use a BUFG symbol, and the software will choose an appropriate buffer type – All major synthesis tools can infer global buffers onto clock signals that come from off-chip Synchronous Design Techniques 11 - 13 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

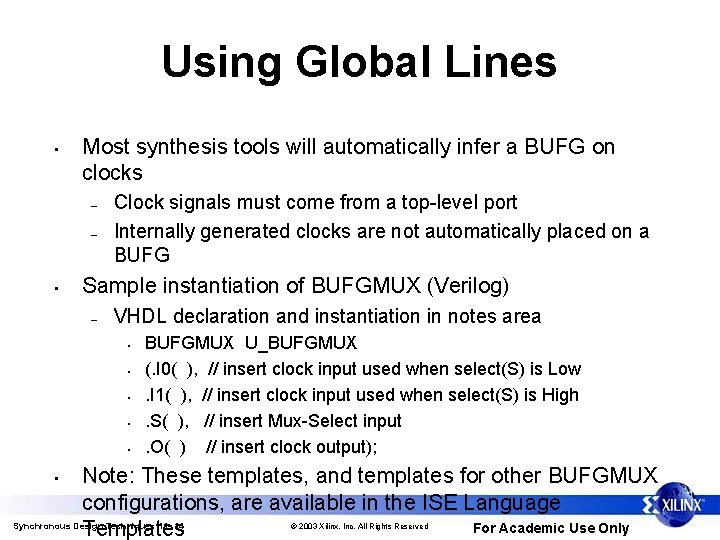

Using Global Lines • Most synthesis tools will automatically infer a BUFG on clocks – – • Clock signals must come from a top-level port Internally generated clocks are not automatically placed on a BUFG Sample instantiation of BUFGMUX (Verilog) – VHDL declaration and instantiation in notes area • • • BUFGMUX U_BUFGMUX (. I 0( ), // insert clock input used when select(S) is Low. I 1( ), // insert clock input used when select(S) is High. S( ), // insert Mux-Select input. O( ) // insert clock output); Note: These templates, and templates for other BUFGMUX configurations, are available in the ISE Language Synchronous Design Techniques 11 - 14 For Academic Use Only Templates • © 2003 Xilinx, Inc. All Rights Reserved

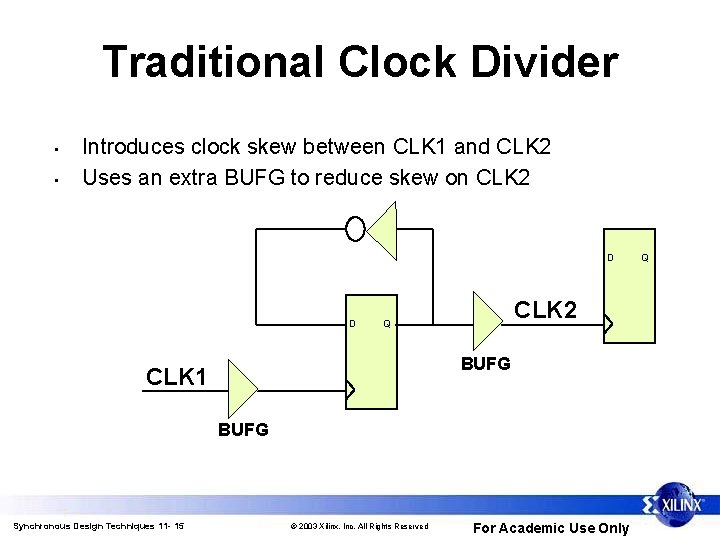

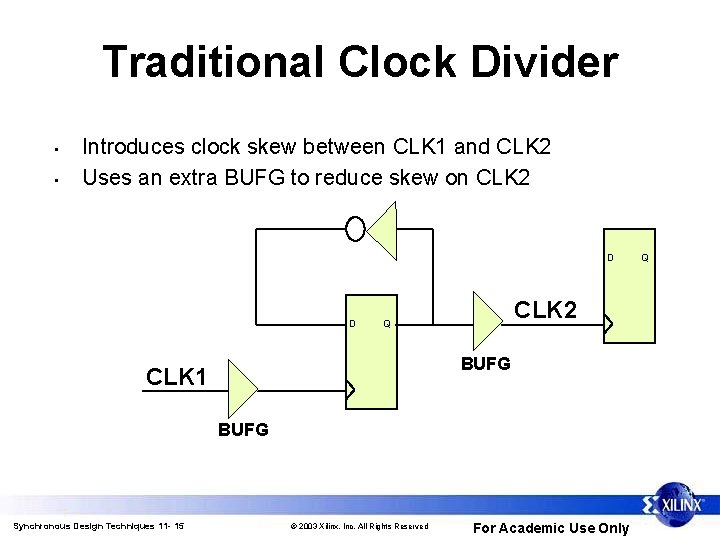

Traditional Clock Divider • • Introduces clock skew between CLK 1 and CLK 2 Uses an extra BUFG to reduce skew on CLK 2 D D CLK 2 Q BUFG CLK 1 BUFG Synchronous Design Techniques 11 - 15 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only Q

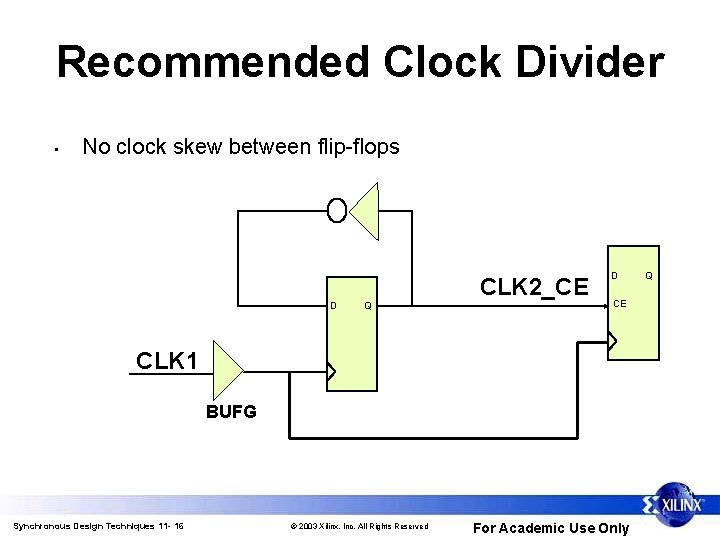

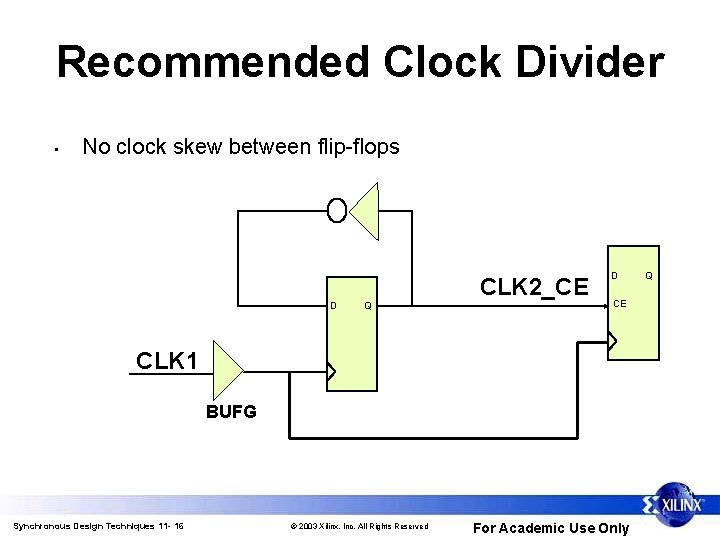

Recommended Clock Divider • No clock skew between flip-flops D Q CLK 2_CE D CE CLK 1 BUFG Synchronous Design Techniques 11 - 16 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only Q

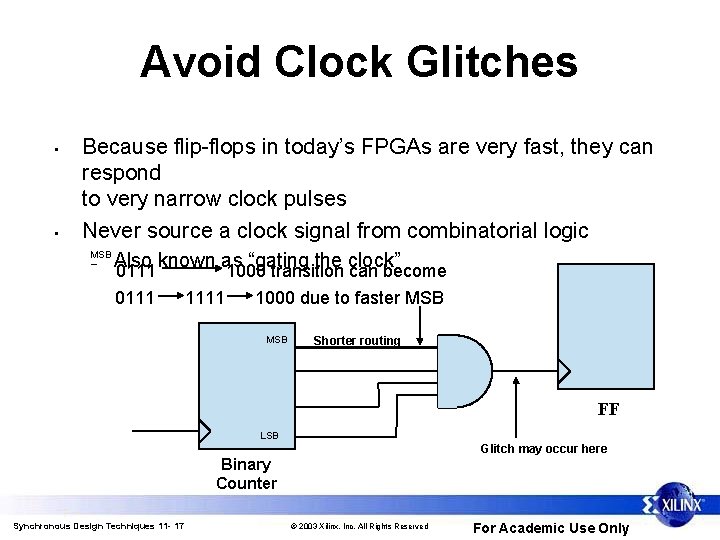

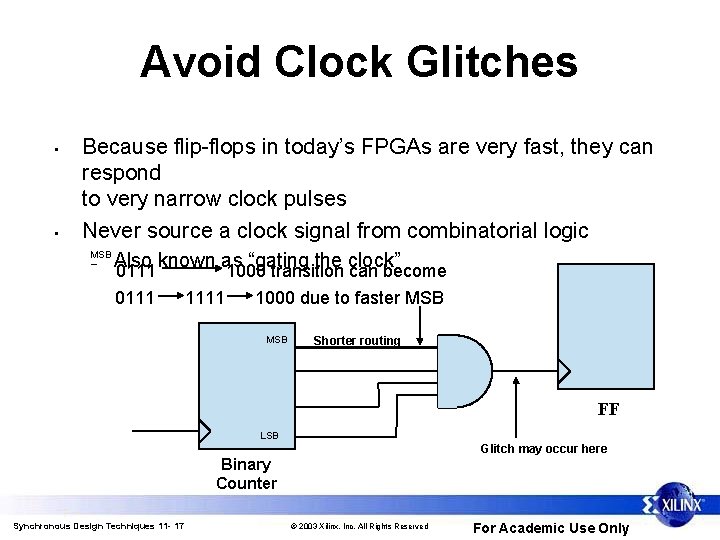

Avoid Clock Glitches • • Because flip-flops in today’s FPGAs are very fast, they can respond to very narrow clock pulses Never source a clock signal from combinatorial logic MSB – Also known as “gating the clock” 0111 1000 transition can become 0111 1000 due to faster MSB Shorter routing FF LSB Glitch may occur here Binary Counter Synchronous Design Techniques 11 - 17 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

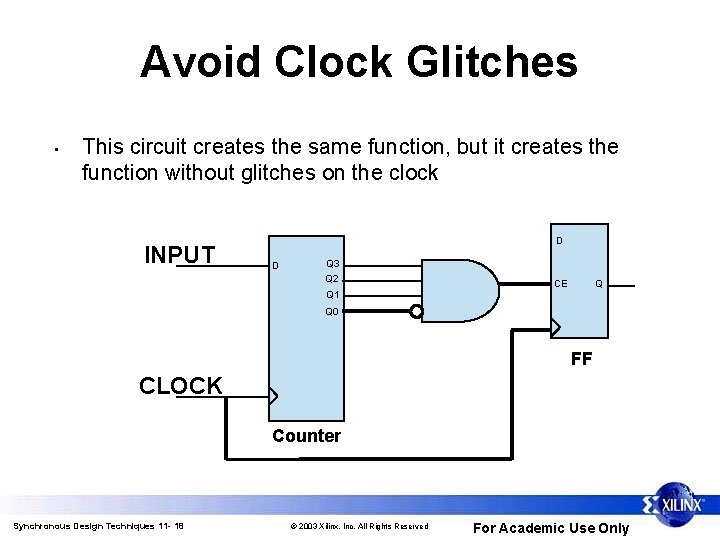

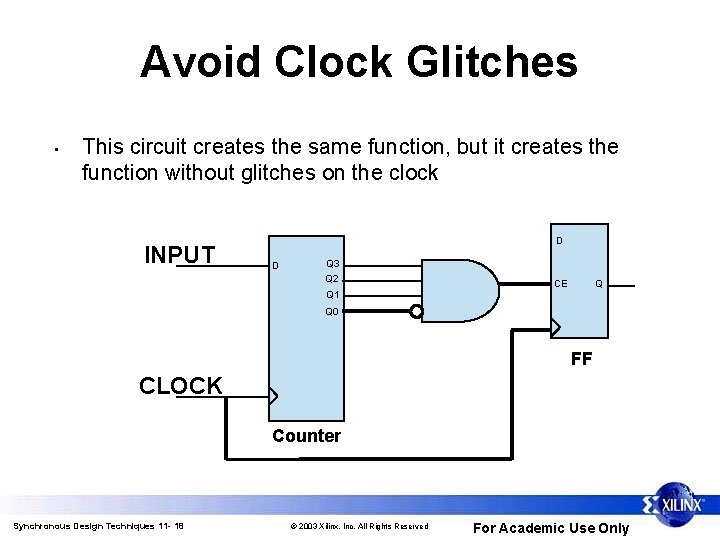

Avoid Clock Glitches • This circuit creates the same function, but it creates the function without glitches on the clock INPUT D D Q 3 Q 2 Q 1 Q CE Q 0 FF CLOCK Counter Synchronous Design Techniques 11 - 18 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

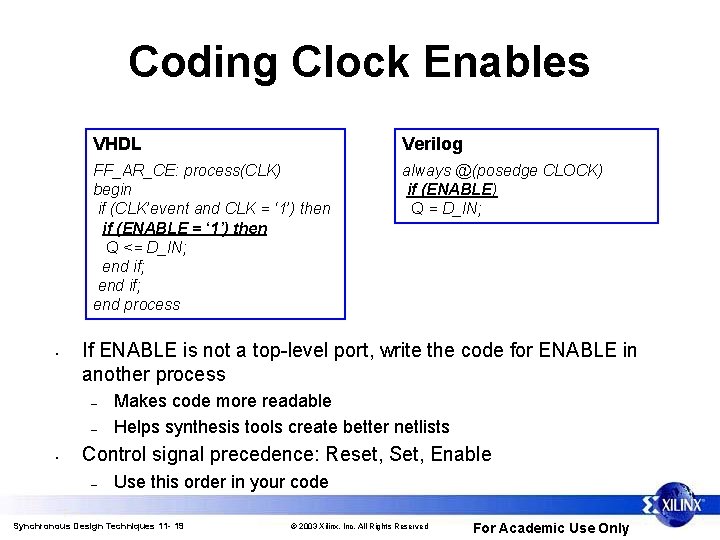

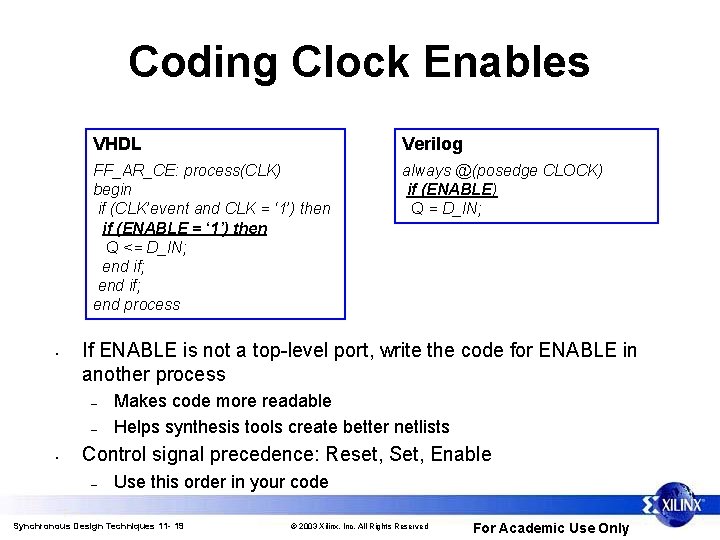

Coding Clock Enables • VHDL Verilog FF_AR_CE: process(CLK) begin if (CLK’event and CLK = ‘ 1’) then if (ENABLE = ‘ 1’) then Q <= D_IN; end if; end process always @(posedge CLOCK) if (ENABLE) Q = D_IN; If ENABLE is not a top-level port, write the code for ENABLE in another process – – • Makes code more readable Helps synthesis tools create better netlists Control signal precedence: Reset, Set, Enable – Use this order in your code Synchronous Design Techniques 11 - 19 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

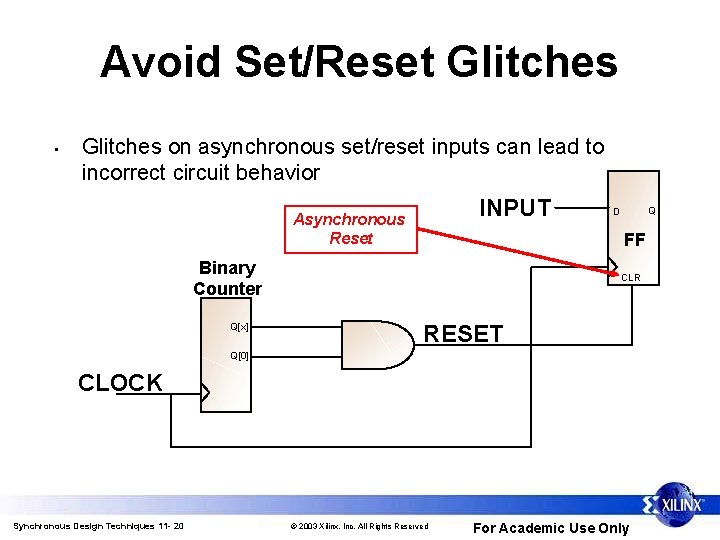

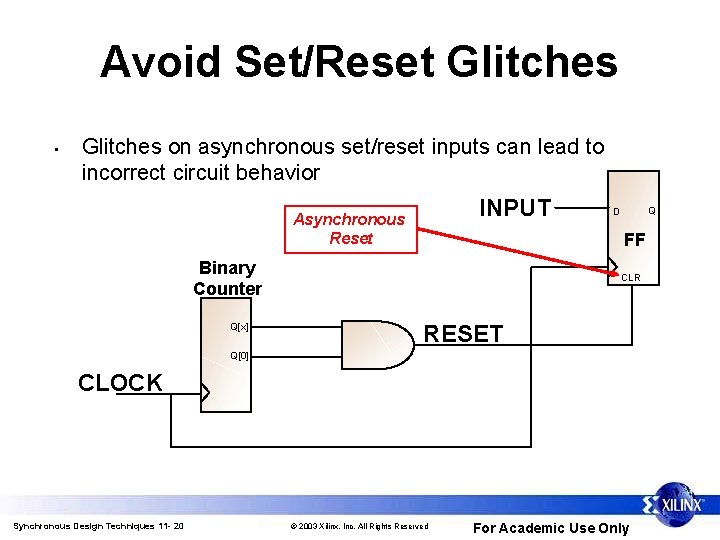

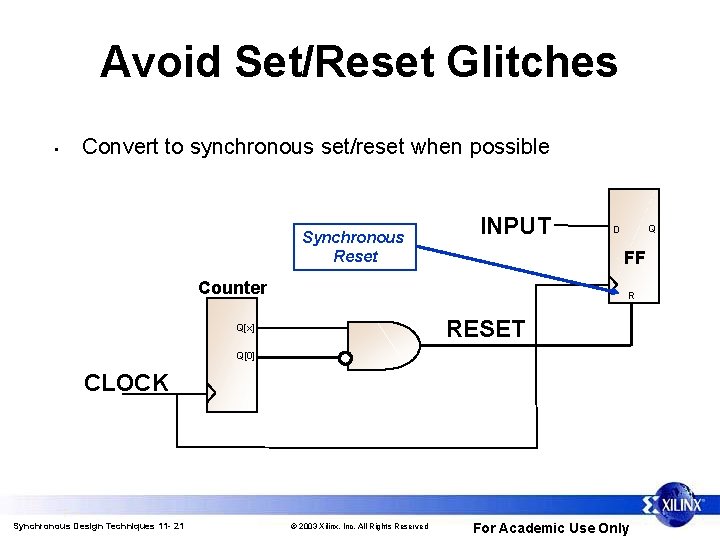

Avoid Set/Reset Glitches • Glitches on asynchronous set/reset inputs can lead to incorrect circuit behavior INPUT Asynchronous Reset FF Binary Counter Q[x] Q D CLR RESET Q[0] CLOCK Synchronous Design Techniques 11 - 20 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

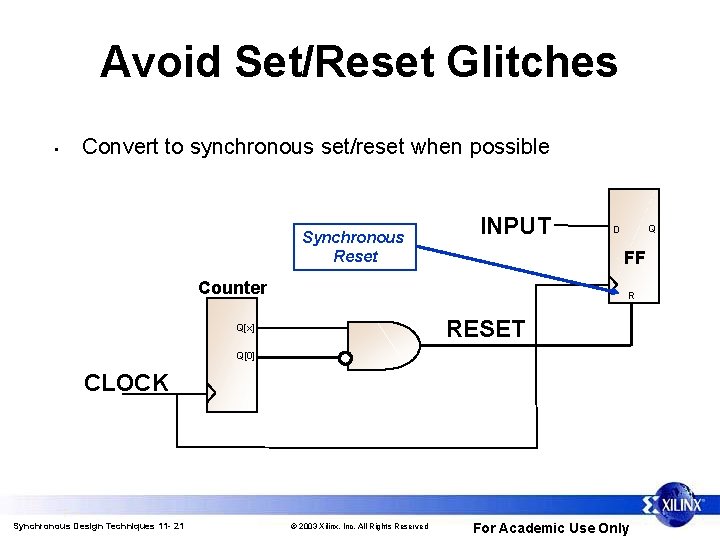

Avoid Set/Reset Glitches • Convert to synchronous set/reset when possible Synchronous Reset INPUT Q D FF Counter R RESET Q[x] Q[0] CLOCK Synchronous Design Techniques 11 - 21 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

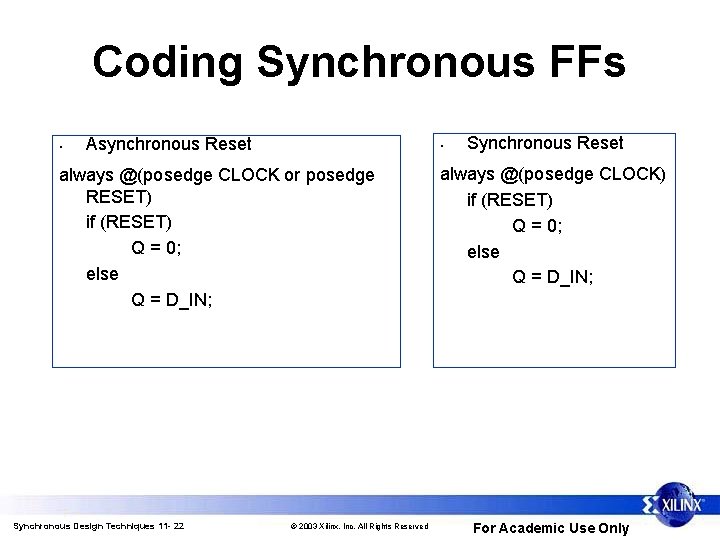

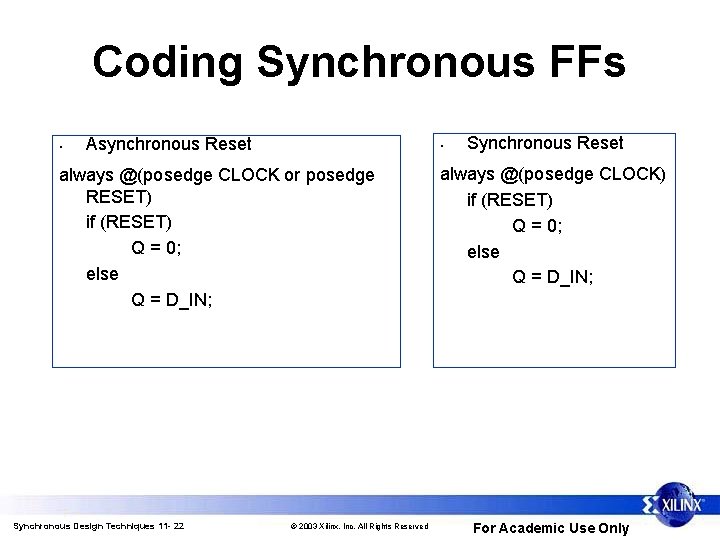

Coding Synchronous FFs • Asynchronous Reset • always @(posedge CLOCK or posedge RESET) if (RESET) Q = 0; else Q = D_IN; Synchronous Design Techniques 11 - 22 © 2003 Xilinx, Inc. All Rights Reserved Synchronous Reset always @(posedge CLOCK) if (RESET) Q = 0; else Q = D_IN; For Academic Use Only

Outline • • • Synchronous Design Techniques 11 - 23 Hierarchical Design Synchronous Design for Xilinx FPGAs Summary © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Skills Check Synchronous Design Techniques 11 - 24 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Review Questions • List two benefits of hierarchical design • Why should you use global buffers for your clock signals? • What is an alternative to gating a clock? Synchronous Design Techniques 11 - 25 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Answers • List two benefits of hierarchical design – – • Why should you use global buffers for your clock signals? – • Design readability Design reuse To reduce clock skew What is an alternative to gating a clock? – Use a clock enable Synchronous Design Techniques 11 - 26 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Summary • • • Proper use of hierarchy aids design readability and debug Synchronous designs are more reliable than asynchronous designs FPGA design tips – – Global clock buffers and DLLs eliminate skew Avoid glitches on clocks and asynchronous set/resets Synchronous Design Techniques 11 - 27 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Where Can I Learn More? • Application notes on http: //support. xilinx. com – • Under the Design tab, click App Notes Software documentation – – – Development System Reference Guide, Chapter 2: Design Flow, FPGA Design Techniques section Libraries Guide Documentation for your synthesis tool Synchronous Design Techniques 11 - 28 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only