Xilinx CPLD Solutions Roadmap Performance Density CPLD Application

- Slides: 8

Xilinx CPLD Solutions Roadmap ®

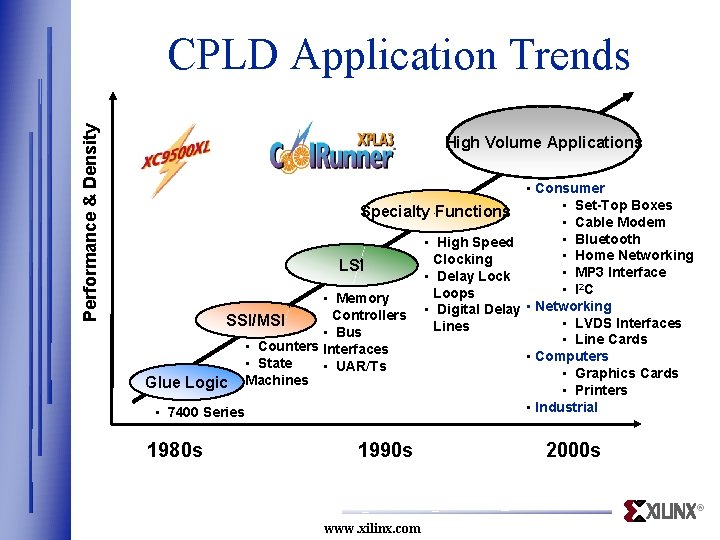

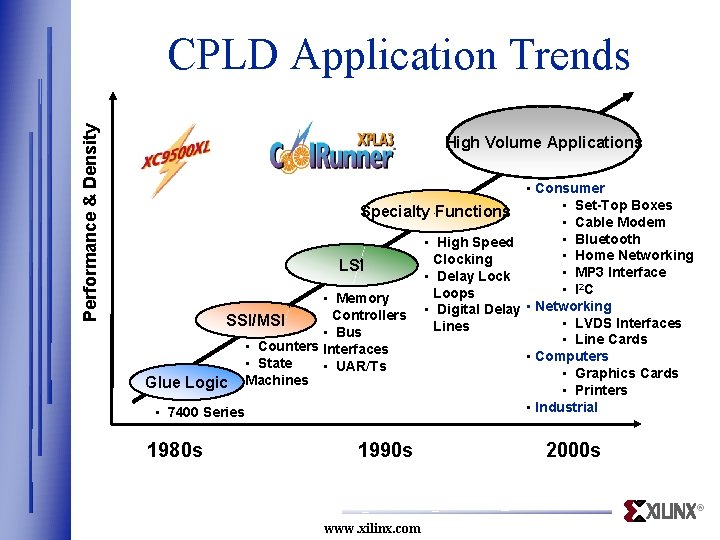

Performance & Density CPLD Application Trends High Volume Applications • Consumer • Set-Top Boxes Specialty Functions • Cable Modem • Bluetooth • High Speed • Home Networking Clocking LSI • MP 3 Interface • Delay Lock • I 2 C Loops • Memory • Digital Delay • Networking Controllers SSI/MSI • LVDS Interfaces Lines • Bus • Line Cards • Counters Interfaces • Computers • State • UAR/Ts • Graphics Cards Glue Logic Machines • Printers • Industrial • 7400 Series 1980 s 1990 s 2000 s ® www. xilinx. com

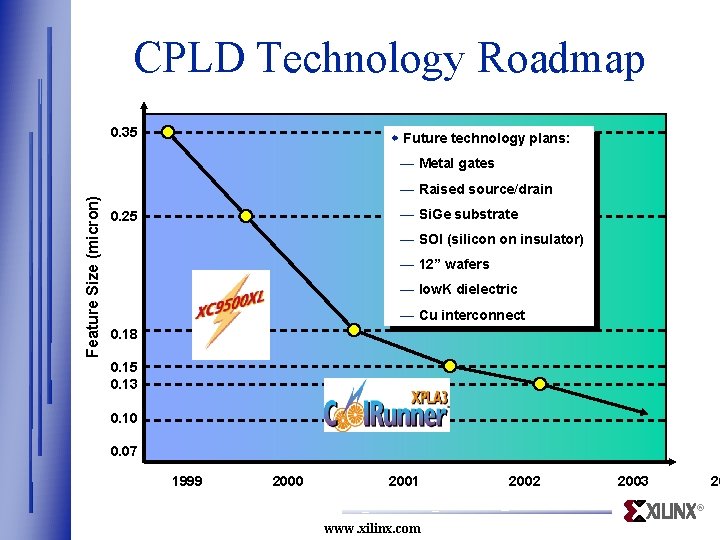

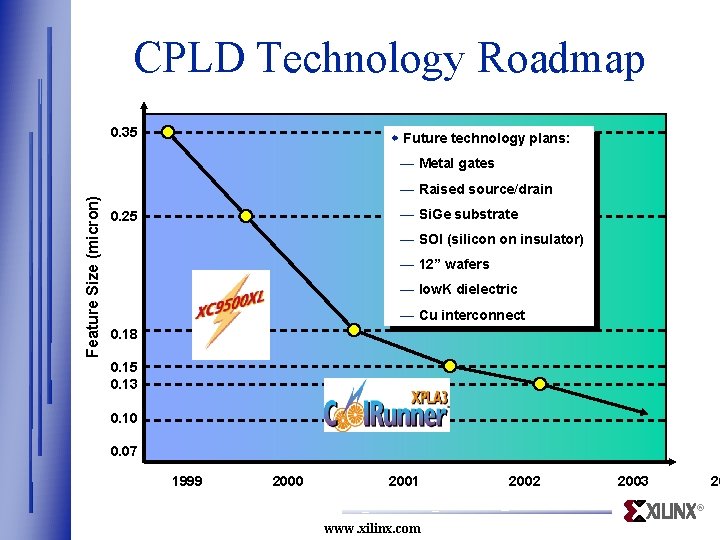

CPLD Technology Roadmap 0. 35 w Future technology plans: Feature Size (micron) — Metal gates — Raised source/drain — Si. Ge substrate 0. 25 — SOI (silicon on insulator) — 12” wafers — low. K dielectric — Cu interconnect 0. 18 0. 15 0. 13 0. 10 0. 07 1999 2000 2001 2002 2003 20 ® www. xilinx. com

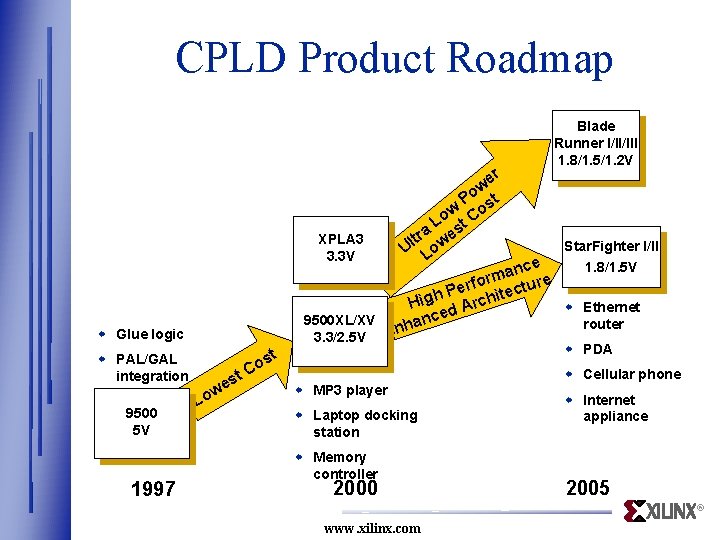

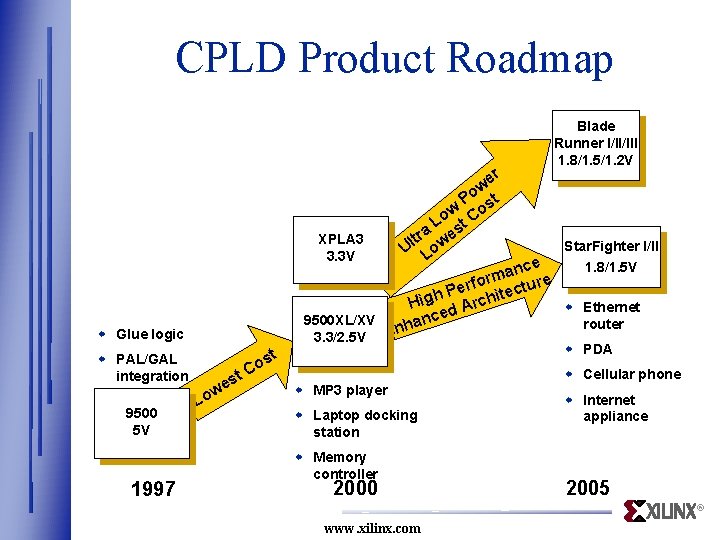

CPLD Product Roadmap Blade Runner I/II/III 1. 8/1. 5/1. 2 V r e w Po st w Co o L st XPLA 3 tl ra we Star. Fighter I/II U Lo 3. 3 V 1. 8/1. 5 V nce a m r e o r erf itectu P h Hig d Arch w Ethernet ce n 9500 XL/XV a router Enh w Glue logic 3. 3/2. 5 V w PAL/GAL integration 9500 5 V 1997 Lo w t es t os C w MP 3 player w Laptop docking station w Memory controller 2000 w PDA w Cellular phone w Internet appliance 2005 ® www. xilinx. com

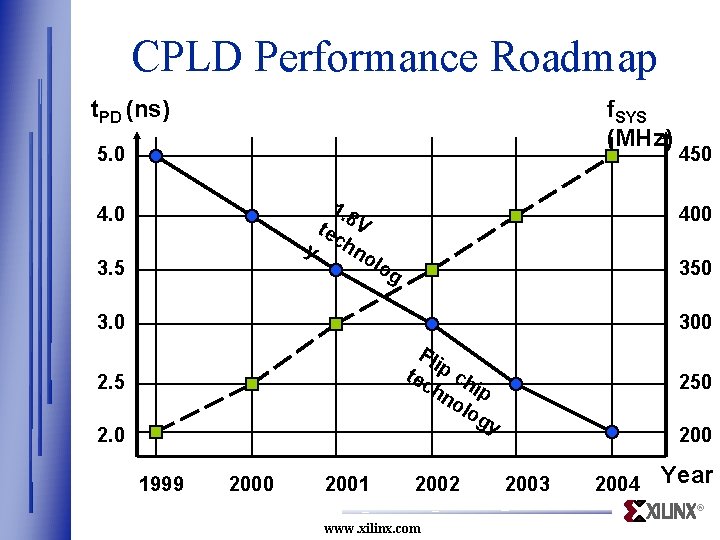

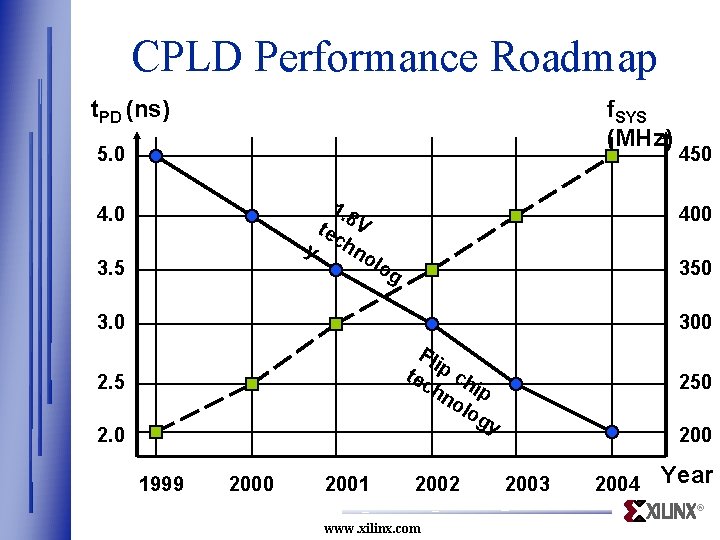

CPLD Performance Roadmap t. PD (ns) f. SYS (MHz) 5. 0 1. 8 tec V y hno lo 4. 0 3. 5 450 400 350 g 3. 0 300 Fli tec p ch hn ip olo gy 2. 5 2. 0 1999 2000 2001 2002 250 2003 2004 Year ® www. xilinx. com

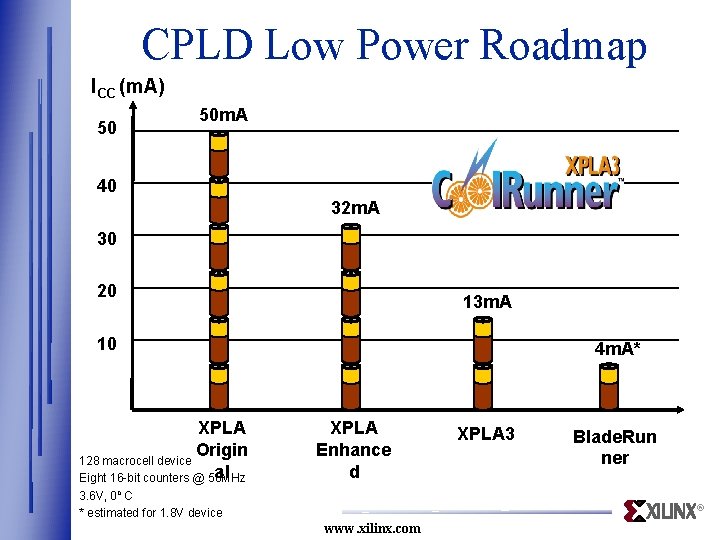

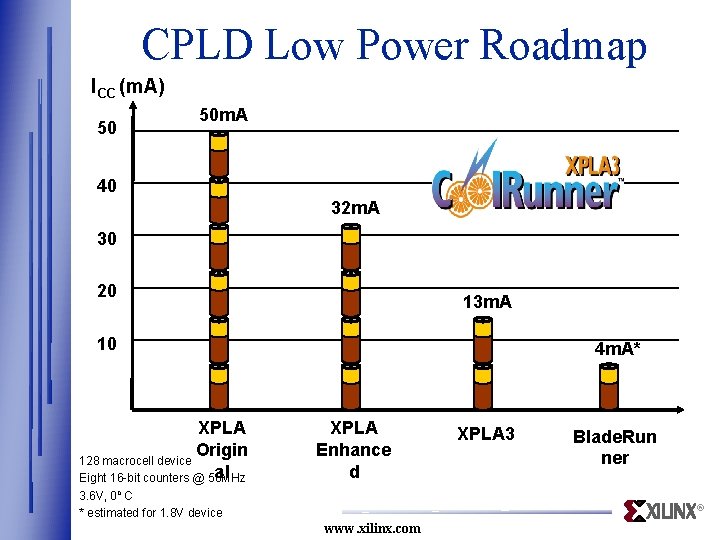

CPLD Low Power Roadmap ICC (m. A) 50 50 m. A 40 32 m. A 30 20 13 m. A 10 XPLA Origin 128 macrocell device al Eight 16 -bit counters @ 50 MHz 4 m. A* XPLA Enhance d 3. 6 V, 0 o C * estimated for 1. 8 V device XPLA 3 Blade. Run ner ® www. xilinx. com

CPLD Product Support Plan XC 9500 XL 0. 5 u (5 V) 0. 35 u (3. 3 V) XC 9500 XV XPLA 3 0. 25 u (2. 5 V) 0. 35 u (3. 3 V) Blade. Run 0. 18 u ner (1. 8 V) Star. Fighte 0. 18 u r (1. 8 V) Blade. Runne r II 0. 15 u (1. 5 V) Star. Fighte r II 1999 2000 2001 2002 www. xilinx. com 2003 0. 15 u (1. 5 V) ®

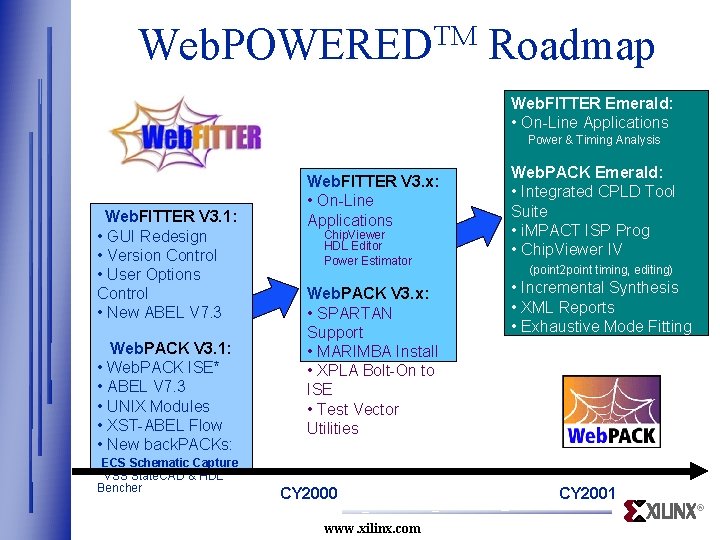

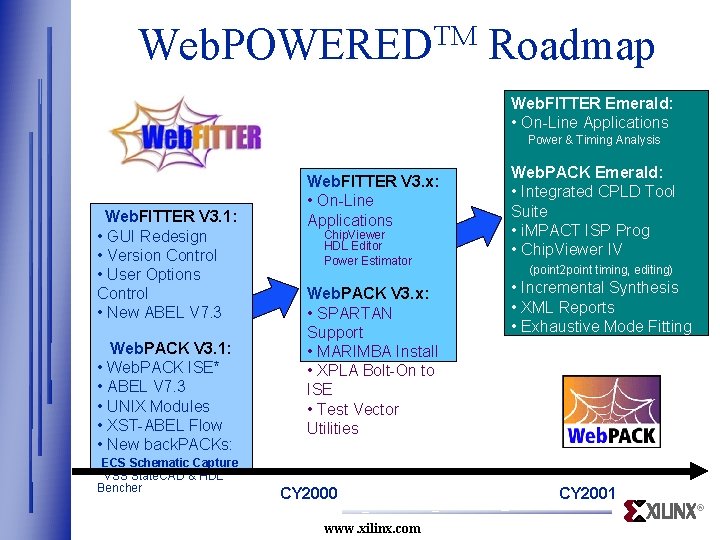

Web. POWEREDTM Roadmap Web. FITTER Emerald: • On-Line Applications Power & Timing Analysis Web. FITTER V 3. 1: • GUI Redesign • Version Control • User Options Control • New ABEL V 7. 3 Web. PACK V 3. 1: • Web. PACK ISE* • ABEL V 7. 3 • UNIX Modules • XST-ABEL Flow • New back. PACKs: ECS Schematic Capture VSS State. CAD & HDL Bencher Web. FITTER V 3. x: • On-Line Applications Chip. Viewer HDL Editor Power Estimator Web. PACK V 3. x: • SPARTAN Support • MARIMBA Install • XPLA Bolt-On to ISE • Test Vector Utilities CY 2000 www. xilinx. com Web. PACK Emerald: • Integrated CPLD Tool Suite • i. MPACT ISP Prog • Chip. Viewer IV (point 2 point timing, editing) • Incremental Synthesis • XML Reports • Exhaustive Mode Fitting (Timing & Area) CY 2001 ®