Xilinx University Program Agenda u u u 2

- Slides: 27

Xilinx University Program

Agenda u u u 2 Xilinx University Program Teaching Tools Advanced Teaching Tools Xilinx Confidential

Xilinx University Program (XUP) Group Mission To facilitate the teaching of engineering curriculum using PLDs as the target solution of choice. (To make your job easier) 3 Xilinx Confidential

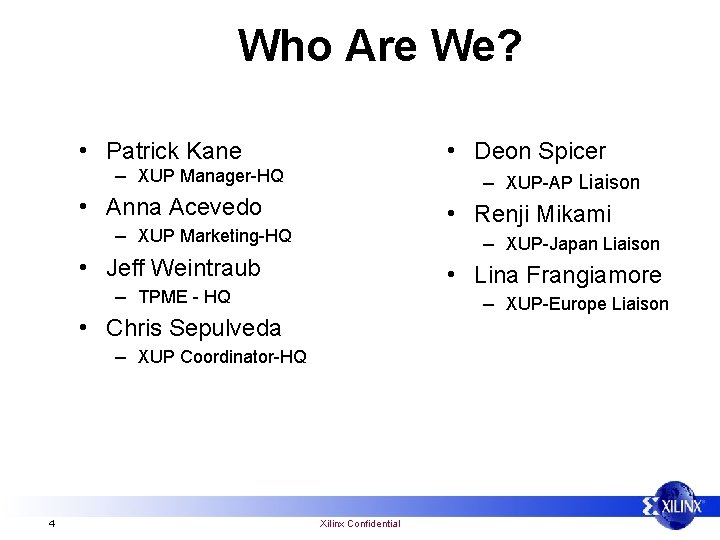

Who Are We? • Patrick Kane • Deon Spicer – XUP Manager-HQ – XUP-AP Liaison • Anna Acevedo • Renji Mikami – XUP Marketing-HQ – XUP-Japan Liaison • Jeff Weintraub • Lina Frangiamore – TPME - HQ – XUP-Europe Liaison • Chris Sepulveda – XUP Coordinator-HQ 4 Xilinx Confidential

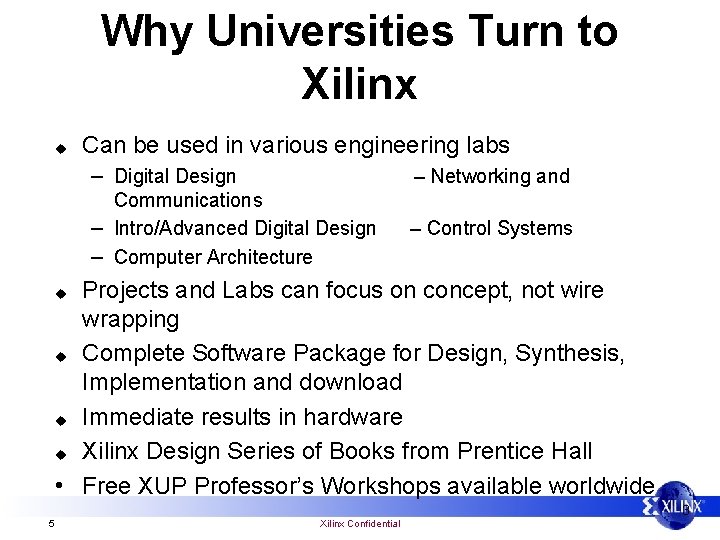

Why Universities Turn to Xilinx u Can be used in various engineering labs – Digital Design – Networking and Communications – Intro/Advanced Digital Design – Computer Architecture – Control Systems Projects and Labs can focus on concept, not wire wrapping u Complete Software Package for Design, Synthesis, Implementation and download u Immediate results in hardware u Xilinx Design Series of Books from Prentice Hall • Free XUP Professor’s Workshops available worldwide u 3 5 Xilinx Confidential

XUP Programs and Products • • • Extensive Donation Program XUP Professor Workshops Sponsor Design Contests Research Collaboration Web Sites – university. xilinx. com – xup. msu. edu • Government Sponsorship • Prentice Hall relationship 6 Xilinx Confidential

XUP Programs and Products XUP Donation Policy “If a new or expanded course with lab or a research project is being added and funding is not adequate to purchase the required products at the University Program discounts, Xilinx encourages any university or college to submit a donation request. ” To Purchase or To Request a Donation What's Practical for you? If you have sufficient budget to purchase Xilinx software, development boards, and/or chips, then we encourage you to do so. We offer significant discounts for Xilinx software and Xilinx development boards. However, we recognize that very often, schools simply do not have the funding even for the discounted products. In some cases, a school might have some funding, but not enough to obtain everything that is needed for the lab. We encourage you to make the choice that you feel is right for your situation. Most importantly, if money is any barrier to your immediate use of Xilinx products, you should request a donation for what you need. 7 Xilinx Confidential

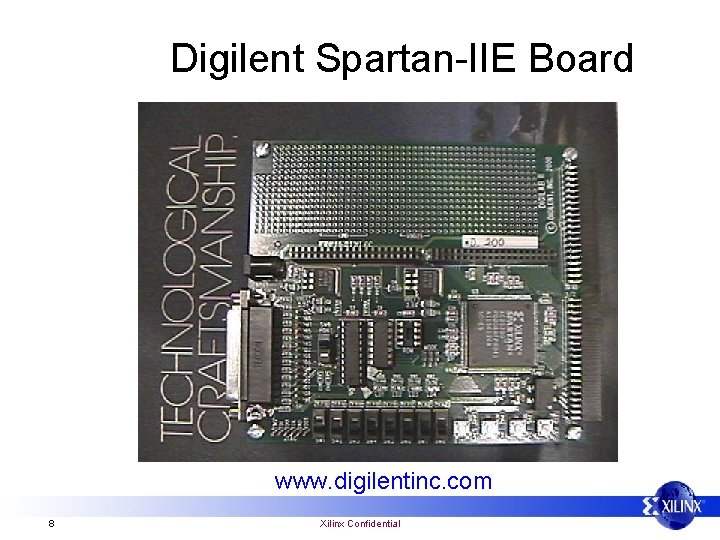

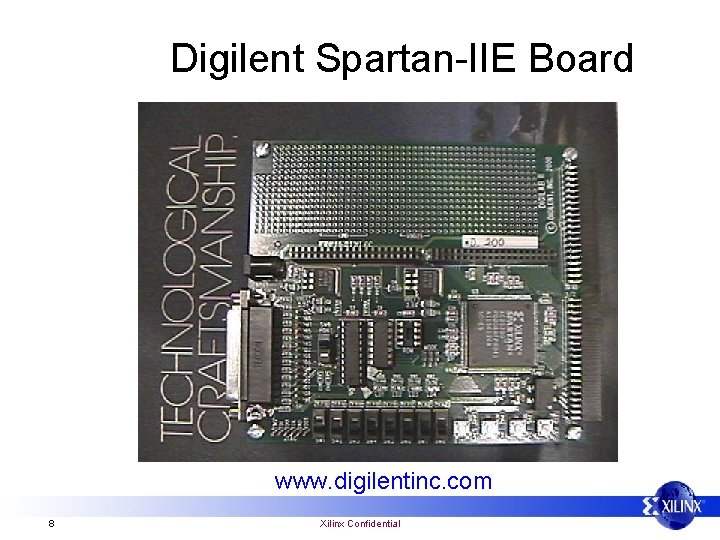

Digilent Spartan-IIE Board www. digilentinc. com 8 Xilinx Confidential

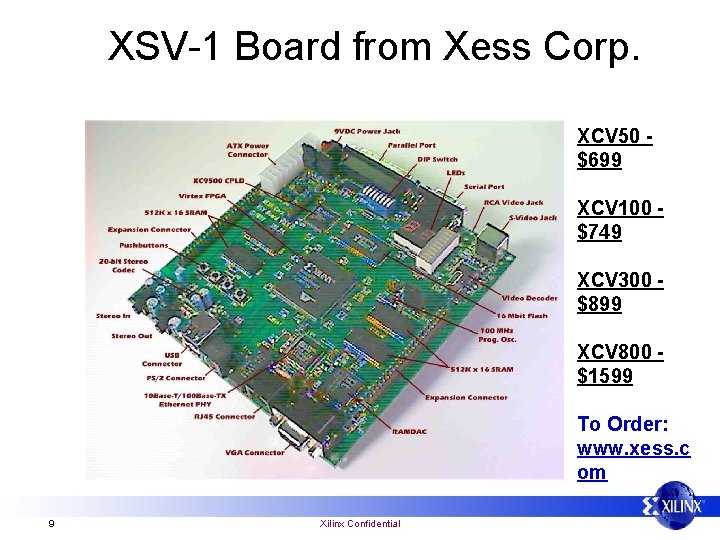

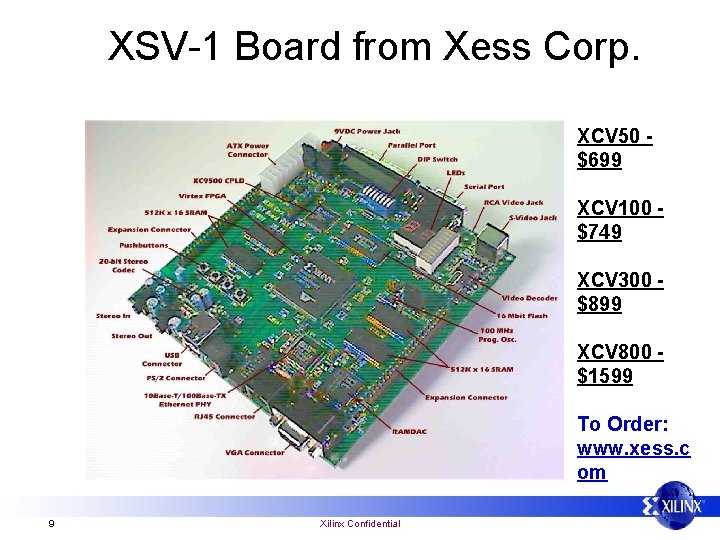

XSV-1 Board from Xess Corp. XCV 50 $699 XCV 100 $749 XCV 300 $899 XCV 800 $1599 To Order: www. xess. c om 9 Xilinx Confidential

Xilinx Student Edition v 4. 2 i u Includes – v 4. 2 i ISE for students’ computers – VHDL and Verilog synthesis with XST – Includes CPLDs (XC 9500, Cool. Runner-II) and FPGAs (Spartan -II/E, Virtex(E), Virtex-II Pro) up to 300 K gates u u u Sold through university bookstores. Also available at www. prenhall. com and www. Amazon. com Bundled with Xilinx Design Series or $55 stand alone New Web Pack Software - free download – Includes CPLDs (XC 9500, Cool. Runner-II) and FPGAs (Spartan -II/E, Virtex(E), Virtex-II Pro) up to 300 K gates VHDL, edition Verilog Note: Xilinx– student software is for student’s personal use and not to be installed in university labs 10 Xilinx Confidential

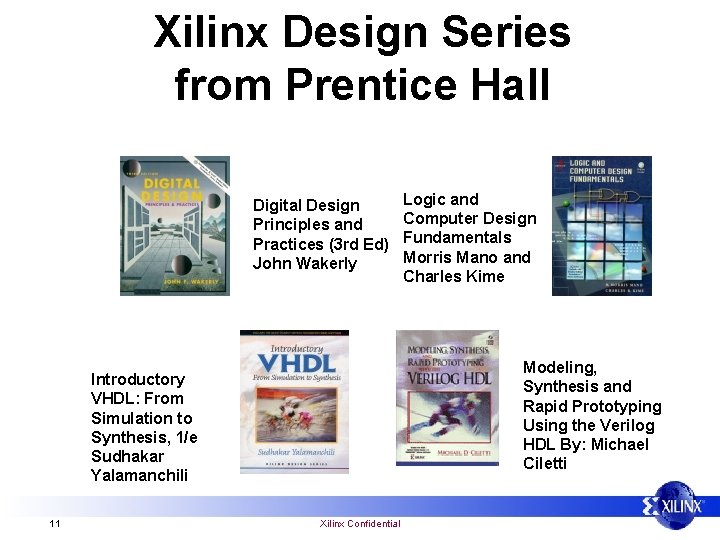

Xilinx Design Series from Prentice Hall Digital Design Principles and Practices (3 rd Ed) John Wakerly Modeling, Synthesis and Rapid Prototyping Using the Verilog HDL By: Michael Ciletti Introductory VHDL: From Simulation to Synthesis, 1/e Sudhakar Yalamanchili 11 Logic and Computer Design Fundamentals Morris Mano and Charles Kime Xilinx Confidential

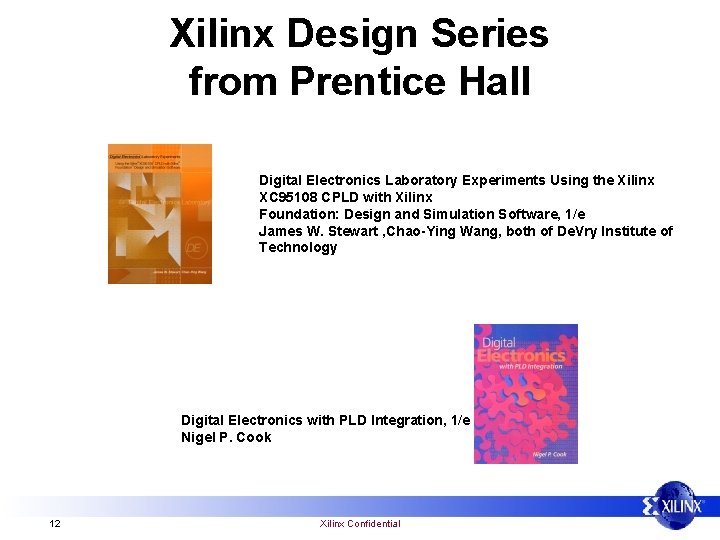

Xilinx Design Series from Prentice Hall Digital Electronics Laboratory Experiments Using the Xilinx XC 95108 CPLD with Xilinx Foundation: Design and Simulation Software, 1/e James W. Stewart , Chao-Ying Wang, both of De. Vry Institute of Technology Digital Electronics with PLD Integration, 1/e Nigel P. Cook 12 Xilinx Confidential

XUP URL: university. xilinx. com 13 Xilinx Confidential

Xilinx University Resource Center Hosted by Michigan State University u Professor Resources u - Teaching Materials - Support Texts u Student Resources - Tutorials - Project Examples u General Resources - Hardware/Software u Online Support - Discussion Forum www. xup. msu. edu - FAQ’s - Email support 14 Xilinx Confidential

http: //support. xilinx. com The Most Up-to-Date Information on Xilinx Products u Forums u Database search u tech. Xclusives u Software Updates u Problem Solvers u Software Manuals u Web Case for Professors u 15 Xilinx Confidential

FAQ u Who will Xilinx support in the universities? – Xilinx will give technical support to Professors and teaching assistants in the university labs. Students should get their support from their Professors or at support. xilinx. com or www. xup. msu. edu 16 Xilinx Confidential

Agenda u u u 17 Xilinx University Program Teaching Tools Advanced Teaching Tools Xilinx Confidential

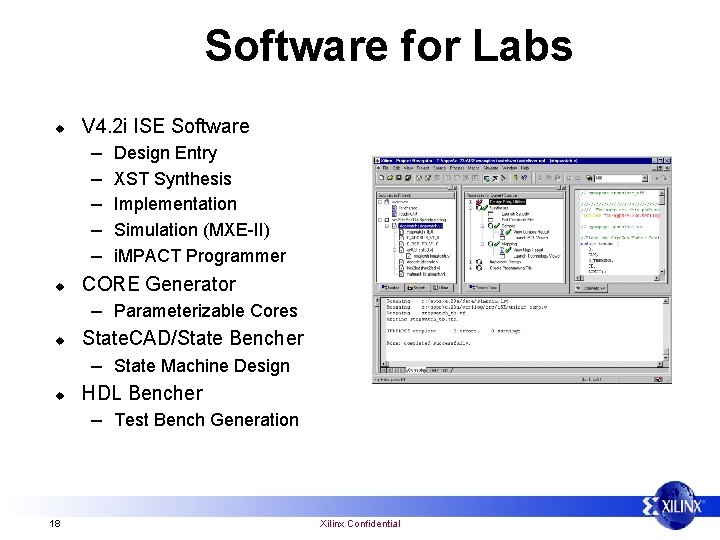

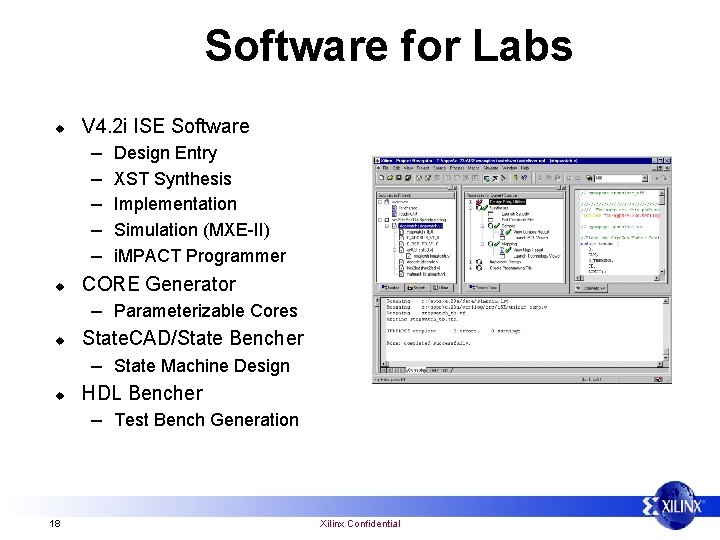

Software for Labs u u 18 V 4. 2 i ISE Software – Design Entry – XST Synthesis – Implementation – Simulation (MXE-II) – i. MPACT Programmer CORE Generator – Parameterizable Cores State. CAD/State Bencher – State Machine Design HDL Bencher – Test Bench Generation Xilinx Confidential

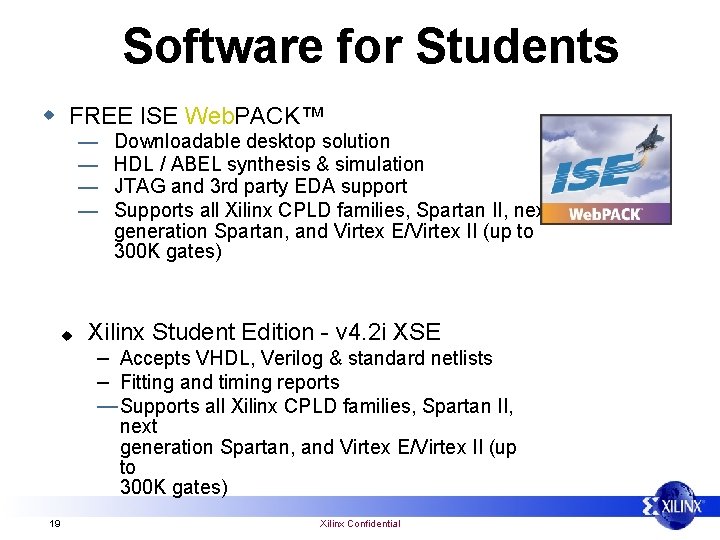

Software for Students w FREE ISE Web. PACK™ — — u Downloadable desktop solution HDL / ABEL synthesis & simulation JTAG and 3 rd party EDA support Supports all Xilinx CPLD families, Spartan II, next generation Spartan, and Virtex E/Virtex II (up to 300 K gates) Xilinx Student Edition - v 4. 2 i XSE – Accepts VHDL, Verilog & standard netlists – Fitting and timing reports — Supports all Xilinx CPLD families, Spartan II, next generation Spartan, and Virtex E/Virtex II (up to 300 K gates) 19 Xilinx Confidential

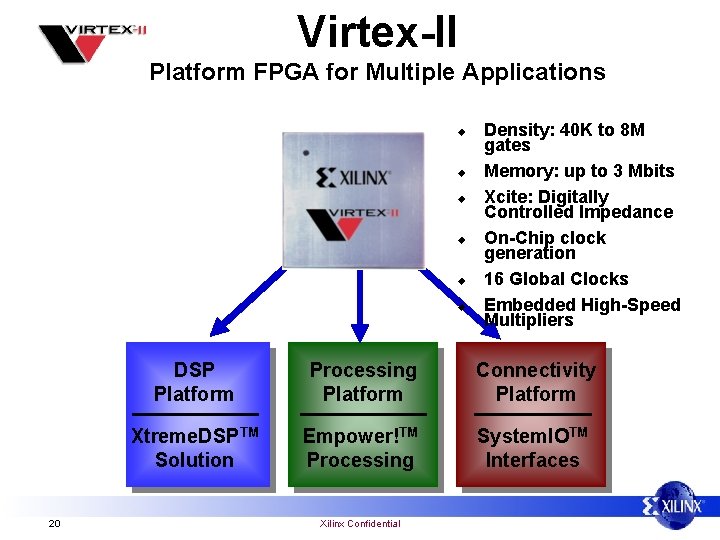

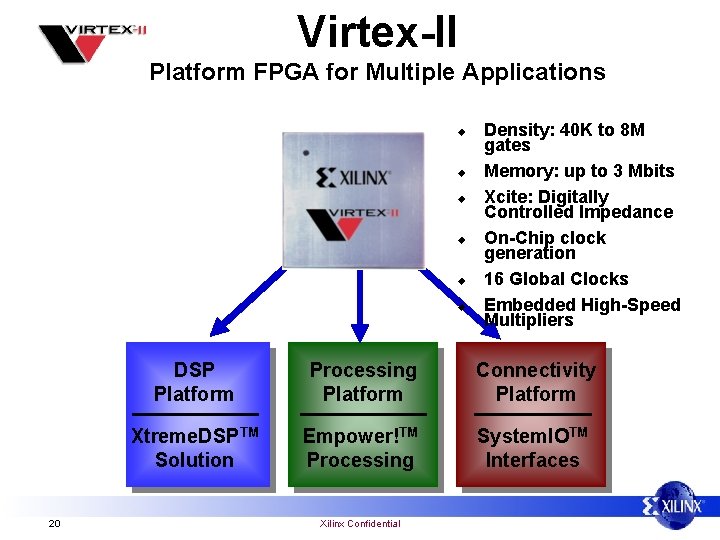

Virtex-II Platform FPGA for Multiple Applications u u u 20 Density: 40 K to 8 M gates Memory: up to 3 Mbits Xcite: Digitally Controlled Impedance On-Chip clock generation 16 Global Clocks Embedded High-Speed Multipliers DSP Platform Processing Platform Connectivity Platform Xtreme. DSPTM Solution Empower!TM Processing System. IOTM Interfaces Xilinx Confidential

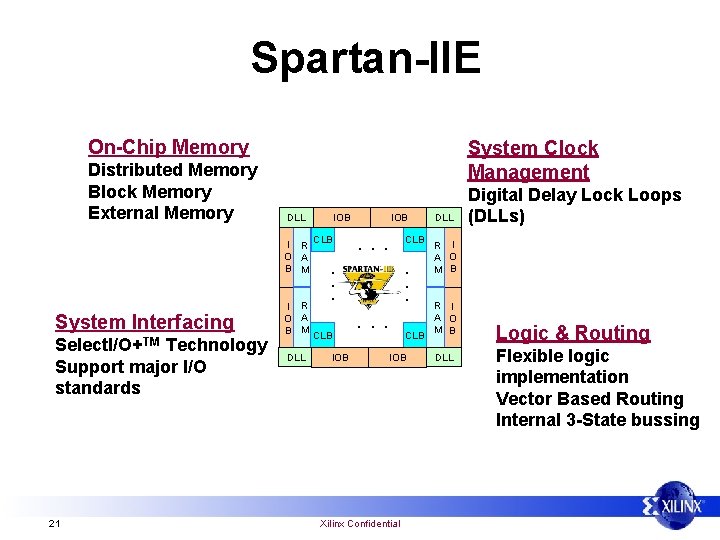

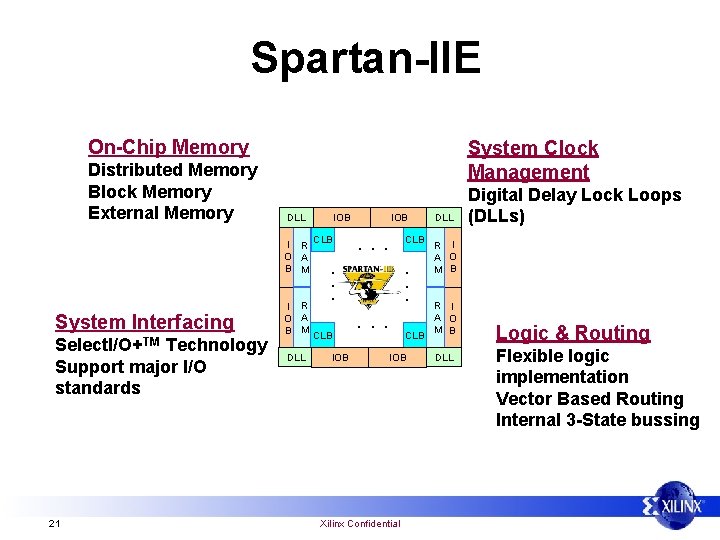

Spartan-IIE On-Chip Memory DLL System Interfacing Select. I/O+TM Technology Support major I/O standards 21 I R O A B M DLL CLB IOB . . . CLB . . . I R O A B M IOB . . . Distributed Memory Block Memory External Memory System Clock Management . . . CLB IOB Xilinx Confidential DLL Digital Delay Lock Loops (DLLs) R I A O M B DLL Logic & Routing Flexible logic implementation Vector Based Routing Internal 3 -State bussing

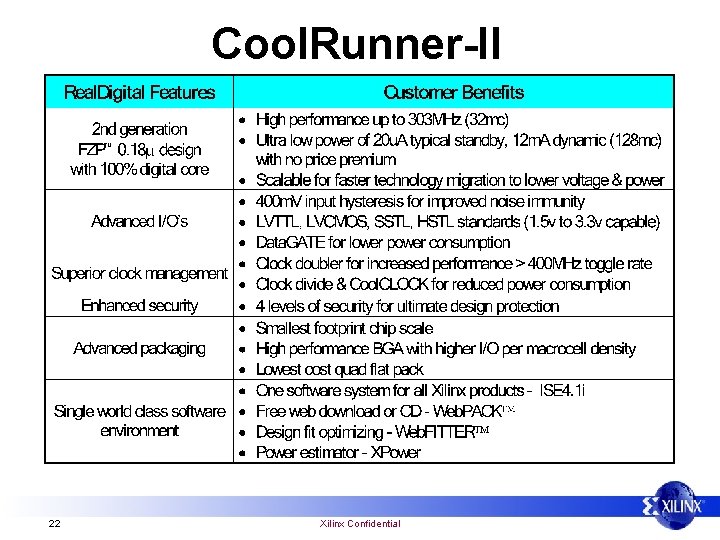

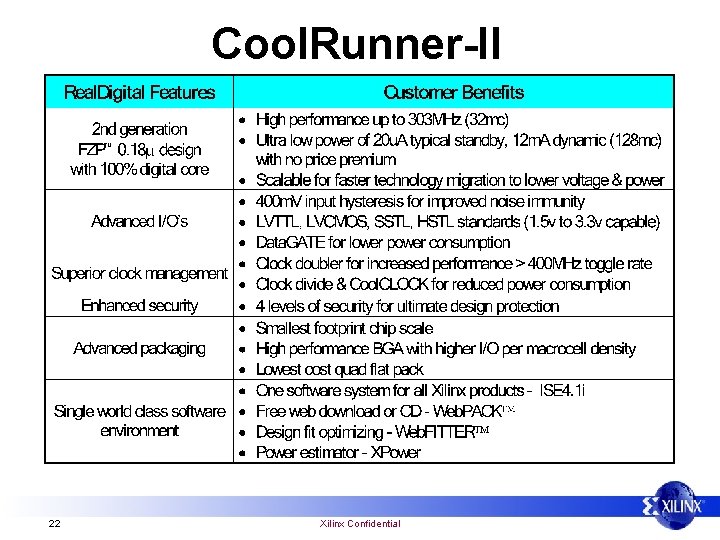

Cool. Runner-II 22 Xilinx Confidential

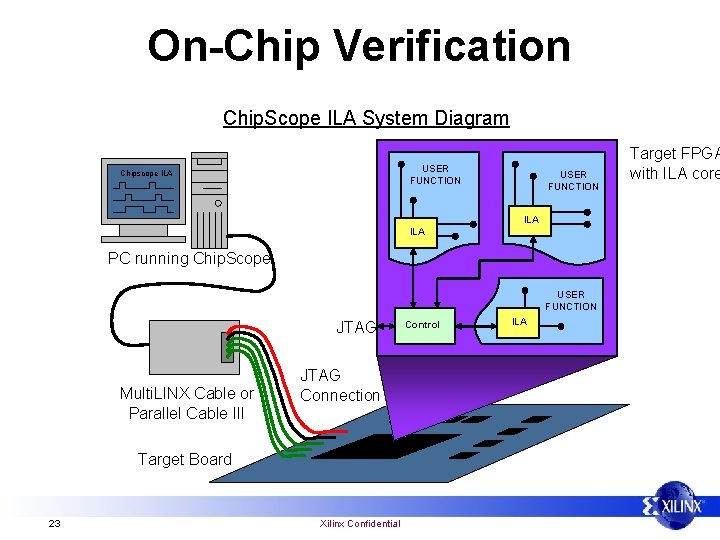

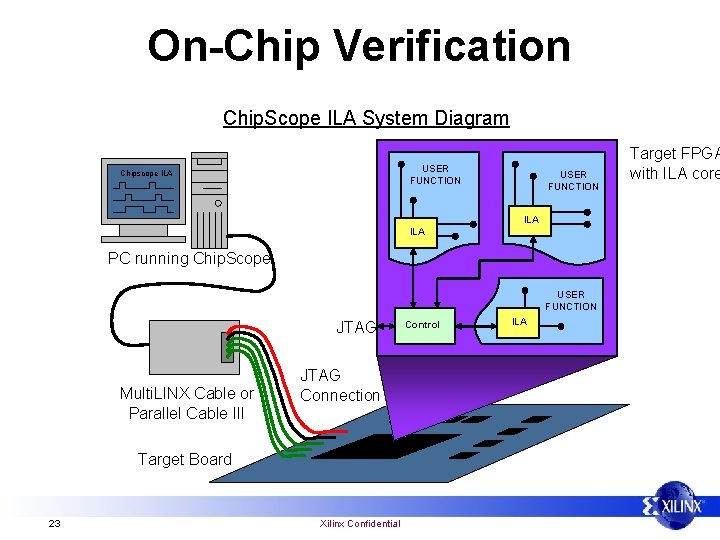

On-Chip Verification Chip. Scope ILA System Diagram USER FUNCTION Chipscope ILA USER FUNCTION ILA PC running Chip. Scope USER FUNCTION JTAG Multi. LINX Cable or Parallel Cable III JTAG Connection Target Board 23 Xilinx Confidential Control ILA Target FPGA with ILA core

Agenda u u u 24 Xilinx University Program Teaching Tools Advanced Teaching Tools Xilinx Confidential

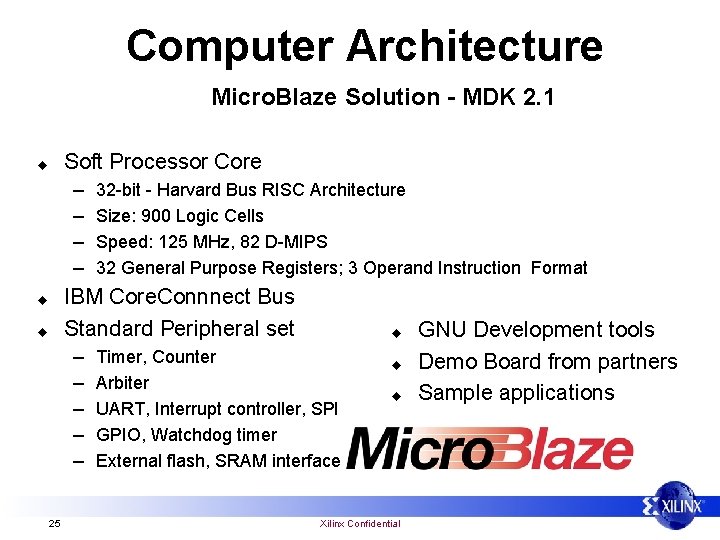

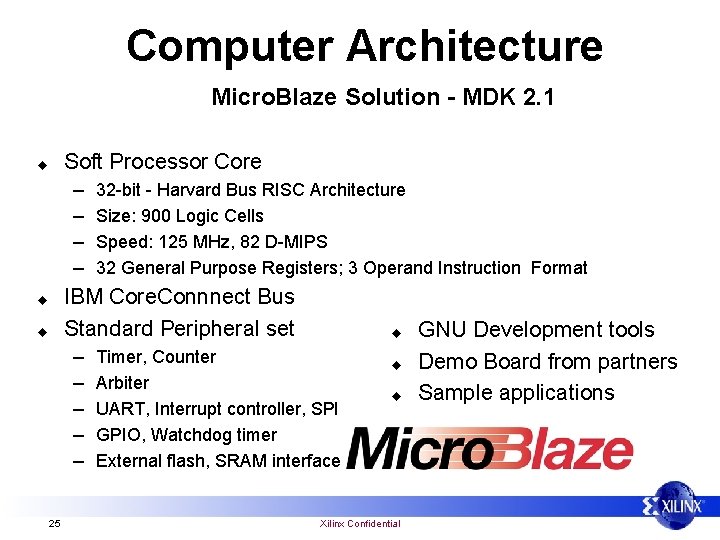

Computer Architecture Micro. Blaze Solution - MDK 2. 1 Soft Processor Core u – – 32 -bit - Harvard Bus RISC Architecture Size: 900 Logic Cells Speed: 125 MHz, 82 D-MIPS 32 General Purpose Registers; 3 Operand Instruction Format IBM Core. Connnect Bus Standard Peripheral set u u – – – 25 u Timer, Counter Arbiter UART, Interrupt controller, SPI GPIO, Watchdog timer External flash, SRAM interface u u Xilinx Confidential GNU Development tools Demo Board from partners Sample applications

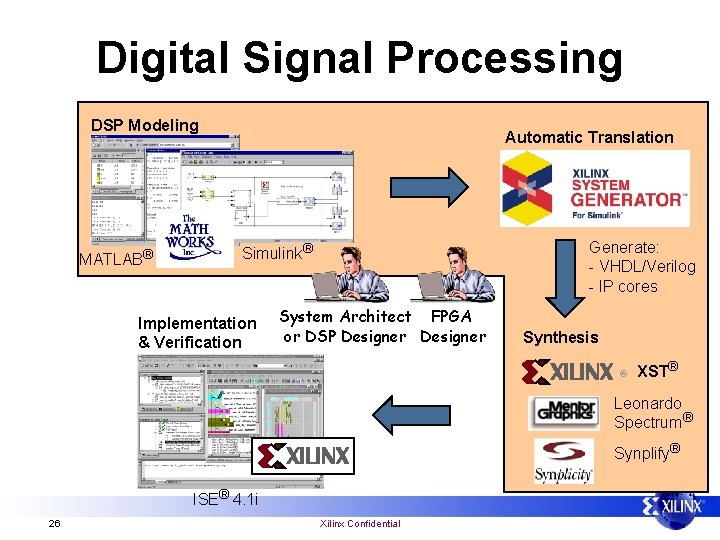

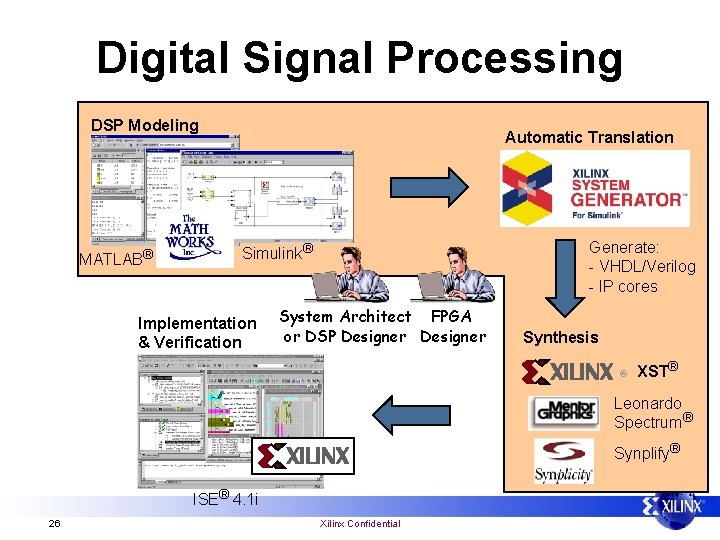

Digital Signal Processing DSP Modeling MATLAB® Automatic Translation Generate: - VHDL/Verilog - IP cores Simulink® Implementation & Verification System Architect FPGA or DSP Designer Synthesis ® XST® Leonardo Spectrum® Synplify® ISE® 4. 1 i 26 Xilinx Confidential

Summary u u Xilinx is an excellent choice as target technology for many engineering courses and projects. XUP’s job is to make your job easier – Make it easy for professors to stay current with technology and to get Xilinx software and hardware – Offer web sites with lab exercises – Prentice-Hall Xilinx Design Series textbooks 27 Xilinx Confidential