Synthesis of asynchronous controllers from Signal Transition Graphs

![petrify: logic synthesis [la] = rr*csc 0’; [rr] = csc 0’; [csc 0] = petrify: logic synthesis [la] = rr*csc 0’; [rr] = csc 0’; [csc 0] =](https://slidetodoc.com/presentation_image_h2/d12a4aa5b1f60feefa1bcbb669c54592/image-93.jpg)

![petrify: technology mapping # gate [la] = # gate [rr] = # gate [csc petrify: technology mapping # gate [la] = # gate [rr] = # gate [csc](https://slidetodoc.com/presentation_image_h2/d12a4aa5b1f60feefa1bcbb669c54592/image-94.jpg)

- Slides: 108

Synthesis of asynchronous controllers from Signal Transition Graphs: Jordi Cortadella Universitat Politècnica de Catalunya Joint work with: Michael Kishinevsky, Intel Corporation Alex Kondratyev, Xilinx Luciano Lavagno, Politecnico di Torino Alex Yakovlev, University of Newcastle EMICRO 2016 Synthesis of async controllers from STGs 1

Outline • • • Asynchronous controllers Specification with Signal Transition Graphs Synthesis from Signal Transition Graphs Petrify Advanced topics EMICRO 2016 Synthesis of async controllers from STGs 2

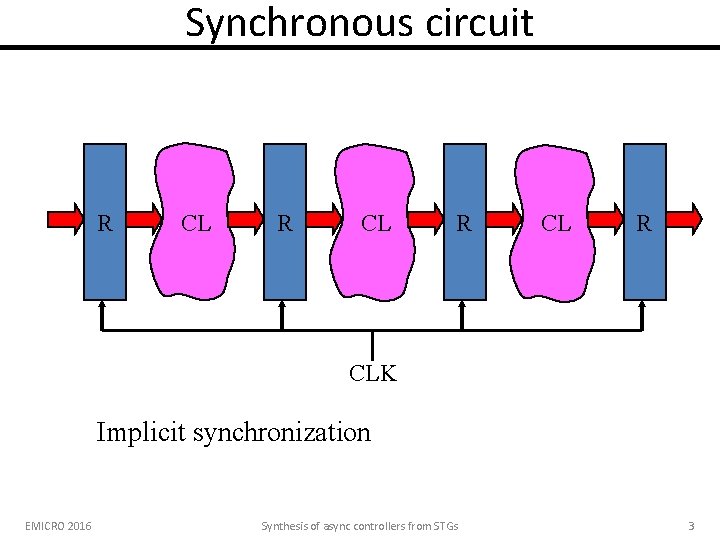

Synchronous circuit R CLK Implicit synchronization EMICRO 2016 Synthesis of async controllers from STGs 3

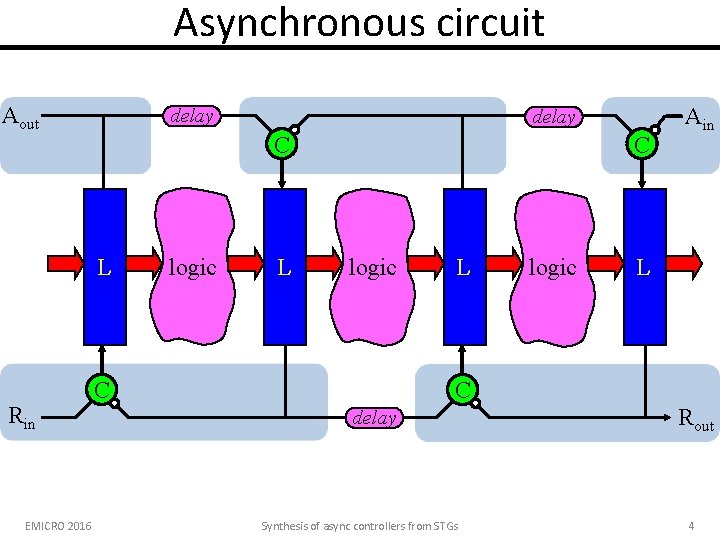

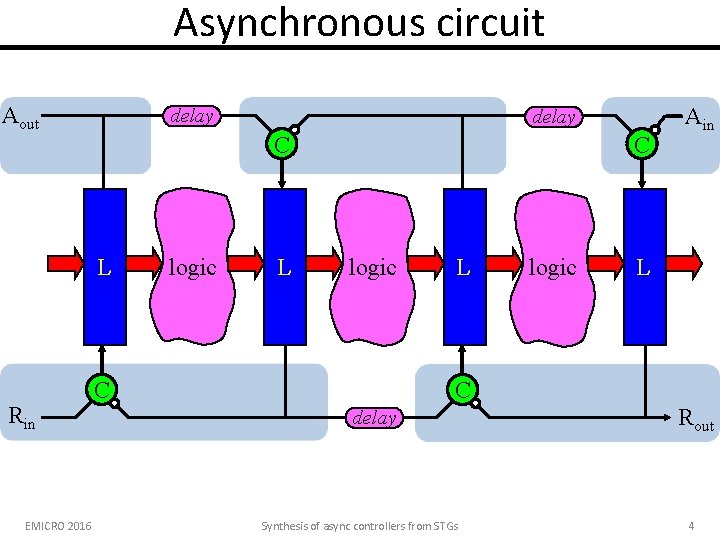

Asynchronous circuit Aout delay C L Rin EMICRO 2016 delay logic L C logic C L logic Ain L C delay Synthesis of async controllers from STGs Rout 4

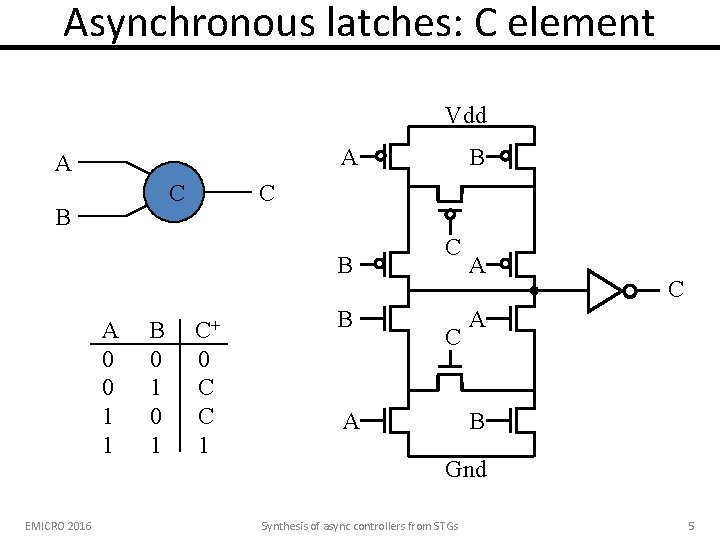

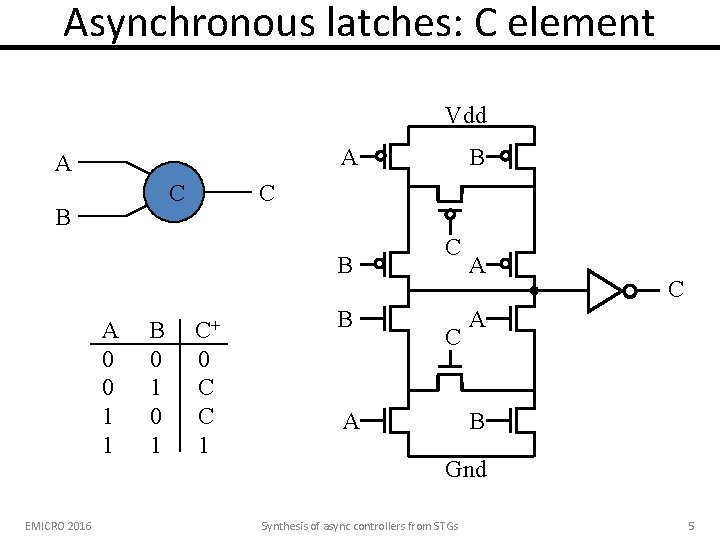

Asynchronous latches: C element Vdd A A C B A 0 0 1 1 EMICRO 2016 B 0 1 B C+ 0 C C 1 B C C A A C A B Gnd Synthesis of async controllers from STGs 5

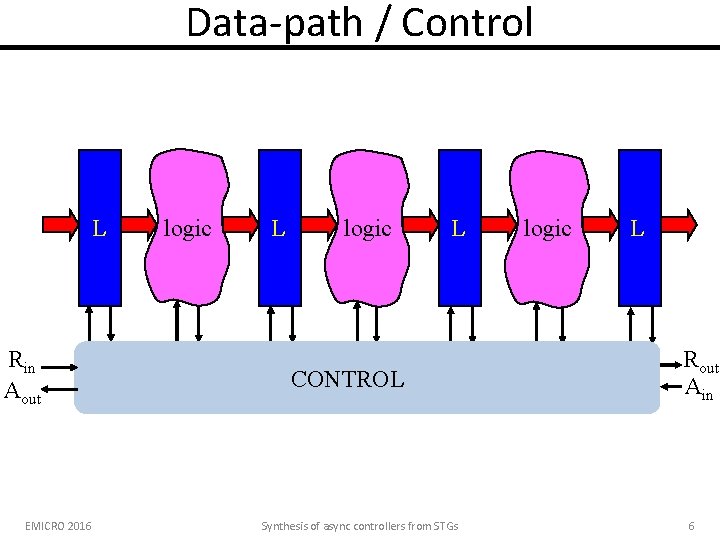

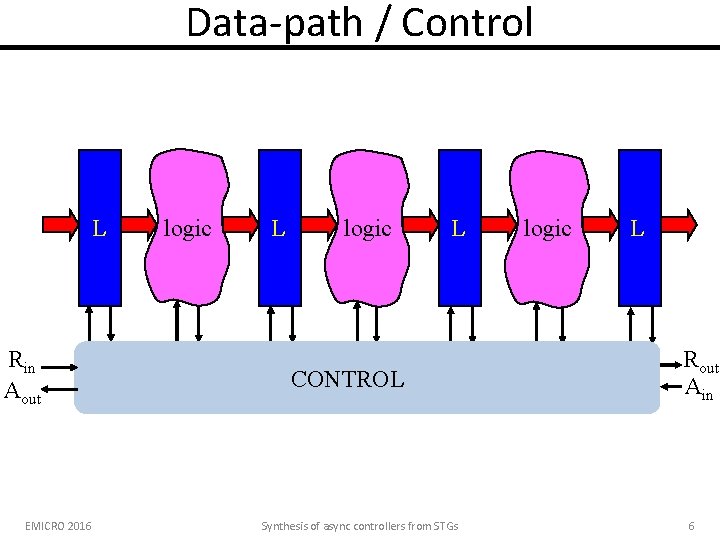

Data-path / Control L Rin Aout EMICRO 2016 logic L CONTROL Synthesis of async controllers from STGs logic L Rout Ain 6

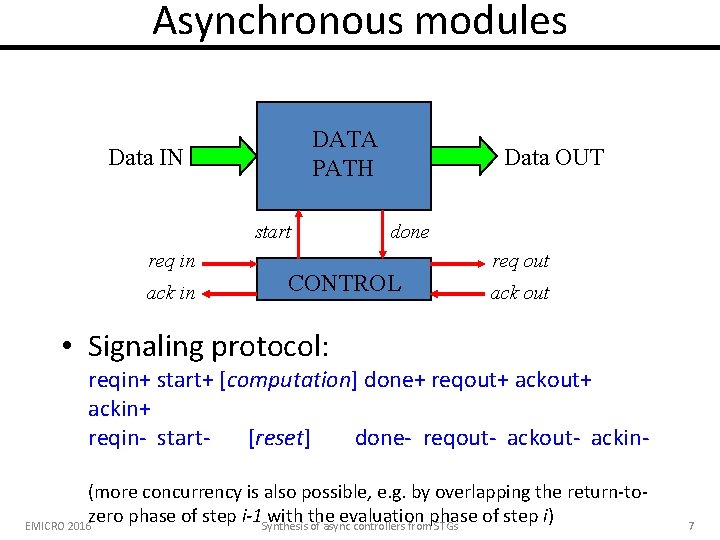

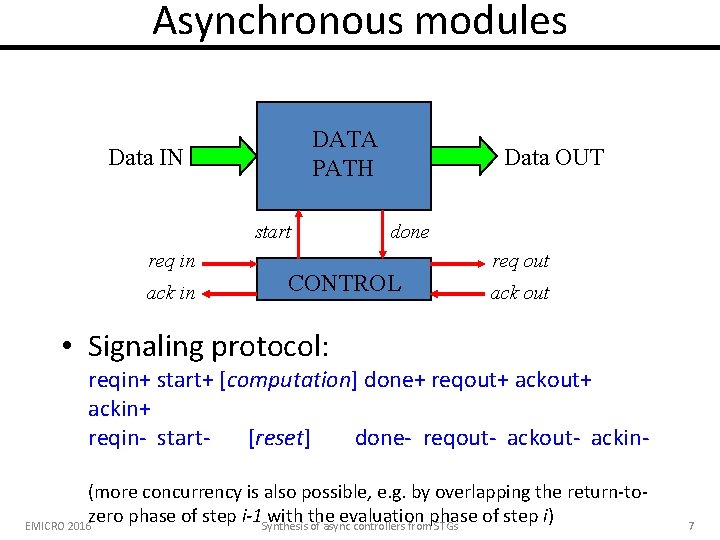

Asynchronous modules DATA PATH Data IN start req in ack in Data OUT done CONTROL req out ack out • Signaling protocol: reqin+ start+ [computation] done+ reqout+ ackin+ reqin- start[reset] done- reqout- ackin- (more concurrency is also possible, e. g. by overlapping the return-tozero phase of step i-1 Synthesis with the evaluation phase of step i) EMICRO 2016 of async controllers from STGs 7

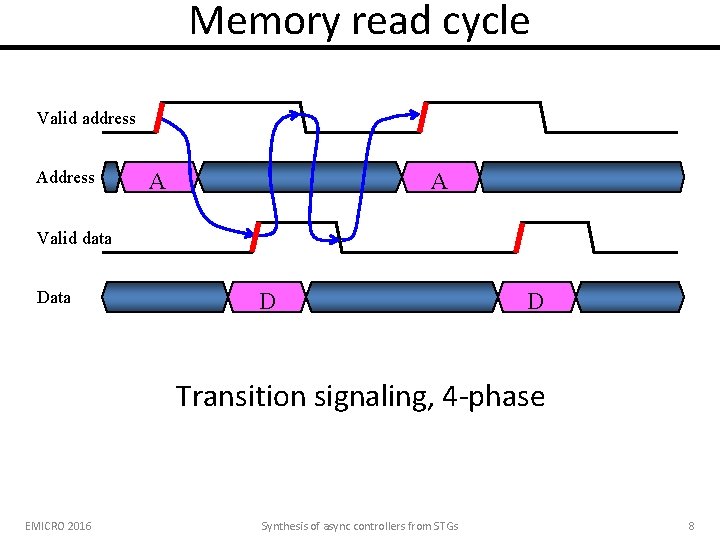

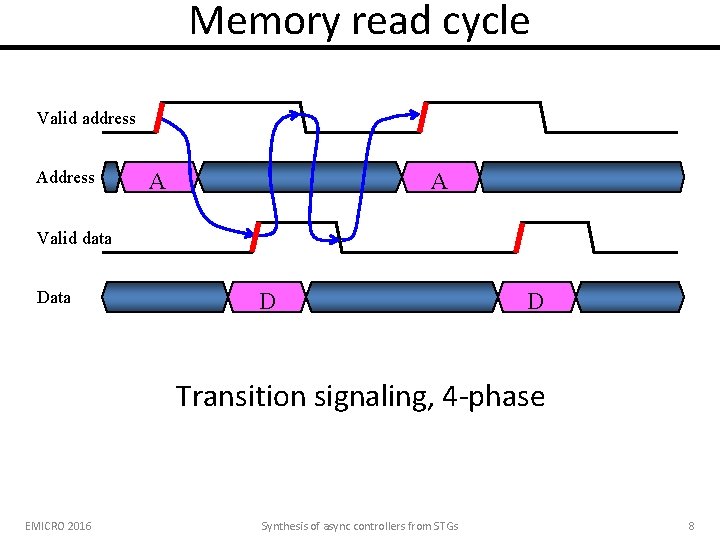

Memory read cycle Valid address A A Valid data D D Transition signaling, 4 -phase EMICRO 2016 Synthesis of async controllers from STGs 8

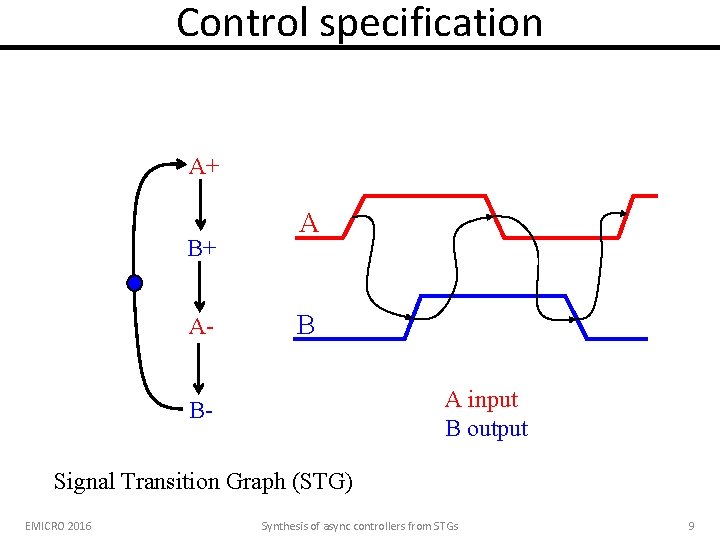

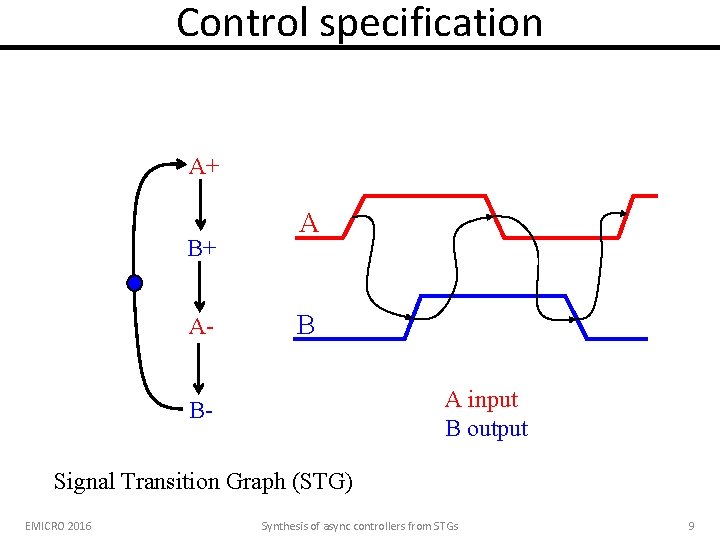

Control specification A+ B+ A- A B A input B output BSignal Transition Graph (STG) EMICRO 2016 Synthesis of async controllers from STGs 9

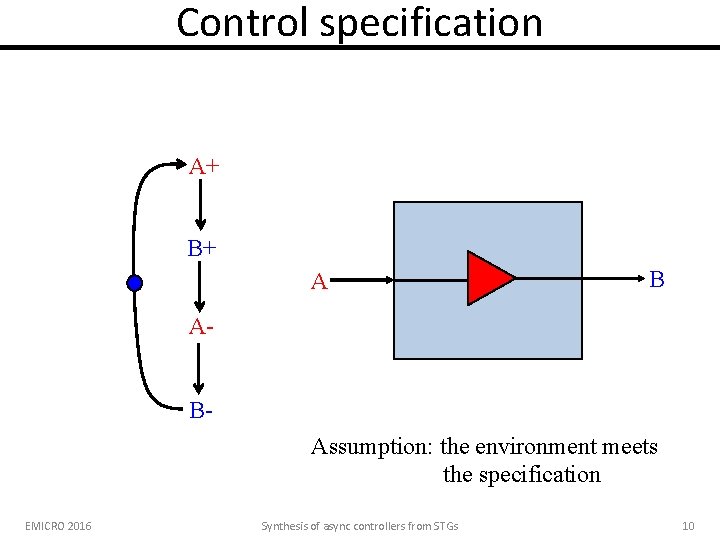

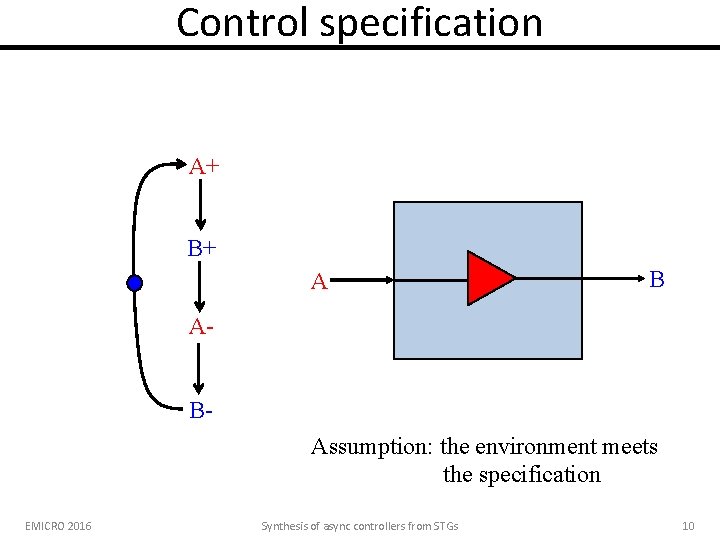

Control specification A+ B+ A B ABAssumption: the environment meets the specification EMICRO 2016 Synthesis of async controllers from STGs 10

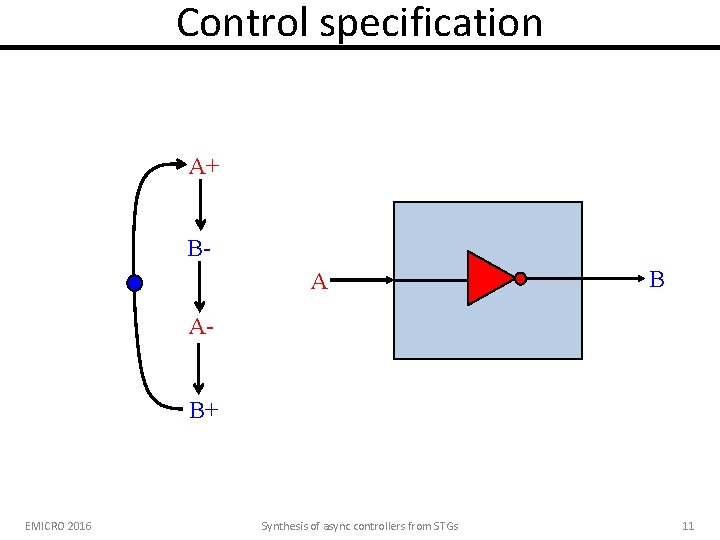

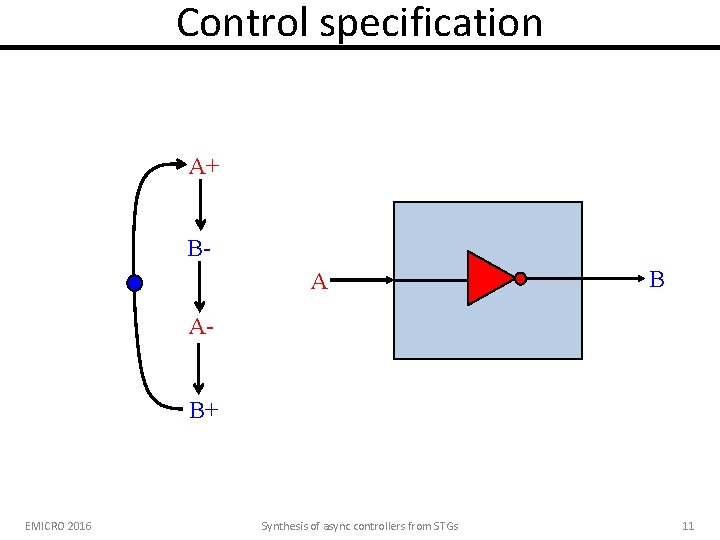

Control specification A+ BA B AB+ EMICRO 2016 Synthesis of async controllers from STGs 11

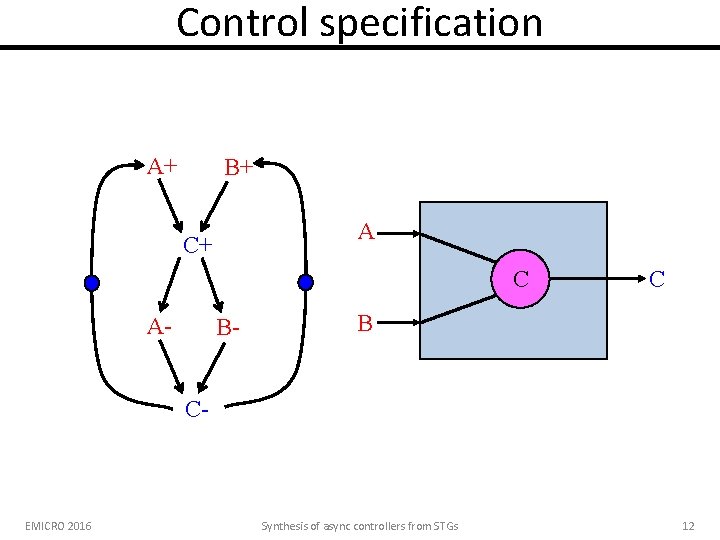

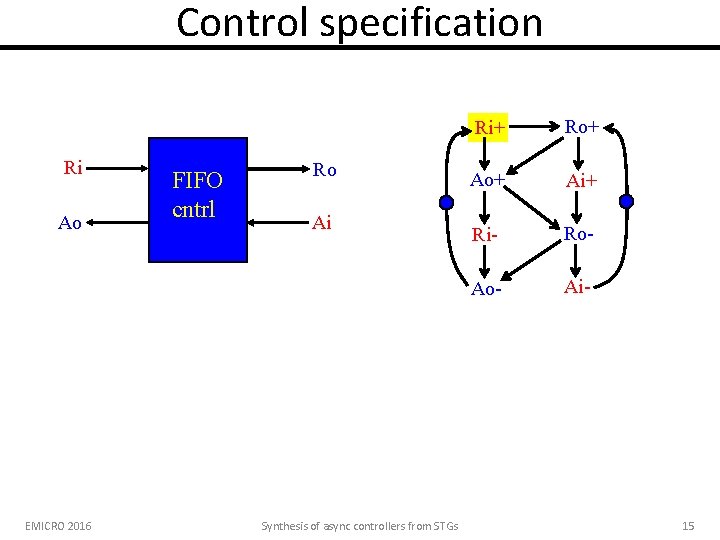

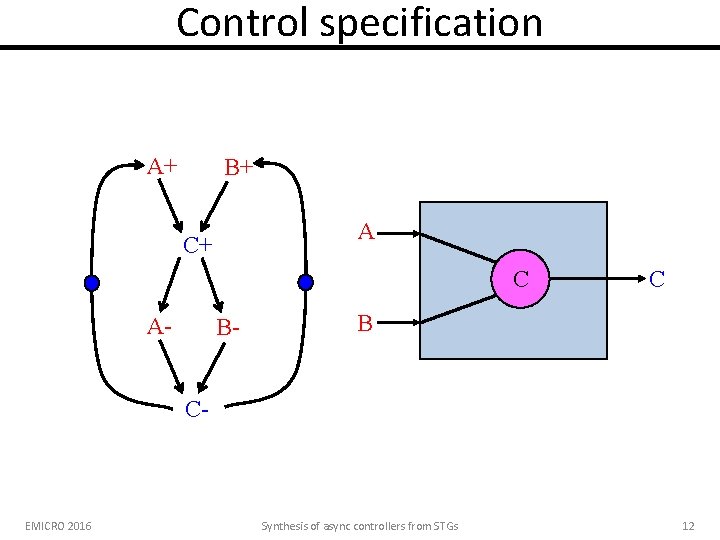

Control specification A+ B+ A C+ C A- B- C B C- EMICRO 2016 Synthesis of async controllers from STGs 12

Control specification A+ B+ C+ A- A C C B BC- EMICRO 2016 Synthesis of async controllers from STGs 13

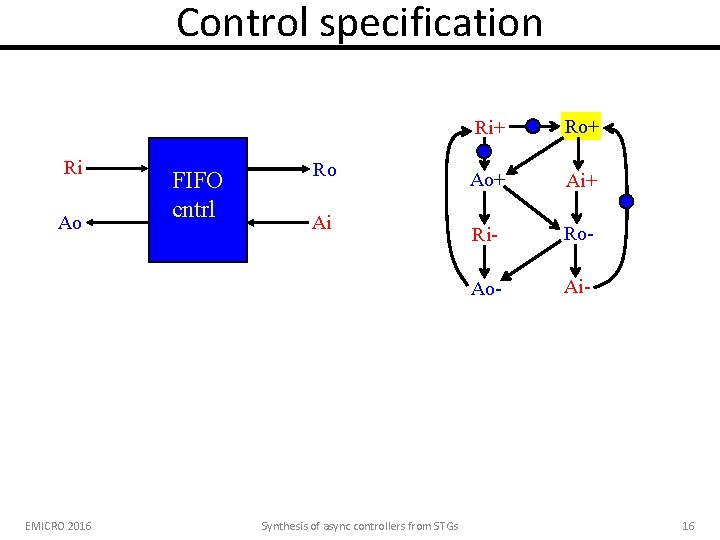

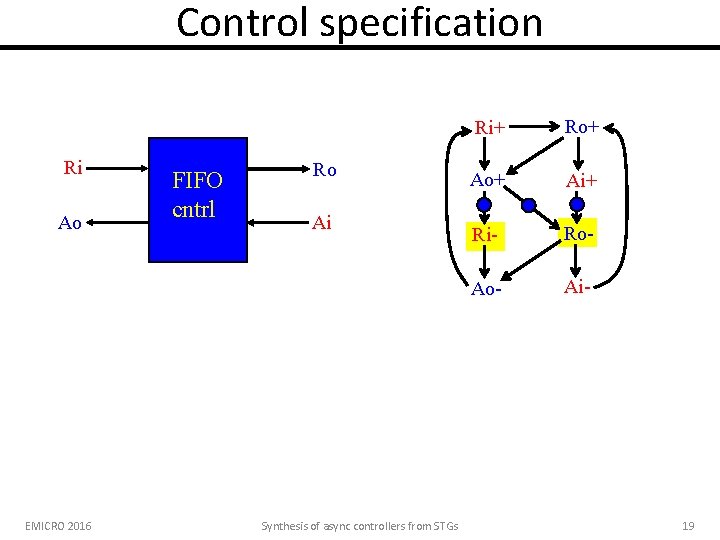

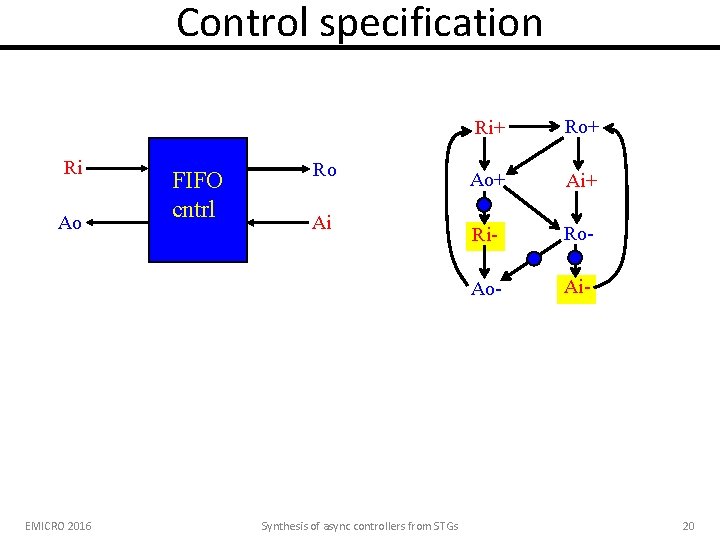

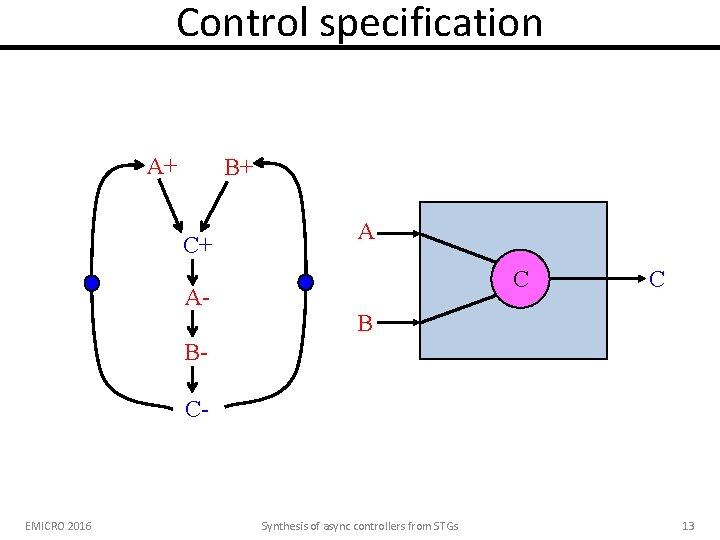

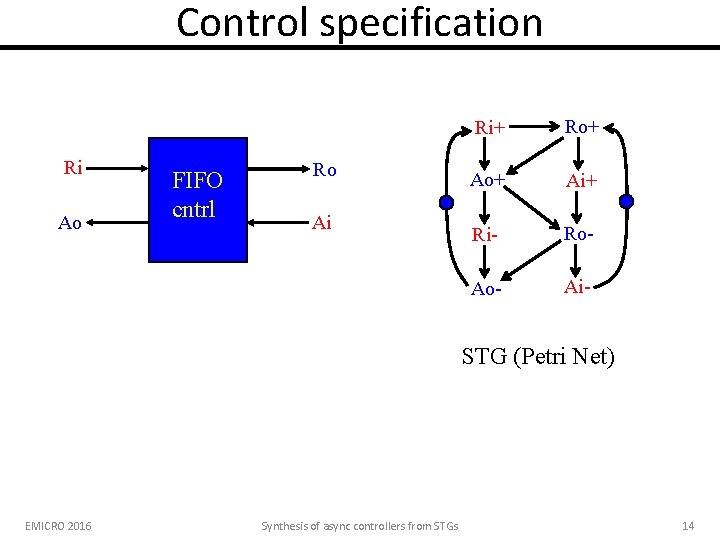

Control specification Ri Ao FIFO cntrl Ro Ai Ri+ Ro+ Ai+ Ri- Ro- Ai- STG (Petri Net) EMICRO 2016 Synthesis of async controllers from STGs 14

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 15

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 16

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 17

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 18

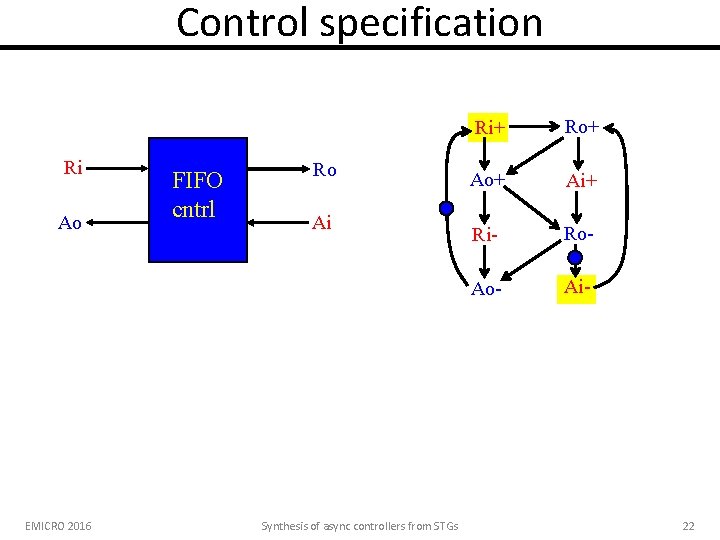

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 19

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 20

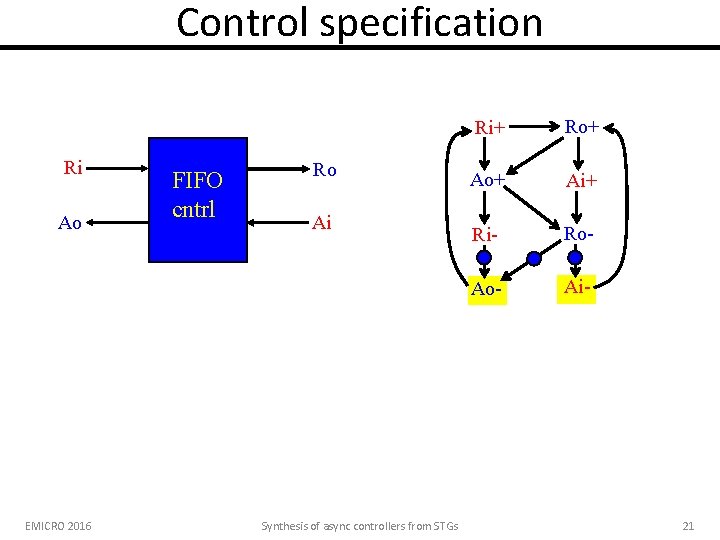

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 21

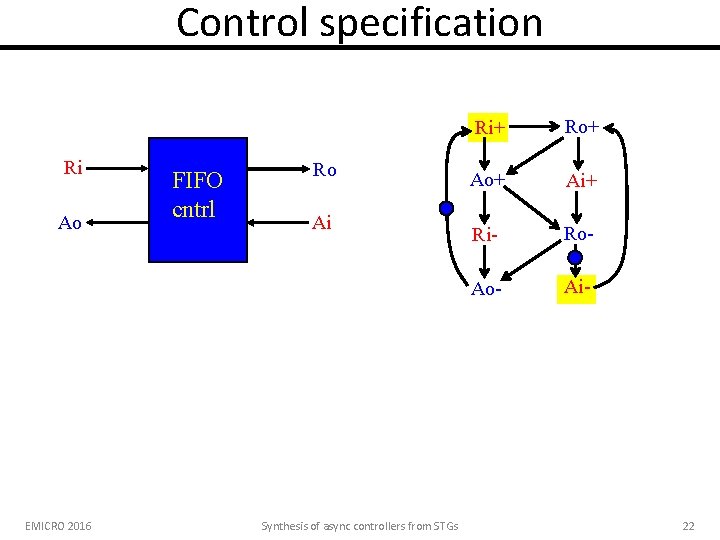

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 22

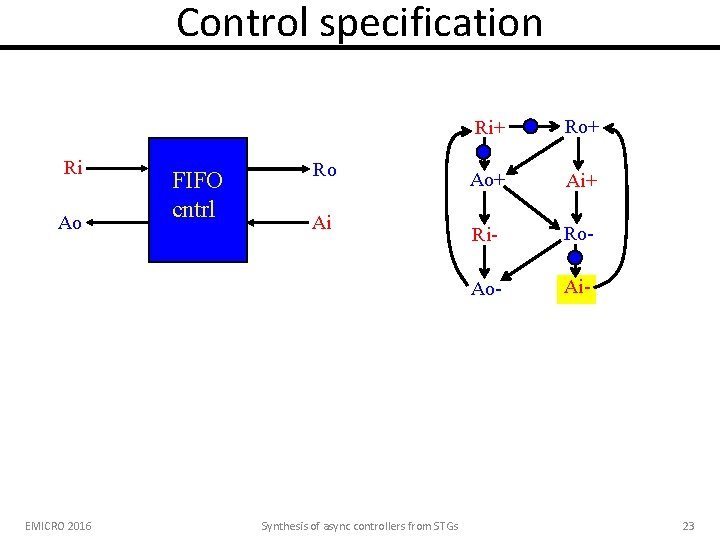

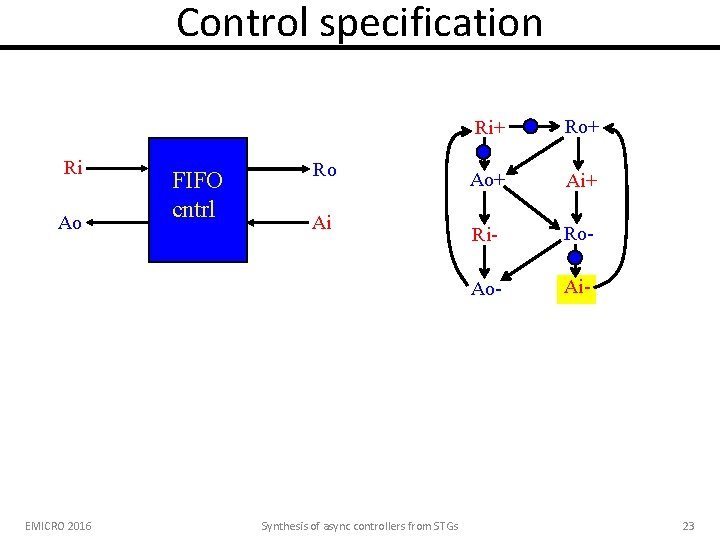

Control specification Ri Ao EMICRO 2016 FIFO cntrl Ro Ai Synthesis of async controllers from STGs Ri+ Ro+ Ai+ Ri- Ro- Ai- 23

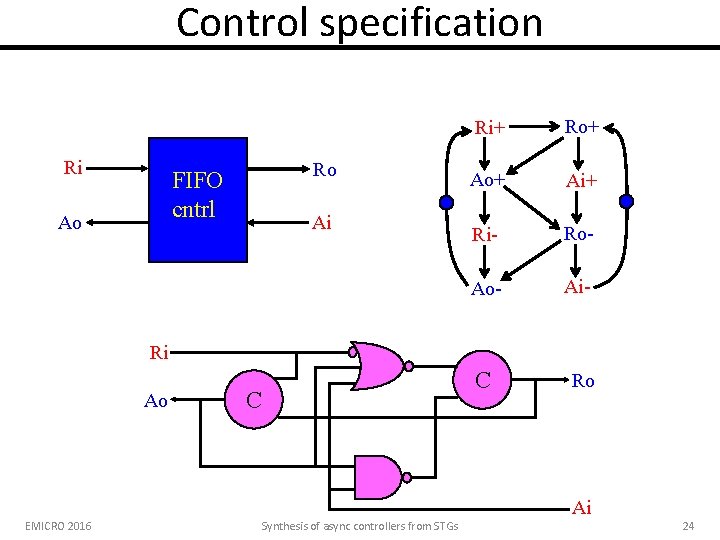

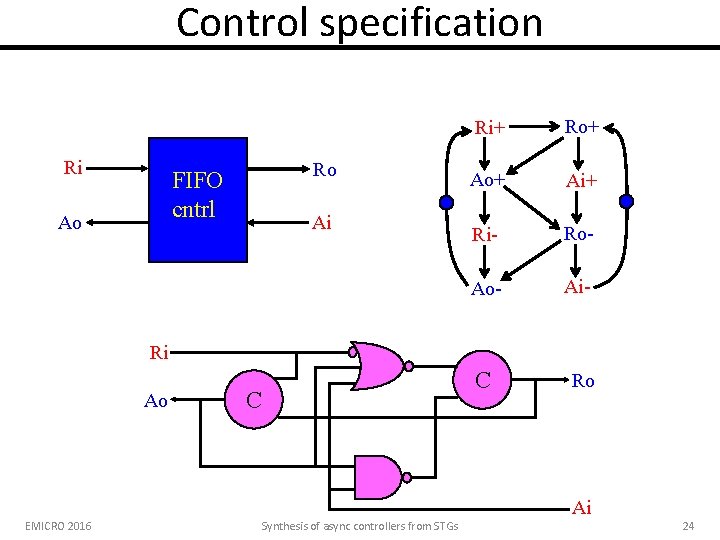

Control specification Ri Ro FIFO cntrl Ao Ai Ri+ Ro+ Ai+ Ri- Ro- Ai- Ri Ao EMICRO 2016 C Synthesis of async controllers from STGs C Ro Ai 24

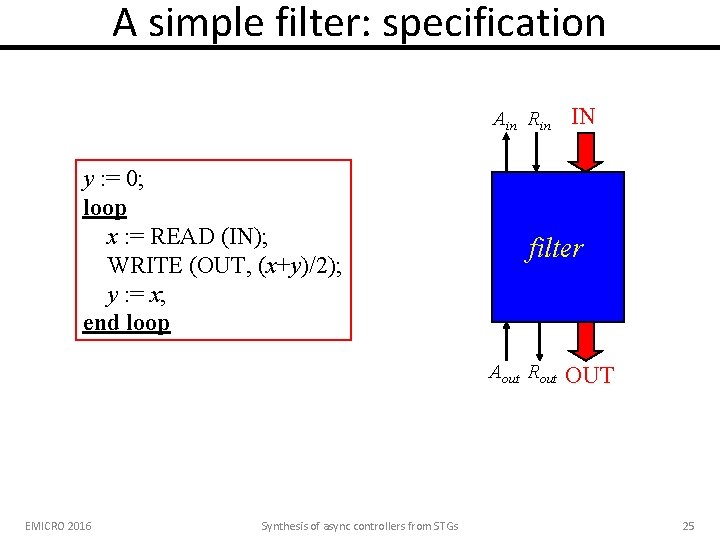

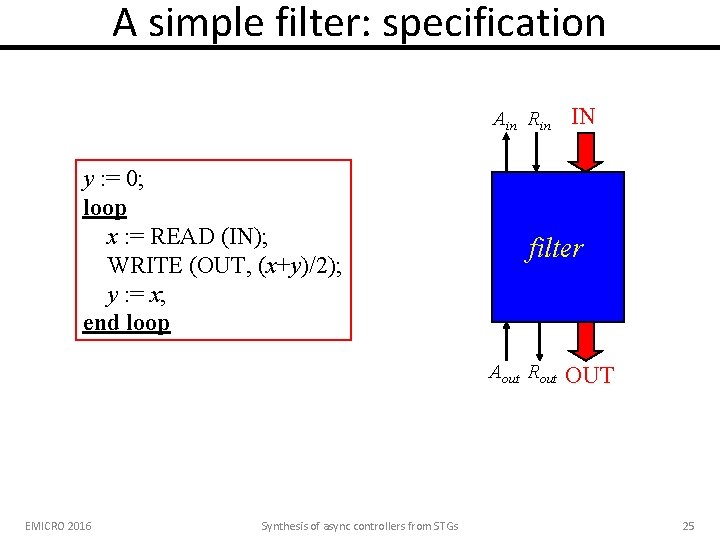

A simple filter: specification Ain Rin y : = 0; loop x : = READ (IN); WRITE (OUT, (x+y)/2); y : = x; end loop filter Aout Rout EMICRO 2016 Synthesis of async controllers from STGs IN OUT 25

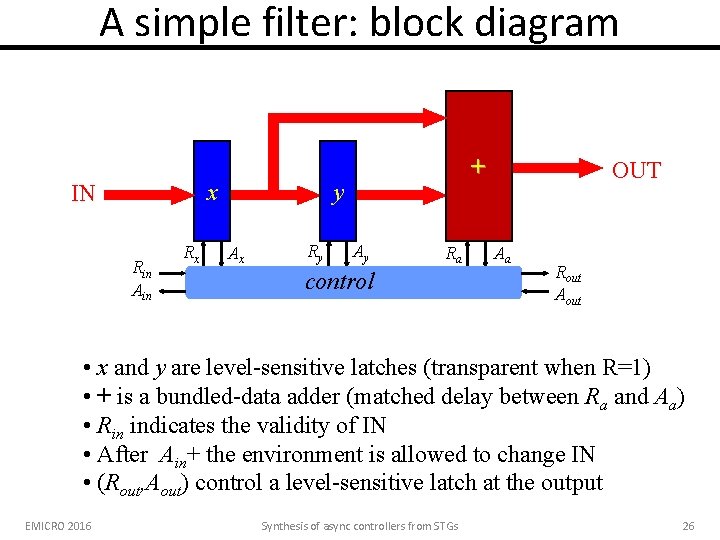

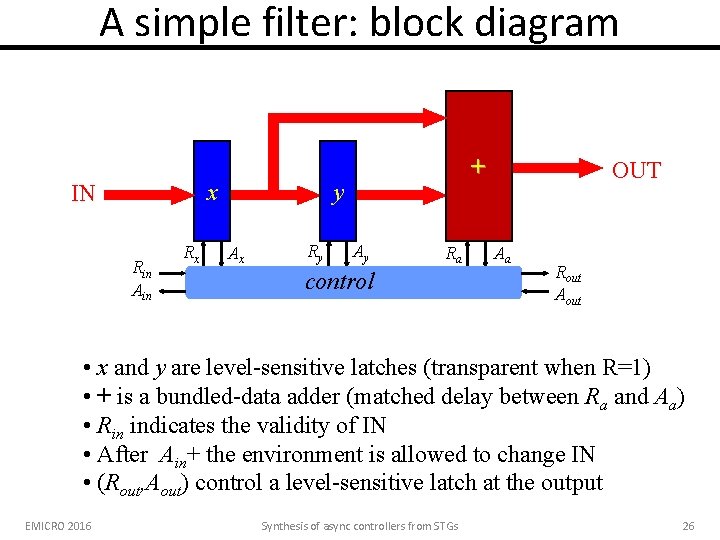

A simple filter: block diagram x IN Rin Ain Rx + y Ax Ry Ay Ra control OUT Aa Rout Aout • x and y are level-sensitive latches (transparent when R=1) • + is a bundled-data adder (matched delay between Ra and Aa) • Rin indicates the validity of IN • After Ain+ the environment is allowed to change IN • (Rout, Aout) control a level-sensitive latch at the output EMICRO 2016 Synthesis of async controllers from STGs 26

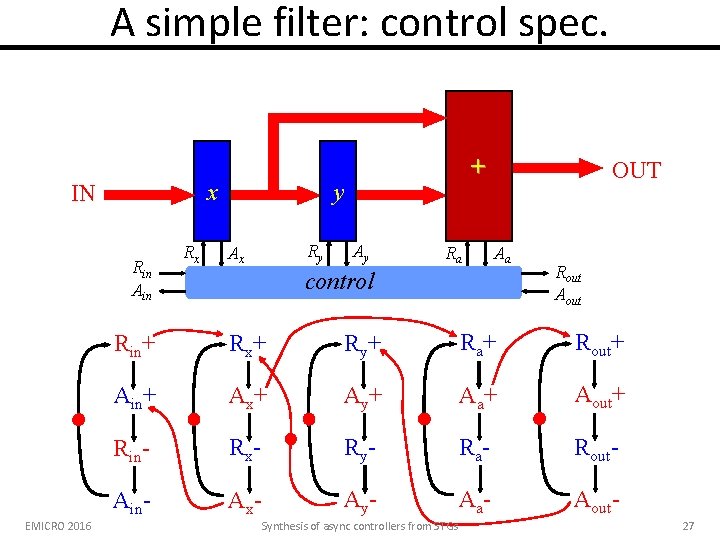

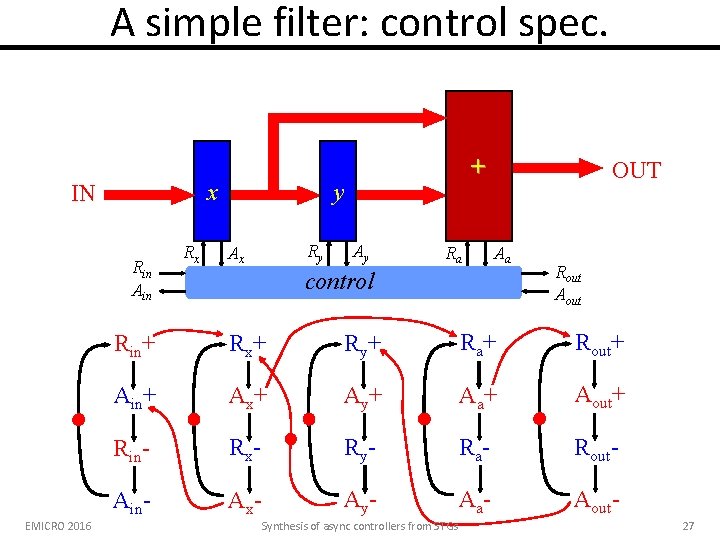

A simple filter: control spec. x IN Rin Ain EMICRO 2016 Rx + y Ry Ax Ay Ra OUT Aa control Rout Aout Rin+ R x+ R y+ R a+ Rout+ Ain+ A x+ A y+ Aa + Aout+ Rin- R x- R y- R a- Rout- Ain- A x- A y- Aa - Aout- Synthesis of async controllers from STGs 27

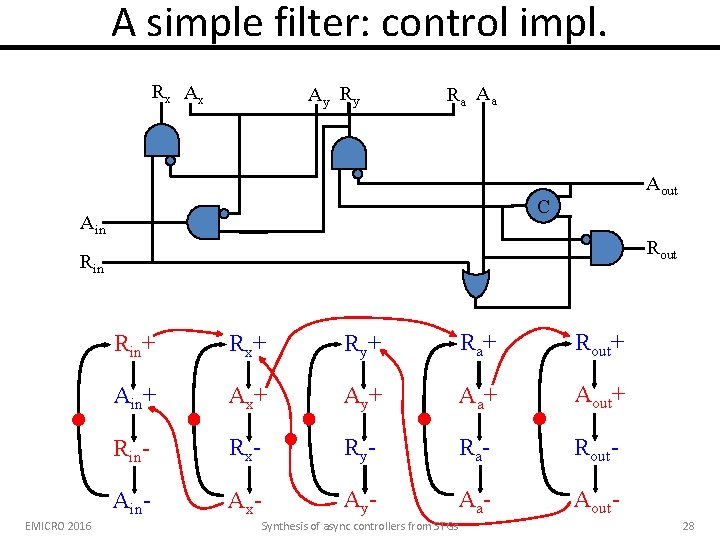

A simple filter: control impl. R x Ax Ay R a Aa Aout C Ain Rout Rin EMICRO 2016 Rin+ R x+ R y+ R a+ Rout+ Ain+ A x+ A y+ Aa + Aout+ Rin- R x- R y- R a- Rout- Ain- A x- A y- Aa - Aout- Synthesis of async controllers from STGs 28

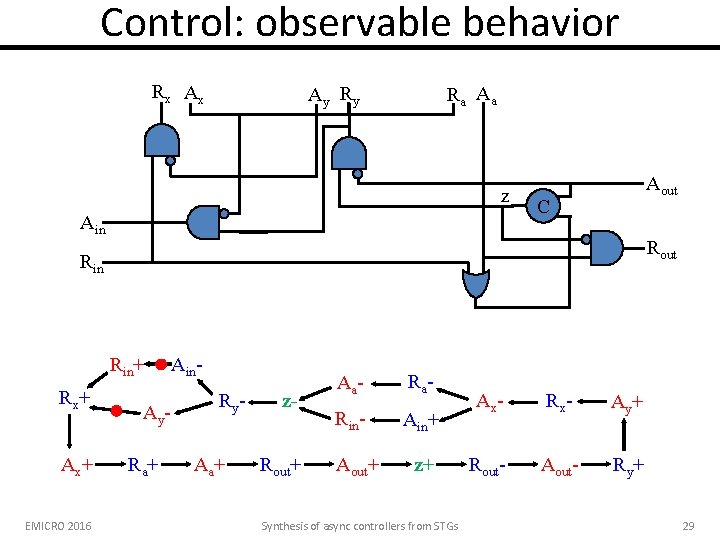

Control: observable behavior R x Ax R a Aa Ay R y z Ain Aout C Rout Rin+ Rx+ Ax + EMICRO 2016 Ay Ra + Ain. Ry. Aa + z. Rout+ Aa - Rin- Ain+ Aout+ z+ Synthesis of async controllers from STGs Ax - Rx- Ay + Rout- Aout- Ry+ 29

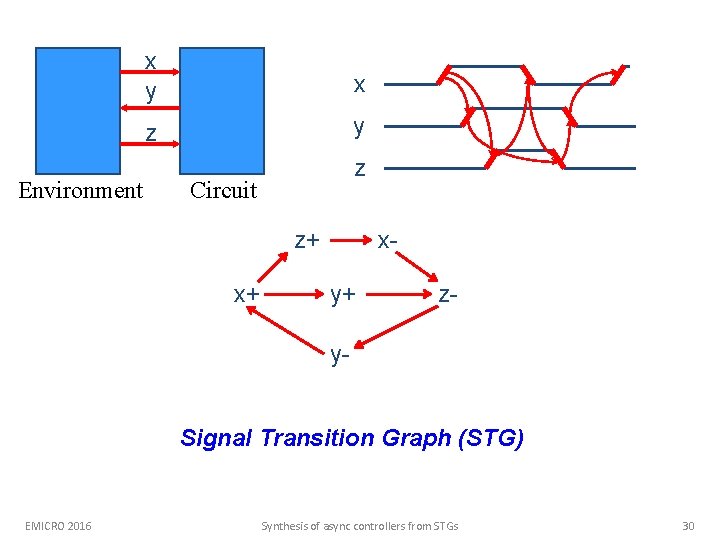

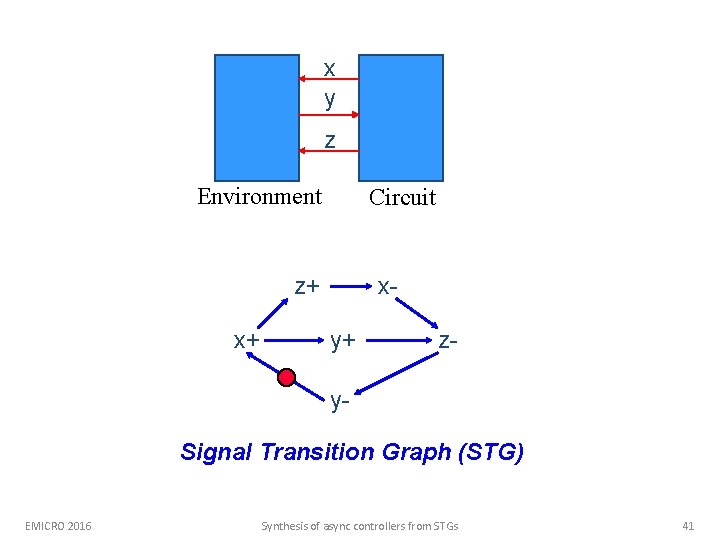

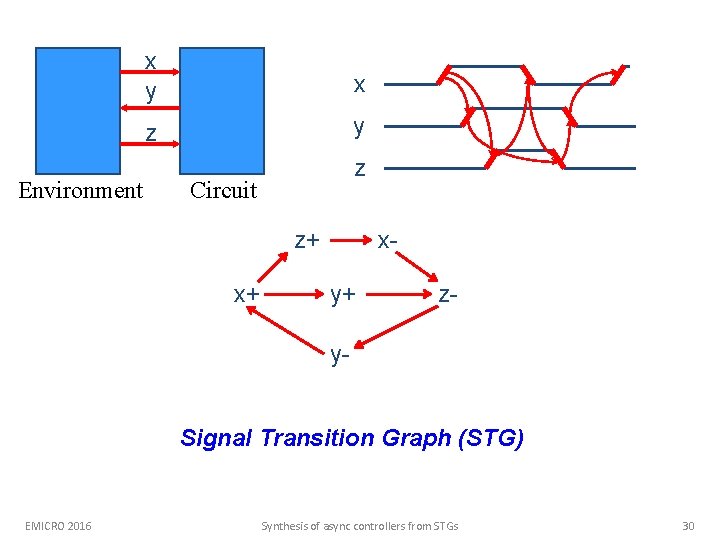

Environment x y x z y z Circuit z+ x+ xy+ z- y. Signal Transition Graph (STG) EMICRO 2016 Synthesis of async controllers from STGs 30

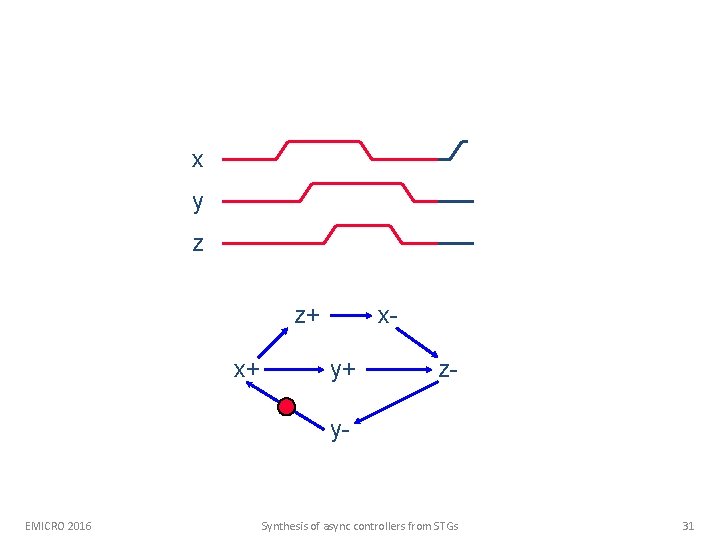

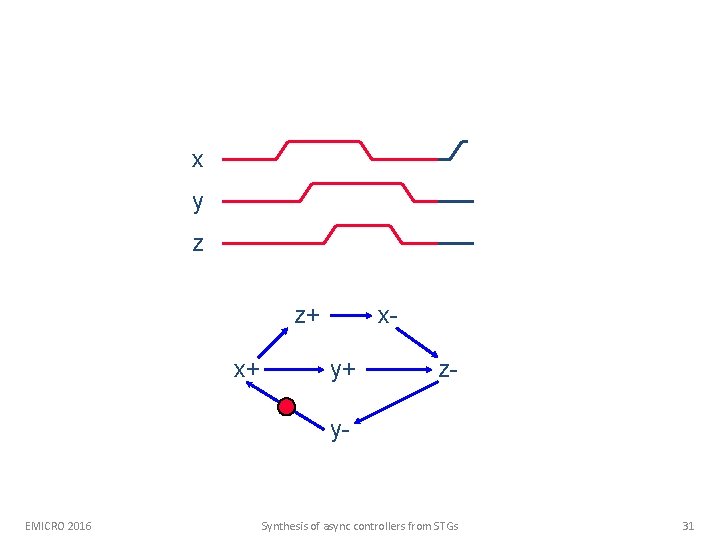

x y z z+ x+ xy+ z- y- EMICRO 2016 Synthesis of async controllers from STGs 31

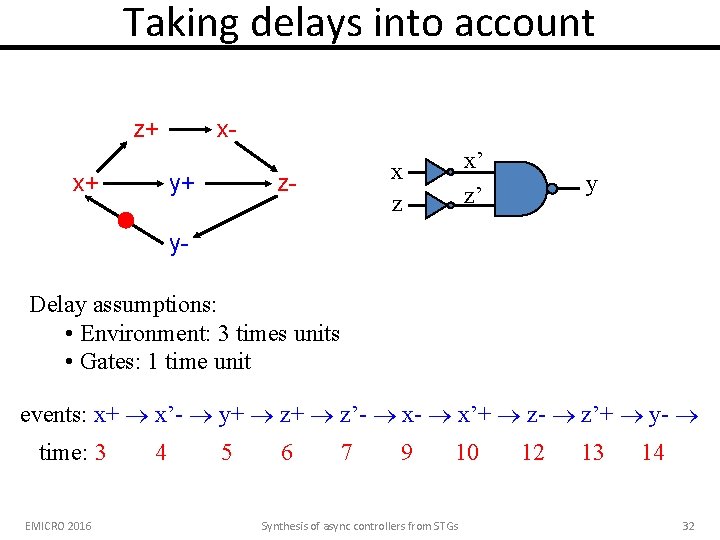

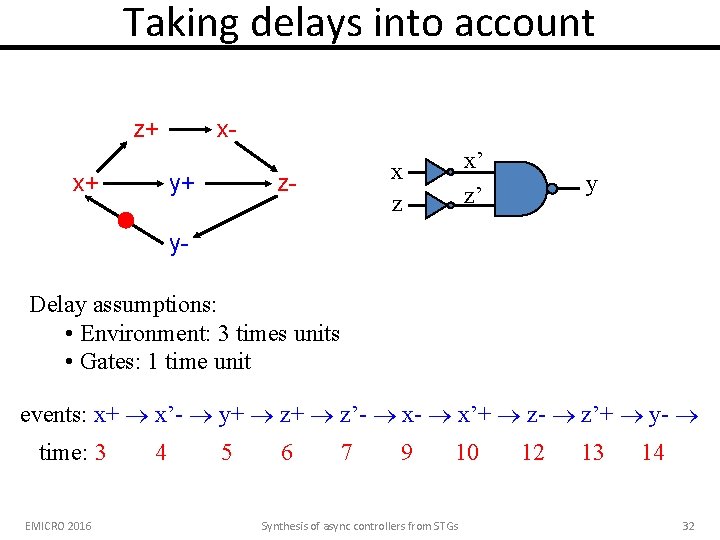

Taking delays into account z+ x+ xz- y+ x’ z’ x z y y. Delay assumptions: • Environment: 3 times units • Gates: 1 time unit events: x+ x’- y+ z’- x’+ z- z’+ y- time: 3 EMICRO 2016 4 5 6 7 9 10 Synthesis of async controllers from STGs 12 13 14 32

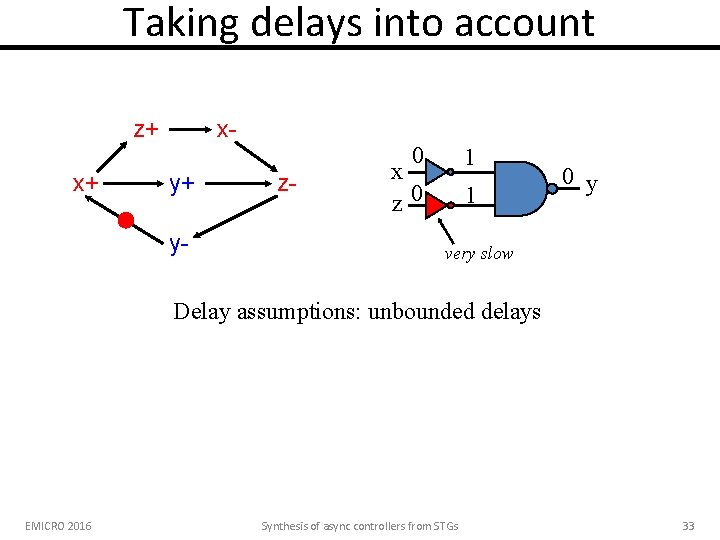

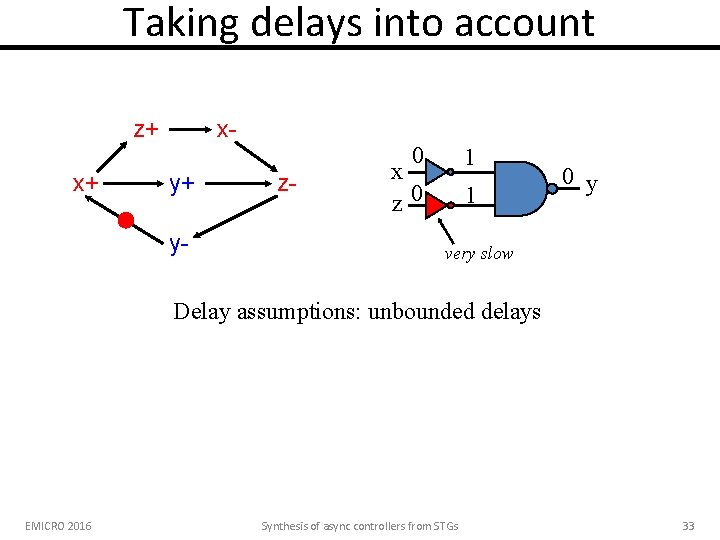

Taking delays into account z+ x+ xy+ y- 0 z- 1 x z 0 1 0 y very slow Delay assumptions: unbounded delays EMICRO 2016 Synthesis of async controllers from STGs 33

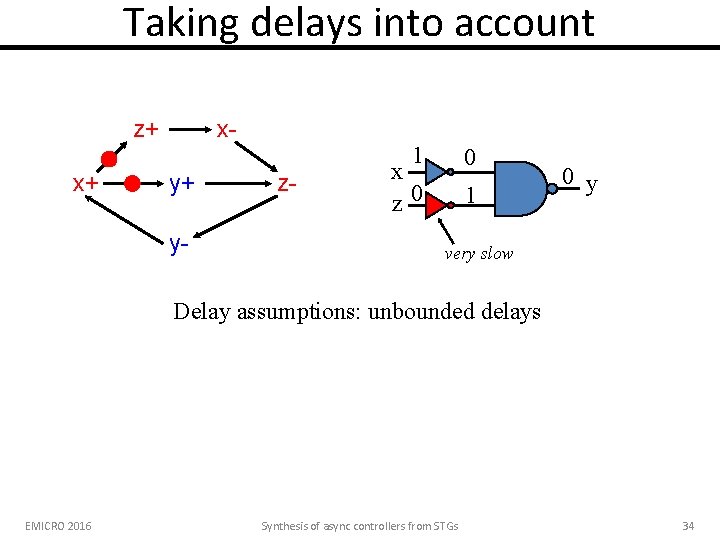

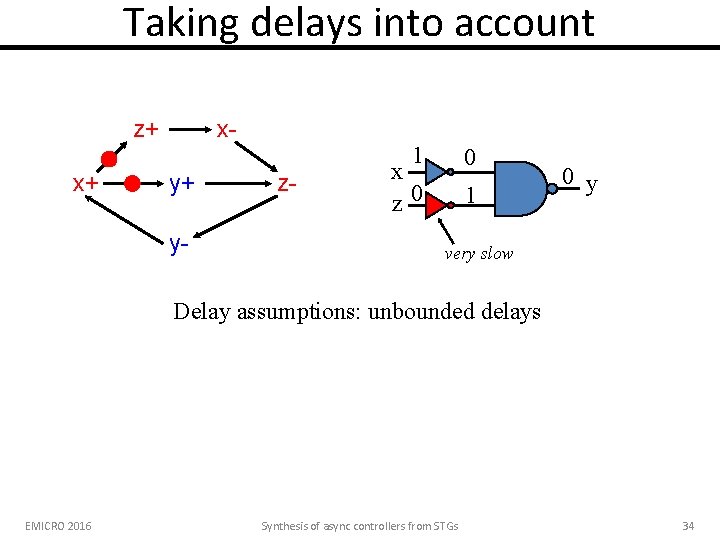

Taking delays into account z+ x+ xy+ y- 1 z- 0 x z 0 1 0 y very slow Delay assumptions: unbounded delays EMICRO 2016 Synthesis of async controllers from STGs 34

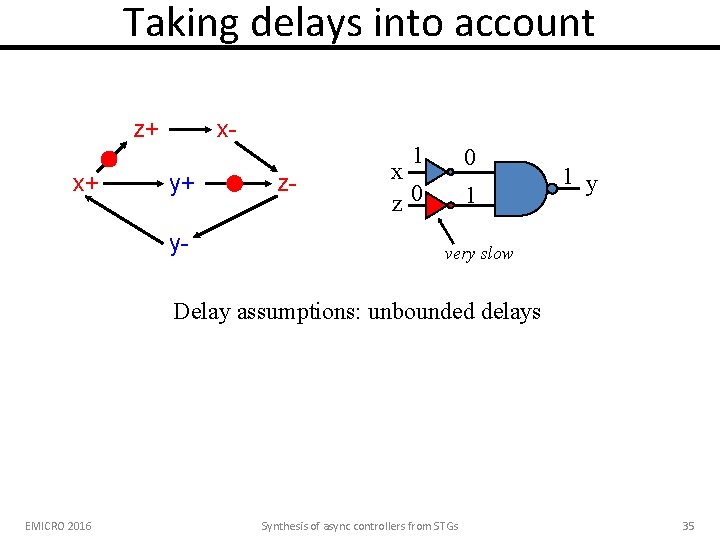

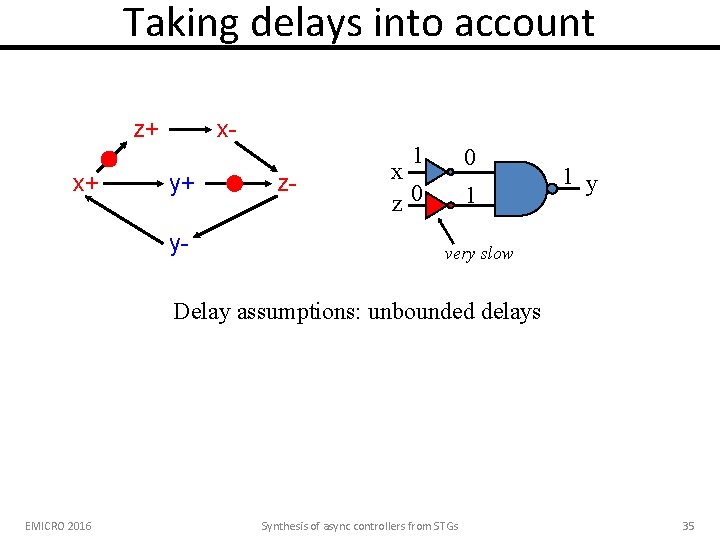

Taking delays into account z+ x+ xy+ y- 1 z- 0 x z 0 1 1 y very slow Delay assumptions: unbounded delays EMICRO 2016 Synthesis of async controllers from STGs 35

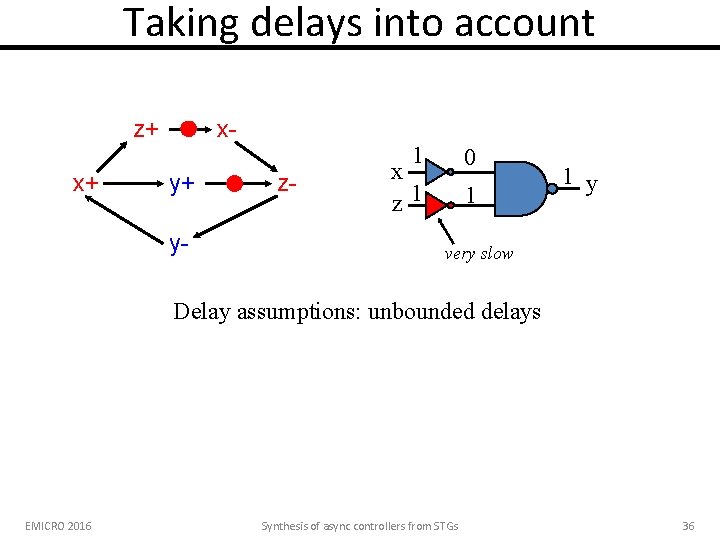

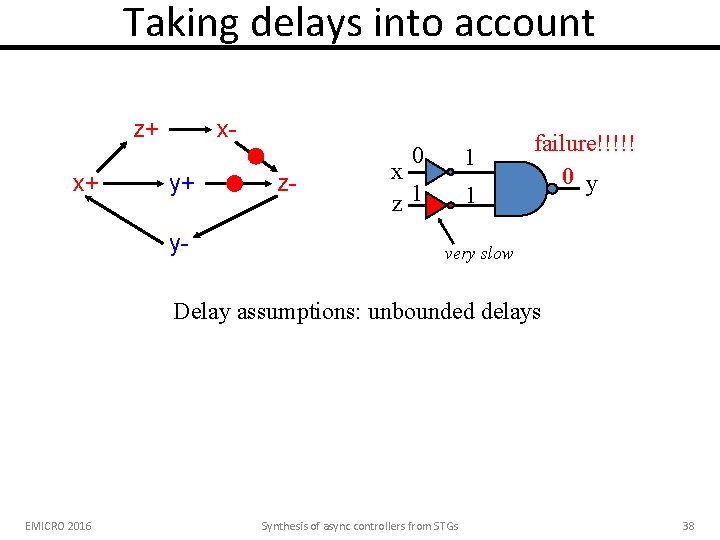

Taking delays into account z+ x+ xy+ y- 1 z- 0 x z 1 1 1 y very slow Delay assumptions: unbounded delays EMICRO 2016 Synthesis of async controllers from STGs 36

Taking delays into account z+ x+ xy+ y- 0 z- 1 x z 1 1 1 y very slow Delay assumptions: unbounded delays EMICRO 2016 Synthesis of async controllers from STGs 37

Taking delays into account z+ x+ xy+ y- 0 z- 1 x z 1 1 failure!!!!! 0 y very slow Delay assumptions: unbounded delays EMICRO 2016 Synthesis of async controllers from STGs 38

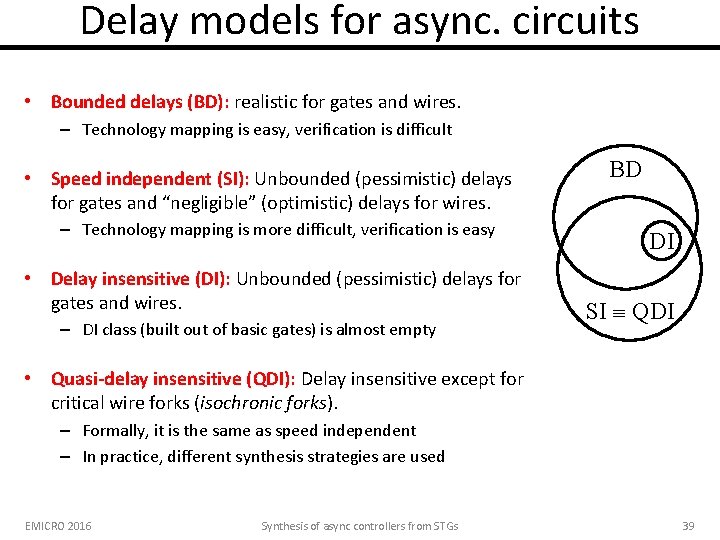

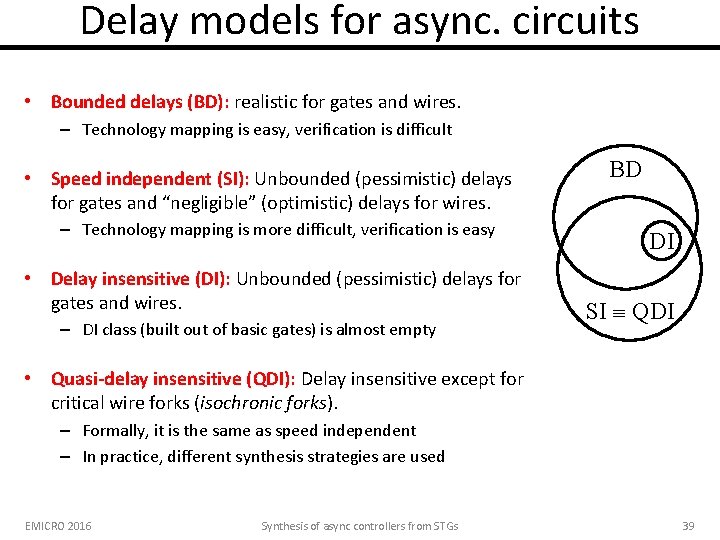

Delay models for async. circuits • Bounded delays (BD): realistic for gates and wires. – Technology mapping is easy, verification is difficult • Speed independent (SI): Unbounded (pessimistic) delays for gates and “negligible” (optimistic) delays for wires. – Technology mapping is more difficult, verification is easy • Delay insensitive (DI): Unbounded (pessimistic) delays for gates and wires. – DI class (built out of basic gates) is almost empty BD DI SI QDI • Quasi-delay insensitive (QDI): Delay insensitive except for critical wire forks (isochronic forks). – Formally, it is the same as speed independent – In practice, different synthesis strategies are used EMICRO 2016 Synthesis of async controllers from STGs 39

Synthesis of asynchronous controllers from STGs EMICRO 2016 Synthesis of async controllers from STGs 40

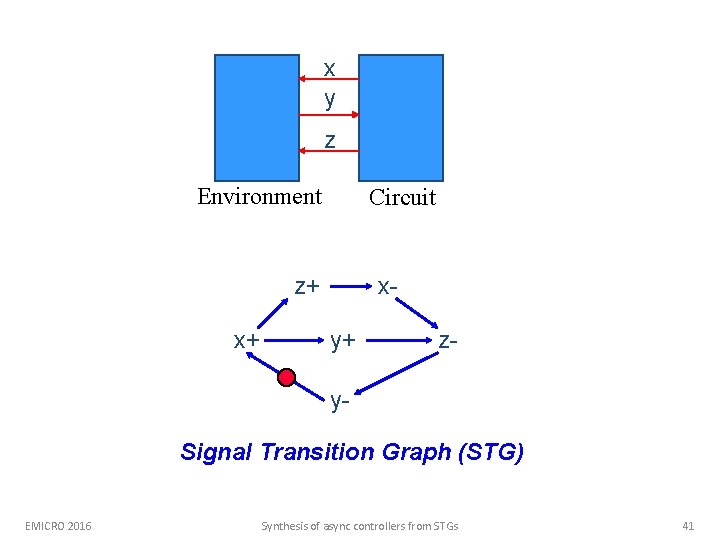

x y z Environment Circuit z+ x+ xy+ z- y. Signal Transition Graph (STG) EMICRO 2016 Synthesis of async controllers from STGs 41

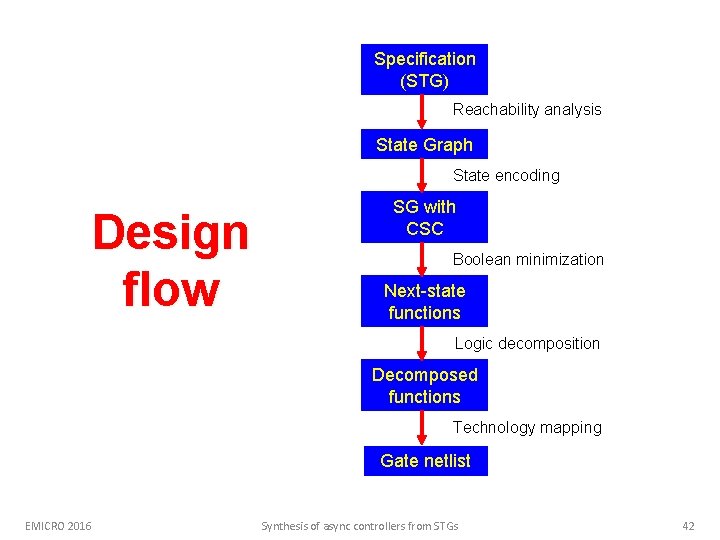

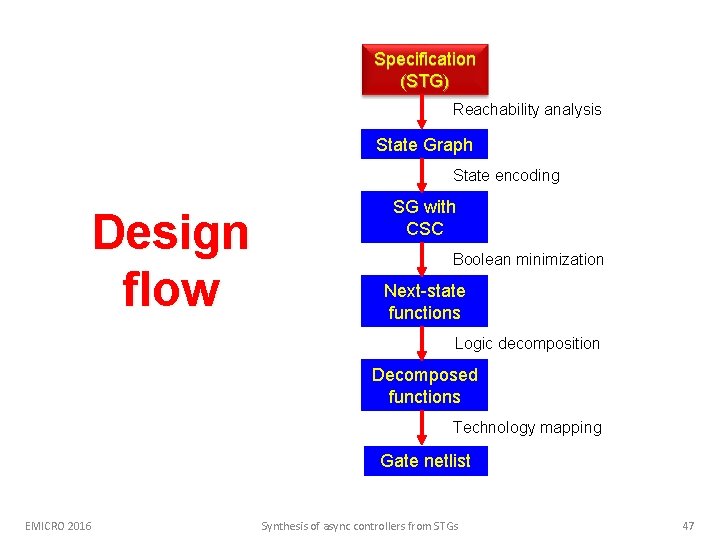

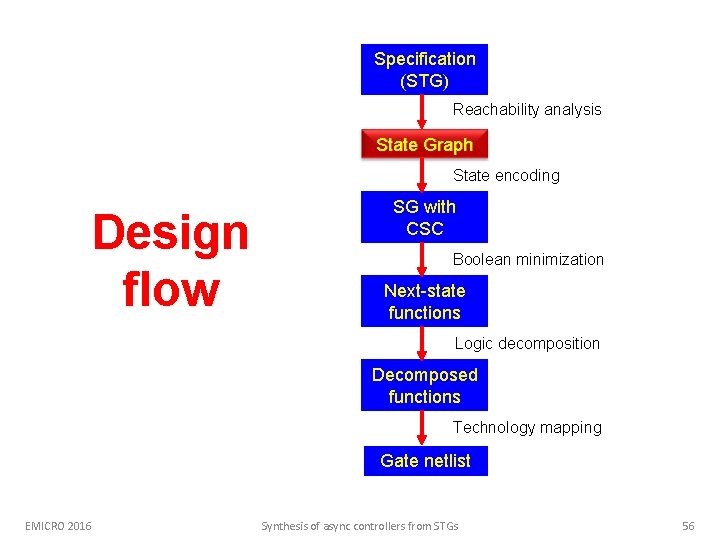

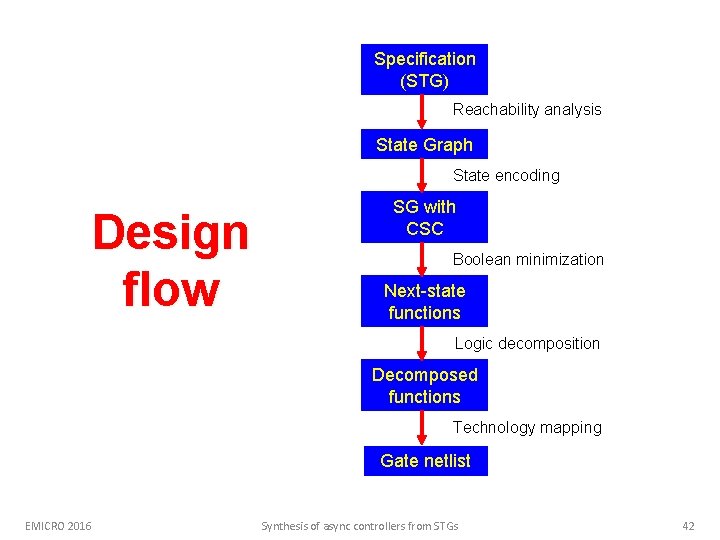

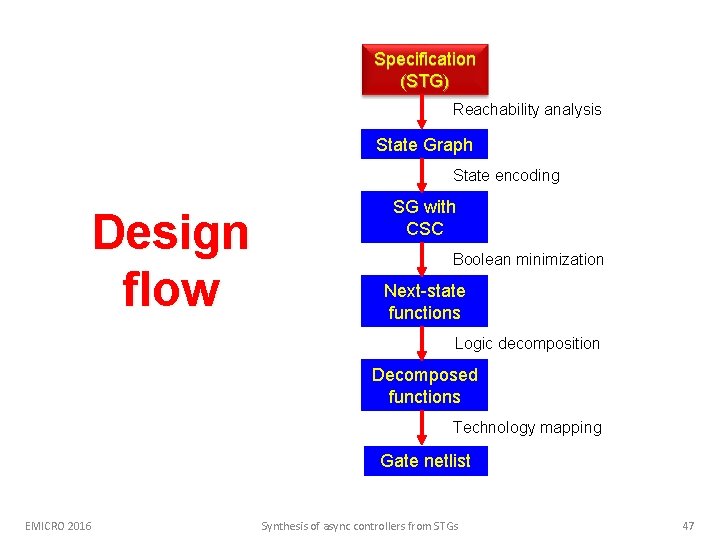

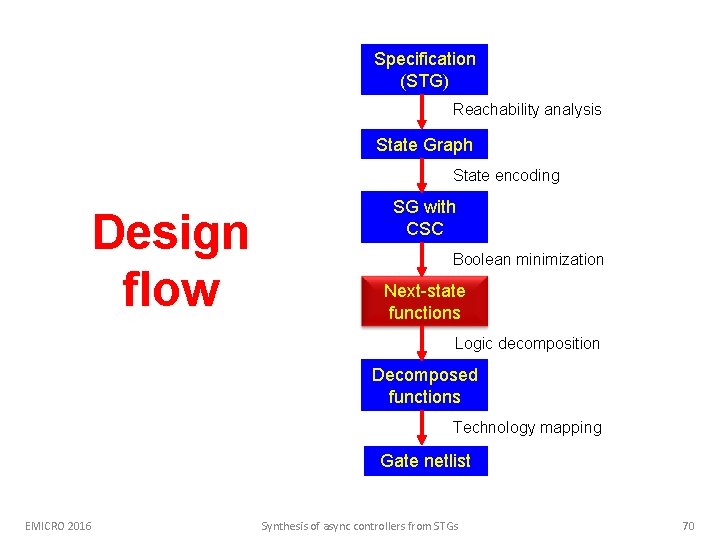

Specification (STG) Reachability analysis State Graph State encoding Design flow SG with CSC Boolean minimization Next-state functions Logic decomposition Decomposed functions Technology mapping Gate netlist EMICRO 2016 Synthesis of async controllers from STGs 42

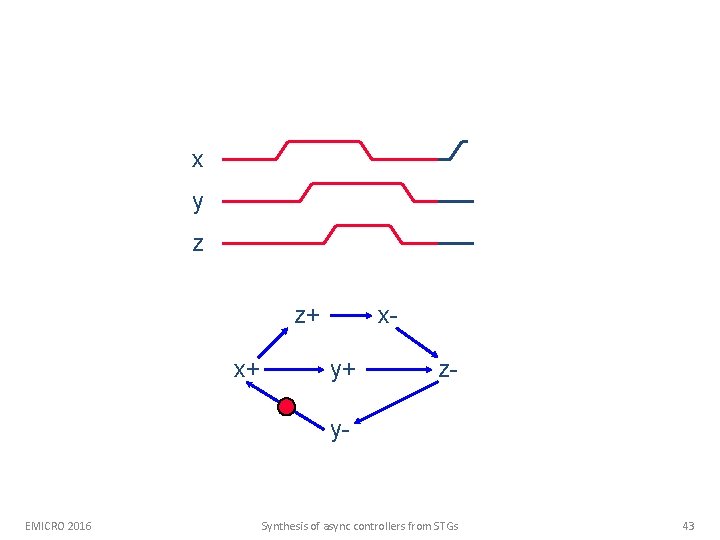

x y z z+ x+ xy+ z- y- EMICRO 2016 Synthesis of async controllers from STGs 43

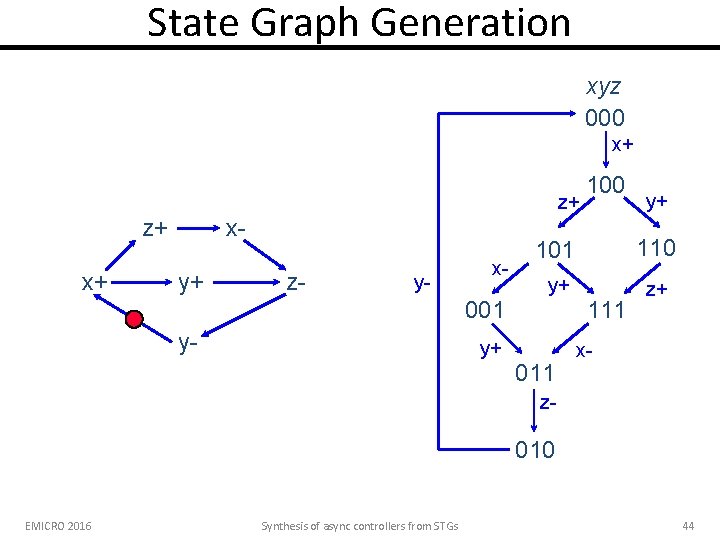

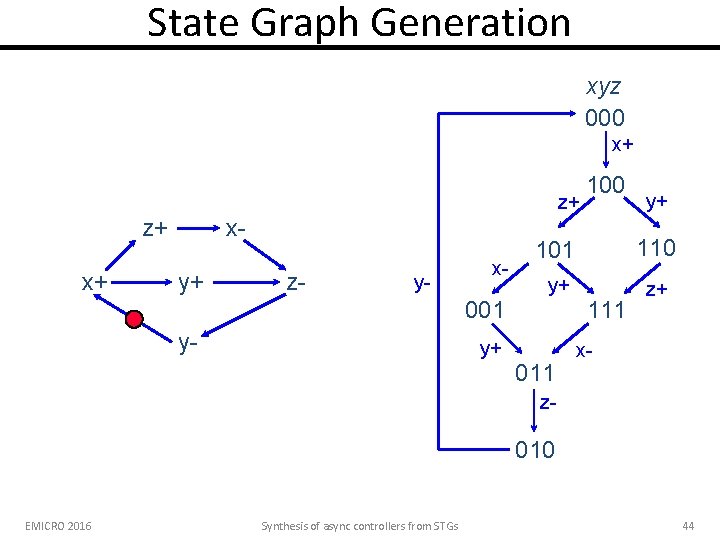

State Graph Generation xyz 000 x+ z+ z+ x+ xy+ z- y- x- 001 y- y+ 100 y+ 101 110 y+ z+ 011 111 x- z- 010 EMICRO 2016 Synthesis of async controllers from STGs 44

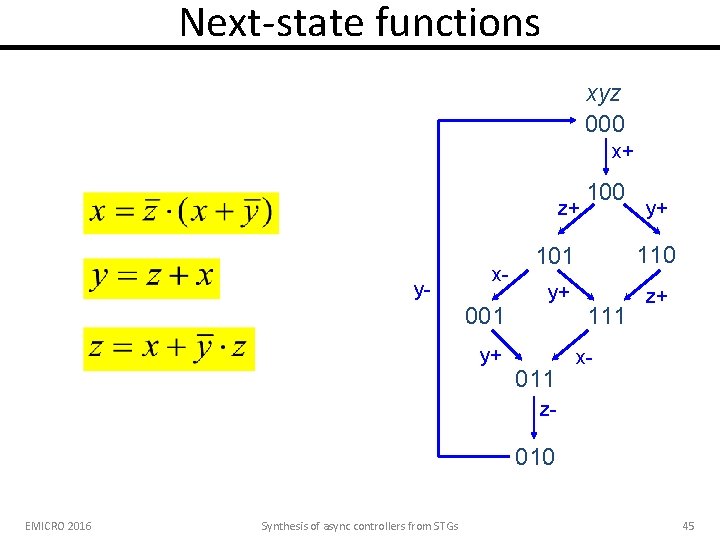

Next-state functions xyz 000 x+ z+ y- x- 001 y+ 100 y+ 101 110 y+ z+ 011 111 x- z- 010 EMICRO 2016 Synthesis of async controllers from STGs 45

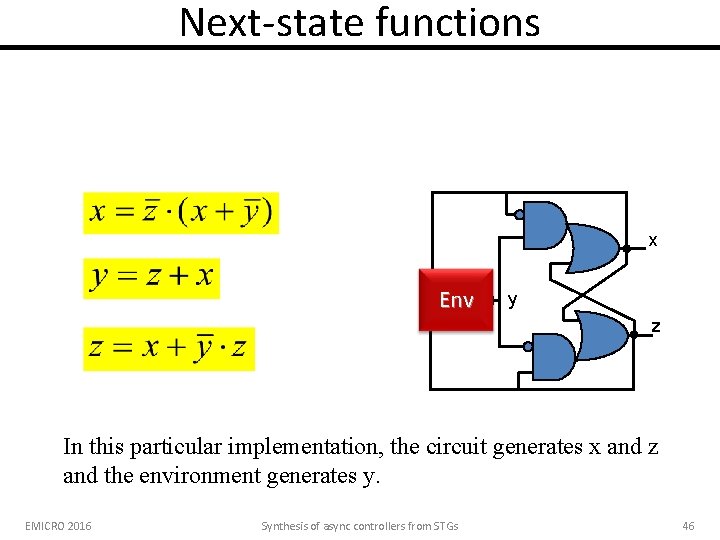

Next-state functions x Env y z In this particular implementation, the circuit generates x and z and the environment generates y. EMICRO 2016 Synthesis of async controllers from STGs 46

Specification (STG) Reachability analysis State Graph State encoding Design flow SG with CSC Boolean minimization Next-state functions Logic decomposition Decomposed functions Technology mapping Gate netlist EMICRO 2016 Synthesis of async controllers from STGs 47

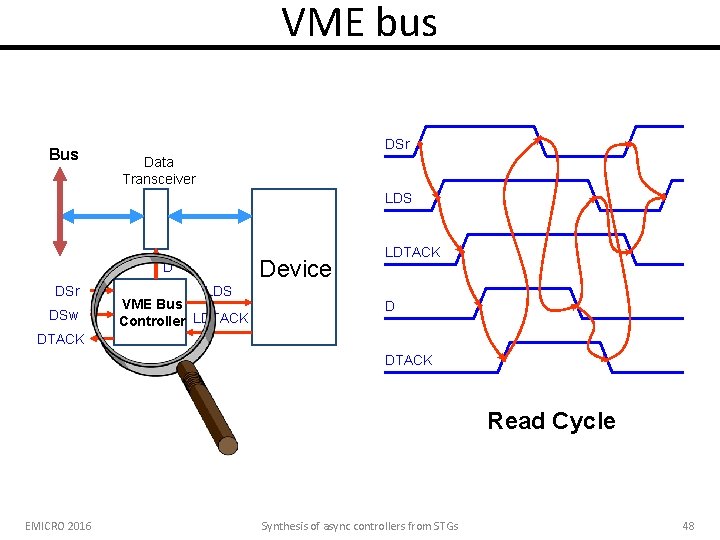

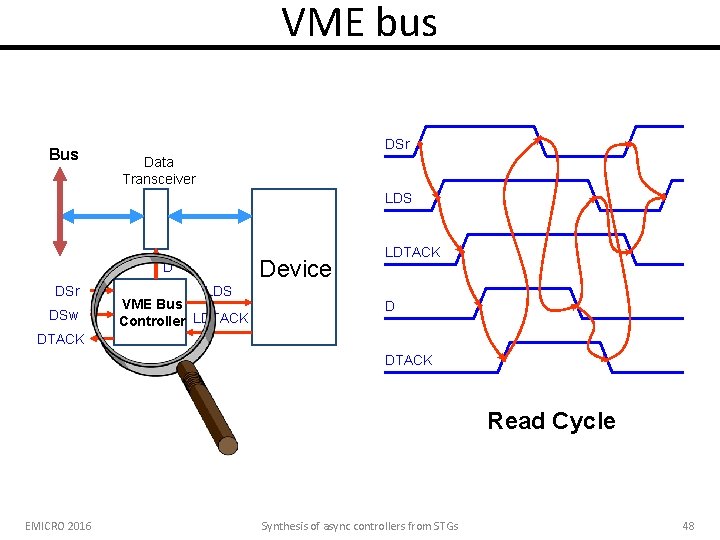

VME bus Bus DSr Data Transceiver LDS Device D DSr DSw LDS VME Bus Controller LDTACK D DTACK Read Cycle EMICRO 2016 Synthesis of async controllers from STGs 48

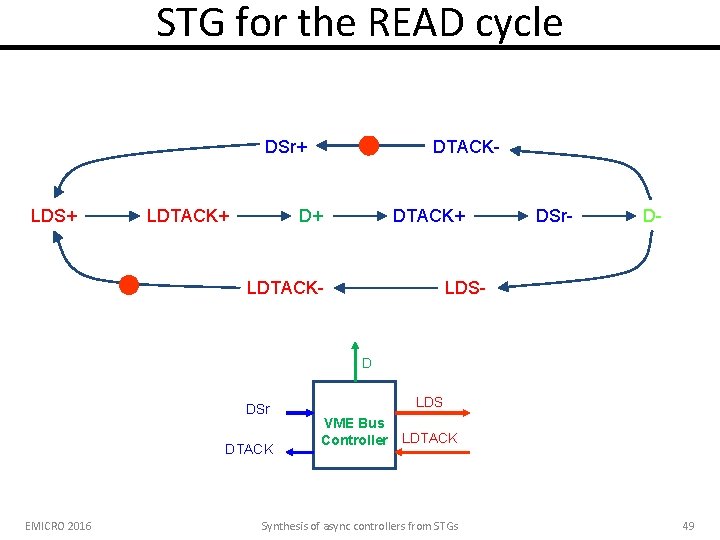

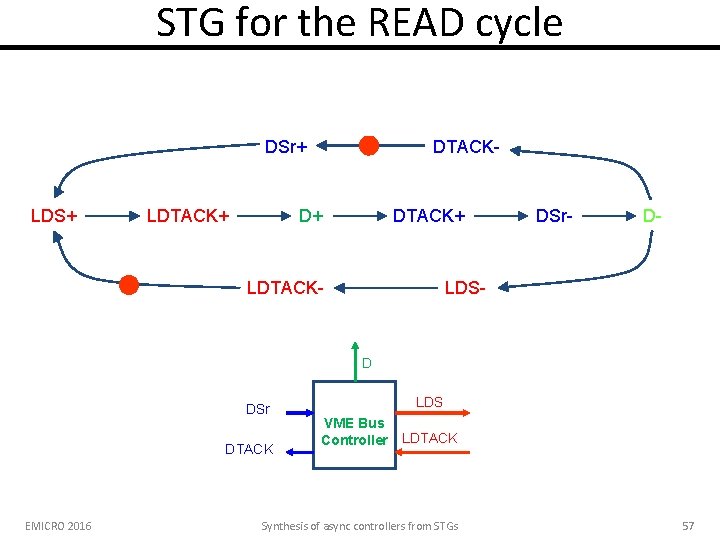

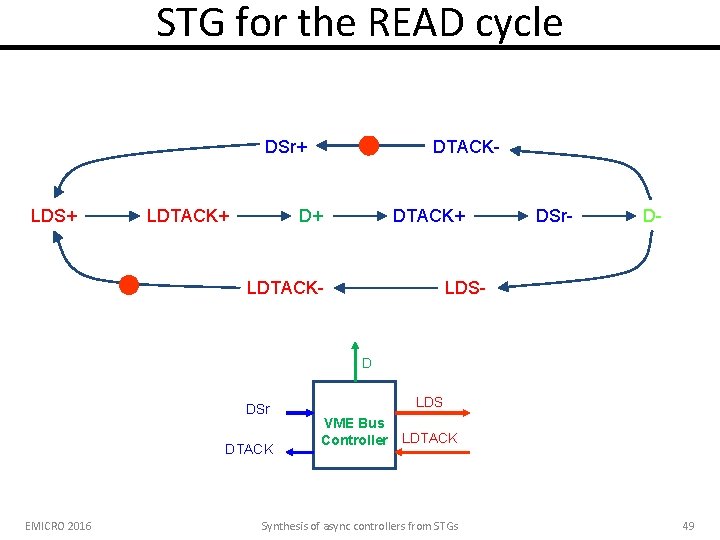

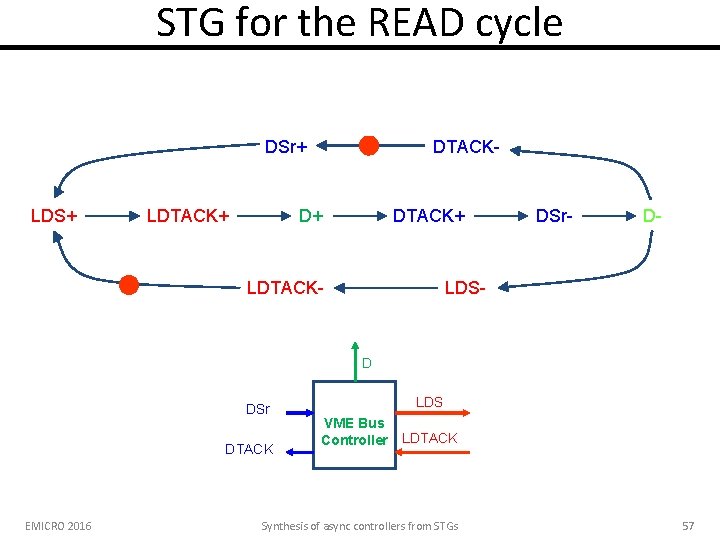

STG for the READ cycle DSr+ LDS+ LDTACK+ DTACK- D+ DTACK+ LDTACK- DSr- D- LDS- D DSr DTACK EMICRO 2016 LDS VME Bus Controller LDTACK Synthesis of async controllers from STGs 49

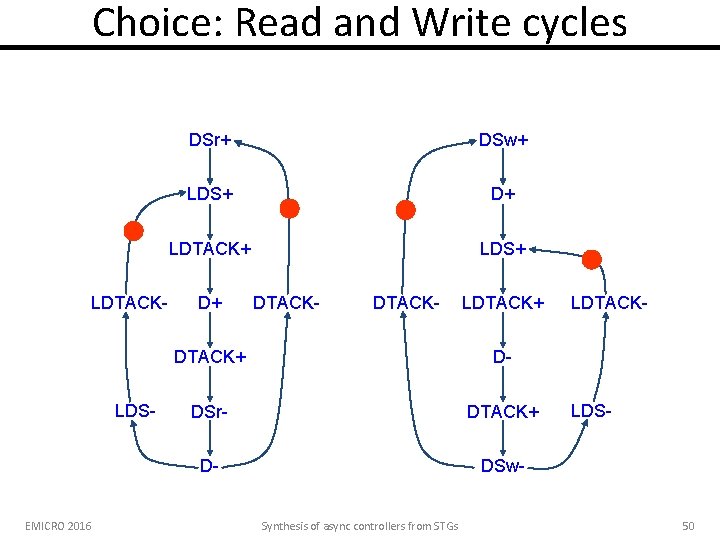

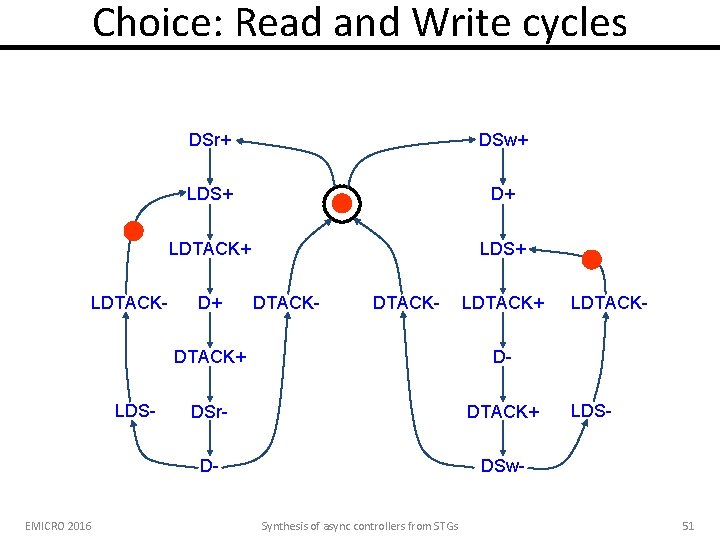

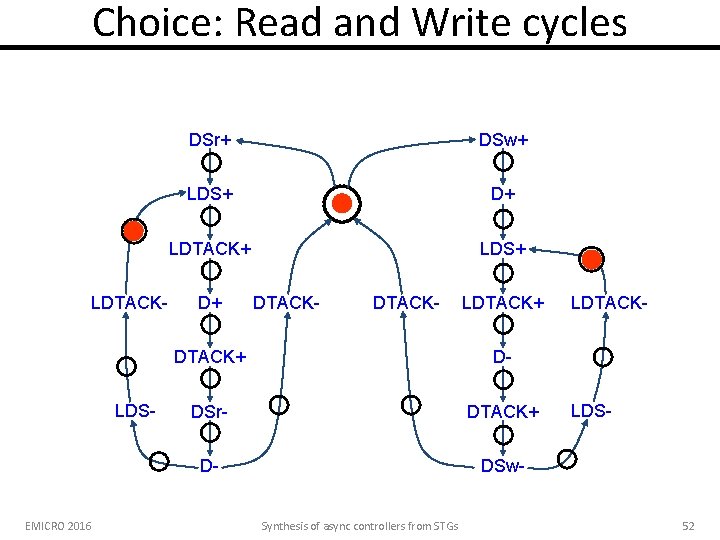

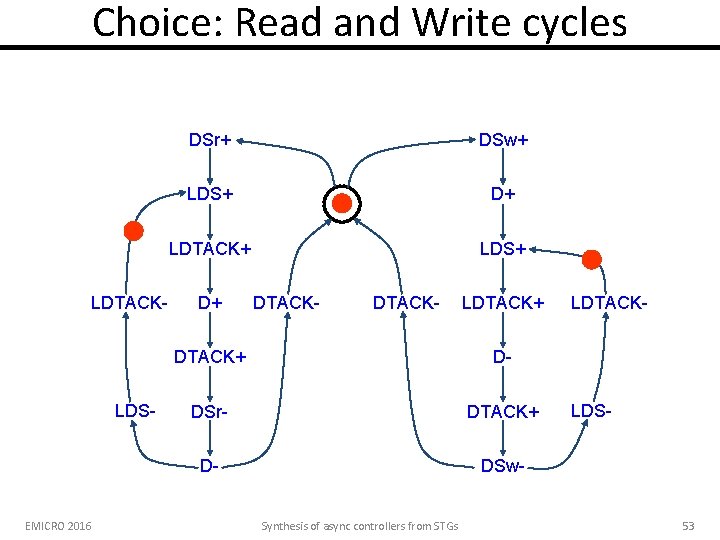

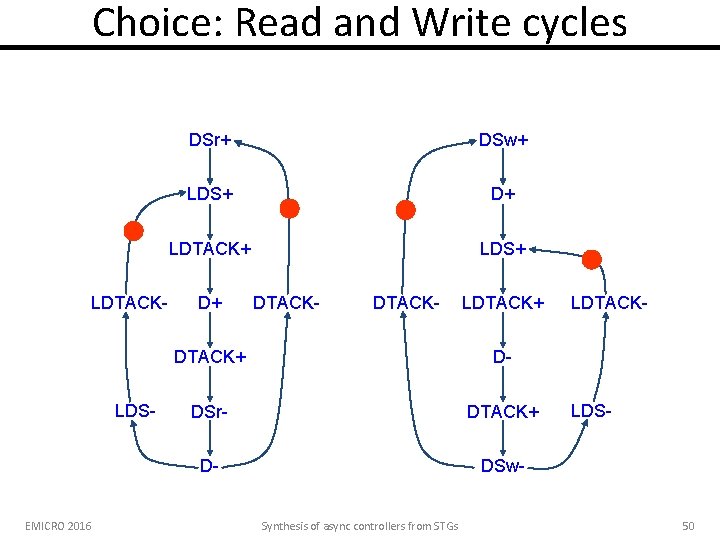

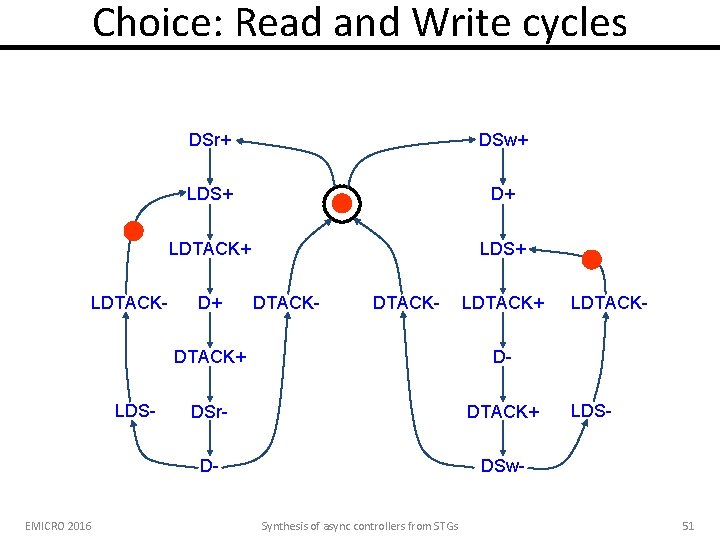

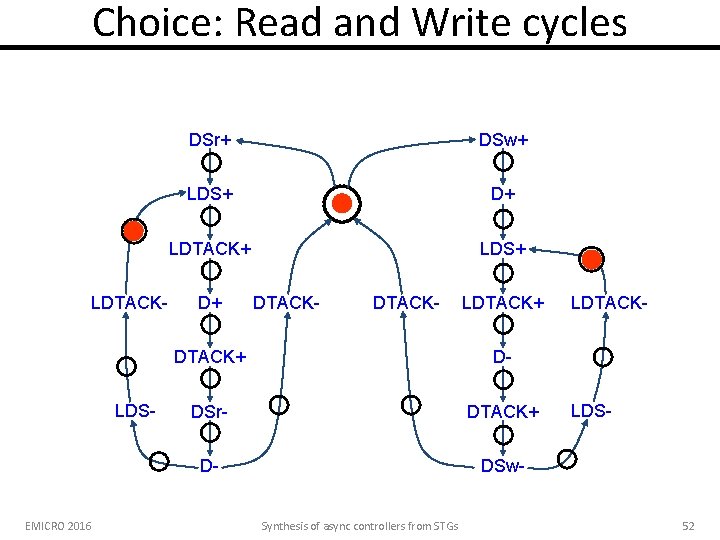

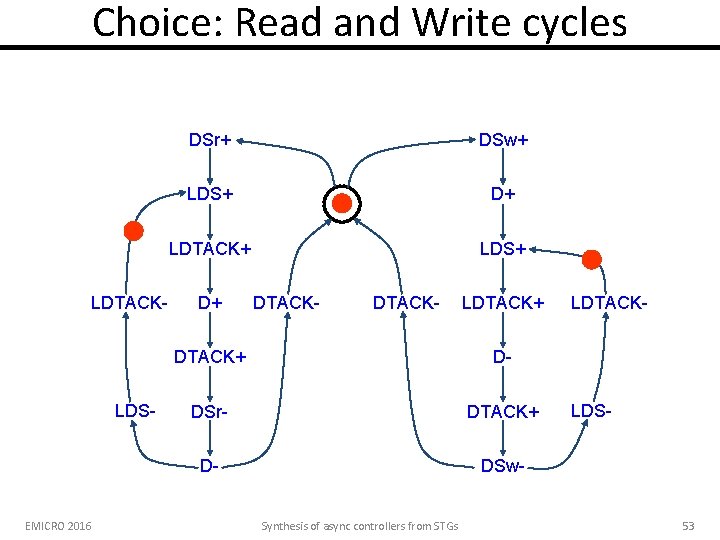

Choice: Read and Write cycles LDTACK- LDS- EMICRO 2016 DSr+ DSw+ LDS+ D+ LDTACK+ LDS+ D+ DTACK- LDTACK+ D- DSr- DTACK+ D- DSw. Synthesis of async controllers from STGs LDTACK- LDS- 50

Choice: Read and Write cycles LDTACK- LDS- EMICRO 2016 DSr+ DSw+ LDS+ D+ LDTACK+ LDS+ D+ DTACK- LDTACK+ D- DSr- DTACK+ D- DSw. Synthesis of async controllers from STGs LDTACK- LDS- 51

Choice: Read and Write cycles LDTACK- LDS- EMICRO 2016 DSr+ DSw+ LDS+ D+ LDTACK+ LDS+ D+ DTACK- LDTACK+ D- DSr- DTACK+ D- DSw. Synthesis of async controllers from STGs LDTACK- LDS- 52

Choice: Read and Write cycles LDTACK- LDS- EMICRO 2016 DSr+ DSw+ LDS+ D+ LDTACK+ LDS+ D+ DTACK- LDTACK+ D- DSr- DTACK+ D- DSw. Synthesis of async controllers from STGs LDTACK- LDS- 53

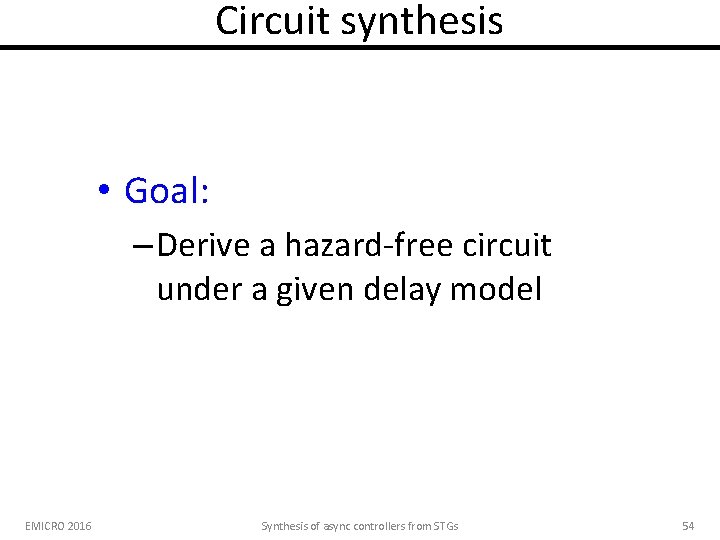

Circuit synthesis • Goal: – Derive a hazard-free circuit under a given delay model EMICRO 2016 Synthesis of async controllers from STGs 54

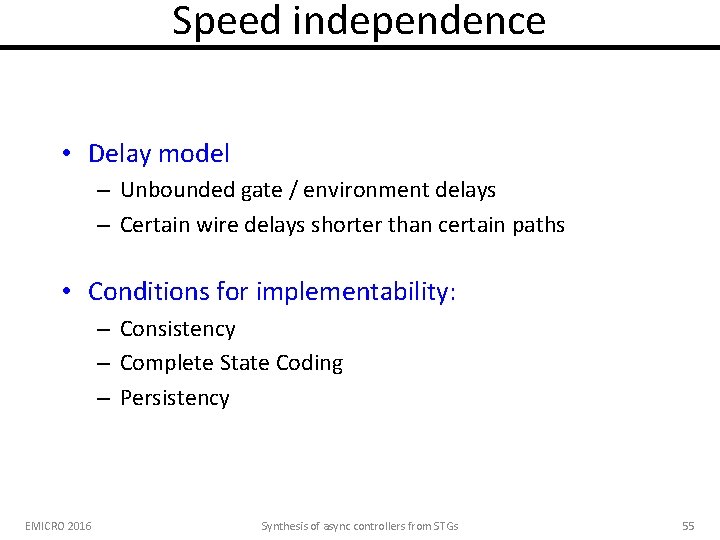

Speed independence • Delay model – Unbounded gate / environment delays – Certain wire delays shorter than certain paths • Conditions for implementability: – Consistency – Complete State Coding – Persistency EMICRO 2016 Synthesis of async controllers from STGs 55

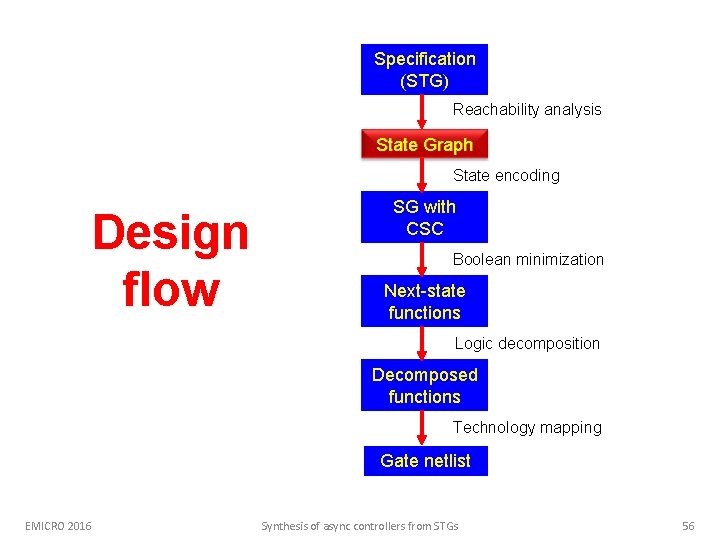

Specification (STG) Reachability analysis State Graph State encoding Design flow SG with CSC Boolean minimization Next-state functions Logic decomposition Decomposed functions Technology mapping Gate netlist EMICRO 2016 Synthesis of async controllers from STGs 56

STG for the READ cycle DSr+ LDS+ LDTACK+ DTACK- D+ DTACK+ LDTACK- DSr- D- LDS- D DSr DTACK EMICRO 2016 LDS VME Bus Controller LDTACK Synthesis of async controllers from STGs 57

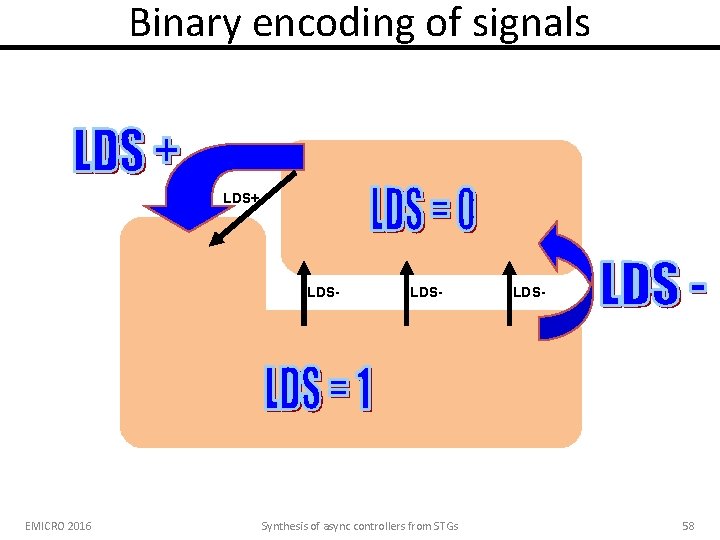

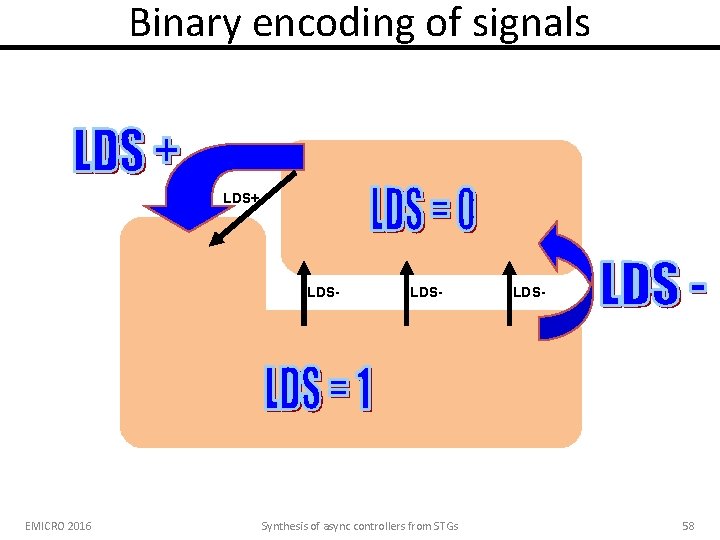

Binary encoding of signals DSr+ LDS+ LDTACKDSr+ LDTACK+ LDSDSr+ D+ LDTACK- LDS- DTACK- DDTACK+ EMICRO 2016 DTACK- DSr- Synthesis of async controllers from STGs 58

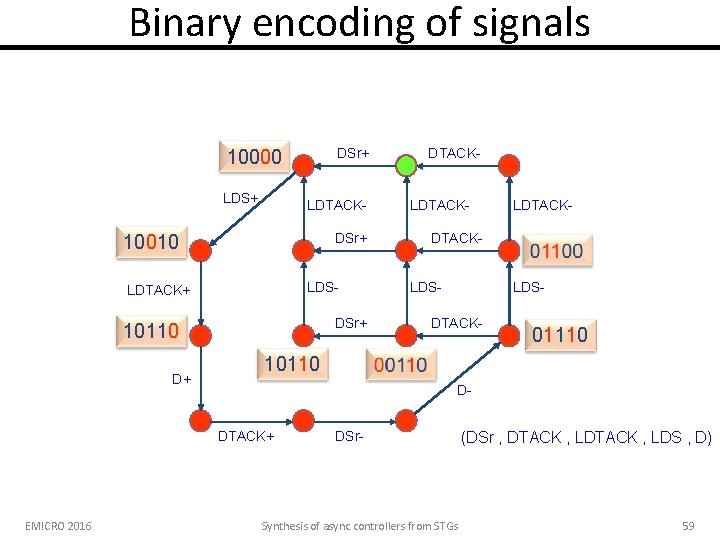

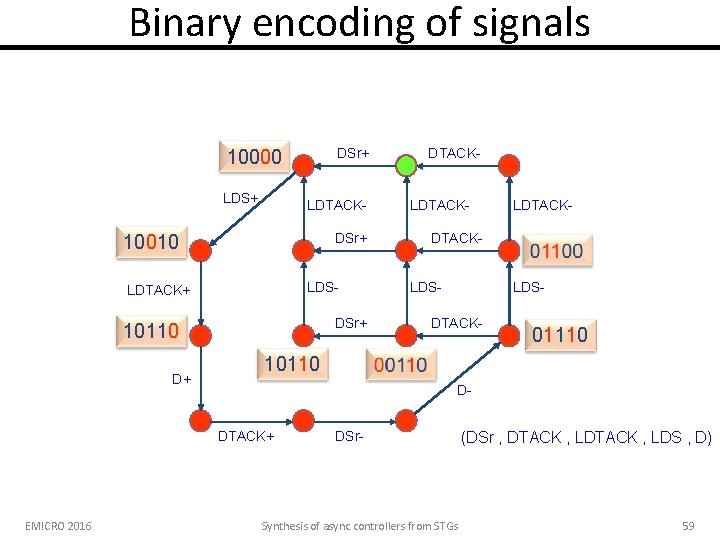

Binary encoding of signals DSr+ 10000 LDS+ LDTACKDSr+ 10010 LDS- LDTACK+ DSr+ 10110 D+ LDTACK- DTACKLDS- DTACK- 01110 10110 DDTACK+ EMICRO 2016 DTACK- DSr- Synthesis of async controllers from STGs (DSr , DTACK , LDS , D) 59

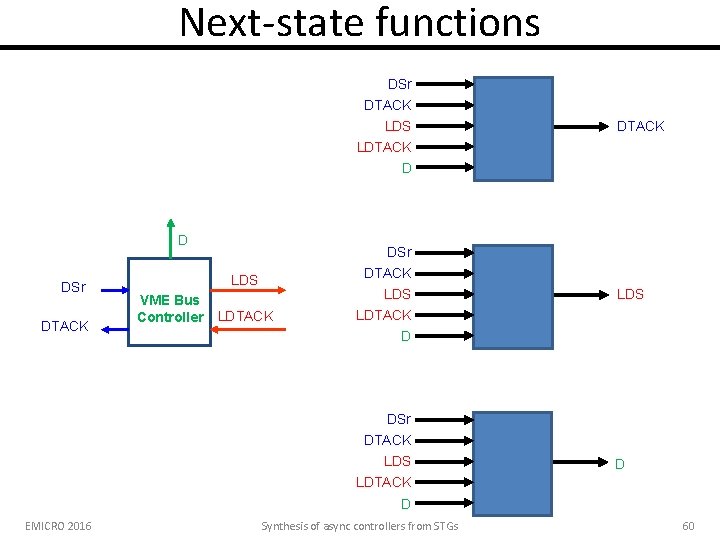

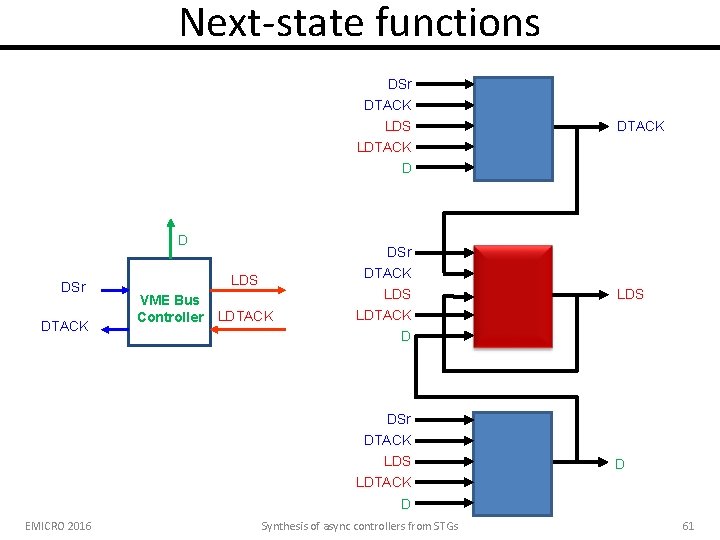

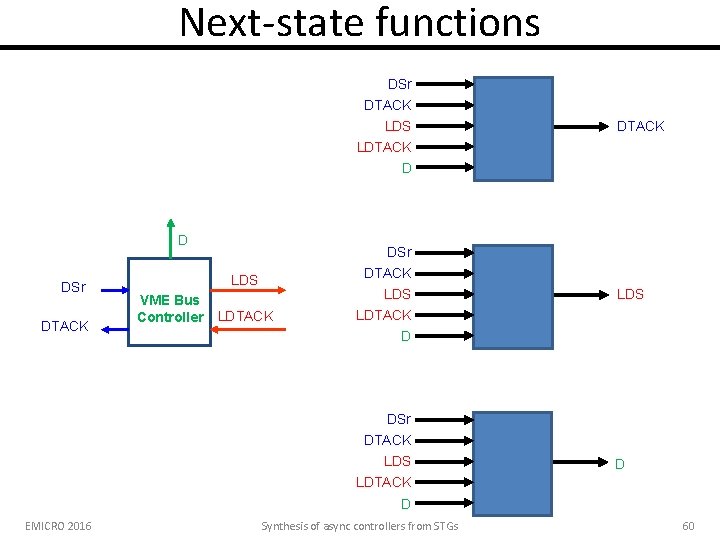

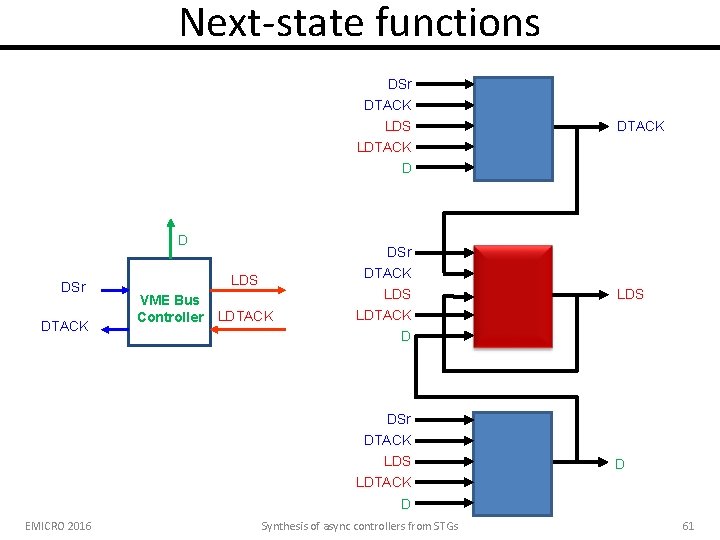

Next-state functions DSr DTACK LDS DTACK LDTACK D D DSr DTACK VME Bus Controller DSr LDS DTACK LDTACK LDS D DSr DTACK LDS D LDTACK D EMICRO 2016 Synthesis of async controllers from STGs 60

Next-state functions DSr DTACK LDS DTACK LDTACK D D DSr DTACK VME Bus Controller DSr LDS DTACK LDS LDTACK LDS D DSr DTACK LDS D LDTACK D EMICRO 2016 Synthesis of async controllers from STGs 61

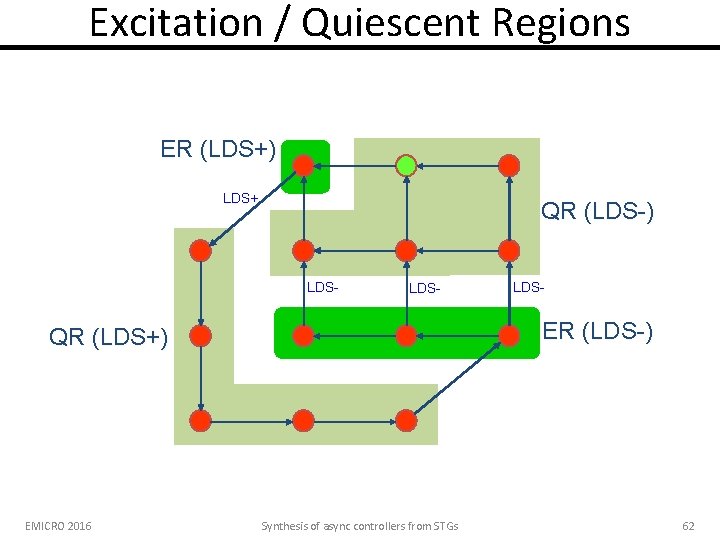

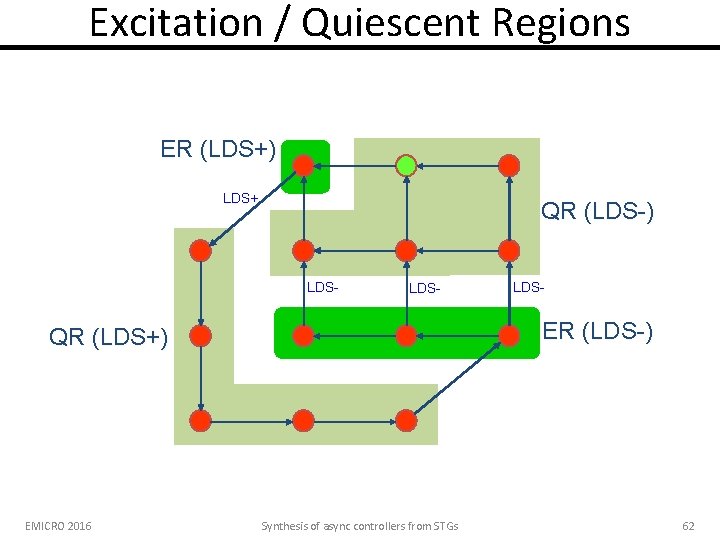

Excitation / Quiescent Regions ER (LDS+) LDS+ QR (LDS-) LDS- ER (LDS-) QR (LDS+) EMICRO 2016 LDS- Synthesis of async controllers from STGs 62

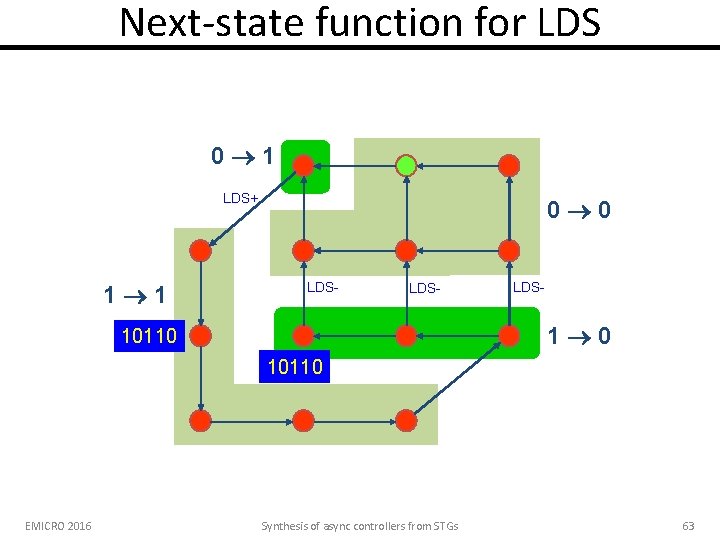

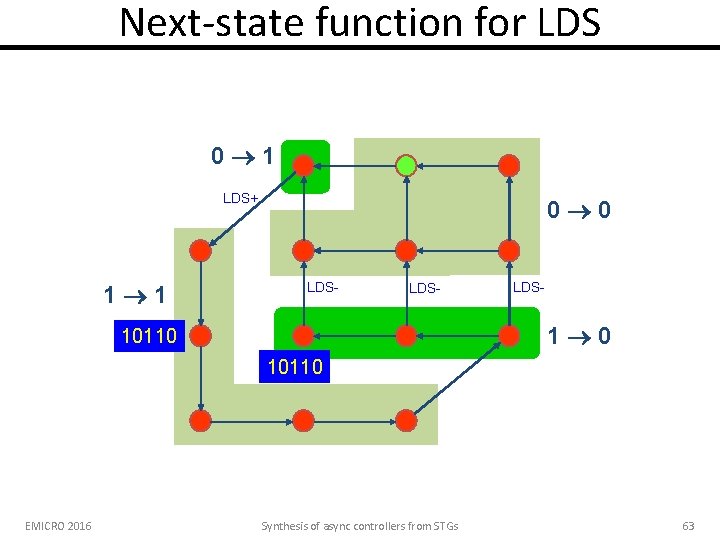

Next-state function for LDS 0 1 LDS+ 1 1 0 0 LDS- 1 0 10110 EMICRO 2016 Synthesis of async controllers from STGs 63

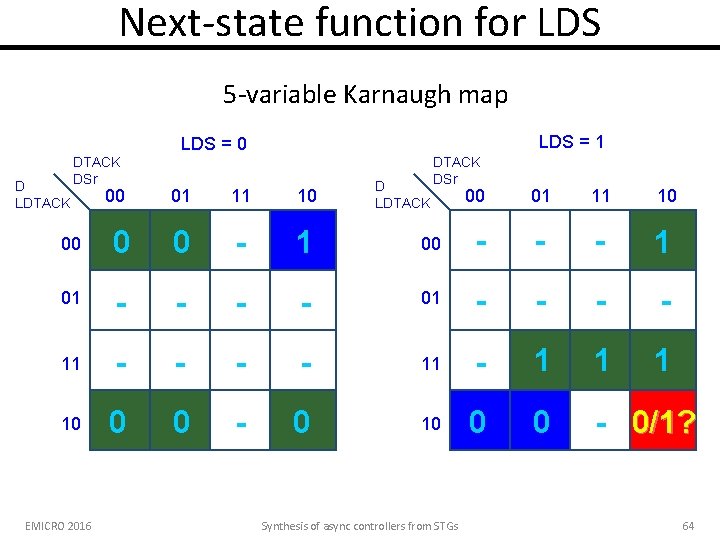

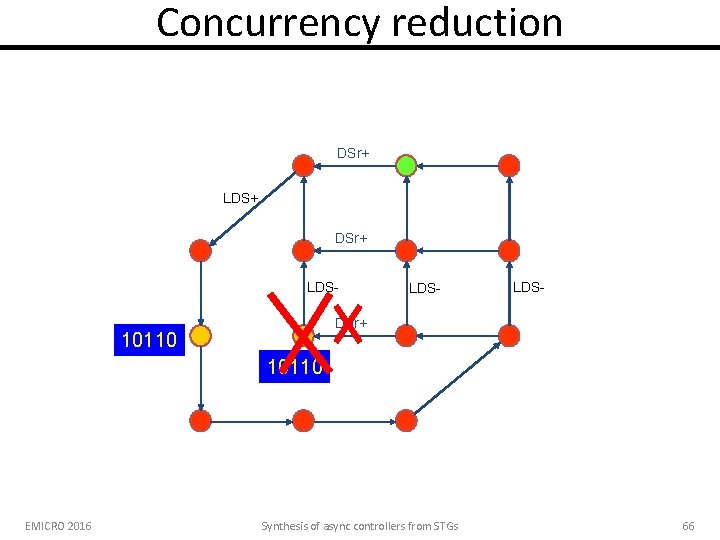

Next-state function for LDS 5 -variable Karnaugh map LDS = 1 LDS = 0 D LDTACK DSr 00 01 11 10 00 0 0 - 1 00 - - - 1 01 - - - - 11 - 1 10 0 0 - 0/1? EMICRO 2016 Synthesis of async controllers from STGs 64

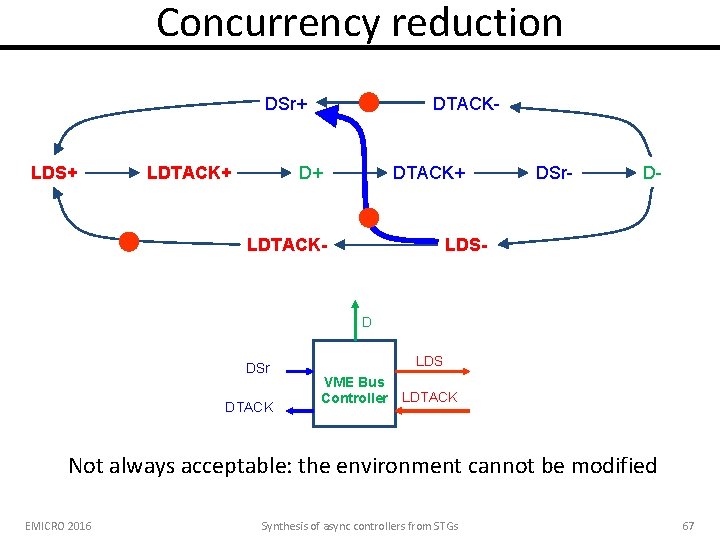

Specification (STG) Reachability analysis State Graph State encoding Design flow SG with CSC Boolean minimization Next-state functions Logic decomposition Decomposed functions Technology mapping Gate netlist EMICRO 2016 Synthesis of async controllers from STGs 65

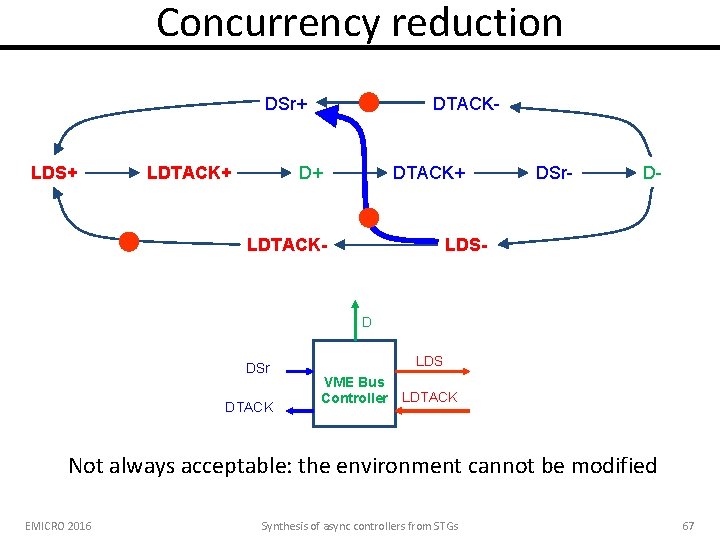

Concurrency reduction DSr+ LDS+ DSr+ LDS- DSr+ 10110 EMICRO 2016 Synthesis of async controllers from STGs 66

Concurrency reduction DSr+ LDS+ LDTACK+ DTACK- D+ DTACK+ LDTACK- DSr- D- LDS- D DSr DTACK LDS VME Bus Controller LDTACK Not always acceptable: the environment cannot be modified EMICRO 2016 Synthesis of async controllers from STGs 67

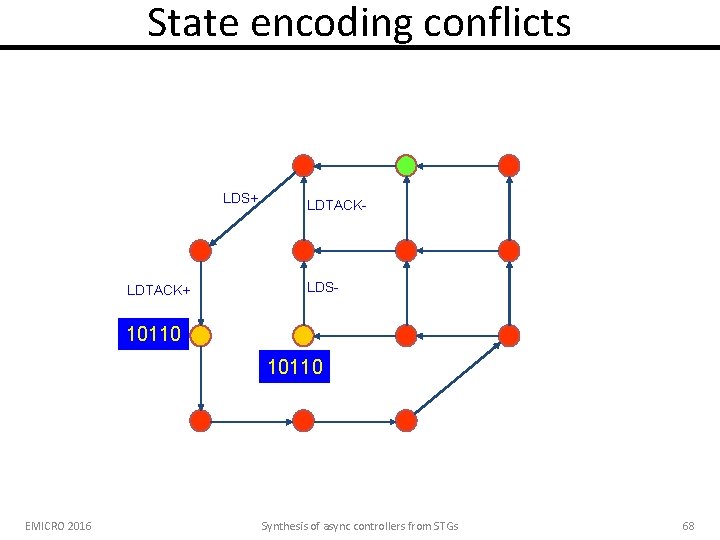

State encoding conflicts LDS+ LDTACK- LDS- 10110 EMICRO 2016 Synthesis of async controllers from STGs 68

Signal Insertion CSC+ LDS+ LDTACK- LDS- 101101 101100 D- DSr- EMICRO 2016 CSC- Synthesis of async controllers from STGs 69

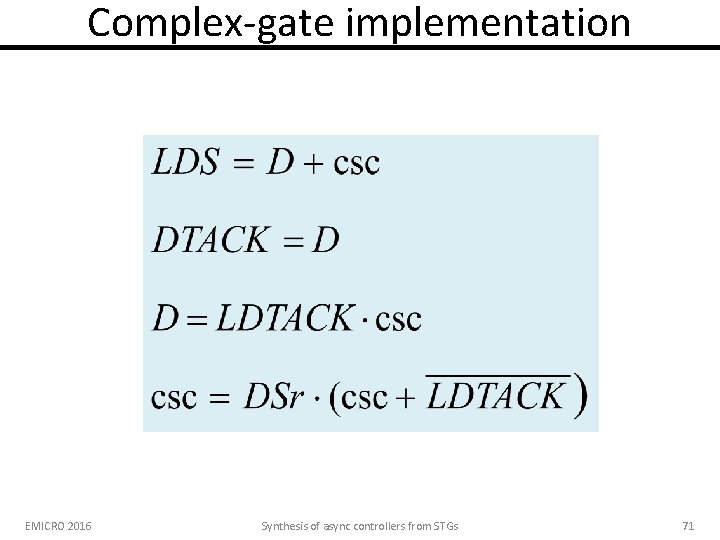

Specification (STG) Reachability analysis State Graph State encoding Design flow SG with CSC Boolean minimization Next-state functions Logic decomposition Decomposed functions Technology mapping Gate netlist EMICRO 2016 Synthesis of async controllers from STGs 70

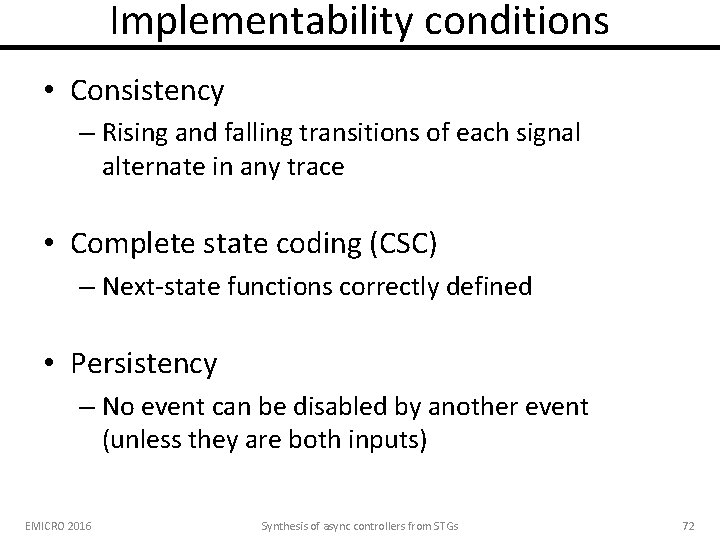

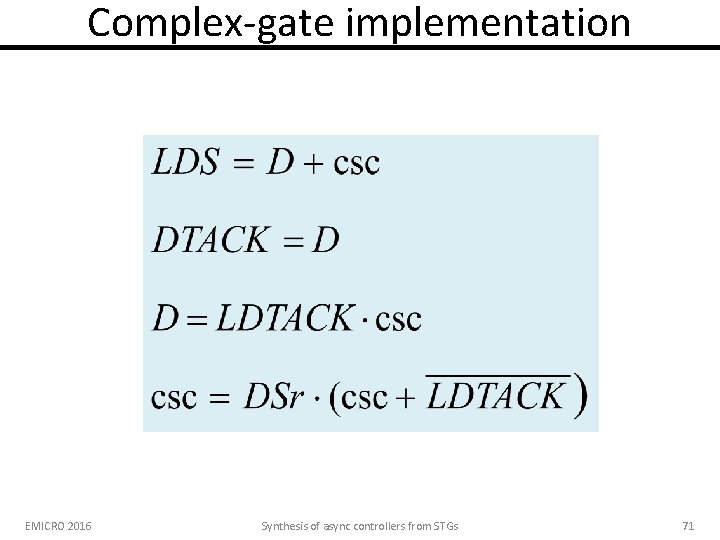

Complex-gate implementation EMICRO 2016 Synthesis of async controllers from STGs 71

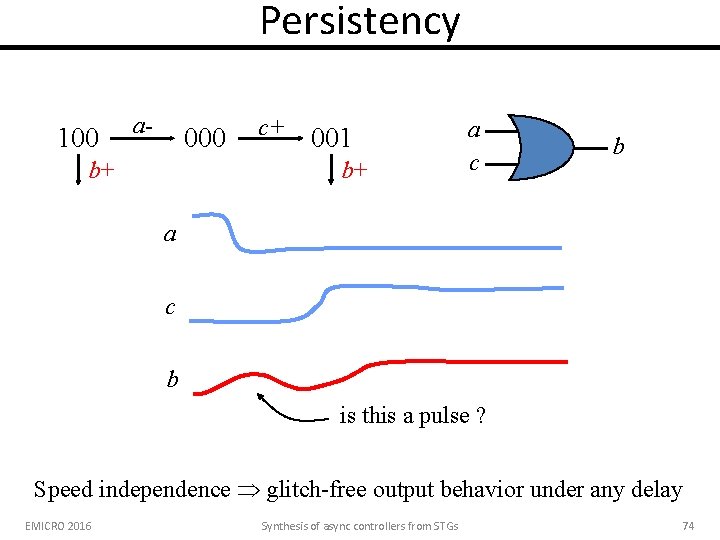

Implementability conditions • Consistency – Rising and falling transitions of each signal alternate in any trace • Complete state coding (CSC) – Next-state functions correctly defined • Persistency – No event can be disabled by another event (unless they are both inputs) EMICRO 2016 Synthesis of async controllers from STGs 72

Implementability conditions • Consistency + CSC + persistency • There exists a speed-independent circuit that implements the behavior of the STG (under the assumption that any Boolean function can be implemented with one complex gate) EMICRO 2016 Synthesis of async controllers from STGs 73

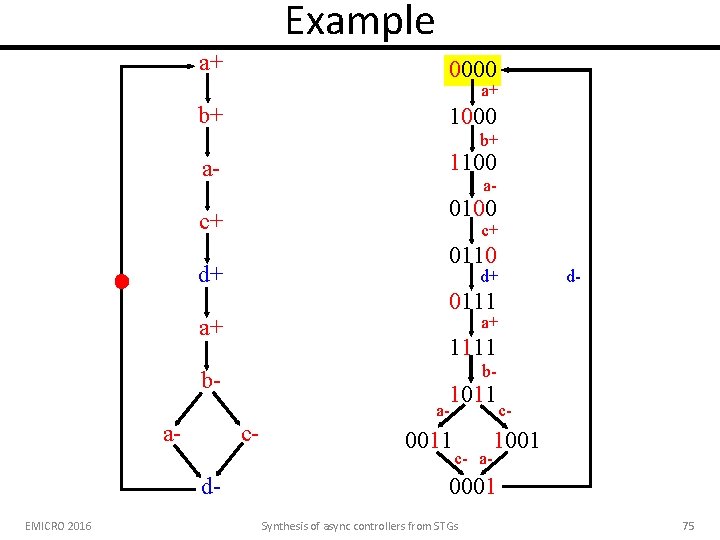

Persistency 100 a- 000 c+ 001 b+ b+ a c b is this a pulse ? Speed independence glitch-free output behavior under any delay EMICRO 2016 Synthesis of async controllers from STGs 74

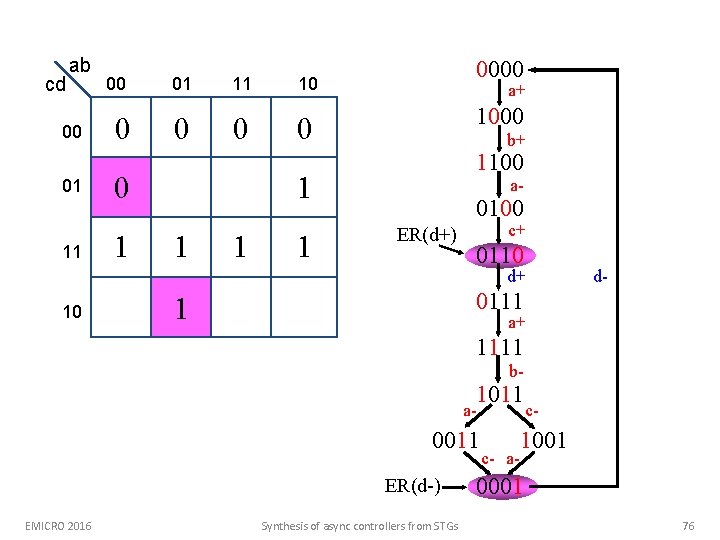

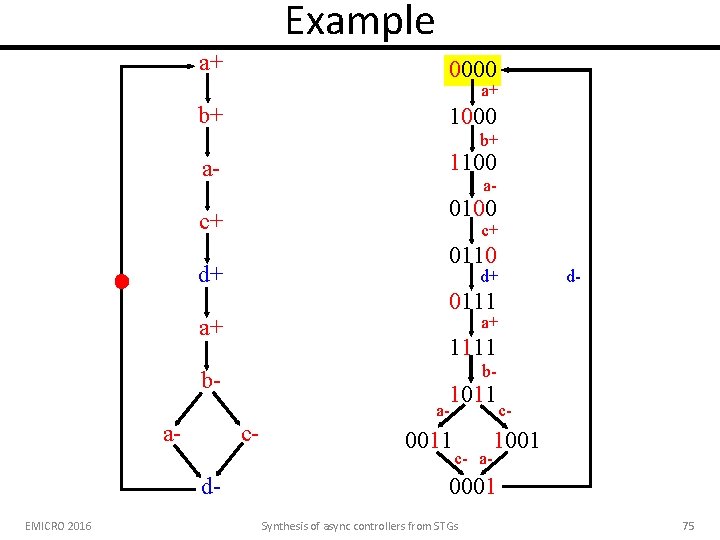

Example a+ 0000 a+ b+ 1000 b+ 1100 a- a- 0100 c+ c+ 0110 d+ d+ 0111 a+ a+ 1111 b- ba- EMICRO 2016 1011 cd- d- a- 0011 c- a- c- 1001 0001 Synthesis of async controllers from STGs 75

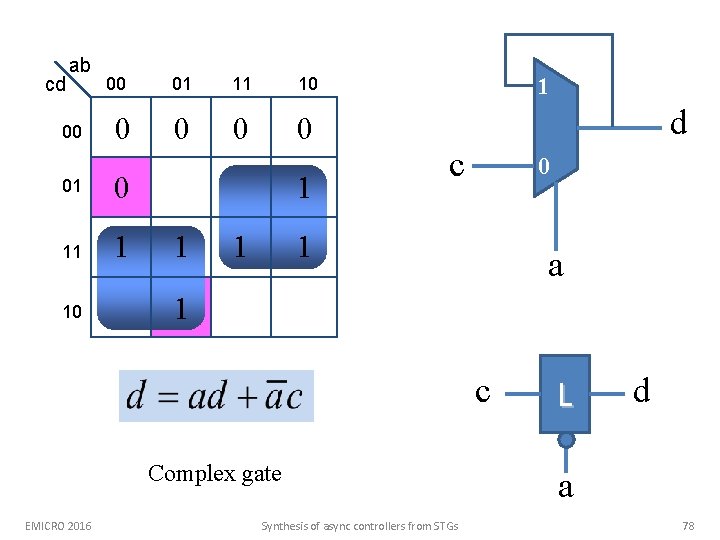

cd ab 00 01 11 00 0 01 0 11 0 a+ 1000 0 b+ 1100 1 0000 10 1 1 1 a- 0100 ER(d+) c+ 0110 d+ 10 d- 0111 1 a+ 1111 b- 1011 a- 0011 ER(d-) EMICRO 2016 Synthesis of async controllers from STGs c- a- c- 1001 0001 76

cd ab 00 01 11 00 0 01 0 11 0 a+ 1000 0 b+ 1100 1 0000 10 1 a- 0100 c+ 1 1 0110 d+ 10 d- 0111 1 a+ 1111 b- 1011 a- 0011 Complex gate EMICRO 2016 Synthesis of async controllers from STGs c- a- c- 1001 0001 77

cd ab 00 00 01 11 10 0 0 01 0 11 1 10 1 1 1 d c 0 1 1 a 1 c Complex gate EMICRO 2016 Synthesis of async controllers from STGs L d a 78

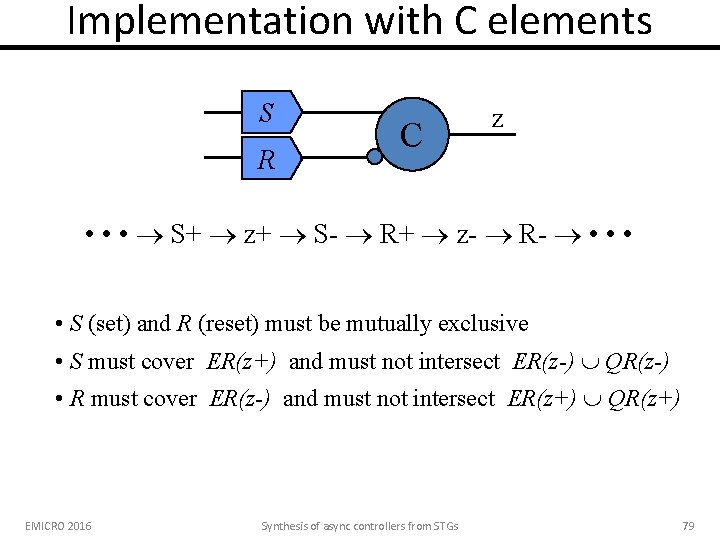

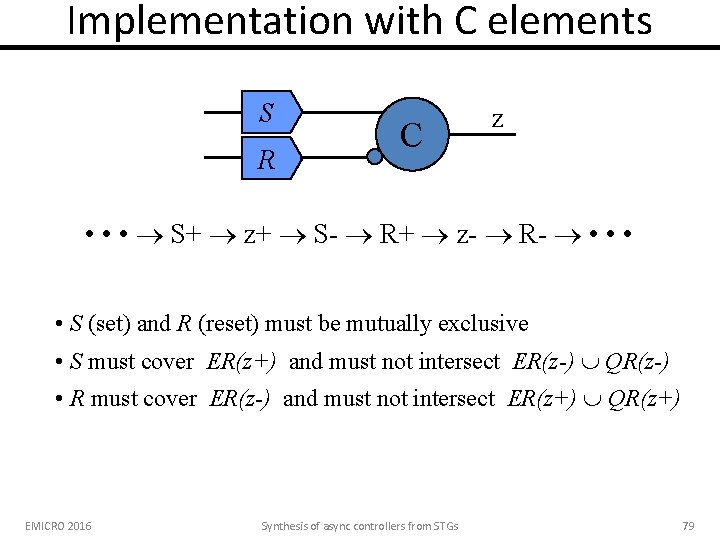

Implementation with C elements S R C z • • • S+ z+ S- R+ z- R- • • S (set) and R (reset) must be mutually exclusive • S must cover ER(z+) and must not intersect ER(z-) QR(z-) • R must cover ER(z-) and must not intersect ER(z+) QR(z+) EMICRO 2016 Synthesis of async controllers from STGs 79

cd ab 00 01 11 00 0 01 0 11 0 a+ 1000 0 b+ 1100 1 0000 10 1 a- 0100 c+ 1 1 0110 d+ 10 d- 0111 1 a+ 1111 b- 1011 S R C d a- 0011 c- a- c- 1001 0001 EMICRO 2016 Synthesis of async controllers from STGs 80

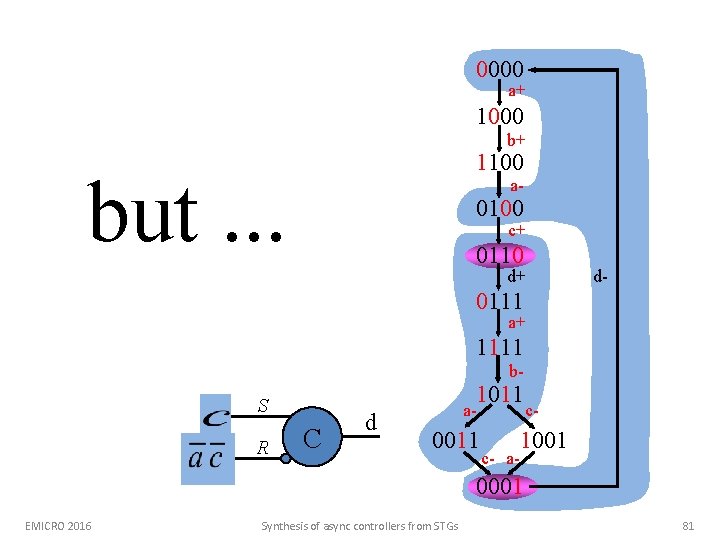

0000 a+ 1000 b+ 1100 but. . . a- 0100 c+ 0110 d+ d- 0111 a+ 1111 b- 1011 S R C d a- 0011 c- a- c- 1001 0001 EMICRO 2016 Synthesis of async controllers from STGs 81

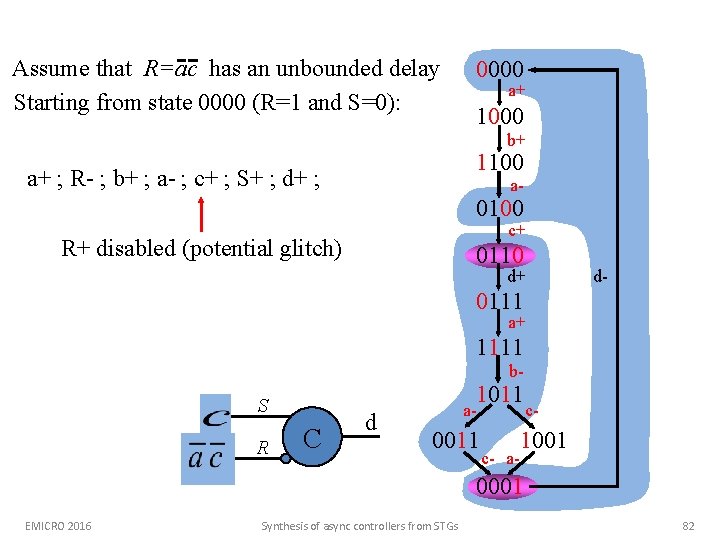

Assume that R=ac has an unbounded delay Starting from state 0000 (R=1 and S=0): 0000 a+ 1000 b+ 1100 a+ ; R- ; b+ ; a- ; c+ ; S+ ; d+ ; a- 0100 c+ R+ disabled (potential glitch) 0110 d+ d- 0111 a+ 1111 b- 1011 S R C d a- 0011 c- a- c- 1001 0001 EMICRO 2016 Synthesis of async controllers from STGs 82

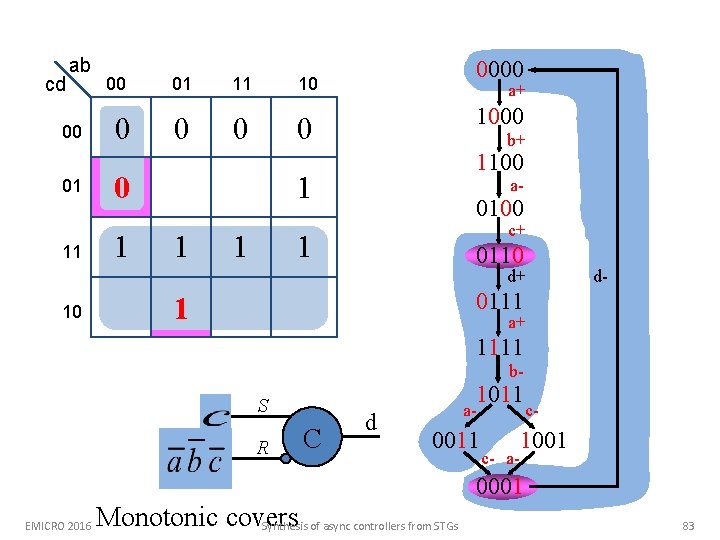

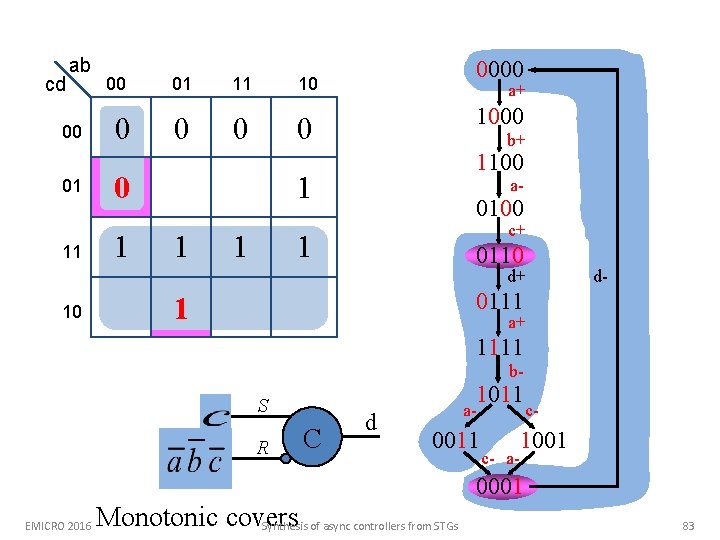

cd ab 00 01 11 00 0 01 0 11 0 a+ 1000 0 b+ 1100 1 0000 10 1 a- 0100 c+ 1 1 0110 d+ 10 d- 0111 1 a+ 1111 b- 1011 S R C d a- 0011 c- a- c- 1001 0001 EMICRO 2016 Monotonic covers Synthesis of async controllers from STGs 83

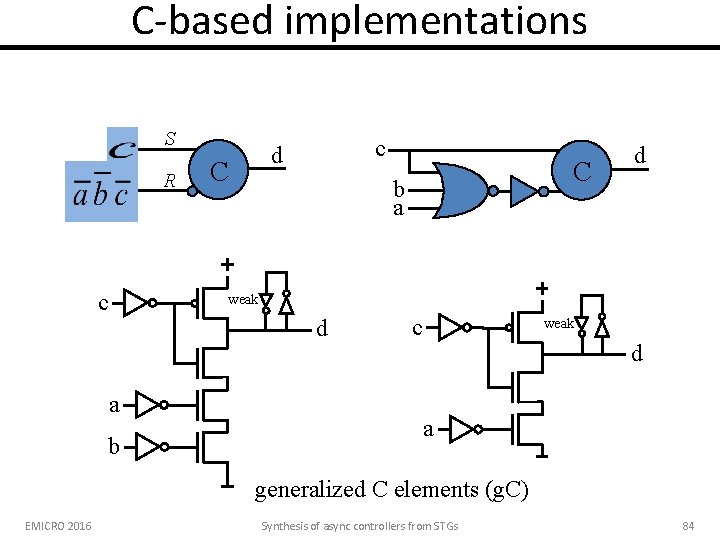

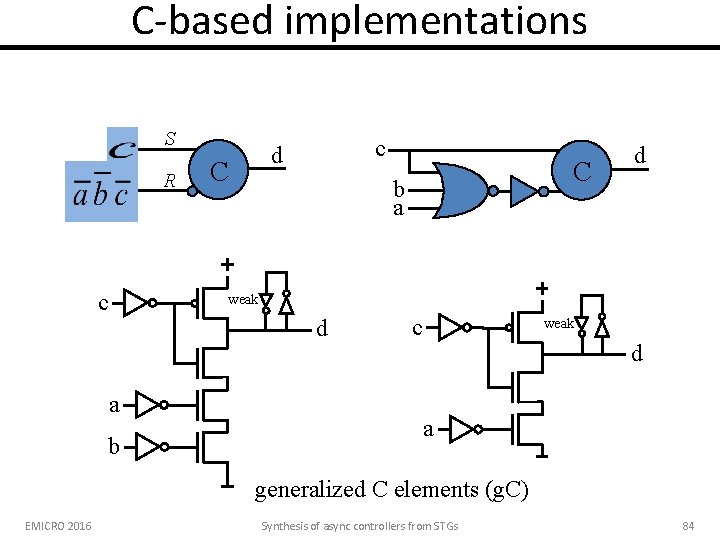

C-based implementations S R c a b c d C C b a d weak d c weak d a generalized C elements (g. C) EMICRO 2016 Synthesis of async controllers from STGs 84

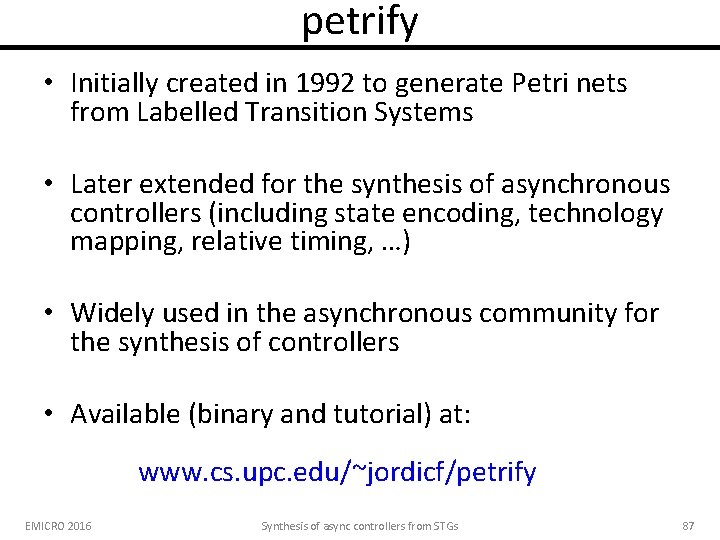

Speed-independent implementations • Implementability conditions – Consistency – Complete state coding – Persistency • Circuit architectures – Complex (hazard-free) gates – C elements with monotonic covers –. . . EMICRO 2016 Synthesis of async controllers from STGs 85

Petrify: a tool for the synthesis of Petri nets and asynchronous controllers EMICRO 2016 Synthesis of async controllers from STGs 86

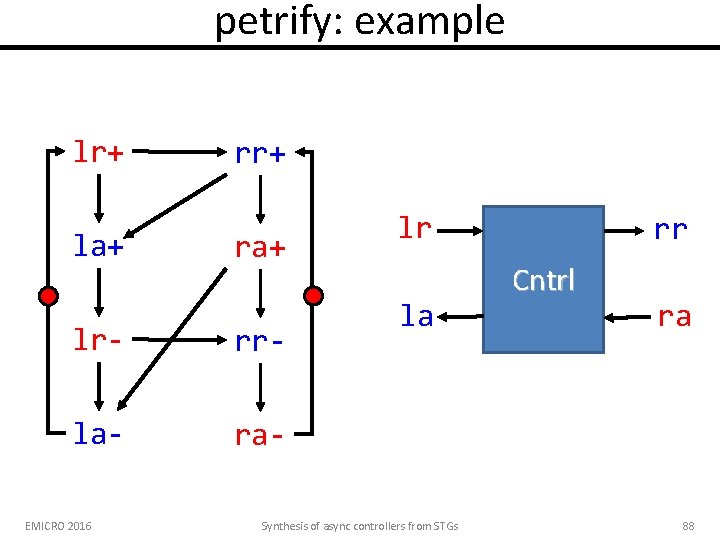

petrify • Initially created in 1992 to generate Petri nets from Labelled Transition Systems • Later extended for the synthesis of asynchronous controllers (including state encoding, technology mapping, relative timing, …) • Widely used in the asynchronous community for the synthesis of controllers • Available (binary and tutorial) at: www. cs. upc. edu/~jordicf/petrify EMICRO 2016 Synthesis of async controllers from STGs 87

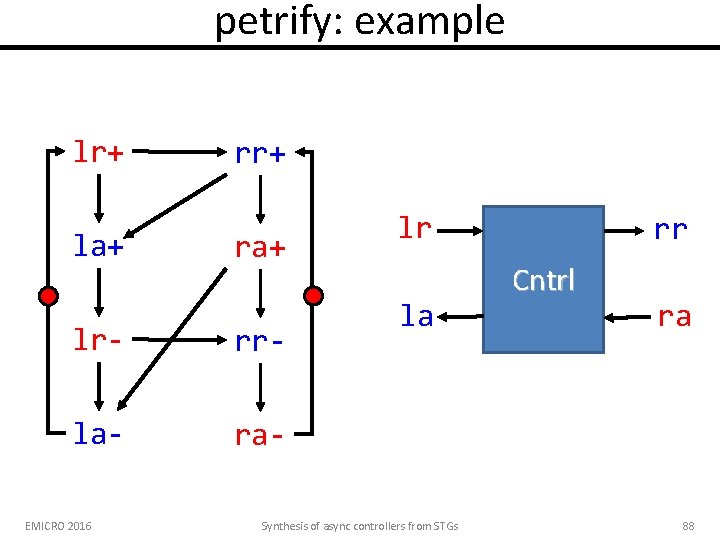

petrify: example lr+ la+ rr+ ra+ lr- rr- la- ra- EMICRO 2016 lr la Synthesis of async controllers from STGs rr Cntrl ra 88

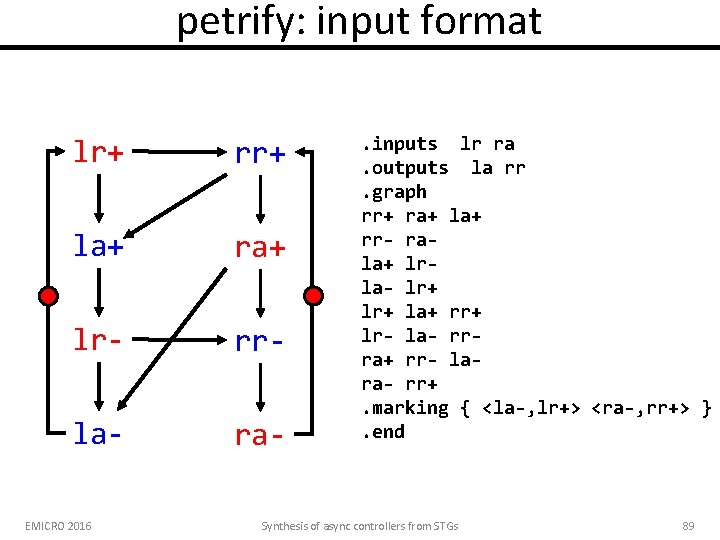

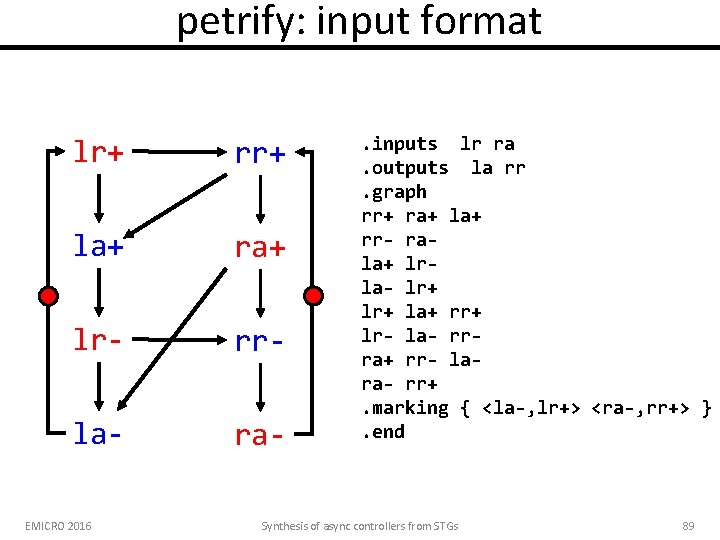

petrify: input format lr+ rr+ la+ ra+ lr- rr- la- ra- EMICRO 2016 . inputs lr ra. outputs la rr. graph rr+ ra+ la+ rr- rala+ lrla- lr+ la+ rr+ lr- la- rrra+ rr- lara- rr+. marking { <la-, lr+> <ra-, rr+> }. end Synthesis of async controllers from STGs 89

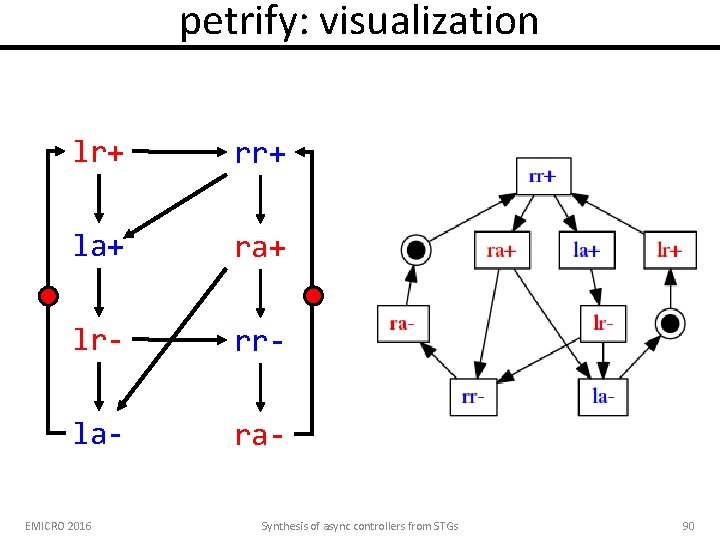

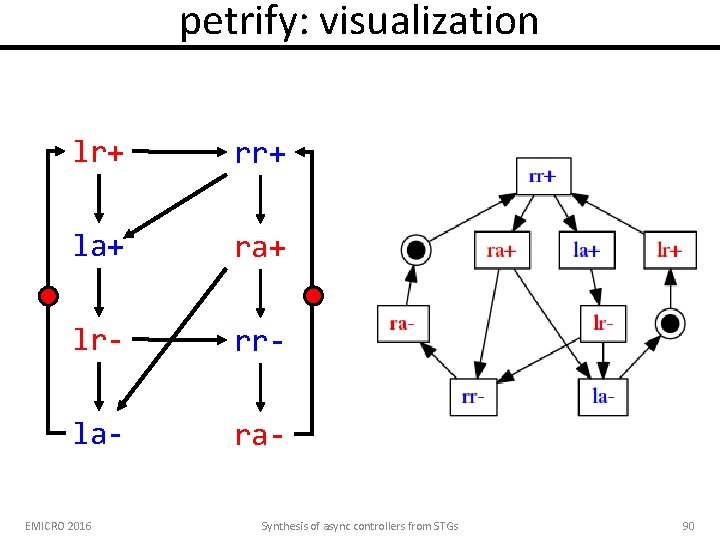

petrify: visualization lr+ rr+ la+ ra+ lr- rr- la- ra- EMICRO 2016 Synthesis of async controllers from STGs 90

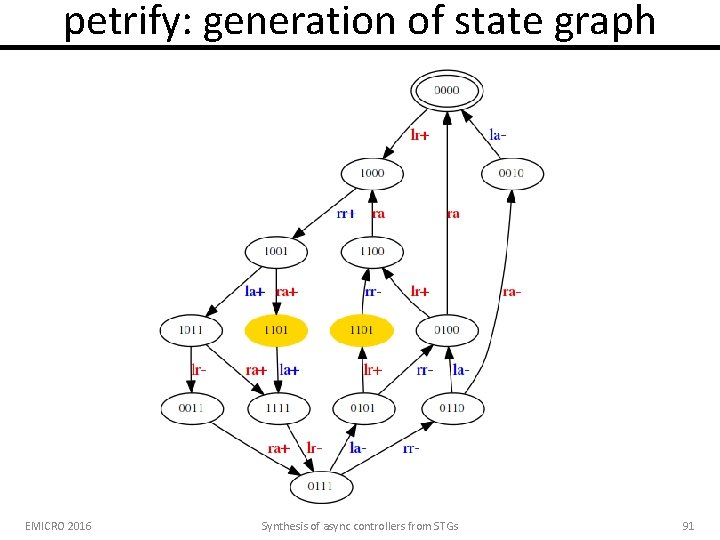

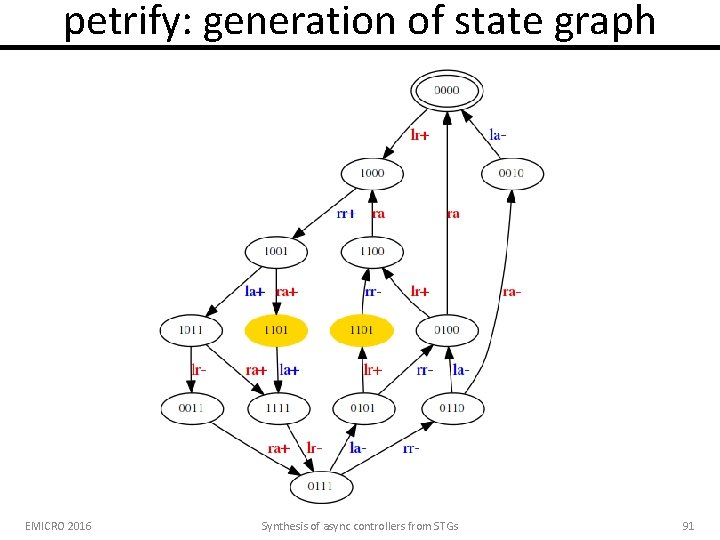

petrify: generation of state graph EMICRO 2016 Synthesis of async controllers from STGs 91

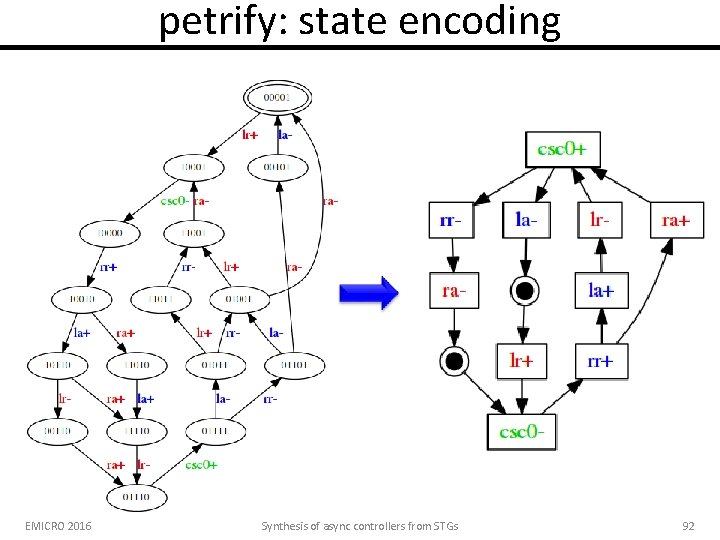

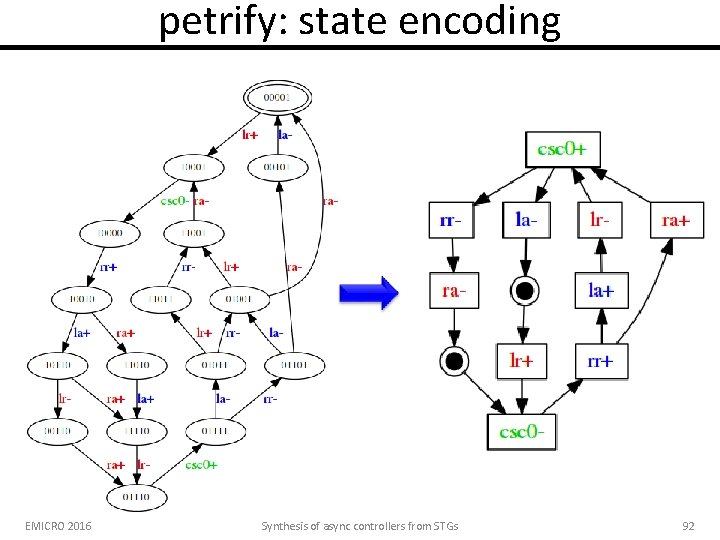

petrify: state encoding EMICRO 2016 Synthesis of async controllers from STGs 92

![petrify logic synthesis la rrcsc 0 rr csc 0 csc 0 petrify: logic synthesis [la] = rr*csc 0’; [rr] = csc 0’; [csc 0] =](https://slidetodoc.com/presentation_image_h2/d12a4aa5b1f60feefa1bcbb669c54592/image-93.jpg)

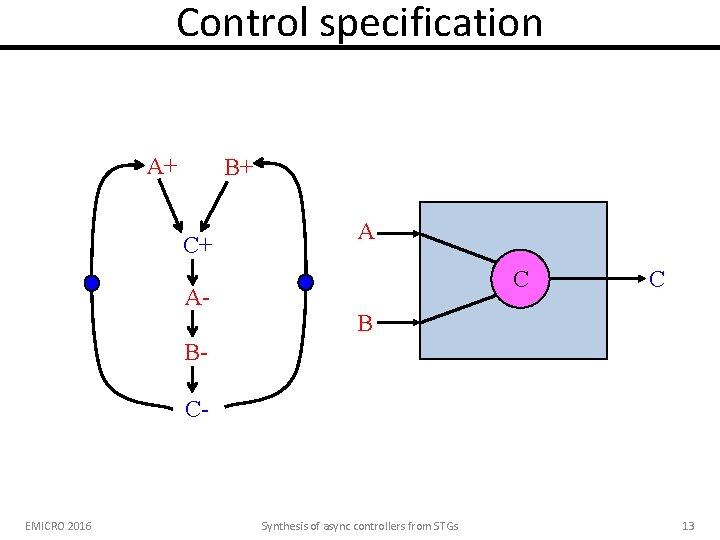

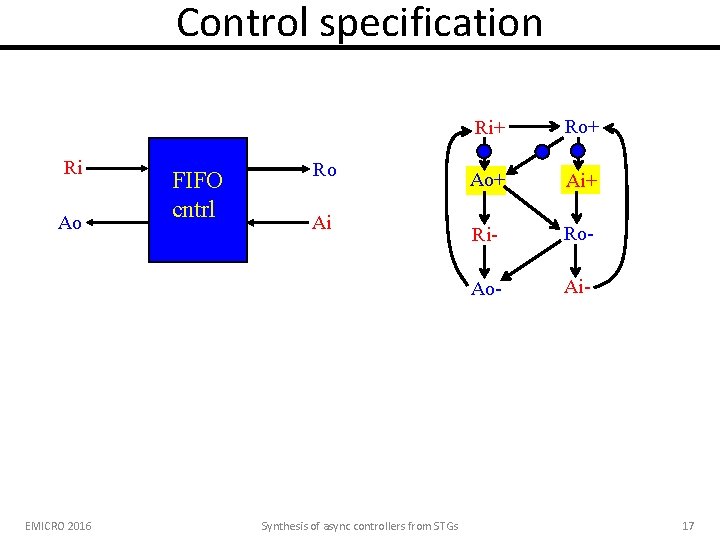

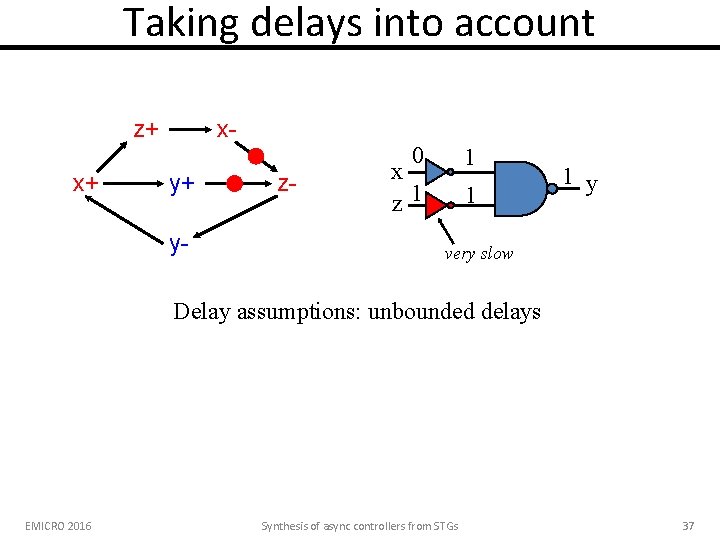

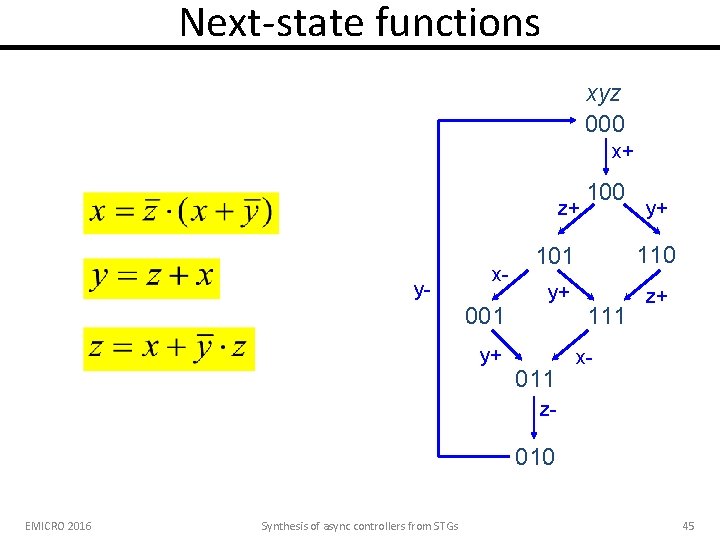

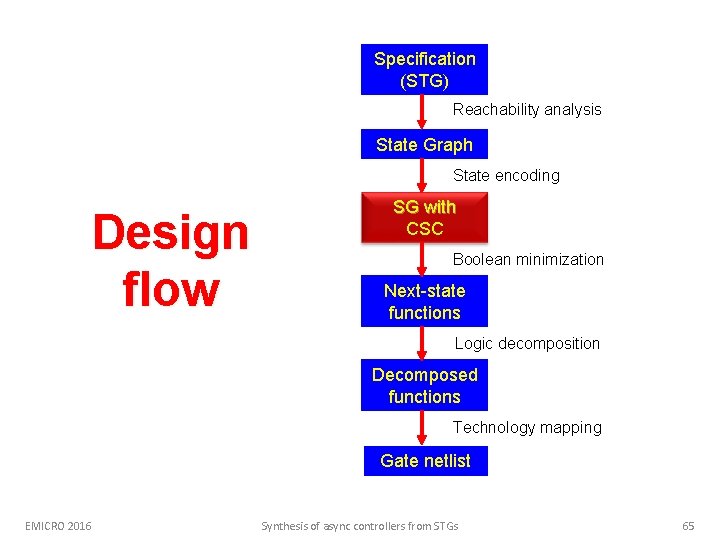

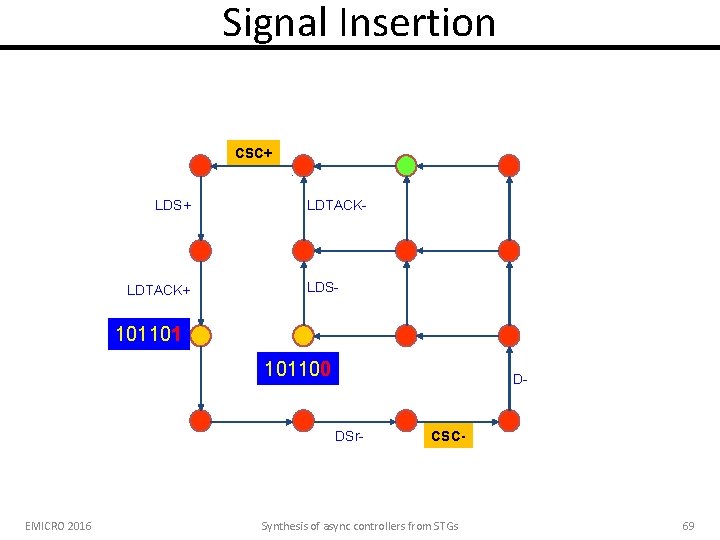

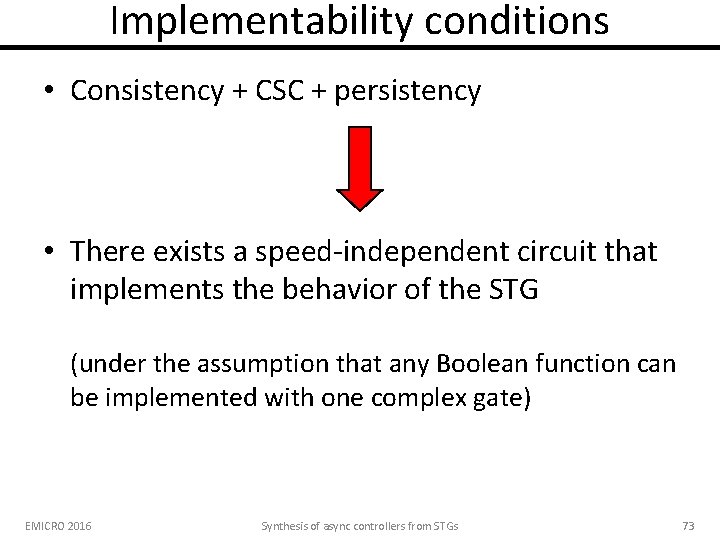

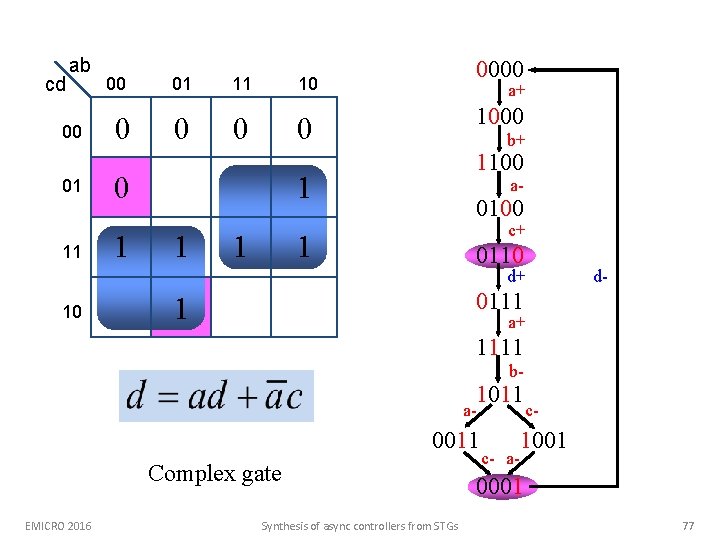

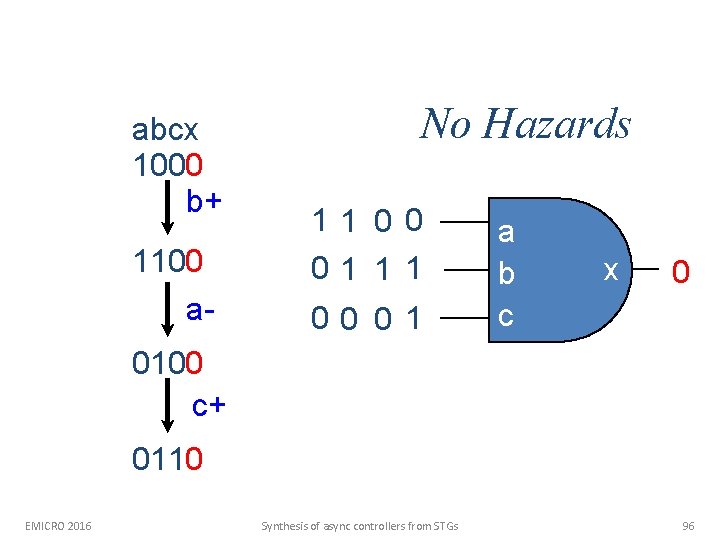

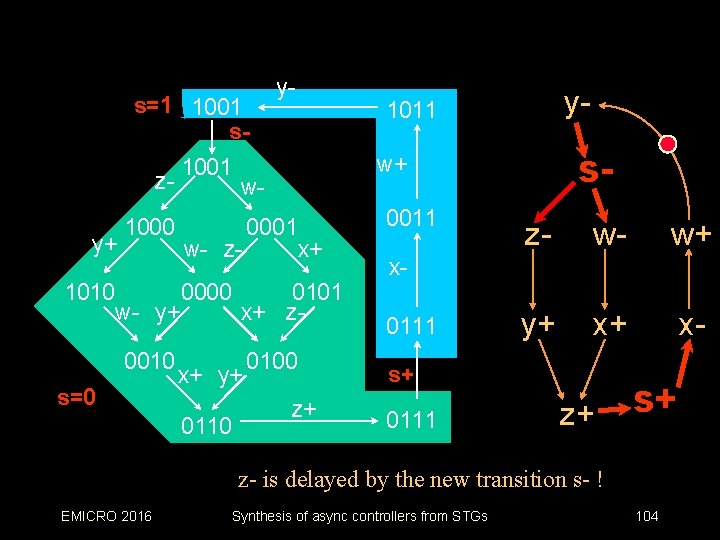

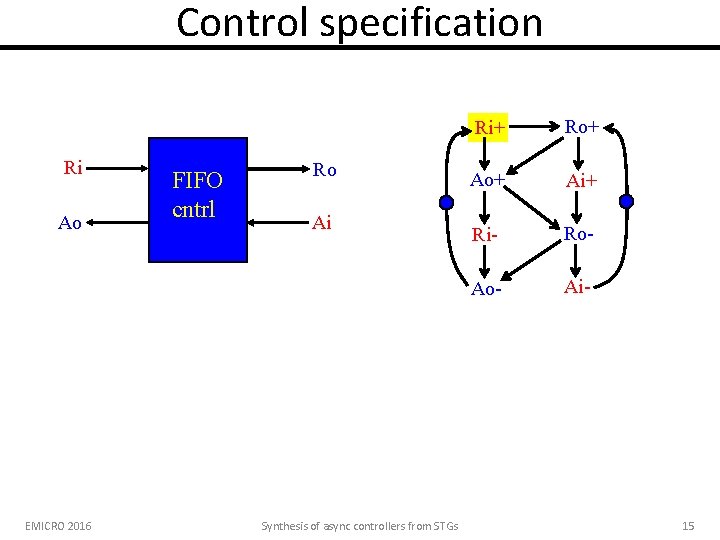

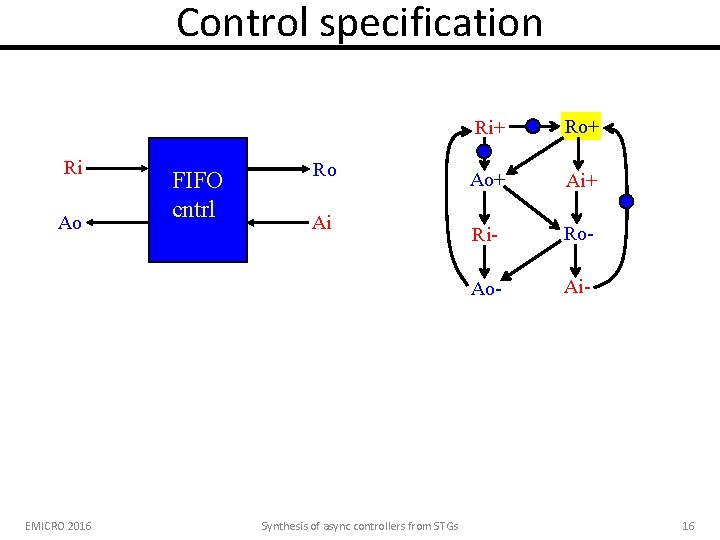

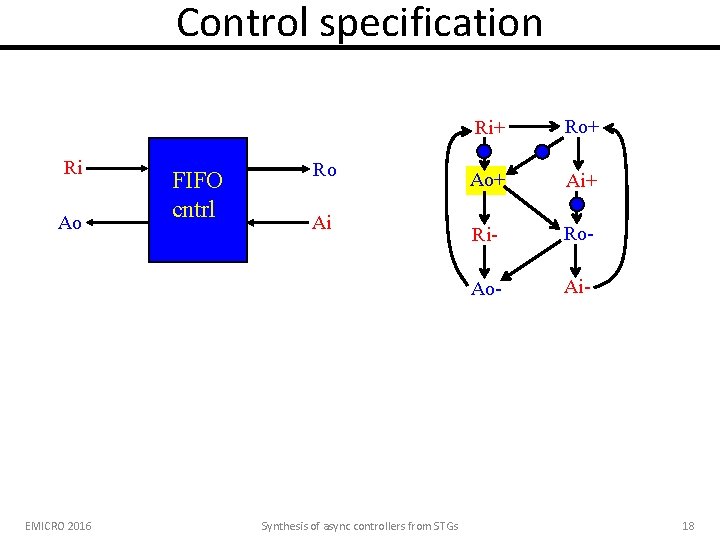

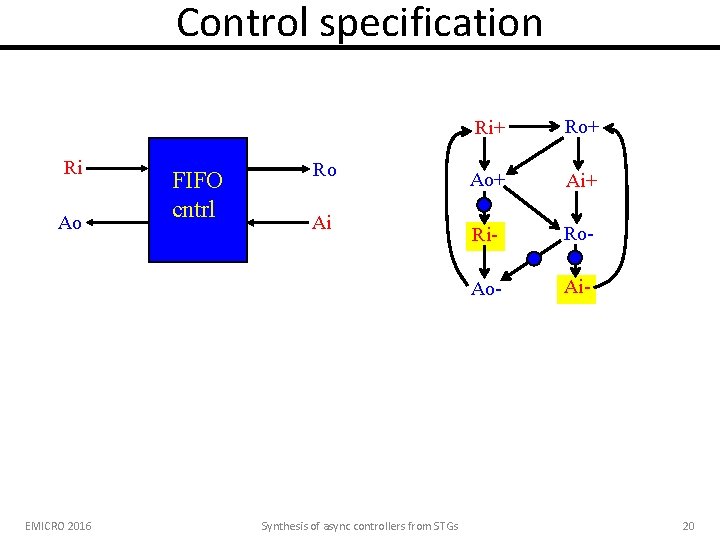

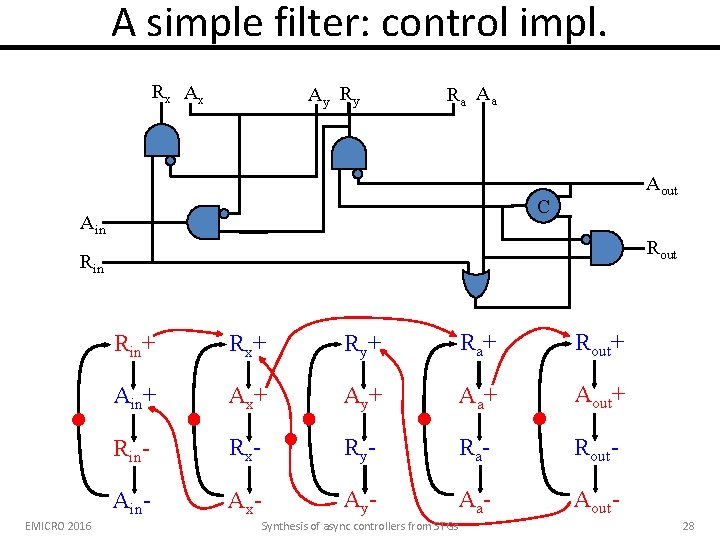

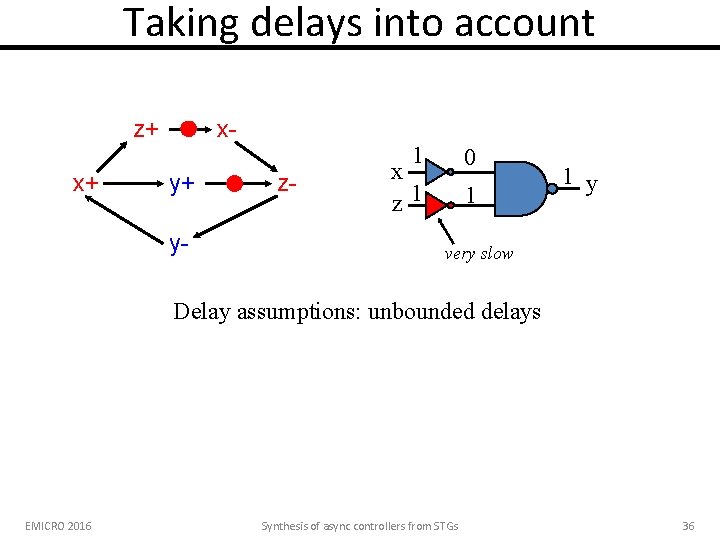

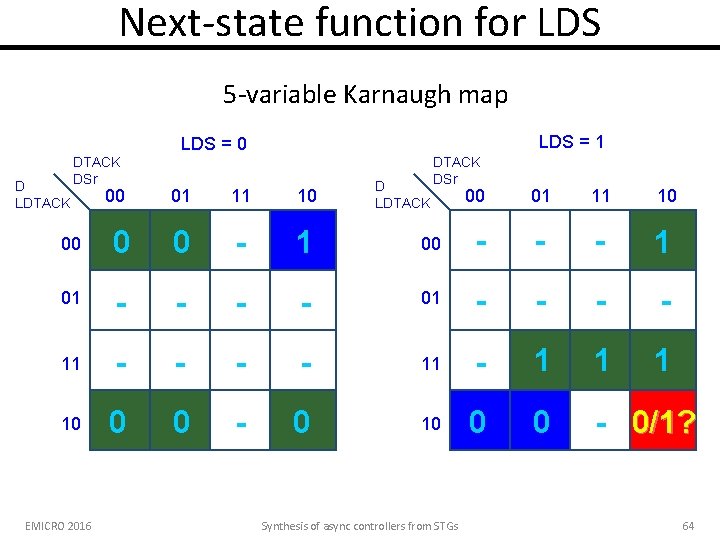

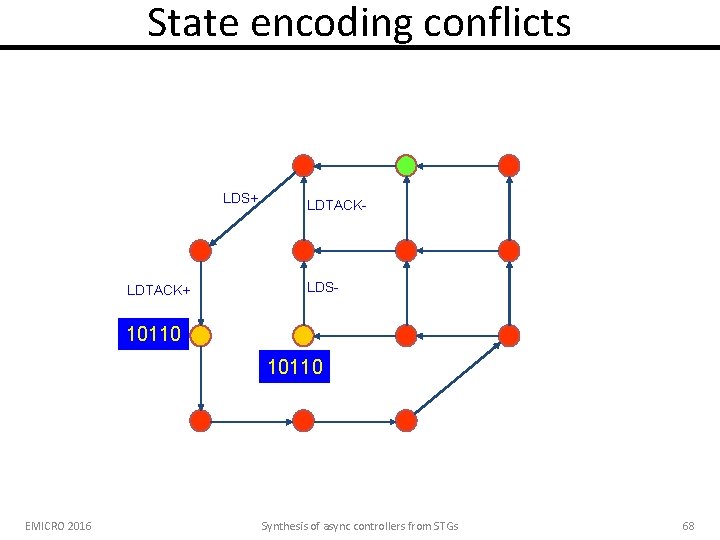

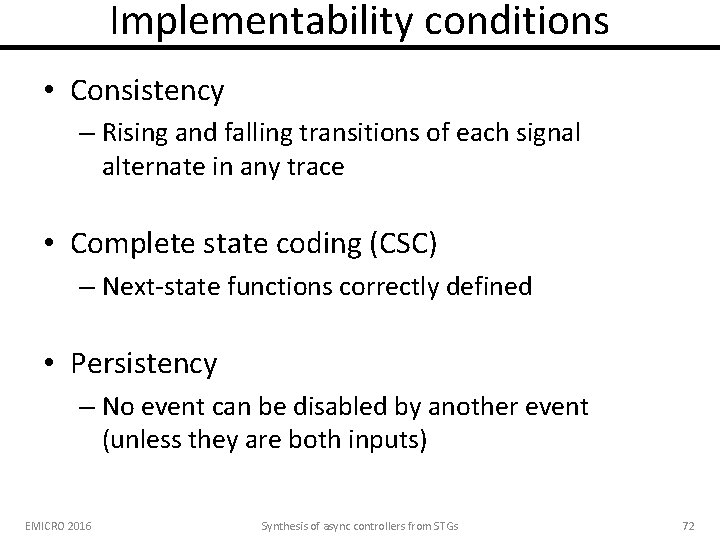

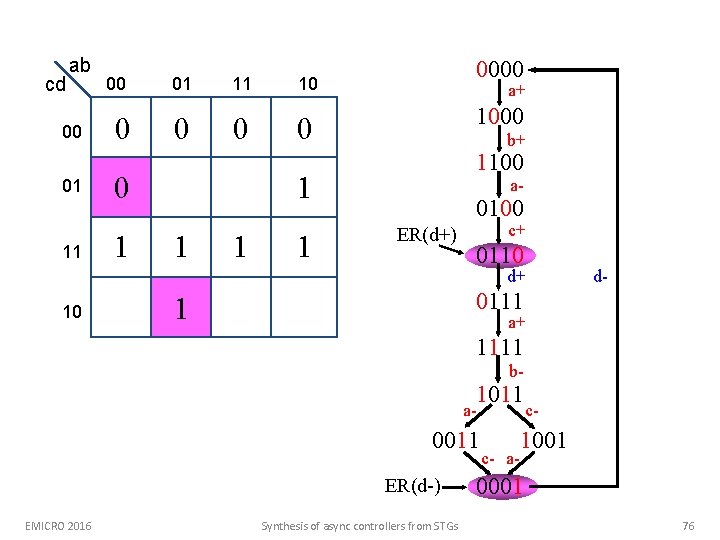

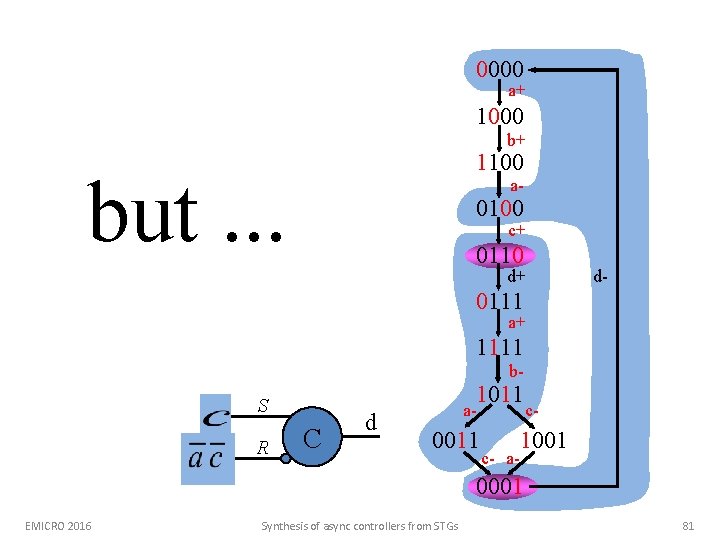

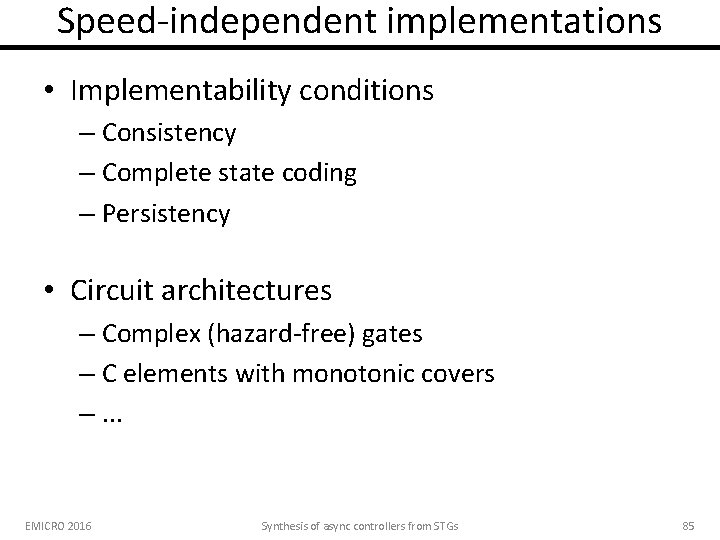

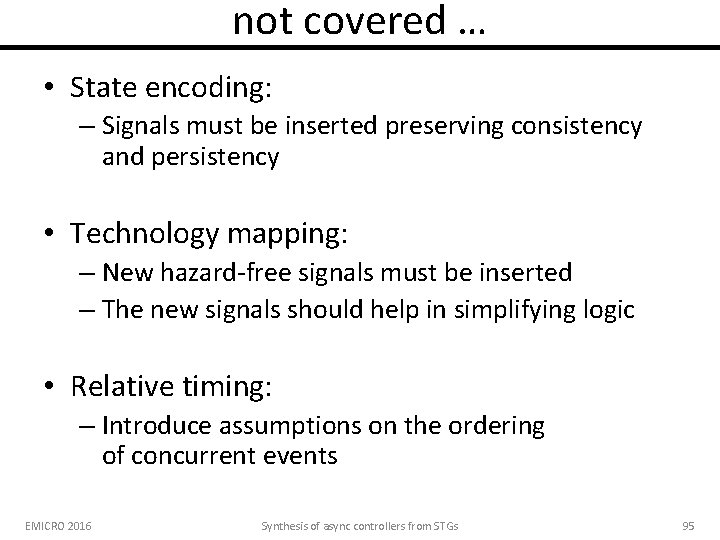

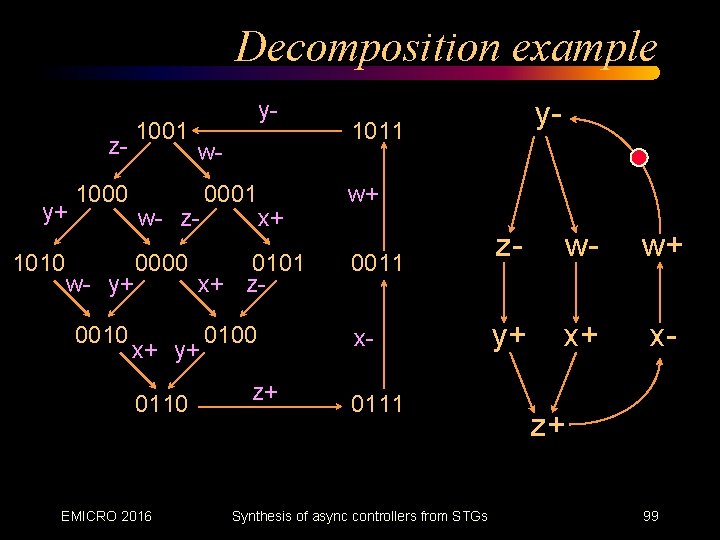

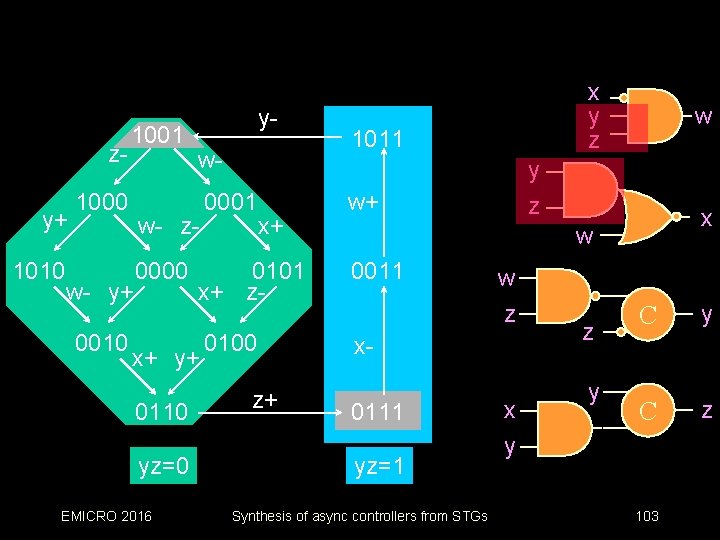

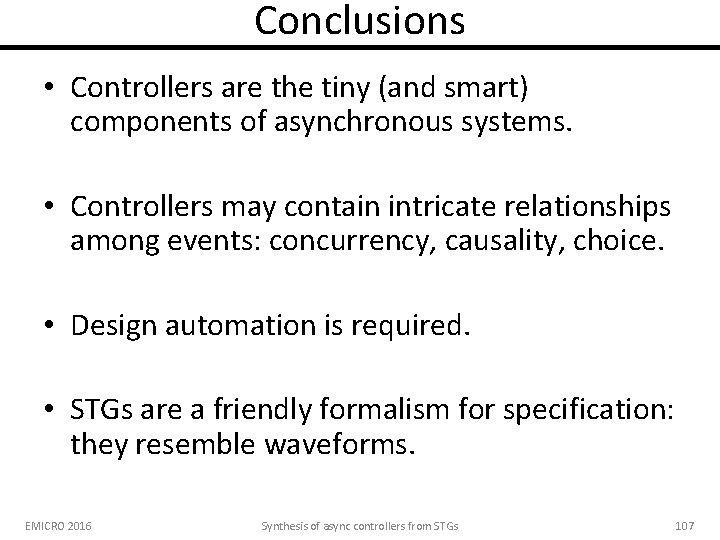

petrify: logic synthesis [la] = rr*csc 0’; [rr] = csc 0’; [csc 0] = csc 0*(lr’ + ra) + lr’*ra; EMICRO 2016 Synthesis of async controllers from STGs 93

![petrify technology mapping gate la gate rr gate csc petrify: technology mapping # gate [la] = # gate [rr] = # gate [csc](https://slidetodoc.com/presentation_image_h2/d12a4aa5b1f60feefa1bcbb669c54592/image-94.jpg)

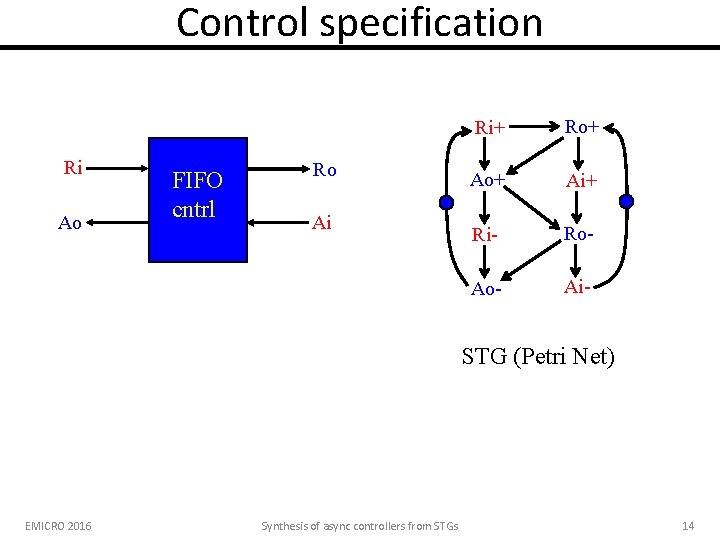

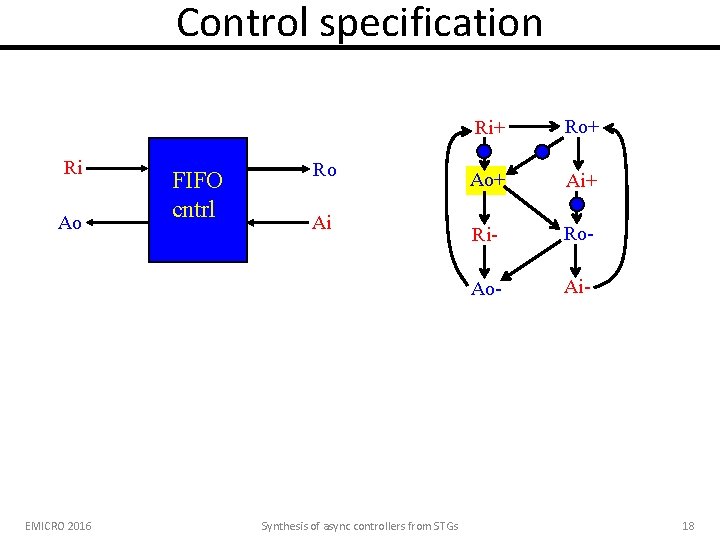

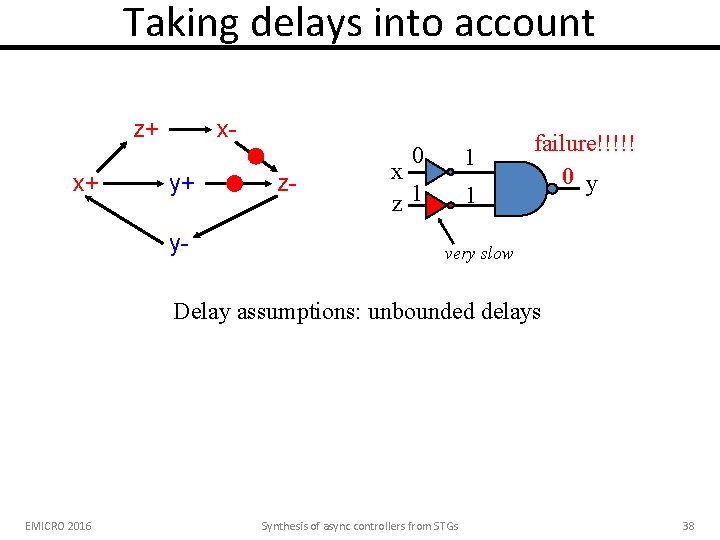

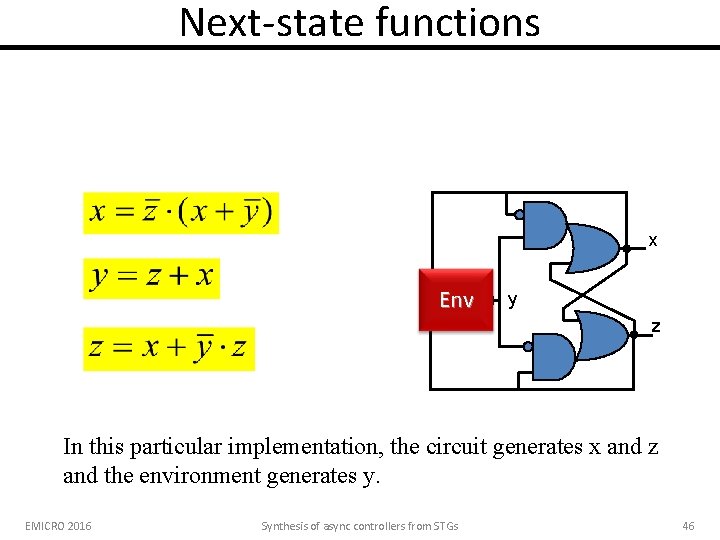

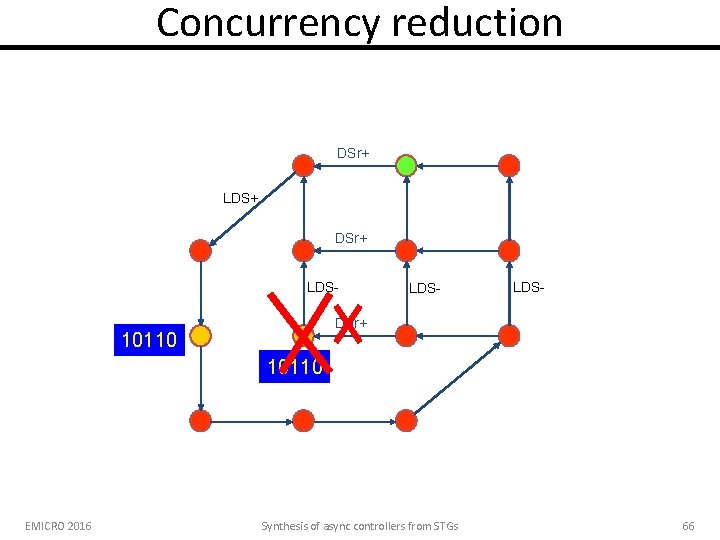

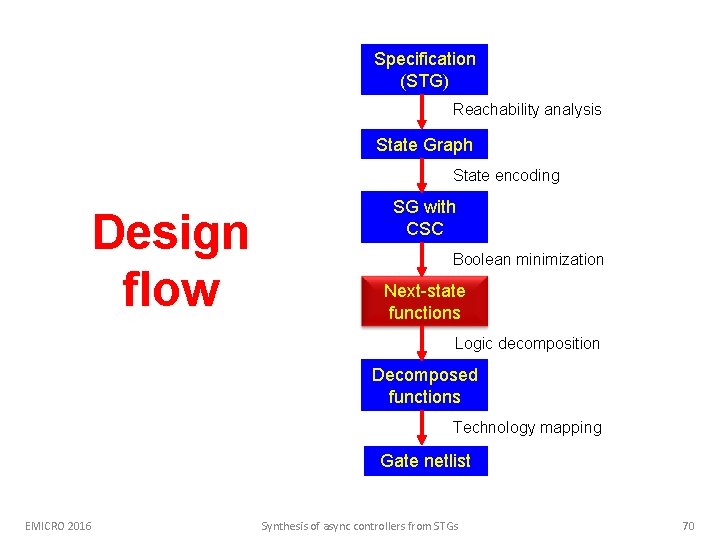

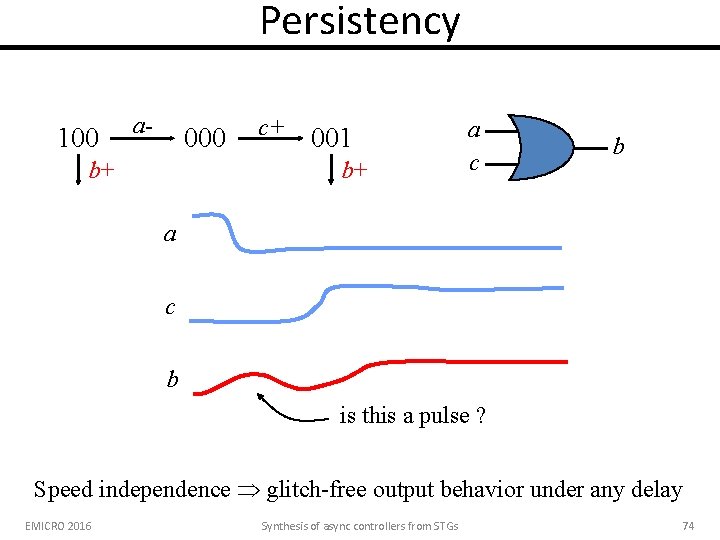

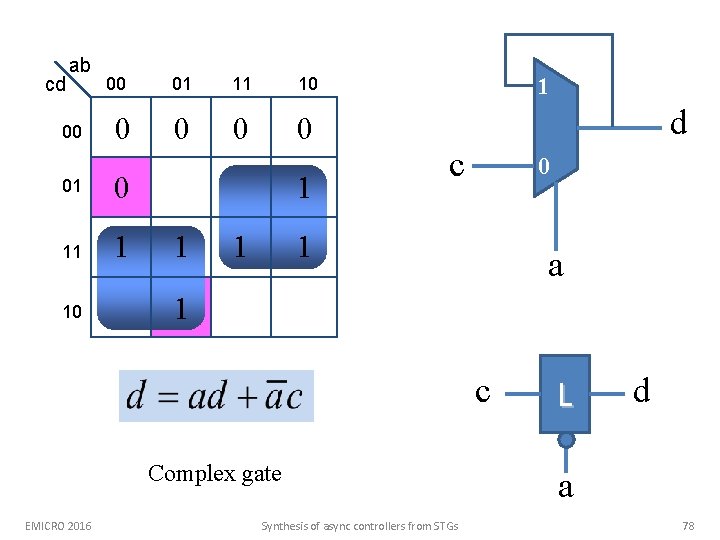

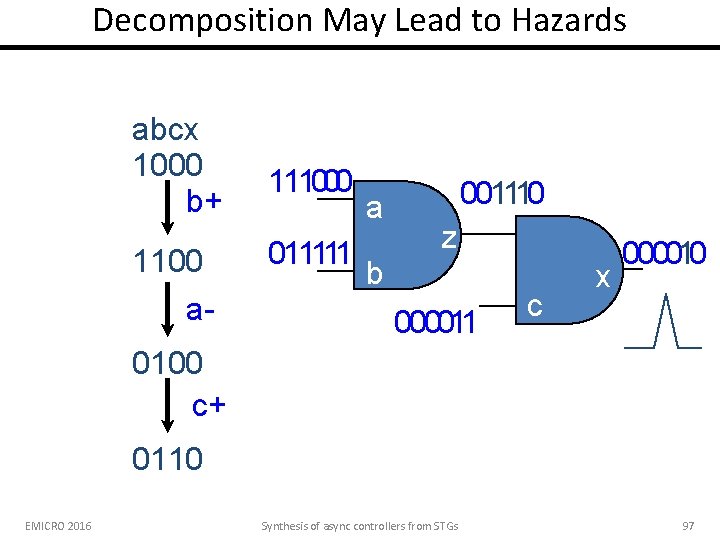

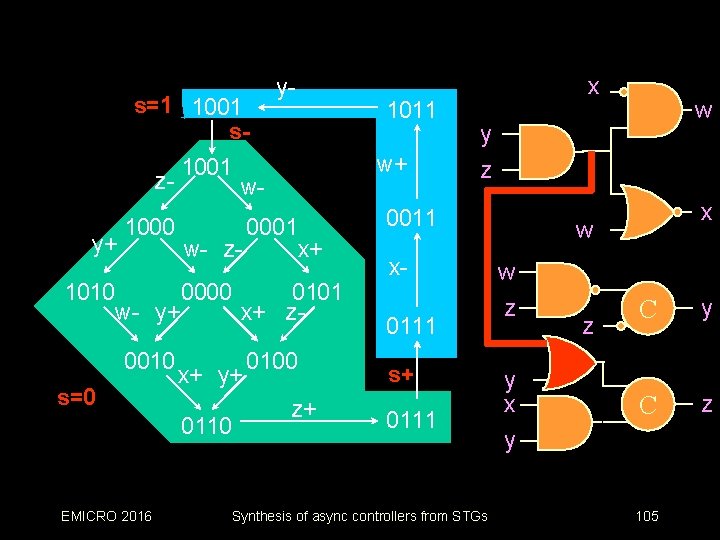

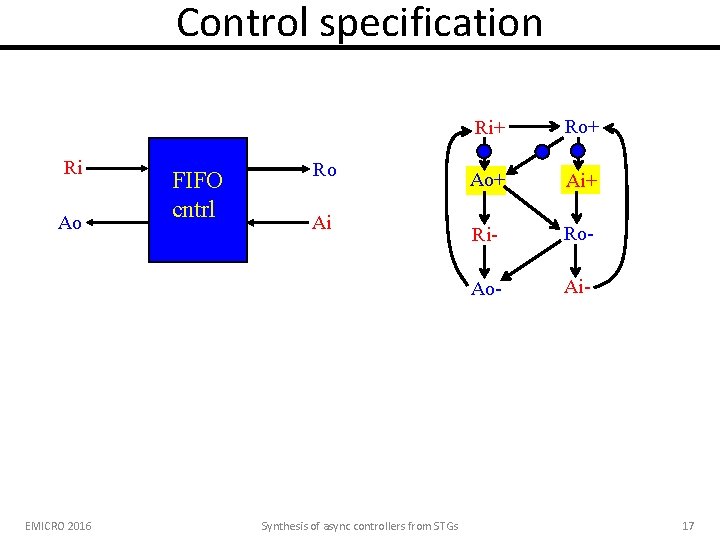

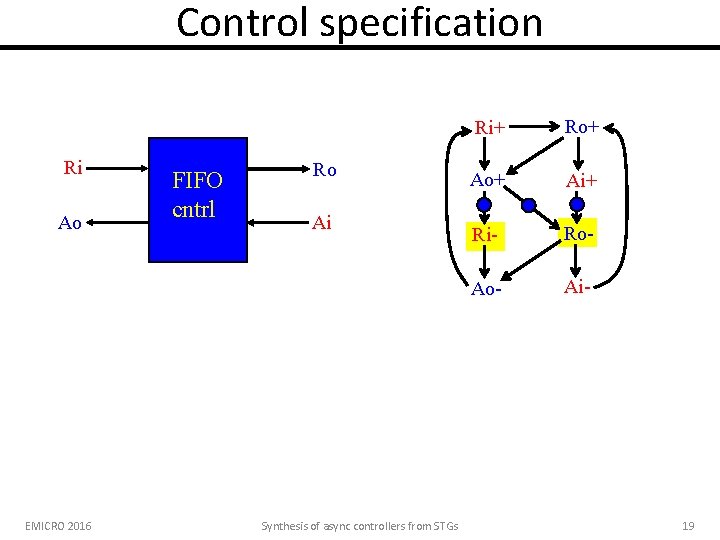

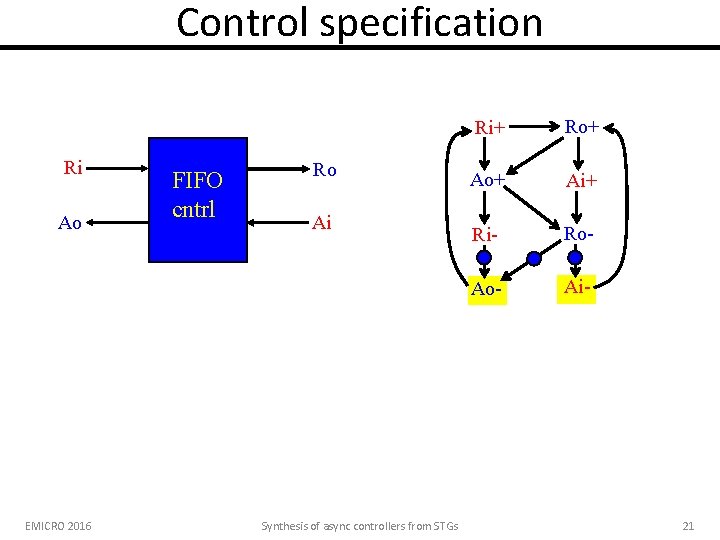

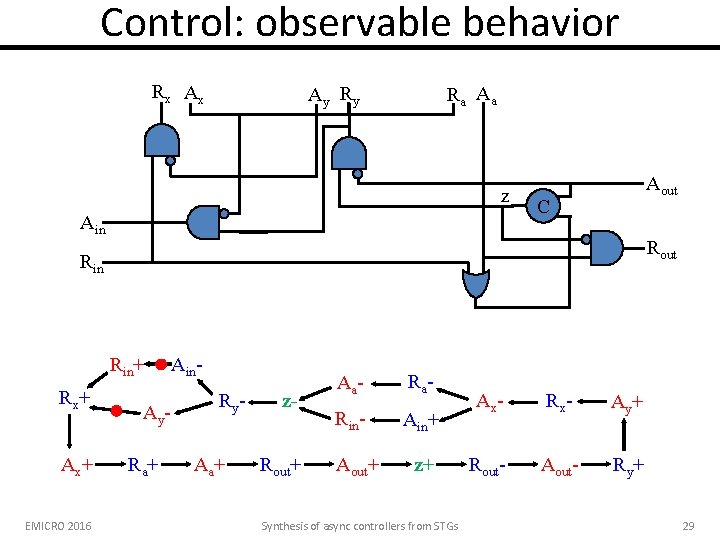

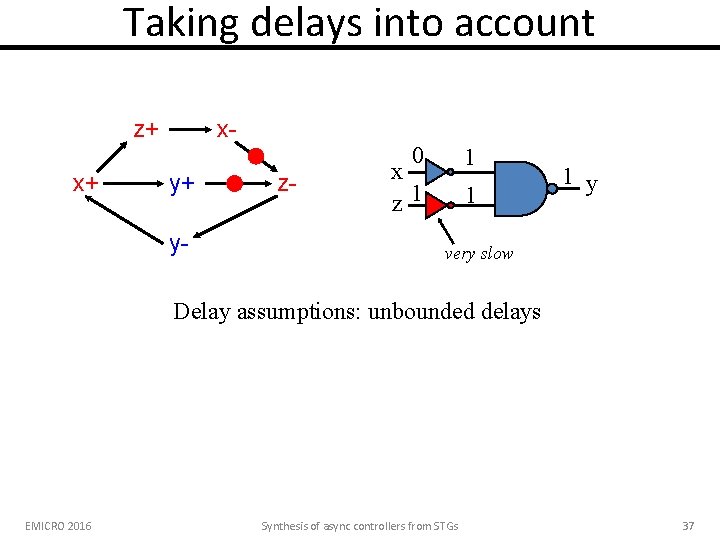

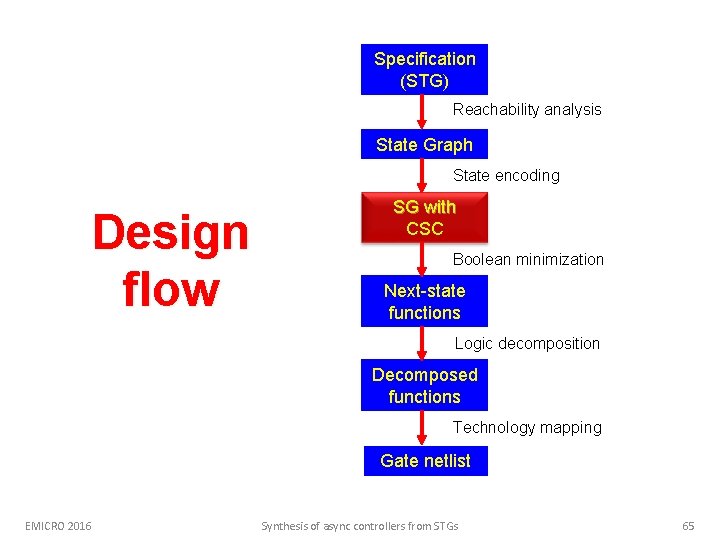

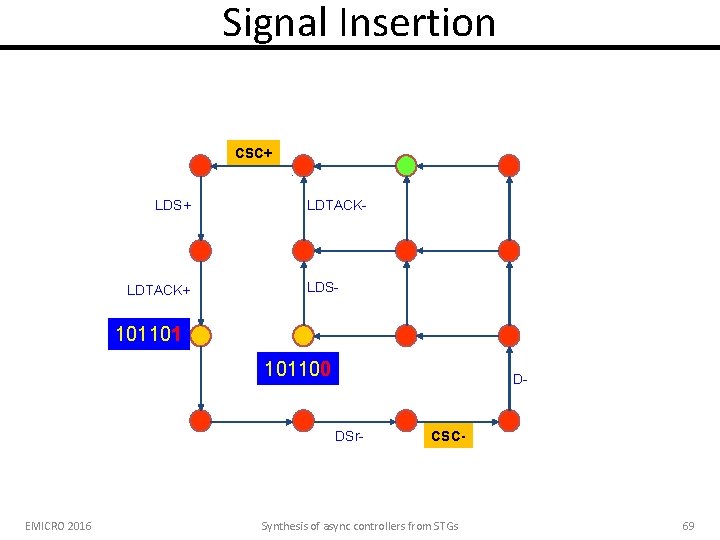

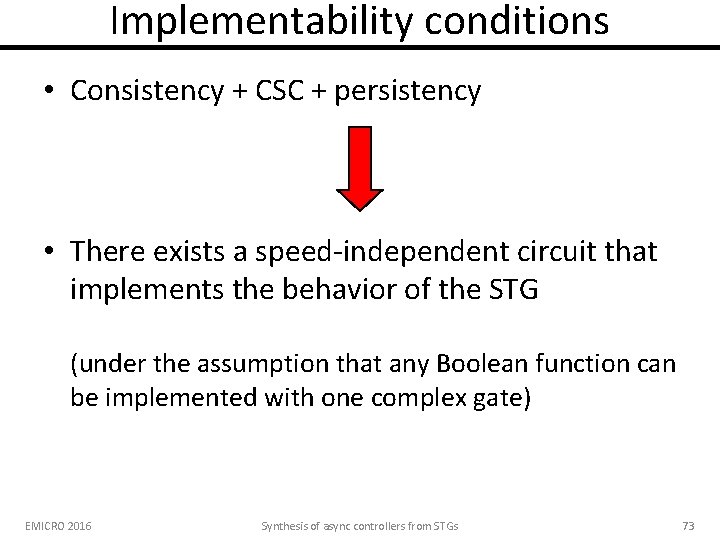

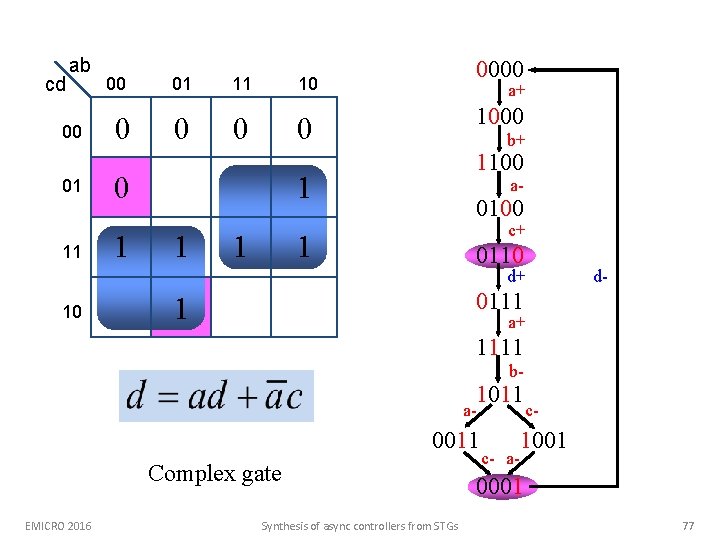

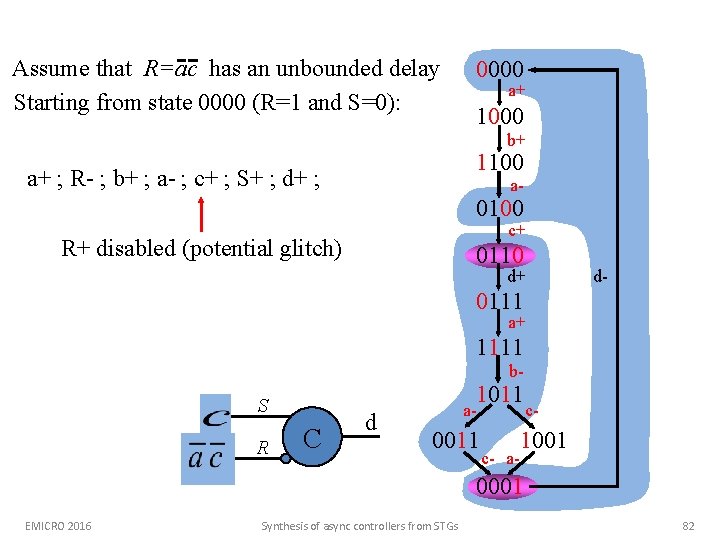

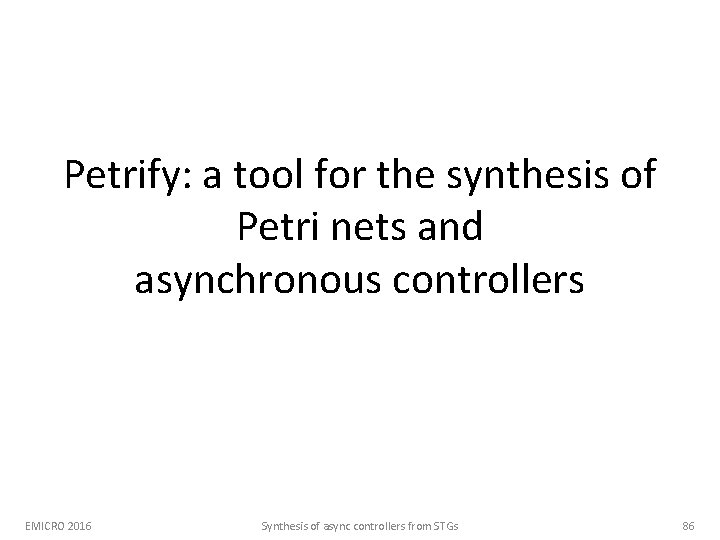

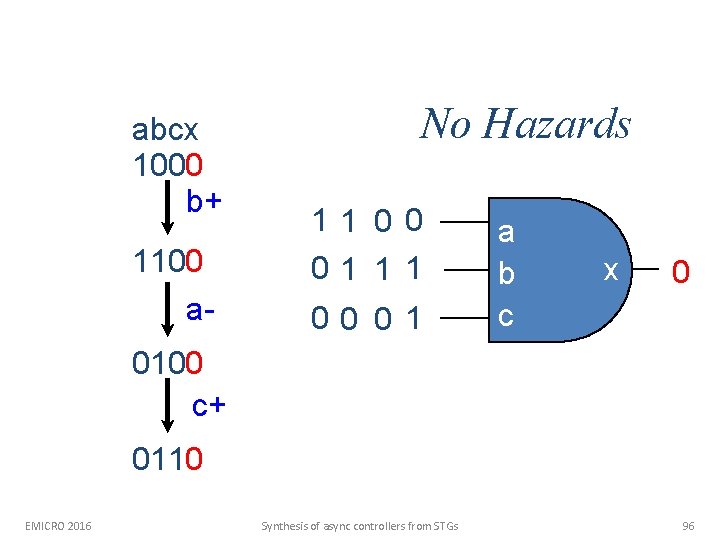

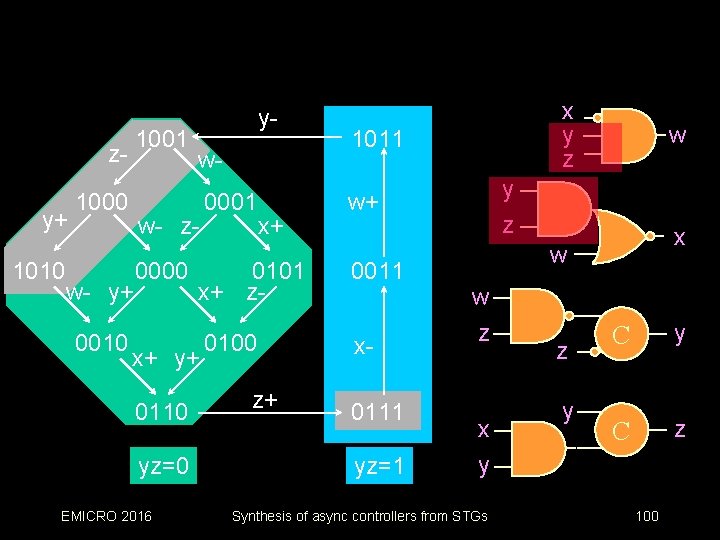

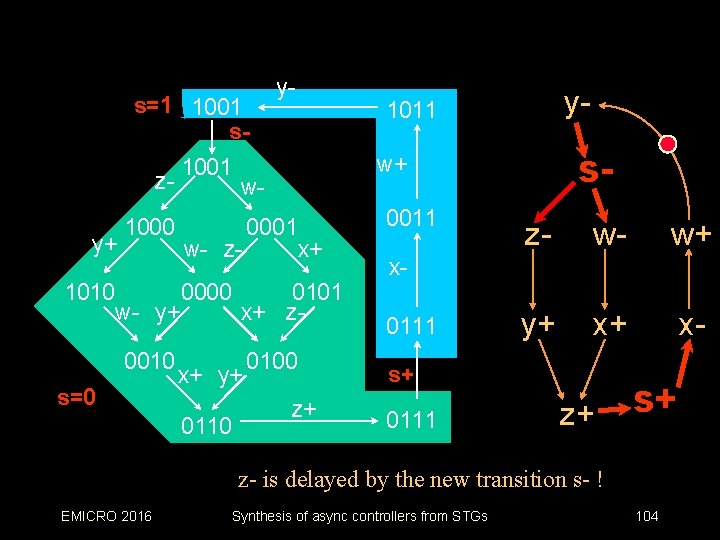

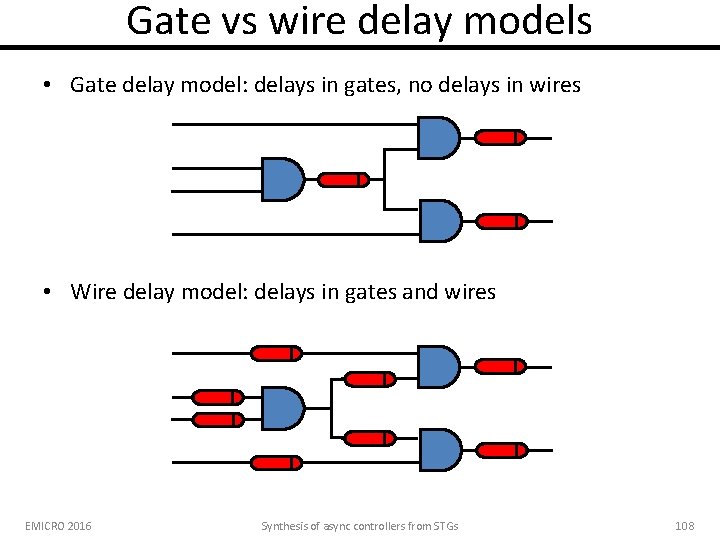

petrify: technology mapping # gate [la] = # gate [rr] = # gate [csc 0] and 2_1 rr*csc 0'; inv csc 0'; c_element 1 = ra*(lr' + csc 0) + lr'*csc 0; (Note: tech mapping is not that easy. Be careful with glitches) EMICRO 2016 Synthesis of async controllers from STGs 94

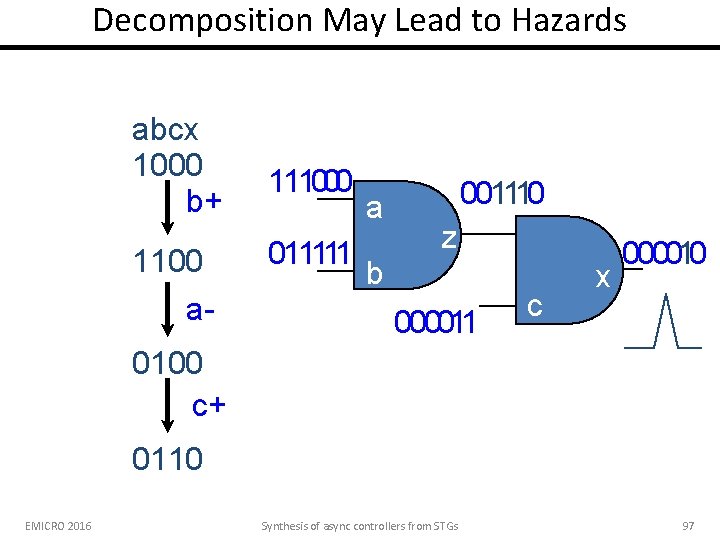

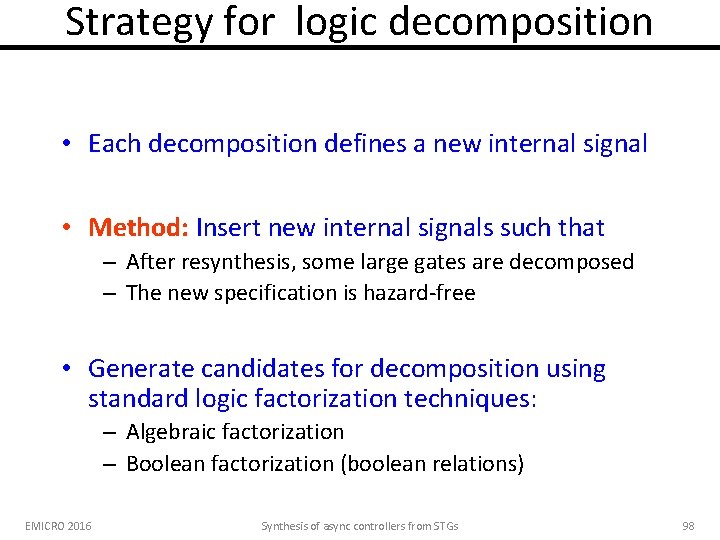

not covered … • State encoding: – Signals must be inserted preserving consistency and persistency • Technology mapping: – New hazard-free signals must be inserted – The new signals should help in simplifying logic • Relative timing: – Introduce assumptions on the ordering of concurrent events EMICRO 2016 Synthesis of async controllers from STGs 95

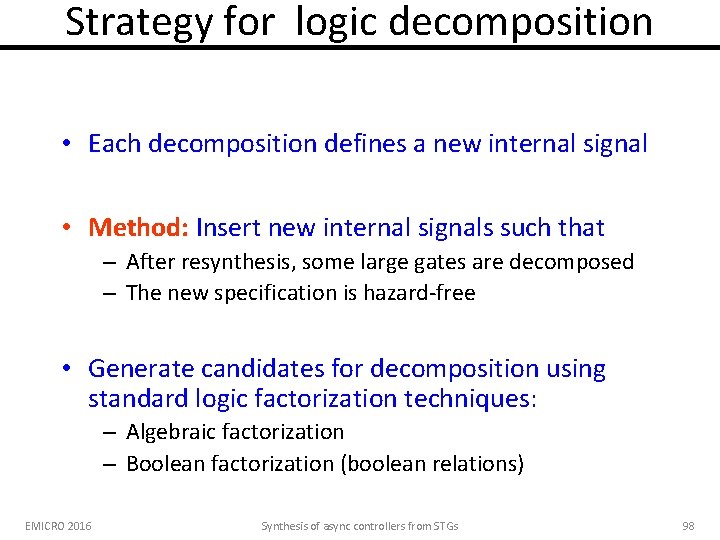

abcx 1000 b+ 1100 a- No Hazards 11 0 0 01 1 1 00 0 1 a b c x 0 0100 c+ 0110 EMICRO 2016 Synthesis of async controllers from STGs 96

Decomposition May Lead to Hazards abcx 1000 b+ 1100 a- 111000 011111 a b 001110 z 000011 c x 000010 0100 c+ 0110 EMICRO 2016 Synthesis of async controllers from STGs 97

Strategy for logic decomposition • Each decomposition defines a new internal signal • Method: Insert new internal signals such that – After resynthesis, some large gates are decomposed – The new specification is hazard-free • Generate candidates for decomposition using standard logic factorization techniques: – Algebraic factorization – Boolean factorization (boolean relations) EMICRO 2016 Synthesis of async controllers from STGs 98

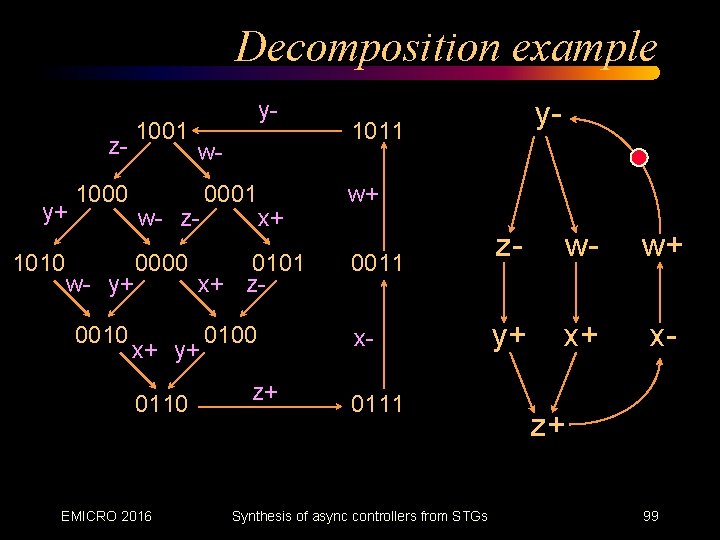

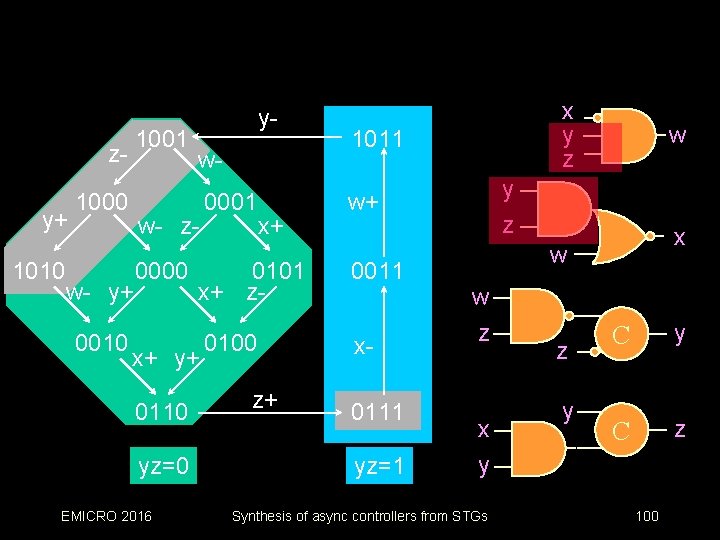

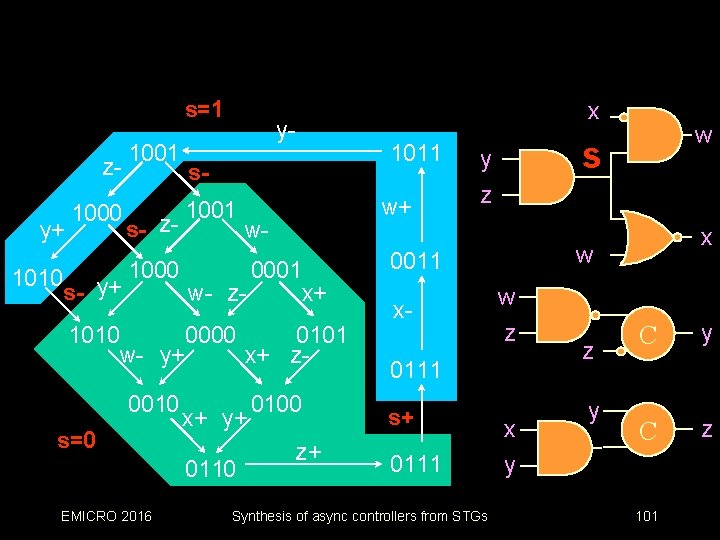

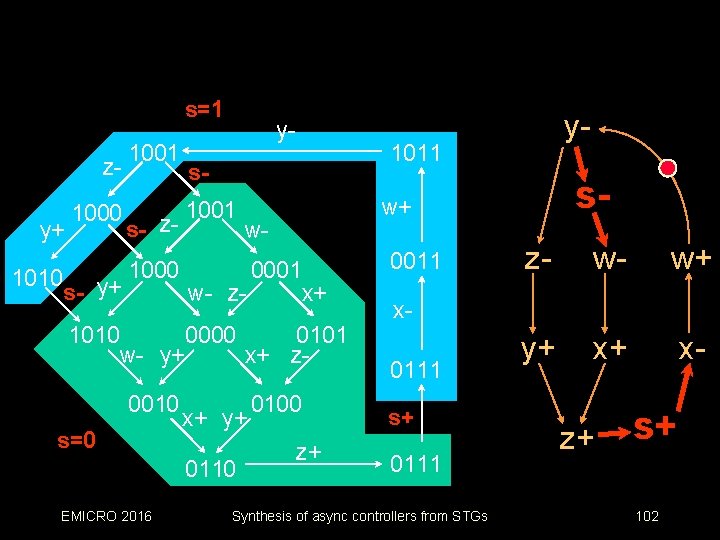

Decomposition example 1001 zy+ 1010 1000 w- w- z- w- y+ 0010 y- 0000 EMICRO 2016 x+ 1011 w+ 0101 x+ z- 0011 0100 x- x+ y+ 0110 0001 z+ y- 0111 Synthesis of async controllers from STGs z- w- w+ y+ x+ x- z+ 99

1001 zy+ 1010 1000 w- w- z- w- y+ 0010 y- 0000 yz=0 EMICRO 2016 x+ 1011 0100 x- z+ 0111 yz=1 w y z w+ 0101 x+ z- x+ y+ 0110 0001 x y z x w w z x y Synthesis of async controllers from STGs z y C z 100

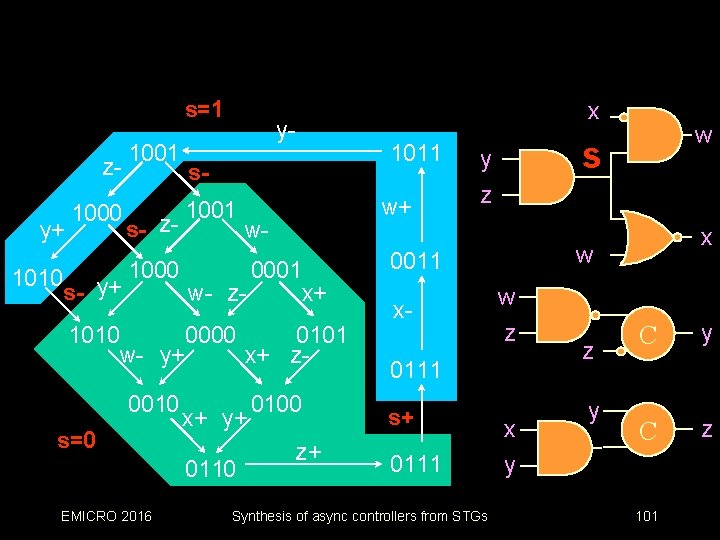

s=1 zy+ 1010 1000 s- y+ 1010 1001 1000 0000 w+ 0001 x+ 0100 z+ x- 0111 Synthesis of async controllers from STGs x w w z 0111 s+ w s y z 0011 0101 x+ z- x+ y+ 0110 EMICRO 2016 1011 w- w- z- w- y+ s=0 y- s- s- z- 0010 x x y z y C z 101

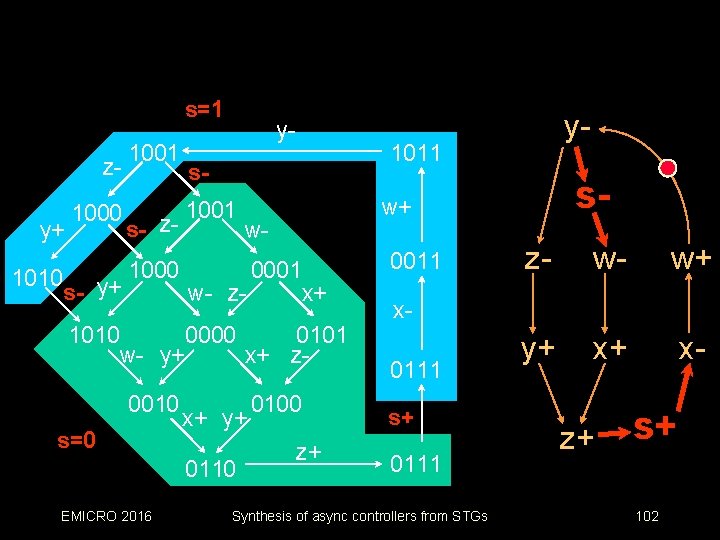

s=1 zy+ 1010 1000 s- y+ 1010 1001 1000 w- y+ s=0 0000 0110 EMICRO 2016 0001 0011 x+ 0101 x+ z- x+ y+ s- w+ w- w- z- y- 1011 s- s- z- 0010 y- 0100 z+ z- w- w+ y+ x+ x- x 0111 s+ 0111 Synthesis of async controllers from STGs z+ s+ 102

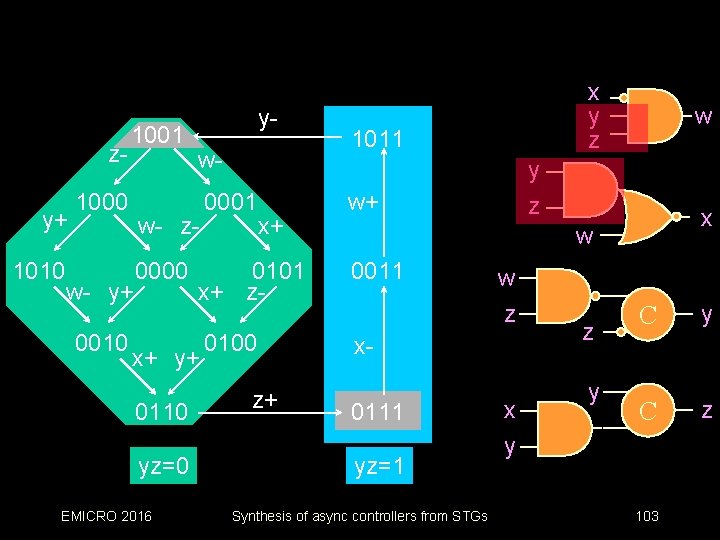

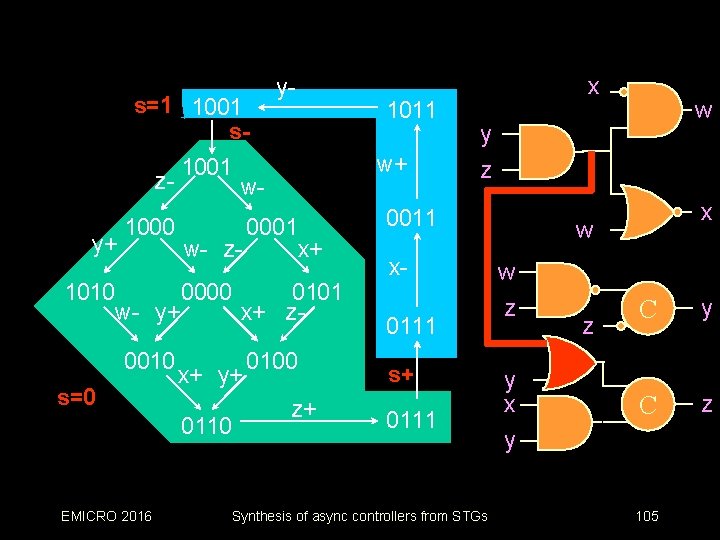

zy+ 1010 1001 1000 w- w- z- w- y+ 0010 y- 0000 yz=0 EMICRO 2016 x+ 0101 x+ z- x+ y+ 0110 0001 0100 z+ x y z 1011 w y z w+ x w 0011 w z x 0111 yz=1 Synthesis of async controllers from STGs x y z y C z 103

s=1 1001 s 1001 zy+ 1010 1000 w- y+ 0010 s=0 0110 s- w+ 0001 0011 x+ 0101 x+ z- x+ y+ y- 1011 w- w- z 0000 y- 0100 z+ z- w- w+ y+ x+ x- x 0111 s+ 0111 z+ s+ z- is delayed by the new transition s- ! EMICRO 2016 Synthesis of async controllers from STGs 104

s=1 1001 s 1001 zy+ 1010 1000 w- y+ 0010 s=0 EMICRO 2016 w+ 0001 x x+ 0100 z+ w y z 0011 0101 x+ z- x+ y+ 0110 1011 w- w- z 0000 y- x 0111 s+ 0111 Synthesis of async controllers from STGs x w w z y x y z C y C z 105

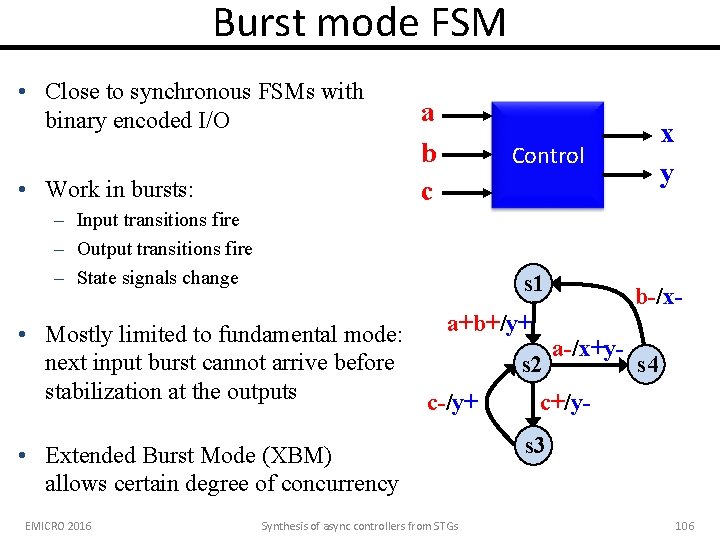

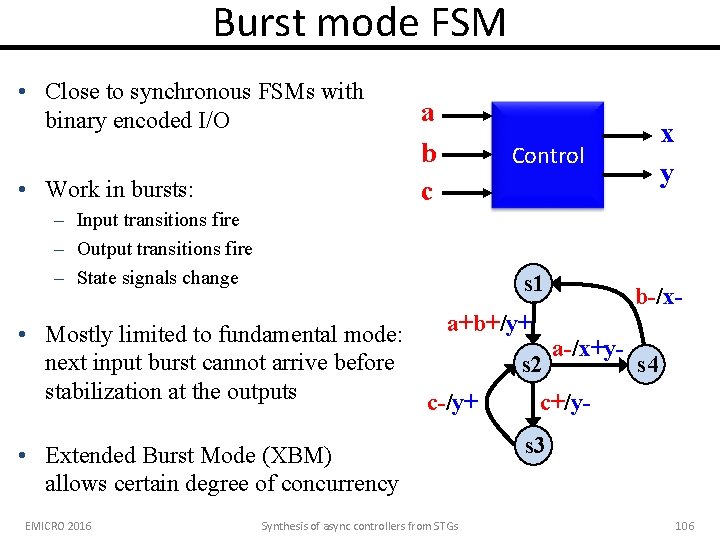

Burst mode FSM • Close to synchronous FSMs with binary encoded I/O • Work in bursts: a b c – Input transitions fire – Output transitions fire – State signals change x y Control s 1 b-/x- a+b+/y+ • Mostly limited to fundamental mode: a-/x+ynext input burst cannot arrive before s 2 s 4 stabilization at the outputs c-/y+ c+/y- • Extended Burst Mode (XBM) allows certain degree of concurrency EMICRO 2016 Synthesis of async controllers from STGs s 3 106

Conclusions • Controllers are the tiny (and smart) components of asynchronous systems. • Controllers may contain intricate relationships among events: concurrency, causality, choice. • Design automation is required. • STGs are a friendly formalism for specification: they resemble waveforms. EMICRO 2016 Synthesis of async controllers from STGs 107

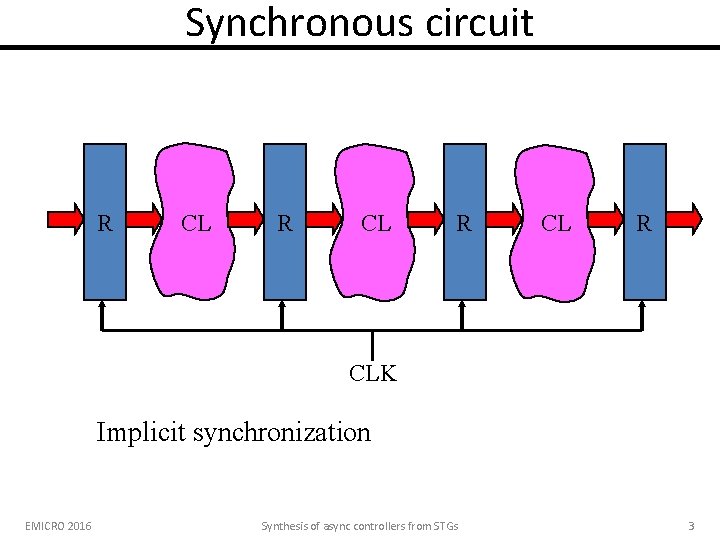

Gate vs wire delay models • Gate delay model: delays in gates, no delays in wires • Wire delay model: delays in gates and wires EMICRO 2016 Synthesis of async controllers from STGs 108