Introduction to the MIPS Lecture for CPSC 5155

![Memory Operand Example 1 n C code: g = h + A[8]; n g Memory Operand Example 1 n C code: g = h + A[8]; n g](https://slidetodoc.com/presentation_image_h2/5f3d6b233cc7d4bd3c85b2e8a113c9b8/image-17.jpg)

![Memory Operand Example 2 n C code: A[12] = h + A[8]; n h Memory Operand Example 2 n C code: A[12] = h + A[8]; n h](https://slidetodoc.com/presentation_image_h2/5f3d6b233cc7d4bd3c85b2e8a113c9b8/image-18.jpg)

![Compiling Loop Statements n C code: while (save[i] == k) i += 1; n Compiling Loop Statements n C code: while (save[i] == k) i += 1; n](https://slidetodoc.com/presentation_image_h2/5f3d6b233cc7d4bd3c85b2e8a113c9b8/image-37.jpg)

- Slides: 44

Introduction to the MIPS Lecture for CPSC 5155 Edward Bosworth, Ph. D. Computer Science Department Columbus State University

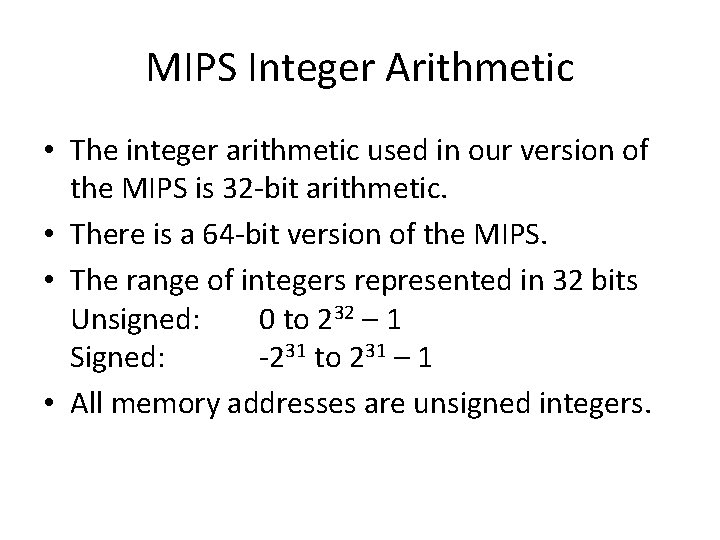

Introduction to the MIPS • The Microprocessor without Interlocked Pipeline Stages is a RISC microprocessor architecture developed by MIPS Technologies, Inc, starting in about 1981. • The first commercial product was the R 2000, marketed in 1984. • For a good historical account, go to http: //en. wikipedia. org/wiki/MIPS_architecture • MIPS processors are found in a variety of products, such as Ti. Vo, Cisco routers, the Nintendo 64, and Sony Play. Station.

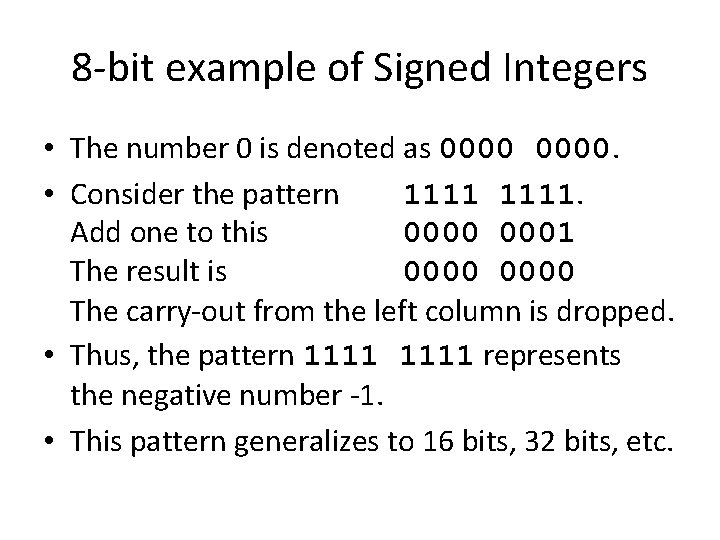

MIPS Integer Arithmetic • The integer arithmetic used in our version of the MIPS is 32 -bit arithmetic. • There is a 64 -bit version of the MIPS. • The range of integers represented in 32 bits Unsigned: 0 to 232 – 1 Signed: -231 to 231 – 1 • All memory addresses are unsigned integers.

8 -bit example of Signed Integers • The number 0 is denoted as 0000. • Consider the pattern 1111. Add one to this 0000 0001 The result is 0000 The carry-out from the left column is dropped. • Thus, the pattern 1111 represents the negative number -1. • This pattern generalizes to 16 bits, 32 bits, etc.

The Two’s Complement • Recall that the one’s complement of a bit pattern is achieved by changing every 0 to a 1 and every 1 to a 0. What is the sum X + X’? • We have only 0 + 1 = 1 and 1 + 0 = 1, so X + X’ = -1. Consider the example. X 1011 1001 X’ 0100 0110 Sum 1111 • If X + X’ = -1, then X + (X’ + 1) = 0; -X = X’ + 1.

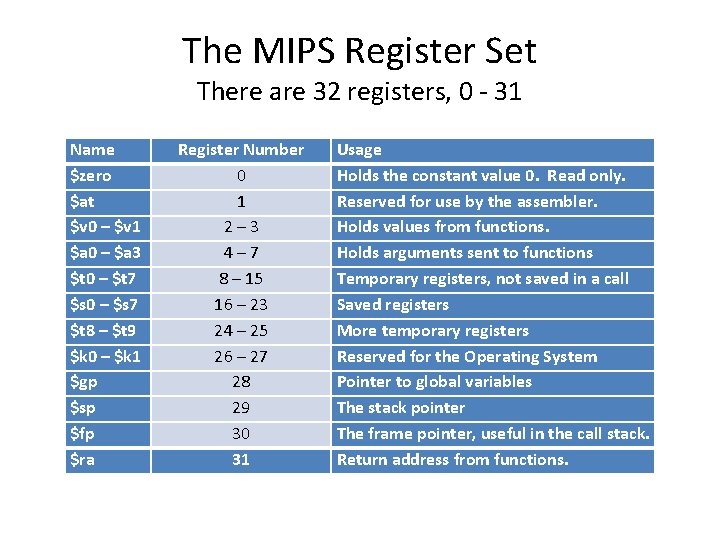

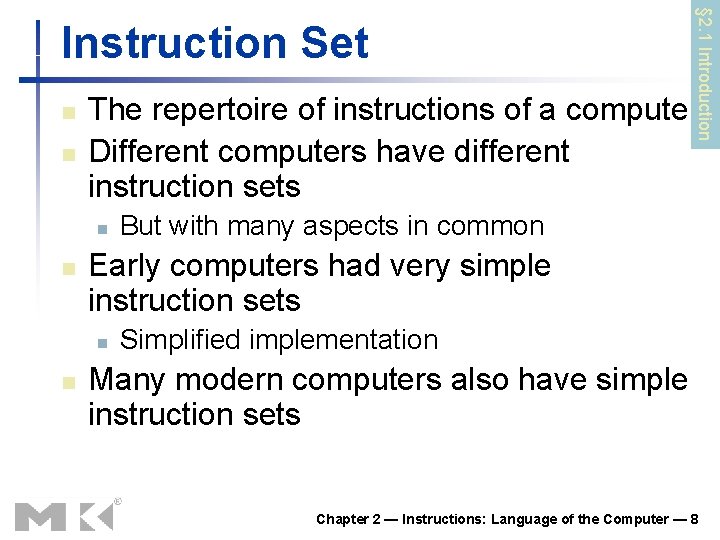

n n Arithmetic instructions use register operands MIPS has a 32 × 32 -bit register file n n Assembler names n n n Use for frequently accessed data Numbered 0 to 31 32 -bit data called a “word” $t 0, $t 1, …, $t 9 for temporary values $s 0, $s 1, …, $s 7 for saved variables § 2. 3 Operands of the Computer Hardware Register Operands Design Principle 2: Smaller is faster n c. f. main memory: millions of locations Chapter 2 — Instructions: Language of the Computer — 6

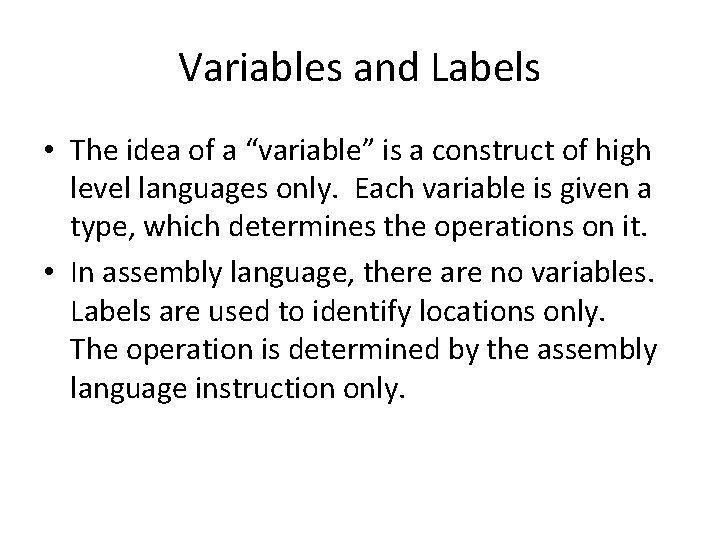

The MIPS Register Set There are 32 registers, 0 - 31 Name $zero $at $v 0 – $v 1 $a 0 – $a 3 $t 0 – $t 7 $s 0 – $s 7 $t 8 – $t 9 $k 0 – $k 1 $gp $sp $fp $ra Register Number 0 1 2– 3 4– 7 8 – 15 16 – 23 24 – 25 26 – 27 28 29 30 31 Usage Holds the constant value 0. Read only. Reserved for use by the assembler. Holds values from functions. Holds arguments sent to functions Temporary registers, not saved in a call Saved registers More temporary registers Reserved for the Operating System Pointer to global variables The stack pointer The frame pointer, useful in the call stack. Return address from functions.

n n The repertoire of instructions of a computer Different computers have different instruction sets n n But with many aspects in common Early computers had very simple instruction sets n n § 2. 1 Introduction Instruction Set Simplified implementation Many modern computers also have simple instruction sets Chapter 2 — Instructions: Language of the Computer — 8

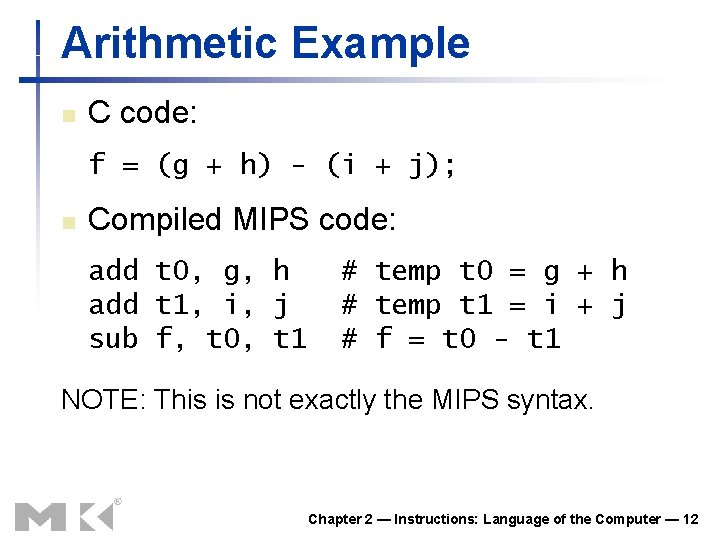

Variables and Labels • The idea of a “variable” is a construct of high level languages only. Each variable is given a type, which determines the operations on it. • In assembly language, there are no variables. Labels are used to identify locations only. The operation is determined by the assembly language instruction only.

The MIPS Instruction Set n n n Used as the example throughout the book Stanford MIPS commercialized by MIPS Technologies (www. mips. com) Large share of embedded core market n n Applications in consumer electronics, network/storage equipment, cameras, printers, … Typical of many modern ISAs n See MIPS Reference Data tear-out card, and Appendixes B and E Chapter 2 — Instructions: Language of the Computer — 10

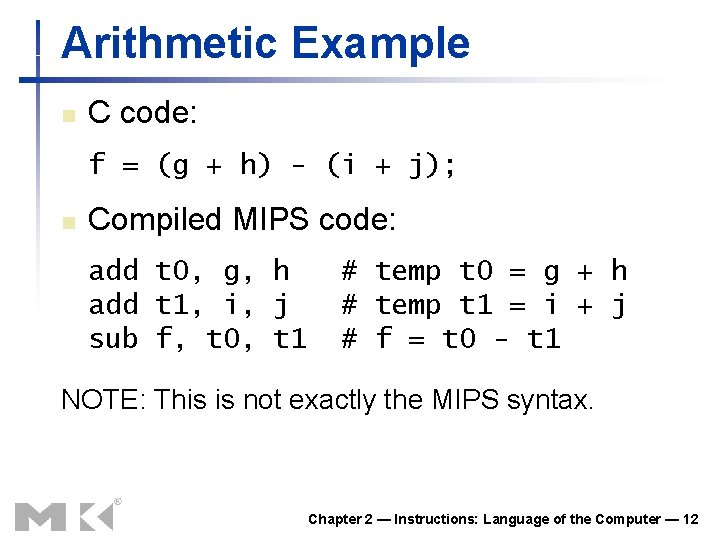

n Add and subtract, three operands n n n Two sources and one destination add a, b, c # a gets b + c All arithmetic operations have this form Design Principle 1: Simplicity favours regularity n n § 2. 2 Operations of the Computer Hardware Arithmetic Operations Regularity makes implementation simpler Simplicity enables higher performance at lower cost Chapter 2 — Instructions: Language of the Computer — 11

Arithmetic Example n C code: f = (g + h) - (i + j); n Compiled MIPS code: add t 0, g, h add t 1, i, j sub f, t 0, t 1 # temp t 0 = g + h # temp t 1 = i + j # f = t 0 - t 1 NOTE: This is not exactly the MIPS syntax. Chapter 2 — Instructions: Language of the Computer — 12

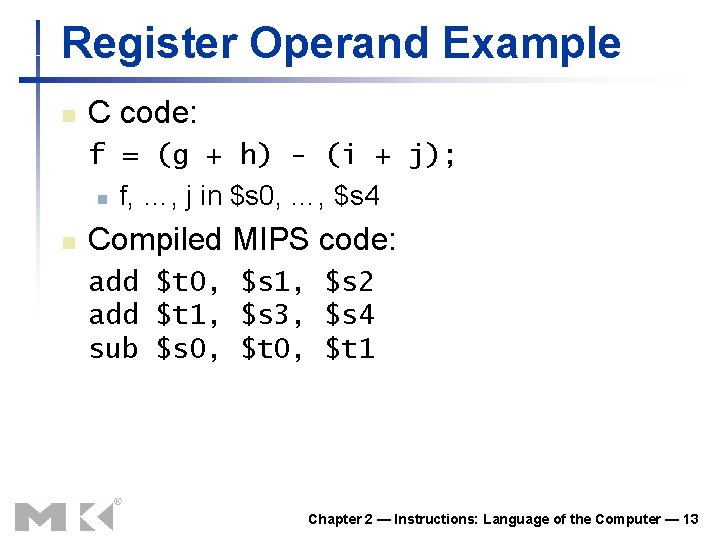

Register Operand Example n C code: f = (g + h) - (i + j); n f, …, j in $s 0, …, $s 4 n Compiled MIPS code: add $t 0, $s 1, $s 2 add $t 1, $s 3, $s 4 sub $s 0, $t 1 Chapter 2 — Instructions: Language of the Computer — 13

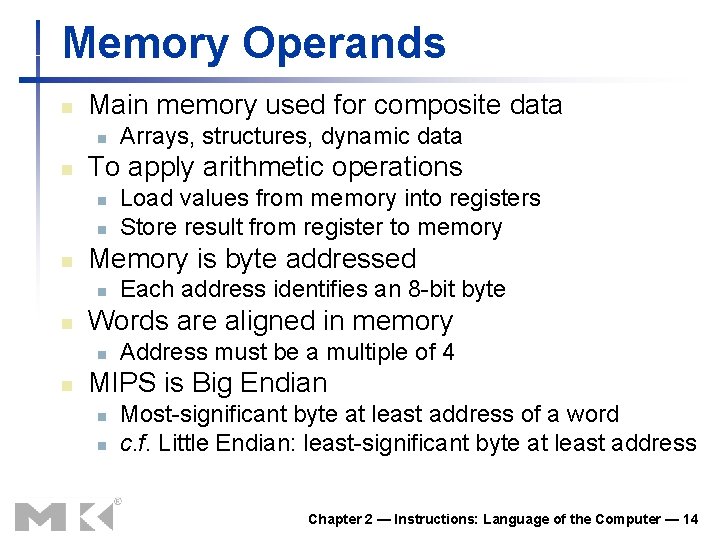

Memory Operands n Main memory used for composite data n n To apply arithmetic operations n n n Each address identifies an 8 -bit byte Words are aligned in memory n n Load values from memory into registers Store result from register to memory Memory is byte addressed n n Arrays, structures, dynamic data Address must be a multiple of 4 MIPS is Big Endian n n Most-significant byte at least address of a word c. f. Little Endian: least-significant byte at least address Chapter 2 — Instructions: Language of the Computer — 14

Big-Endian vs. Little-Endian

Memory Dump

![Memory Operand Example 1 n C code g h A8 n g Memory Operand Example 1 n C code: g = h + A[8]; n g](https://slidetodoc.com/presentation_image_h2/5f3d6b233cc7d4bd3c85b2e8a113c9b8/image-17.jpg)

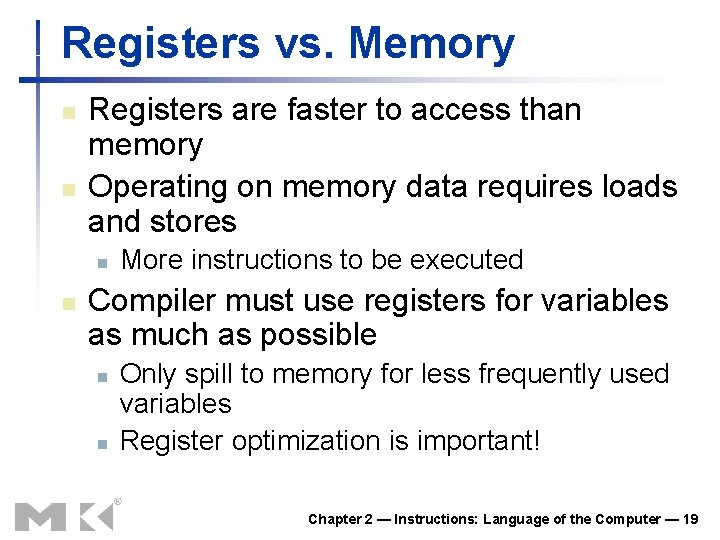

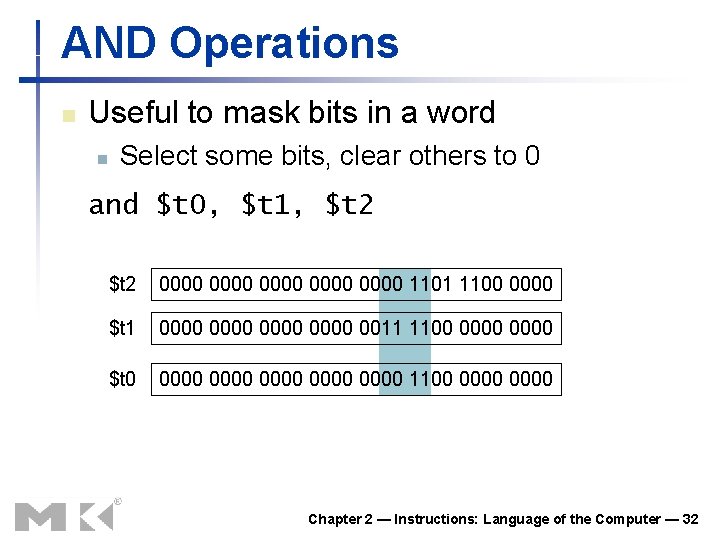

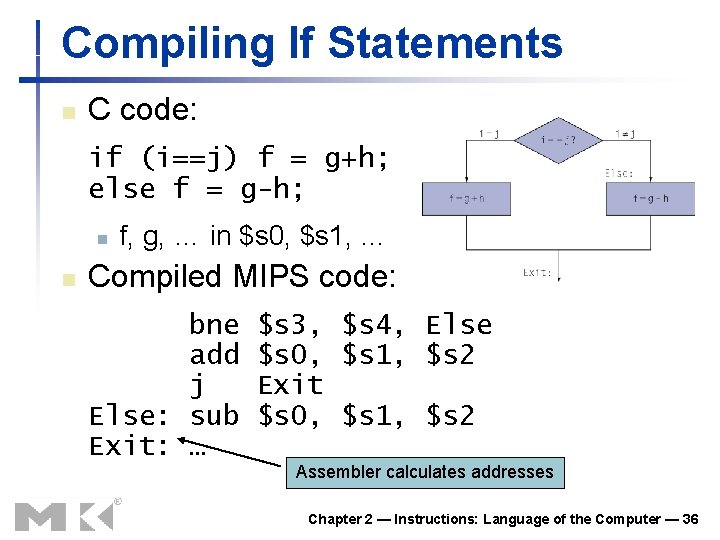

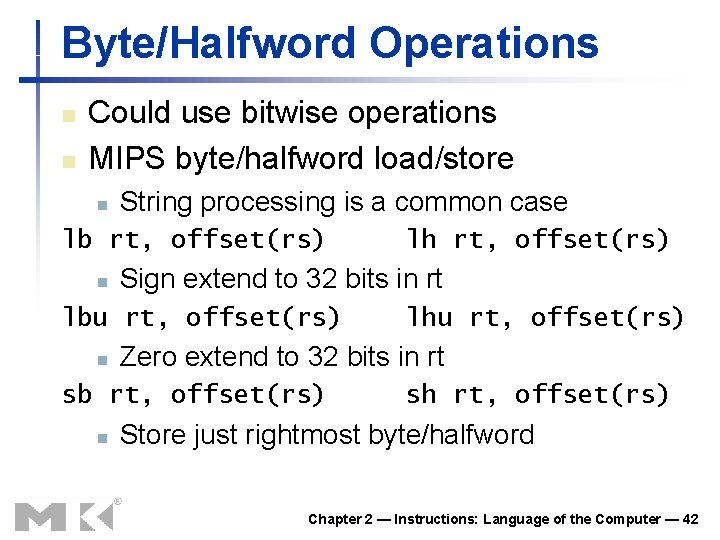

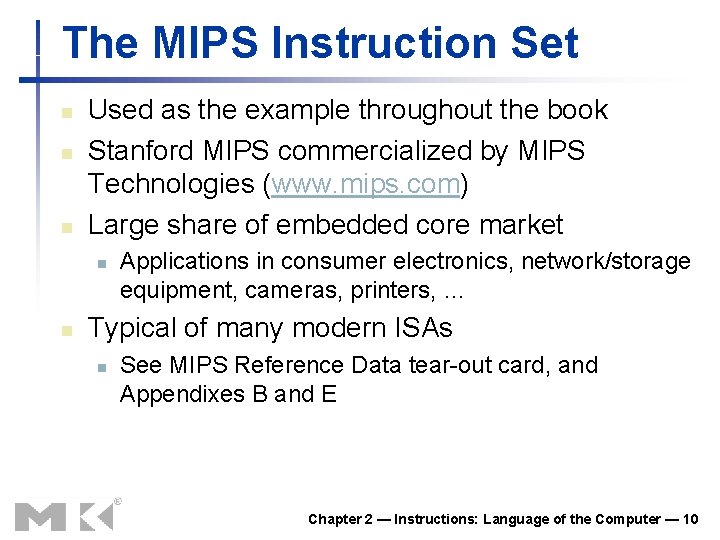

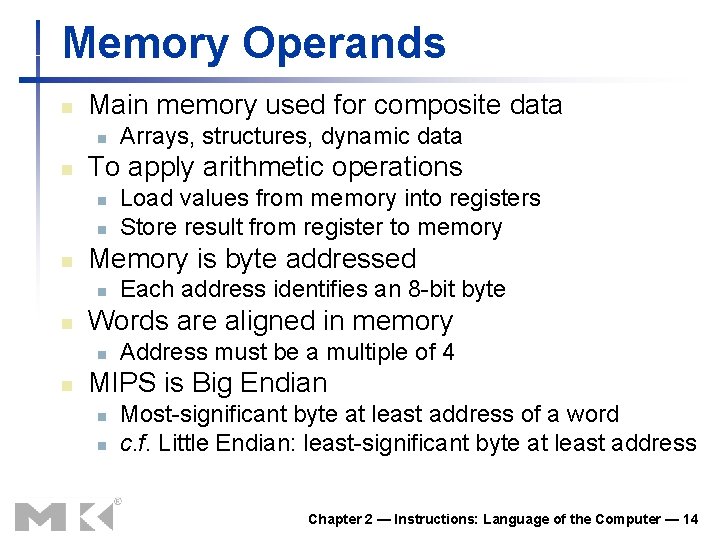

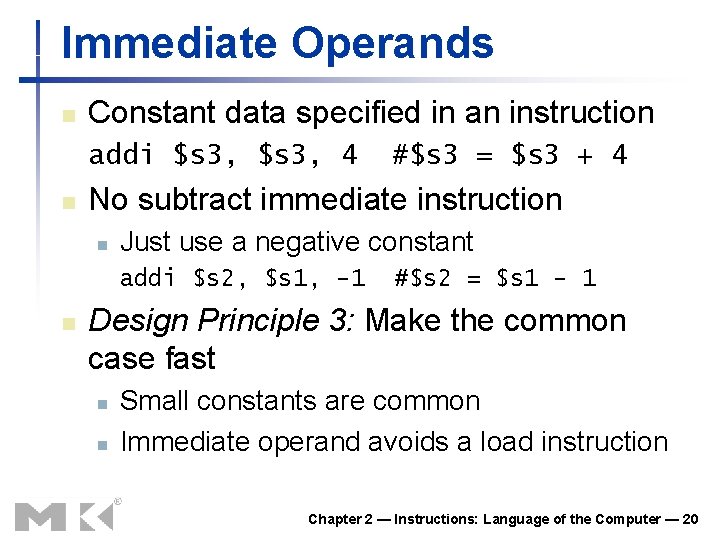

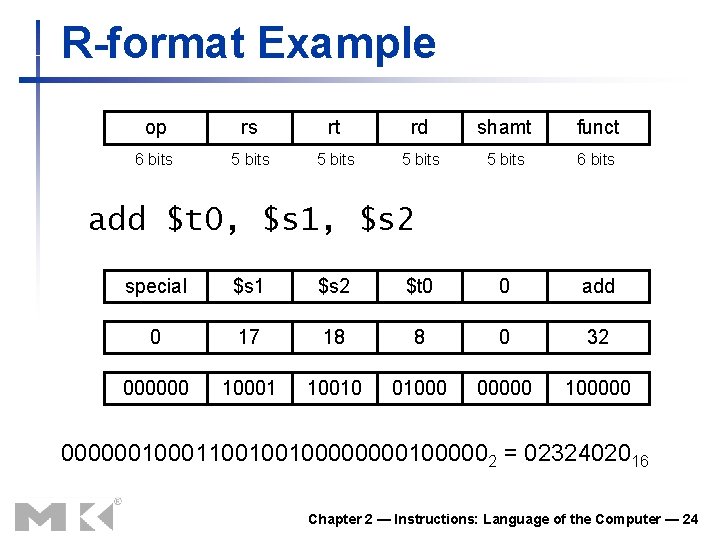

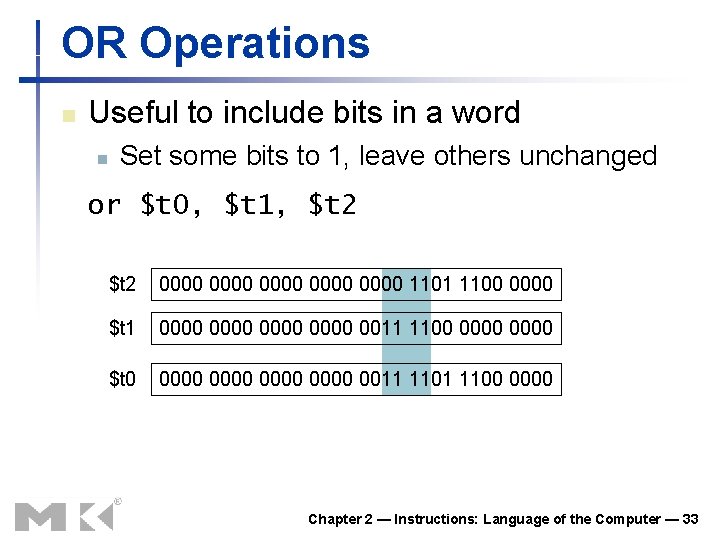

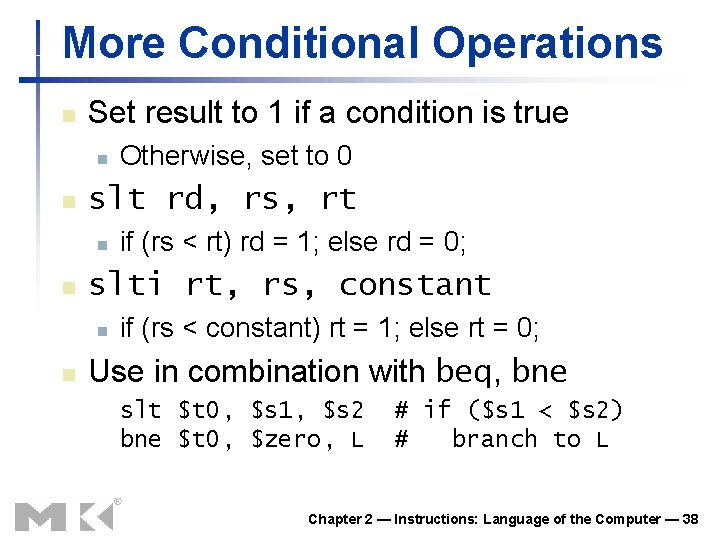

Memory Operand Example 1 n C code: g = h + A[8]; n g in $s 1, h in $s 2, base address of A in $s 3 n Compiled MIPS code: n Index 8 requires offset of 32 n 4 bytes per word lw $t 0, 32($s 3) add $s 1, $s 2, $t 0 offset # load word base register Chapter 2 — Instructions: Language of the Computer — 17

![Memory Operand Example 2 n C code A12 h A8 n h Memory Operand Example 2 n C code: A[12] = h + A[8]; n h](https://slidetodoc.com/presentation_image_h2/5f3d6b233cc7d4bd3c85b2e8a113c9b8/image-18.jpg)

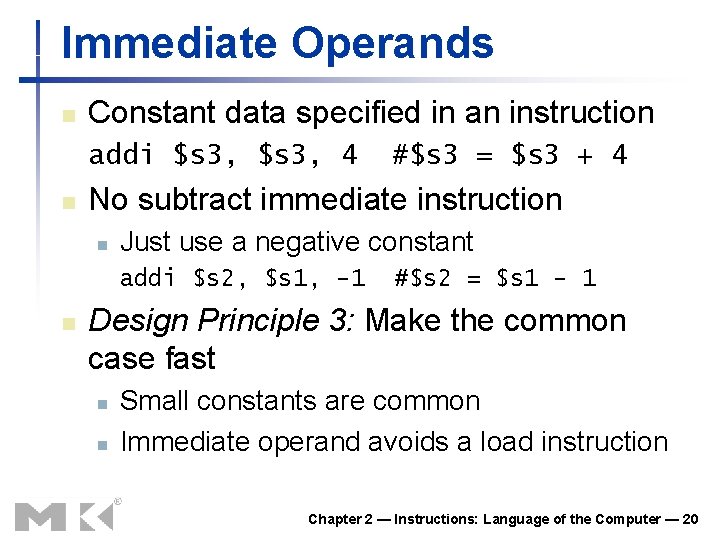

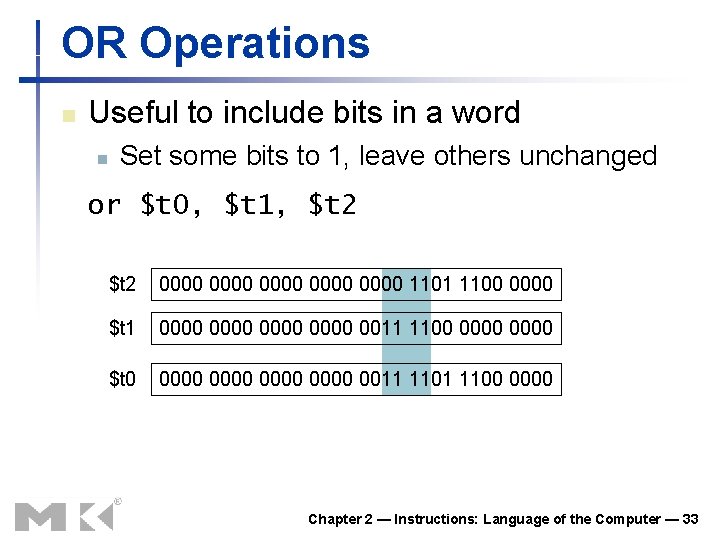

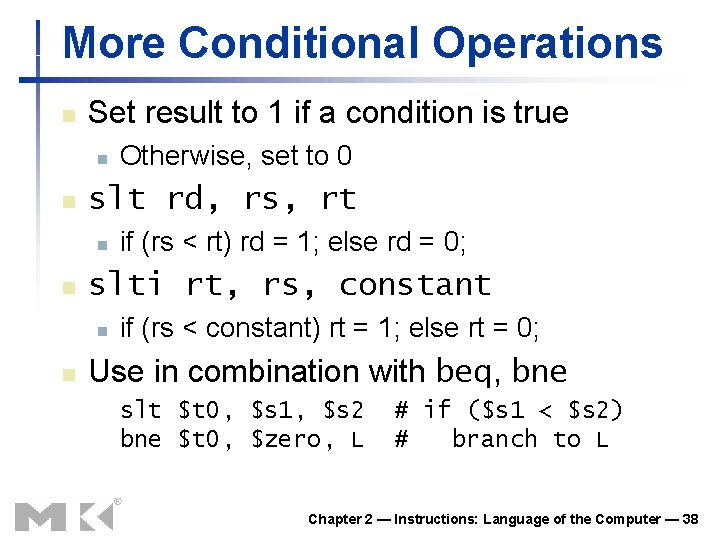

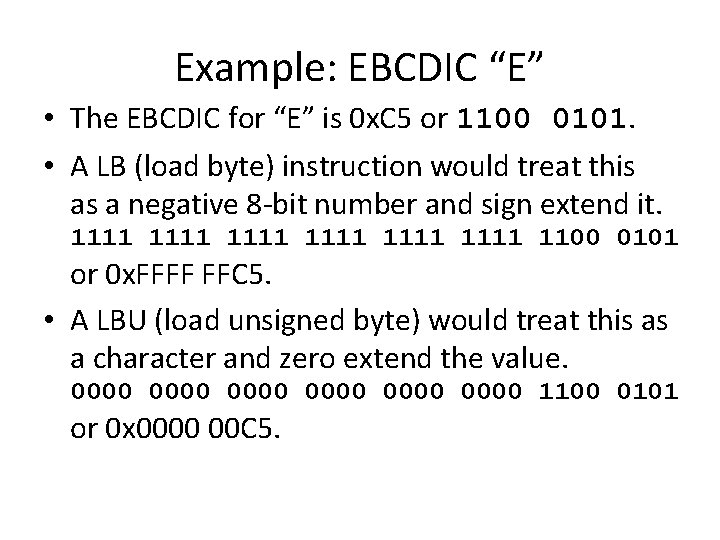

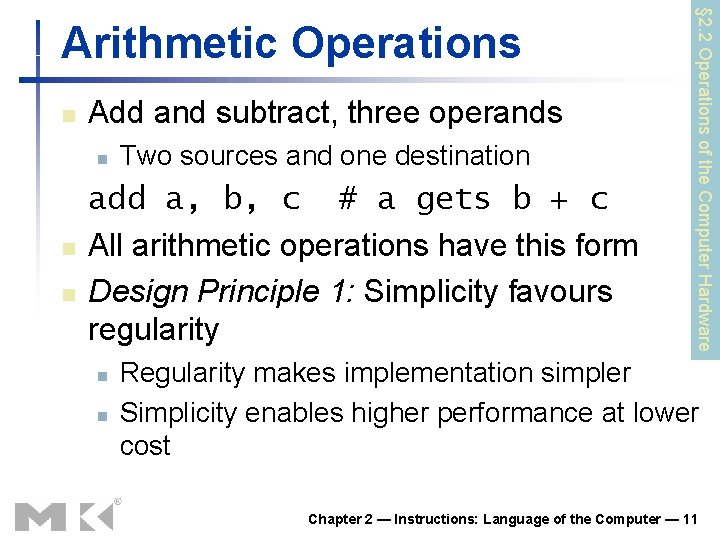

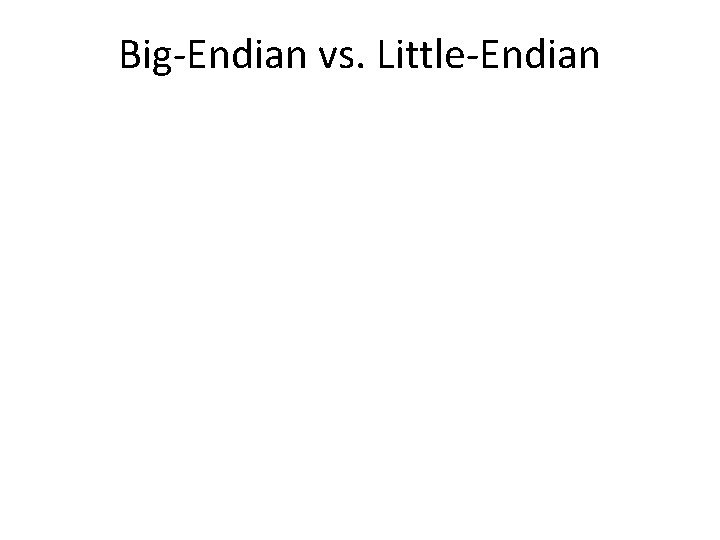

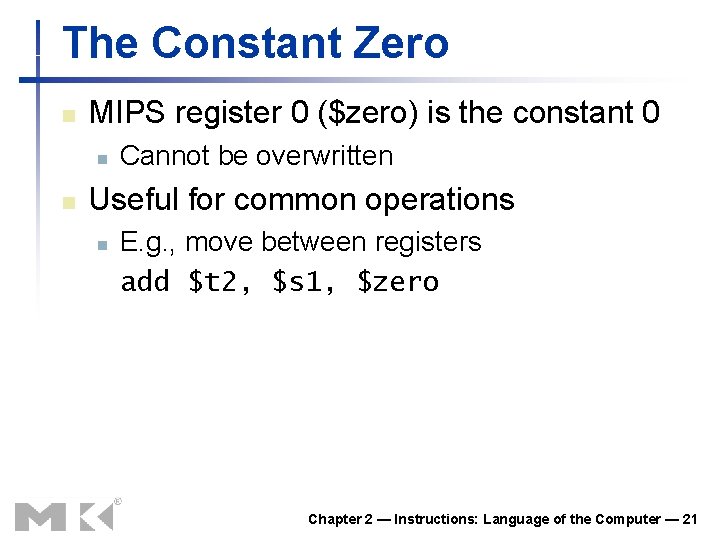

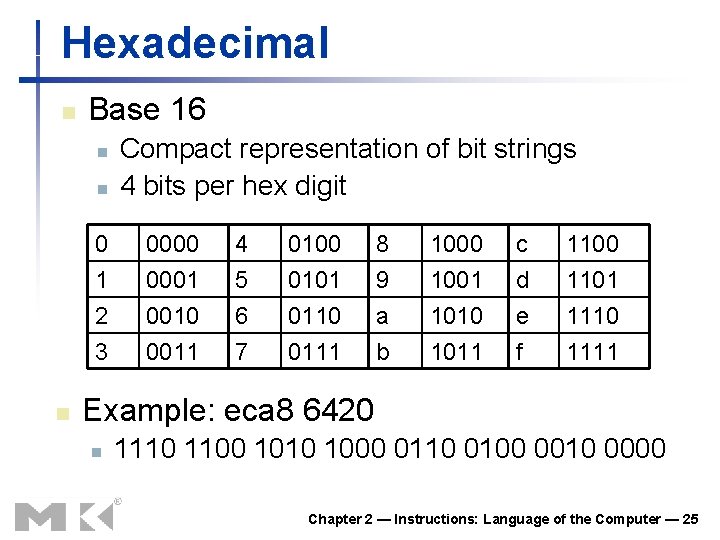

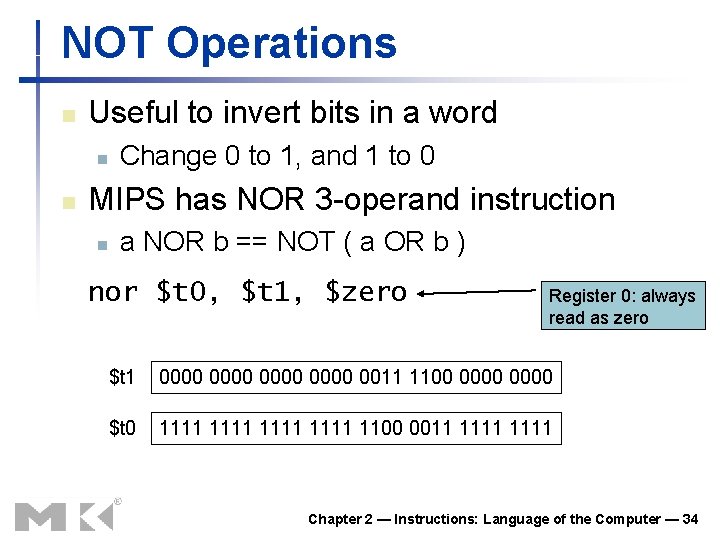

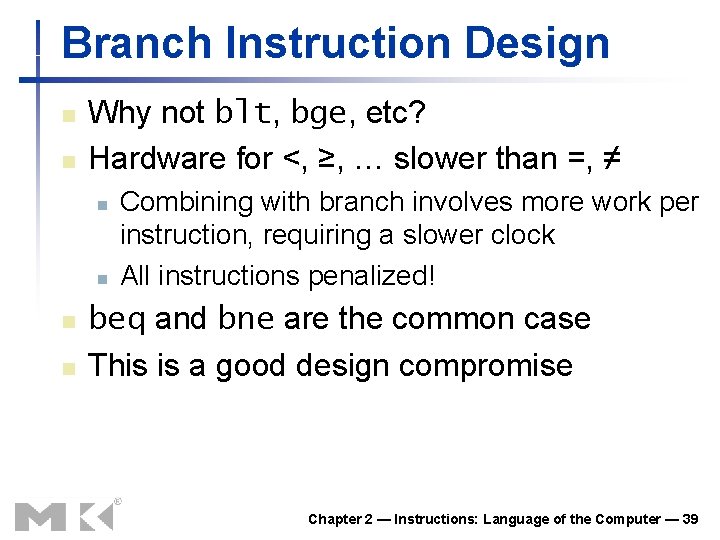

Memory Operand Example 2 n C code: A[12] = h + A[8]; n h in $s 2, base address of A in $s 3 n Compiled MIPS code: Index 8 requires offset of 32 lw $t 0, 32($s 3) # load word add $t 0, $s 2, $t 0 sw $t 0, 48($s 3) # store word n Chapter 2 — Instructions: Language of the Computer — 18

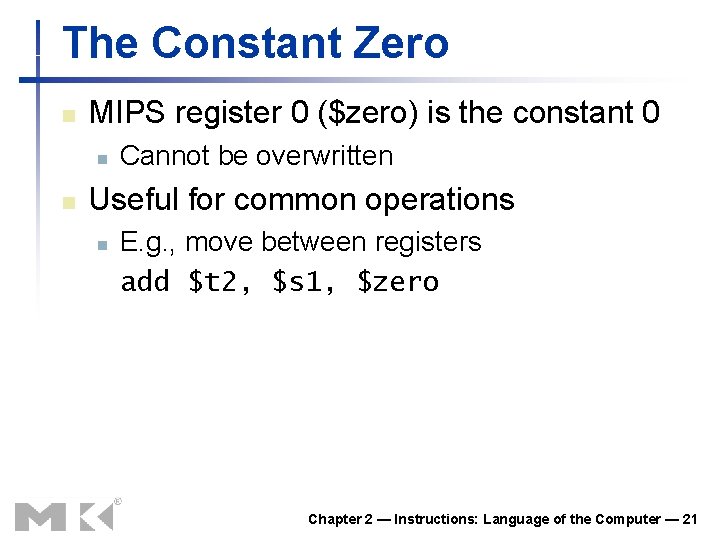

Registers vs. Memory n n Registers are faster to access than memory Operating on memory data requires loads and stores n n More instructions to be executed Compiler must use registers for variables as much as possible n n Only spill to memory for less frequently used variables Register optimization is important! Chapter 2 — Instructions: Language of the Computer — 19

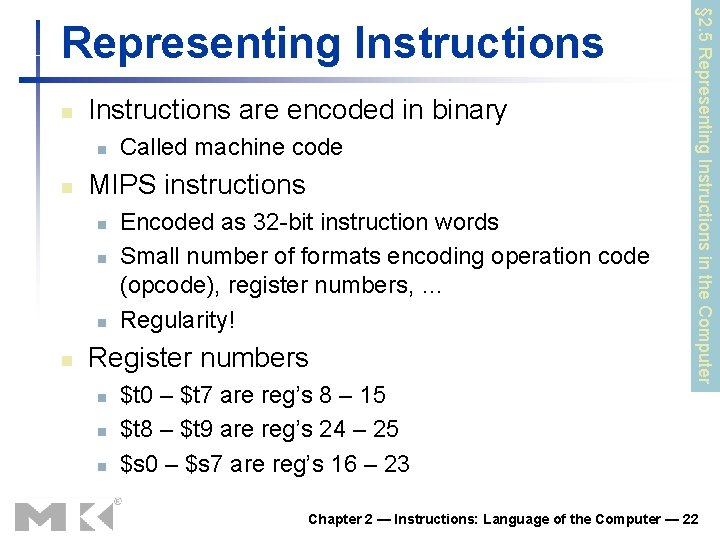

Immediate Operands n Constant data specified in an instruction addi $s 3, 4 n No subtract immediate instruction n Just use a negative constant addi $s 2, $s 1, -1 n #$s 3 = $s 3 + 4 #$s 2 = $s 1 - 1 Design Principle 3: Make the common case fast n n Small constants are common Immediate operand avoids a load instruction Chapter 2 — Instructions: Language of the Computer — 20

The Constant Zero n MIPS register 0 ($zero) is the constant 0 n n Cannot be overwritten Useful for common operations n E. g. , move between registers add $t 2, $s 1, $zero Chapter 2 — Instructions: Language of the Computer — 21

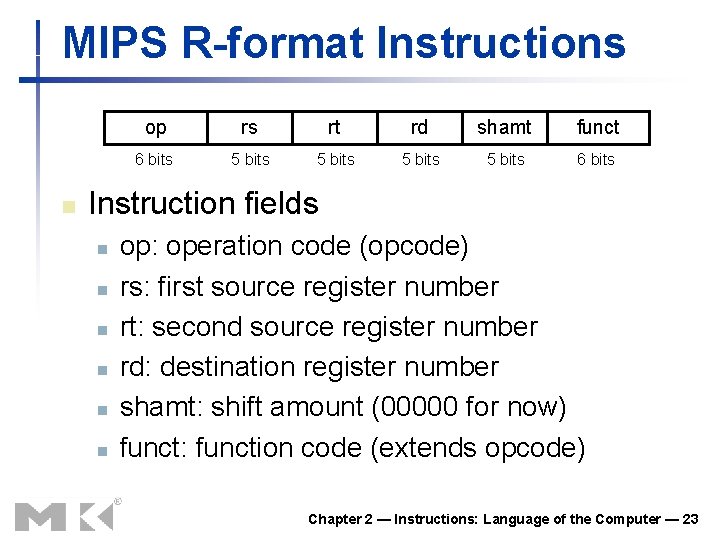

n Instructions are encoded in binary n n MIPS instructions n n Called machine code Encoded as 32 -bit instruction words Small number of formats encoding operation code (opcode), register numbers, … Regularity! Register numbers n n n $t 0 – $t 7 are reg’s 8 – 15 $t 8 – $t 9 are reg’s 24 – 25 $s 0 – $s 7 are reg’s 16 – 23 § 2. 5 Representing Instructions in the Computer Representing Instructions Chapter 2 — Instructions: Language of the Computer — 22

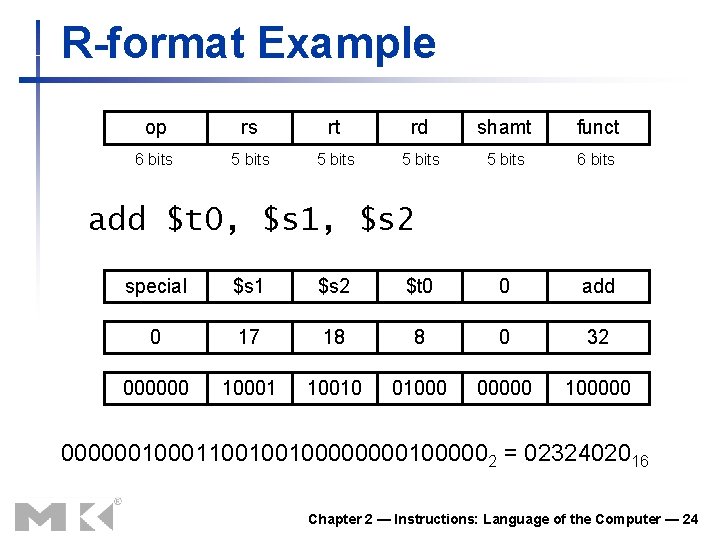

MIPS R-format Instructions n op rs rt rd shamt funct 6 bits 5 bits 6 bits Instruction fields n n n op: operation code (opcode) rs: first source register number rt: second source register number rd: destination register number shamt: shift amount (00000 for now) funct: function code (extends opcode) Chapter 2 — Instructions: Language of the Computer — 23

R-format Example op rs rt rd shamt funct 6 bits 5 bits 6 bits add $t 0, $s 1, $s 2 special $s 1 $s 2 $t 0 0 add 0 17 18 8 0 32 000000 10001 10010 01000 00000 10000001100100100001000002 = 0232402016 Chapter 2 — Instructions: Language of the Computer — 24

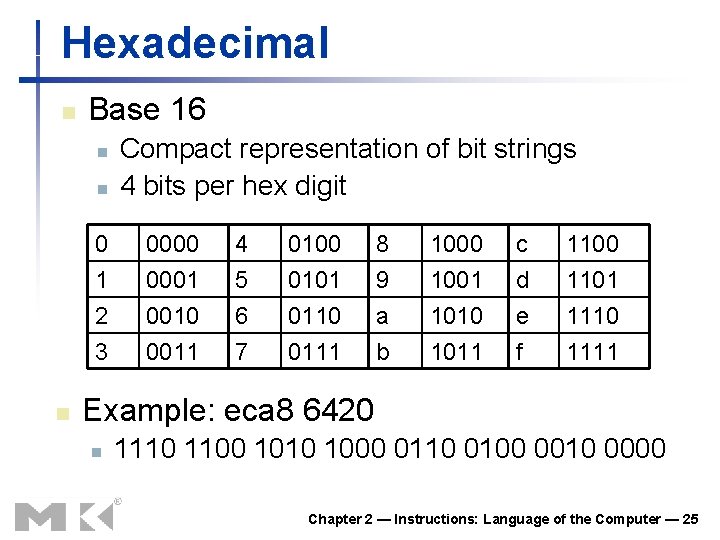

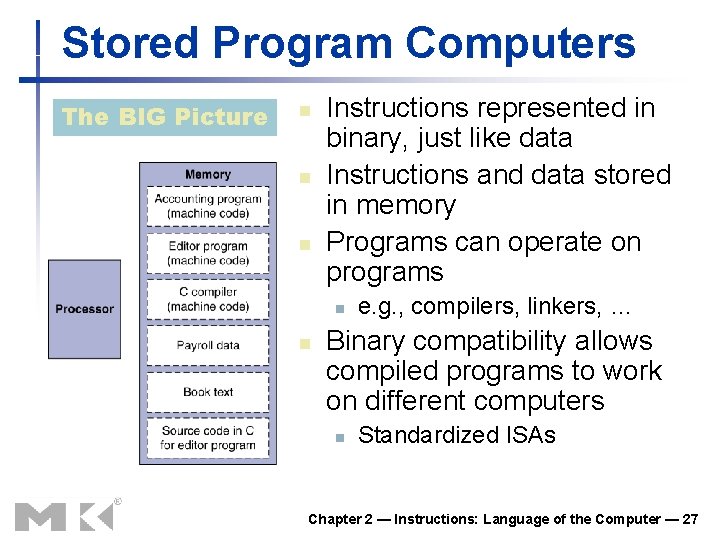

Hexadecimal n Base 16 n n 0 1 2 3 n Compact representation of bit strings 4 bits per hex digit 0000 0001 0010 0011 4 5 6 7 0100 0101 0110 0111 8 9 a b 1000 1001 1010 1011 c d e f 1100 1101 1110 1111 Example: eca 8 6420 n 1110 1100 1010 1000 0110 0100 0010 0000 Chapter 2 — Instructions: Language of the Computer — 25

MIPS I-format Instructions n rs rt constant or address 6 bits 5 bits 16 bits Immediate arithmetic and load/store instructions n n op rt: destination or source register number Constant: – 215 to +215 – 1 Address: offset added to base address in rs Design Principle 4: Good design demands good compromises n n Different formats complicate decoding, but allow 32 -bit instructions uniformly Keep formats as similar as possible Chapter 2 — Instructions: Language of the Computer — 26

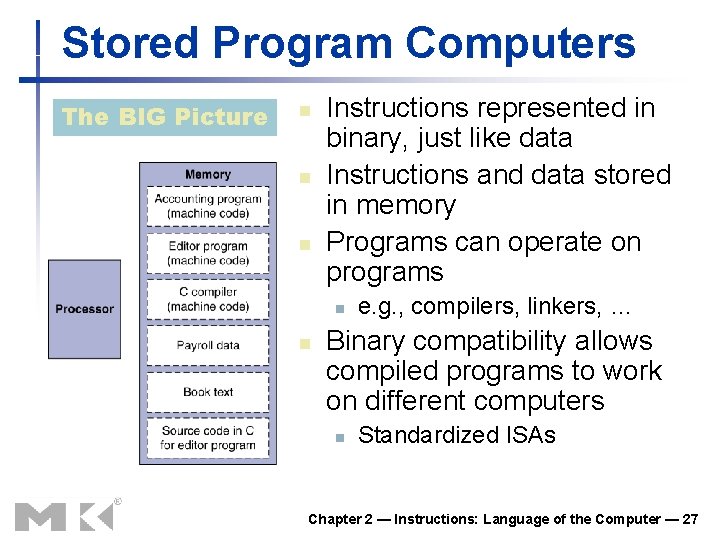

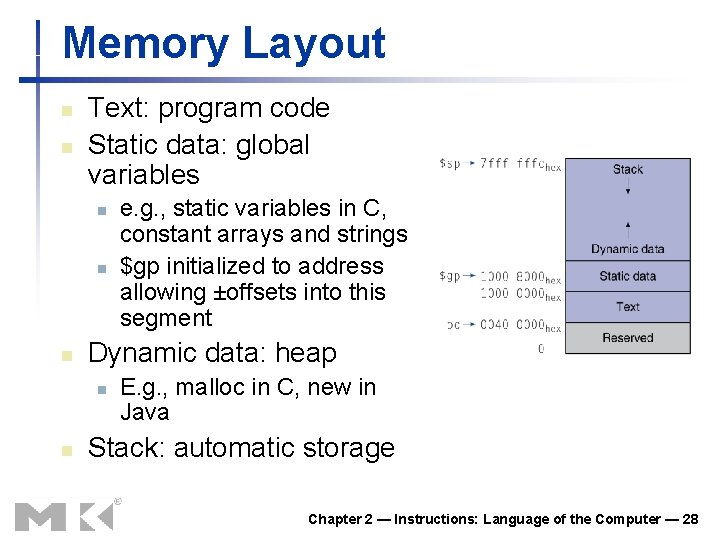

Stored Program Computers The BIG Picture n n n Instructions represented in binary, just like data Instructions and data stored in memory Programs can operate on programs n n e. g. , compilers, linkers, … Binary compatibility allows compiled programs to work on different computers n Standardized ISAs Chapter 2 — Instructions: Language of the Computer — 27

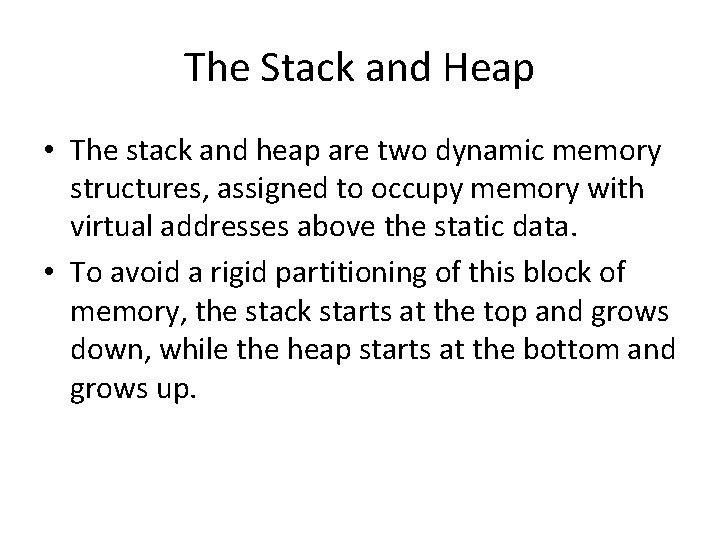

Memory Layout n n Text: program code Static data: global variables n n n Dynamic data: heap n n e. g. , static variables in C, constant arrays and strings $gp initialized to address allowing ±offsets into this segment E. g. , malloc in C, new in Java Stack: automatic storage Chapter 2 — Instructions: Language of the Computer — 28

All Memory Maps Use Virtual Addresses • Virtual memory is a service of the computer’s operating system in conjunction with the MMU (Memory Management Unit). • Logical addresses are generated by the code and then translated into physical addresses. • For example, the global pointer contains the logical address 0 x 1000 8000. The actual physical address is determined by the OS.

The Stack and Heap • The stack and heap are two dynamic memory structures, assigned to occupy memory with virtual addresses above the static data. • To avoid a rigid partitioning of this block of memory, the stack starts at the top and grows down, while the heap starts at the bottom and grows up.

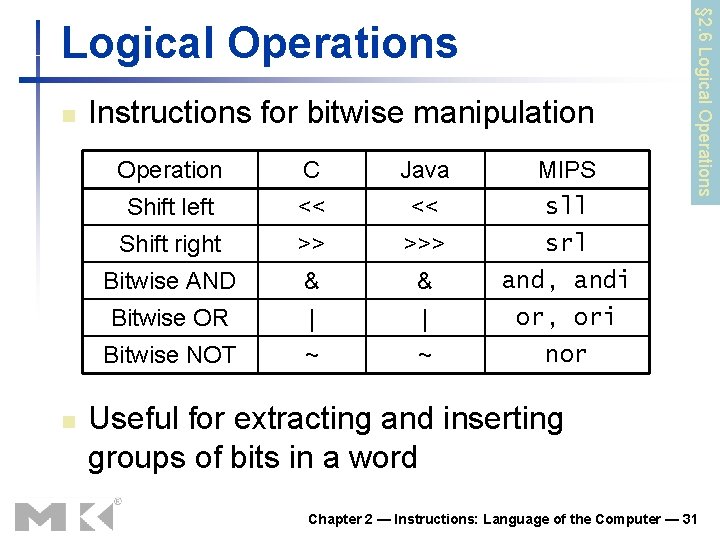

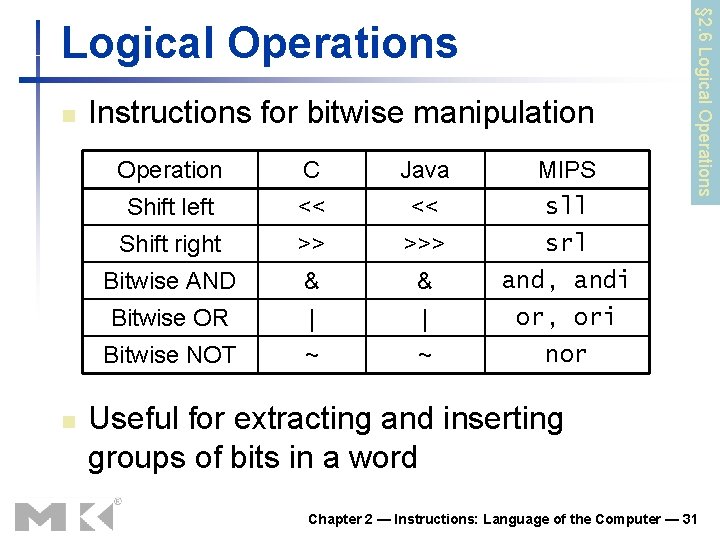

n n Instructions for bitwise manipulation Operation C Java MIPS Shift left << << sll Shift right >> >>> srl Bitwise AND & & and, andi Bitwise OR | | or, ori Bitwise NOT ~ ~ nor § 2. 6 Logical Operations Useful for extracting and inserting groups of bits in a word Chapter 2 — Instructions: Language of the Computer — 31

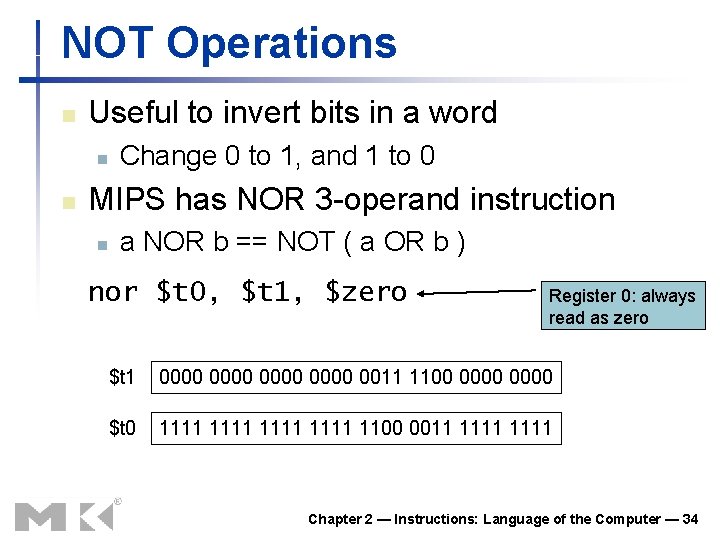

AND Operations n Useful to mask bits in a word n Select some bits, clear others to 0 and $t 0, $t 1, $t 2 0000 0000 1101 1100 0000 $t 1 0000 0011 1100 0000 $t 0 0000 0000 1100 0000 Chapter 2 — Instructions: Language of the Computer — 32

OR Operations n Useful to include bits in a word n Set some bits to 1, leave others unchanged or $t 0, $t 1, $t 2 0000 0000 1101 1100 0000 $t 1 0000 0011 1100 0000 $t 0 0000 0011 1100 0000 Chapter 2 — Instructions: Language of the Computer — 33

NOT Operations n Useful to invert bits in a word n n Change 0 to 1, and 1 to 0 MIPS has NOR 3 -operand instruction n a NOR b == NOT ( a OR b ) nor $t 0, $t 1, $zero Register 0: always read as zero $t 1 0000 0011 1100 0000 $t 0 1111 1100 0011 1111 Chapter 2 — Instructions: Language of the Computer — 34

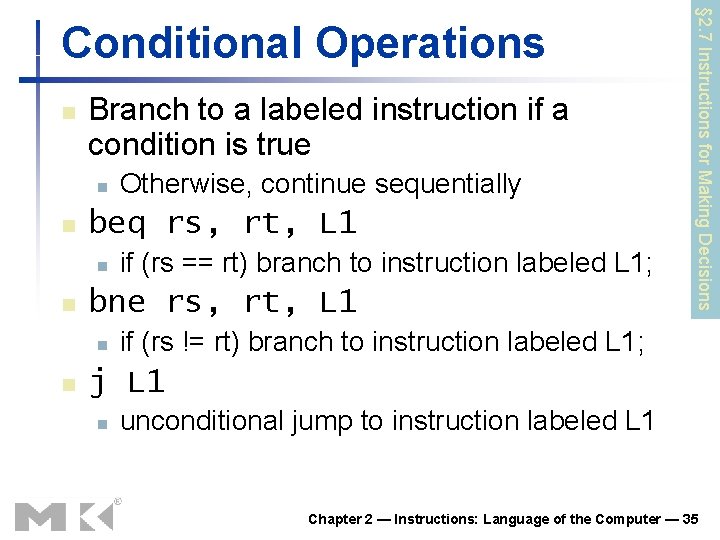

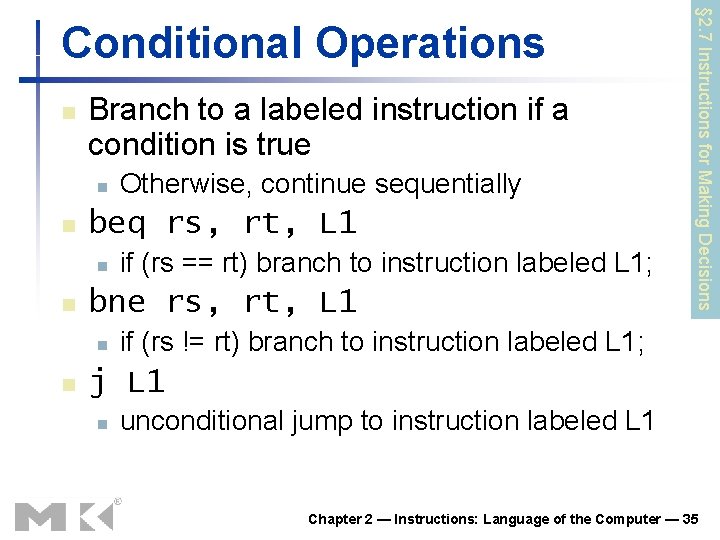

n Branch to a labeled instruction if a condition is true n n beq rs, rt, L 1 n n if (rs == rt) branch to instruction labeled L 1; bne rs, rt, L 1 n n Otherwise, continue sequentially § 2. 7 Instructions for Making Decisions Conditional Operations if (rs != rt) branch to instruction labeled L 1; j L 1 n unconditional jump to instruction labeled L 1 Chapter 2 — Instructions: Language of the Computer — 35

Compiling If Statements n C code: if (i==j) f = g+h; else f = g-h; n n f, g, … in $s 0, $s 1, … Compiled MIPS code: bne add j Else: sub Exit: … $s 3, $s 4, Else $s 0, $s 1, $s 2 Exit $s 0, $s 1, $s 2 Assembler calculates addresses Chapter 2 — Instructions: Language of the Computer — 36

![Compiling Loop Statements n C code while savei k i 1 n Compiling Loop Statements n C code: while (save[i] == k) i += 1; n](https://slidetodoc.com/presentation_image_h2/5f3d6b233cc7d4bd3c85b2e8a113c9b8/image-37.jpg)

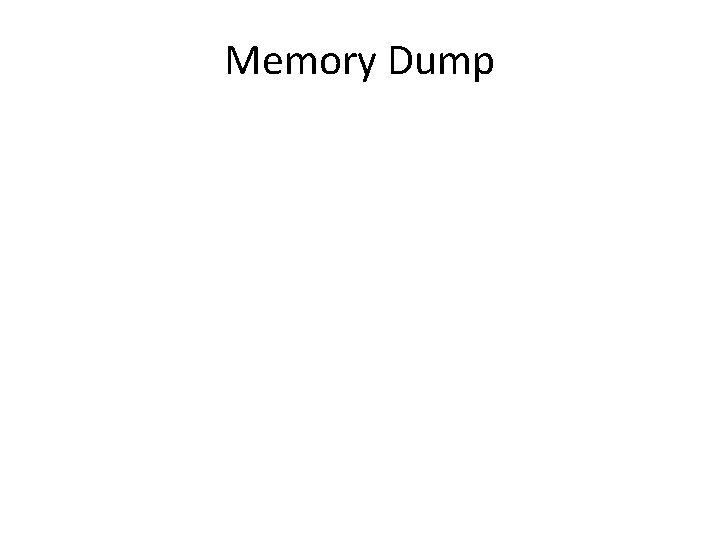

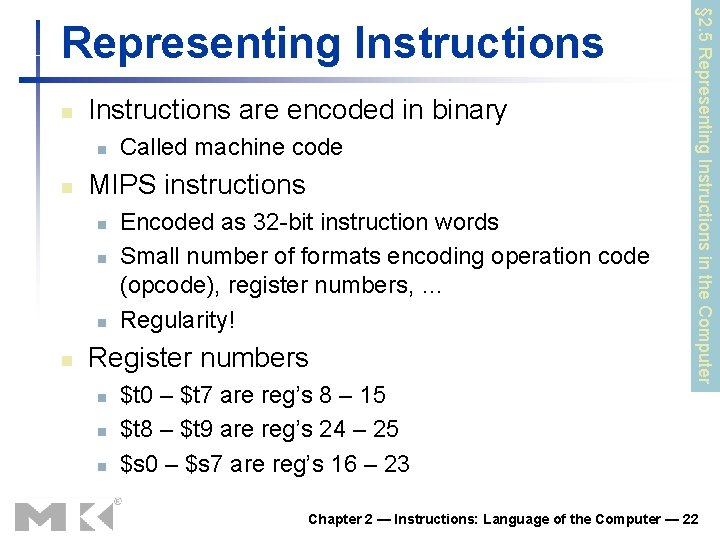

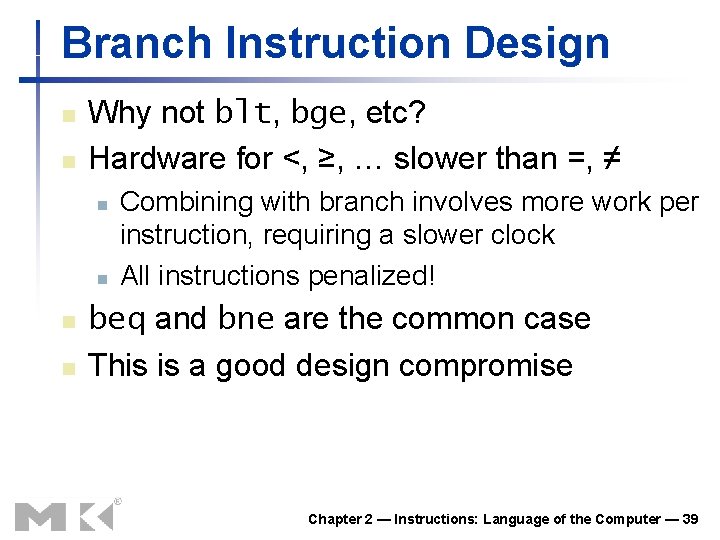

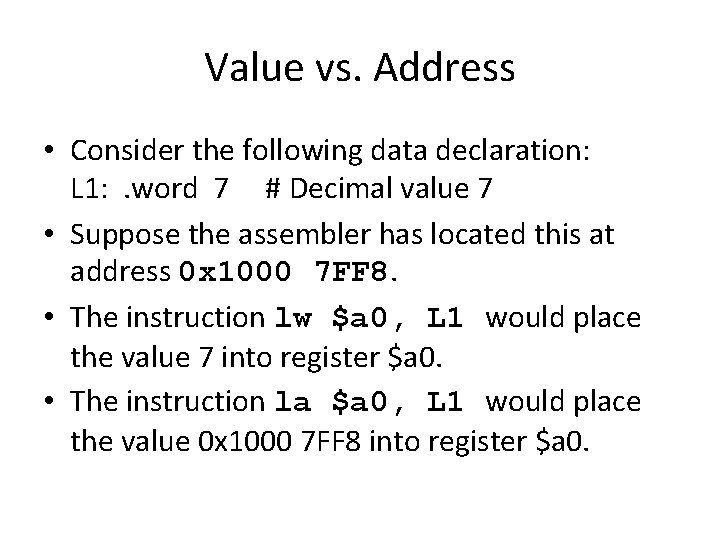

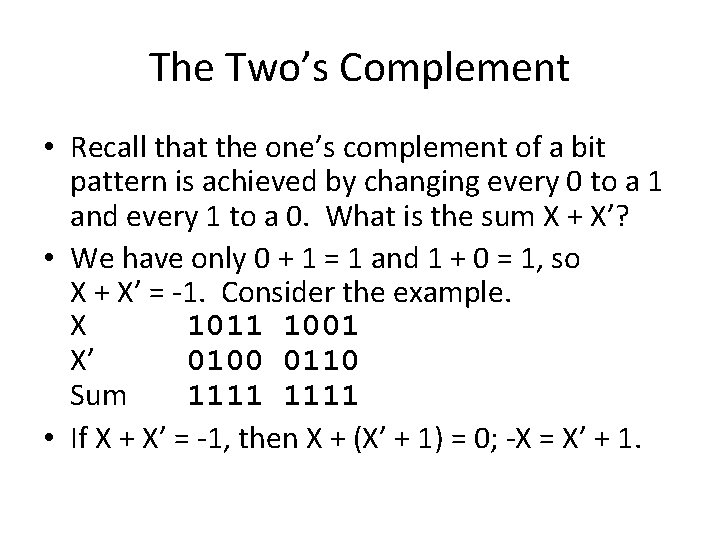

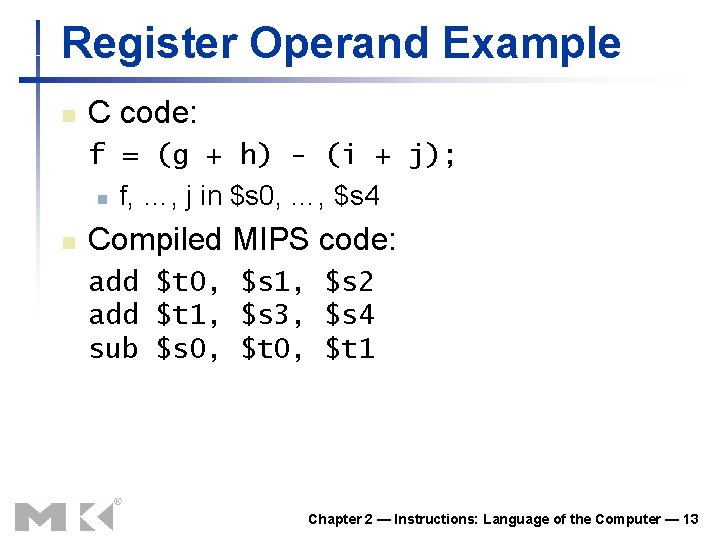

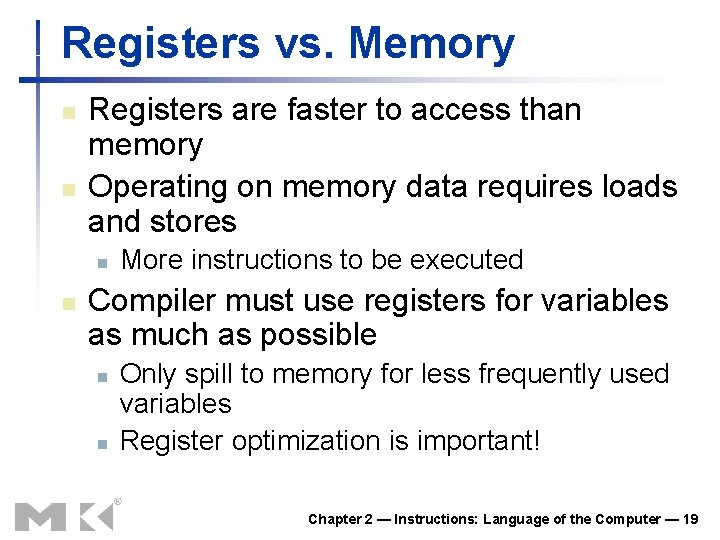

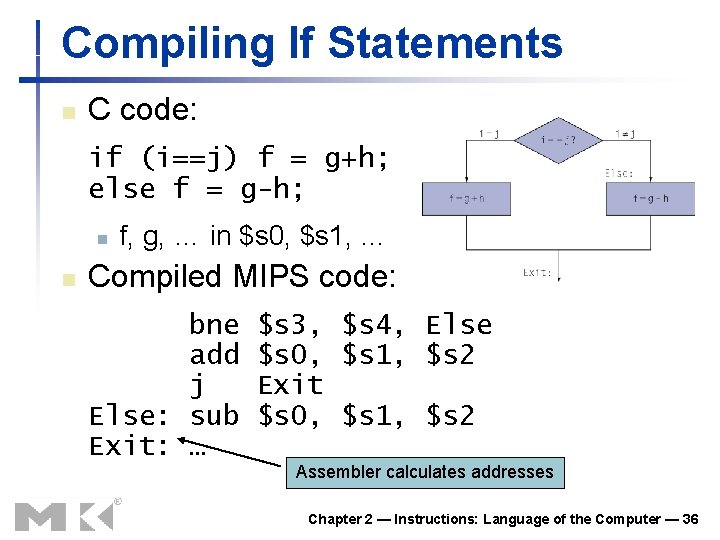

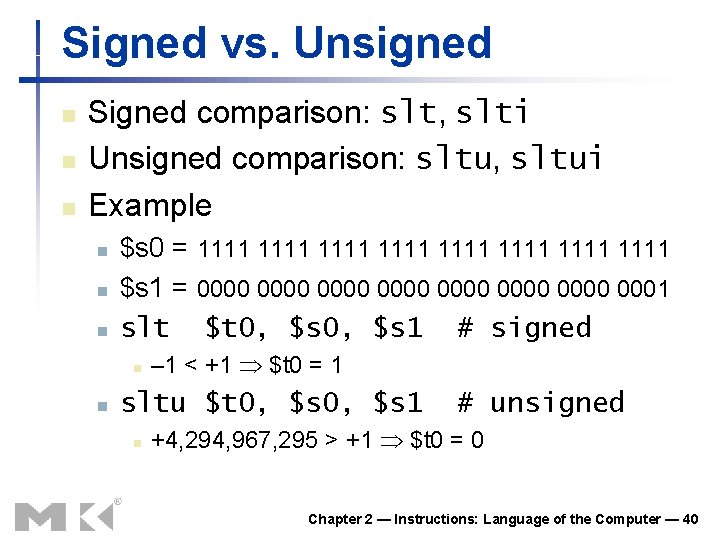

Compiling Loop Statements n C code: while (save[i] == k) i += 1; n n i in $s 3, k in $s 5, address of save in $s 6 Compiled MIPS code: Loop: sll add lw bne addi j Exit: … $t 1, $t 0, $s 3, Loop $s 3, 2 $t 1, $s 6 0($t 1) $s 5, Exit $s 3, 1 Chapter 2 — Instructions: Language of the Computer — 37

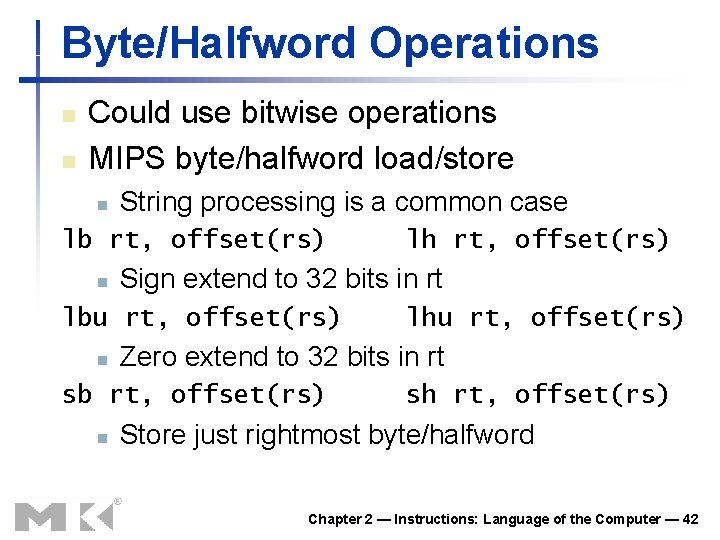

More Conditional Operations n Set result to 1 if a condition is true n n slt rd, rs, rt n n if (rs < rt) rd = 1; else rd = 0; slti rt, rs, constant n n Otherwise, set to 0 if (rs < constant) rt = 1; else rt = 0; Use in combination with beq, bne slt $t 0, $s 1, $s 2 bne $t 0, $zero, L # if ($s 1 < $s 2) # branch to L Chapter 2 — Instructions: Language of the Computer — 38

Branch Instruction Design n n Why not blt, bge, etc? Hardware for <, ≥, … slower than =, ≠ n n Combining with branch involves more work per instruction, requiring a slower clock All instructions penalized! beq and bne are the common case This is a good design compromise Chapter 2 — Instructions: Language of the Computer — 39

Signed vs. Unsigned n n n Signed comparison: slt, slti Unsigned comparison: sltu, sltui Example n n n $s 0 = 1111 1111 $s 1 = 0000 0000 0001 slt $t 0, $s 1 # signed n n – 1 < +1 $t 0 = 1 sltu $t 0, $s 1 n # unsigned +4, 294, 967, 295 > +1 $t 0 = 0 Chapter 2 — Instructions: Language of the Computer — 40

The MIPS is a Load/Store RISC • Only 2 types of instructions reference memory Load register from memory: LW, LBU, etc. Store register to memory: SW, SB, etc. • This restriction leads to a CPU design that is considerably simpler and faster. • The MIPS is designed to work with a virtual memory system. The load/store feature simplifies the handling of page faults. More on this when we discuss the control unit.

Byte/Halfword Operations n n Could use bitwise operations MIPS byte/halfword load/store n String processing is a common case lb rt, offset(rs) n Sign extend to 32 bits in rt lbu rt, offset(rs) n lhu rt, offset(rs) Zero extend to 32 bits in rt sb rt, offset(rs) n lh rt, offset(rs) sh rt, offset(rs) Store just rightmost byte/halfword Chapter 2 — Instructions: Language of the Computer — 42

Example: EBCDIC “E” • The EBCDIC for “E” is 0 x. C 5 or 1100 0101. • A LB (load byte) instruction would treat this as a negative 8 -bit number and sign extend it. 1111 1111 1100 0101 or 0 x. FFFF FFC 5. • A LBU (load unsigned byte) would treat this as a character and zero extend the value. 0000 0000 1100 0101 or 0 x 0000 00 C 5.

Value vs. Address • Consider the following data declaration: L 1: . word 7 # Decimal value 7 • Suppose the assembler has located this at address 0 x 1000 7 FF 8. • The instruction lw $a 0, L 1 would place the value 7 into register $a 0. • The instruction la $a 0, L 1 would place the value 0 x 1000 7 FF 8 into register $a 0.