FPGA Architecture TsungYi Wu Topics n Designers n

- Slides: 33

FPGA Architecture Tsung-Yi Wu

Topics n Designer’s n FPGA Choice Architecture n Example: Spartan-II Architecture n Xilinx vs. Altera

Designer’s Choice n SSI (small scale integrated circuits) or MSI (medium scale integrated circuits) components • Difficulties arises as design size increases • Interconnections grow with complexity resulting in a prolonged testing phase n Simple programmable logic devices – PALs (programmable array logic) – PLAs (programmable logic array) • Architecture not scalable; Power consumption and delays play an important role in extending the architecture to complex designs • Implementation of larger designs leads to same difficulty as that of discrete components

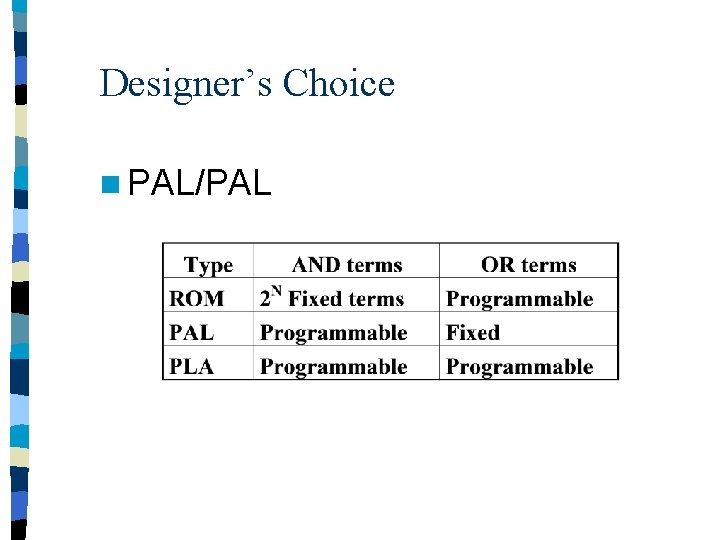

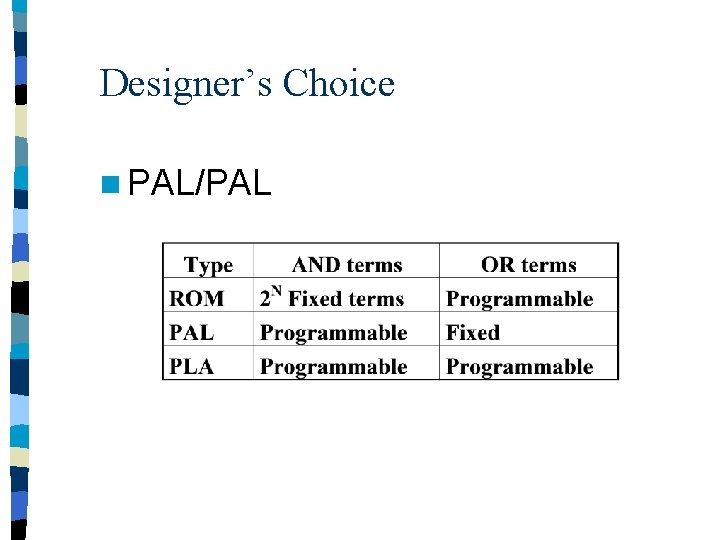

Designer’s Choice n PAL/PAL

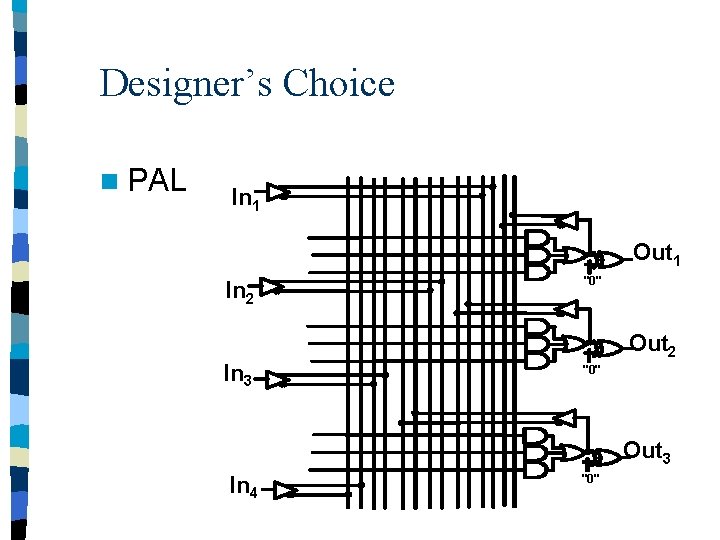

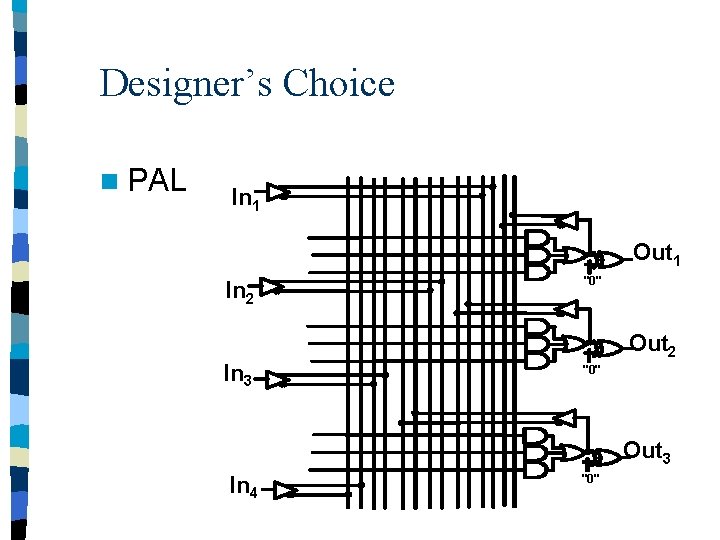

Designer’s Choice n PAL In 1 Out 1 In 2 "0" Out 2 In 3 "0" Out 3 In 4 "0"

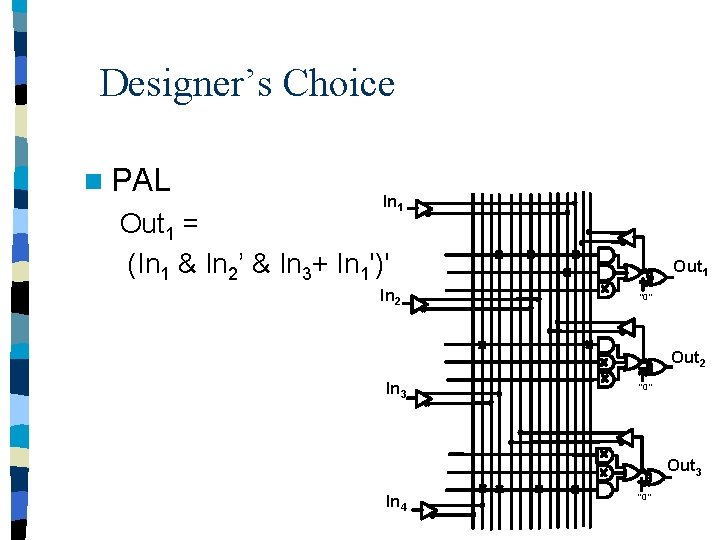

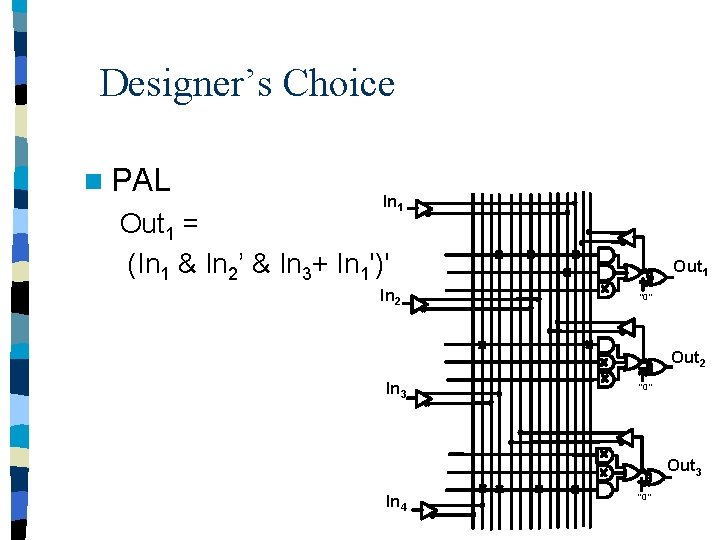

Designer’s Choice n PAL In 1 Out 1 = (In 1 & In 2’ & In 3+ In 1')' In 2 Out 1 "0" Out 2 In 3 "0" Out 3 In 4 "0"

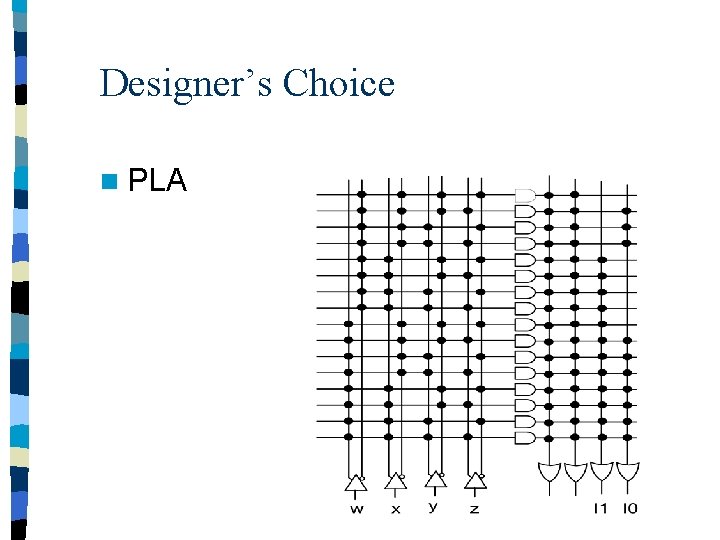

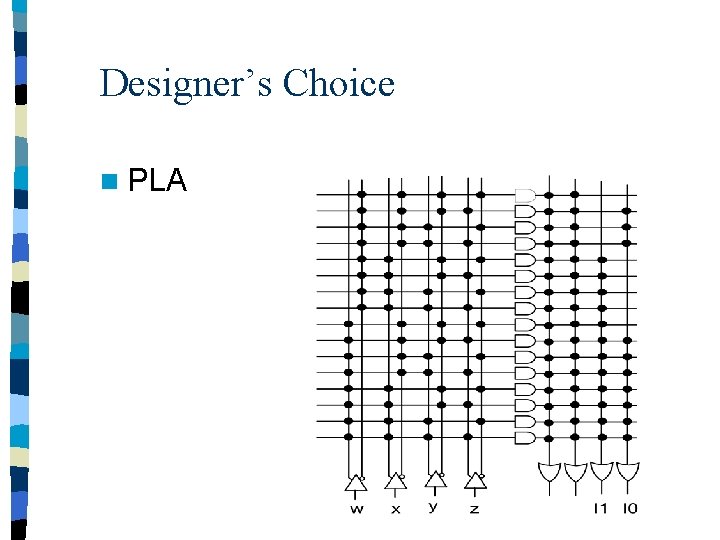

Designer’s Choice n PLA

Designer’s Choice n FPGA (Field Programmable Logic Devices) • • • Customized by end user Implements multi-level logic function Fast time to market and low risk Channel Based Routing Post Layout Timing

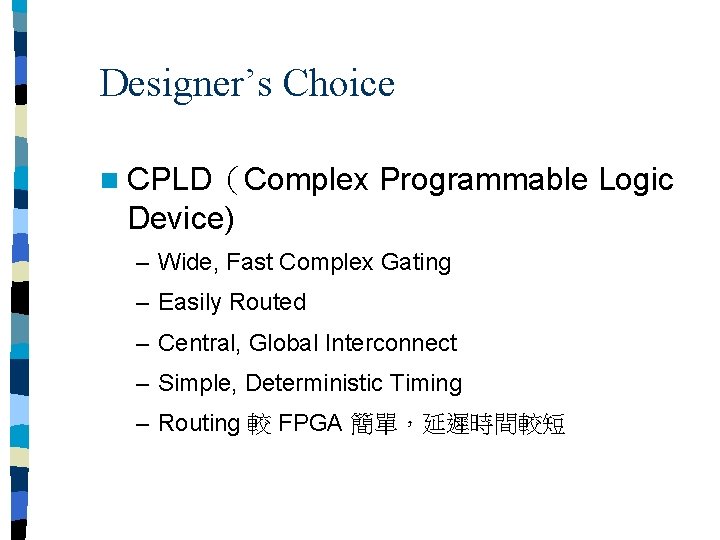

Designer’s Choice n CPLD(Complex Programmable Logic Device) – Wide, Fast Complex Gating – Easily Routed – Central, Global Interconnect – Simple, Deterministic Timing – Routing 較 FPGA 簡單,延遲時間較短

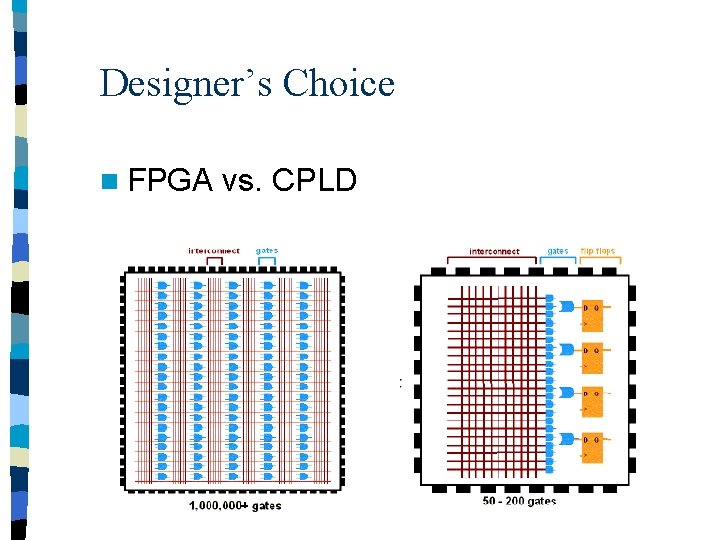

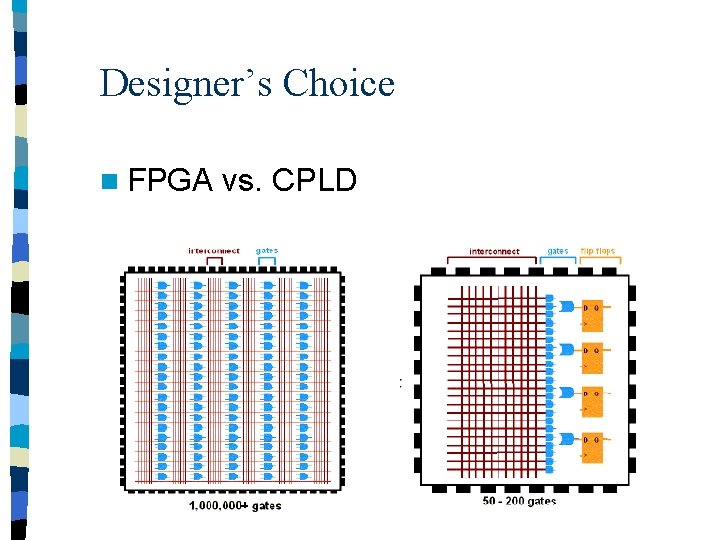

Designer’s Choice n FPGA vs. CPLD

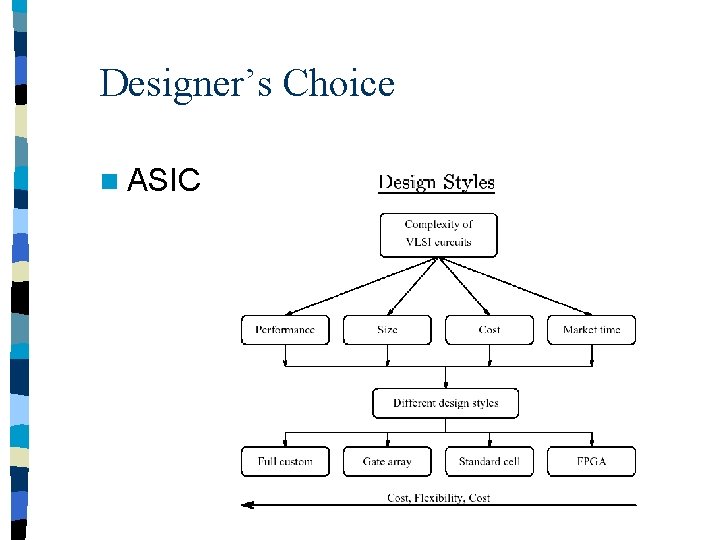

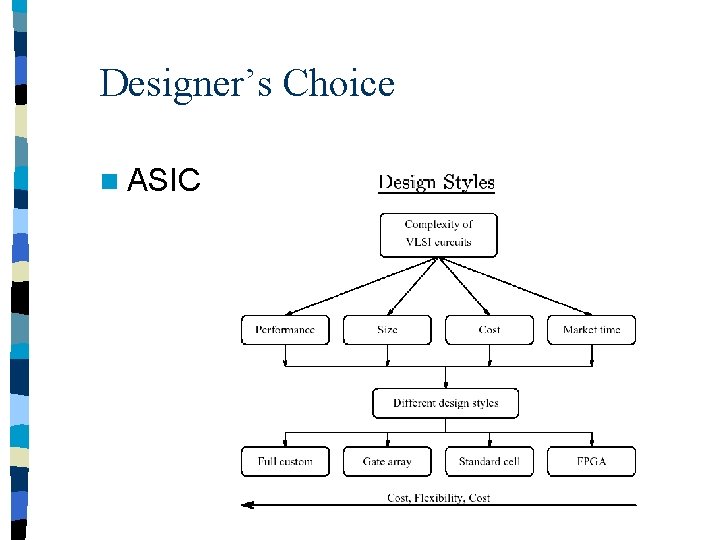

Designer’s Choice n ASIC

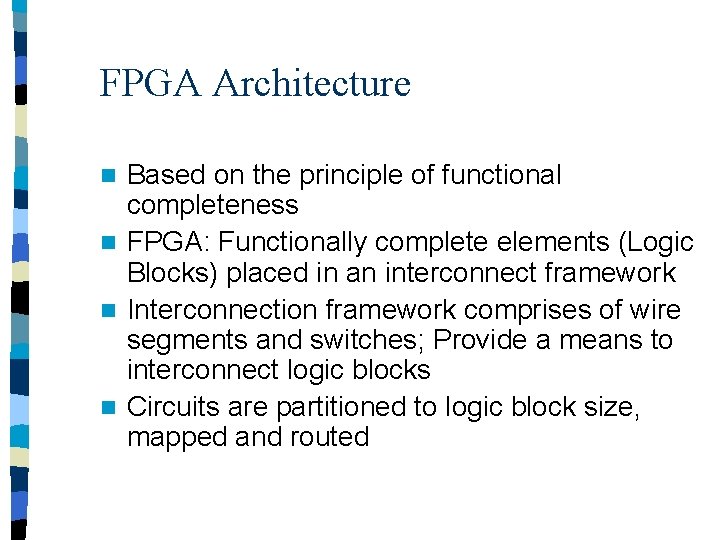

FPGA Architecture Based on the principle of functional completeness n FPGA: Functionally complete elements (Logic Blocks) placed in an interconnect framework n Interconnection framework comprises of wire segments and switches; Provide a means to interconnect logic blocks n Circuits are partitioned to logic block size, mapped and routed n

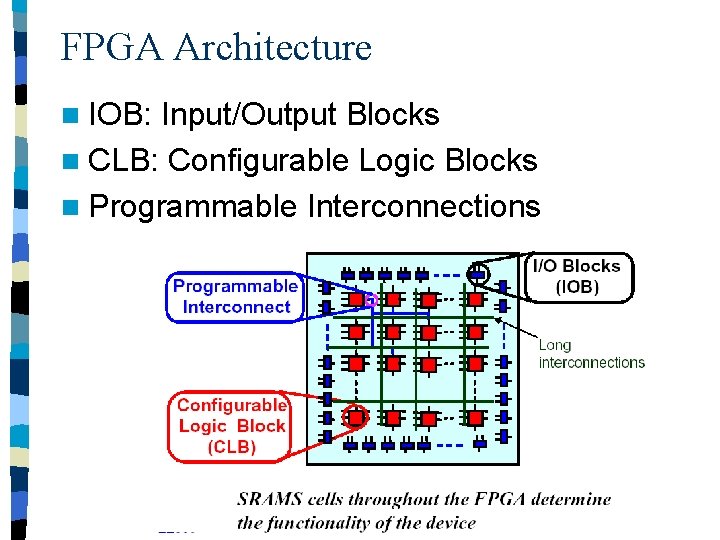

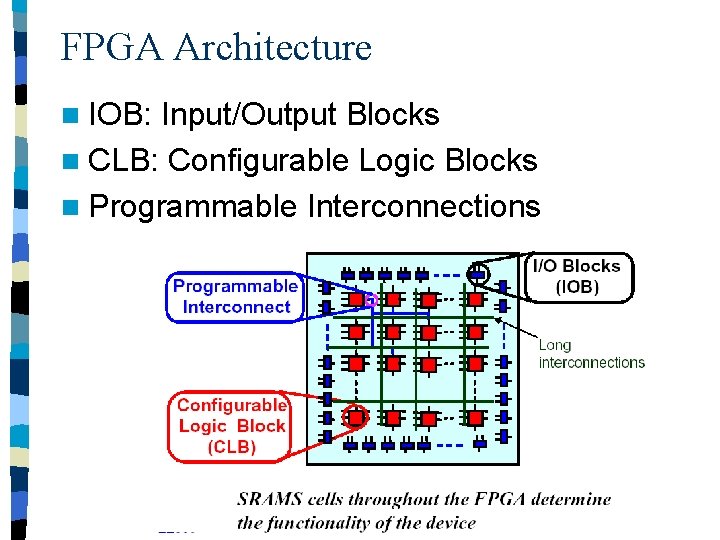

FPGA Architecture n IOB: Input/Output Blocks n CLB: Configurable Logic Blocks n Programmable Interconnections

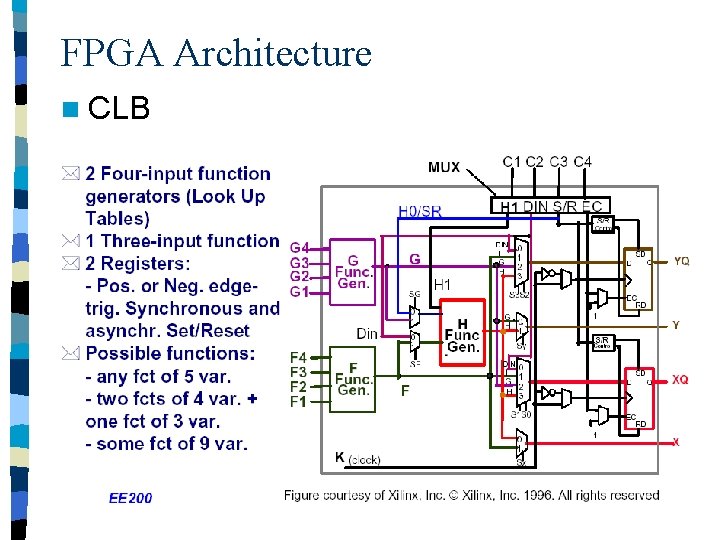

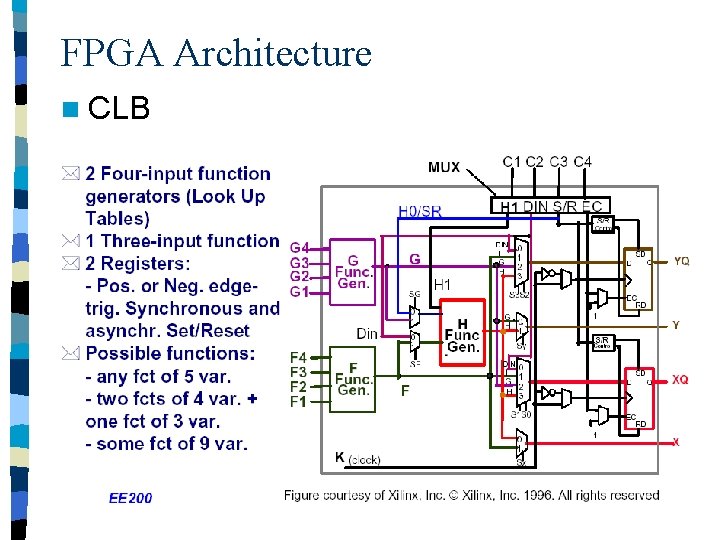

FPGA Architecture n CLB

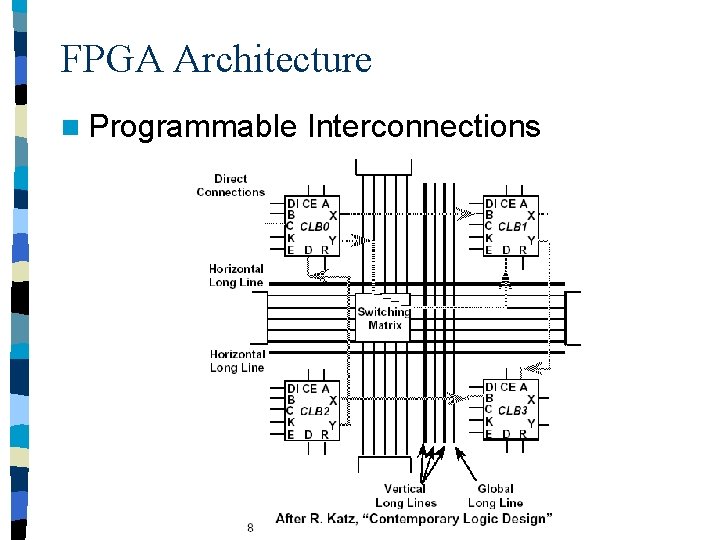

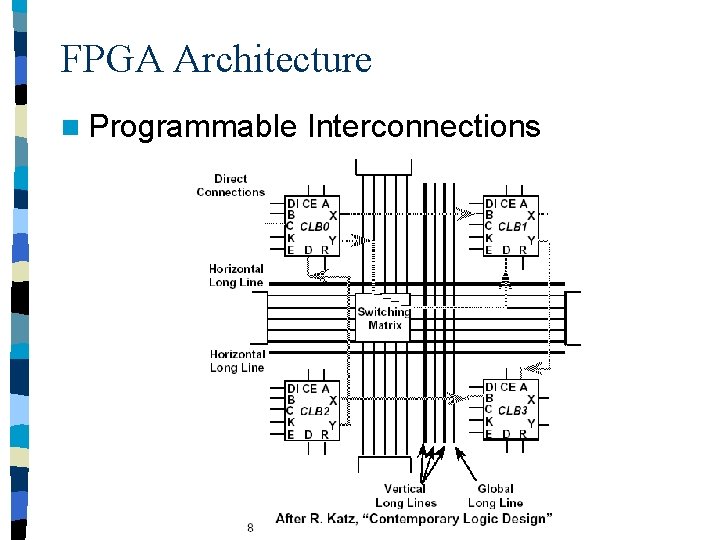

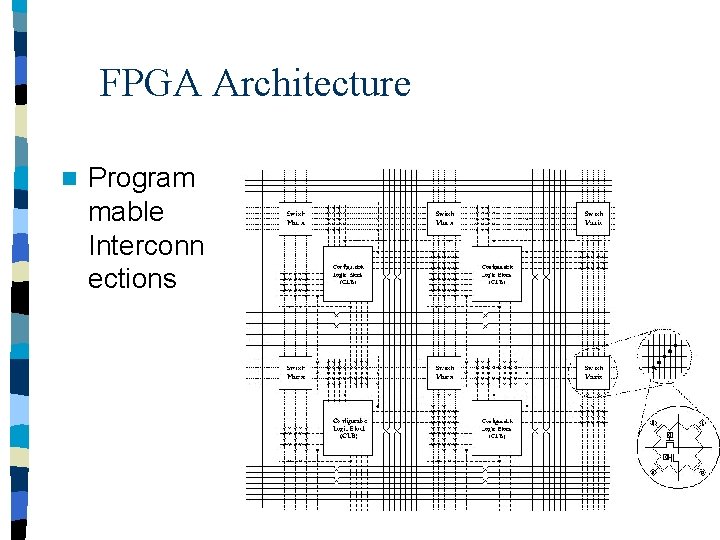

FPGA Architecture n Programmable Interconnections

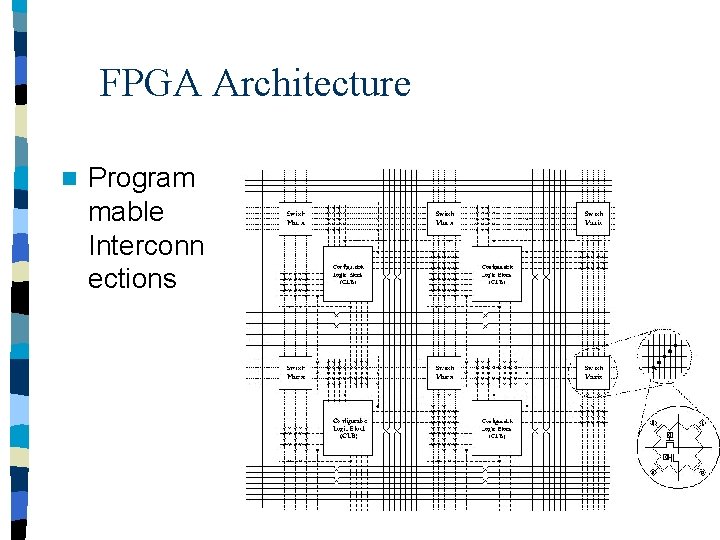

FPGA Architecture n Program mable Interconn ections

FPGA Architecture n Field Programmability – Achieve through switches (Transistors controlled by memory elements or fuses) – Switches control the following aspects • Interconnection among wire segments • Configuration of logic blocks – Distributed memory elements controlling the switches and configuration of logic blocks are together called “Configuration Memory”

FPGA Architecture n Technology of Programmable Elements – Vary from vendor to vendor. – All share the common property: Configurable in one of the two positions – ‘ON’ or ‘OFF’ – Can be classified into three categories: • SRAM based • Fuse based • EPROM/EEPROM/Flash based – Desired properties: – – Minimum area consumption Low on resistance; High off resistance Low parasitic capacitance to the attached wire Reliability in volume production

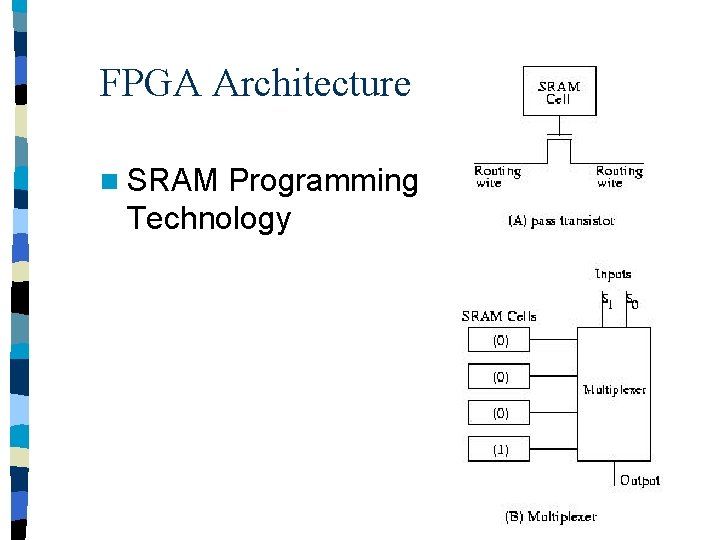

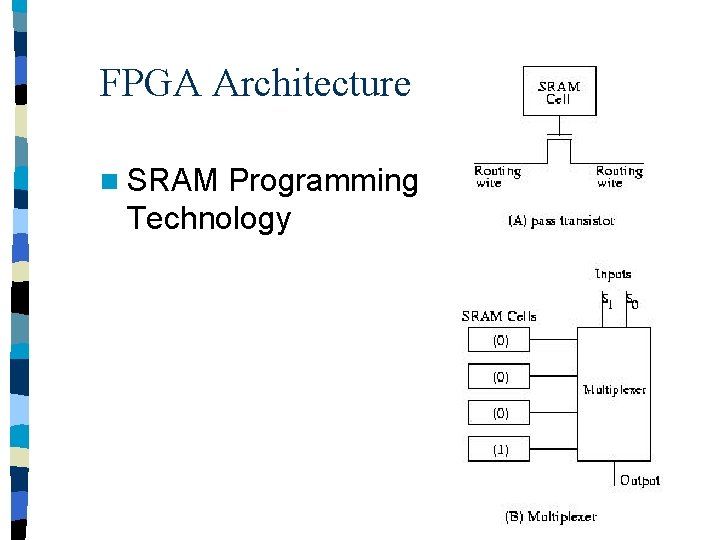

FPGA Architecture n SRAM Programming Technology – Employs SRAM (Static RAM) cells to control pass transistors and/or transmission gates – SRAM cells control the configuration of logic block as well – Volatile • Needs an external storage • Needs a power-on configuration mechanism • In-circuit re-programmable – Lesser configuration time – Occupies relatively larger area

FPGA Architecture n SRAM Programming Technology

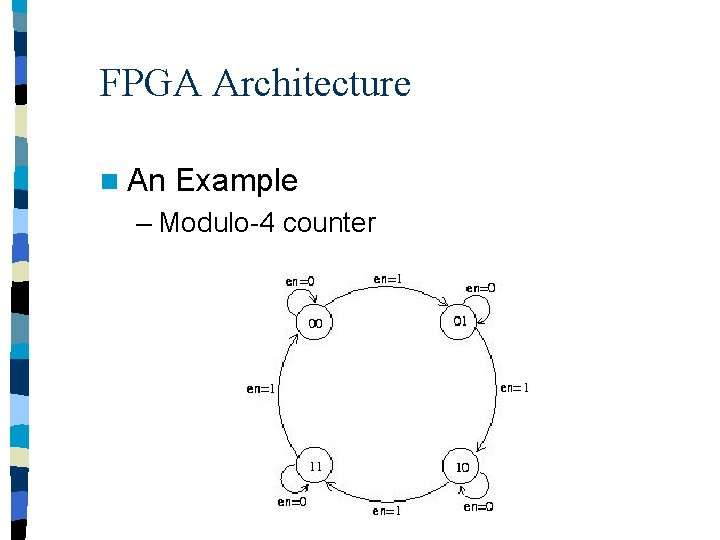

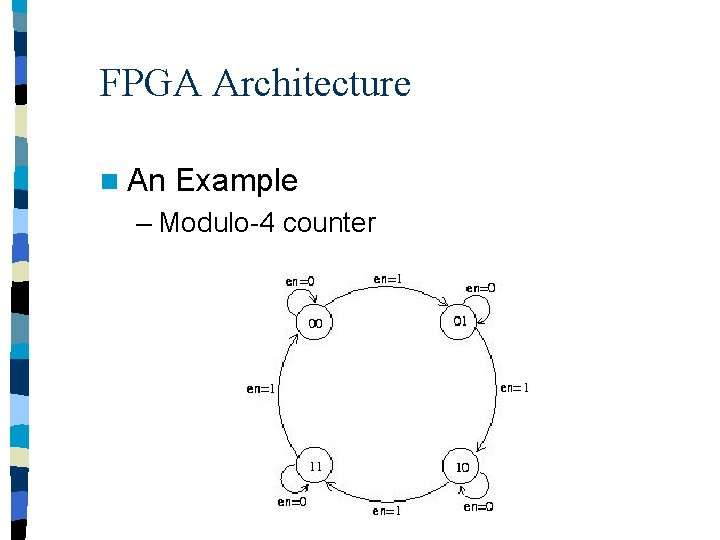

FPGA Architecture n An Example – Modulo-4 counter

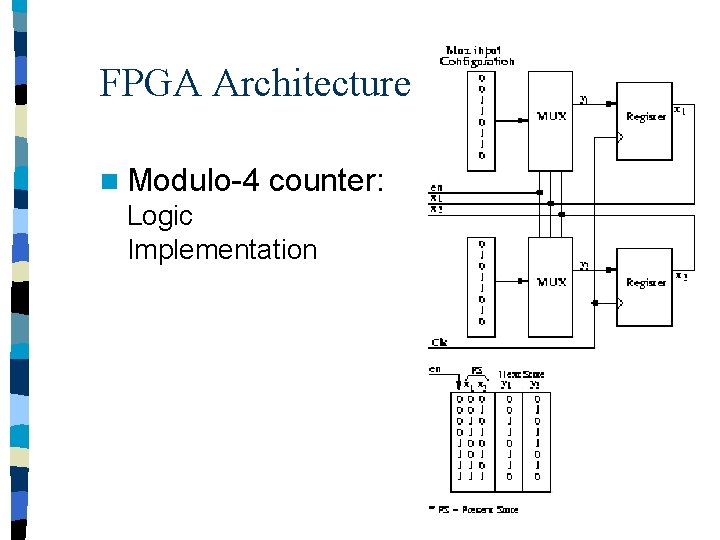

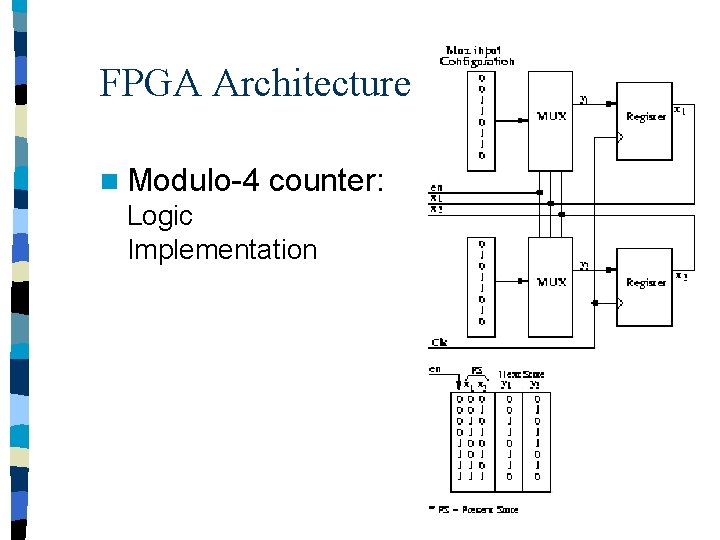

FPGA Architecture n Modulo-4 counter: Logic Implementation

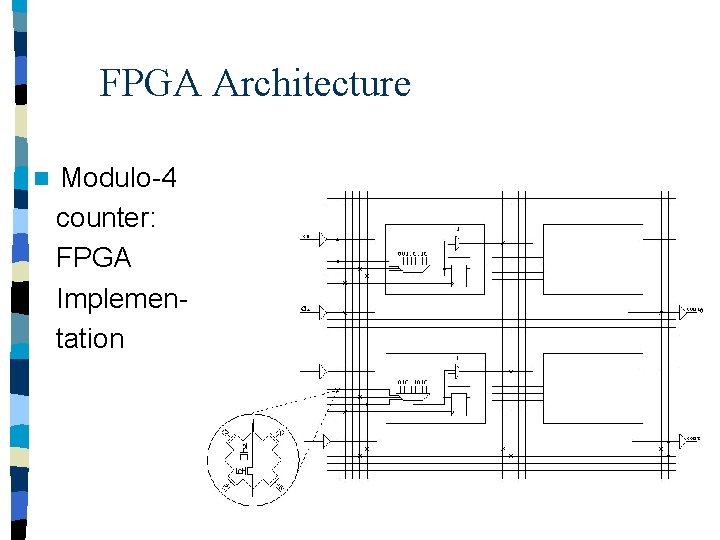

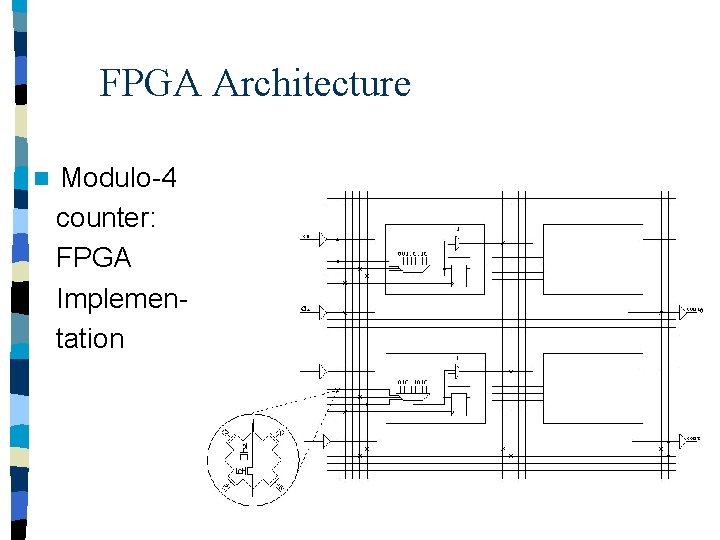

FPGA Architecture n Modulo-4 counter: FPGA Implementation

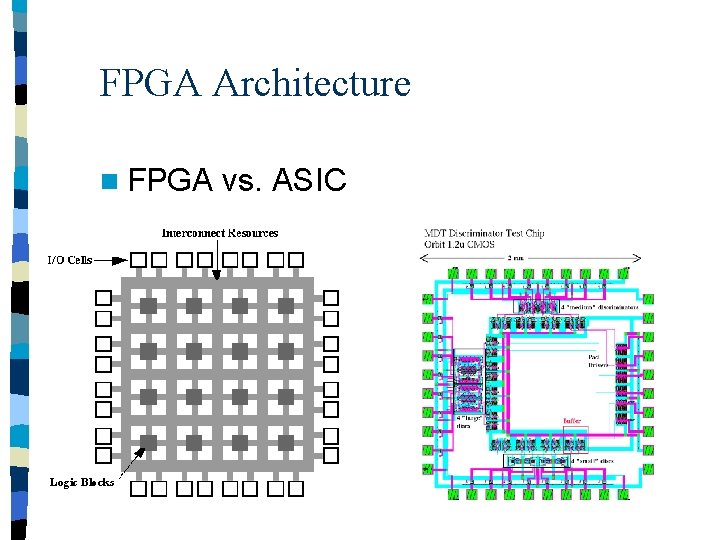

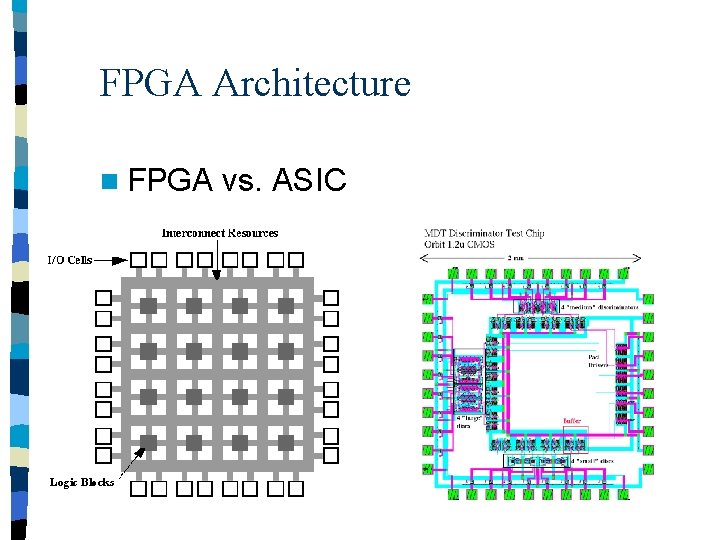

FPGA Architecture n FPGA vs. ASIC

Example: Spartan-II Architecture n Configurable logic blocks – Implement logic here! n I/O blocks – Communicate with other chips – Choose from 16 signal standards n Block RAM – On-chip memory for higher performance

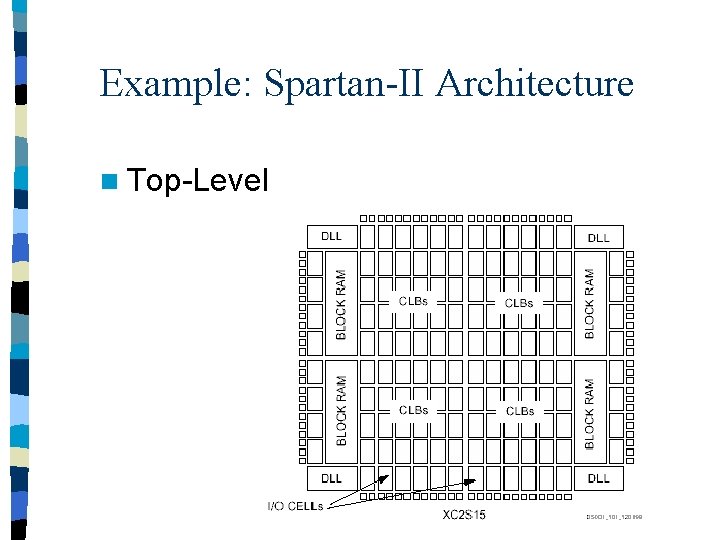

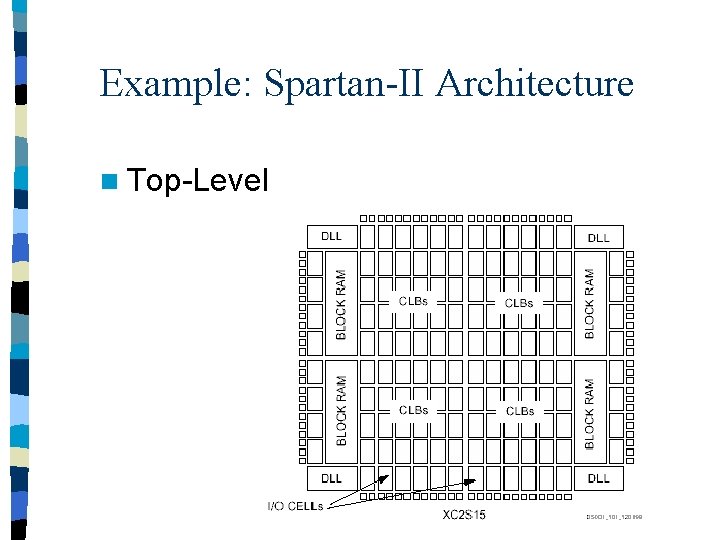

Example: Spartan-II Architecture n Top-Level

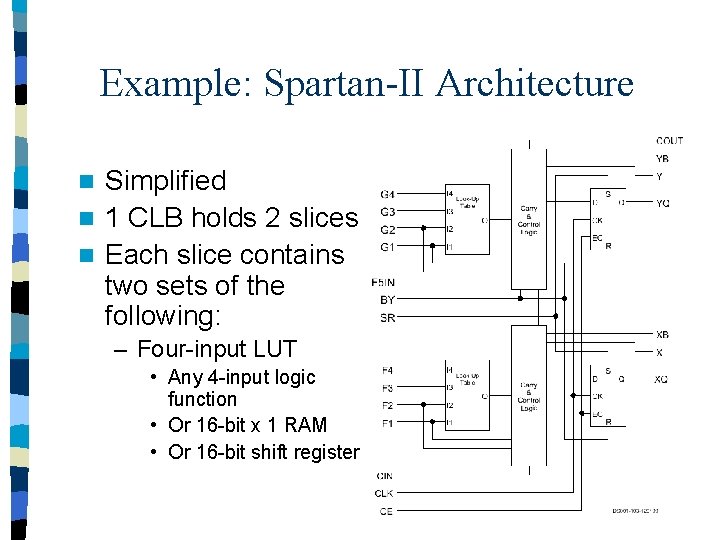

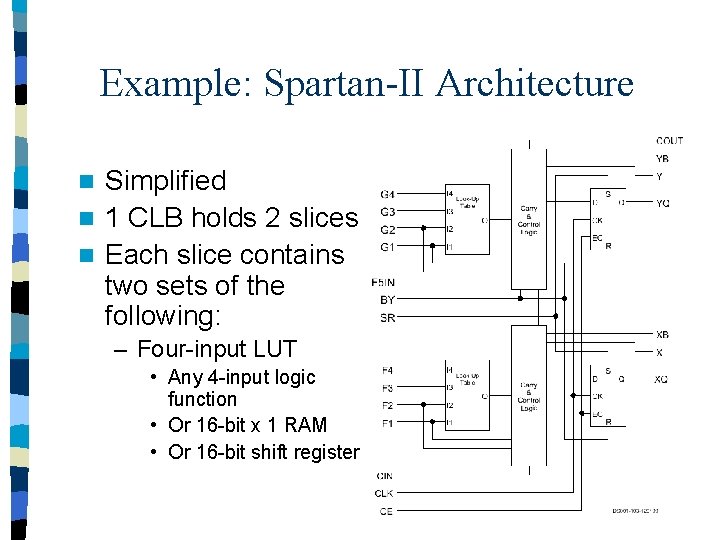

Example: Spartan-II Architecture Simplified n 1 CLB holds 2 slices n Each slice contains two sets of the following: n – Four-input LUT • Any 4 -input logic function • Or 16 -bit x 1 RAM • Or 16 -bit shift register

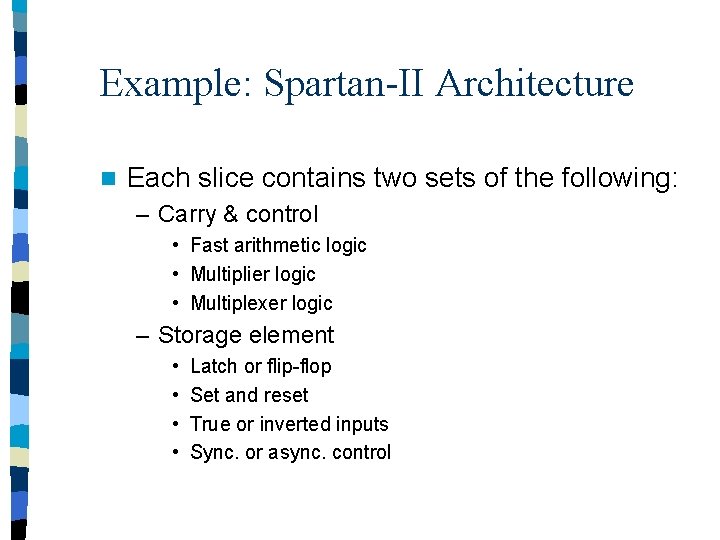

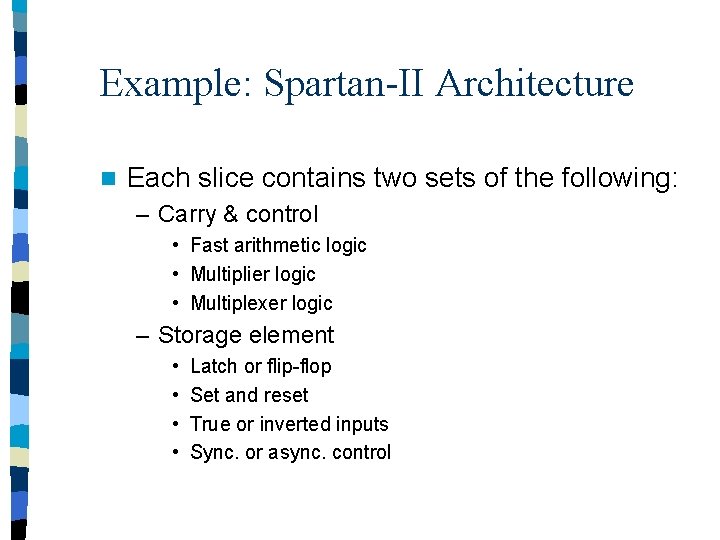

Example: Spartan-II Architecture n Each slice contains two sets of the following: – Carry & control • Fast arithmetic logic • Multiplier logic • Multiplexer logic – Storage element • • Latch or flip-flop Set and reset True or inverted inputs Sync. or async. control

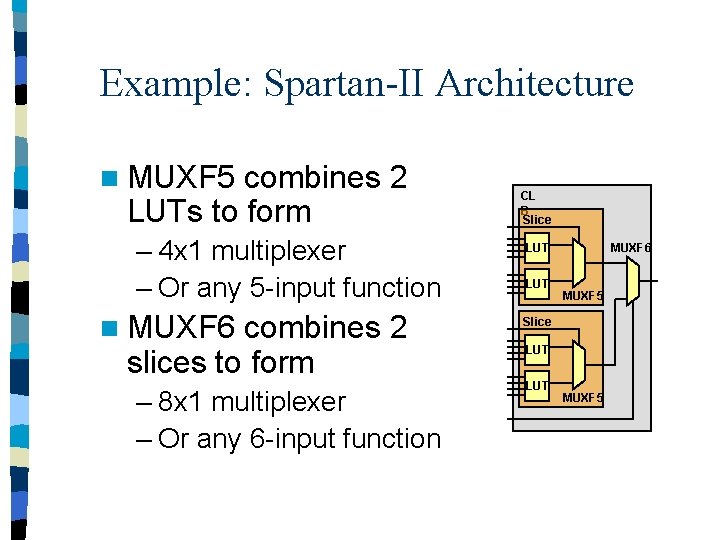

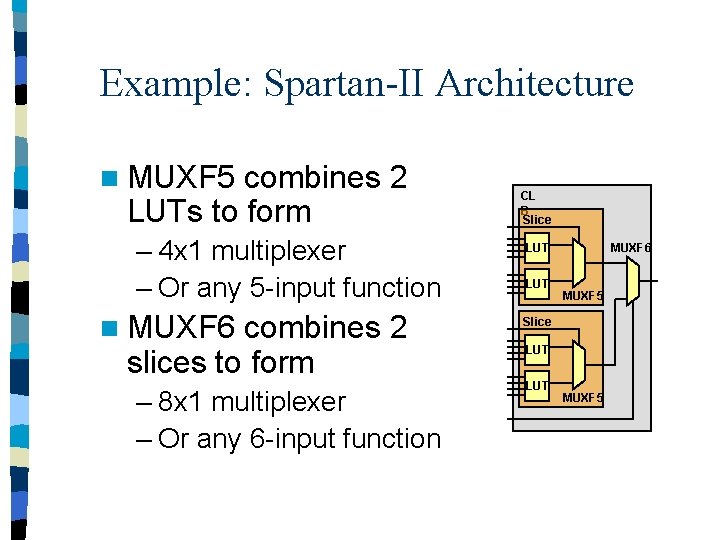

Example: Spartan-II Architecture n MUXF 5 combines 2 LUTs to form – 4 x 1 multiplexer – Or any 5 -input function n MUXF 6 combines 2 slices to form – 8 x 1 multiplexer – Or any 6 -input function CL B Slice MUXF 6 LUT MUXF 5 Slice LUT MUXF 5

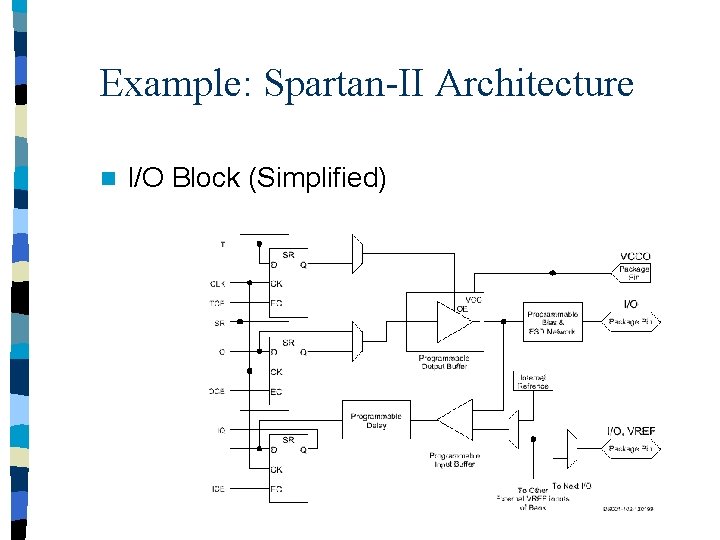

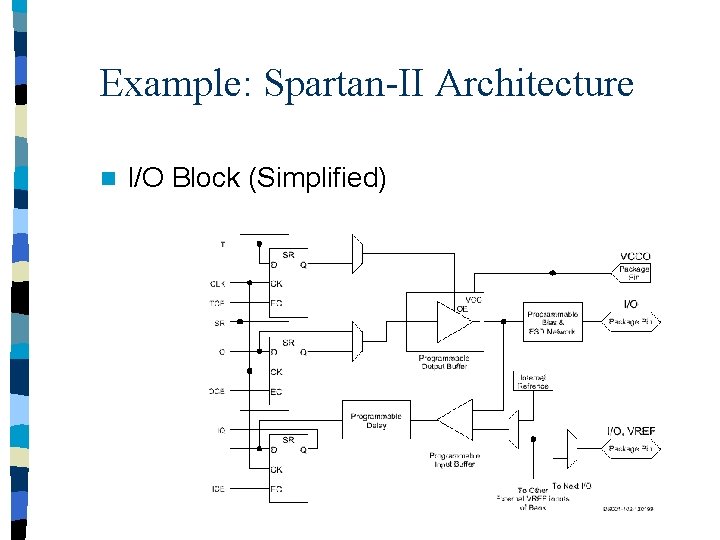

Example: Spartan-II Architecture n I/O Block (Simplified)

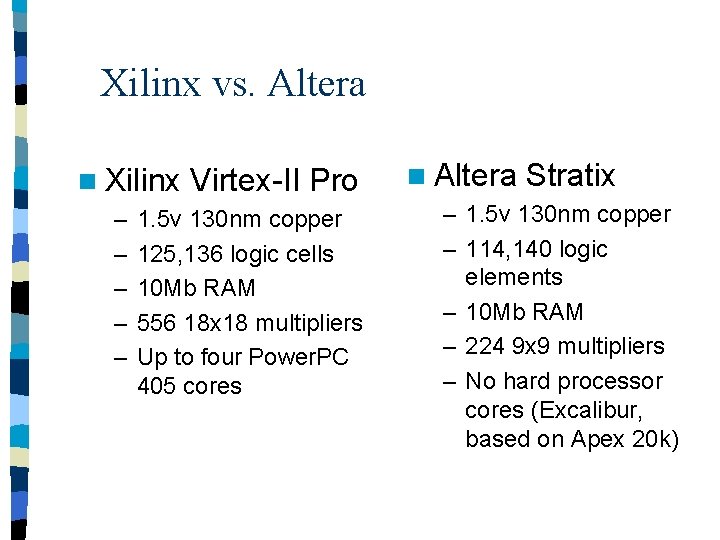

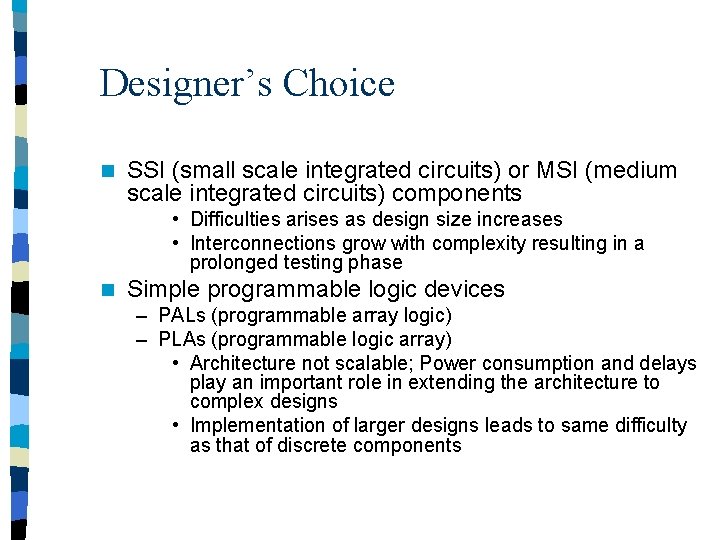

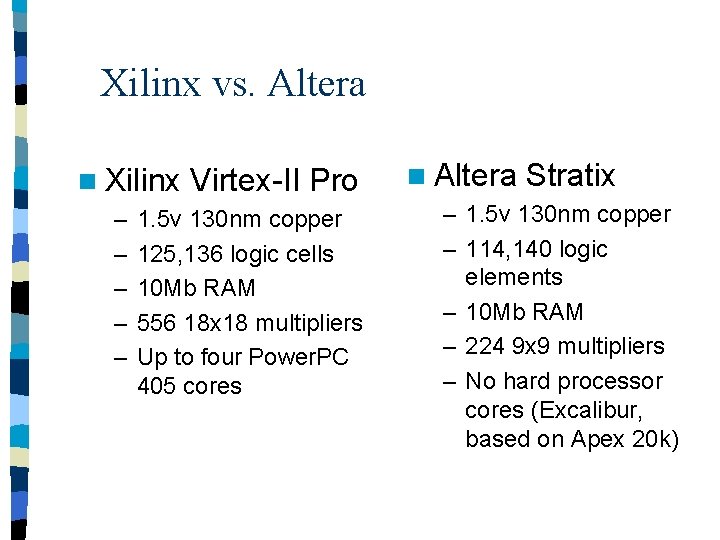

Xilinx vs. Altera n Xilinx – – – Virtex-II Pro 1. 5 v 130 nm copper 125, 136 logic cells 10 Mb RAM 556 18 x 18 multipliers Up to four Power. PC 405 cores n Altera Stratix – 1. 5 v 130 nm copper – 114, 140 logic elements – 10 Mb RAM – 224 9 x 9 multipliers – No hard processor cores (Excalibur, based on Apex 20 k)

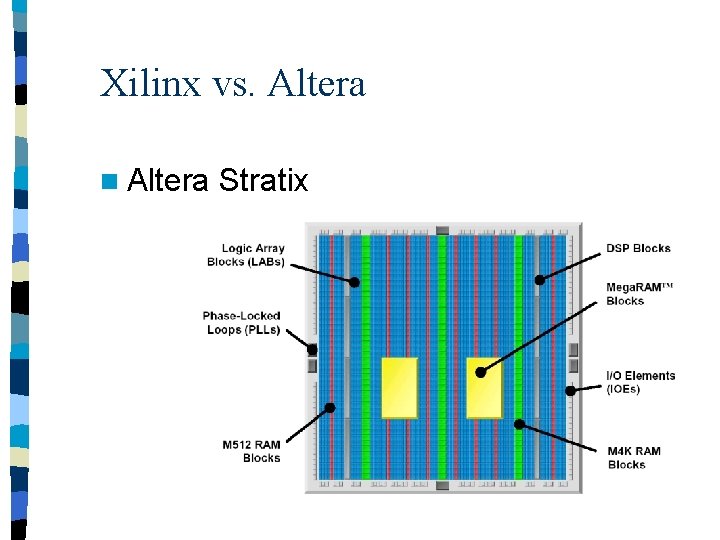

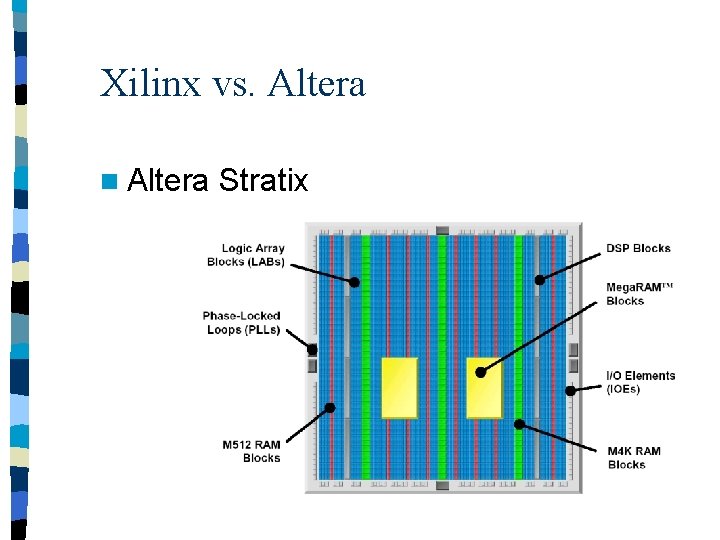

Xilinx vs. Altera n Altera Stratix

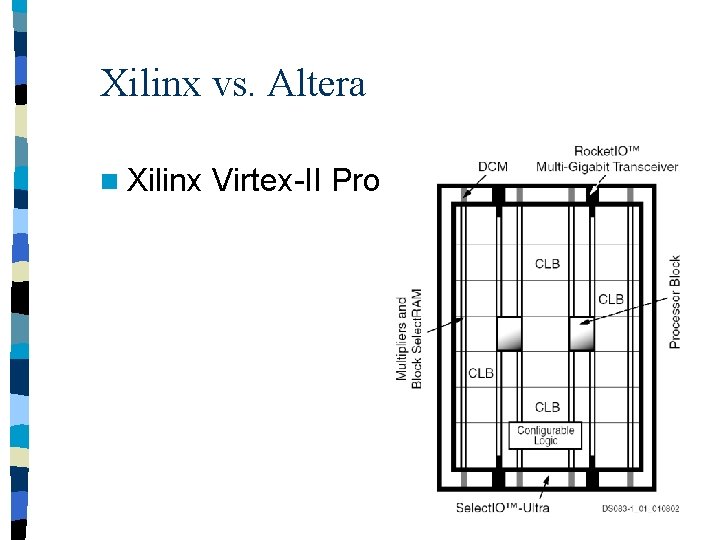

Xilinx vs. Altera n Xilinx Virtex-II Pro